Page 1

Service information

Control no.: 06SI010-R

CLARION Europa GmbH, Hessenring 19-21, 64546 Morfelden-Walldorf, ++49 6105 / 977-0 Fx / 977-100

06SI010-R 10.11.06 Page 1 of 2

HDD access error message

1) Model outline:

NAX963HD

2) Description:

The navigation shows “ACCESS ERROR” on the display, as shown below.

3) Solution

Reset the NAX963HD navigation unit to the factory setting by following

the below mentioned procedure:

1) Press “Menu” on the main unit.

2) Select “Settings” on the touch screen

3) Press “Next”

4) Select “ Service option”

5) Select “Reset to Factory Settings”

6) Press “OK”, when asked for.

Page 2

Service information

Control no.: 06SI010-R

CLARION Europa GmbH, Hessenring 19-21, 64546 Morfelden-Walldorf, ++49 6105 / 977-0 Fx / 977-100

06SI010-R 10.11.06 Page 2 of 2

Attention:

All user data on the hard drive will be lost and the factory settings will be

installed again.

After the installation of the factory settings, the NAX963HD will start up

automatically.

It may happen that the NAX963HD show this error message again. In this

case, switch off the unit and restart it manually. Now the error message

shall not be shown again.

In case the error message will not disappear, a hardware defect on the

unit is detected and the unit has to be exchanged via CEF.

Page 3

NAX963HD

- 1 -

Service Manual

Published by Service Dept.

Printed in Japan

Clarion Co., Ltd.

50 Kamitoda, Toda-shi, Saitama 335-8511 Japan

Service Dept.: 5-66 Azuma , Kitamoto-shi, Saitama 364-0007 Japan

Tel: +81-48-541-2335 / 2432 FAX: +81-48-541-2703

298-6375-00

AUG.2006

Model

HDD Navigation System

(QY-5000E-A)

SPECIFICATIONS

Navigation System

GPS receiving frequency:

1575.42 MHz, C/A Code

Sensibility: -130 dBm or better

Number of GPS channels:

15 channels

Voice synthesis: ADPCM,

Sampling frequency;11.025 kHz

Power supply voltage: +14V

Ground: Negative

Current consumption: less than 3.0A

Dimensions(mm): 205(W)x29.5(H)x169(D)

GPS aerial

Mode: Microstrip flat aerial

Dimensions(mm): 30.4(W)x11.7(H)x35.5(D)

Impedance: 50 ohm

NOTES

About the hard disk drive

* Data saved to the hard disk drive may get lost in case of

a breakdown, malfunction, or other trouble of this unit.

Importing Data via USB Port

* Data may be broken when using USB memories sticks

in the following situation: When disconnecting the USB

memory stick or turning the power off during writing or

reading data. When affected by static electricity or electric noises.

* Music files (MP3, WMA, etc.) stored in the USB memory

stick cannot be played back.

("Data" : Including the stored locations and their data,

route data, data stored in the Favourite & Frequent List,

setting data set from the Setting menu, and data imported

from the USB memory stick (Wallpapers, Safety Camera locations, etc.)

* The special equipment is necessary to replace IC103.

* We cannot supply PWB with component parts in

principle. When a circuit on PWB has failure, please

repair it by component parts base.

Parts which are not mentioned in service manual are

not supplied.

* Specifications and design are subject to change without

notice for further improvement.

This product is a lead free model.

Lead free solder is used in PWB stamped LF mark.

Please keep the following conditions when you repair.

1. Use lead free solder.

* Koki's lead free solder S3X-55M 0.6mm

(CLARION Parts No.642-0231-01)

* Koki's lead free solder S3X-55M 1.0mm

(CLARION Parts No.642-0231-02)

2. Use a nitrogen solder system.

3. Do not use "General solder" and "Lead free solder"

together.

Page 4

NAX963HD

- 2 -

To engineers in charge of repair or

inspection of our products.

Before repair or inspection, make sure to follow the

instructions so that customers and Engineers in charge

of repair or inspection can avoid suffering any risk or

injury.

1. Use specified parts.

The system uses parts with special safety features against fire

and voltage. Use only parts with equivalent characteristics

when replacing them.

The use of unspecified parts shall be regarded as remodeling

for which we shall not be liable. The onus of product liability

(PL) shall not be our responsibility in cases where an accident

or failure is as a result of unspecified parts being used.

2. Place the parts and wiring back in their original positions after

replacement or re-wiring.

For proper circuit construction, use of insulation tubes, bonding, gaps to PWB, etc, is involved. The wiring connection and

routing to the PWB are specially planned using clamps to keep

away from heated and high voltage parts. Ensure that they are

placed back in their original positions after repair or inspection.

If extended damage is caused due to negligence during repair, the legal responsibility shall be with the repairing company.

3. Check for safety after repair.

Check that the screws, parts and wires are put back securely

in their original position after repair. Ensure for safety reasons

there is no possibility of secondary ploblems around the repaired spots.

If extended damage is caused due to negligence of repair, the

legal responsibility shall be with the repairing company.

4. Caution in removal and making wiring connection to the parts

for the automobile.

Disconnect the battery terminal after turning the ignition key

off. If wrong wiring connections are made with the battery connected, a short circuit and/or fire may occur. If extensive damage is caused due to negligence of repair, the legal responsibility shall be with the repairing company.

5. Cautions in soldering

Please do not spread liquid flux in soldering.

Please do not wash the soldering point after soldering.

6. Cautions in soldering for chip capacitors

Please solder the chip capacitors after pre-heating for replacement because they are very weak to heat.

Please do not heat the chip capacitors with a soldering iron

directly.

7. Cautions in handling for chip parts.

Do not reuse removed chips even when no abnormality is observed in their appearance. Always replace them with new

ones. (The chip parts include resistors, capacitors, diodes, transistors, etc).

Please make an operation test after replacement.

8. Cautions in handling flexible PWB

Before working with a soldering iron, make sure that the iron

tip temperature is around 270 . Take care not to apply the

iron tip repeatedly(more than three times)to the same patterns.

Also take care not to apply the tip with force.

9. Turn the unit OFF during disassembly and parts replacement.

Recheck all work before you apply power to the unit.

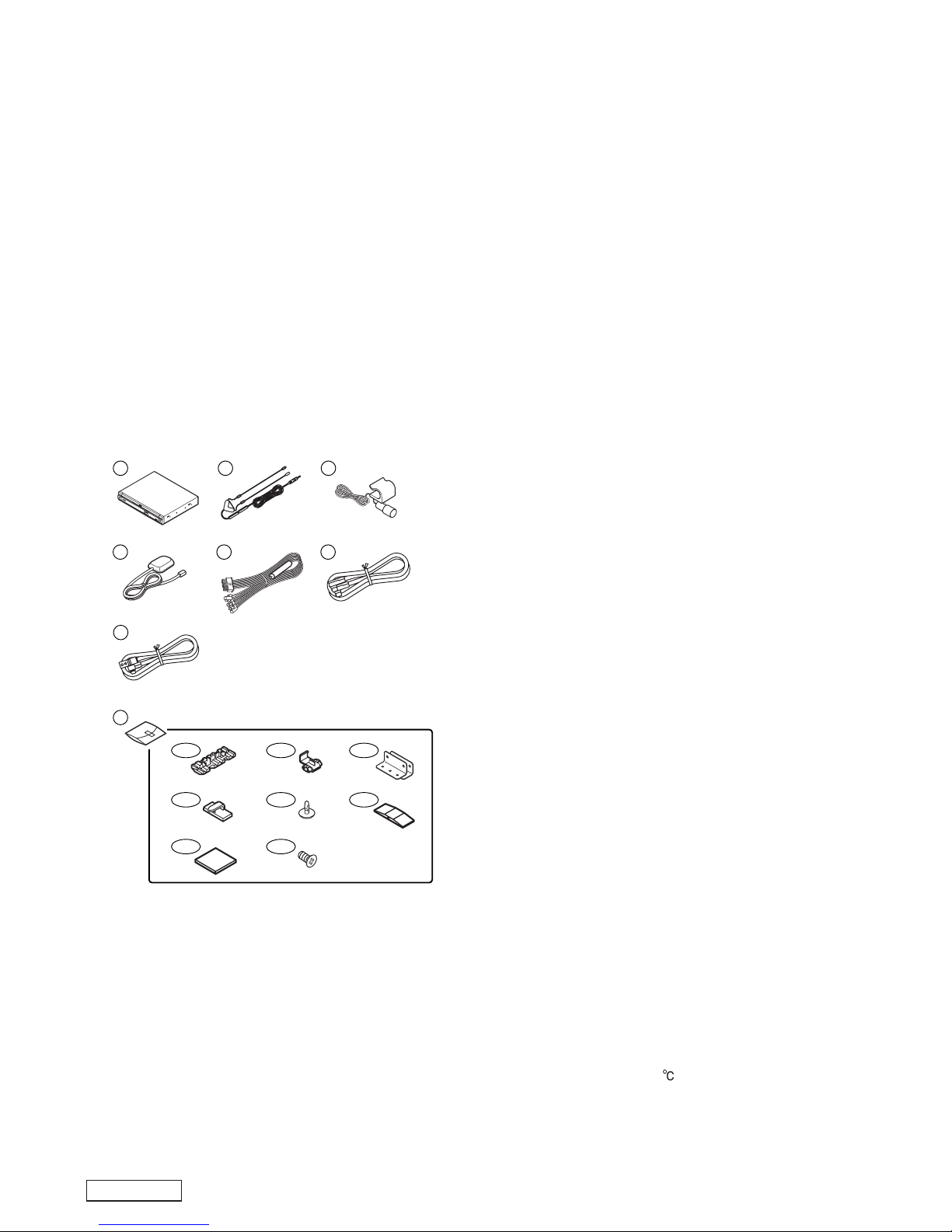

COMPONENTS

QY-5000E-A

1. Main unit ----------- 1

2. RDS-TMC amtenna ZCA-412-310 1

3. Microphone for voice control 081-0034-00 1

4. GPS antenna 096-0147-00 1

5. Power supply lead 854-6451-50 1

(5A Fuse 120-0050-00 1)

6. RGB cable(2.5m) 855-2433-01 1

7. CeNET cable(2.5m) 855-3421-90 1

8. Accessory bag ----------- 1

8-1. Electro-tap(for speed sensor) 060-0018-00 2

8-2. Electro-tap 060-0305-00 1

8-3. Mounting bracket 300-7362-03 2

8-4. Cord holder 321-1026-01 10

8-5. Canoe clip 335-2515-00 4

8-6. Waterproof rubber 345-7473-00 1

8-7. Double-sided tape for fastening the antenna

347-6369-00 1

8-8. Inatallation bolt(M4x6) 714-4006-8B 4

1 2 3

4 5 6

7

8

8-1 8-2 8-3

8-4 8-5 8-6

8-7 8-8

Page 5

NAX963HD

- 3 -

The provider of RDS-TMC is not

automatically selected.

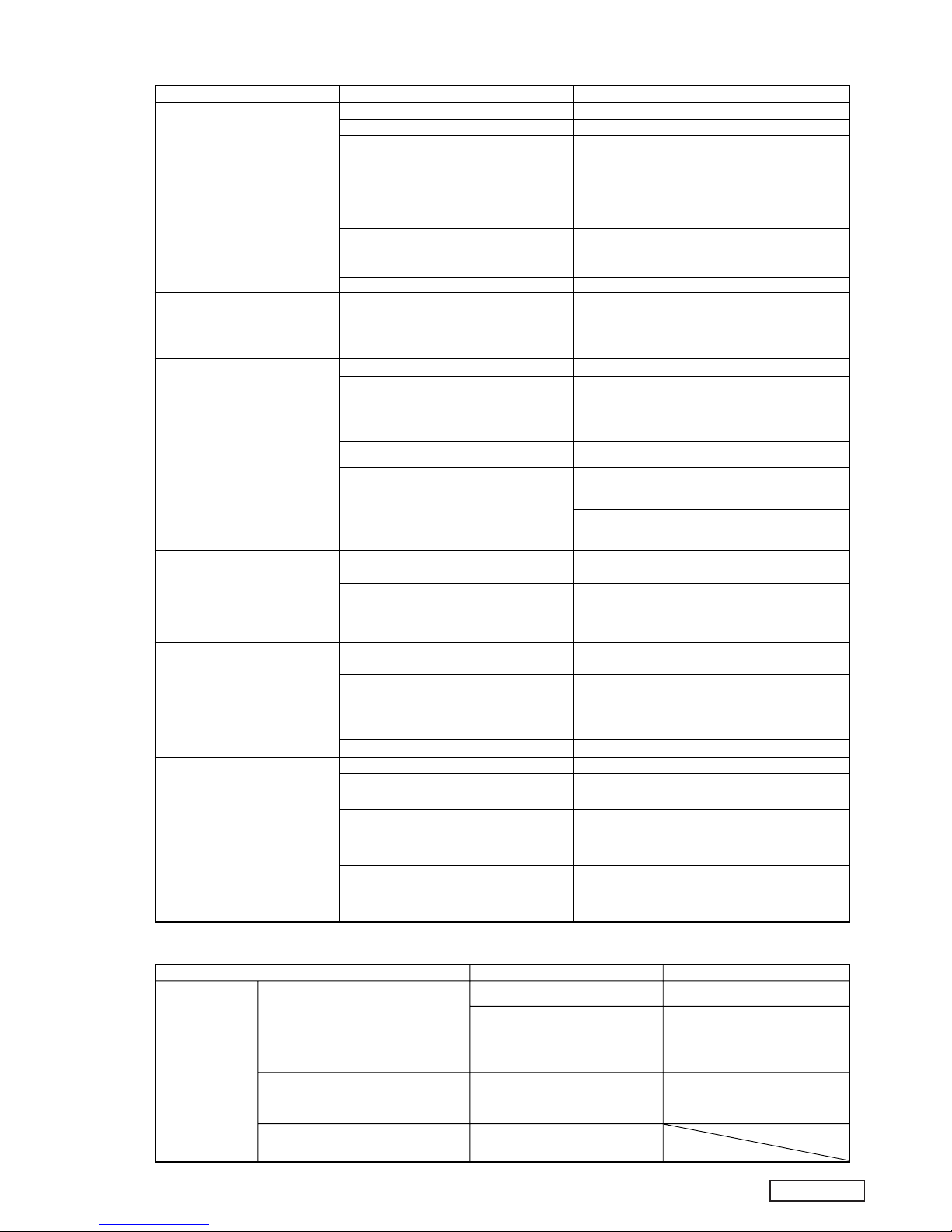

Error Message Cause Remedy

USB memory

device

ACCESS ERROR

The USB memory device cannot be

accessed.

The USB memory is not

connected correctly.

Connect the USB memory again.

The USB memory is not recognised.

Connect another USB memory.

Hard Disk Drive

TEMP ERROR

Cannot operate correctly due to high

temperature. Please wait until

temperature becomes normal again.

The HDD cannot be accessed

because the temperature in the

vehicle is extremely high

Please wait until the temperature

becomes appropriate.

TEMP ERROR

Cannot operate correctly due to low

temperature. Please wait until

temperature becomes normal again.

The HDD cannot be accessed

because the temperature in the

vehicle is extremely low

Please wait until the temperature

becomes appropriate.

ACCESS ERROR

Malfunction occured in the HDD.

Please consult your nearest dealer.

The HDD cannot be accessed.

The sectors or clusters of the

HDD may be damaged.

Problem Check point Remedy

Connection of power cable

Connection of RGB cable

Output of RGB signal

Output level of RGB signal

Dot clock

Connect power cable properly.

Confirm the frequency of the dot clock. (TP534)

Connect RGB cable properly.

Connect microphone properly.

Connect GPS antenna properly.

Connect antenna properly.

Change the installation position.

Separate from the antenna of the vehicle.

(especially, glass antenna)

Connect internal wiring (ANT700,ANT701) properly.

Connect speed pulse cable properly.

Connection of CeNET cable

Connect CeNET cable properly.

Power supply circuit

Confirm the output voltage of the power properly.

TP1000 HDD_5V

TP1001 D_5V

TP1003 D_3.3V

TP1008 DDR_2.5V

TP1004 VCC 1.22V

Confirm the output of RGB signal.

TP1115 R

TP1116 G

TP1114 R

Confirm the output level of RGB signal.

TP1115 R

TP1116 G

TP1114 R

Confirm collector voltage of Q803.

0V : MUTE-ON

3.3V : MUTE-OFF

Confirm IC800.

pin9(SDTO):Data output according to voice input.

pin10(LRCK):11.025KHz

pin11(MCLK):8.46MHz

pin12(SCLK):705KHz

Confirm collector voltage of Q801.

0V : MUTE-ON

3.3V : MUTE-OFF

Confirm audio wave form of TP801(AD_IN).

Confirm an output signal of TP1105(ECC).

Confirm the power supply voltage.

TP2101 R_TU8V

TP2113 TUNER3.2V

Confirm the oscillation of X2102(10MHz)

and output power of TP2209 (BU5V).

Measure pin1(VOUT) of Gyro(IC702) with the

tester. Confirm the voltage.

At geostationary: about 2.5V

When sets are rotatedand: voltage moves.

Confirm IC801.

pin1(LRCK):11.025KHz

pin18(MCLK):8.46MHz

pin19(BCLK):705KHz

pin20(DIN):Data input

Confirm an analog aoudio signal output of pin12 of

IC801.

HDD

Insert HDD, and put protecting.

Adjust the volume properly.

The color of the screen is defective.

Guide voice doesn't sound.

Volume level of guide voice

Clock and data input of DAC(IC801)

Output of DAC(IC801)

MUTE setting

Connection of microphone

Connection of speed pulse

Connection of GPS antenna

Connection of antenna

Setting position of window antenna

Noise source in car (PC,DC/AC converter)

Connection of internal wiring

Wave form of speed pulse

Input signal of ADC(IC800)

Clock and data output of ADC(IC800)

Gyro sensor

Stop the equipment that generates the noise.

Tuner Pack

RDS/TMC microcomputer

Selection of "TMC Provider screen".

Select "Automatic".

Power indicator doesn't light.

(The power supply doesn't enter).

Screen is not displayed.

Map is not displayed.

The car position doesn't move.

GPS reception is defective.

RDS-TMC reception is defective.

Voice recognition is defective.

TROUBLESHOOTING

ERROR MESSAGES

Page 6

NAX963HD

- 4 -

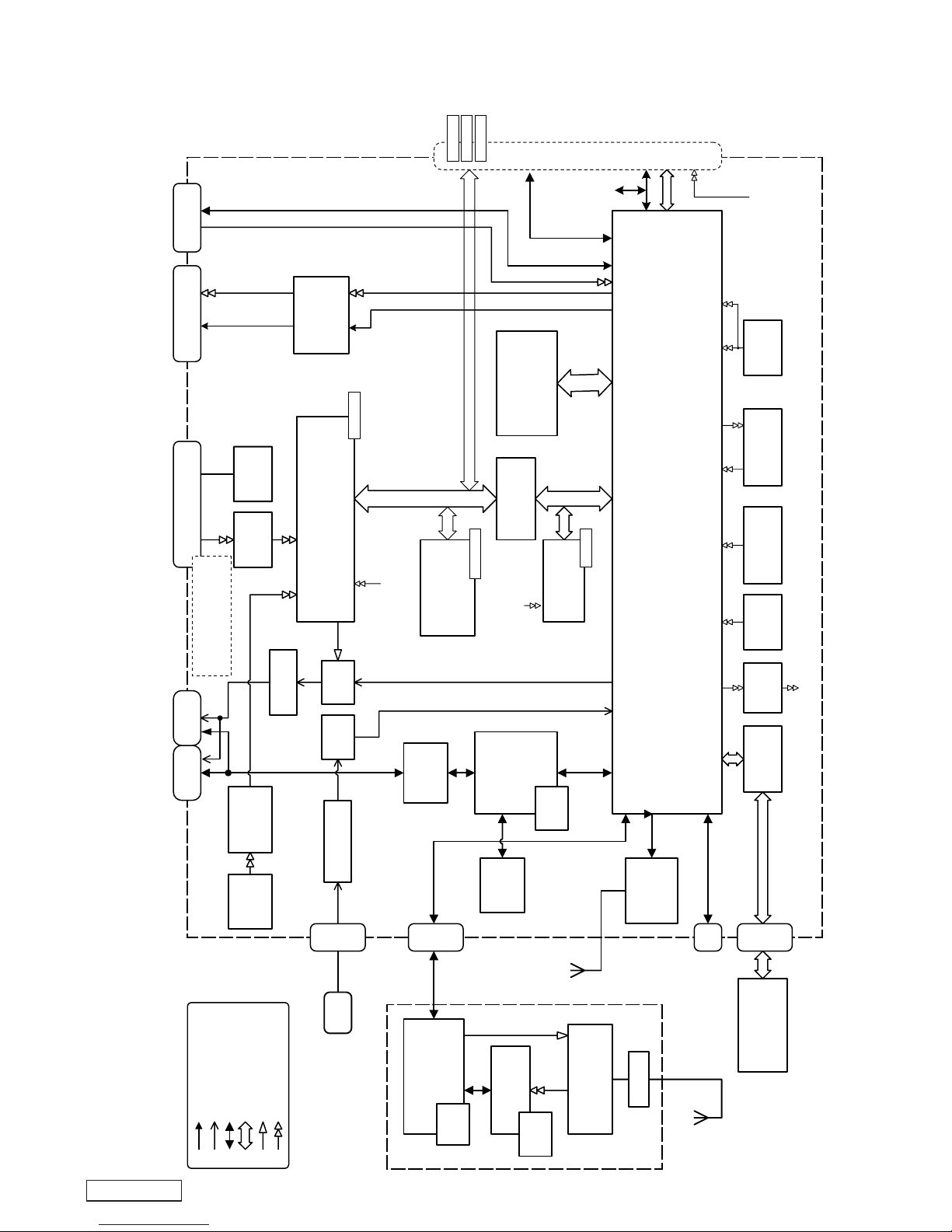

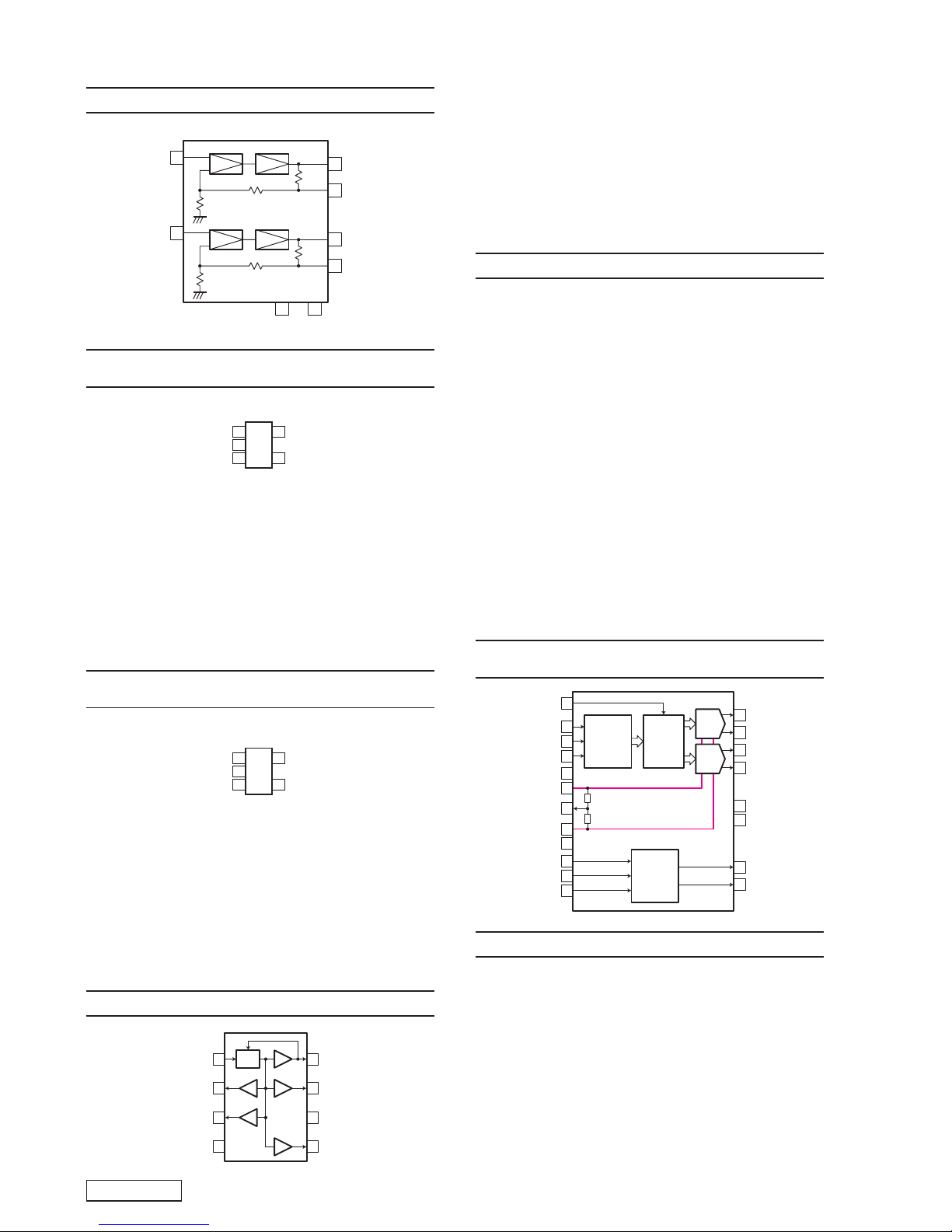

IC403

SRAM

512KB

IC200,IC201,

IC202,IC203

DDR-SDRAM

128MB(256Mbx4)

IC400

DISK ON CHIP

64MB

IC800

ADC

SENSOR

I/F

J1102 J1103 P701

(Connector for production)

IC700

ADC

BL700

GPS

Tuner Pack

J701

IC702

GYRO

SENSOR

J800

MIC

IC803

FILTER

R/G/B

IC401

BUS BUFER

16

64

16

16

IC501

FPGA

CSYNC

IC103

CPU

IC602

BUS

BUFFER

2.5inch 30GB

HARD DISK DRIVE

16

SCIF5

SCIF0

USB Host

ATAPI

RGB

DDR I/FEX-BUS

SSI0

SSI1

CS0

EX_CS0

8

H-UDI

JTAG

IC801

DAC

Control

IR IN

(96MHz)

(32MHz)

IC1102,IC1103

RGB

BUFFER

GUIDE

SIG.

TTS/WAVE (GUIDE VOICE)

VOICE RECOGNITION

16

X101

OSC

48MHz

X100

OSC

14.31818MHz

EXTALDOTCLKIN USBCLKAUDIO_CLK

CLKOUT

(CKIO)

32MHz

- FPGA

- DOC

- DEBUG CN

CLKIN(CKIO)

From SH7770

32MHz

EX_CS2

IC909

MICOM

IC912

IE-BUS

DRIVER

X900

XTAL

10MHz

IC802,IC804

BUFFER

SCIF2

UART

J500(Unmounting)

DEBUG CONNECTOR for Development

X102

OSC

8.46MHz

IC2105

MICOM

RDS-

DEMODURATOR

IC2102

BL2101

RDS/TMC Tuner

C2B

X2102

XTAL

10MHz

X2101

XTAL

4.33MHz

UART

UART

UART

SCIF7

16

EX_CS4

EX_CS7

EX_CS1

From SH7770

32MHz

From SH7770

32MHz

IC908

EEPROM

1Kbit

Note

RDS-TMC PWB Block

Main PWB Block

J1100 J1101

Control signal

Other signal

Video signal

Audio signal

㪧㪸㫉㪸㫃㫃㪼㫃㩷BUS

㪪㪼㫉㫀㪸㫃㩷㪺㫆㫄㫄㫌㫅㫀㪺㪸㫋㫀㫆㫅

CSYNC

TP

IC505

PLL

(9.1101MHz㪄10.085663MHz)

PDOUT4FSCEXCLK

SCIF4

ANT AMP

RDS-TMC

ANT

GPS

ANT

POWER

SUPPLY

BLOCK

Q1100,Q1101,IC1100,IC1101

SENSOR I/F:

PKB,BACK,ECC

B/U

12V

IC502

BUFFER

MIC CON.

CeNET

CONN.

CeNET

CONN.

To RDS

CONNECT.

HDD

CONNECT.

USB

CON.

BU12V, PKB/BACK/ECC

CONNECTOR

RGB

CONNECTOR

SERIAL

CONNECTOR

BLOCK DIAGRAM

Video/Audio/Control block

Page 7

NAX963HD

- 5 -

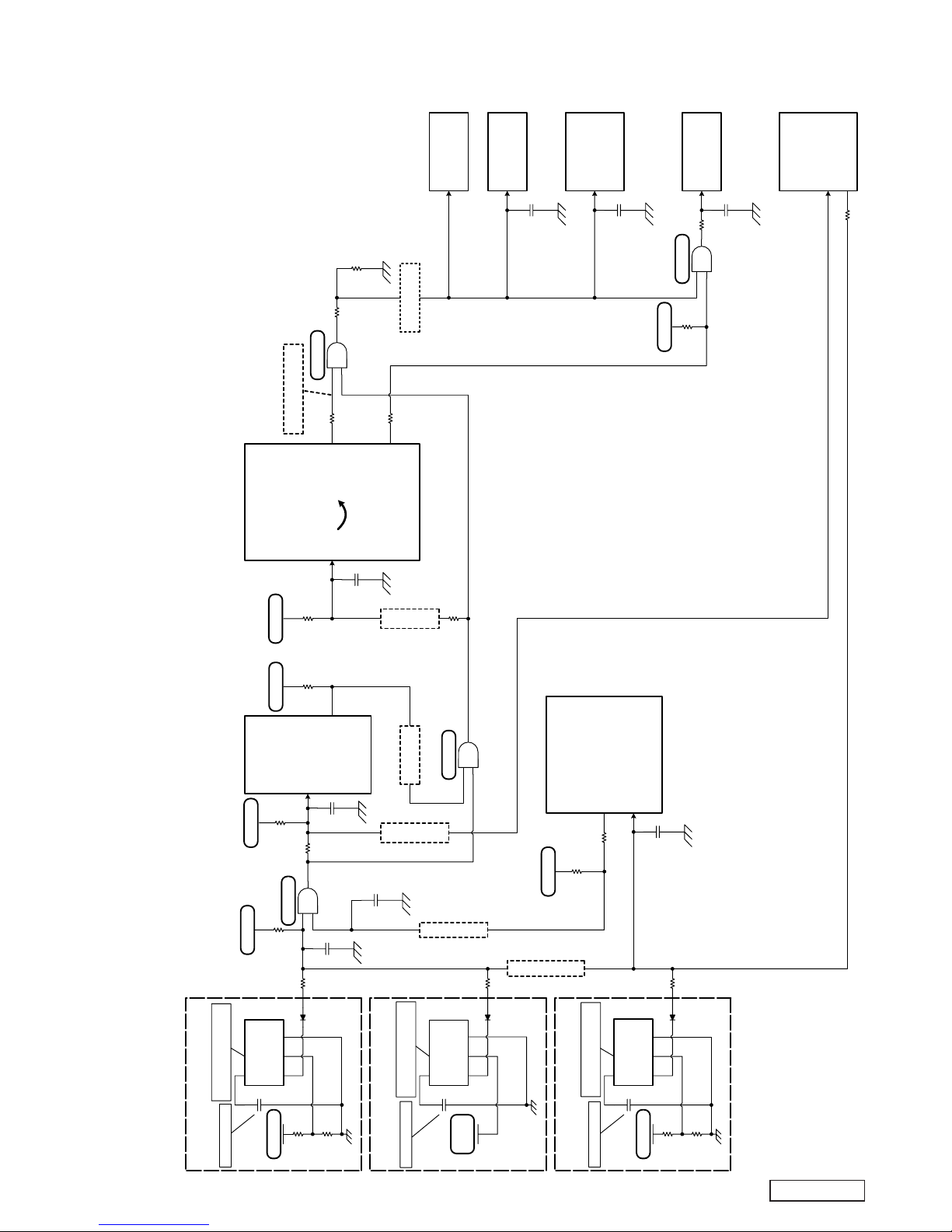

Debug

Connector

Reset Block

IC103

CPU

SH Navi1

/RESET

/RESET_OUT

SRAM

FPGA

HDD

ADC

(AK5357)

IC904

Detector

R3112N211A

IC900

Detector

R3112N211A

IC901

Detector

R3112N211A

HDD_5V DET.

10K

3.9K

3.3K

D_5V

DET VOLT(high):4.81V

DET VOLT(Low):4.58V

0.033uF

100

DDR_2.5V DET.

D_3.3V DET.

DDR

2.5V

0.033uF

100

Disk On Chip

/BUSY

/RSTIN

D_3.3V

D_3.3V

D_3.3V

D_3.3V

D_3.3V

Delay:150ms

1000pF1000pF

/PERI _RESET

47K

D_3.3V

D_5V

1000pF

100

D_3.3V

IC909

SUB

Micon

/RESET

/CPU_RST

100

1000pF

100

10K

/IDE_RST

82

100

/RESET_OUT

/RESET_IN

D_3.3V

100

16K

39K

D_3.3V

0.033uF

100

/NAVI_RESET

100

1000pF

47K

D_3.3V

100

1000pF

SN74ALVC08

(2/4)

SN74ALVC08

(3/4)

SN74ALVC08

(4/4)

SN74ALVC08

47K

10K

10K

/BASE_RESET

/SH_RESET_OUT

/DOC_RST IN

/NAVI_RESET

/DOC_BUSY

1000pF

1000pF

Delay:150ms

Delay:150ms

DET VOLT(high):2.20V

DET VOLT(Low):2.10V

DET VOLT(high):3.11V

DET VOLT(Low):2.96V

Reset block

Page 8

NAX963HD

- 6 -

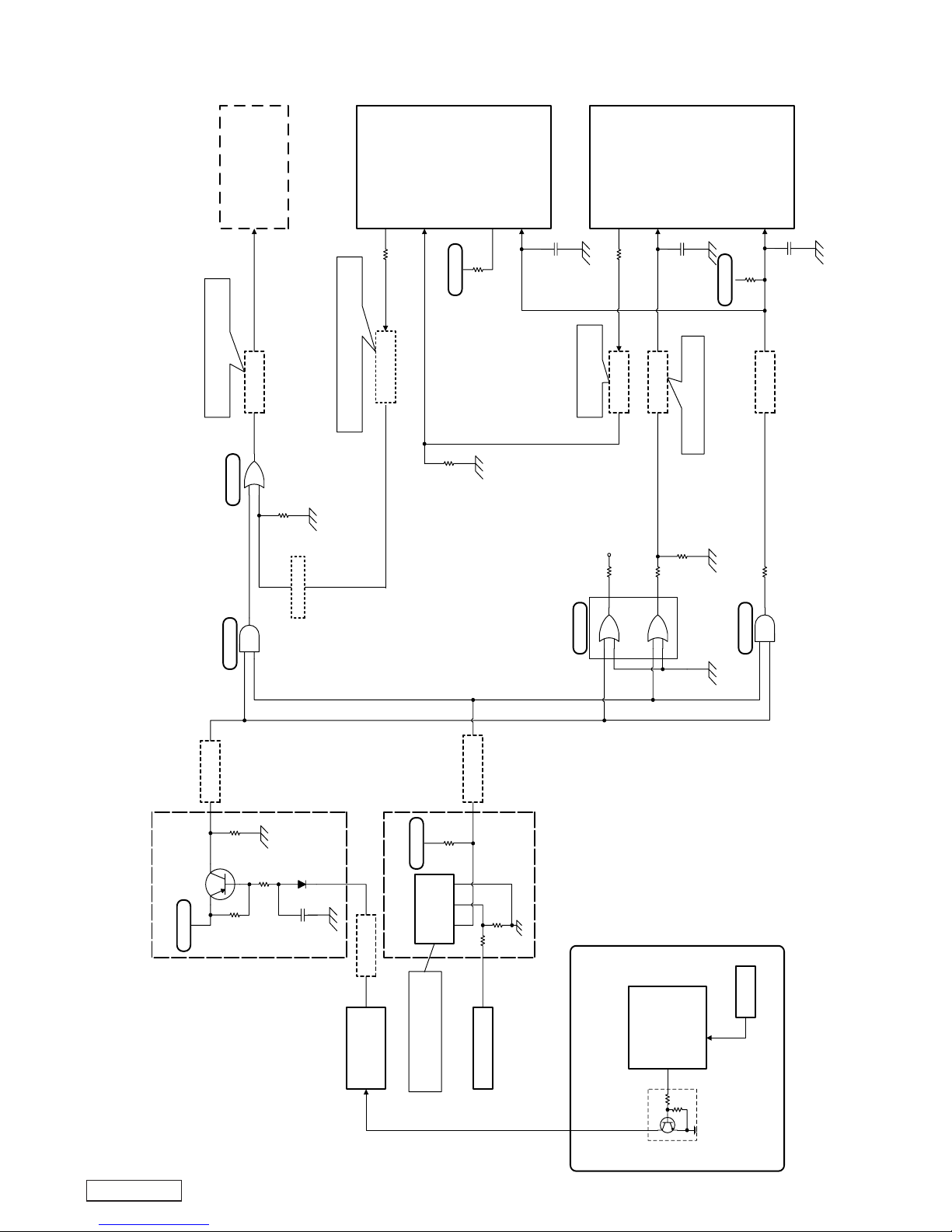

Power Detect Block

Micro

Controller

B/U 12V

IC903

Detector

R3111N271A

ACC_DET

BU_9V_DET

ACC DET.

/SYS-ACC

B/U DET.

/P_OFF

NAVI_PON

/BU-DET

Power supply ON/OFF SW

on Mian PWB

Power-OFF signal

from SH

B/U-VOLT watch signal

to SH

SN74LVC2G32

TC7S32FU

SN74LVC1G08

47K

4.7K

56K

24.7K

47K10K

10K

0.1u

Q900

2SA1586

47K

100

100

B/U_3.3V

B/U_3.3V

B/U_3.3V

B/U_3.3V

D_3.3V

Power supply

(Power circuit block)

B/U

DET. VOLT(high):9.26V

DET. VOLT(Low):8.82V

1SS355

1000pF

100

S-TV

Ce-net

Connector

ACC

IC103

SH-Navi1

NMI

IC909

SUB

Micro

Controller

/SHUTDOWN

100

47K

Shout down signal

by compulsion from microcomputer

1000pF

/P_OFF_B

/NMI_MONI

/SHUTDOWN

/BU_DET

1000pF

NMI

100

D_3.3V

SN74ALVC08(1/4)

GPIO2A20/TX9

GPIO2A22/CSK9

/NAVI_MONI

10K

D_3.3V

10K

D_3.3V

Power detect block

Page 9

NAX963HD

- 7 -

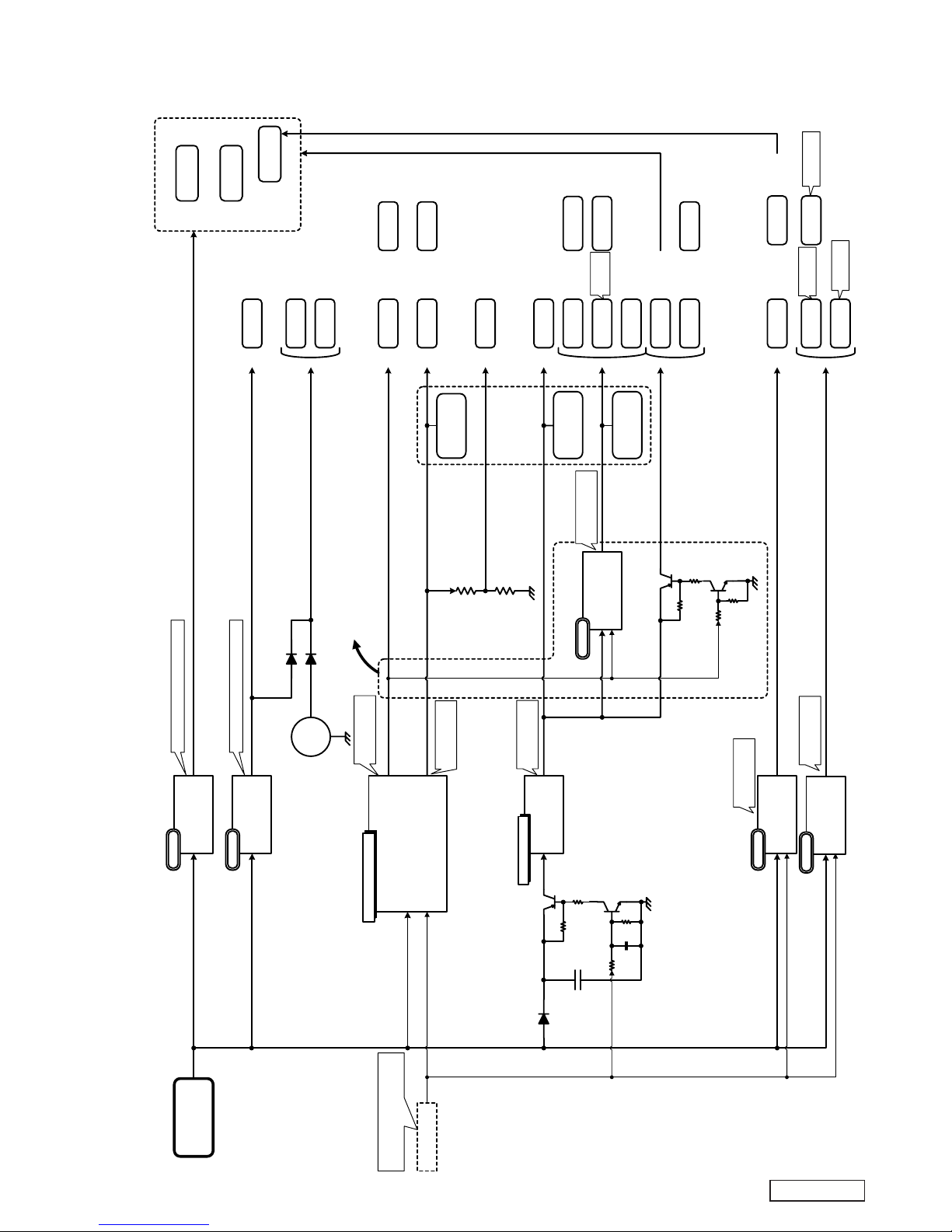

Power circuit block

Power Circuit Block

CAR

BATTERY

IC1002

B/U_5V

TDA3664

Max. permissible current:100mA

Max. permissible current:150mA

Max. permissible

current:3000mA

[D_3.3V] , [D_5V] ON/OFF SW by VCC_1.22V

*

Setting of timing for core power of [Navi core-FPGA] and I/O power.

*

[D_5V] ON/OFF SW for protection of [Navi core] and [FPGA].

IC1000

B/U_3.3V

LM2954

IC1005

VCC_1.22V

DDR_2.5V

TPS5120

IC1003

HDD_5V

LM3485

IC1001 A_9V

BA09CC0WFP

10k

3.9k

10k

2SD1306

2SA2096

4700uF x 2

100(1/4W) x6

RDS PWB

NAVI_P_ON

Detector

2.20V Release

2.10V Det.

Detector

4.81V Release

4.58V Det.

Detector

3.11V Release

2.96V Det.

1.22V

2.5V

IC1006 D_3.3V

BD00KA5WFP

Coin

Battery

DC/DC (200kHz)

DC/DC (100kHz)

Linear

Linear

Linear

IC1004 A_5V

BA05CC0WFP

Vref

Logic

SRAM

GPS

Receiver

SHNavi1 FPGA

SHNavi1 DDR

DDR

HDD

SHNavi1 FPGA

Audio

DAC/ADC

USB

Sub Micon

GPS

Receiver

Gyro

Analog

circuit

Audio

DAC/ADC

Mic

RGB

Encoder

Logic

Max. permissible

current:3000mA

Max. permissible

current:500mA

Max. permissible

current:1000mA

Max. permissible

current:1000mA

Max. permissible

current:3000mA

10k

470

10k

2SC4081

2SB1188

220

Power supply circuit ON/OFF

SW on Navi PWB

RDS/TMC

Tuner

8.5uA typ.

120uA max.

85mA typ.

95mA max.

GPS

Receiver

Tuner

Micon

RDS De-

Modulator

105mA max.

500mA max.

40mA max.

20mA max.

(DataSheet)

13.5mA max.

(DataSheet)

30mA max.

(DataSheet)

30mA max.

(DataSheet)

2.2u

15k

(F)

15k

(F)

Linear

Linear

Page 10

NAX963HD

- 8 -

5A Fuse

(120-0050-00)

Main power supply (Yellow)

Speed sensor (Pink)

Reverse gear signal (Purple/white)

Ground (Black)

NAX963HD

Front view

(inside of Escutcheon)

Rear view

VRX868RVD

GPS antenna

(096-0147-00)

Microphone for voice control

(081-0034-00)

RDS-TMC antenna

(ZCP-412-310)

Power supply lead

(854-6451-50)

RGB cable

(855-2433-01)

CeNET cable

(855-3421-90)

Handbrake (Green)

Connectors

Example of connecting to the VRX868RVD

HDD

1

RDS-TMC antenna recept.

3

1

2

3 4

Mic.jack

6

GPS antenna recept.

8

5

7

8

6

Power supply connector

2468

1357

4

1

2

3

4

5

6

7

8

N.C.

PARKING BRAKE

N.C.

SPEED SENSOR

GROUND

REVERSE SIG.

BATTERY (+)

N.C.

RGB connector

3

7

5

6

8

2

1

4

7

1

2

3

4

5

6

7

8

B

C-SYNC

R

N.C.

N.C.

G

N.C.

N.C.

1234

USB connector

2

1

2

3

4

5V

DD+

GND

CeNET connector

11 12

78910

3456

1132

5

1

2

3

4

5

6

7

8

GND

SYS B/U

L-CH(+)

EXT(+)

EXT(-)

GUS(+)

R-CH(+)

R-CH(-)

9

10

11

12

13

SYS ACC

BUS(-)

L-CH(-)

ILLUMI.

N.C.

WIRE CONNECTION

Page 11

NAX963HD

- 9 -

EXPLANATION OF IC

051-3304-90 LP2954IMX Voltage Regulator

Terminal Description

pin 1: Power out : O : DC power voltage output.

pin 2: Sense : IN : The voltage regulator may be pin-strapped

for 5V operation using its internal resistive

divider by tying the Output and Sense pins

together.

pin 3: Shut Down_ : IN : A logic-level signal will shut off the regu-

lator output when aLOW (<1.2V) is

applied to the Shutdown input.

pin 4: Ground : - : Ground.

pin 5: Error_ : O : Error flag output.

pin 6: 5V-TAP : IN : The voltage regulator may be pin-strapped

for 5V operation using its internal resistive

divider by tying the Feedback pin and 5V-

Tap pins together.

pin 7: Feed back : IN : Feed back voltage input.

pin 8: INPUT : IN : Positive power supply input.

051-3356-90 BD00KA5WFP

Positive Voltage Regurator(Adjustable)

051-3377-90 LM3485MM Hysteretic PFET Buck Controller

General Description

The LM3485 is a high efficiency PFET switching regulator controller

that can be used to quickly and easily develop a small, low cost,

switching buck regulator for a wide range of applications.

The hysteretic control architecture provides for simple design without

any control loop stability concerns using a wide variety of external

components.

The PFET architecture also allows for low component count as well

as ultra-low dropout, 100% duty cycle operation.

Another benefit is high efficiency operation at light loads without an

increase in output ripple.

Current limit protection is provided by measuring the voltage across

the PFET's RDS(ON), thus eliminating the need for a sense resistor.

The cycle-by-cycle current limit can be adjusted with a single resistor, ensuring safe operation over a range of output currents.

Terminal Description

pin 1: I SENSE : The current sense input pin. This pin should

be connected to Drain node of the external

PFET.

pin 2: GND : Signal ground.

8

7

6

5

INPUT

FEEDBACK

5V TAP

ERROR_

1

2

3

4

OUTPUT

SENSE

SHUTDOWN_

GROUND

5.

4.

3.

2.

1.

Adjust

Output

N.C.

Vcc

On/Off (H=ON)

FinGround

R1

R2

Vc

Vo

I SENSE

GND

NC

FB

1

2

3

4

V IN

P GATE

PWR GND

ADJ

8

7

6

5

pin 3: NC : No connection.

pin 4: FB : The feedback input. Connect the FB to a

resistor voltage divider between the output

and GND for an adjustable output voltage.

pin 5: ADJ : Current limit threshold adjustment. It con-

nects to an internal 5.5uA current source. A

resistor is connected between this pin and

the input Power Supply. The voltage across

this resistor is compared with the VDS of the

external PFET to determine if an over-current

condition has occurred.

pin 6: PWR GND : Power ground.

pin 7: P GATE : Gate Drive output for the external PFET.

PGATE swings between VIN and VIN-5V.

pin 8: V I N : Power supply input pin.

051-3380-90 TPS5120DBTRG4

Dual output, Two-phase synchronous buck DC/DC controller

Terminal Description

pin 1: INV 1 : IN : Inverting input of CH 1 error amplifier, skip

comparator, and OVP1/UVP1 comparator.

pin 2 : F B 1 : O : Feedback output of CH 1 error amplifier.

pin 3 : SOFT START 1 :I/O: Soft start pin for CH1.

pin 4: PWM/SKIP :IN: PWM/SKIP mode select pin.

pin 5: CT :I/O:External capacitor from CT to GND for

adjusting the triangle oscillator.

pin 6 : 5V STBY : IN : 5V linear regulator output.

pin 7: GND : - : Control ground.

pin 8 : REF : O : 0.85V reference voltage output.

pin 9 : STBY 1 : IN : Standby control for CH1.

pin 10: STBY 2 : IN: Standby control for CH2.

pin 11 : FLT :I/O: Fault latch timer pin.

pin 12 : POWER GOOD : O : Power good open-drain output.

pin 13: SOFT START 2 :I/O: Soft start pin for CH2.

pin 14 : FB 2 : O : Feedback output of CH 2 error amplifier.

pin 15: INV 2 : IN : Inverting input of CH 2 error amplifier, skip

comparator, and OVP2/UVP2 comparator.

pin 16: LH 2 :I/O:Bootstrap capacitor connection for CH2

high-side gate drive.

pin 17: OUT 2u : O : Gate drive output for CH2 high-side

switching FETs.

pin 18: LL 2 :I/O: Bootstrap this pin for CH2 high-side gate

driving return and output current protec-

tion. Connect this pin to the junction of

the high-side FETs for a floating drive

configuration.

pin 19: OUT 2d : O : Gate drive output for CH2 low side gate

drive.

pin 20: OUT GND 2 : - : Ground for CH1 FET drivers.

pin 21: REG 5V IN :IN : External 5V input.

pin 22: Vref 5 : O : 5V internal regulator output.

pin 23: TRIP 2 : IN : External resistor connection for CH2 out-

put current control.

pin 24 : VCC : - : Supply voltage input.

pin 25: TRIP 1 : IN : External resistor connection for CH1 out-

put current control.

pin 26: OUT GND 1 : - : Ground for CH1 FET drivers.

pin 27: OUT 1d : O : Gate drive output for CH1 low side gate

drive.

pin 28: LL 1 :I/O: Bootstrap this pin for CH1 high-side gate

driving return and output current protec-

tion. Connect this pin to the junction of

the high-side FETs for a floating drive

configuration.

pin 29: OUT 1u : O : Gate drive output for CH1 high-side

switching FETs.

pin 30: LH 1 :I/O:Bootstrap capacitor connection for CH1

high-side gate drive.

Page 12

NAX963HD

- 10 -

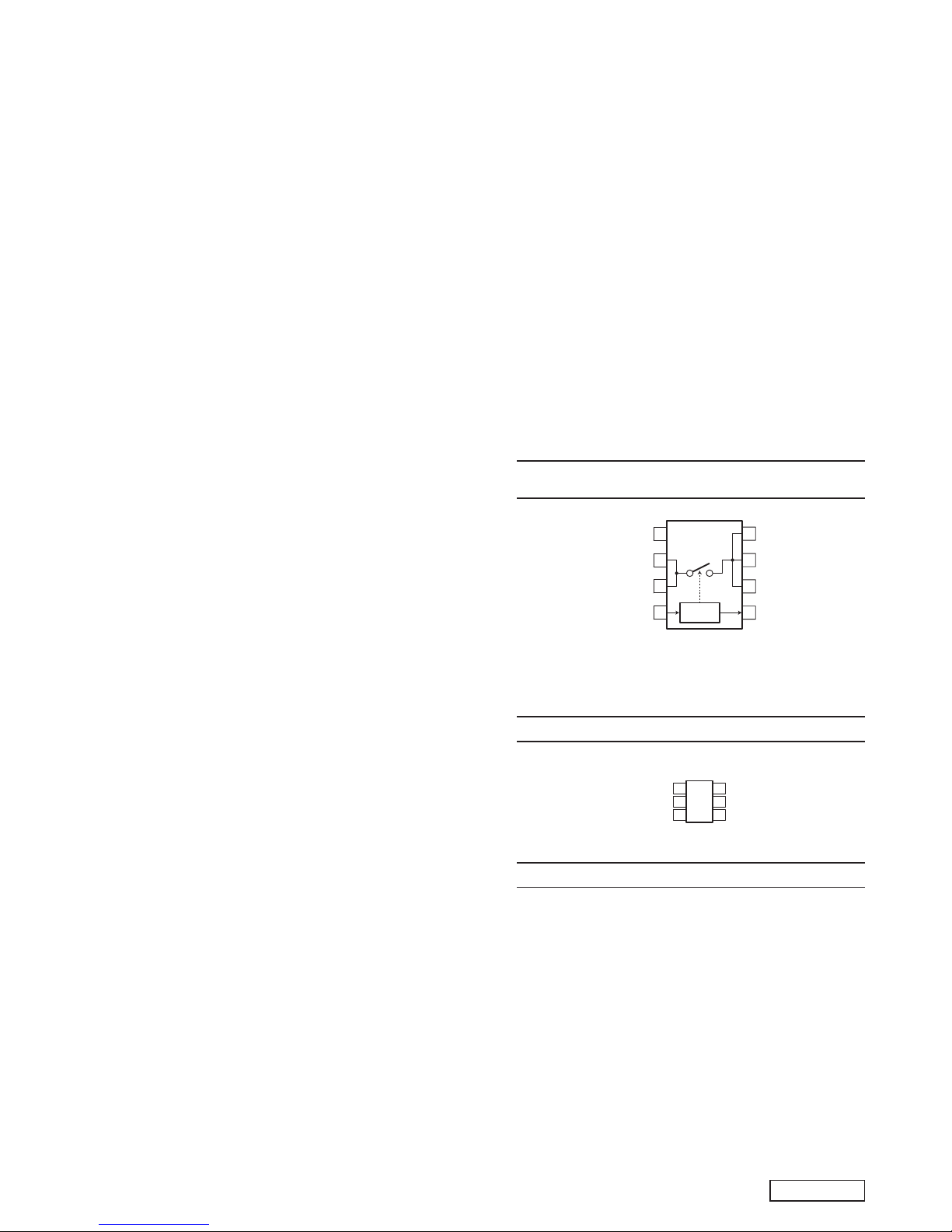

051-5344-90 NJM2267V-TE2 Dual Video Driver

051-5408-38 R3112N211A-TR-FA

Voltage Drop Detector 2.1V

Terminal description

pin 1: OUTPUT : N channel open drain output.

This terminal will output L, if the voltage of

VDD becomes lower than the setting voltage.

pin 2: VDD : Positive supply voltage.

pin 3: GND : Ground.

pin 4: N.C. : Not in use.

pin 5: C.T. : Delay time capacitor connection.

051-5418-28 R3111N271A-TR-FA

Precision Voltage Down Detector 2.7V

Terminal description

pin 1: OUTPUT : N channel open drain output.

This terminal will output L, if the voltage of

VDD becomes lower than the setting voltage.

pin 2: VDD : Positive supply voltage, negative logic input.

pin 3: GND : Ground.

pin 4: NC : Not in use.

pin 5: NC : Not in use.

051-6650-90 NB2305AT1HDR2G 3.3V Zero Delay Clock Buffer

Terminal Description

pin 1: REF : Input reference frequency, 5 V tolerant input.

pin 2: CLK 2 : Buffered clock output.

pin 3: CLK 1 : Buffered clock output.

pin 4: GND : Ground.

pin 5: CLK 3 : Buffered clock output.

pin 6: VDD : 3.3 V supply.

pin 7: CLK 4 : Buffered clock output.

pin 8: CLK OUT : Buffered clock output, internal feedback on

this pin.

6dB

75ohm Driver

750

ohm

2.0k

ohm

2.2k ohm

1

4

3

6dB

75ohm Driver

750

ohm

2.0k

ohm

2.2k ohm

8

5

6

7 2

GNDVCC

1

2

3

54C.T.

N.C.

OUTPUT

VDD

GND

1

2

3

54N.C.

N.C.

OUTPUT

VDD

GND

CLK OUT

CLK 4

VDD

CLK 3

8

7

6

5

REF

CLK 2

CLK 1

GND

1

2

3

4

PLL

Bit CK IN 19

LR CK IN 1

DATA IN 20

Vref P 5

Vref N 6

V MID 8

Audio

Interface

Digital

Filters

DAC

Vout L P12

Vout L N11

DAC

Vout R P9

Vout R N10

A VDD 4

A GND 7

Serial data IN 14

LATCH IN 13

Serial CK IN 15

Control

Interface

Zero Flag L17

Zero Flag R16

Master Clock 18

D VDD2

D GND3

051-6834-00 XC3S50-4VQG100I-0985 FPGA

Terminal Description

pin 1: A20 : Address input.

pin 2: A19 : Address input.

pin 3: GND : Ground.

pin 4: A18 : Address input.

pin 5: A5 : Address input.

pin 6: VCCO : 3.3V power supply for IC.

pin 7: VCCAUX : 2.5V power supply for AUX.

pin 8: A4 : Address input.

pin 9: A3 : Address input.

pin 10: GND :Ground.

pin 11: A2 : Address input.

pin 12: A1 : Address input.

051-6718-90 AK5357VT-E2 96kHz 24Bit ADC

Terminal Description

pin 1 : A IN R : IN: R channel audio signal input.

pin 2 : A IN L : IN: L channel audio signal input.

pin 3 : CK S 1 : IN: Clock Mode select.

pin 4 : V COMMON : O : Common voltage output = A VDD/2

pin 5: A G ND : - : Analog ground.

pin 6: A VDD : - : Positive voltage supply for analog section.

pin 7 : D VDD : - : Positive voltage supply for digital section.

pin 8: D G ND : - : Digital ground.

pin 9 : SDO : O : Audio Serial data output.

pin 10: LR CK I/O :I/O: Output channel clock. L output in Master

Mode at Power-down mode.

pin 11 : MASTER CLK : IN : Master clock input.

pin 12: S CLK :I/O: Audio Serial data clock input. L output in

Master Mode at Power-down mode.

pin 13: PDN : IN : Power down & reset signal input.

L = Power-down mode.

pin 14 : DIF : IN: Audio interface format.

H = 24bit I2S compatible

L = 24bit MSB justified

pin 15 : CK S 2 : IN: Clock Mode select.

pin 16 : CK S 0 : IN: Clock Mode select.

051-6731-90 WM8718SEDS/R

24 bit Differential Stereo DAC with Volume control

Page 13

NAX963HD

- 11 -

pin 13: D15 : Data input/output.

pin 14: D14 : Data input/output.

pin 15: D13 : Data input/output.

pin 16: D12 : Data input/output.

pin 17: D11 : Data input/output.

pin 18: VCCINT : 1.2V power supply for Core.

pin 19: VCCO :3.3V power supply for IC.

pin 20: GND :Ground.

pin 21: D10 : Data input/output.

pin 22: D9 : Data input/output.

pin 23: D8 : Data input/output.

pin 24: M1 : Configuration mode setting.

pin 25: M0 : Configuration mode setting.

pin 26: M2 : Configuration mode setting.

pin 27: CS_B : For Configuration.

pin 28: RDWR_B : Read/Write signal input.

pin 29: GND :Ground.

pin 30: D7 : Data input/output.

pin 31: VCCO :3.3V power supply for IC.

pin 32: D6 : Data input/output.

pin 33: VCCAUX :2.5V power supply for AUX.

pin 34: D5 : Data input/output.

pin 35: D4 : Data input/output.

pin 36: NC : Not in use.

pin 37: NC : Not in use.

pin 38: N_SH_RDY : Ready signal output for CPU.

pin 39: CKIO : Clock input.

pin 40: NC : Not in use.

pin 41: GND :Ground.

pin 42: INIT_B : For Configuration.

pin 43: D3 : Data input/output.

pin 44: D2 : Data input/output.

pin 45: VCCINT : 1.2V power supply for Core.

pin 46: VCCO :3.3V power supply for IC.

pin 47: D1 : Data input/output.

pin 48: D0 : Data input/output.

pin 49: N_WE1 : Write enable input.

pin 50: N_WE0 : Write enable input.

pin 51: DONE : High output after configuration.

pin 52: CCLK : Configuration clock input.

pin 53: N_RD : Read signal input.

pin 54: N_CS_FPGA : Chip select input.

pin 55: NC : Not in use.

pin 56: GND :Ground.

pin 57: VCCO :3.3V power supply for IC.

pin 58: VCCAUX :2.5V power supply for AUX.

pin 59: NC : Not in use.

pin 60: NC : Not in use.

pin 61: NC : Not in use.

pin 62: N_EIRQ1 : Interrupt signal output for CPU.

pin 63: NC : Not in use.

pin 64: NC : Not in use.

pin 65: VOL_DATA : Data output to Audio-ADC.

pin 66: GND :Ground.

pin 67: VOL_CLK : Clock output to Audio-ADC.

pin 68: VOL_CS :Chip select output to Audio-ADC.

pin 69: VCCINT : 1.2V power supply for Core.

pin 70: VCCO :3.3V power supply for IC.

pin 71: EXTCONT : EXT-AUDIO ON/OFF signal for CeNET.

pin 72: N_MUTE : Audio mute.

pin 73: GND :Ground.

pin 74: N_ILL : Illumination detect.

pin 75: NC : Not in use.

pin 76 : TDO : For JTAG.

pin 77 : TCK : For JTAG.

pin 78 : TMS : For JTAG.

pin 79: GYRO_DATA : Data input from GYRO-ADC.

pin 80: ADC_CLK : Clock output to GYRO-ADC.

pin 81: ADC_CS : Chip select output to GYRO-ADC.

pin 82: GND :Ground.

pin 83: VCCO :3.3V power supply for IC.

pin 84: VCCAUX :2.5V power supply for AUX.

pin 85: PKB : Parking signal input.

pin 86: N_BACK : Back signal input.

pin 87: NC : Not in use.

pin 88: NC : Not in use.

pin 89: NC : Not in use.

pin 90: N_RESETI : Reset input.

pin 91: SPEED_IN : Speed pulse input.

pin 92: NC : Not in use.

pin 93: VCCINT : 1.2V power supply for Core.

pin 94: VCCO :3.3V power supply for IC.

pin 95: GND :Ground.

pin 96: A22 : Address input.

pin 97: A21 : Address input.

pin 98: HSWAP_EN : For Configuration.

pin 99: PROG_B : For Configuration.

pin100: TDI : For JTAG.

051-6921-90 TPS2041BDGNR

SINGLE, CURRENT-LIMITED, POWER-DISTRIBUTION SWITCH

OC_ ( pin 5 ): Overcurrent and overtemperature false re-

porting, active-low, open-drain output.

051-6923-08 ADCS7476AIMF 1 M SPS 12 bit ADC

051-7289-90 MC74HC4046ADT PLL

Terminal Description

pin 1: PC P OUT : Phase Comparator Pulse Output

pin 2: PC 1 OUT : Phase Comparator 1 Output

pin 3: COMP IN : Comparator Input

pin 4: VCO OUT : VCO Output

pin 5: INH : Inhibit Input

pin 6: C 1 A : Capacitor C1 Connection A

pin 7: C 1 B : Capacitor C1 Connection B

pin 8: GND : Ground (0 V) VSS

pin 9: VCO IN : VCO Input

pin 10 : DEM OUT : Demodulator Output

pin 11: R 1 : Resistor R1 Connection

pin 12: R 2 : Resistor R2 Connection

pin 13 : PC 2 OUT : Phase Comparator 2 Output

pin 14: SIG IN : Signal Input

pin 15 : PC 3 OUT : Phase Comparator 3 Output

pin 16: VCC : Positive Supply Voltage

1

2

3

4

OUT

OUT

OUT

OC_

GND

IN

IN

EN_ ( L = Switch ON )

8

7

6

5

LOGIC

6

5

4

Chip Select input

Serial data output

Clock pulse input

1

2

3

VDD

GND

Analog signal input : Vin

Page 14

NAX963HD

- 12 -

051-7529-90 SN74LVC541APW Octal Bus Buffer

Truth Table

Switch G 1 ( pin 1 ) G 2 ( pin 19 )

OFF H H

OFF H L

OFF L H

ON L L

051-7534-90 SN74LVC1G97DCKR

Configurable Multiple-function Gate

Truth Table

Y IN 2 IN 1 IN 0

L L L L

L L L H

H L H L

H L H H

L H L L

H H L H

L H H L

H H H H

051-7537-90 SN74LVC1G14DCKR

Single Schmitt-Trigger Inverter Gate

051-7539-90 SN74LVC3G34DCTR Triple Buffers

051-7503-78 SN74LVCHR16245AGR 8 x 2 Bus Transceiver

Truth Table

OE_ DIR SW 1 SW 2

L L ON OFF

L H OFF ON

H L OFF OFF

H H OFF OFF

051-7505-08 SN74LV08APWR Quad 2-input AND Gate

051-7505-18 SN74ALVC08PWR Quad 2-input AND Gate

051-7520-08 SN74LVC1G04DCKR Single Inverter

051-7522-08 SN74LVC1G32DCKR Single 2-inputs OR Gate

051-7524-08 SN74LVC1G08DCK Single 2-inputs AND GATE

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

48

47 46 45 44 43 42 41 40 39 38 37

36 35 34 33 32 31 30 29 28 27 26 25

SW-1SW-2

Logic

SW-1SW-2

Logic

DIR 1

GND

VDD

GND

GND

GND

GND

GND

GND

GND

VDD VDD

VDD

OE 1_

OE 2_DIR 2

14

13

12

11

10

9

8

1

2

3

4

5

6

7

GND

VDD

1

2

3

54VCC

OUT

NC

IN

GND

1

2

3

54VCC

GND

1

2

3

54VCC

GND

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

10

GROUND

G1

VCC

G2

Logic

IN 2

VCC

Y

6

5

4

IN 1

GND

IN 0

1

2

3

IN 0 3

IN 1 1

IN 2 6

Y4

1

2

3

N.C.

GND

54VCC

8

7

6

5

GND

VDD

1

2

3

4

Page 15

NAX963HD

- 13 -

051-7540-90 SN74LVC2G32DCTR Dual 2-input OR Gate

051-9125-60 BS616LV4013EI-70 4 M bit SRAM

Terminal Description

pin 1 : A 4 : IN: Address signal input.

pin 2 : A 3 : IN: Address signal input.

pin 3 : A 2 : IN: Address signal input.

pin 4 : A 1 : IN: Address signal input.

pin 5 : A 0 : IN: Address signal input.

pin 6 : CE_ : IN : Chip enable signal input.

pin 7 : DQ 0 :I/O: The data input / output.

pin 8 : DQ 1 :I/O: The data input / output.

pin 9 : DQ 2 :I/O: The data input / output.

pin 10: DQ 3 :I/O: The data input / output.

pin 11 : VCC : - : Positive supply voltage.

pin 12: GND : - : Ground.

pin 13: DQ 4 :I/O: The data input / output.

pin 14: DQ 5 :I/O: The data input / output.

pin 15: DQ 6 :I/O: The data input / output.

pin 16: DQ 7 :I/O: The data input / output.

pin 17 : WE_ : IN: Write enable signal input.

pin 18 : A 17 : IN : Address signal input.

pin 19 : A 16 : IN : Address signal input.

pin 20 : A 15 : IN : Address signal input.

pin 21 : A 14 : IN : Address signal input.

pin 22 : A 13 : IN : Address signal input.

pin 23 : A 12 : IN : Address signal input.

pin 24 : A 11 : IN : Address signal input.

pin 25 : A 10 : IN : Address signal input.

pin 26 : A 9 : IN: Address signal input.

pin 27 : A 8 : IN: Address signal input.

pin 28: NU : - : Not in use.

pin 29: DQ 8 :I/O: The data input / output.

pin 30: DQ 9 :I/O: The data input / output.

pin 31: DQ 10 :I/O: The data input / output.

pin 32: DQ 11 :I/O: The data input / output.

pin 33 : VCC : - : Positive supply voltage.

pin 34: GND : - : Ground.

pin 35: DQ 12 :I/O: The data input / output.

pin 36: DQ 13 :I/O: The data input / output.

pin 37: DQ 14 :I/O: The data input / output.

pin 38: DQ 15 :I/O: The data input / output.

pin 39 : LB_ : IN : Upper byte control signal input.

pin 40 : UB_ : IN : Lower byte control signal input.

pin 41 : OE_ : IN: Output enable signal input.

pin 42 : A 7 : IN: Address signal input.

pin 43 : A 6 : IN: Address signal input.

pin 44 : A 5 : IN: Address signal input.

Truth Table

CE_ WE_ OE_ LB_ UB_ DQ 0 DQ 8

in in in in in to to

(pin 6) (pin 17) (pin 41) (pin 39) (pin 40) DQ 7 DQ 15

H X X X X high Z high Z

L H H X X high Z high Z

L H L L L output output

L H L H L high Z output

L H L L H output high Z

L L X L L input input

L L X H L X input

L L X L H input X

051-9333-30 MT46V16M16P-6T-IT

256M bit DDR SDRAM (16M words x 16 bits)

Terminal Description

pin 1: VDD : - : Positive voltage supply.

pin 2 : DQ 0 :I/O: Data signal input/output.

pin 3: VDD Q : - : Positive power supply for the data I/O

ports.

pin 4 : DQ 1 :I/O: Data signal input/output.

pin 5 : DQ 2 :I/O: Data signal input/output.

pin 6: VSS Q : - : Ground terminal for the data I/O ports.

pin 7 : DQ 3 :I/O: Data signal input/output.

pin 8 : DQ 4 :I/O: Data signal input/output.

pin 9: VDD Q : - : Positive power supply for the data I/O

ports.

pin 10 : DQ 5 :I/O: Data signal input/output.

pin 11 : DQ 6 :I/O: Data signal input/output.

pin 12: VSS Q : - : Ground terminal for the data I/O ports.

pin 13 : DQ 7 :I/O: Data signal input/output.

pin 14: NU : - : Not in use.

pin 15: VDD Q : - : Positive power supply for the data I/O

ports.

pin 16: Lower DQ S :I/O: Read data strobe output / Write data

strobe input.

pin 17: NU : - : Not in use.

pin 18 : VDD : - : Positive voltage supply.

pin 19: NU : - : Not in use.

pin 20: Lower DM : IN : When this pin is High, the data input are

masked.

pin 21 : WE : IN: Write enable signal input.

pin 22 : CAS :IN : Column address strobe input.

pin 23 : RAS : IN : Row address strobe input.

pin 24 : CS IN :IN : The chip select command input.

pin 25: NU : - : Not in use.

pin 26 : BA 0 : IN : Bank address input.

pin 27 : BA 1 : IN : Bank address input.

pin 28: A10(AP) :IN : Address signal input.

pin 29 : A 0 :IN : Address signal input.

pin 30 : A 1 :IN : Address signal input.

pin 31 : A 2 :IN : Address signal input.

pin 32 : A 3 :IN : Address signal input.

pin 33 : VDD : - : Positive voltage supply.

pin 34 : VSS : - : Negative voltage supply.

pin 35 : A 4 :IN : Address signal input.

pin 36 : A 5 :IN : Address signal input.

pin 37 : A 6 :IN : Address signal input.

pin 38 : A 7 :IN : Address signal input.

pin 39 : A 8 :IN : Address signal input.

pin 40 : A 9 :IN : Address signal input.

pin 41 : A 11 : IN : Address signal input.

pin 42 : A 12 : IN : Address signal input.

pin 43: NU : - : Not in use.

pin 44 : CKE :IN : Clock enable signal input.

pin 45 : CK : IN : Master clock input.

pin 46 : /CK : IN : Master clock input.

pin 47: Upper DM : IN : When this pin is High, the data input are

8

7

6

5

1

2

3

4

GROUND

VDD

Page 16

NAX963HD

- 14 -

masked.

pin 48 : VSS : - : Negative voltage supply.

pin 49 : Vref : - : Reference voltage.

pin 50: NU : - : Not in use.

pin 51: Upper DQ S :I/O: Read data strobe output / Write data

strobe input.

pin 52: VSS Q : - : Ground terminal for the data I/O ports.

pin 53: NU : - : Not in use.

pin 54 : DQ 8 :I/O: Data signal input/output.

pin 55: VDD Q : - : Positive power supply for the data I/O

ports.

pin 56 : DQ 9 :I/O: Data signal input/output.

pin 57 : DQ 10 :I/O: Data signal input/output.

pin 58: VSS Q : - : Ground terminal for the data I/O ports.

pin 59 : DQ 11 :I/O: Data signal input/output.

pin 60 : DQ 12 :I/O: Data signal input/output.

pin 61: VDD Q : - : Positive power supply for the data I/O

ports.

pin 62 : DQ 13 :I/O: Data signal input/output.

pin 63 : DQ 14 :I/O: Data signal input/output.

pin 64: VSS Q : - : Ground terminal for the data I/O ports.

pin 65 : DQ 15 :I/O: Data signal input/output.

pin 66 : VSS : - : Negative voltage supply.

IC103 R8A77700ADA01BGV

RISC Microcomputer for QY5000EA

Terminal Description

pin 1: VSSQ25 : DDR ground

pin 2: VCCQ25 :DDR 2.5V power supply

pin 3: DSA[6] : DDR-SDRAM address output

pin 4: DSA[4] : DDR-SDRAM address output

pin 5: DSA[2] : DDR-SDRAM address output

pin 6: DSA[0] : DDR-SDRAM address output

pin 7: DSRAS# : DDR-SDRAM row address select output

pin 8: DSCAS# : DDR-SDRAM column address select out-

put

pin 9: DSDQ[36] : DDR-SDRAM data input/output

pin 10: DSDM[4] : DDR-SDRAM data select output

pin 11: DSDQ[39] : DDR-SDRAM data input/output

pin 12: DSDQ[45] : DDR-SDRAM data input/output

pin 13: DSDM[5] : DDR-SDRAM data select output

pin 14: DSDQ[46] : DDR-SDRAM data input/output

pin 15: DSDQ[52] : DDR-SDRAM data input/output

pin 16: DSDM[6] : DDR-SDRAM data select output

pin 17: DSDQ[55] : DDR-SDRAM data input/output

pin 18: DSDQ[61] : DDR-SDRAM data input/output

pin 19: DSDM[7] : DDR-SDRAM data select output

pin 20: DSDQ[63] : DDR-SDRAM data input/output

pin 21: TX0/MD[2] : In the reset operation, this port is CPU

setting input. At usually operation, this

port is serial data output to GPS receiv-

er.

pin 22: TX1/MD[3] : In the reset operation, this port is CPU

setting input. At usually operation, this

port is not in use.

pin 23: TX3/IrDA-TX/MD[5] : In t he reset operation, this port is CPU

setting input. At usually operation, this

port is not in use.

pin 24: TX5/HSPI0_CLK : Serial data output to RDS microcomput-

er.

pin 25: NU : Not in use.

pin 26: NU : Not in use.

pin 27: NU : Not in use.

pin 28: NU : Not in use.

pin 29: VSSDLL : DLL ground

pin 30: VDDPLL1 : PLL 1.25V power supply

pin 31: VSSPLL1 : PLL ground

pin 32: VCCQ25 : DDR 2.5V power supply

pin 33: VSSQ25 : DDR ground

pin 34: VCCQ25 :DDR 2.5V power supply

pin 35: DSA[7] : DDR-SDRAM address output

pin 36: DSA[3] : DDR-SDRAM address output

pin 37: DSA[1] : DDR-SDRAM address output

pin 38: DSBA[0] : DDR-SDRAM bank address output

pin 39: /DSWE : DDR-SDRAM write enable.

pin 40: DSDQ[32] : DDR-SDRAM data input/output

pin 41: DSDQS[4] : DDR-SDRAM data input/output

pin 42: DSDQ[35] : DDR-SDRAM data input/output

pin 43: DSDQ[41] : DDR-SDRAM data input/output

pin 44: DSDQS[5] : DDR-SDRAM data strobe input/output

pin 45: DSDQ[42] : DDR-SDRAM data input/output

pin 46: DSDQ[48] : DDR-SDRAM data input/output

pin 47: DSDQS[6] : DDR-SDRAM data strobe input/output

pin 48: DSDQ[51] : DDR-SDRAM data input/output

pin 49: DSDQ[57] : DDR-SDRAM data input/output

pin 50: DSDQS[7] : DDR-SDRAM data strobe input/output

pin 51: DSDQ[59] : DDR-SDRAM data input/output

pin 52 : RX0 : GPS serial data input

pin 53: NU : Not in use.

pin 54: NU : Not in use.

pin 55: RX 5/HSPI0_CS# : Serial data input from RDS microcomput-

er.

pin 56: NU : Not in use.

pin 57: NU : Not in use.

pin 58: NU : Not in use.

pin 59: TX6/MD[10] : In the reset o peration, this por t is CPU

setting input. At usually operation, this

port is not in use.

pin 60: VDDDLL : DLL 1.25V power supply

pin 61: VDDPLL2 : PLL 1.25V power supply

pin 62: VSSPLL2 : PLL ground

pin 63: VCCQ25 :DDR 2.5V power supply

pin 64: VCCQ25 :DDR 2.5V power supply

pin 65: VSSQ25 : DDR ground

pin 66: VCCQ25 :DDR 2.5V power supply

pin 67: DSA[5] : DDR-SDRAM address output

pin 68: DSBA[1] : DDR-SDRAM bank address output

pin 69: VSSQ25 : DDR ground

pin 70: NU : Not in use.

pin 71: DSDQ[37] : DDR-SDRAM data input/output

pin 72: DSDQ[38] : DDR-SDRAM data input/output

pin 73: DSDQ[44] : DDR-SDRAM data input/output

pin 74: VCCQ25 :DDR 2.5V power supply

pin 75: VSSQ25 : DDR ground

pin 76: DSDQ[47] : DDR-SDRAM data input/output

pin 77: DSDQ[53] : DDR-SDRAM data input/output

pin 78: DSDQ[54] : DDR-SDRAM data input/output

pin 79: DSDQ[60] : DDR-SDRAM data input/output

pin 80: VCCQ25 :DDR 2.5V power supply

pin 81: DSDQ[62] : DDR-SDRAM data input/output

pin 82: NU : Not in use.

pin 83: VSSQ25 : DDR ground

pin 84: TX2/MD[4] : In the reset operatio n, this port is CPU

setting input. At usually operation, this

port is serial data output.

pin 85: TX4/HSPI0_TX : Serial data output

pin 86: TX7/HSPI1_TX : Serial data output to sub-microcomputer

Page 17

NAX963HD

- 15 -

pin 87: NU : Not in use.

pin 88: TX9/GPIO_2A20 :Used as GPIO. /P_OFF

pin 89: NU : Not in use.

pin 90: VSSQ : I/O power ground

pin 91: VCCQ :I/O 3.3V power supply

pin 92: VCCQ :I/O 3.3V power supply

pin 93: EXTAL : External clock input (48MHz)

pin 94: DSCK# : DDR-SDRAM clock output (inverted)

pin 95: DSCAP : DDR-SDRAM controller CAP

pin 96: VCCQ25 :DDR 2.5V power supply

pin 97: VSSQ25 : DDR ground

pin 98: VCCQ25 :DDR 2.5V power supply

pin 99: DSA[10] : DDR-SDRAM address output

pin100:VSSQ25 : DDR ground

pin101: DSCS# :DDR-SDRAM area space selection

pin102: DSDQ[33] : DDR-SDRAM data input/output

pin103: DSDQ[34] : DDR-SDRAM data input/output

pin104: DSDQ[40] : DDR-SDRAM data input/output

pin105: VCCQ25 :DDR 2.5V power supply

pin106:VSSQ25 : DDR ground

pin107: DSDQ[43] : DDR-SDRAM data input/output

pin108: DSDQ[49] : DDR-SDRAM data input/output

pin109: DSDQ[50] : DDR-SDRAM data input/output

pin110: DSDQ[56] : DDR-SDRAM data input/output

pin111: VCCQ25 :DDR 2.5V power supply

pin112: DSDQ[58] : DDR-SDRAM data input/output

pin113: NU : Not in use.

pin114:VSSQ25 : DDR ground

pin115: RX2 : Serial data input

pin116: RX4/HSPI0_RX : Serial data input

pin117:RX7/HSPI1_RX : Serial data input from sub-microcomput-

er

pin118: NU : Not in use.

pin119: RX9/GPIO_2A21 : Used as GPIO. /BU_DET

pin120: VSSQ : I/O power ground

pin121: VCCQ : I/O 3.3V power supply

pin122: VSSQ : I/O power ground

pin123: VSSQ : I/O power ground

pin124:XTAL : CPU crystal connection

pin125:DSCK : DDR-SDRAM clock output

pin126: NU : Not in use.

pin127: VCCQ25 :DDR 2.5V power supply

pin128: VCCQ25 :DDR 2.5V power supply

pin129:VSSQ25 : DDR ground

pin130: VCCQ25 :DDR 2.5V power supply

pin131:VSSQ25 : DDR ground

pin132: VCCQ25 :DDR 2.5V power supply

pin133:VSSQ25 : DDR ground

pin134: VDD : Core 1.25V power supply

pin135:VSS : Core power ground

pin136: VCCQ25 :DDR 2.5V power supply

pin137:VSSQ25 : DDR ground

pin138: VCCQ25 :DDR 2.5V power supply

pin139:VSSQ25 : DDR ground

pin140: VDD : Core 1.25V power supply

pin141:VSS : Core power ground

pin142: VCCQ25 :DDR 2.5V power supply

pin143:VSSQ25 : DDR ground

pin144: VDD : Core 1.25V power supply

pin145:VSSQ25 : DDR ground

pin146:VSS : Core power ground

pin147: VSSQ : I/O power ground

pin148: VCCQ : I/O 3.3V power supply

pin149: VCCQ : I/O 3.3V power supply

pin150: VSSQ : I/O power ground

pin151: VCCQ : I/O 3.3V power supply

pin152: VSSQ : I/O power ground

pin153:TRST# :H-UDI reset input

pin154: NU : Not in use.

pin155: NU : Not in use.

pin156:DSA[11] : DDR-SDRAM address output

pin157:DSA[12] : DDR-SDRAM address output

pin158:DSA[8] : DDR-SDRAM address output

pin159:DSA[9] : DDR-SDRAM address output

pin160: VCCQ25 :DDR 2.5V power supply

pin161: VSSQ : I/O power ground

pin162: TMS : H-UDI mode input

pin163: TDI : H-UDI data input

pin164: TDO : H-UDI data output

pin165: TCK : H-UDI clock input

pin166: DSCKE : DDR-SDRAM clock output enable

pin167: NU : Not in use.

pin168:DSA[13] : DDR-SDRAM address output

pin169:VSSQ25 : DDR ground

pin170:VSSQ25 : DDR ground

pin171: VCCQ : I/O 3.3V power supply

pin172: NU : Not in use.

pin173: NU : Not in use.

pin174: NU : Not in use.

pin175: NU : Not in use.

pin176: DSDQ[30] : DDR-SDRAM data input/output

pin177: DSDQ[26] : DDR-SDRAM data input/output

pin178: DSDQ[31] : DDR-SDRAM data input/output

pin179: DSDQ[27] : DDR-SDRAM data input/output

pin180: VDD : Core 1.25V power supply

pin181:VSS : Core power ground

pin182: NU : Not in use.

pin182: NU : Not in use.

pin184: ASEBRK# :Emulator input/output( brake,

acknowledge)

pin185: NU : Not in use.

pin186: DSDQ[29] : DDR-SDRAM data input/output

pin187: DSDQ[25] : DDR-SDRAM data input/output

pin188: DSDM[3] : DDR-SDRAM data select output

pin189: DSDQS[3] : DDR-SDRAM data input/output

pin190:VSS : Core power ground

pin191: VDD : Core 1.25V power supply

pin192: NU : Not in use.

pin193: NU : Not in use.

pin194: NU : Not in use.

pin195: NU : Not in use.

pin196: DSDQ[23] : DDR-SDRAM data input/output

pin197: DSDQ[19] : DDR-SDRAM data input/output

pin198: DSDQ[28] : DDR-SDRAM data input/output

pin199: DSDQ[24] : DDR-SDRAM data input/output

pin200: VCCQ25 :DDR 2.5V power supply

pin201:VSS : Core power ground

pin202: NU : Not in use.

pin203: NU : Not in use.

pin204: NU : Not in use.

pin205: NU : Not in use.

pin206: DSDM[2] : DDR-SDRAM data select output

Page 18

NAX963HD

- 16 -

pin207:DSDQS[2] : DDR-SDRAM data strobe input/output

pin208: DSDQ[22] : DDR-SDRAM data input/output

pin209: DSDQ[18] : DDR-SDRAM data input/output

pin210:VSSQ25 : DDR ground

pin211: VDD : Core 1.25V power supply

pin212: NU : Not in use.

pin213: NU : Not in use.

pin214: NU : Not in use.

pin215: NU : Not in use.

pin216: DSDQ[20] : DDR-SDRAM data input/output

pin217: DSDQ[16] : DDR-SDRAM data input/output

pin218: DSDQ[21] : DDR-SDRAM data input/output

pin219: DSDQ[17] : DDR-SDRAM data input/output

pin220: VDD : Core 1.25V power supply

pin221: VSSQ : I/O power ground

pin222: SPDIF_IN : Extended GPIO data latch output

pin223: SPDIF_OUT : FPGA PROG_B output

pin224: NU : Not in use.

pin225: NU : Not in use.

pin226: DSDQ[14] : DDR-SDRAM data input/output

pin227: DSDQ[10] : DDR-SDRAM data input/output

pin228: DSDQ[15] : DDR-SDRAM data input/output

pin229: DSDQ[11] : DDR-SDRAM data input/output

pin230:VSS : Core power ground

pin231: VCCQ : I/O 3.3V power supply

pin232: SSI_SDATA 1 : Data output to DAC for guide signal

pin233:SSI_SDATA0 : The data input from ADC for microphone

pin234: NU : Not in use.

pin235:AUDIO_CLK :Audio clock input for SSI module

(8.46MHz)

pin236: DSDM[1] : DDR-SDRAM data select output

pin237: DSDQS[1] : DDR-SDRAM data strobe input/output

pin238:VSSQ25 : DDR ground

pin239:VSSQ25 : DDR ground

pin240:VSSQ25 : DDR ground

pin241:VSS : Core power ground

pin242:SSI_WS0 : LR clock input

pin243: SSI_SCK0 :Serial bit clock input

pin244: SSI_WS1/HAC_RES#

: LR clock input

pin245: SSI_SCK1 :Serial bit clock input

pin246: DSDQ[12] : DDR-SDRAM data input/output

pin247: DSDQ[8] : DDR-SDRAM data input/output

pin248: DSDQ[13] : DDR-SDRAM data input/output

pin249: DSDQ[9] : DDR-SDRAM data input/output

pin250:VSSQ25 : DDR ground

pin251:VSS : Core power ground

pin252: NU : Not in use.

pin253: NU : Not in use.

pin254: NU : Not in use.

pin255: NU : Not in use.

pin256: DSDQ[6] : DDR-SDRAM data input/output

pin257: DSDQ[2] : DDR-SDRAM data input/output

pin258: DSDQ[7] : DDR-SDRAM data input/output

pin259: DSDQ[3] : DDR-SDRAM data input/output

pin260: VCCQ25 :DDR 2.5V power supply

pin261: VSSQ : I/O power ground

pin262:IDED[7] : IDE data input/output

pin263:IDED[8] : IDE data input/output

pin264: IDERST# : IDE reset output

pin265: DIRECTION : IDE bus buffer direction control output

pin266: DSDQ[5] : DDR-SDRAM data input/output

pin267: DSDQ[1] : DDR-SDRAM data input/output

pin268: DSDM[0] : DDR-SDRAM data select output

pin269: DSDQS[0] : DDR-SDRAM data strobe input/output

pin270:VSSQ25 : DDR ground

pin271: VCCQ : I/O 3.3V power supply

pin272:IDED[5] : IDE data input/output

pin273: IDED[10] : IDE data input/output

pin274:IDED[6] : IDE data input/output

pin275:IDED[9] : IDE data input/output

pin276: DSDQ[4] : DDR-SDRAM data input/output

pin277: DSDQ[0] : DDR-SDRAM data input/output

pin278: VCCQ25 :DDR 2.5V power supply

pin279: VCCQ25 :DDR 2.5V power supply

pin280: VCCQ25 :DDR 2.5V power supply

pin281: VDD : Core 1.25V power supply

pin282:IDED[3] : IDE data input/output

pin283: IDED[12] : IDE data input/output

pin284:IDED[4] : IDE data input/output

pin285: IDED[11] : IDE data input/output

pin286:DSVREF : DDR-SDRAM reference voltage input

pin287: VSS : Core power ground

pin288: VSS : Core power ground

pin289: VSS : Core power ground

pin290: VSS : Core power ground

pin291: VSS : Core power ground

pin292:IDED[1] : IDE data input/output

pin293: IDED[14] : IDE data input/output

pin294:IDED[2] : IDE data input/output

pin295: IDED[13] : IDE data input/output

pin296: VDD : Core 1.25V power supply

pin297: VDD : Core 1.25V power supply

pin298: VDD : Core 1.25V power supply

pin299: VDD : Core 1.25V power supply

pin300: VDD : Core 1.25V power supply

pin301: VCCQ : I/O 3.3V power supply

pin302: IDEIOWR# :IDE disk write output

pin303: IODREQ : IDE-DMA request input

pin304:IDED[0] : IDE data input/output

pin305: IDED[15] : IDE data input/output

pin306: NU : Not in use.

pin307: NU : Not in use.

pin308: VSS : Core power ground

pin309: VSS : Core power ground

pin310: VSS : Core power ground

pin311: VSSQ : I/O power ground

pin312: IDEINT : IDE interrupt request input

pin313: IODACK# : IDE-DMA acknowledge output

pin314: IDEIORDY : IDE ready input

pin315:IDEIORD# : IDE disk resd output

pin316:NMI# : NMI

pin317:IRQ#[4]/EX_CS#[6] : Interrupt input

pin318: IRQ#[5]/EX_CS#[7] : Chip select output

pin319: IRQ#[1]/EX_WAIT[1]

: Interrupt input

pin320: VDD : Core 1.25V power supply

pin321: VDD : Core 1.25V power supply

pin322: IDECS#[0] :IDE chip select output

pin323:IDEA[2] : IDE address output

pin324:IDEA[0] : IDE address output

pin325:IDEA[1] : IDE address output

Page 19

NAX963HD

- 17 -

pin326: NU : Not in use.

pin327:IRQ#[0] : Interrupt input

pin328: NU : Not in use.

pin329: NU : Not in use.

pin330: VSSQ : I/O power ground

pin331:VSS : Core power ground

pin332: NU : Not in use.

pin333: NU : Not in use.

pin334: NU : Not in use.

pin335: IDECS#[1] :IDE chip select output

pin336: NU : Not in use.

pin337: NU : Not in use.

pin338: NU : Not in use.

pin339: NU : Not in use.

pin340: VCCQ : I/O 3.3V power supply

pin341: VDD : Core 1.25V power supply

pin342: GPIO-3-A27 : LED1 control signal output to sub-micro-

computer

pin343: GPIO-3-A28 : LED2 control signal output to sub-micro-

computer

pin344: IRREC : Remote control input

pin346: NU : Not in use.

pin347: NU : Not in use.

pin348: NU : Not in use.

pin349: NU : Not in use.

pin350: VSSQ : I/O power ground

pin351:VSS : Core power ground

pin352: VSSRTC : RTC ground

pin353: NU : Not in use.

pin354: RESOUT# : Reset output

pin355: RESET# : Reset input

pin355: RESET# : Reset input

pin356: NU : Not in use.

pin357: NU : Not in use.

pin358: NU : Not in use.

pin359: NU : Not in use.

pin360: VCCQ : I/O 3.3V power supply

pin361: VCCQ : I/O 3.3V power supply

pin362: NU : Not in use.

pin363: NU : Not in use.

pin364: NU : Not in use.

pin365: NU : Not in use.

pin366: NU : Not in use.

pin367: NU : Not in use.

pin368: EX_CS#[4]/EXCPU_IRQ#

: Chip select output

pin369: VCCQ : I/O 3.3V power supply

pin370: VSSQ : I/O power ground

pin371: VCCQ : I/O 3.3V power supply

pin372: VSSQ : I/O power ground

pin373: VCCQ : I/O 3.3V power supply

pin374: VSSQ : I/O power ground

pin375: VCCQ : I/O 3.3V power supply

pin376:VSS : Core power ground

pin377: VDD : Core 1.25V power supply

pin378: VSSQ : I/O power ground

pin379: VCCQ : I/O 3.3V power supply

pin380: VSSQ : I/O power ground

pin381: VCCQ : I/O 3.3V power supply

pin382:VSS : Core power ground

pin383: VDD : Core 1.25V power supply

pin384: VSSQ : I/O power ground

pin385: VCCQ : I/O 3.3V power supply

pin386: VSSQ : I/O power ground

pin387: VCCQ : I/O 3.3V power supply

pin388: VSS : Core power ground

pin389: VDD : Core 1.25V power supply

pin390: VSSQ : I/O power ground

pin391: VCCQ : I/O 3.3V power supply

pin392: VSSQ : I/O power ground

pin393: VCCQ : I/O 3.3V power supply

pin394:VCCRTC :RTC power supply 3.3V

pin395: NU : Not in use.

pin396: NU : Not in use.

pin397: WE#[2] : EXBUS write enable output

pin398: WE#[3] : EXBUS write enable output

pin399: VCCQ : I/O 3.3V power supply

pin400: VSSQ : I/O power ground

pin401: VCCQ : I/O 3.3V power supply

pin402:D[4] : EXBUS data input/output

pin403:D[0] : EXBUS data input/output

pin404: WE#[1] : EXBUS write enable output

pin405:EX_CS#[1] : EXBUS extended area chip select output

pin406: RD/WR# : EXBUS read/write

pin407: NU : Not in use.

pin408: NU : Not in use.

pin409: NU : Not in use.

pin410: A[3] : EXBUS Address output.

pin411: A[7] : EXBUS Address output.

pin412: A[8] : EXBUS Address output.

pin413: A[15] : EXBUS Address output.

pin414: A[19] : EXBUS Address output.

pin415: A[23] : EXBUS Address output.

pin416: NU : Not in use.

pin417: VSSQ : I/O power ground

pin418: VCCQ : I/O 3.3V power supply

pin419: NU : Not in use.

pin420: NU : Not in use.

pin421: GPIO-3-A25 : PLL 4fsc/K output

pin422:VSSA : Analog ground

pin423:CBU : DAC capacitor connection

pin424: VSSQ : I/O power ground

pin425: VCCQ : I/O 3.3V power supply

pin426: NU : Not in use.

pin427:VSSA : Analog ground

pin428: RD# : EXBUS read output

pin429: NU : Not in use.

pin430: VSSQ : I/O power ground

pin431:D[11] : EXBUS data input/output

pin432:D[8] : EXBUS data input/output

pin433:D[5] : EXBUS data input/output

pin434:D[1] : EXBUS data input/output

pin435: WE#[0] : EXBUS write enable output

pin436:EX_CS#[0] : EXBUS extended area chip select output

pin437:EX_WAIT[0]/EXCPU_RDY#

: EXBUS extended area external weight

signal input

pin438: NU : Not in use.

pin439: NU : Not in use.

pin440: NU : Not in use.

pin441: A[2] : EXBUS Address output.

pin442: A[6] : EXBUS Address output.

Page 20

NAX963HD

- 18 -

pin443: A[9] : EXBUS Address output.

pin444:A[14] : EXBUS Address output.

pin445:A[18] : EXBUS Address output.

pin446:A[22] : EXBUS Address output.

pin447: NU : Not in use.

pin448: OVC : USB over current detection

pin449: NU : Not in use.

pin450: DISP/CSYNC#/DE : CSYNC signal output

pin451: NU : Not in use.

pin452: GPIO-3-A26 : PLL Dclk/N output

pin453: NU : Not in use.

pin454:REXT : DAC external reference

pin455:VCCA : Analog 3.3V power supply

pin456: VSSQ : I/O power ground

pin457: NU : Not in use.

pin458: NU : Not in use.

pin459: VSSQ : I/O power ground

pin460: VSSQ : I/O power ground

pin461:D[14] : EXBUS data input/output

pin462:D[12] : EXBUS data input/output

pin463:D[9] : EXBUS data input/output

pin464:D[6] : EXBUS data input/output

pin465:D[2] : EXBUS data input/output

pin466: NU : Not in use.

pin467: NU : Not in use.

pin468: NU : Not in use.

pin469: NU : Not in use.

pin470: NU : Not in use.

pin471: NU : Not in use.

pin472:A[1] : EXBUS Address output.

pin473:A[5] : EXBUS Address output.

pin474:A[11] : EXBUS Address output.

pin475:A[13] : EXBUS Address output.

pin476:A[17] : EXBUS Address output.

pin477:A[21] : EXBUS Address output.

pin478:A[25] : EXBUS Address output.

pin479: PENC : USB power enable output

pin480: HP : USB port D+

pin481: NU : Not in use.

pin482: NU : Not in use.

pin483: VSSQ : I/O power ground

pin484: NC3 / 4fscEXCLK : 4fsc clock (14.31818MHz)

pin485: AG : Video signal Green output

pin486:VSSA : Analog ground

pin487: NU : Not in use.

pin488: VSSQ : I/O power ground

pin489:VCCA : Analog 3.3V power supply

pin490: VCCQ : I/O 3.3V power supply

pin491: VCCQ : I/O 3.3V power supply

pin492:D[15] : EXBUS data input/output

pin493:D[13] : EXBUS data input/output

pin494:D[10] : EXBUS data input/output

pin495:D[7] : EXBUS data input/output

pin496:D[3] : EXBUS data input/output

pin497: EX_CS#[2]/EXCPU_CS#[0]

: Chip select output

pin498: CS#[0] : Chip select output

pin499:CLK OUT : CKIO output (32MHz)

pin500: NU : Not in use.

pin501: NU : Not in use.

pin502: NU : Not in use.

pin503: A[0] : Not in use.

pin504: A[4] : EXBUS Address output.

pin505: A[10] : EXBUS Address output.

pin506: A[12] : EXBUS Address output.

pin507: A[16] : EXBUS Address output.

pin508: A[20] : EXBUS Address output.

pin509: A[24] : EXBUS Address output.

pin510: USBCLK :USB clock input (48MHz)

pin511: HM : USB port Dpin512: NU : Not in use.

pin513:DOTCLKIN : Dot clock input

pin514: NU : Not in use.

pin515: NU : Not in use.

pin516: AR : Video signal Red output

pin517: AB : Video signal Blue output

pin518: NU : Not in use.

pin519: VSSQ : I/O power ground

pin520: VCCA : Analog 3.3V power supply

052-1325-00 M30621MCA-FX2GP RDS-TMC

Terminal Description

pin 1: NU : - : Not in use.

pin 2: NU : - : Not in use.

pin 3: NU : - : Not in use.

pin 4: NU : - : Not in use.

pin 5 : RDS CLK : IN : RDS clock pulse input.

pin 6: NU : - : Not in use.

pin 7: NU : - : Not in use.

pin 8: NU : - : Not in use.

pin 9: RESET :IN : Reset signal input.

pin 10 : X ou t : O : Crystal connection.

pin 11 : VSS : - : Negative voltage supply.

pin 12 : X i n : IN: Crystal connection.

pin 13 : VCC : - : Positive voltage supply.

pin 14: NU : - : Not in use.

pin 15 : ACC DET : IN: ACC detection signal input.

pin 16: NU : - : Not in use.

pin 17: B/U DET : IN : Backup voltage ON signal input.

pin 18: NU : - : Not in use.

pin 19: NU : - : Not in use.

pin 20: NU : - : Not in use.

pin 21: NU : - : Not in use.

pin 22: SH RX : IN : Serial data input from SH.

pin 23: SH TX : O : Serial data output to SH.

pin 24: NU : - : Not in use.

pin 25: NU : - : Not in use.

pin 26: NU : - : Not in use.

pin 27: NU : - : Not in use.

pin 28: NU : - : Not in use.

pin 29: NU : - : Not in use.

pin 30: NU : - : Not in use.

pin 31: NU : - : Not in use.

pin 32: SYS ON : O : System ON signal output.

pin 33: NU : - : Not in use.

pin 34: NU : - : Not in use.

pin 35: NU : - : Not in use.

pin 36: NU : - : Not in use.

pin 37: NU : - : Not in use.

pin 38: NU : - : Not in use.

pin 39: NU : - : Not in use.

pin 40: NU : - : Not in use.

pin 41: NU : - : Not in use.

pin 42: NU : - : Not in use.

Page 21

NAX963HD

- 19 -

pin 43 : RDS DATA : IN : RDS serial data input.

pin 44: NU : - : Not in use.

pin 45: NU : - : Not in use.

pin 46: NU : - : Not in use.

pin 47 : SD : IN : Station detection signal input.

pin 48: PLL CE : O : The chip enable signal output to the PLL

IC.

pin 49: PLL DI : IN : Serial data input from the PLL IC.

pin 50: PLL CLK : O : The clock pulse output to the PLL IC.

pin 51: PLL DO : O : Serial data output to the PLL IC.

pin 52: NU : - : Not in use.

pin 53: NU : - : Not in use.

pin 54: NU : - : Not in use.

pin 55: NU : - : Not in use.

pin 56: NU : - : Not in use.

pin 57: NU : - : Not in use.

pin 58: NU : - : Not in use.

pin 59: NU : - : Not in use.

pin 60: NU : - : Not in use.

pin 61: NU : - : Not in use.

pin 62: NU : - : Not in use.

pin 63: NU : - : Not in use.

pin 64: NU : - : Not in use.

pin 65: NU : - : Not in use.

pin 66: NU : - : Not in use.

pin 67: NU : - : Not in use.

pin 68: NOISE :IN: The noise level for RDS.

pin 69 : Noise Clear : O : Noise clear signal output.

pin 70: NU : - : Not in use.

pin 71: NU : - : Not in use.

pin 72: NU : - : Not in use.

pin 73: NU : - : Not in use.

pin 74 : S MET ER :IN : The input terminal of internal A/D convert-

er to monitor the radio field strength.

pin 75: A V SS : - : Negative voltage supply for analog section.

pin 76: NU : - : Not in use.

pin 77 : Vref : - : Reference voltage.

pin 78: A VCC : - : Positive voltage supply for the internal

analog section.

pin 79: NU : - : Not in use.

pin 80: NU : - : Not in use.

052-3580-00 MD4832-d512-V3Q18-X-P

DiskOnChip G3 64MB (512Mb)

Ball Diagrams

Terminal Description

No. : B-No : I/O : Signal : Description

1 : D4 : IN : RSTIN# : Reset.

2 : H1 : IN : CE# : Chip enable.

3 : C5 : IN : WE# : Write enable.

4 : H2 : IN : OE# : Output enable.

5 : D7 : IN : A12 : Address.

6 : C7 : IN : A11 : Address.

7 : F6 : IN : A10 : Address.

8 : E6 : IN : A9 : Address.

9 : C6 : IN : A8 : Address.

10 : C2 : IN : A7 : Address.

11 : D2 : IN : A6 : Address.

12 : J4 : - : VCC : Core power supply.

13 : G2 : - : VSS :Ground.

14 : E2 : IN : A5 : Address.

15 : F2 : IN : A4 : Address.

16 : D1 : IN : A3 : Address.

17 : E1 : IN : A2 : Address.

18 : F1 : IN : A1 : Address.

19 : G1 : IN : A0 : Address.

20 : E3 : - : RSRVD : Reserved.

21 : G7 : IN : DMARQ# : DMA request.

22 : F3 : IN : IF_CFG : Interface configuration. High=16bit.

23 : E7 : IN : LOCK# : Lock set.

24 : F7 : IN : ID0 : Identification number.

25 : H8 : - : RSRVD :Reserved.

26 : G8 : IN : ID1 : Identification number.

27 : E4 : O : BUSY# : Busy.

28 : J2 : I /O : D0 :Data.

29 : G3 : I/O : D1 : Data.

30 : K3 : I/O : D2 : Data.

31 : H4 : I/O : D3 : Data.

32 : H5 : I/O : D4 : Data.

33 : K6 : I/O : D5 : Data.

34 : G6 : I/O : D6 : Data.

35 : J7 : I /O : D7 :Data.

36 : J8 : - : VSS : Ground.

37 : J5 : - : VCCQ : I/O power supply.

38 : K5 : IN : CLK : Clock.

39 : K2 : I/O : D8 : Data.

40 : H3 : I/O : D9 : Data.

41 : J3 : I/O : D10 : Data.

42 : K4 : I/ O : D11 : Data.

43 : J6 : I/O : D12 : Data.

44 : H6 : I/O : D13 : Data.

45 : K7 : I/ O : D14 : Data.

46 : H7 : I/O : D15 : Data.

47 : F8 : O : IRQ# : Interrupt request.

48 : E8 : - : RSRVD : Reserved.

052-7086-00 M30620MCP-D16GP Sub-microcomputer

Terminal Description

pin 1: NU : - : Not in use.

pin 2: NU : - : Not in use.

pin 3: NU : - : Not in use.

pin 4: NU : - : Not in use.

pin 5: NU : - : Not in use.

pin 6: BYTE : IN: The data length selection(8bit/16bit).

pin 7 : CN VSS : IN : L = Normal, H = Flash memory rewrite.

pin 8 : SHUT DOWN : O : Shut down signal output.

pin 9 : NAVI RESET : O : Reset signal output.

pin 10: RESET :IN : Reset signal input.

pin 11 : X ou t : O : Crystal connection.

pin 12 : VSS : - : Negative voltage supply.

pin 13 : X i n : IN: Crystal connection.

pin 14 : VCC : - : Positive voltage supply.

pin 15: NU : - : Not in use.

pin 16: NAVI MONI : IN : L = SH7770 is stop.

12345678

A

B

C

D

E

F

G

H

J

K

L

M

10396

161115

1714202782348

18152272447

191329342126

24403132444625

28411237433536

393042383345

Top View

Page 22

NAX963HD

- 20 -

pin 17: NMI MONI : IN : H = ACC ON.

pin 18 : BU DET : IN: Backup detection signal input.

pin 19 : BUS WATCH : IN : IE-Bus watching signal input.

pin 20: NU : - : Not in use.

pin 21: NU : - : Not in use.

pin 22: NU : - : Not in use.

pin 23: NU : - : Not in use.

pin 24: NU : - : Not in use.

pin 25: NU : - : Not in use.

pin 26: NU : - : Not in use.

pin 27: Ce-NET RX : IN: The serial data input from Ce-NET.

pin 28: Ce-NET TX : O : The serial data output to Ce-NET.

pin 29 : FL TX : O : The serial data output for the flash mem-

ory.

pin 30: FL RX : IN : The serial data input for the flash memo-

ry.

pin 31: FLASH CK : IN: The clock pulse input for the flash mem-

ory.

pin 32: NU : - : Not in use.

pin 33: SH TX : O : Serial data output to SH.

pin 34: SH RX : IN : Serial data input from SH.

pin 35: NU : - : Not in use.

pin 36: NU : - : Not in use.

pin 37: NU : - : Not in use.

pin 38: NU : - : Not in use.

pin 39 : FLASH EPM :IN : For flash memory.

pin 40: NU : - : Not in use.

pin 41: NU : - : Not in use.

pin 42: NU : - : Not in use.

pin 43: NU : - : Not in use.

pin 44 : FLASH CE : IN : The chip enable signal input for the flash

memory.

pin 45: NU : - : Not in use.

pin 46: NU : - : Not in use.

pin 47: NU : - : Not in use.

pin 48: NU : - : Not in use.

pin 49: NU : - : Not in use.

pin 50: NU : - : Not in use.

pin 51: NU : - : Not in use.

pin 52: NU : - : Not in use.

pin 53: LED 2 : IN: LED control input. Refer Table 1.

pin 54: LED 1 : IN: LED control input. Refer Table 1.

pin 55: TEST BOOT 2 : O : TEST BOOT output. Refer Tble 2.

pin 56: TEST BOOT 1 : O : TEST BOOT output. Refer Tble 2.

pin 57: NU : - : Not in use.

pin 58: LED ON : O : LED control output. Refer Table 1.

pin 59: NU : - : Not in use.

pin 60 : VCC : - : Positive voltage supply.

pin 61: NU : - : Not in use.

pin 62 : VSS : - : Negative voltage supply.

pin 63: NU : - : Not in use.

pin 64: NU : - : Not in use.

pin 65: NU : - : Not in use.

pin 66: EEP DI :IN : The serial data input from the EEP-ROM.

pin 67: EEP DO : O : The serial data output to the EEP-ROM.

pin 68: EEP CLK : O : The clock pulse output to the EEP-ROM.

pin 69: EEP CE : O : The chip enable signal output to the EEP-

ROM.

pin 70: NU : - : Not in use.

pin 71: MODE 1 : IN : Mode select input. Refer Table 2.

pin 72: MODE 0 : IN : Mode select input. Refer Table 2.

pin 73: NU : - : Not in use.

pin 74: NU : - : Not in use.

pin 75: NU : - : Not in use.

pin 76: NU : - : Not in use.

pin 77: NU : - : Not in use.

pin 78: NU : - : Not in use.

pin 79: NU : - : Not in use.

pin 80: NU : - : Not in use.

pin 81: NU : - : Not in use.

pin 82: NU : - : Not in use.

pin 83: NU : - : Not in use.

pin 84: NU : - : Not in use.

pin 85: NU : - : Not in use.

pin 86: NU : - : Not in use.

pin 87: NU : - : Not in use.

pin 88: NU : - : Not in use.

pin 89: NU : - : Not in use.

pin 90: NU : - : Not in use.