Page 1

(DRZ9255)

Clarion Co., Ltd.

50 Kamitoda, Toda-shi, Saitama 335-8511 Japan

Service Dept.: 5-66 Azuma , Kitamoto-shi, Saitama 364-0007 Japan

Tel: +81-48-541-2335 / 2432 FAX: +81-48-541-2703

Published by Service Dept.

298-6163-00

Printed in Japan

Jun.2004 P

Service Manual

High-Fidelity AM/FM CD Player

Model

(PE-2628B-A / For U.S.A.)

Model

P

O

W

B

A

E

TT

R

ER

S

U

Y

P

P

L

G

Y

R

O

U

N

D

(PE-2628K-A / For other countries)

SPECIFICATIONS

FM tuner section

Frequency range: 87.9MHz to 107.9MHz(U.S.A.)

87.0MHz to 108.0MHz(OTHERS)

Usable sensitivity: 9dBf

50dB quieting sensitivity: 15dBf

Alternate channel selectivity:

70dB

Stereo separation: 35dB (1kHz)

Frequency response: 30Hz to 15kHz (+/-3dB)

AM tuner section

Frequency range: 530kHz to 1710kHz(U.S.A.)

531kHz to 1629kHz(OTHERS)

Usable sensitivity: 25uV

CD player section

System: Compact disc digital audio system

Usable discs: Compact disc

Frequency response: 5Hz to 20kHz (+/-1dB)

S/N ratio: 112dB (1kHz)

Dynamic range: 100dB (1kHz)

Distortion: 0.003%(20Hz to 20kHz)

Audio section

Bass control action: +/-12dB (50Hz)

Treble control action: +/-12dB (10kHz)

Line output level: Vol.0dB=4V

Vol.+6dB=8V(Max)

(CD 1kHz)

DSP/DAC

A/D conversion: 24-bit 64x oversampling

A/D converter

D/A conversion: 96kHz/24-bit advanced segment

D/A converter

8x oversampling digital filter

Blocked band attenuation:

-130 dB

Transmitted band attenuation:

+/-0.00001dB

Sampling rate converter

Input sampling rate: fs32k, fs44.1k, fs48k,fs96k

Output sampling rate: fs48k, fs96k

DSP: 24-bit audio DSP, 34-bit arithmetic

operation (overflow margin 4-bit)

General

Power supply voltage: 14.4V DC(10.8V to 15.6V allow-

able) negative ground

Current consumption: Less than 5A

Dimensions(mm)

Source unit: 178(W)x50(H)x155(D)

DC-DC converter: 163(W)x42(H)x98(D)

Remote control unit: 52(W)x125(H)x12(D)

Weight

Source unit: 1.8kg

DC-DC converter: 700g

Remote control unit: 50g(including battery)

NOTES

* Use only compact discs bearing the or mark.Do

not play heart-shaped, octagonal, or other specially shaped

compact discs.

Some CDs recorded in CD-R/CD-RW mode may not be

usable.

* We cannot supply PWB with component parts in principle.

When a circuit on PWB has failure, please repair it by

component parts base. Parts which are not mentioned in

service manual are not supplied.

* Specifications and design are subject to change without

notice for further improvement.

- 1 -

DRZ9255

HX-D2

Page 2

COMPONENTS

PE-2628B-A,PE-2628K-A

1. Main unit ----------- 1

2. DC-DC converter EE-1236B-A 1

3. Rmote controller RCB-169-600 1

4. Battery(CR2025) ----------- 1

5. Strap 300-4976-00 1

6. Universal MTG-bracket 300-9035-01 1

7. Outer escutcheon 370-6116-00 1

8. 16-Pin extension lead(1.5m) 854-6428-00 1

(Fuse 3A 120-0030-00 1 )

9. Memory B/U lead(YEL:3.5m) 854-6423-01 1

(Fuse 10A 060-0057-56 1 )

CAUTIONS

Use of controls, adjustment or performance of procedures

other than those specified herein, may result in hazardous

radiation exposure.

The COMPACT DISC player should not be adjusted or repaired by anyone except properly qualified service personnel.

10. Ground lead(BLK:1.5m) 854-6424-01 1

11. Parts bag for DC-DC converter ----------- 1

11-1. Mounting bracket 300-7362-02 2

11-2. Terminal cover 345-7403-00 1

11-3. Tapping screw 700-5016-89 4

11-4. Machine screw(M5x8) 714-4008-89 4

11-5. Plate nut 725-0216-00 4

12. Parts bag for source unit ----------- 1

12-1. Hook plate 330-8216-03 2

12-2. Lead holder 335-0833-03 1

12-3. Hexagonal screw(M5x8) 716-0496-01 1

MODEL

12V GROUND

AM 530 -1710kHz /FM 87.9 -107.9MHz

THIS DEVICE COMPLIES WITH PART 15 OF THE FCC RULES.

OPERATION IS SUBJECT TO THE FOLLOWING TWO CONDITIONS:

(1) THIS DEVICE MAY NOT CAUSE HARMFUL INTERFERENCE, AND

(2) THIS DEVICE MUST ACCEPT ANY INTERFERENCE RECEIVED,

INCLUDING INTERFERENCE THAT MAY CAUSE UNDESIRED

OPERATION.

THIS PRODUCTION COMPLIES WITH DHHS RULES 21 CFR

SUBCHAPTER J APPLICABLE AT DATE OF MANUFACTURE.

CLARION CO.,LTD.

50 KAMITODA,TODA-SHI,SAITAMA-KEN,JAPAN

MANUFACTURED:

To engineers in charge of repair or inspection of our products.

Before repair or inspection, make sure to follow the

instructions so that customers and Engineers in

charge of repair or inspection can avoid suffering

any risk or injury.

1. Use specified parts.

The system uses parts with special safety features against

fire and voltage. Use only parts with equivalent characteristics when replacing them.

The use of unspecified parts shall be regarded as remodeling for which we shall not be liable. The onus of product

liability (PL) shall not be our responsibility in cases where

an accident or failure is as a result of unspecified parts

being used.

2. Place the parts and wiring back in their original positions

after replacement or re-wiring.

For proper circuit construction, use of insulation tubes,

bonding, gaps to PWB, etc, is involved. The wiring connection and routing to the PWB are specially planned using

clamps to keep away from heated and high voltage parts.

Ensure that they are placed back in their original positions

after repair or inspection.

If extended damage is caused due to negligence during

repair, the legal responsibility shall be with the repairing

company.

3. Check for safety after repair.

Check that the screws, parts and wires are put back securely in their original position after repair. Ensure for safety

reasons there is no possibility of secondary ploblems around

the repaired spots.

If extended damage is caused due to negligence of repair,

the legal responsibility shall be with the repairing company.

DRZ9255

HX-D2

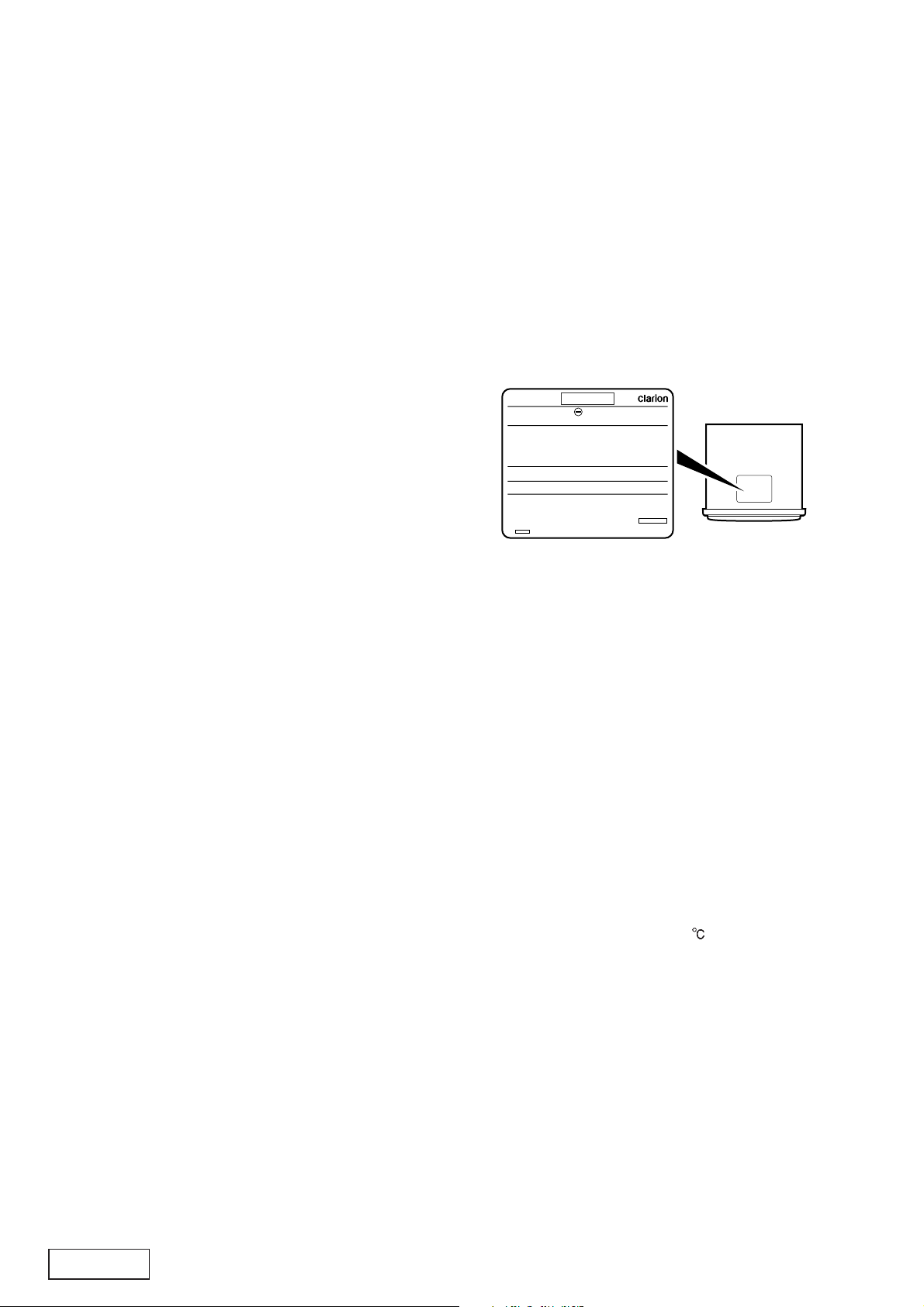

SERIAL No.

PE-

Clarion Co.,Ltd.

MADE IN

Bottom View of DRZ9255

4. Caution in removal and making wiring connection to the

parts for the automobile.

Disconnect the battery terminal after turning the ignition

key off. If wrong wiring connections are made with the

battery connected, a short circuit and/or fire may occur. If

extensive damage is caused due to negligence of repair,

the legal responsibility shall be with the repairing company.

5. Cautions regarding chips.

Do not reuse removed chips even when no abnormality is

observed in their appearance. Always replace them with

new ones. (The chip parts include resistors, capacitors,

diodes, transistors, etc). The negative pole of tantalum

capacitors is highly susceptible to heat, so use special care

when replacing them and check the operation afterwards.

6. Cautions in handling flexible PWB

Before working with a soldering iron, make sure that the

iron tip temperature is around 270

. Take care not to apply the iron tip repeatedly(more than three times)to the

same patterns. Also take care not to apply the tip with force.

7. Turn the unit OFF during disassembly and parts replacement. Recheck all work before you apply power to the unit.

8. Cautions in checking that the optical pickup lights up.

The laser is focused on the disc reflection surface through

the lens of the optical pickup. When checking that the laser optical diode lights up, keep your eyes more than 30cms

away from the lens. Prolonged viewing of the laser within

30cms may damage your eyesight.

9. Cautions in handling the optical pickup

The laser diode of the optical pickup can be damaged by

electrostatic charge caused by your clothes and body. Make

sure to avoid electrostatic charges on your clothes or body,

or discharge static electricity before handling the optical

pickup.

- 2 -

Page 3

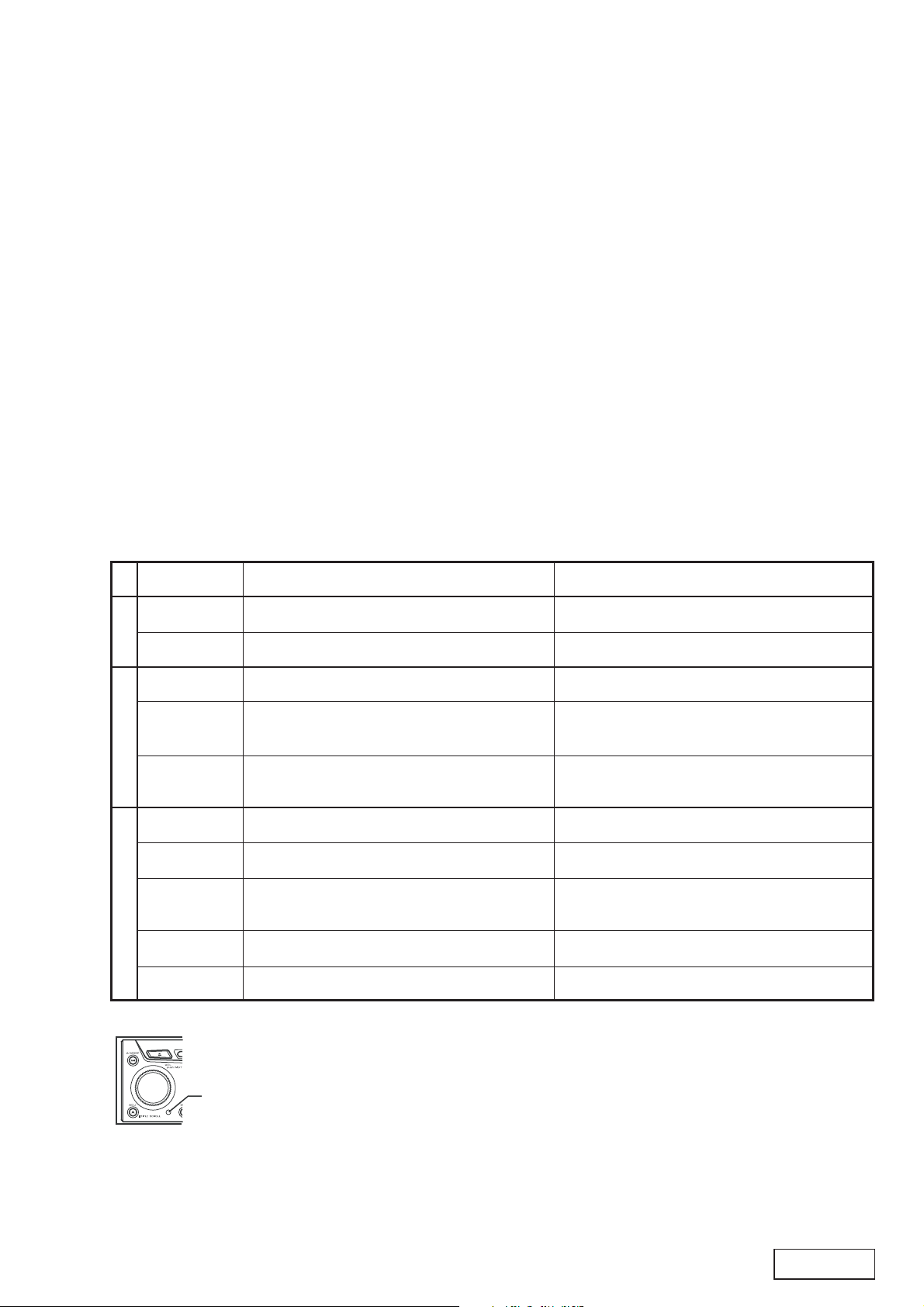

ERROR 2

ERROR 3

ERROR 2

ERROR 3

ERROR 6

ERROR 2

ERROR 3

ERROR 6

ERROR P

ERROR R

A CD is caught inside the CD deck and is not ejected.

A CD cannot be played due to scratches,etc.

A CD inside the CD changer is not loaded.

A CD inside the CD changer cannot be played due

to scratches, etc.

A CD inside the CD changer cannot be played

because it is loaded upside-down.

A DISC inside the DVD changer cannot be played.

A DISC cannot be played due to scratches,etc.

A DISC inside the DVD changer cannot be played

because it is loaded upside-down.

Parental level error

Region code error

This is a failure of CD deck's mechanism.

Replace with a non-scratched,non-warped-disc.

This is a failure of CD changer's mechanism.

Replace with a non-scratched, non-warped disc.

Eject the disc then reload it properly.

This is a failure of DVD mechanism.

Retry or replace with a non-scratched, non-warped-disc.

Eject the disc then reload it properly.

Set the correct Parental level.

Eject the disc and replace correct region code disc.

CD

DVD changer

CD changer

Cause MeasureError Display

If an error display other than the ones described above appears,

press the reset button.

Reset button

9-1. Laser diode

The laser diode terminals are shorted for transportation in order to prevent electrostatic damage. After

replacement, open the shorted circuit. When removing the pickup from the mechanism, short the

terminals by soldering them to prevent this damage.

9-2. Actuator

The actuator has a powerful magnetic circuit. If a

magnetic material is put close to it. Its characteristics will change. Ensure that no foreign substances enter through the ventilation slots in the

cover.

9-3. Cleaning the lens

Dust on the optical lens affects performance. To

clean the lens, apply a small amount of isopropyl

alcohol to lens paper and wipe the lens gently.

SYSTEM CHECK

The first time this unit is turned on after the wire connections

are completed, it must be checked what equipment is connected. When the power is turned on,

SYSTEM CHK

and Push POWERappear in the display alternately, so

press the [FUNC] button. The system check starts within

the unit. When the system check is complete, press the

[FUNC] button again.

ERROR DISPLAYS

If an error occurs, one of the following displays is displayed.

Take the measures described below to eliminate the problem.

Digital wiring

When the optical digital cable is connected to or disconnected from this set later, press the function button while

holding down direct buttons [1] and [6] with the power OFF

to perform a system check.

Though pressing the reset button also performs a system

check, the contents of memory will be erased completely in

this case.

- 3 -

DRZ9255

HX-D2

Page 4

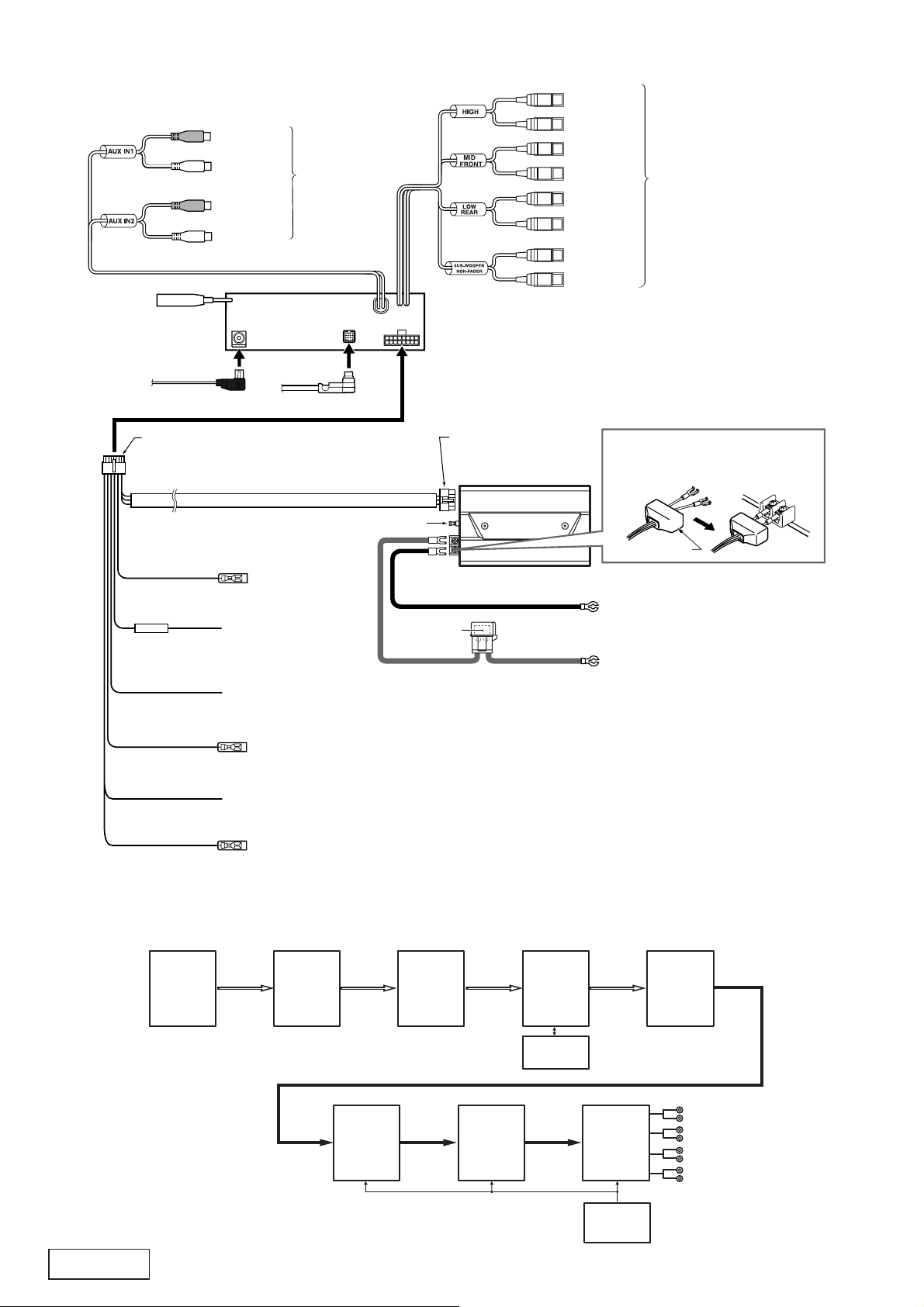

WIRE CONNECTIONS

Red

White

Red

White

Black

Antenna input

AUX INPUT-1

Right

AUX INPUT-1

Left

AUX INPUT-2

Right

AUX INPUT-2

Left

To external unit

Source unit

Red

White

Red

White

Red

White

Red

White

HIGH

Right

HIGH

Left

MID/FRONT

Right

MID/FRONT

Left

LOW/REAR

Right

LOW/REAR

Left

Subwoofer

Right

Subwoofer

Left

To external amplifier

Digital input/output

Optical digital cable

16-Pin Connector Extension Lead 1.5m

Brown wire(phone mute lead)

Yellow wire(Bus power lead)

Fuse(3A)

Red wire(Power lead)

Blue/White wire(Amplifier turn-on lead)

Orange/White wire(Illumination lead)

Blue wire(Auto antenna lead)

Black

Connect directly to

battery.

Accessory +12V

Connect to the car power supply terminal for illumination.

CeNET input

Connect to cellular

phone mute lead.

Connect to remote turn-on lead of amplifier.

Connect it to the car supply terminal for the antenna.

CeNET cable

10-Pin Connector

DC-DC Converter

Fuse(5A)

Black wire(Ground lead)1.5m

Fuse(10A)

Yellow wire(Memory back-up lead)3.5m

Terminal Cover

Place the terminal cover on the terminals

to prevent a short circuit.

Terminal Cover

Connect to vehicle chassis ground.

Connect the terminal on the main power cord to

the car battery(+) terminal.

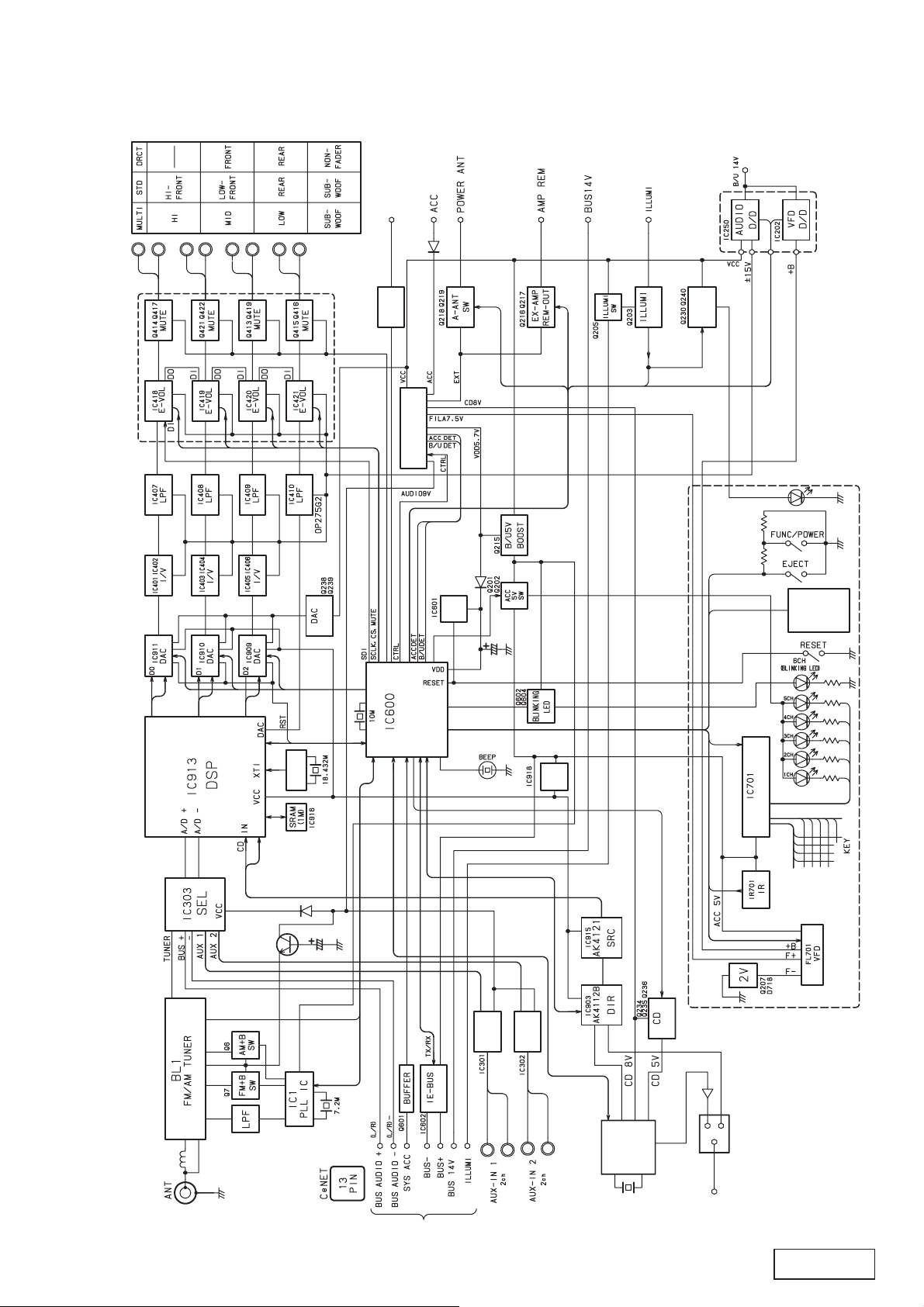

BLOCK DIAGRAM

Audio line sction

CD

Mechanism

DRZ9255

HX-D2

IC903

DIGITAL DIGITAL DIGITAL DIGITAL

Digital

Interface

Receiver

IC401

ANALOG ANALOG ANALOG

䌾IC406

I/V

Converter

IC915

Sampling

-rate

Converter

IC407

䌾IC410

Low-pass

Filter

IC913

Digital

Signal

Processor

IC918

S-RAM

IC418

䌾IC421

High-quality

Electrical

Volume

IC250

DC/DC

Converter

- 4 -

+

-

15V

IC909

䌾IC911

24bit

D/A

Converter

ANALOG

8ch Line-out

Hi

Mid

Low

Sub-woofer

Page 5

System section

PHONE INT

DC/DC PWB

RCA LINEOUT

5V STB

Q603

INT

PHONE

MASTER

IC200

POWER SUPPLY

U-COM

2.1V

DET

DET

ILL+B

KEY ILL

S718

VOL

IC912

CLK IC

DRIVER

STB

3.3V

EXPANDER

SW PWB

ISOLAT

ISOLAT

5V STB

CD MECH

DIGITAL IN

- 5 -

DRZ9255

HX-D2

Page 6

EXPLANATION OF IC

052-3393-00 M30622MEP-161GP System Controller

Terminal Description

pin 1: CD SBSY : IN : The sub Q data request command input

pin 2: TIME BASE : IN : Time base pulse input.

pin 3: DSP RDY : IN: Ready signal input from the DSP IC.

pin 4: NU : - : Not in use.

pin 5: REMOCON : IN: Remote controller signal input terminal.

pin 6: BYTE : IN : The data length selection(8bit/16bit).

pin 7: CN VSS :IN : Connect to VSS.

pin 8: INIT 1 : IN : Destination setting input. Refer Table 1.

pin 9: INIT 2 : IN : Destination setting input. Refer Table 1.

pin 10: RESET :IN : Reset signal input.

pin 11: X out : O : Crystal connection.

pin 12: VSS : - : Negative voltage supply.

pin 13: X IN : IN : Crystal connection.

pin 14: VCC : - : Positive voltage supply.

pin 15: NU : - : Not in use.

pin 16: ACC DET :IN : ACC detection signal input.

pin 17: B U DET : IN : Backup detection signal input.

pin 18: KEY INT : IN : Key interrupting signal input.

pin 19: 27pinConnect :IN : Connect to pin 27.

pin 20: VFD BLANK : O : Blank pulse output to the VFD driver.

pin 21: BUS IN/out : O : The audio signal control for Ce-NET.

pin 22: BEEP : O : Beep out.

pin 23: E VOL CS : O : The chip select signal output to Electric

pin 24: E VOL SD : O : The serial data output to Electric Volume

pin 25 : E VOL SCLK : O : The serial clock output to Electric Volume

pin 26: CLK REF : O : Reference clock pulse output.

pin 27 : IE BUS RX : IN : IE Bus serial data input.

pin 28 : IE BUS TX : O : IE Bus serial data output.

pin 29: EMULATOR TX : O : The serial data output to the emulator.

pin 30: EMULATOR RX : IN : The serial data input from the emulator.

pin 31: CONNECT G : - : Connect to the ground.

pin 32: NU : - : Not in use.

pin 33: VFD SO : O : The serial data output to the VFD driver.

pin 34: NU : - : Not in use.

pin 35: VFD CLK : O : The clock pulse output to the VFD driver.

pin 36: VFD LAT : O : The latch strove signal output to the VFD

pin 37: JOG CW : IN : Jog key signal input.

pin 38 : JOG CCW : IN: Jog key signal input.

pin 39: CONNECT G : - : Connect to the ground.

pin 40: CATS LED : O : CATS LED drive output.

pin 41: KEY Set : O : Set signal output to the key scan IC.

pin 42: KEY CHIP SEL : O : The chip select signal output to the key

pin 43: KEY CLK : O : The clock pulse output for the key scan IC.

pin 44: CONNECT G : - : Connect to the ground.

pin 45: KEY DI : IN : Key scan data input.

pin 46: KEY DO : O : The serial data output to the Key scan IC.

pin 47: LD MUTE : O : Muting signal output to the CD mechanism.

pin 48: LD CONT : O : The laser diode control signal output.

pin 49: CD TR A : IN : The photo sensor signal input from the CD

pin 50: CD TR B : IN : The photo sensor signal input from the CD

pin 51: CD CHK SW : IN: CD disc chucking signal input.

pin 52: CD SSTOP : IN: At loading, detects the chucking. And next,

pin 53: CD RESET : O : The reset pulse output to the CD IC.

pin 54: CD CCE : O : The chip enable signal output to the CD

pin 55: CD BU CK : O : CD IC clock pulse output.

pin 56: CD BUS 3 :I/O: The data bus.

pin 57: CD BUS 2 :I/O: The data bus.

pin 58: CD BUS 1 :I/O: The data bus.

pin 59: CD BUS 0 :I/O: The data bus.

from the CD IC.

Volume IC.

IC.

IC.

driver.

scan IC.

mechanism.

mechanism.

detects the inside limit of the pick up position.

IC.

pin 60: VCC : - : Positive voltage supply.

pin 61: CD 5V : O : 5V power supply ON signal output for CD.

pin 62: VSS : - : Negative voltage supply.

pin 63: REG CTRL : O : Power supply IC control signal output.

pin 64: 5V REM : O : 5V power supply ON signal output.

pin 65: PLL SI : IN : Serial data input from the PLL IC.

pin 66: PLL SO : O : Serial data output to the PLL IC.

pin 67: PLL SCK : O : The clock pulse output to the PLL IC.

pin 68 : PLL CE : O : The chip enable signal output to the PLL

pin 69: ST SD : IN: At receiving the FM station, this port de-

pin 70: VFD DD ON : O : VFD DD converter ON signal output.

pin 71: ILL DET : IN : Illumination ON signal input.

pin 72: DIR ERF :IN : Unlock & Parity error flag input from the

pin 73: PHONE INT : IN : The telephone interrupt signal input.

pin 74: AUTO ANT : O : Motor antenna control signal output.

pin 75: AMP REM : O : Standby signal output to Audio power am-

pin 76: DIG In/Out sel : O : Digital input/output selection.

pin 77: SYS MUTE : O : System muting signal output.

pin 78: PRE MUTE : O : Pre-mute signal output.

pin 79: SEL CLK : O : The serial clock output to the audio selec-

pin 80: SEL DATA : O : The serial data output to the audio selec-

pin 81: KEY ILL REM : O : Key illumination ON signal output.

pin 82: DAC MC : O : Clock pulse output to the DAC.

pin 83: DAC MD : O : Serial command data output to the DAC.

pin 84: DAC MS : O : Chip select output to the DAC.

pin 85: DIR PDN : O : The power down signal output to the DIR

pin 86: PCM DET : IN : Non-PCM detection signal input.

pin 87 : DIR CDT O : O : The control data output to the DIR IC.

pin 88: DIR CCLK : O : The control clock output to the DIR IC.

pin 89: DIR CSN : O : The chip select output to the DIR IC.

pin 90: DSP INIT RST : O : The reset signal output to DSP IC.

pin 91: DSP RST : O : Reset pulse output to the DSP IC.

pin 92: SYS ACC : O : ACC detect signal output.

pin 93: DSP REQ : O : Request signal output to DSP IC.

pin 94: A V SS : - : Negative voltage supply for analog section.

pin 95: KEY AD : IN : Input terminal of A/D converter for Key

pin 96: Vref : - : Reference voltage.

pin 97: A VCC : - : Positive voltage supply for the internal an-

pin 98: DSP SI : IN : Serial data input from the DSP IC.

pin 99: DSP SO : O : Serial data output to the DSP IC.

pin100: DSP SCK : O : The clock pulse output to DSP IC.

Table 1. Destination setting

INIT 1 ( pin 8 ) H H L

INIT 2 ( pin 9 ) H L L

IC.

tects the stereo signal. At seeking or scanning, this port detects the station detection

signal.

DIR IC.

plifier.

tor IC.

tor IC.

IC.

judgment.

alog section.

Japan Noth America Asia

DRZ9255

HX-D2

- 6 -

Page 7

051-6705-00 AK7720A Audio DSP with 2ch ADC and 6ch DAC

Terminal Description

pin 1: LFLT :IN : The capacitor and the resistor connection

pin 2: A VSS : - : Analog ground.

pin 3: A V DD : - : Positive supply voltage for the Analog sec-

pin 4: INIT RESET : IN : The initial reset input.

pin 5: CODEC RESET : IN : The CODEC reset input.

pin 6: DSP RESET : IN : DSP reset input.

pin 7: S MUTE : IN : The soft muting command input.

pin 8: B VSS : - : Ground for the bus interface section.

pin 9: PLL : IN : Open or Connect to DVSS usually.

pin 10: CKS : IN : The clock pulse selection.

pin 11: S Data in A : IN : DSP serial data input. Open or connect to

pin 12: S Data in 1 : IN : DSP serial data input.

pin 13: S Data in 2 : IN : DSP serial data input.

pin 14: S Data out 1 : O : DSP serial data output.

pin 15: S Data out 2 : O : DSP serial data output.

pin 16: S Data out 3/AD: O : DSP/ADC serial data output.

pin 17: S D OUT : O : The serial data output.

pin 18:LR CK I/O :I/O: SMODE(pin20) = L : 1fs clock input.

pin 19: BIT CLK :I/O: SMODE(pin20) = L : 64fs clock input.

pin 20: S MODE : IN : Slave master selection.

pin 21: Clock Out : O : Clock Out.

pin 22: D VSS : - : Digital ground.

pin 23: D VD D : - : Positive supply voltage for the digital sec-

pin 24: XT I : IN : Oscillation terminal.

pin 25: XT O : O : Oscillation terminal.

pin 26: JX : IN : External jumping signal input.

pin 27 : RQ : IN: The request signal input from the master

pin 28: S CL K : IN : Sift clock input.

pin 29: SI : IN : Serial data input.

pin 30: SO : O : Serial data output.

pin 31: Write Ready : O : Write ready flag output.

pin 32: Data Ready : O : Data output ready flag output.

pin 33:CAS :O :The column address strobe output to

pin 34: RAS : O : The row address strobe output to DRAM.

pin 35: WRITE ENBL : O : The write enable signal output.

pin 36: D VD D : - : Positive supply voltage for the digital sec-

pin 37: D VSS : - : Digital ground.

pin 38: A 0 : O : Address signal output.

pin 39: A 1 : O : Address signal output.

pin 40: A 2 : O : Address signal output.

pin 41: A 3 : O : Address signal output.

pin 42: A 4 : O : Address signal output.

pin 43: A 5 : O : Address signal output.

pin 44: A 6 : O : Address signal output.

pin 45: A 7 : O : Address signal output.

pin 46: A 8 : O : Address signal output.

pin 47: A 9 : O : Address signal output.

pin 48: A 1 0 : O : Address output to the external DRAM.

pin 49: A 1 1 : O : Address output to the external DRAM.

pin 50: A 12 : O : Address signal output.

pin 51: A 13 : O : Address signal output.

pin 52: A 14 : O : Address signal output.

pin 53: A 15 : O : Address signal output.

pin 54: A 16 : O : Address signal output.

pin 55: D VD D : - : Positive supply voltage for the digital sec-

pin 56: D VSS : - : Digital ground.

pin 57: OUT ENABLE : O : The output enable command output.

pin 58: I/O 0 :I/O: Data input/output.

pin 59: I/O 1 :I/O: Data input/output.

pin 60: I/O 2 :I/O: Data input/output.

terminal for PLL.

tion.

DVSS usually.

SMODE(pin20) = H : 1fs clock output.

SMODE(pin20) = H : 64fs clock output.

tion.

side.

DRAM.

tion.

tion.

- 7 -

pin 61: I/O 3 :I/O: Data input/output.

pin 62: I/O 4 :I/O: Data input/output.

pin 63: I/O 5 :I/O: Data input/output.

pin 64: I/O 6 :I/O: Data input/output.

pin 65: I/O 7 :I/O: Data input/output.

pin 66: D VD D : - : Positive supply voltage for the digital sec-

pin 67: D VSS : - : Digital ground.

pin 68: TEST : - : For the Test.

pin 69: TEST : - : For the Test.

pin 70: B VSS : - : Ground.

pin 71: A OUT 3 R- : O : Inverted Right channel audio signal output

pin 72: A OUT 3 R+ : O : Non-inverted Right channel audio signal

pin 73: NU : - : Not in use.

pin 74: A OUT 3 L- : O : Inverted Left channel audio signal output of

pin 75: A OUT 3 L+ : O : Non-inverted Left channel audio signal out-

pin 76: A OUT 2 R- : O : Inverted Right channel audio signal output

pin 77: A OUT 2 R+ : O : Non-inverted Right channel audio signal

pin 78: NU : - : Not in use.

pin 79: A OUT 2 L- : O : Inverted Left channel audio signal output of

pin 80: A OUT 2 L+ : O : Non-inverted Left channel audio signal out-

pin 81: NU : - : Not in use.

pin 82: A OUT 1 R- : O : Inverted Right channel audio signal output

pin 83: A OUT 1 R+ : O : Non-inverted Right channel audio signal

pin 84: NU : - : Not in use.

pin 85: A OUT 1 L- : O : Inverted Left channel audio signal output of

pin 86: A OUT 1 L+ : O : Non-inverted Left channel audio signal out-

pin 87: Vr DAC Low : IN : The reference voltage input.

pin 88: A VSS : - : Analog ground.

pin 89: A VSS : - : Analog ground.

pin 90: A VD D : - : Positive supply voltage for the Analog sec-

pin 91: Vr DAC High : IN : The reference voltage input.

pin 92: NU : - : Not in use.

pin 93: Vr ADC Low : IN : The reference voltage input.

pin 94: A VSS : - : Analog ground.

pin 95: A VD D : - : Positive supply voltage for the Analog sec-

pin 96: Vr ADC High : IN : The reference voltage input.

pin 97: A IN R- : IN : Inverted Right channel audio signal input.

pin 98: A IN R+ : IN: Non-inverted Right channel audio signal

pin 99: A IN L- : IN : Inverted Left channel audio signal input.

pin100: A IN L+ : IN : Non-inverted Left channel audio signal in-

tion.

of DAC-3.

output of DAC-3.

DAC-3.

put of DAC-3.

of DAC-2.

output of DAC-2.

DAC-2.

put of DAC-2.

of DAC-1.

output of DAC-1.

DAC-1.

put of DAC-1.

tion.

tion.

input.

put.

DRZ9255

HX-D2

Page 8

051-6399-00 TC94A15F CD IC

Terminal Description

pin 1: IPF OUT : O : IP flag output.

pin 2: SB O K O : O : Sub code Q data CRCC OK signal output.

pin 3: CLOCKIO :I/O: The clock pulse input/output for the sub

code reading.

pin 4: VDD : - : Positive supply voltage.

pin 5: VSS : - : Negative supply voltage.

pin 6: DATA : O : DATA

pin 7: SF S Y O : O : Playback frame synchronous signal output.

pin 8: SB SY O : O : Sub code block synchronous signal output.

pin 9: HSO : O : The play speed flag output.

pin 10: UHSO : O : The play speed flag output.

pin 11: AR SEL IN : IN : Fix to the high level.

pin 12: AWRC : O : The control signal output for the active

wide range VCO.

pin 13: P VDD : - : PLL positive supply voltage.

pin 14: PDO : O : Phase difference signal output of EFM-

PLCK.

pin 15: TMAX S : O : T max judgment output.

pin 16: TMAX : O : T max judgment output.

pin 17 : LPF N : IN : Inverted input of LPF for PLL.

pin 18: LPF OUT : O : The output terminal for the Low Pass Fil-

ter.

pin 19: P Vref : - : PLL reference voltage.

pin 20: VCO FILTER : O : Loop filter for VCO.

pin 21: VCO Ref : IN : VCO reference voltage input.

pin 22 : DTC N : O : For the analog slicer.

pin 23: DTC P : O : For the analog slicer.

pin 24: PLL VSS : - : PLL ground.

pin 25: SLCO : O : Output of internal DAC for data slice level

generation.

pin 26: RF IN : IN : RF signal input.

pin 27: RF R P : IN : RF ripple input.

pin 28: RF EQ O UT : O : The output of the RF equalizer.

pin 29: A VD D : - : Positive supply voltage for the Analog sec-

tion.

pin 30: RES IN : - : For reference current setting.

pin 31: Vref OUT : O : The reference voltage output.

pin 32: VMDIR : O : The reference voltage output.

pin 33: TESTR : O : The compensation terminal for RFEQO off-

set.

pin 34: INVSEL : IN : MDI polarity selection.

pin 35: AGCI :IN : The input terminal of RF AGC amplifier.

pin 36: RF DCI : IN : The input terminal for RF peak detection.

pin 37: RF O UT : O : RF signal output.

pin 38: PN S EL : IN : The transistor type selection input for laser

diode driver. L=NPN, H=PNP.

pin 39: E Q SET : O : The equalizer setting terminal.

pin 40: RF VDD : - : RF power supply.

pin 41: LDO : O : The laser diode drive output.

pin 42: MDI : IN : Monitor photo diode signal input.

pin 43: RF VSS : - : RF ground.

pin 44: FNI 2 : IN : Main beam signal input.

pin 45: FNI 1 : IN : Main beam signal input.

pin 46: FPI 2 : IN : Main beam signal input.

pin 47: FPI 1 : IN : Main beam signal input.

pin 48: TPI : IN : Sub beam signal input.

pin 49: TNI :IN : Sub beam signal input.

pin 50: FTEO : O : For test.

pin 51: RF ZI : IN : RF ripple zero cross signal input.

pin 52: A VSS : - : Analog ground.

pin 53: RF R P : O : RF ripple signal output.

pin 54: RF D C : O : RF peak detection signal output. (hologram

suitable)

pin 55: FEI : O : Focus error signal output.

pin 56: SBAD : O : Sub beam add signal output.

pin 57: TEI : O : Tracking error signal output.

pin 58: TE Z IN : IN : Tracking error signal inpur for zero cross.

pin 59: A VD D : - : Positive supply voltage for the Analog sec-

tion.

pin 60: FOO : O : Focus equalizer output.

DRZ9255

HX-D2

pin 61: TRO : O : Tracking equalizer output.

pin 62: Vref : O : Reference voltage output.

pin 63: FMO :O : Field equalizer output / Speed error output.

pin 64: DMO : O : Disk equalizer output.

pin 65: IO2A :I/O: General input/output.

pin 66: IO3A :I/O: General input/output.

pin 67: MONIT : O : Internal DSP signal monitor.

pin 68: FG IN : IN : FG input for the spindle CAV servo.

pin 69: VSS : - : Negative supply voltage.

pin 70: VDD : - : Positive supply voltage.

pin 71: TESIN : IN : For test.

pin 72: X V SS : - : Master clock analog ground.

pin 73: X IN : IN : Crystal connection.

pin 74: X O : O : Crystal connection.

pin 75: X VDD : - : Clock power supply.

pin 76: D VSS : - : Digital ground.

pin 77: RO : O : Right channel data output for 1-bit DAC.

pin 78: D VD D : - : Positive supply voltage for the digital sec-

tion.

pin 79: D Vref : O : Digital reference voltage.

pin 80: LO : O : Left channel data output for 1-bit DAC.

pin 81: D VSS : - : Digital ground.

pin 82: Z DET O : O : 1bit DAC zero flag output.

pin 83: VSS : - : Negative supply voltage.

pin 84: BUS 0 :I/O: CD IC Data input / output.

pin 85: BUS 1 :I/O: CD IC Data input / output.

pin 86: BUS 2 :I/O: CD IC Data input / output.

pin 87: BUS 3 :I/O: CD IC Data input / output.

pin 88: BU CK IN : IN : CD IC Data clock input.

pin 89: CCEI : IN : Chip enable input.

pin 90: RSTI :IN : Reset signal input.

pin 91: VDD : - : Positive supply voltage.

pin 92: EMPHI/FAO :I/O: Emphasis input for 1-bit DAC / Flag A

pin 93: BCKI/FBO :I/O:Bit clock input for 1-bit DAC / Flag B out-

output.

put.

pin 94: AIN/FCO :I/O: Audio input for 1-bit DAC / Flag C output.

pin 95: LRCKI/FDO :I/O:LR clock input for 1-bit DAC / Flag D out-

put.

pin 96: EMPHO : O : Emphasis flag output. H=Emphasis ON.

pin 97: B C K O : O : Bit clock output.

pin 98: A OUT : O : Audio signal output.

pin 99: LR CK O : O : LR clock output.

pin100: D O UT : O : Serial data output.

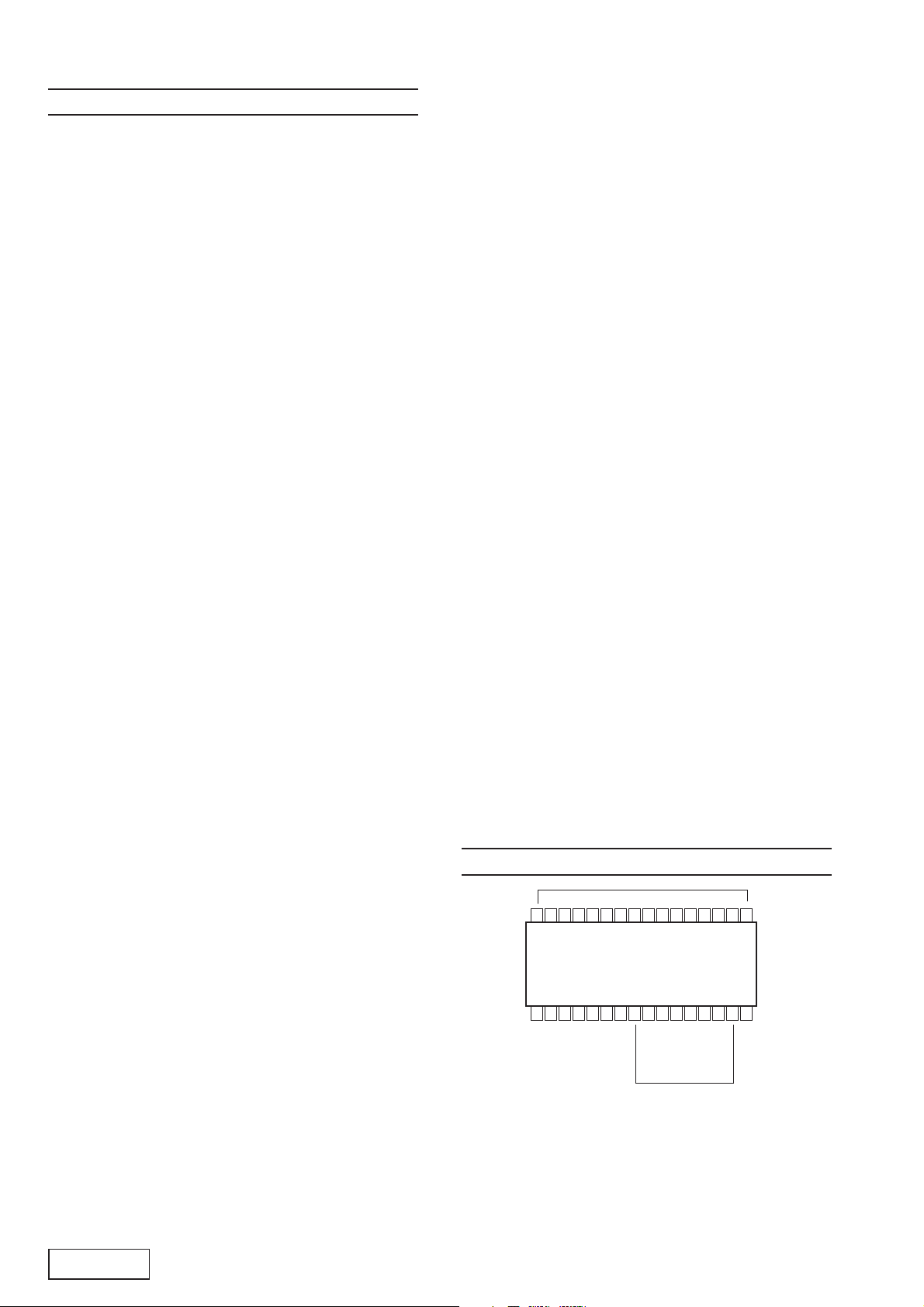

051-6643-90 M66010GP 24-bit I/O Expander

Parallel Data Input/Output

323130292827262524232221201918

D 1

D 2

D 3

D 4

D 5

D 6

D 7

D 8

D 9

D 10

D 11

D 12

DODICLKCSVCC

123456789

Serial Data output

Serial Data input

SET

GND

Clock Pulse input

Chip Select input

Positive Supply

Set Signal input

Ground

D 24

D 23

D 22

D 21

10111213141516

Parallel

Data

Input/Output

D 20

D 13

D 19

D 14

D 18

D 15

D 17

17

D 16

GND

Ground

- 8 -

Page 9

051-6373-18 AK4112BVF Digital Interface Receiver

Terminal Description

pin 1: D V DD : - : Positive voltage supply for the digital sec-

tion.

pin 2: D VSS : - : Digital ground.

pin 3: T VDD : - : Positive voltage supply for output-buffer.

pin 4: VALIDITY : O : Validity flag output in the parallel mode.

: TX : O : Transmit channel (through data) output in

serial mode.

pin 5: XT I : IN : Oscillation terminal.

pin 6: XT O : O : Oscillation terminal.

pin 7: PDN : IN : Power down & reset signal input.

pin 8: RESIST : - : The resistor connection.

pin 9: A VDD : - : Positive voltage supply for analog section.

pin 10: A V SS : - : Negative voltage supply for analog section.

pin 11: RX 1 : IN : The receiver channel 1 in serial mode.

pin 12: DIF 0 : IN : The audio data format selection in parallel

mode, refer Table 1.

: RX 2 : IN : The receiver channel 2 in serial mode.

pin 13: DIF 1 : IN : The audio data format selection in parallel

mode, refer Table 1.

: RX 3 : IN : The receiver channel 3 in serial mode.

pin 14: DIF 2 : IN : The audio data format selection in parallel

mode, refer Table 1.

: RX 4 : IN : The receiver channel 4 in serial mode.

pin 15: PCM DET : O : Non-PCM detect. L = Non detect.

pin 16: PARA/SERI :IN : Parallel("H")/Serial("L") mode select input.

pin 17: FS96 : O : 96kHz Sampling detect.

RX mode

H : fs = 88.2kHz or more

L : fs = 54kHz or less

Xtal mode

H : XFS96 = 1

L : XFS96 = 0

pin 18: ERF : O : Unlock & Parity error output. L = No error.

pin 19: LR CK I/O :I/O: Left/Right clock.

pin 20 : SDT O : O : The audio serial data output.

pin 21: BI CK :I/O: Audio serial data clock.

pin 22: D AUX : IN : Auxiliary audio serial data input.

pin 23: MCK O 2 : O : Master clock output, refer Table 2.

pin 24: MCK O 1 : O : Master clock output, refer Table 2.

pin 25: OCK Sel 0 : IN : Output clock select in parallel mode.

refer Table 2.

: CSN : IN : Chip select input in serial mode.

pin 26: OCK Sel 1 : IN : Output clock select in parallel mode.

refer Table 2.

: C CLK : IN : Control clock input in serial mode.

pin 27: C M 1 : IN : Master clock operation select input in par-

allel mode, refer Table 3.

: CDTI :IN : Control data input in serial mode.

pin 28: C M 0 : IN : Master clock operation select input in par-

allel mode, refer Table 3.

: CDTO : O : Control data output in serial mode.

Table 1. Audio data format

DIF 2 DIF 1 DIF 0 D AUX SDT O LR CK BI CK

(pin 14) (pin 13) (pin 12) (pin 22) (pin 20) (pin 19) (pin 21)

0 0 0 Left Right

0 0 1 Left Right

0 1 0 Left Right

0 1 1 Left Right

1 0 0 Left Left

101

1 1 0 Left Left

111

24bit 16bit H/L 64fs

justified justified Output Output

24bit 18bit H/L 64fs

justified justified Output Output

24bit 20bit H/L 64fs

justified justified Output Output

24bit 24bit H/L 64fs

justified justified Output Output

24bit 24bit H/L 64fs

justified justified Output Output

24bit 24bit L/H 64fs

I2S I2S Output Output

24bit 24bit H/L 64-128fs

justified justified Intput Input

24bit 24bit H/L 64-128fs

I2S I2S Intput Input

Table 2. Master clock frequency select

OCK S 1 OCK S 0 MCK O 1 MCK O 2

(pin 26) (pin 25) (pin 24) (pin 23) X'tal fs(kHz)

0 0 256fs 256fs 256fs 44.1

0 1 256fs 128fs 256fs 44.1

1 0 512fs 256fs 512fs 44.1

1 1 - - Test Mode - -

Table 3. Clock operation mode select

CM 1 CM 0 Clock FS96 SDT O

(pin 27) (pin 28) UNLOCK PLL X'tal source (pin 17) (pin 20)

0 0 x ON OFF PLL RFS96 RX

0 1 x OFF ON X'tal XFS96 D AUX

1 0 0 ON O N PLL RFS96 RX

1 0 1 ON ON X'tal XFS96 D AUX

1 1 x ON ON X'tal XFS96 D AUX

32.0

48.0

96.0

32.0

48.0

96.0

32.0

48.0

- 9 -

DRZ9255

HX-D2

Page 10

051-6708-90 AK4121VF Asynchronous Sample Rate Converter

Terminal Description

pin 1: FILT : O : PLL filter output.

pin 2: A V SS : - : Negative voltage supply for analog section.

pin 3: PDN : IN : Power down & reset signal input.

pin 4: S MUTE : IN : The soft muting command input.

pin 5 : DEM 0 : IN : De-emphasis Frequency Selection.

pin 6 : DEM 1 : IN : De-emphasis Frequency Selection.

pin 7: I L R CK : IN : Left/Right clock input for the input signal.

pin 8: I BI C K : IN : Bit clock input for the input signal.

pin 9: SDT I : IN : The serial data input.

pin 10: I DIF 0 : IN : Input data format select.

pin 11: I DIF 1 : IN : Input data format select.

pin 12: I DIF 2 : IN : Input data format select.

pin 13: C MODE 0 : IN : The clock mode select.

pin 14: C MODE 1 : IN : The clock mode select.

pin 15: C MODE 2 : IN : The clock mode select.

pin 16: O DIF 0 : IN : Output data format select.

pin 17: O DIF 1 : IN : Output data format select.

pin 18 : SDT O : O : The audio serial data output.

pin 19: O BI C K :I/O: Bit clock input/output for the output signal.

pin 20: O L R CK :I/O: Left/Right clock input/output for the output

signal.

pin 21: MASTER CLK : IN : Master clock input.

pin 22: T VDD : - : Positive voltage supply for output-buffer.

pin 23: D VSS : - : Digital ground.

pin 24: VDD : - : Positive voltage supply.

Table 1. Master/Slave control

Cmode 2 Cmode 1 Cmode 0 Master CLK Master/Slave

(pin 15) (pin 14) (pin 13) (pin 21) (Output port)

L L L 256fso(fso to 96kHz) Master

L L H 384fso(fso to 96kHz) Master

L H L 512fso(fso to 48kHz) Master

L H H 768fso(fso to 48kHz) Master

H L L Connect to DVSS Slave

H H H Connect to DVSS Master(bypass mode)

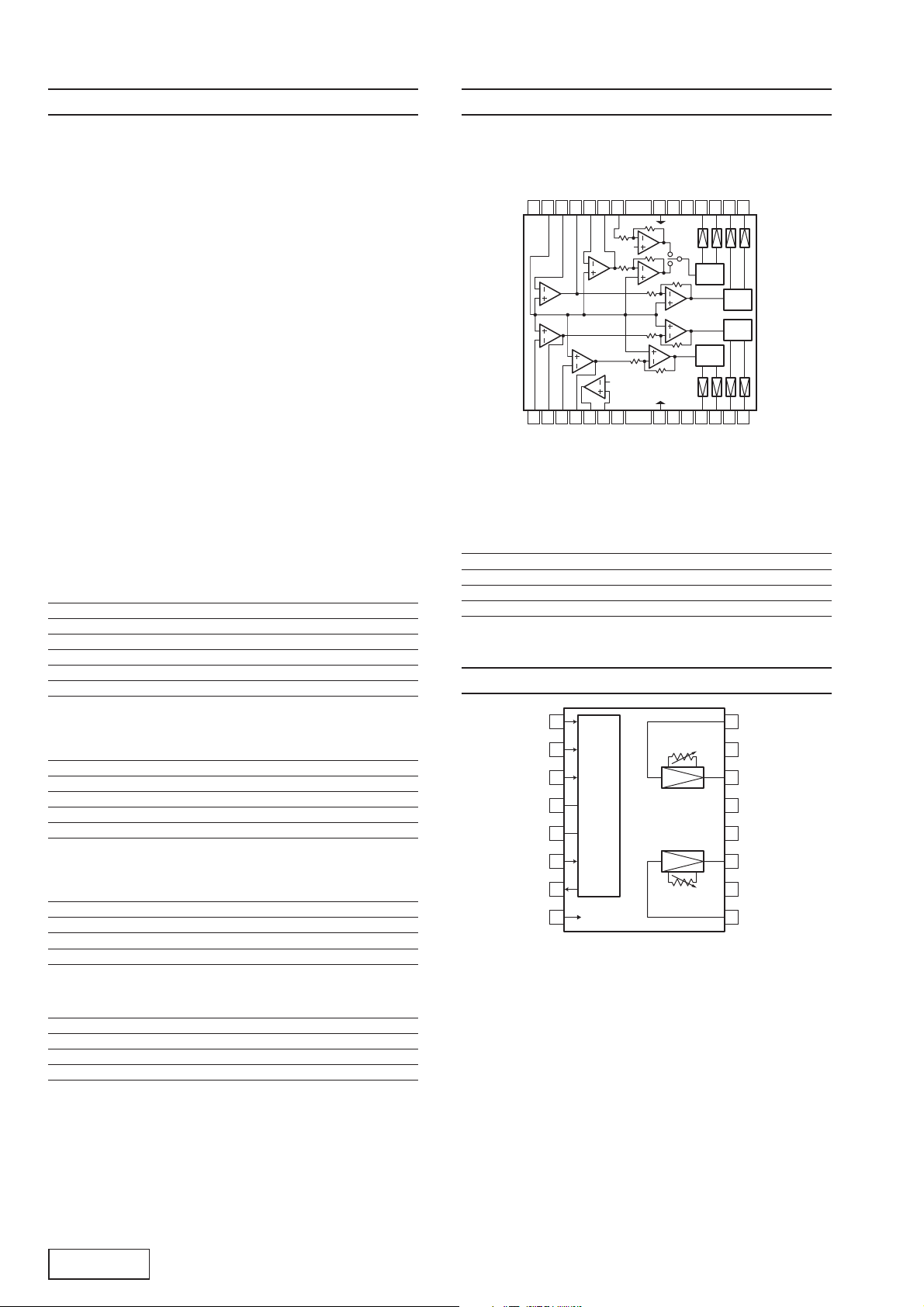

051-6071-08 BA5825FP-E2 Quad Motor Drivers

Pre VCC

Bias

3-ch OP in-

3-ch OP out

SL OP in-

SL OP out

Loading in-

Control in

Power Ground

Power Vcc

4-ch drive out-

4-ch drive out+

3-ch drive out-

28272625242322

2.4V

2.4V

1234567

2-ch OP in-

2-ch OP out

1-ch OP in-

1-ch OP out

REG-Base

REG-FB

Pr-Ground

21201918171615

Level

Shift

Level

Shift

8

9

1011121314

Mute in

Power GND

Power Vcc

3-ch drive out+

Level

Shift

Level

Shift

1-ch drive out-

1-ch drive out+

2-ch drive out-

2-ch drive out+

Truth Table

MUTE CNT CH1,2,3 CH4

(pin 9) (pin 21) output output

H H MUTE OFF LD ON

H L MUTE OFF SL ON

L H MUTE ON LD ON

L L MUTE ON MUTE ON

051-5036-90 PGA2310UA Stereo Volume Controller

Table 2. Input Audio data Formats

I DIF 2 I DIF 1 I DIF 0 SDT I format I BI CK (slave)

(pin 12) (pin 11) (pin 10) (pin 9) (pin 8)

L L L 16bit LSB Justified 32 or less

L L H 20bit LSB Justified 40 or less

L H L 20bit MSB Justified 40 or less

L H H 20/16bit I2C compat. 32/40fs or less

H L L 24bit LSB Justified 48 or less

Table 3. Output Audio data Formats

O DIF 1 O DIF 0 SDT O format O BI CK O BI CK

(pin 17) (pin 16) (pin 18) (Slave) (Master)

L L 16bit LSB Justified 64fs 64fs

L H 20bit LSB Justified 64fs 64fs

H L 20/16bit MSB Justif. 32/40fs or less 64fs

H H 20/16bit I2C compat. 32/40fs or less 64fs

Table 4. De-emphasis filter control

DEM 1 (pin 6) DEM 0 (pin 5) De-emphasis filter

L L 44.1kHz

L H off

H L 48.0kHz

L H 32.0kHz

L IN

ZCEN

CS_

S Data I

D VDD

D GND

S CLK

S Data O

Mute In

1

2

3

Logic

Control

4

5

6

7

8

16

15

14

13

12

11

10

9

L A GND

L OUT

A V-

A V+

R OUT

R A GND

R IN

Terminal Description

pin 1: ZCEN : IN : Zero Cross Enable signal input.

pin 2: CS IN : IN : The chip select command input.

pin 3: S DATA IN : IN : The serial data input.

pin 4: D VDD : - : Positive voltage supply for digital section.

pin 5: D GND : - : Digital ground.

pin 6: S CL K : IN : The serial clock input.

pin 7: S DATA OUT : O : The serial data output.

pin 8: MUTE IN : IN : Mute command input.

pin 9: R A IN : IN : Right channel audio signal input.

pin 10: R A GND : - : Right channel audio signal ground.

pin 11: R A OUT : O : Right channel audio signal output.

pin 12: A V+ : - : Positive voltage supply for analog section.

pin 13: A V - : - : Negative voltage supply for analog section.

pin 14: L A OUT : O : Left channel audio signal output.

pin 15: L A GND : - : Left channel audio signal ground.

pin 16: L A IN : IN : Left channel audio signal input.

DRZ9255

HX-D2

- 10 -

Page 11

051-9126-00 BS62LV1024STI-70 128 x 8 bit SRAM

051-6709-90 PCM1792DBR 24bit 192kHz DA Converter

Terminal Description

pin 1: A 11 :IN : Address signal input.

pin 2: A 9 : IN : Address signal input.

pin 3: A 8 : IN : Address signal input.

pin 4: A 13 :IN : Address signal input.

pin 5: W E_ : IN : Write enable signal input.

pin 6: CE 2 : IN : The chip enable signal input.

pin 7: A 15 :IN : Address signal input.

pin 8: VCC : - : Positive voltage supply.

pin 9: NU : - : Not in use.

pin 10: A 16 : IN : Address signal input.

pin 11: A 14 : IN : Address signal input.

pin 12: A 12 : IN : Address signal input.

pin 13: A 7 : IN: Address signal input.

pin 14: A 6 : IN: Address signal input.

pin 15: A 5 : IN: Address signal input.

pin 16: A 4 : IN: Address signal input.

pin 17: A 3 : IN: Address signal input.

pin 18: A 2 : IN: Address signal input.

pin 19: A 1 : IN: Address signal input.

pin 20: A 0 : IN: Address signal input.

pin 21: D 0 :I/O: Data input/output.

pin 22: D 1 :I/O: Data input/output.

pin 23: D 2 :I/O: Data input/output.

pin 24: GND : - : Ground.

pin 25: D 3 :I/O: Data input/output.

pin 26: D 4 :I/O: Data input/output.

pin 27: D 5 :I/O: Data input/output.

pin 28: D 6 :I/O: Data input/output.

pin 29: D 7 :I/O: Data input/output.

pin 30: CE 1_ :IN : The chip enable signal input.

pin 31: A 10 : IN : Address signal input.

pin 32: OE_ : IN : Output enable signal input.

Truth Table

WE_ CE 1_ CE 2 OE_

(pin 5) (pin 30) (pin 6) (pin 32) I/O Operation

x H x x High Z

x x L x High Z

H L H H High Z

H L H L data out

L L H x data in

Terminal Description

pin 1: ZERO L : O : ZERO flag output for Left channel.

pin 2: ZERO R : O : ZERO flag output for Right channel.

pin 3: M SEL : IN : I2C/SPI_ select.

pin 4: LR CK IN : IN : Left/Right clock input.

pin 5: DATA IN : IN : Serial data input.

pin 6: B C K IN : IN : Bit clock input.

pin 7: SCK : IN : The system clock pulse input.

pin 8: D GND : - : Digital ground.

pin 9: D V DD : - : Positive voltage supply for the digital sec-

tion.

pin 10: MS : IN : Chip select for mode control.

pin 11: MDI : IN : Mode control data input.

pin 12: MC : IN : Mode control clock input.

pin 13: MD : O : Mode control read back data output.

pin 14: RSTI :IN : Reset signal input.

pin 15: A VCC : - : Positive voltage supply for the internal an-

alog section.

pin 16: A GND : - : Analog ground.

pin 17: I out R+ : O : Right channel analog signal current output

pin 18: I out R- : O : Right channel analog signal current output

+.

-.

pin 19: A GND : - : Analog ground.

pin 20: Iref : - : Output current bias.

pin 21: V com R : - : Right channel internal bias.

pin 22: V com L : - : Left channel internal bias.

pin 23: A VCC : - : Positive voltage supply for the internal an-

alog section.

pin 24: A GND : - : Analog ground.

pin 25: I out L+ : O : Left channel analog signal current output +.

pin 26: I out L- : O : Left channel analog signal current output -

.

pin 27: A GND : - : Analog ground.

pin 28: A VCC : - : Positive voltage supply for the internal an-

alog section.

051-7285-08 CD74HC4050PWR Hex Buffer

16

NC

VCC

1

15

14

13

NC

2

3

4

11

12

5

6

9

10

GND

7

8

051-3232-90 uPD29M33T 3.3V Voltage Regulator

Terminal Description

pin 1: Input(power source)

pin 2: Ground

pin 3: Output

- 11 -

051-3042-90 OPA2134UA Dual Operational Amplifier

7

6

5

VCC 8

1

2

VEE

3

4

051-3012-90 OP275GS Dual Operational Amplifier

7

6

5

VCC 8

1

2

VEE

3

4

DRZ9255

HX-D2

Page 12

EXPLODED VIEW / PARTS LIST

Main section

38

51

41

D1

82

39

85

D2

91

38

92

57

82

E1

A1

40

38

A1

E1

79

D3

73

53

D1

83

47

82

D4

E2

82

80

38

D2

E2

75

A2

71

72

78

E3

60

65

68

40

E2

64

66

E4

59

87

A2

40

62

63

E3

61

D3

42

77

69

86

D4

E4

40

E4

58

40

74

(x12)

32

10

9

DRZ9255

HX-D2

31

35

36

37

30

45

5

6

32

89

46

43

55

84

67

52

82

76

70

81

91

92

46

34

27

25

13

24

12

(x5)

23

14

15

22

21

20

54

50

19

16

(x3)

18

17

(x6)

49

56

(x6)

48

26

33

31

88

90

4

7

11

44

8

29

28

3

1

2

- 12 -

Page 13

1 378-0546-00 BADGE(PE2628BA:DRZ9255) 1

2 371-5778-01 FACE PANEL(PE2628BA) 1

3 373-1036-00 DIAL COVER 1

4 370-6112-01 ESCUTCHEON 1

5 380-5591-00 KNOB CAP 1

6 345-5402-00 RUBBER RING 1

7 380-5592-00 INNER KNOB 1

8 335-7212-00 ILLUMI PLATE (L) 1

9 346-0163-00 LEATHER SHEET 1

10 371-5779-00 TRIM PLATE 1

11 382-6997-00 BUTTON (L) 1

12 335-7209-00 PACK ILLUMI 1

13 382-6998-00 BUTTON (1-4) 1

14 382-6999-00 BUTTON (2-5) 1

15 382-7000-00 BUTTON (3-6) 1

16 335-7219-00 BUTTON ILLUMI 3

17 335-7210-00 IND-ILLUMI 6

18 335-7211-00 ILLUMI PLATE 1

19 335-7213-00 BUTTON HOLDER 1

20 382-6995-00 BUTTON (P/A) 1

21 382-6994-00 BUTTON (BAND) 1

22 382-6993-00 BUTTON (>>) 1

23 382-6992-00 BUTTON (ENT) 1

24 382-6991-00 BUTTON (<<) 1

25 382-6990-00 BUTTON (FUNC) 1

26 382-6996-00 BUTTON (D) 1

27 335-7215-00 BUTTON HOLDER 5

28 335-7214-00 IR-FILTER 1

29 347-7383-00 DOUBLE FACE 2

30 016-0025-00 VR W/SHAFT 1

31 347-7384-00 SHADE FILM(R/L) 2

32 347-7385-00 SHADE FILM(VFD) 2

33 347-7386-00 DOUBLE FACE(VFD) 1

34 347-7387-00 DOUBLE FACE(ILLUMI) 2

35 379-4053-28 VFD 1

36 335-7216-00 VFD HOLDER 1

37 335-7218-00 ILLUMI PLATE (C) 1

38 714-2603-81 MACHINE SCREW (M2.6x3) 4

39 345-5798-00 CUSHION 1

40 716-0306-10 SCREW (M3x6) 7

41 929-0291-80 CD MECH MODULE 1

42 855-5505-00 RCA PIN CORD (8CH) 1

43 074-1105-22 OUTLET SOCKET 1

44 347-7408-00 SHADE FILM 1

45 覧覧SWITCH PWB 1

46 716-0872-01 PAD SCREW (M1.7x5) 5

47 331-3775-00 MECH BRACKET 1

48 347-7380-00 SHADE FILM (L) 1

49 347-7382-00 SHADE FILM (R) 1

378-0547-00 BADGE(PE2628KA:HX-D2) 1

371-5778-00 FACE PANEL(PE2628KA) 1

- 13 -

NO. PART NO. DESCRIPTION Q'TYNO. PART NO. DESCRIPTION Q'TY

50 347-7379-00 SHADE FILM (PRESET) 6

51 816-4004-00 FLAT WIRE 1

52 347-7376-00 E-SHEET 1

53 309-0798-00 FRONT PLATE 1

54 714-2004-81 MACHINE SCREW (M2x4) 2

55 716-0872-11 SCREW (M1.7x6) 2

56 345-5140-00 RUBBER SPACER 6

57 305-0248-02 SIDE COVER (L) 1

58 305-0249-02 SIDE COVER (R) 1

59 313-1895-00 HEAT SINK 1

60 307-0702-00 REAR COVER 1

61 331-2946-00 SHIELD COVER (R) 1

62 331-2945-00 SHIELD COVER (F) 1

63 347-7377-00 INSULATOR 1

64 313-1781-00 HEAT SINK 1

65 074-1023-16 OUTLET SOCKET (POWER) 1

66 074-1194-00 OUTLET SOCKET (Ce NET) 1

67 345-5796-00 CUSHION 1

68 074-1138-76 OUTLET SOCKET 1

69 075-0385-10 JACK (OPTICAL-IN) 1

70 347-7375-00 INSULATOR 1

71 076-6002-12 PLUG 1

72 076-0515-08 PLUG (8P) 1

73 076-0515-12 PLUG (12P) 1

74 345-3799-01 RUBBER PART 12

75 076-0515-22 PLUG 1

76 304-0470-01 LOWER COVER 1

77 092-2214-00 ANT-RECEPT 1

78 074-1106-08 OUTLET SOCKET 1

79 303-0458-08 UPPER COVER 1

80 074-1106-12 OUTLET SOCKET 1

81 286-6456-00 SETPLATE(PE2629BA) 1

82 714-3006-81 MACHINE SCREW (M3x6) 6

83 覧覧MAIN PWB 1

84 345-5795-00 CUSHION 1

85 345-5797-00 HEAT RUBBER 1

86 855-5500-00 RCA PIN CORD (4CH) 1

87 880-2090B TUNER PACK 1

88 347-7415-00 FILM 1

89 347-7416-00 FILM 1

90 347-7417-00 FILM 1

91 750-2796-02 SPRING 2

92 714-5008-41 MACHINE SCREW 2

286-6457-00 SETPLATE(PE2629KA) 1

DRZ9255

HX-D2

Page 14

DC-DC converter(EE-1236B-A) section

18

12

6

7

4

5

3

2

17

15

11

9

10

7

1

16

7

11

10

12

13

NO. PART NO. DESCRIPTION Q'TY

1 ----------- DC/DC PWB 1

2 073-0722-01 TERMINAL (BATT/GND) 1

3 077-0091-00 FUSE-RECEPT 1

8

4 074-0884-02 OUTLET SOCKET (10P) 1

5 060-0057-54 AUTO FUSE(5A) 1

6 331-3776-00 CONECTOR HOLDER 1

7 716-0821-02 IT SCREW 4

8 303-0487-00 UPPER COVER 1

9 383-0715-01 DECORATE PANEL 1

10 345-5443-00 O-RING 2

11 716-3521-00 LOCK SCREW (M3X4) 2

12 714-3006-89 MACHINE SCREW (M3X6) 4

13 311-1886-01 LOWER COVER 1

14 702-3008-89 TAP SCREW 2

15 702-2006-19 TAP SCREW 2

16 345-5444-00 SPACER 1

17 073-0731-01 TERMINAL 1

18 347-7378-00 PROTECT SHEET 1

14

CD mechanism(929-0291-80) section

1 966-0595-25 DRIVE PLATE ASSY 1

2 969-0065-31 PICK UP UNIT 1

3 ----------- LED PWB 1

4 ----------- CD PWB 1

5 SMA-182-100 MOTOR ASSY(SPINDLE) 1

6 SMA-183-100 MOTOR ASSY(SLED) 1

7 HBS-524-100 CLAMPER SUB ASSY 1

7-1 620-1022-25 CLAMPER LINK 1

7-2 620-1023-23 CLAMPER PLATE 1

7-3 620-1024-23 SENSOR ARM 1

7-4 621-0708-20 CLAMPER RING 1

7-5 621-0626-21 STOPPER LINK 1

7-6 621-0627-21 DISC STOPPER 1

7-7 750-3471-20 SENSOR SPRING 1

8 803-4906-60 VINYL COAT WIRE(ORG) 1

9 816-2591-00 LEAD WIRE(YEL) 1

10 620-1025-22 ID-LOCK PLATE 1

11 620-1026-21 SPRING PLATE 1

12 620-1027-27 LOWER CHASSIS 1

13 620-1028-23 UPPER CHASSIS 1

14 966-0638-20 SH-RACK ASSY 1

15 621-0598-27 UPPER GUIDE 1

16 621-0599-26 ROLLER GUIDE 1

17 621-0600-26 SHIFT LEVER 1

18 621-0601-21 RACK 1

19 621-0602-22 LOCK ARM L 1

DRZ9255

HX-D2

NO. PART NO. DESCRIPTION Q'TYNO. PART NO. DESCRIPTION Q'TY

20 621-0603-25 LOCK ARM R 1

21 621-0724-21 GEAR BASE 1

22 621-0605-22 GEAR COVER 1

23 621-0723-20 IDLE CASE 1

24 816-2590-00 VINYL COAT WIRE(GRN) 1

25 621-0608-21 SECOND GEAR 1

26 621-0609-20 BASE GEAR 1

27 621-0610-20 IDLE GEAR A 1

28 621-0611-20 IDLE GEAR B 1

29 621-0612-21 ROLLER GEAR A 1

30 621-0719-20 ROLLER GEAR B 1

31 621-0720-20 ROLLER GEAR C 1

32 621-0721-20 ROLLER GEAR D 1

33 621-0616-20 POWER GEAR A 1

34 621-0617-20 POWER GEAR B 1

35 621-0618-20 POWER GEAR C 1

36 621-0619-20 POWER GEAR D 1

37 621-0620-20 THREAD GEAR A 1

38 621-0621-20 THREAD GEAR B 1

39 621-0622-21 ROLLER SLEEVE 2

40 621-0623-23 LS-HOLDER 1

41 621-0624-22 GUIDE RAIL 1

42 816-2593-00 LEAD WIRE(PUR) 1

43 816-2542-01 FLAT WIRE(10P) 1

44 716-3473-00 IT SCREW(M2 x 3) 2

45 621-0709-20 SH-BASE 1

- 14 -

Page 15

46 621-0629-20 LOADING ROLLER 2

47 345-8704-20 CUSHION RUBBER 1

48 622-1571-21 ROLLER SHAFT 1

49 624-0018-01 LEAD SCREW 1

50 629-0081-20 DAMPER F 2

51 629-0082-20 DAMPER R 1

52 714-2003-81 MACHINE SCREW(M2 x 3) 2

53 716-1507-00 SCREW(M2 x 3) 9

54 716-1733-00 SCREW(M1.7 x 2.3) 2

55 716-3469-00 SCREW(φ3 x 4) 2

56 716-3446-00 SCREW(M1.4 x 2.5) 2

NO. PART NO. DESCRIPTION Q'TYNO. PART NO. DESCRIPTION Q'TY

57 750-3465-21 ROLLER SPRING L 1

58 750-3466-20 ROLLER SPRING R 1

59 750-3467-21 SHIFT SPRING 1

60 750-3468-20 RACK SPRING 1

61 750-3469-20 CLAMPER SPRING 1

62 750-3470-20 ID-LOCK SPRING 1

63 816-2592-00 LEAD WIRE(BLU) 1

64 750-3472-21 DR-SPRING F 2

65 750-3473-20 DR-SPRING RA 1

66 750-3474-20 DR-SPRING RB 1

67 750-3475-21 DR-SPRING C 1

64

52

19

44

D1

B2

57

G13

A6

52

A4

H3

H1

H2

3

A5

44

15

31

13

A7

F1

7-4

E2

7-5

7-7

7-2

7-3

E1

7-1

16

B1

32

G12

D2

58

48

46

E2

B2

39

46

8

63

9

H3

H1

42

H6

24

H4

H2

H5

H7

G6

39

B1

G13

A1

5

H8

3

H6

I1

H7

53

65

A1

50

D1

A4

A8

64

A6

A3

G2

A2

50

D2

I2

47

51

F1

A5

4

43

53

I1

54

1

67

A8

G6

H5

H4

56

6

C6

C7

L2

56

11

53

25

G3

66

A7

12

53

M1

20

7-6

62

10

G14

G2

G16

41

54

G14

G16

C2

A2

C6

C7

21

C3

37

29

G5

G15

G4

A3

C1

30

G15

G9

C5

G1

G8

G7

G7

G5

40

G11

G10

C4

53

G3

G10

17

G1

G8

G9

M1

C5

59

E1

18

I2

2

35

36

34

60

G4

61

38

7

55

45

14

G1

49

C2

33

23

28

C1

26

27

C4

L1

22

C3

H8

53

- 15 -

DRZ9255

HX-D2

Page 16

ELECTRICAL PARTS LIST

Main PWB(B1) section

REF No. PART No. DESCRIPTION REF No. PART No. DESCRIPTION REF No. PART No. DESCRIPTION

BL1 880-2090B TUNER PACK

C1 168-2232-55 0.022uF K

C2 163-2263-35 16V22uF

C4 163-1053-65 50V1uF

C5 168-3332-78 0.033uF K

C6 168-3332-78 0.033uF K

C7 187-4763-35 16V47uF

C8 168-2232-55 0.022uF K

C9 168-2232-55 0.022uF K

C10 168-6822-55 6800pF K

C11 042-1631-50 10V100uF

C12 042-1631-50 10V100uF

C13 168-1032-55 0.01uF K

C14 168-1532-55 0.015uF K

C16 168-1032-55 0.01uF K

C18 163-3353-65 50V3.3uF

C20 163-4763-15 6.3V47uF

C21 166-1011-50 100pF CH

C22 166-1011-50 100pF CH

C23 166-1011-50 100pF CH

C24 166-3311-50 330pF CH

C25 166-1801-50 18pF CH

C26 166-1501-50 15pF CH

C27 163-2253-65 50V2.2uF

C28 163-2253-65 50V2.2uF

C29 168-2232-55 0.022uF K

C55 166-2201-50 22pF CH

C66 166-2201-50 22pF CH

C67 168-1032-55 0.01uF K

C68 168-1032-55 0.01uF K

C200 187-1073-35 16V 100uF

C201 187-1073-35 16V 100uF

C203 187-1063-35 16V 10uF

C204 042-9129-00 16V270uF

C205 187-4763-35 16V47uF

C206 042-1549-12 16V220uF

C207 187-1063-35 16V 10uF

C208 042-1549-12 16V220uF

C210 163-2263-35 16V22uF

C211 187-4763-35 16V47uF

C212 042-1631-50 10V100uF

C213 042-1631-50 10V100uF

C214 163-1063-35 16V10uF

C215 168-1032-55 0.01uF K

C216 042-1631-50 10V100uF

C217 163-2263-35 16V22uF

C218 172-2231-15 0.022uF

C219 168-1022-55 1000pF K

C220 168-1042-78 16V 0.1uF

C221 187-1063-65 50V10uF

C222 168-1022-55 1000pF K

C223 043-0318-90 5600pF

C224 166-1011-50 100pF CH

C225 168-1032-55 0.01uF K

C226 168-1032-55 0.01uF K

C227 168-1022-55 1000pF K

C228 168-1022-55 1000pF K

C229 168-1032-55 0.01uF K

C230 168-1022-55 1000pF K

(PE2628KA)

C231 168-1011-50 100pF CH

(PE2628KA)

C233 168-1022-55 1000pF K

(PE2628KA)

C301 168-4732-78 0.047uF K

C302 168-4732-78 0.047uF K

C303 042-0654-52 16V 10uF

C304 042-0654-52 16V 10uF

C305 042-0654-52 16V 10uF

C306 042-0654-52 16V 10uF

C307 042-0654-52 16V 10uF

C308 042-0654-52 16V 10uF

C309 042-0654-52 16V 10uF

DRZ9255

HX-D2

C310 042-0654-52 16V 10uF

C311 166-3301-50 33pF CH

C312 166-3301-50 33pF CH

C313 166-3301-50 33pF CH

C314 166-3301-50 33pF CH

C315 166-3301-50 33pF CH

C316 166-3301-50 33pF CH

C317 166-3301-50 33pF CH

C318 166-3301-50 33pF CH

C319 163-2253-65 50V2.2uF

C320 163-2253-65 50V2.2uF

C321 163-2253-65 50V2.2uF

C322 163-2253-65 50V2.2uF

C323 187-1073-35 16V 100uF

C324 168-1042-78 16V 0.1uF

C325 042-0654-52 16V 10uF

C326 042-0654-52 16V 10uF

C327 042-0654-52 16V 10uF

C328 042-0654-52 16V 10uF

C329 042-0654-52 16V 10uF

C330 042-0654-52 16V 10uF

C331 042-0654-52 16V 10uF

C332 168-1042-78 16V 0.1uF

C333 042-0654-52 16V 10uF

C334 168-1042-78 16V 0.1uF

C335 168-1042-78 16V 0.1uF

C336 163-1053-65 50V1uF

C337 163-1053-65 50V1uF

C338 163-1053-65 50V1uF

C339 163-1053-65 50V1uF

C340 163-2263-35 16V22uF

C341 178-4742-78 0.47uF

C342 042-0423-97 16V10uF

C343 042-0654-52 16V 10uF

C344 042-0654-52 16V 10uF

C345 042-0654-52 16V 10uF

C346 042-0654-52 16V 10uF

C347 166-3301-50 33pF CH

C348 166-3301-50 33pF CH

C349 166-3301-50 33pF CH

C350 166-3301-50 33pF CH

C351 042-0654-52 16V 10uF

C352 042-0654-52 16V 10uF

C353 042-0654-52 16V 10uF

C354 042-0654-52 16V 10uF

C355 168-1032-55 0.01uF K

C356 168-1032-55 0.01uF K

C357 168-1032-55 0.01uF K

C358 168-1032-55 0.01uF K

C359 168-1022-55 1000pF K

C360 166-1011-50 100pF CH

C401 043-0264-51 2200pF

C402 043-0264-51 2200pF

C403 043-0264-51 2200pF

C404 043-0264-51 2200pF

C405 043-0264-51 2200pF

C406 043-0264-51 2200pF

C407 043-0264-51 2200pF

C408 043-0264-51 2200pF

C409 043-0264-51 2200pF

C410 043-0264-51 2200pF

C411 043-0264-51 2200pF

C412 043-0264-51 2200pF

C413 173-5611-18 560pF J

C414 173-5611-18 560pF J

C415 173-5611-18 560pF J

C416 173-5611-18 560pF J

C417 173-5611-18 560pF J

C418 173-5611-18 560pF J

C419 166-5611-50 560pF CH

C420 166-5611-50 560pF CH

C421 166-2211-50 220pF CH

C422 166-2211-50 220pF CH

- 16 -

C423 166-2211-50 220pF CH

C424 166-1211-50 12pF CH

C425 166-2211-50 220pF CH

C426 166-2211-50 220pF CH

C427 166-2211-50 220pF CH

C428 166-1211-50 12pF CH

C429 166-2211-50 220pF CH

C430 166-2211-50 220pF CH

C431 166-2211-50 220pF CH

C432 166-1211-50 12pF CH

C433 166-2211-50 220pF CH

C434 166-2211-50 220pF CH

C435 166-2211-50 220pF CH

C436 166-1211-50 12pF CH

C437 168-1042-78 16V 0.1uF

C439 168-1022-55 1000pF K

(PE2628KA)

C440 042-0654-50 6.3V 22uF

C441 042-0654-50 6.3V 22uF

C442 042-0654-50 6.3V 22uF

C443 042-0654-50 6.3V 22uF

C449 168-1032-55 0.01uF K

C450 168-1032-55 0.01uF K

C451 168-1032-55 0.01uF K

C452 168-1032-55 0.01uF K

C453 168-1032-55 0.01uF K

C454 168-1032-55 0.01uF K

C455 168-1032-55 0.01uF K

C456 168-1032-55 0.01uF K

C457 168-1032-55 0.01uF K

C458 168-1032-55 0.01uF K

C459 168-1032-55 0.01uF K

C460 168-1032-55 0.01uF K

C461 168-1032-55 0.01uF K

C462 168-1032-55 0.01uF K

C463 168-1032-55 0.01uF K

C464 168-1032-55 0.01uF K

C465 042-1505-89 10V10uF(OS)

C466 042-1505-89 10V10uF(OS)

C467 042-1505-89 10V10uF(OS)

C468 042-1505-89 10V10uF(OS)

C469 168-1032-55 0.01uF K

C470 168-1032-55 0.01uF K

C471 168-1032-55 0.01uF K

C472 168-1032-55 0.01uF K

C473 168-1032-55 0.01uF K

C474 168-1032-55 0.01uF K

C475 042-1505-89 10V10uF(OS)

C476 042-1505-89 10V10uF(OS)

C477 042-1505-89 10V10uF(OS)

C478 042-1505-89 10V10uF(OS)

C479 168-1032-55 0.01uF K

C480 168-1032-55 0.01uF K

C481 042-1547-00 16V22uF

C482 042-1547-00 16V22uF

C483 042-1547-00 16V22uF

C484 042-1547-00 16V22uF

C485 042-1547-00 16V22uF

C486 042-1547-00 16V22uF

C487 042-1563-68 16V22uF

C488 042-1563-68 16V22uF

C489 168-1032-55 0.01uF K

C491 042-1547-00 16V22uF

C492 042-1547-00 16V22uF

C493 168-1032-55 0.01uF K

C600 168-1032-55 0.01uF K

C601 042-1576-01 5.5V0.22uF

C603 168-1032-55 0.01uF K

C605 042-1577-00 6.3V100uF

C609 168-4732-78 0.047uF K

C612 163-1063-35 16V10uF

C615 168-1032-55 0.01uF K

C900 168-1032-55 0.01uF K

Page 17

REF No. PART No. DESCRIPTION REF No. PART No. DESCRIPTION REF No. PART No. DESCRIPTION

C901 168-1042-78 16V 0.1uF

C902 042-0423-20 10V10uF

C903 042-0423-20 10V10uF

C904 168-1042-78 16V 0.1uF

C905 166-8096-50 8pF D CH

C906 166-8096-50 8pF D CH

C908 168-1042-78 16V 0.1uF

C909 168-1042-78 16V 0.1uF

C910 163-1063-35 16V10uF

C911 168-1042-78 16V 0.1uF

C912 168-1042-78 16V 0.1uF

C913 168-1042-78 16V 0.1uF

C914 168-1022-55 1000pF K

C915 042-0423-94 10V 4.7uF

C916 168-1042-78 16V 0.1uF

C917 163-1063-35 16V10uF

C918 168-1042-78 16V 0.1uF

C919 042-0423-20 10V10uF

C920 042-0423-97 16V10uF

C921 042-0423-20 10V10uF

C922 168-1042-78 16V 0.1uF

C923 168-1042-78 16V 0.1uF

C924 042-0423-20 10V10uF

C925 168-1042-78 16V 0.1uF

C926 168-1042-78 16V 0.1uF

C927 168-1042-78 16V 0.1uF

C928 166-1011-50 100pF CH

C929 168-6822-55 6800pF K

C930 168-1042-78 16V 0.1uF

C931 042-0423-20 10V10uF

C932 042-0423-20 10V10uF

C933 168-1042-78 16V 0.1uF

C934 168-1042-78 16V 0.1uF

C935 042-0423-20 10V10uF

C936 168-1032-55 0.01uF K

C937 168-1022-55 1000pF K

C938 178-4742-78 0.47uF

C939 168-1042-78 16V 0.1uF

C940 168-1022-55 1000pF K

C941 042-0423-20 10V10uF

C942 168-1042-78 16V 0.1uF

C943 168-1032-55 0.01uF K

C944 168-1032-55 0.01uF K

C945 042-0423-20 10V10uF

C946 168-1042-78 16V 0.1uF

C947 168-1042-78 16V 0.1uF

C948 168-1042-78 16V 0.1uF

C949 042-0632-50 6.3V47uF

C950 042-0632-50 6.3V47uF

C951 042-0632-50 6.3V47uF

C952 168-1042-78 16V 0.1uF

C953 168-1042-78 16V 0.1uF

C954 168-1042-78 16V 0.1uF

C955 168-1042-78 16V 0.1uF

C956 168-1042-78 16V 0.1uF

C957 168-1042-78 16V 0.1uF

C958 042-0632-50 6.3V47uF

C959 042-0632-50 6.3V47uF

C960 042-0632-50 6.3V47uF

C961 168-1032-55 0.01uF K

C962 042-0592-58 16V10uF

C963 042-0423-97 16V10uF

C964 042-0592-58 16V10uF

C965 042-0592-58 16V10uF

C966 042-0423-97 16V10uF

C967 042-0592-58 16V10uF

C968 042-0592-58 16V10uF

C969 042-0423-97 16V10uF

C970 042-0592-58 16V10uF

C975 166-1011-50 100pF CH

(PE2628BA)

C977 166-1011-50 100pF CH

C978 168-1032-55 0.01uF K

C979 166-1011-50 100pF CH

C980 168-1022-55 1000pF K

C981 168-1022-55 1000pF K

C982 168-1032-55 0.01uF K

C983 166-2211-50 220pF CH

(PE2628BA)

C984 168-1032-55 0.01uF K

C986 168-1022-55 1000pF K

C987 168-1032-55 0.01uF K

C988 168-1032-55 0.01uF K

C989 168-1032-55 0.01uF K

C9005 168-1032-55 0.01uF K

C9006 168-1032-55 0.01uF K

CCT901 010-3042-54 BLA3216A601

SG4T1

CCT902 010-3042-54 BLA3216A601

SG4T1

CCT903 010-3042-54 BLA3216A601

SG4T1

CCT904 010-3042-54 BLA3216A601

SG4T1

CCT905 010-3042-54 BLA3216A601

SG4T1

CCT906 010-3042-54 BLA3216A601

SG4T1

CCT907 010-3042-54 BLA3216A601

SG4T1

D201 001-0529-68 MA8180-L

D202 001-0516-90 MA111

D203 001-0516-90 MA111

D205 001-0516-90 MA111

D206 001-0516-90 MA111

D207 001-0516-90 MA111

D208 001-0516-90 MA111

D209 001-0466-91 S5688G

D210 001-0466-91 S5688G

D215 001-0529-32 MA8056-M

D219 001-0529-14 MA8030-L

D301 001-0516-90 MA111

D302 001-0516-90 MA111

D303 001-0516-90 MA111

D311 001-0529-44 MA8082-M

D350 001-0516-90 MA111

D351 001-0516-90 MA111

D352 001-0516-90 MA111

D353 001-0516-90 MA111

D450 001-0529-38 MA8068-M

D451 001-0516-90 MA111

D452 001-0529-38 MA8068-M

D453 001-0516-90 MA111

D454 001-0529-38 MA8068-M

D455 001-0516-90 MA111

D456 001-0529-38 MA8068-M

D600 001-0516-90 MA111

D601 001-0516-90 MA111

D602 001-0516-90 MA111

D603 001-0529-32 MA8056-M

D604 001-0529-32 MA8056-M

D901 001-0516-90 MA111

D902 001-0516-90 MA111

D903 001-0535-90 MA729

D904 001-0535-90 MA729

D905 001-0535-90 MA729

D906 001-0535-90 MA729

D907 001-0535-90 MA729

D908 001-0535-90 MA729

D909 001-0535-90 MA729

D910 001-0535-90 MA729

FIL901 060-3110-90 NFM4516P13C204

FBI

FIL902 060-3110-90 NFM4516P13C204

FBI

FIL903 060-3110-90 NFM4516P13C204

FBI

FIL904 060-3110-90 NFM4516P13C204

FBI

IC1 051-6212-08 LC72191JM-TLM

IC200 051-3297-10 BA4916-V2

IC301 051-3026-90 NJM4580V

IC302 051-3026-90 NJM4580V

IC303 051-5020-90 M61508FP

- 17 -

IC304 051-3034-90 NJM4558V

IC305 051-7232-08 74VHC4066M

IC306 051-3026-90 NJM4580V

IC307 051-3026-90 NJM4580V

IC401 051-3042-90 OPA2134UA

IC402 051-3042-90 OPA2134UA

IC403 051-3042-90 OPA2134UA

IC404 051-3042-90 OPA2134UA

IC405 051-3042-90 OPA2134UA

IC406 051-3042-90 OPA2134UA

IC407 051-3042-90 OPA2134UA

IC408 051-3042-90 OPA2134UA

IC409 051-3042-90 OPA2134UA

IC410 051-3012-90 OP275GS

IC418 051-5036-90 PGA2310UA

IC419 051-5036-90 PGA2310UA

IC420 051-5036-90 PGA2310UA

IC421 051-5036-90 PGA2310UA

IC600 052-3393-00 M30622MEP-161GP

IC601 051-5437-08 S-80821ANMP-EDJ-

E2

IC602 051-6600-58 HA12187FP

IC901 051-7221-58 SN74AHC1G04

HDCKR

IC902 051-7243-48 SN74AHCT1G08

DCKR

IC903 051-6373-18 AK4112BVF-E2

IC905 051-7221-58 SN74AHC1G04

HDCKR

IC906 051-7269-08 SN74AHC2G53

HDCTR

IC907 051-7285-08 CD74HC4050PWR

IC909 051-6709-90 PCM1792DBR

IC910 051-6709-90 PCM1792DBR

IC911 051-6709-90 PCM1792DBR

IC912 051-6620-08 TC9246F

IC913 051-6705-00 AK7720A

IC915 051-6708-90 AK4121VF-E2

IC916 051-9126-00 BS62LV1024STI-70

IC918 051-3232-90 uPC29M33T

J200 074-1023-16 16P

J401 074-1106-08 8P

J402 074-1106-12 12P

J600 074-1194-00 13P CE-NET

J602 074-1138-76 26P

J901 075-0385-10 OPT JACK

JW1 119-0000-05 1/10W 0 ohm JW

JW2 119-0000-05 1/10W 0 ohm JW

JW3 119-0000-05 1/10W 0 ohm JW

L1 010-2275-53 220uH

L2 010-3103-64 MMZ1608Y1

L3 010-3103-64 MMZ1608Y1

L4 010-3406-54 2.2uH

L5 010-3406-54 2.2uH

L52 010-4046-00 30uH

L230 119-0000-05 1/10W 0 ohm JW

(PE2629BA)

L230 010-3103-64 MMZ1608Y1

(PE2629KA)

L301 010-3406-66 22uH

L302 010-3406-66 22uH

L310 010-3103-64 MMZ1608Y1

L311 010-3103-64 MMZ1608Y1

L490 010-2326-00 BL02RN2-R62

L601 010-3406-54 2.2uH

L902 010-3103-64 MMZ1608Y1

L903 010-3103-64 MMZ1608Y1

L904 010-3103-64 MMZ1608Y1

L905 010-3103-64 MMZ1608Y1

L906 010-3103-64 MMZ1608Y1

L907 010-3103-64 MMZ1608Y1

L908 010-3103-64 MMZ1608Y1

L910 010-3103-64 MMZ1608Y1

L911 010-3406-62 10uH

L913 010-3103-64 MMZ1608Y1

L914 010-3103-64 MMZ1608Y1

L915 010-3103-64 MMZ1608Y1

DRZ9255

HX-D2

Page 18

REF No. PART No. DESCRIPTION REF No. PART No. DESCRIPTION REF No. PART No. DESCRIPTION

L916 010-3406-66 22uH

L917 010-2285-58 BLM21A102FPB

L918 010-3103-64 MMZ1608Y1

L919 010-3103-64 MMZ1608Y1

L920 010-3103-64 MMZ1608Y1

L921 010-3103-64 MMZ1608Y1

L922 010-3103-64 MMZ1608Y1

L923 010-3103-64 MMZ1608Y1

L924 010-3103-64 MMZ1608Y1

L925 010-3103-64 MMZ1608Y1

L926 010-3103-64 MMZ1608Y1

L927 010-3103-64 MMZ1608Y1

L928 010-3103-64 MMZ1608Y1

L929 010-3103-64 MMZ1608Y1

L930 010-3103-64 MMZ1608Y1

L931 010-3103-64 MMZ1608Y1

L932 010-3103-64 MMZ1608Y1

L933 010-3103-64 MMZ1608Y1

L934 010-3103-64 MMZ1608Y1

L935 010-3103-64 MMZ1608Y1

L936 010-3103-64 MMZ1608Y1

L937 010-3103-64 MMZ1608Y1

L938 010-3103-64 MMZ1608Y1

L939 010-3103-64 MMZ1608Y1

L940 010-3103-64 MMZ1608Y1

L941 010-3103-64 MMZ1608Y1

L942 010-3103-64 MMZ1608Y1

L946 010-3103-64 MMZ1608Y1

L947 010-3103-64 MMZ1608Y1

L948 010-3103-64 MMZ1608Y1

L949 010-3103-64 MMZ1608Y1

L950 010-3103-64 MMZ1608Y1

L951 010-3103-64 MMZ1608Y1

L952 010-3103-64 MMZ1608Y1

L953 010-3103-64 MMZ1608Y1

L954 010-3103-64 MMZ1608Y1

L955 010-3103-64 MMZ1608Y1

L956 010-3103-64 MMZ1608Y1

L957 010-3103-64 MMZ1608Y1

L958 010-3103-64 MMZ1608Y1

L959 010-3103-64 MMZ1608Y1

L960 010-3103-64 MMZ1608Y1

L961 010-3103-64 MMZ1608Y1

L962 010-3103-64 MMZ1608Y1

L963 010-3103-64 MMZ1608Y1

L964 010-3103-64 MMZ1608Y1

L965 010-3103-64 MMZ1608Y1

L966 010-3103-64 MMZ1608Y1

P1 076-0515-22 22P

P401 076-0515-08 8P

P402 076-0515-12 12P

P501 076-6002-12 PLUG

Q1 192-2712-51 2SC2712G,L

Q2 192-2712-51 2SC2712G,L

Q3 193-1858-00 2SD1858

Q4 125-2004-93 RN1403

Q5 190-1162-00 2SA1162

Q6 190-1162-00 2SA1162

Q7 190-1162-00 2SA1162

Q201 125-2004-96 RN1406

Q202 190-1298-00 2SA1298

Q203 192-2712-00 2SC2712

Q204 190-1162-00 2SA1162

Q205 190-1162-00 2SA1162

Q207 192-2712-00 2SC2712

Q215 103-2012-00 2SD2012

Q216 125-2004-93 RN1403

Q217 191-1237-00 2SB1237

Q218 125-2004-93 RN1403

Q219 191-1237-00 2SB1237

Q220 125-2004-93 RN1403

Q230 191-1237-50 2SB1237QR

Q234 125-0002-92 RN2402

Q235 193-1802-60 2SD1802FA-R.S.T

Q236 125-2004-92 RN1402

Q238 125-0013-97 RN2427

Q239 125-2004-92 RN1402

DRZ9255

HX-D2

Q240 125-2004-96 RN1406

Q300 125-2004-93 RN1403

Q301 125-2004-96 RN1406

Q302 192-2712-00 2SC2712

Q303 125-2004-92 RN1402

Q413 193-1328-00 2SD1328

Q414 193-1328-00 2SD1328

Q415 193-1328-00 2SD1328

Q416 193-1328-00 2SD1328

Q417 193-1328-00 2SD1328

Q418 125-0002-92 RN2402

Q419 193-1328-00 2SD1328

Q420 125-0002-92 RN2402

Q421 193-1328-00 2SD1328

Q422 193-1328-00 2SD1328

Q600 125-2004-92 RN1402

Q601 125-2004-93 RN1403

Q602 125-2004-93 RN1403

Q603 190-1162-00 2SA1162

Q604 125-0002-92 RN2402

Q605 125-2004-93 RN1403

Q606 125-2004-93 RN1403

Q901 125-2004-92 RN1402

Q902 125-2004-93 RN1403

Q903 125-2004-92 RN1402

Q904 125-2004-92 RN1402

R1 119-1021-15 1/10W 1k ohm

R2 119-3311-15 1/10W 330 ohm

R3 119-4721-15 1/10W 4.7k ohm

R4 119-4721-15 1/10W 4.7k ohm

R5 119-1231-15 1/10W 12k ohm

R6 119-1231-15 1/10W 12k ohm

R7 119-1231-15 1/10W 12k ohm

R9 119-4741-15 1/10W 470k ohm

R10 119-2221-15 1/10W 2.2k ohm

R14 119-5631-15 1/10W 56k ohm

R15 119-1031-15 1/10W 10k ohm

R16 119-2221-15 1/10W 2.2k ohm

R17 119-1521-15 1/10W 1.5k ohm

R18 119-1031-15 1/10W 10k ohm

R19 119-1031-15 1/10W 10k ohm

R20 119-1031-15 1/10W 10k ohm

R21 119-1021-15 1/10W 1k ohm

R24 119-1521-15 1/10W 1.5k ohm

R25 119-1521-15 1/10W 1.5k ohm

R27 119-1021-15 1/10W 1k ohm

R28 119-1021-15 1/10W 1k ohm

R29 119-1021-15 1/10W 1k ohm

R30 119-1041-15 1/10W 100k ohm

R83 119-1021-15 1/10W 1k ohm

R200 119-1041-15 1/10W 100k ohm

R201 119-1041-15 1/10W 100k ohm

R202 119-5621-15 1/10W 5.6k ohm

R203 119-4731-15 1/10W 47k ohm

R204 119-5631-15 1/10W 56k ohm

R205 119-1031-15 1/10W 10k ohm

R206 119-1031-15 1/10W 10k ohm

R207 119-1021-15 1/10W 1k ohm

R209 119-1531-15 1/10W 15k ohm

R210 119-1031-15 1/10W 10k ohm

R211 119-4731-15 1/10W 47k ohm

R212 119-4721-15 1/10W 4.7k ohm

R213 119-2221-15 1/10W 2.2k ohm

R216 119-1021-15 1/10W 1k ohm

R217 119-2231-15 1/10W 22k ohm

R224 119-4701-15 1/10W 47 ohm

R225 119-1031-15 1/10W 10k ohm

R226 116-1221-15 1/4W 1.2k ohm

R227 119-1031-15 1/10W 10k ohm

R228 116-1221-15 1/4W 1.2k ohm

R229 116-1521-15 1/4W 1.5k ohm

R230 119-2221-15 1/10W 2.2k ohm

R231 116-2211-15 1/4W 220 ohm

R233 119-1031-15 1/10W 10k ohm

R234 119-1031-15 1/10W 10k ohm

R235 119-2221-15 1/10W 2.2k ohm

R255 116-4701-15 1/4W 47 ohm

- 18 -

R256 116-4701-15 1/4W 47 ohm

R257 116-1221-15 1/4W 1.2k ohm

R301 119-1041-15 1/10W 100k ohm

R302 119-1041-15 1/10W 100k ohm

R303 119-1041-15 1/10W 100k ohm

R304 119-1041-15 1/10W 100k ohm

R305 119-1021-15 1/10W 1k ohm

R306 119-1021-15 1/10W 1k ohm

R307 032-0140-58 1/10W 51k ohm F

R308 032-0140-58 1/10W 51k ohm F

R309 032-0140-58 1/10W 51k ohm F

R310 032-0140-58 1/10W 51k ohm F

R311 032-0140-58 1/10W 51k ohm F

R312 032-0140-58 1/10W 51k ohm F

R313 032-0140-58 1/10W 51k ohm F

R314 032-0140-58 1/10W 51k ohm F

R315 119-1031-15 1/10W 10k ohm

R316 119-1031-15 1/10W 10k ohm

R317 119-1031-15 1/10W 10k ohm

R318 119-1031-15 1/10W 10k ohm

R319 119-1031-15 1/10W 10k ohm

R320 119-1031-15 1/10W 10k ohm

R321 119-1031-15 1/10W 10k ohm

R322 119-1031-15 1/10W 10k ohm

R323 032-0140-96 1/10W 120k ohm F

R324 032-0140-96 1/10W 120k ohm F

R325 032-0140-96 1/10W 120k ohm F

R326 032-0140-96 1/10W 120k ohm F

R327 119-4721-15 1/10W 4.7k ohm

R328 119-4721-15 1/10W 4.7k ohm