CS49400 Family DSP

Multi-Standard Audio Decoder

Features

CS49300 Legacy Audio Decoder Support

Dolby Digital EXTM, Dolby Pro Logic II

DTS-ES 96/24TM, DTS 96/24TM,DTS-ES

Discrete 6.1TM, DTS-ES Matrix 6.1TM,DTS

Digital Surround

MPEG-2: AAC Multichannel 5.1

MPEG Multichannel and Musicam

MPEG-1/2, Layer III (MP3)

DTS Neo:6TM, LOGIC7®, SRS Circle

Surround II

Cirrus Extra SurroundTM, Cirrus Original

Surround 6.1 (C.O.S. 6.1)

THX Surround EXTM, THX Ultra2 Cinema

12-Channel Serial Audio Inputs

Integrated 8K Byte Input Buffer

Powerful 32-bit Audio DSP

Customer Software Security Keys

Large On-chip X,Y, and Program RAM

Supports SDRAM, SRAM, FLASH

memories

16-channel PCM output

Dual S/PDIF Transmitters

SPI Serial, and Motorola®and Intel®Parallel

Host Control Interfaces

GPIO support for all common sub-circuits

TM

TM

and DTS Virtual 5.1

TM

TM

TM

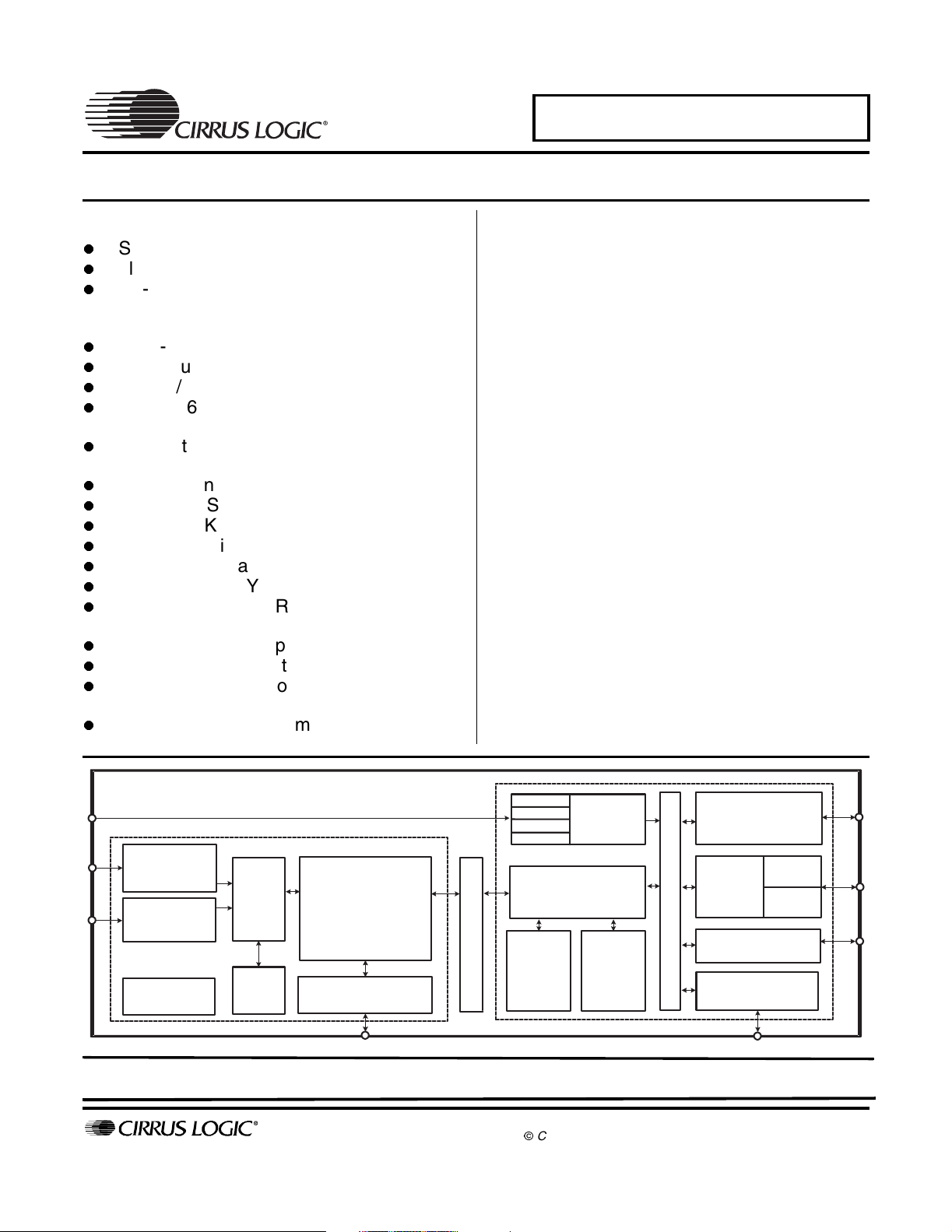

Description

The CS49400 Audio Decoder DSP is targeted as a marketspecific consumer entertainment processor for AV Receivers

and DVD Audio/Video Players. The device is constructed using

an enhanced version of the CS49300 Family DSP audio

decoder followed by a 32-bit programmable post-processor

DSP, which gives the designer the ability to add product

differentiation through the Cirrus Framework

structure and Framework module library. Dolby Digital Pro

Logic II, DTS Digital Surround, MPEG Multichannel, and Cirrus

Original Surround 6.1 PCM Effects Processor (capable of

generating such DSP audio modes as: Hall, Theater, Church)

are included in the cost of the CS49400 Family DSP. Additional

algorithms available through the Crystal Ware

Licensing Program, give the designer the ability to further

TM

deliver end-product differentiation.

The CS49400 contains sufficient on-chip SRAM to support

decoding all major audio decoding algorithms available today

including: AAC Multichannel, DTS 96/24, DTS-ES 96/24. The

CS49400 also supports a glueless SDRAM/SRAM for

increased all-channel delays. The SRAM interface also

supports connection to an external byte-wide EPROM for code

storage or Flash memory thus allowing products to be fieldupgradable as new audio algorithms are developed.

This chip, teamed with Crystal Ware

library, Cirrus digital interface products and mixed signal data

converters, enables the conception and design of next

generation digital entertainment products.

Ordering Information: See page 98

TM

TM

certified decoder

programming

TM

Software

Compressed

Digital

Interface

Digital

Audio

Input

DSP AB

PLL Clock

Manager

Frame

Shifter

Input

Buffer

RAM

Multi-Standard

Audio Decoder

Parallel or Serial

Host Interface

Preliminary Product Information

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

SAI 0

SAI 1

SAI 2

SAI 3

DSP C

Programmable

ared Memory

h

S

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

DSP

RAM

(All Rights Reserved)

Serial

Audio

Interface

32-Bit DSP

DSP

ROM

External Memory

Digital

Audio

Output

Internal Bus

GPIO and I/O

Parallel or Serial

Host Interface

Interface

DAO 0

DAO 1

Controller

DS536PP2

JUL ‘02

1

TABLE OF CONTENTS

1.0 CHARACTERISTICS AND SPECIFICATIONS ...................................................................... 8

1.1 Absolute Maximum Ratings ............................................................................................... 8

1.2 Recommended Operating Conditions ................................................................................ 8

1.3 Digital D.C. Characteristics for VDD Level I/O ................................................................... 8

1.4 Digital D.C. Characteristics for VDDSD Level I/O ..............................................................9

1.5 Power Supply Characteristics ............................................................................................ 9

1.6 Switching Characteristics— RESET .................................................................................. 9

1.7 Switching Characteristics — CLKIN .................................................................................10

1.8 Switching Characteristics — Intel

1.9 Switching Characteristics — Intel

1.10 Switching Characteristics — Motorola

1.11 Switching Characteristics — Motorola

1.12 Switching Characteristics — SPI Control Port Slave Mode (DSPAB) ............................19

1.13 Switching Characteristics — SPI Control Port Slave Mode (DSPC) .............................. 21

1.14 Switching Characteristics — Digital Audio Input (DSPAB) ............................................23

1.15 Switching Characteristics — Serial Audio Input (DSPC) ............................................... 24

1.16 Switching Characteristics — CMPDAT, CMPCLK (DSPAB) ......................................... 25

1.17 Switching Characteristics — Parallel Data Input (DSPAB) ............................................ 26

1.18 Switching Characteristics — Digital Audio Output .........................................................27

1.19 Switching Characteristics — SRAM/FLASH Interface ...................................................29

1.20 Switching Characteristics — SDRAM Interface ............................................................. 31

2. OVERVIEW ............................................................................................................................. 35

®

Host Slave Mode (DSPAB) ......................................11

®

Host Slave Mode (DSPC) ........................................ 13

®

Host Slave Mode (DSPAB) ............................ 15

®

Host Slave Mode (DSPC) ..............................17

Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at:

http://www.cirrus.com/corporate/contacts/sales.cfm

Dolby Digital, Dolby Digital EX, AC-3, Dolby Pro Logic, Dolby Pro Logic II, Dolby Digital EX Pro Logic II, Dolby Surround, Dolby Surround Pro Logic

II, Surround EX, Virtual Dolby Digital and the “AAC” logo are trademarks and the “Dolby” and the double-”D” symbol are registered trademarks of

Dolby Laboratories Licensing Corporation. DTS, DTS Digital Surround, DTS-ES Extended Surround, DTS 96/24, DTS-ES 96/24, DTS Neo:6, and

DTS Virtual 5.1 are trademarks and the “DTS”, “DTS Digital Surround”, “DTS-ES”, “DTS 96/24”, “DTS-ES 96/24”, “DTS Neo:6”, “DTS Virtual 5.1” logos

are registered trademarks of the Digital Theater Systems Corporation. The “MPEG Logo” is a registered trademark of Philips Electronics N.V. THX

Ultra2 Cinema, Timbre-Matching, Re-EQ, Adapative Decorrelation and THX are trademarks or registered trademarks of Lucasfilm, Ltd. Surround EX

is a jointly developed technology of THX and Dolby Labs, Inc. AAC (Advanced Audio Coding) is an “MPEG-2-standard-based” digital audio

compression algorithm (offering up 5.1 discrete decoded channels for this implementation) collaboratively developed by AT&T, the Fraunhofer

Institute, Dolby Laboratories, and the Sony Corporation. In regards to the MP3 capable functionality of the CS494XX Family DSP (via downloading

of mp3_ab_494xxx_vv.uld application code) the following statements are applicable: “Supply of this product conveys a license for persona l, private

and non-commercial use. MPEG Layer-3 audio decoding technology licensed from Fraunhofer IIS and THOMSON Multimedia.” VMAx is a registered

trademark of Harman International. The LO GIC7 logo and LOGIC7 are registered trademarks of Lexicon. SRS CircleSurround, SRS Circle Suround

II, SRS T ruSurround, and SRS TruSurround XT are trademarks of SRS Labs, Inc. The HDCD logo, HDCD, High Definition Compatible Digital and

Pacific Microsonics are either registered trademarks or trademarks of Pacific Microsonics, Inc. in the United States and/or other countries. HDCD

technology provided under license from Pacific Microsonics, Inc. This product’s software is covered by one or more of the following in the United

States: 5,479,168; 5,638,074; 5,640,161; 5,872,531; 5,808,574; 5,838,274; 5,854,600; 5,864,311; and in Australia: 669114; with other patents

pending. Intel is a registered trademark of Intel Corporation. Motorola is a registered trademark of Motorola, Inc. I

Semiconductor. Purchase of I

Philips I2C Patent Rights to use those components in a standard I2Csystem.“Crystal Ware”, “Cirrus Framework”, “Cirrus Extra Surround”, “Cirrus

Triple Crossover Bass Management”, “Cirrus Quadruple Crossover Bass Management” and “Cirrus Original Surround 6.1” are trademarks and “Cirrus

Logic” is a registered trademarks of Cirrus Logic, Inc. All other names are trademarks, registered trademarks, or service marks of their respective

companies.

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance

product information describes products which are in development and subject to develo pment changes. Cirrus Logic, Inc. has made best efforts to

ensure that the information contained in this document is accurate an d reliable. However, the information is subject to change without notice and is

provided “AS IS” without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information,

nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents,

copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any

form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus

Logic website or disk may be printed for use by the user. However, no part of the printout or electronic files may be copied, reproduced, store d in a

retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consentof

Cirrus Logic, Inc.Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent

of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors an d suppliers appearing in this document may be trademarks or

service m arks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can

be found at http://www.cirrus.com.

2

C Components of Cirrus Logic, Inc., or one of its sublicensed Associated Companies conveys a license under the

2

C is a registered trademark of Philips

2

2.1 DSPAB ............................................................................................................................ 36

2.2 DSPC ............................................................................................................................... 36

3. TYPICAL CONNECTION DIAGRAMS ................................................................................... 37

3.1 Multiplexed Pins ..............................................................................................................37

3.2 Termination Requirements .............................................................................................. 37

3.3 Phase Locked Loop Filter ................................................................................................ 37

4. POWER .............................................................................................................................. 38

4.1 Decoupling ....................................................................................................................... 38

4.2 Analog Power Conditioning ............................................................................................. 38

4.3 Ground ............................................................................................................................. 38

4.4 Pads ................................................................................................................................ 38

5. CLOCKING ............................................................................................................................. 42

6. CONTROL .............................................................................................................................. 42

6.1 Serial Communication ..................................................................................................... 42

6.1.1 SPI Communication for DSPAB .......................................................................... 42

6.1.2 SPI Communication for DSPC ............................................................................ 46

6.1.3 FINTREQ Behavior: A Special Case .................................................................. 49

6.2 Parallel Host Communication for DSPAB ........................................................................ 51

6.2.5 Intel Parallel Host Communication Mode for DSPAB ......................................... 51

6.2.6 Motorola Parallel Communication Mode for DSPAB ........................................... 54

6.2.7 Procedures for Parallel Host Mode Communication for DSPAB ......................... 56

6.3 Parallel Host Communication for DSPC .......................................................................... 58

6.3.5 Intel Parallel Host Communication Mode for DSPC ............................................ 60

6.3.6 Motorola Parallel Host Communication Mode for DSPC .................................... 64

6.3.7 Procedures for Parallel Host Mode Communication for DSPC ........................... 68

7. EXTERNAL MEMORY ............................................................................................................ 70

7.1 Configuring SRAM Timing Parameters ........................................................................... 71

8. BOOT PROCEDURE .............................................................................................................. 72

8.1 Host Controlled Master Boot ........................................................................................... 72

8.2 Host Boot Via DSPC ........................................................................................................ 75

9. SOFT RESETTING THE CS49400 ......................................................................................... 77

9.1 Host Controlled Master Soft Reset .................................................................................. 77

10. HARDWARE CONFIGURATION ......................................................................................... 79

11. DIGITAL INPUT AND OUTPUT DATA FORMATS .............................................................. 79

11.1 Digital Audio Formats .................................................................................................... 79

11.1.1 I

2

S ..................................................................................................................... 79

11.1.2 Left Justified ...................................................................................................... 79

11.2 Digital Audio Input Port .................................................................................................. 79

11.3 Compressed Data Input Port ......................................................................................... 80

11.4 Input Data Hardware Configuration for CDI and DAI on DSPAB ................................. 80

11.4.1 Input Configuration Considerations ................................................................ 81

11.5 Serial Audio Input .......................................................................................................... 82

11.6 Digital Audio Output Port ............................................................................................... 82

11.6.1 S/PDIF Outputs ................................................................................................. 83

11.7 Output Data Hardware Configuration ............................................................................ 84

11.8 Creating Hardware Configuration Messages ................................................................. 85

12.0 PIN DESCRIPTION ............................................................................................................. 87

12.1 144-Pin LQFP Package Pin Layout ............................................................................... 87

12.2 100-Pin LQFP Package Pin Layout ............................................................................... 88

12.3 Pin Definitions ................................................................................................................ 89

13. ORDERING INFORMATION ................................................................................................ 99

14. PACKAGE DIMENSIONS .................................................................................................. 100

14.1 144-Pin LQFP Package ............................................................................................... 100

3

LIST OF FIGURES

Figure 1. RESET Timing ..................................................................................................................... 9

Figure 2. CLKIN with CLKSEL = VSS = PLL Enable ........................................................................ 10

Figure 3. Intel

Figure 4. Intel

Figure 5. Intel

Figure 6. Intel

Figure 7. Motorola

Figure 8. Motorola

Figure 9. Motorola

Figure 10. Motorola

Figure 11. SPI Control Port Slave Mode Timing (DSPAB) ............................................................... 20

Figure 12. SPI Control Port Slave Mode Timing (DSPC) ................................................................. 22

Figure 13. Digital Audio Input Data, Slave Clock Timing .................................................................. 23

Figure 14. Serial Audio Input Data, Slave Clock Timing ................................................................... 24

Figure 15. Serial Compressed Data Timing ...................................................................................... 25

Figure 16. Parallel Data Timing ........................................................................................................ 26

Figure 17. Digital Audio Output Data, Input and Output Clock Timing ............................................. 28

Figure 18. Digital Audio Output Data, Input and Output Clock Timing ............................................. 28

Figure 19. SRAM/Flash Controller Timing Diagram - Write Cycle .................................................... 29

Figure 20. SRAM/Flash Controller Timing Diagram - Read Cycle .................................................... 29

Figure 21. SRAM/Flash Controller Timing Diagram - Single Byte Write Cycle ................................. 30

Figure 22. SRAM/Flash Controller Timing Diagram - Single Byte Read Cycle ................................ 30

Figure 23. SDRAM Controller Timing Diagram - Load Mode Register Cycle ................................... 31

Figure 24. SDRAM Controller Timing Diagram - Burst Write Cycle .................................................. 32

Figure 25. SDRAM Controller Timing Diagram - Burst Read Cycle ................................................. 33

Figure 26. SDRAM Controller Timing Diagram - Auto Refresh Cycle .............................................. 34

Figure 27. SPI Control with External Memory - 144 Pin Package .................................................... 39

Figure 28. Intel

Figure 29. Motorola

Figure 30. SPI Write Flow Diagram for DSPAB ................................................................................ 43

Figure 31. SPI Timing for DSPAB ..................................................................................................... 44

Figure 32. SPI Read Flow Diagram for DSPAB ................................................................................ 45

Figure 33. SPI Write Flow Diagram for DSPC .................................................................................. 46

Figure 34. SPI Timing for DSPC .......................................................................................................47

Figure 35. SPI Read Flow Diagram for DSPC .................................................................................. 48

Figure 36. Intel Mode, One-Byte Write Flow Diagram for DSPAB .................................................... 53

Figure 37. Intel Mode, One-Byte Read Flow Diagram for DSPAB ................................................... 54

Figure 38. Motorola Mode, One-Byte Write Flow Diagram for DSPAB ............................................ 55

Figure 39. Motorola Mode, One-Byte Read Flow Diagram for DSPAB ............................................ 55

Figure 40. Typical Parallel Host Mode Control Write Sequence Flow Diagram for DSPAB ............. 56

Figure 41. Typical Parallel Host Mode Control Read Sequence Flow Diagram for DSPAB ............. 57

®

®

®

®

Parallel Host Mode Slave Read Cycle for DSPAB .................................................. 12

Parallel Host Mode Slave Write Cycle for DSPAB ................................................... 12

Parallel Host Slave Mode Read Cycle for DSPC ..................................................... 14

Parallel Host Slave Mode Write Cycle for DSPC ..................................................... 14

®

Parallel Host Slave Mode Read Cycle for DSPAB ........................................... 16

®

Parallel Host Slave Mode Write Cycle for DSPAB ........................................... 16

®

Parallel Host Slave Mode Read Cycle for DSPC ............................................. 18

®

Parallel Host Slave Mode Write Cycle for DSPC ............................................ 18

®

Parallel Control Mode - 144 Pin Package .............................................................. 40

®

Parallel Control Mode - 144 Pin Package ....................................................... 41

4

Figure 42. Intel Mode, One-Byte Write Flow Diagram for DSPC .......................................................60

Figure 44. Intel Mode, One-Byte Read Flow Diagram for DSPC ......................................................61

Figure 43. Intel Mode, 32-bit (4-byte) Write Flow

Diagram for DSPC .............................................................................................................................62

Figure 45. Intel Mode, 32-Bit (4-Byte) Read Flow

Diagram for DSPC .............................................................................................................................63

Figure 46. Motorola Mode, One-Byte Write Flow

Diagram for DSPC .............................................................................................................................64

Figure 47. Motorola Mode, 32-bit (4-byte) Write Flow Diagram for DSPC ........................................65

Figure 48. Motorola Mode, One-Byte Read Flow

Diagram for DSPC .............................................................................................................................66

Figure 49. Motorola Mode, 32-Bit (4-Byte) Read Flow Diagram for DSPC .......................................67

Figure 50. Typical Parallel Host Mode Control Write Sequence Flow Diagram for DSPC ................68

Figure 51. Typical Parallel Host Mode Control Read Sequence Flow Diagram for DSPC ................69

Figure 52. Host Controlled Master Boot

(Downloading both a DSPAB Application Code and a DSPC Application Code) ..............................73

Figure 53. Host Boot Via DSPC .......................................................................................................76

Figure 54. Host Controlled Master Softreset .....................................................................................78

2

Figure 55. I

S Format ........................................................................................................................80

Figure 56. Left Justified Format (Rising Edge Valid SCLK) ...............................................................80

Figure 57. Pin Layout (144-Pin LQFP Package) ...............................................................................87

Figure 58. Pin Layout (100-Pin LQFP Package) ...............................................................................88

Figure 59. 144-Pin LQFP Package Drawing ...................................................................................100

5

LIST OF TABLES

Table 1. PLL Filter Component Values...............................................................................................37

Table 2. Host Modes for DSPAB ........................................................................................................42

Table 3. Host Modes for DSPC ..........................................................................................................42

Table 4. SPI Communication Signals for DSPAB...............................................................................43

Table 5. SPI Communication Signals for DSPC .................................................................................46

Table 6. Intel Mode Communication Signals for DSPAB.................................................................... 51

Table 6. Parallel Input/Output Registers for DSPAB ..........................................................................52

Table 7. Motorola Mode Communication Signals for DSPAB.............................................................54

Table 8. Parallel Input/Output Registers for DSPC.............................................................................59

Table 9. Intel Mode Communication Signals for DSPC ......................................................................60

Table 10. Motorola Mode Communication Signals for DSPC .............................................................64

Table 11. SRAM Interface Pins .......................................................................................................... 70

Table 12. SDRAM Interface Pins ........................................................................................................70

Table 13. SRAM Controller Timing .....................................................................................................71

Table 14. SDRAM Config Register .....................................................................................................71

Table 15. Application Messages from DSPAB ...................................................................................72

Table 16. Boot Write Messages for DSPC .........................................................................................72

Table 17. Boot Read Messages from DSPC ......................................................................................72

Table 18. Digital Audio Input Port.......................................................................................................80

Table 19. Compressed Data Input Port ..............................................................................................80

Table 20. Input Data Type Configuration

(Input Parameter A).............................................................................................................81

Table 21. Input Data Format Configuration

(Input Parameter B).............................................................................................................81

Table 22. Input SCLK Polarity Configuration

(Input Parameter C) ............................................................................................................81

Table 23. Serial Audio Input Port ........................................................................................................82

Table 24. SAI Data Type Configuration

(Input Parameter D) ............................................................................................................82

Table 25. Digital Audio Output Port ....................................................................................................82

Table 26. MCLK/SCLK Master Mode Ratios ......................................................................................83

Table 27. Output Clock Configuration

(Parameter A)......................................................................................................................84

Table 28. Output Data Configuration Parameter B)...........................................................................84

Table 29. Output SCLK/LRCLK Configuration

(Parameter C) ..................................................................................................................... 84

Table 30. Output SCLK Polarity Configuration

(Parameter D) ..................................................................................................................... 85

Table 31. Example Values to be Sent to DSPAB After Download or Soft Reset................................86

Table 32. Example Values to be Sent to DSPC After Download or Soft Reset..................................86

6

1.0 CHARACTERISTICS AND SPECIFICATIONS

Note: All data sheet minimum and maximum timing parameters are guaranteed over the rated voltage and

temperature. Actual production testing is performed at T

=25°C with an appropriate guardband to

A

guarantee minimum and maximum timing specifications over rated voltage and temperature.

1.1 Absolute Maximum Ratings

(VSS, VSSSD, PLLVSS = 0 V; all voltages with respect to 0 V)

Parameter Symbol Min Max Unit

DC power supplies: Core supply

PLL supply

Memory supply

||PLLVDD| – |VDD||

Input current, any pin except supplies I

Digital input voltage on I/O pins powered from VDD V

Digital input voltage on I/O pins powered from VDDSD V

Storage temperature T

VDD

PLLVSS

VDDSD

in

ind

insd

stg

–0.3

–0.3

–0.3

-

2.7

2.7

3.6

0.3

V

V

V

V

- ±10 mA

-3.6V

-3.6V

–65 150 °C

Caution: Operation at or beyond these limits may result in permanent damage to the device. Normal operation

is not guaranteed at these extremes.

1.2 Recommended Operating Conditions

(VSS, VSSSD, PLLVSS = 0 V; all voltages with respect to 0 V)

Parameter Symbol Min Typ Max Unit

DC power supplies: Core supply

PLL supply

Memory supply

VDD

PLLVSS

VDDSD

||PLLVDD| – |VDD||

Ambient operating temperature T

A

1.3 Digital D.C. Characteristics for VDD Level I/O

(TA=25°C;VDD = 2.5 V; measurements performed under static conditions.)

Parameter Symbol Min Typ Max Unit

High-level input voltage V

Low-level input voltage V

High-level output voltage at I

Low-level output voltage at I

= –2.0 mA V

O

=2.0mA V

O

Input leakage current (all pins without internal pullup resistors except CLKIN)

Input leakage current (pins with internal pull-up

resistors, CLKIN)

OH

I

IH

IL

OL

in

2.0 - - V

--0.8V

VDD × 0.9 - - V

--VDD× 0.1 V

--10µA

2.37

2.37

3.15

2.5

2.5

3.3

2.63

2.63

3.45

0.3

0-70°C

50 µA

V

V

V

V

7

1.4 Digital D.C. Characteristics for VDDSD Level I/O

(TA=25°C;VDDSD = 3.3 V±; measurements performed under static conditions.)

Parameter Symbol Min Typ Max Unit

High-level input voltage V

Low-level input voltage V

High-level output voltage at I

Low-level output voltage at I

= –2.0 mA V

O

=2.0mA V

O

Input leakage current (except all pins with internal pull-

I

IH

IL

OH

OL

in

0.65xVDDSD V

0.35xVDDSD V

0.9xVDDSD V

0.1xVDDSD V

10 µA

up)

Input leakage current (all pins with internal pull-up) 50 µA

1.5 Power Supply Characteristics

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V;measurements performed under operating conditions)

Parameter Symbol Min Typ Max Unit

Power supply current: Core and I/O operating: VSS

PLL operating: PLLVSS

Memory operating: VSSSD

400

6

25

mA

mA

mA

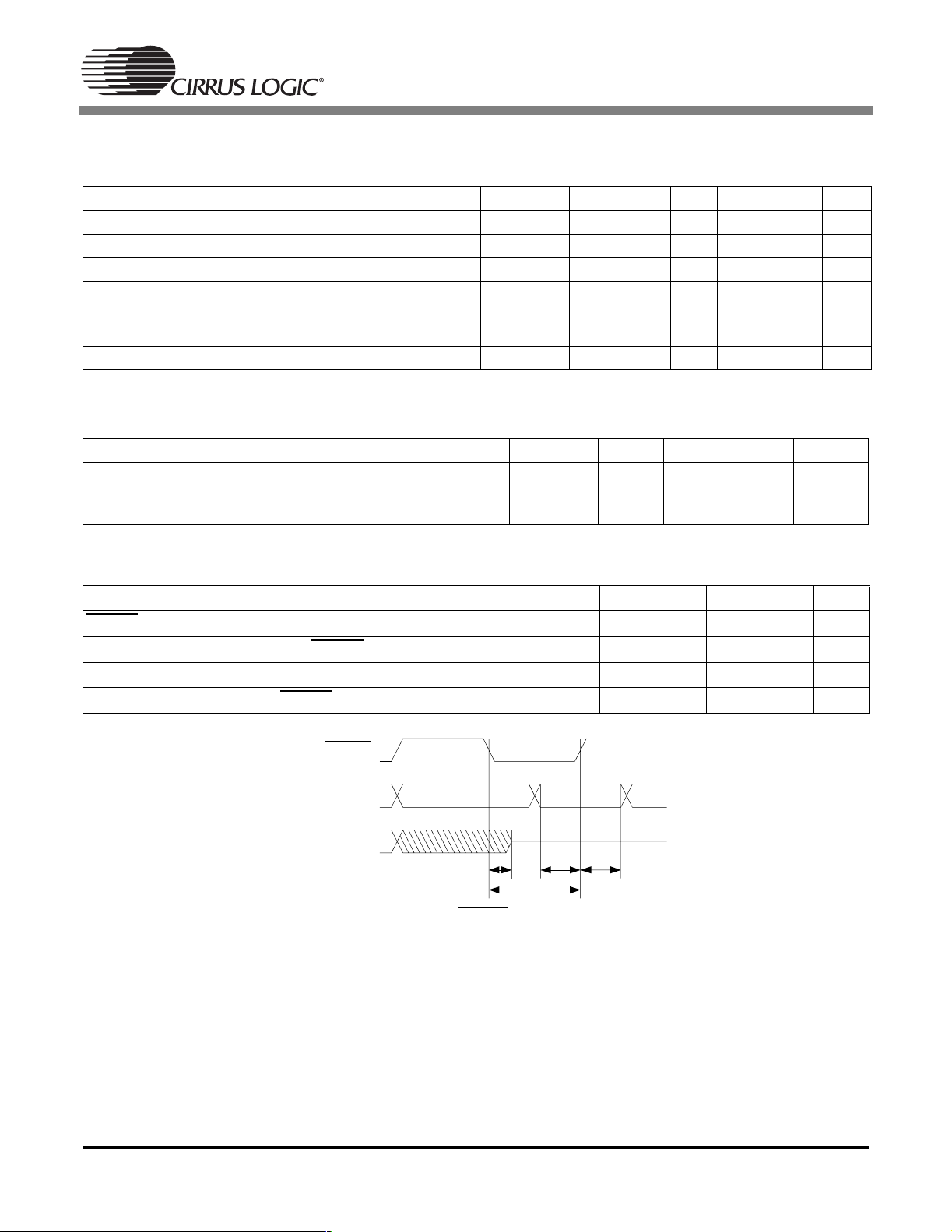

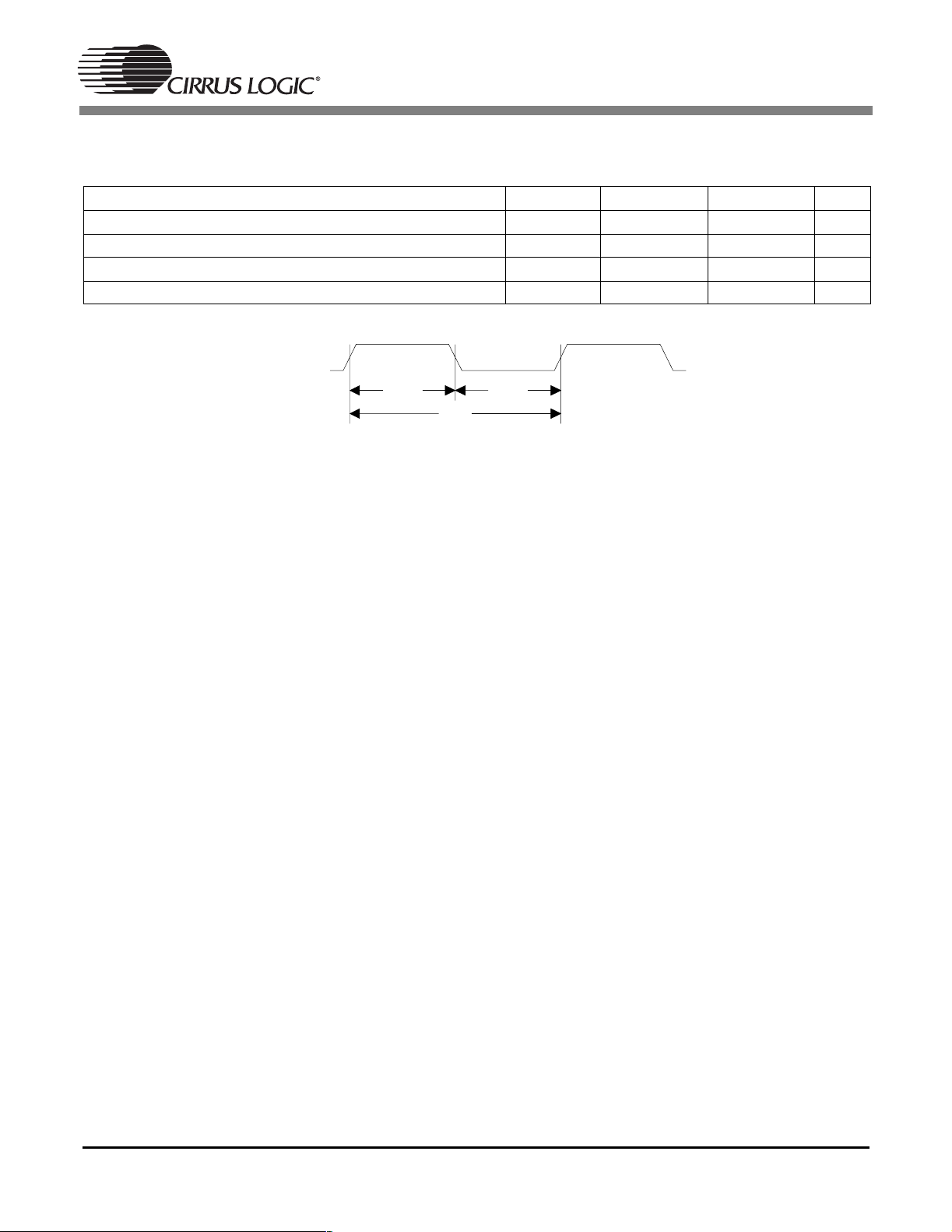

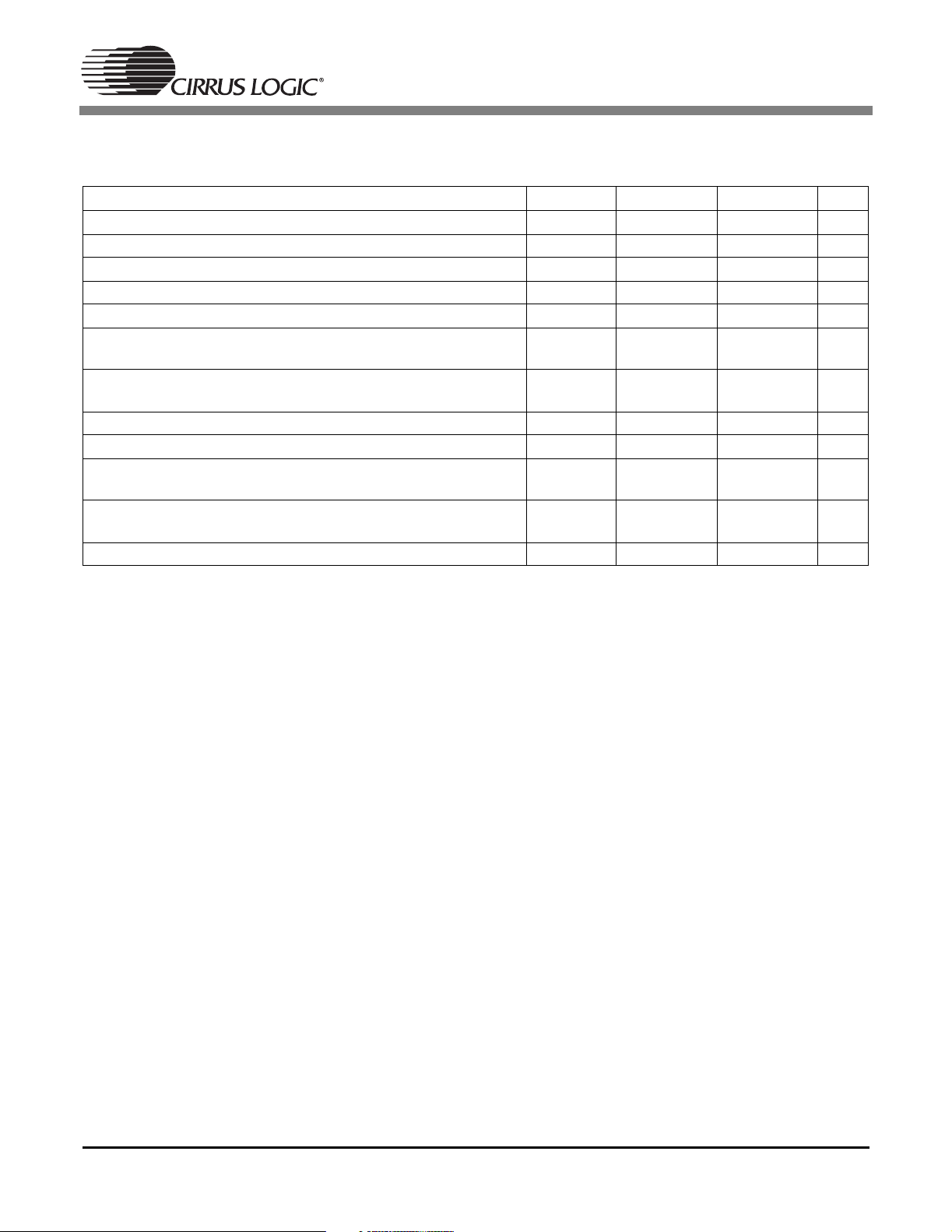

1.6 Switching Characteristics— RESET

(TA=25°C; VDD, PLLVDD= 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

RESET

minimum pulse width low

All bidirectional pins high-Z after RESET

Configuration bits setup before RESET

Configuration bits hold after RESET

All Bidirectional

high

RESET

FHS0,1,2

UHS0,1,2

Pins

low

high

T

rst2z

T

rstl

Figure 1. RESET Timing

T

rstl

T

rst2z

T

rstsu

T

rsthld

T

rstsuTrsthld

10 - µs

50 ns

50 - ns

15 - ns

8

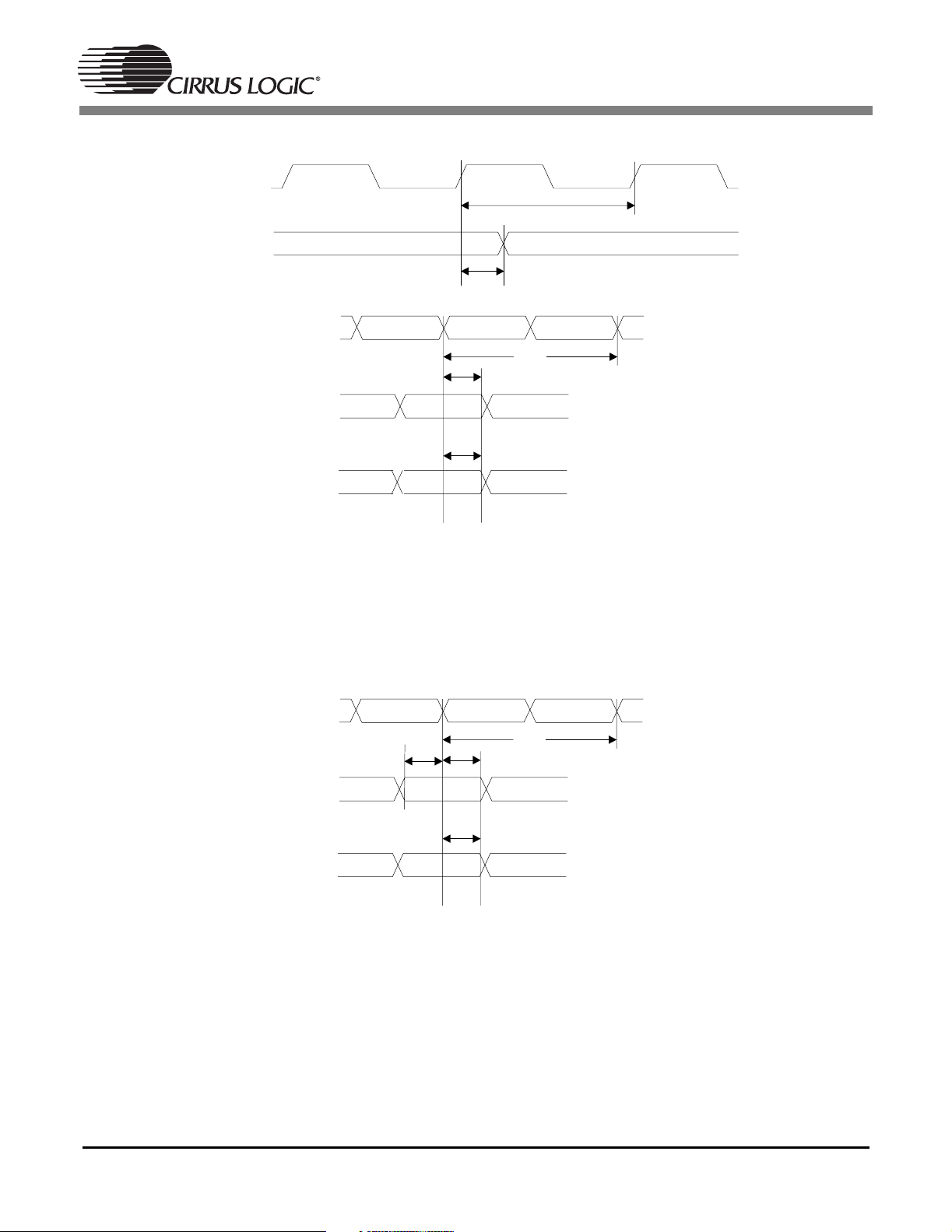

1.7 Switching Characteristics — CLKIN

(TA=25°C; VDD, PLLVDD = 2.5; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

CLKIN period for internal DSP clock mode T

CLKIN high time for internal DSP clock mode T

CLKIN low time for internal DSP clock mode T

External Crystal operating frequency F

CLKIN

clki

clkih

clkil

xtal

35 100 ns

18 ns

18 ns

10 14 MHz

T

clkih

T

clki

T

clkil

Figure 2. CLKIN with CLKSEL = VSS = PLL Enable

9

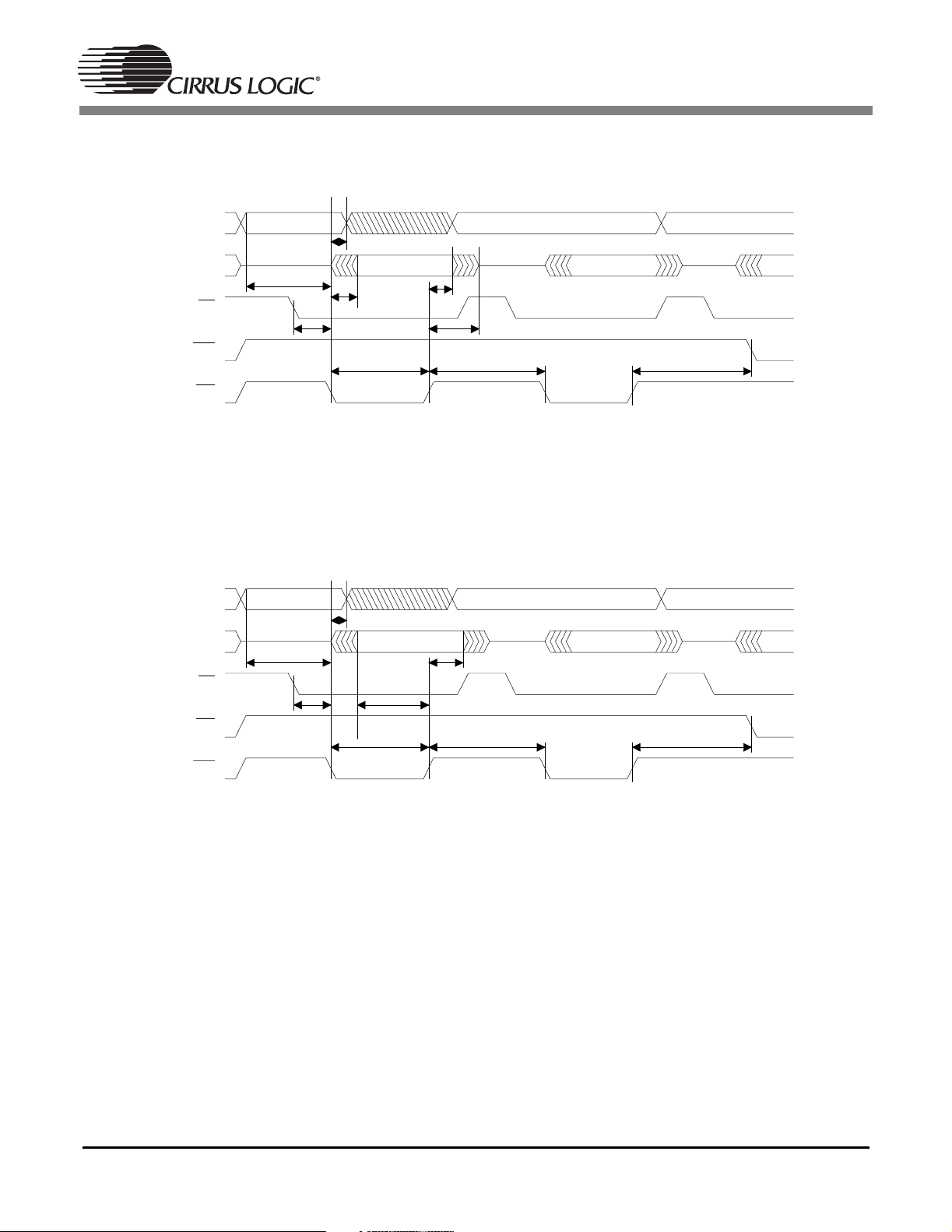

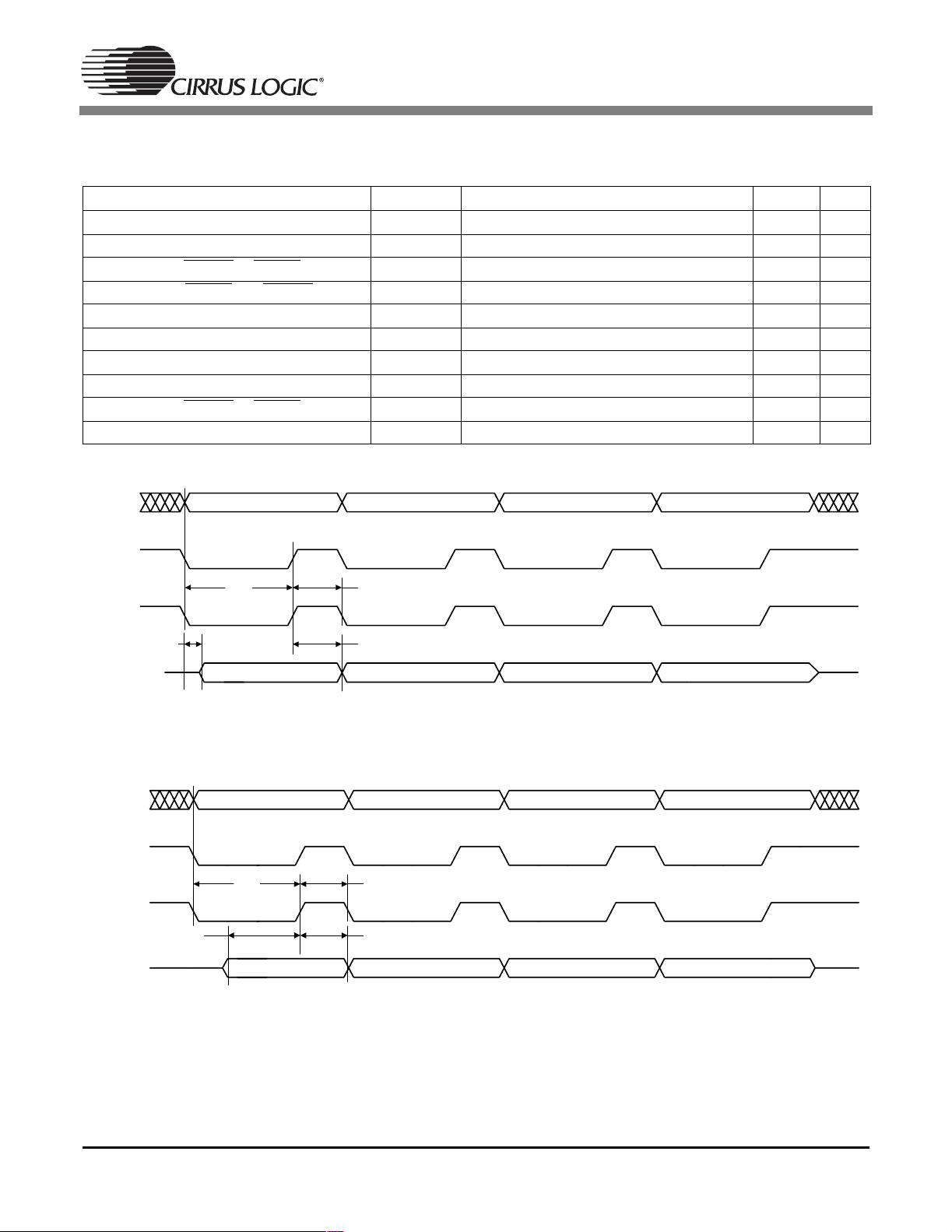

1.8 Switching Characteristics — Intel®Host Slave Mode (DSPAB)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

Address setup before FCS and FRD low or FCS and FWR low

Address hold time after FCS

and FRD low or FCS and FWR

T

ias

T

iah

high

Read

Delay between FRD then FCS low or FCS then FRD low

Data valid after FCS

FCS

and FRD low for read (Note 1)

Data hold time after FCS

Data high-Z after FCS

FCS

or FRD high to FCS and FRD low for next read (Note 1)

FCS

or FRD high to FCS and FWR low for next write (Note 1)

and FRD low T

or FRD high

or FRD high

T

T

T

T

T

icdr

idd

irpw

idhr

idis

T

ird

irdtw

Write

Delay between FWR then FCS low or FCS then FWR low

Data setup before FCS

FCS

and FWR low for write (Note 1)

Data hold after FCS

FCS

or FWR high to FCS and FRD low for next read (Note 1)

FCS

or FWR high to FCS and FWR low for next write (Note 1)

or FWR high

or FWR high

T

T

T

T

T

T

icdw

idsu

iwpw

idhw

iwtrd

iwd

Notes: 1. Certain timing parameters are normalized to the DSP clock period, DCLKP. DCLKP = 1/DCLK. The

DSP clock can be defined as follows:

5-ns

5-ns

0-ns

-21ns

DCLKP + 10 - ns

5-ns

-22ns

2*DCLKP + 10 - ns

2*DCLKP + 10 - ns

0-ns

20 - ns

DCLKP + 10 - ns

5-ns

2*DCLKP + 10 - ns

2*DCLKP + 10 - ns

10

Internal Clock Mode:

DCLK ~ 60MHz before and during boot, i.e. DCLKP ~ 16.6ns

DCLK ~ 86 MHz after boot, i.e. DCLKP ~ 11.6ns

It should be noted that DCLK for the internal clock mode is application specific. The application code

users guide should be checked to confirm DCLK for the particular application.

A1:0F

DATA7:0

F

F

F

F

A1:0F

CS

WR

RD

T

ia h

T

ias

T

icdr

T

idd

idhr

T

idis

T

irpw

T

ird

T

Figure 3. Intel®Parallel Host Mode Slave Read Cycle for DSPAB

T

ird tw

F

DATA7:0

F

F

F

WR

CS

RD

T

iah

T

ias

T

icdw

T

iwpw

T

id hw

T

idsu

T

iw d

T

iwtrd

Figure 4. Intel®Parallel Host Mode Slave Write Cycle for DSPAB

11

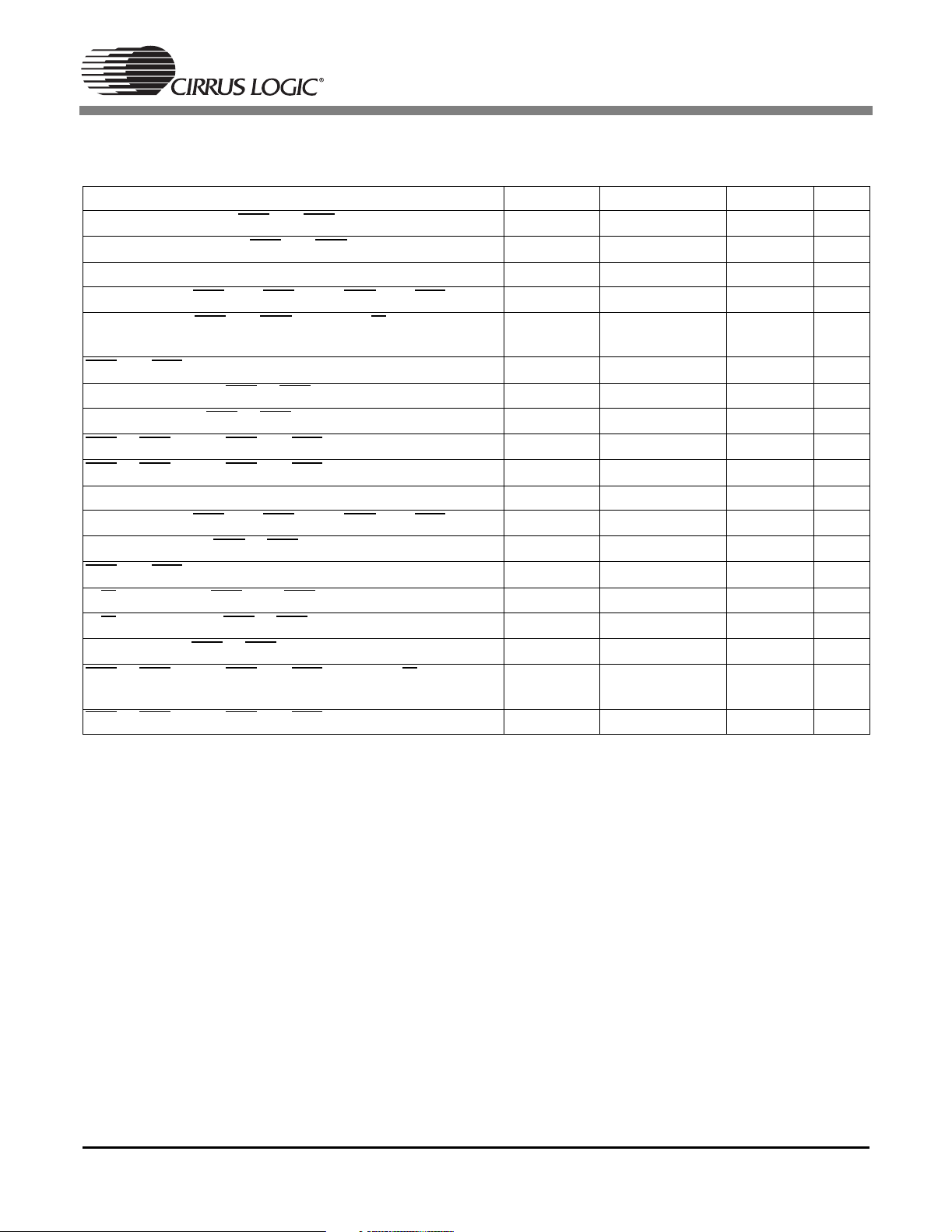

1.9 Switching Characteristics — Intel®Host Slave Mode (DSPC)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

Address setup before CS and RD low or CS and WR low

Address hold time after CS

and RD low or CS and WR low

Read

Delay between RD then CS low or CS then RD low

Data valid after CS

and RD low

T

ias

T

iah

T

icdr

T

idd

DCLKP+15 - ns

DCLKP - ns

0-ns

- 2*DCLKP+25ns

and RD low for read (Note 1)

CS

Data hold time after CS

Data high-Z after CS

CS

or RD high to CS and RD low for next read (Note 1)

CS

or RD high to CS and WR low for next write (Note 1)

or RD high

or RD high

T

T

T

T

irpw

idhr

idis

T

ird

irdtw

2*DCLKP - ns

DCLKP+10 - ns

- 2*DCLKP+10ns

2*DCLKP+10 - ns

2*DCLKP+10 - ns

Write

Delay between WR then CS low or CS then WR low

Data setup before CS

CS

and WR low for write (Note 1)

Data hold after CS

CS

or WR high to CS and RD low for next read (Note 1)

CS

or WR high to CS and WR low for next write (Note 1)

or WR high

or WR high

T

T

T

T

T

T

icdw

idsu

iwpw

idhw

iwtrd

iwd

0-ns

2*DCLKP+10 - ns

2*DCLKP - ns

DCLKP - ns

2*DCLKP+10 - ns

2*DCLKP+10 - ns

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP =

1/DCLK. The DSP clock can be defined as follows:

Internal Clock Mode:

DCLK ~ 60MHz before and during boot, i.e. DCLKP ~ 16.6ns

DCLK ~ 86 MHz after boot, i.e. DCLKP ~ 11.6ns

12

It should be noted that DCLK for the internal clock mode is application specific. The application code

users guide should be checked to confirm DCLK for the particular application.

A1:0

DATA7:0

CS

WR

RD

A1:0

DATA7:0

CS

RD

T

iah

T

ias

T

icdr

T

idhr

T

idd

T

idis

T

irpw

T

ird

Figure 5. Intel®Parallel Host Slave Mode Read Cycle for DSPC

T

iah

T

ias

T

icdw

T

iwpw

T

idhw

T

idsu

T

iwd

T

irdtw

T

iwtrd

WR

Figure 6. Intel®ParallelHostSlaveModeWriteCycleforDSPC

13

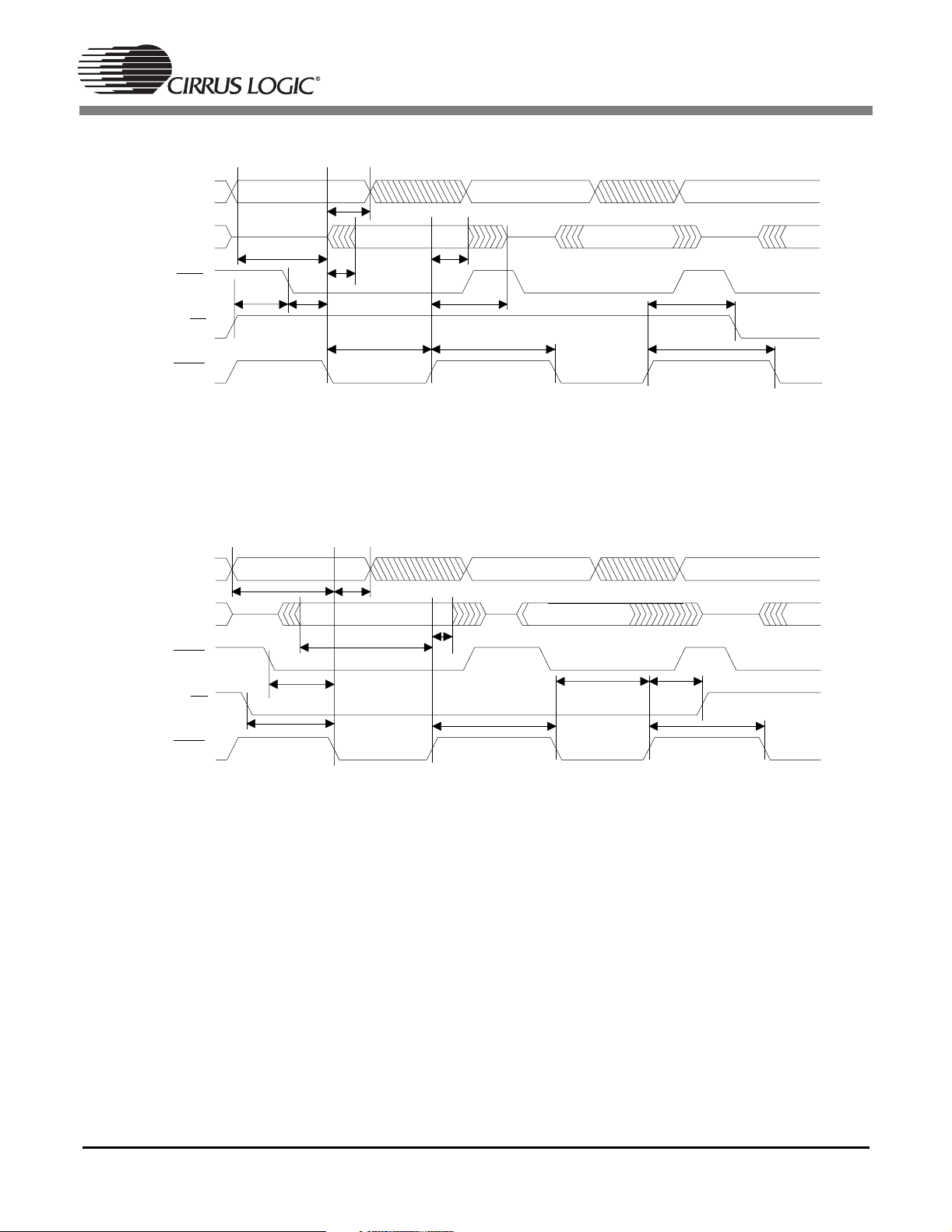

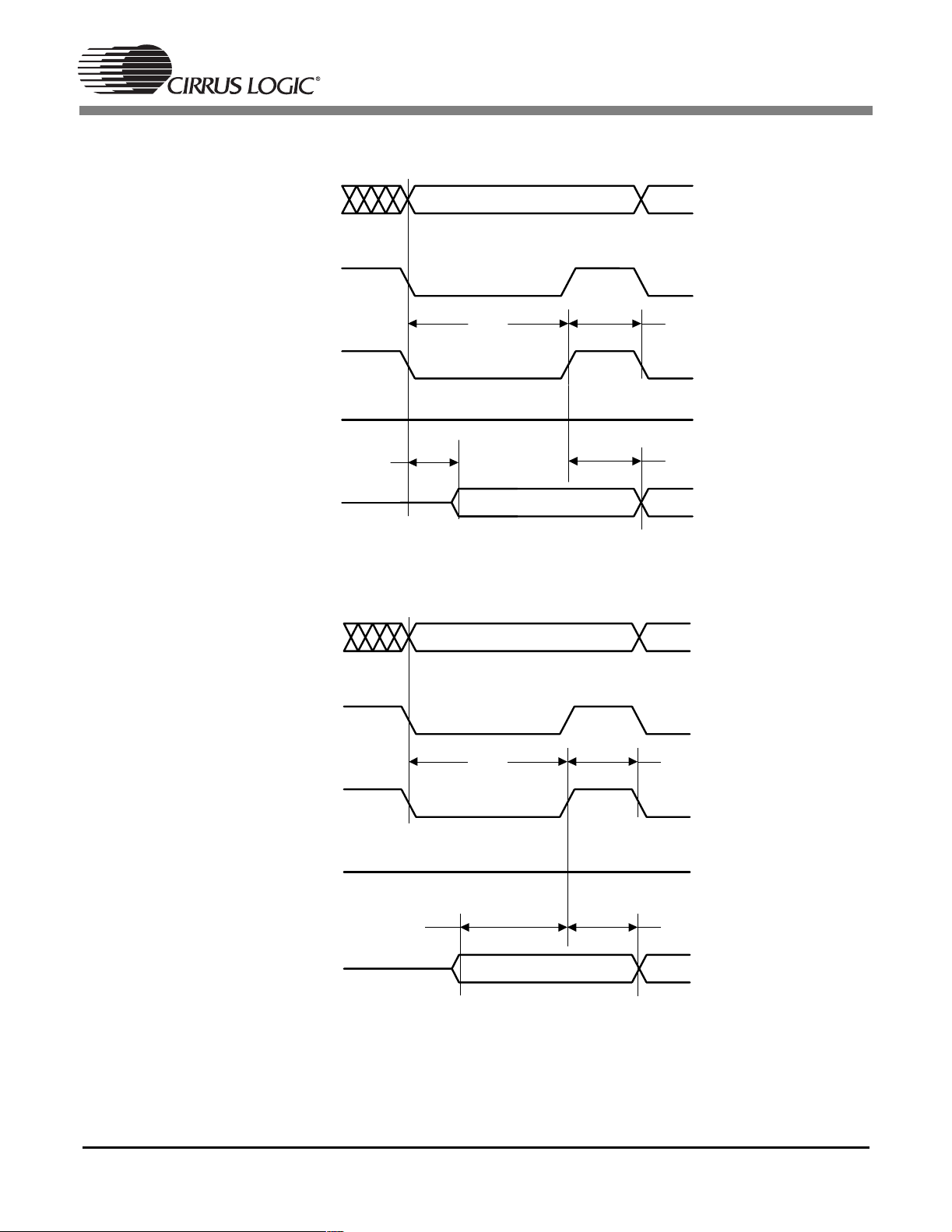

1.10 Switching Characteristics — Motorola®Host Slave Mode (DSPAB)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

Address setup before FCS and FDS low

Address hold time after FCS

and FDS low

Read

Delay between FDS then FCS low or FCS then FDS low

Data valid after FCS

and FRD low with R/W high)

T

T

T

T

mas

mah

mcdr

mdd

5-ns

5-ns

0-ns

-21ns

and FDS low for read (Note 1)

FCS

Data hold time after FCS

Data high-Z after FCS

FCS

or FDS high to FCS and FDS low for next read (Note 1)

FCS

or FDS high to FCS and FDS low for next write(Note 1)

or FDS high after read

or FDS high after read

T

mrpw

T

T

T

T

mrdtw

mdhr

mdis

mrd

DCLKP + 10 - ns

5-ns

-22ns

2*DCLKP + 10 - ns

2*DCLKP + 10 - ns

Write

Delay between FDS then FCS low or FCS then FDS low

Data setup before FCS

FCS

and FDS low for write (Note 1)

R/W

setup before FCS AND FDS low

R/W

hold time after FCS or FDS high

Data hold after FCS

FCS

or FDS high to FCS and FDS low with R/W high for

or FDS high

or FDS high

T

mcdw

T

mdsu

T

mwpw

T

mrwsu

T

mrwhld

T

mdhw

T

mwtrd

0-ns

20 - ns

DCLKP + 10 - ns

5-ns

5-ns

5-ns

2*DCLKP + 10 - ns

next read (Note 1)

or FDS high to FCS and FDS low for next write(Note 1)

FCS

T

mwd

2*DCLKP + 10 - ns

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP =

1/DCLK. The DSP clock can be defined as follows:

Internal Clock Mode:

DCLK ~ 60MHz before and during boot, i.e. DCLKP ~ 16.6ns

DCLK ~ 86 MHz after boot, i.e. DCLKP ~ 11.6ns

14

It should be noted that DCLK for the internal clock mode is application specific. The application code

users guide should be checked to confirm DCLK for the particular application.

A1:0F

T

mah

DATA7:0

F

CS

F

R/W

F

DS

F

T

T

mas

mrwsu

T

mcdr

T

mdhr

T

mdd

T

mdis

T

mrpw

T

mrd

Figure 7. Motorola®Parallel Host Slave Mode Read Cycle for DSPAB

A1:0F

T

mas

F

DATA7:0

FF

CS

F

R/W

F

DS

T

T

mcdw

T

mrwsu

mdsu

T

mah

T

mdhw

T

mwpw

T

mwd

T

mrdtw

T

mrwhld

T

mrwhld

T

mwtrd

Figure 8. Motorola®Parallel Host Slave Mode Write Cycle for DSPAB

15

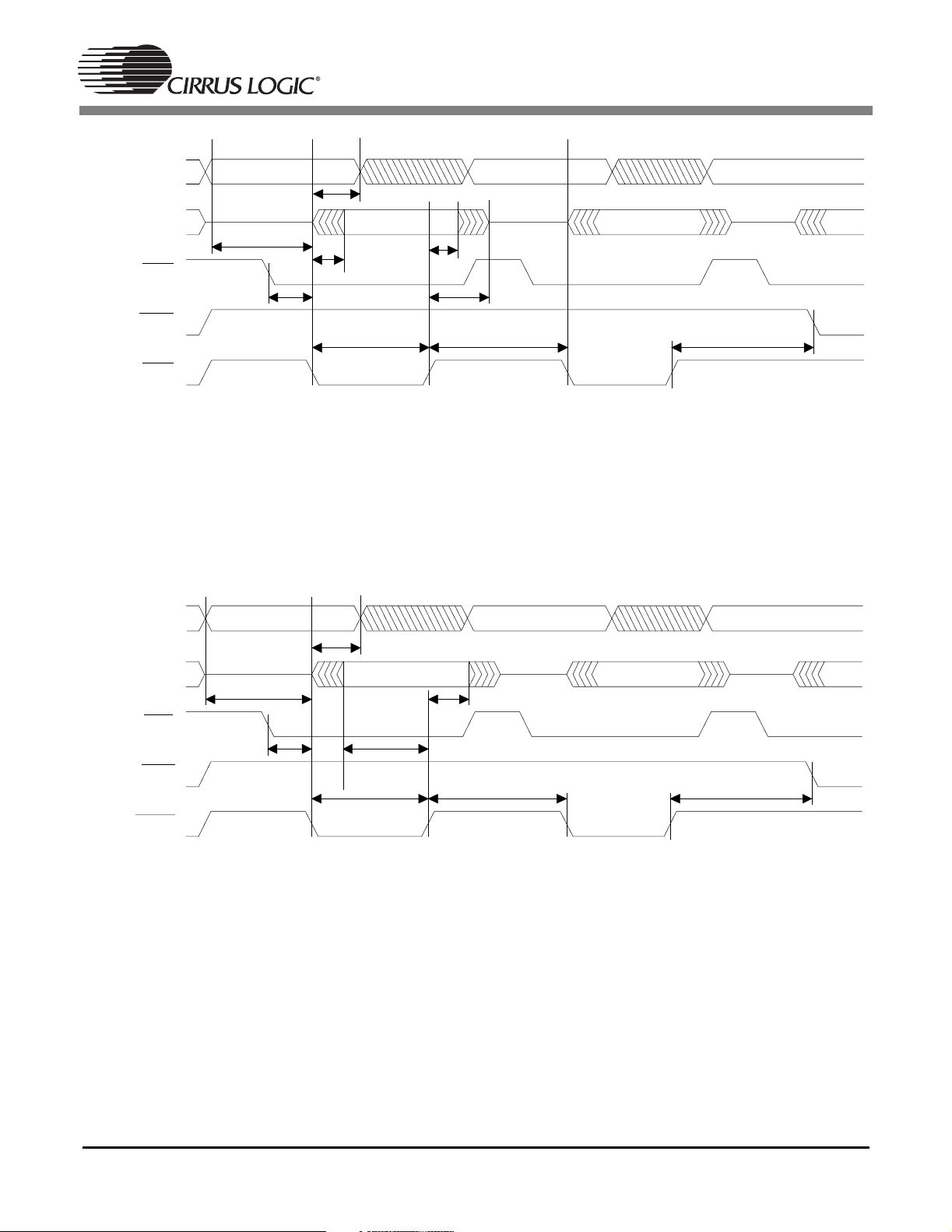

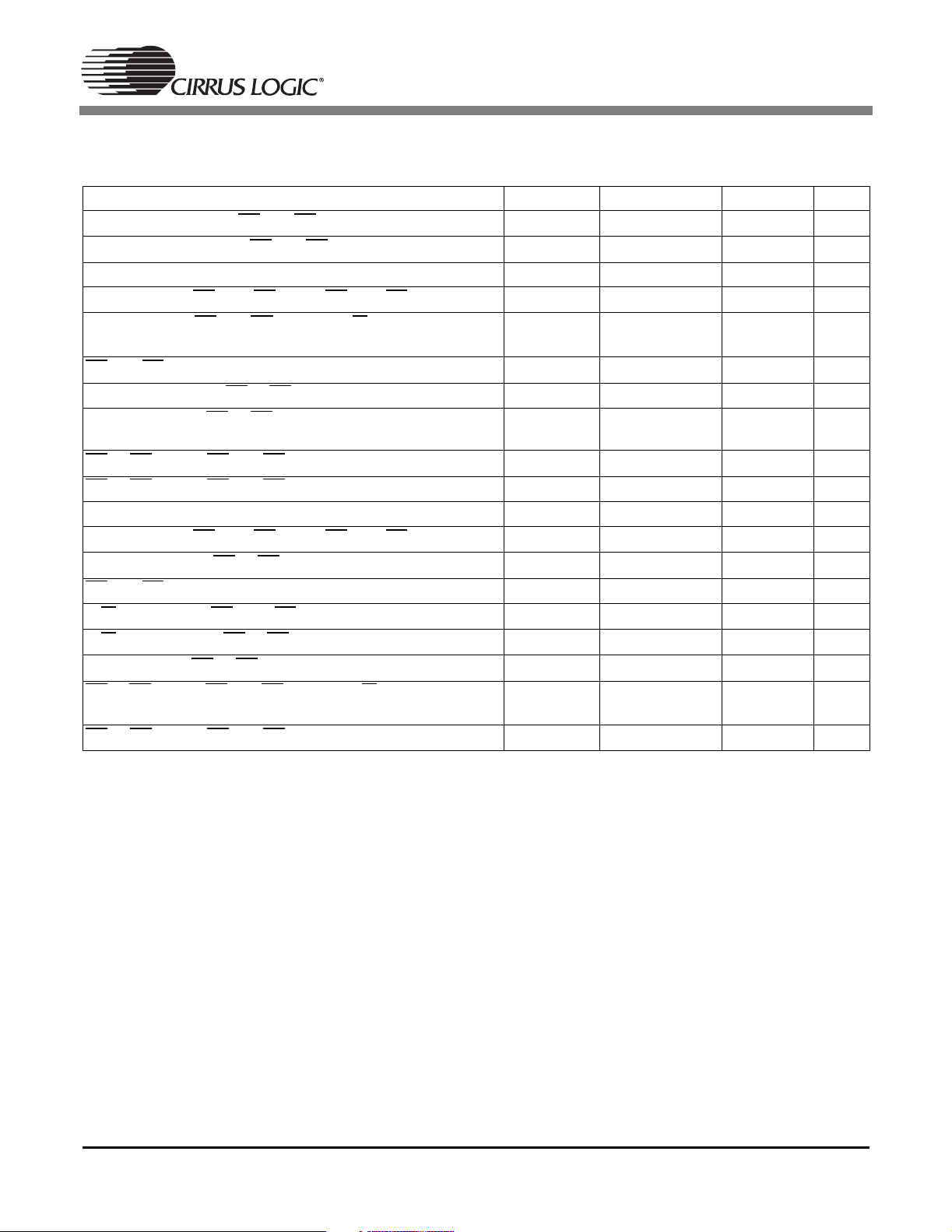

1.11 Switching Characteristics — Motorola®Host Slave Mode (DSPC)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

Address setup before CS and DS low

Address hold time after CS

and DS low

Read

Delay between DS then CS low or CS then DS low

Data valid after CS

and RD low with R/W high

T

T

T

T

mas

mah

mcdr

mdd

DCLKP - ns

DCLKP+15 - ns

0-ns

- 2*DCLKP+25ns

and DS low for read (Note 1)

CS

Data hold time after CS

Data high-Z after CS

or DS high to CS and DS low for next read (Note 1)

CS

CS

or DS high to CS and DS low for next write (Note 1)

or DS high after read

or DS high low after read

T

mrpw

T

T

T

T

mrdtw

mdhr

mdis

mrd

2*DCLKP - ns

DCLKP+ 10 - ns

- 2*DCLKP+10ns

2*DCLKP+10 - ns

2*DCLKP+10 - ns

Write

Delay between DS then CS low or CS then DS low

Data setup before CS

CS

and DS low for write (Note 1)

R/W

setup before CS AND DS low

R/W

hold time after CS or DS high

Data hold after CS

CS

or DS high to CS and DS low with R/W high for next read

or DS high

or DS high

T

mcdw

T

mdsu

T

mwpw

T

mrwsu

T

mrwhld

T

mdhw

T

mwtrd

0-ns

2*DCLKP+10 - ns

2*DCLKP - ns

DCLKP - ns

5-ns

DCLKP - ns

2*DCLKP+10 - ns

(Note 1)

CS or DS high to CS and DS low for next write (Note 1)

T

mwd

2*DCLKP+10 - ns

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLKP, in nanoseconds. DCLKP =

1/DCLK. The DSP clock can be defined as follows:

16

Internal Clock Mode:

DCLK ~ 60MHz before and during boot, i.e. DCLKP ~ 16.6ns

DCLK ~ 86 MHz after boot, i.e. DCLKP ~ 11.6ns

It should be noted that DCLK for the internal clock mode is application specific. The application code

users guide should be checked to confirm DCLK for the particular application.

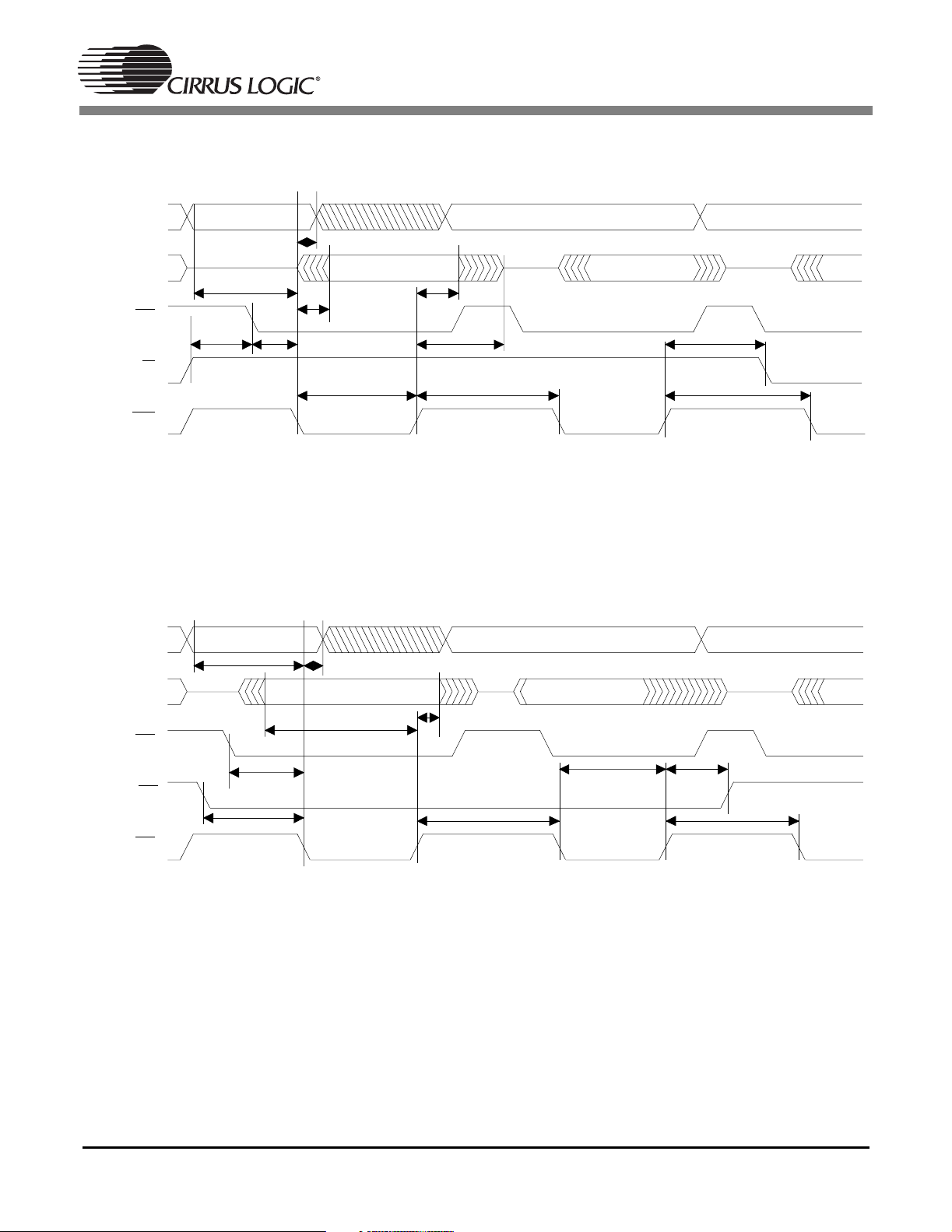

A1:0

DATA7:0

CS

R/W

DS

A1:0

DATA7:0

CS

R/W

DS

T

mas

T

mah

T

T

mrwsu

mas

T

mcdr

T

mdd

T

mrpw

T

mdhr

T

mrd

T

mdis

Figure 9. Motorola®ParallelHostSlaveModeReadCycleforDSPC

T

mah

T

T

mcdw

T

mrwsu

mdsu

T

mdhw

T

mwpw

T

mwd

T

mrdtw

T

mrwhld

T

mrwhld

T

mwtrd

Figure 10. Motorola®Parallel Host Slave Mode Write Cycle for DSPC

17

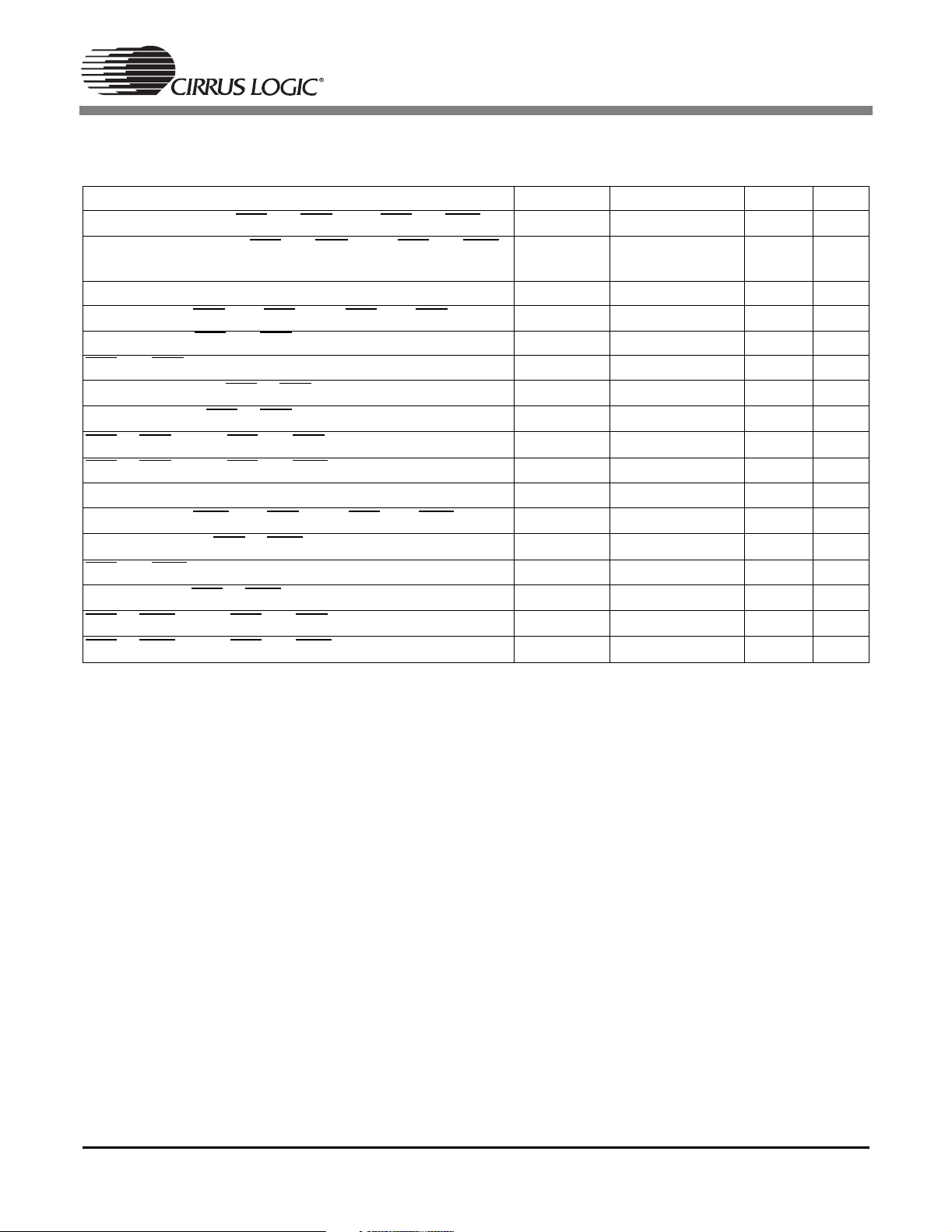

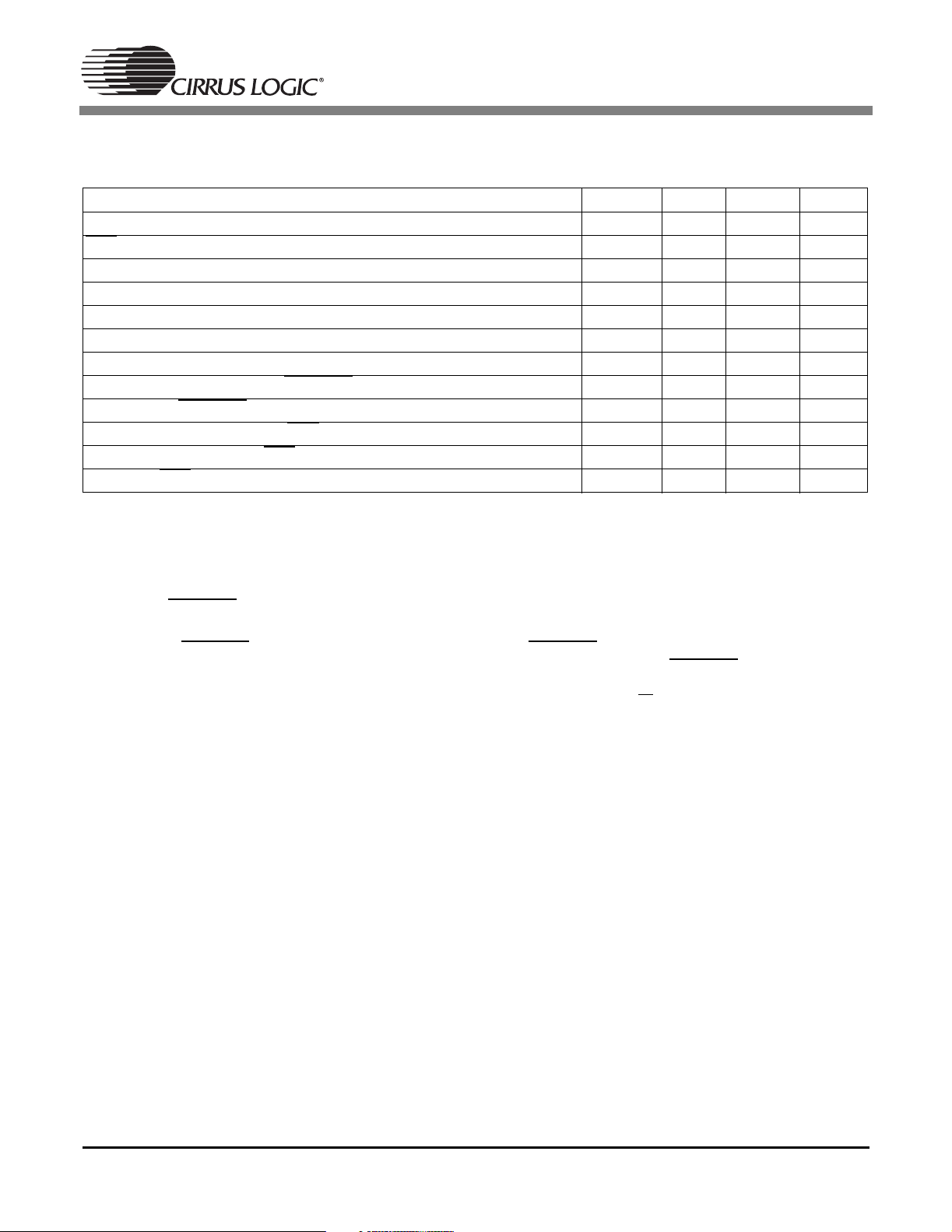

1.12 Switching Characteristics — SPI Control Port Slave Mode (DSPAB)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Units

FSCCLK clock frequency (Note 1) f

falling to FSCCLK rising t

FCS

FSCCLK low time t

FSCCLK high time t

Setup time FSCDIN to FSCCLK rising t

Hold time FSCCLK rising to FSCDIN (Note 2) t

Transition time from FSCCLK to FSCDOUT valid t

Time from FSCCLK rising to FINTREQ

Hold time for FINTREQ

from FSCCLK rising (Note 4, 5) t

Time from FSCCLK falling to FCS

rising (Note 3) t

rising t

High time between active FCS

Time from FCS

Notes: 1. The specification f

rising to FSCDOUT high-Z t

indicates the maximum speed of the hardware. The system designer should be

sck

aware that the actual maximum speed of the communication port may be limited by the DSP application

code. The relevant application code user’s manual should be consulted for the software speed

limitations.

2. Data must be held for sufficient time to bridge the transition time of FSCCLK.

3. FINTREQ

goes high only if there is no data to be read from the DSP at the rising edge of FSCCLK for

the second-to-last bit of the last byte of data during a read operation as shown.

4. If FINTREQ

goes high as indicated in (Note 3), then FINTREQ is guaranteed to remain high until the

next rising edge of FSCCLK. If there is more data to be read at this time, FINTREQ

again. Treat this condition as a new read transaction. Raise chip select to end the current read

transaction and then drop it, followed by the 7-bit address and the R/W

a new read transaction.

sck

css

scl

sch

cdisu

cdih

scdov

scrh

scrl

sccsh

t

csht

cscdo

-2MHz

20 - ns

150 - ns

150 - ns

50 - ns

50 - ns

-40ns

-200ns

0-ns

20 - ns

200 - ns

20 ns

goes active low

bit (set to 1 for a read) to start

18

sccsh

t

A6

csht

t

LSB

LSB

tri-state

cscdo

t

scrl

t

675

scdov

07

62

MSB

R/W

A0A6 A5

t

MSB

scdov

t

scrh

t

Figure 11. SPI Control Port Slave Mode Timing (DSPAB)

cdih

1

scl

t

0

css

t

sch

t

f

t

r

t

t

cdisu

t

FCS

FSCCLK

FSCDIN

FSCDOUT

FINTREQ

19

1.13 Switching Characteristics — SPI Control Port Slave Mode (DSPC)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Units

SCCLK clock frequency (Note 1) f

falling to SCCLK rising t

CS

SCCLK low time t

SCCLK high time t

Setup time SCDIN to SCCLK rising t

Hold time SCCLK rising to SCDIN (Note 2) t

Time from SCCLK low to SCDOUT valid t

Time from SCCLK rising to INTREQ

Hold time for INTREQ

from SCCLK rising t

Time from SCCLK falling to CS

Time from SCCLK low to CS

falling t

rising t

rising t

High time between active CS

Time from CS

Notes: 1. The specification f

rising to SCDOUT high-Z t

indicates the maximum speed of the hardware. The system designer should be

sck

aware that the actual maximum speed of the communication port may be limited by the software. The

relevant application code user’s manual should be consulted for the software speed limitations.

2. Data must be held for sufficient time to bridge the transition time of SCCLK.

sck

css

scl

sch

cdisu

cdih

scdov

scrh

scrl

sccsh

sccsl

t

csht

cscdo

-5MHz

4*DCLKP - ns

4*DCLKP - ns

4*DCLKP - ns

DCLKP - ns

DCLKP+20 - ns

- 3*DCLKP+20 ns

- DCLKP ns

DCLKP - ns

2*DCLKP+15 - ns

10 ns

4*DCLKP - ns

DCLKP ns

20

Figure 12. SPI Control Port Slave Mode Timing (DSPC)

21

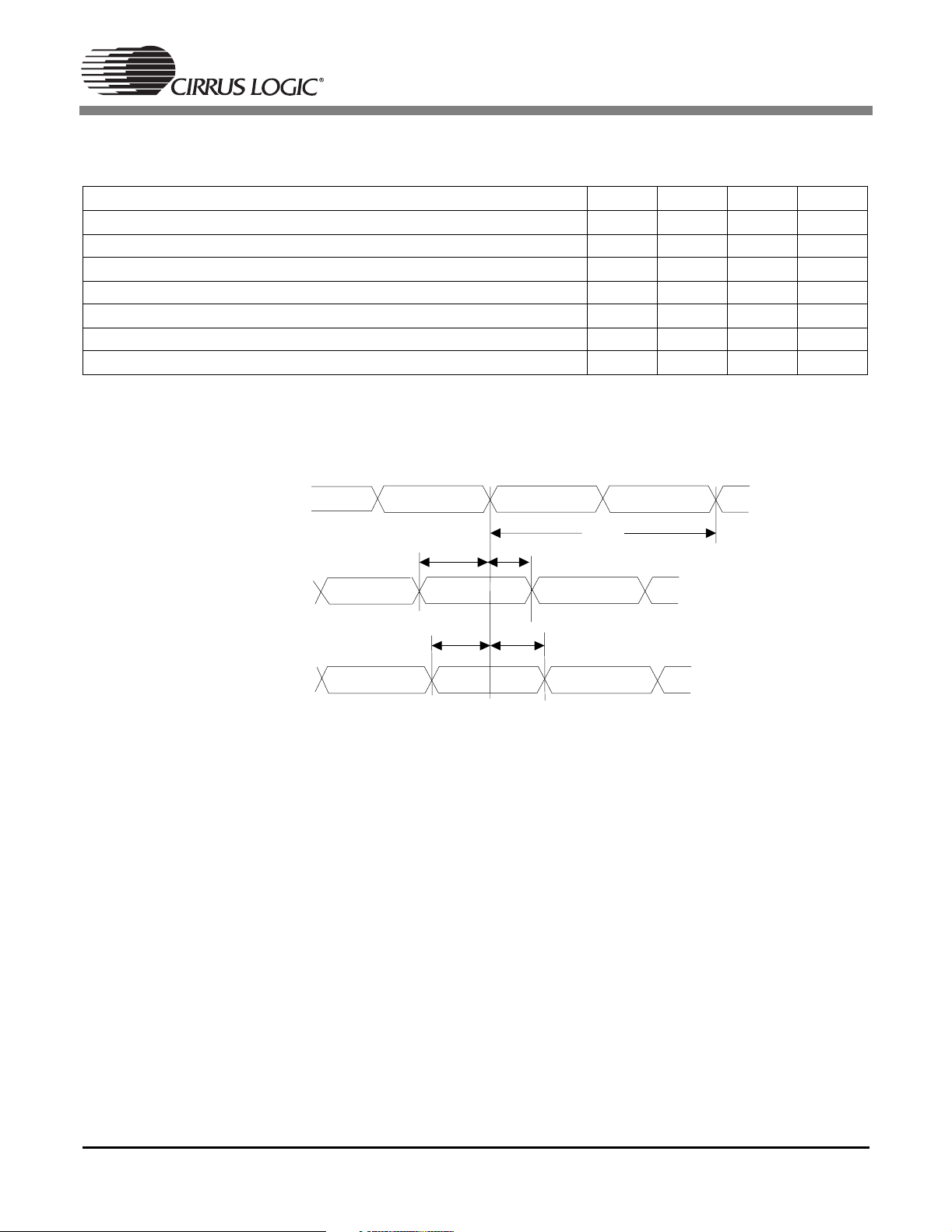

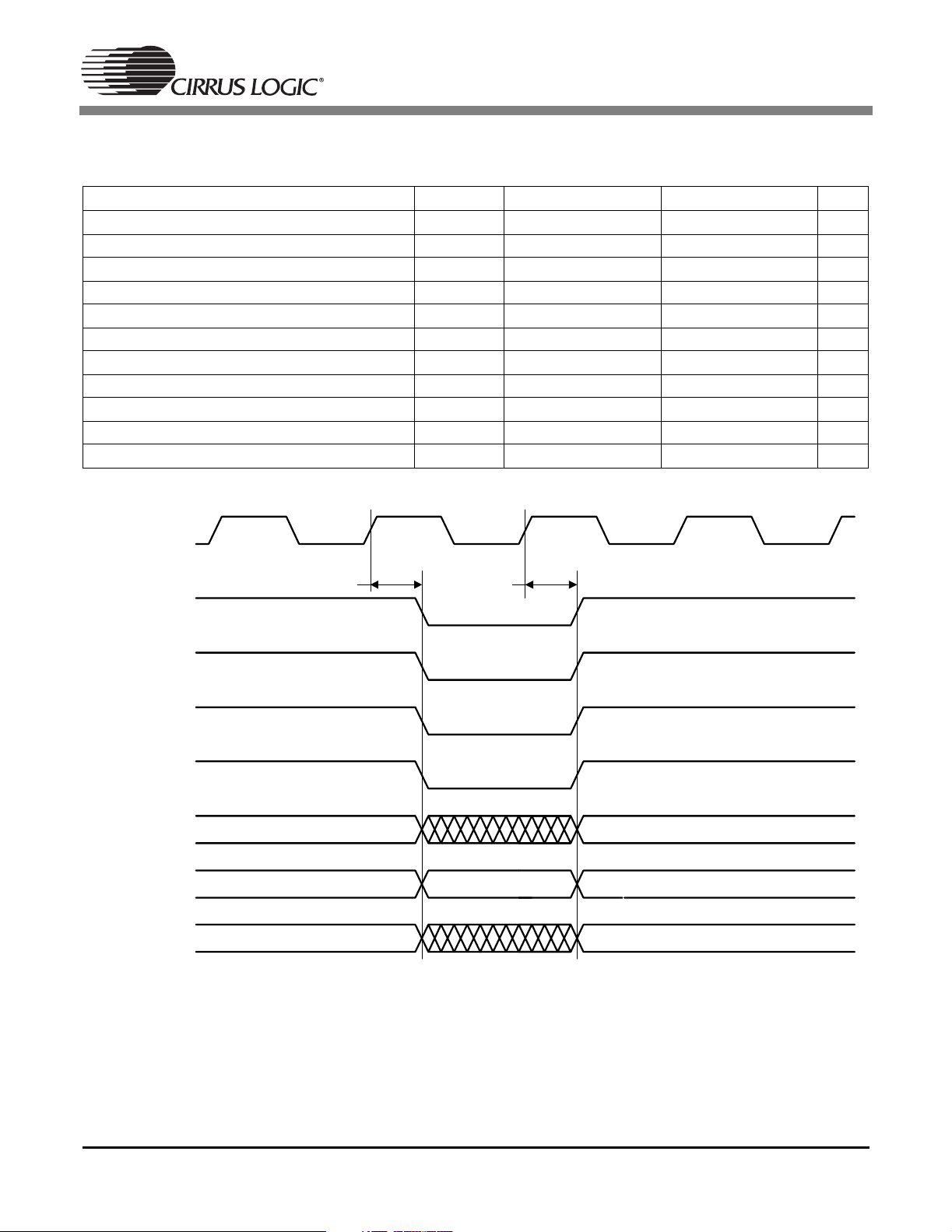

1.14 Switching Characteristics — Digital Audio Input (DSPAB)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

FSCLKN1 period for Slave mode T

sclki

FSCLKN1 duty cycle for Slave mode 45 55 %

Slave Mode (Note 2)

Time from active edge of FSCLKN1(2) to FLRCLKN1(2) transition T

Time from FLRCLKN1(2) transition to FSCLKN1(2) active edge T

FSDATAN1(2) setup to FSCLKN1(2) transition (Note 1) T

FSDATAN1(2) hold time after FSCLKN1(2) transition (Note 1) T

stlr

lrts

sdsus

sdhs

Notes: 1. This timing parameter is defined from the active edge of FSCLKN1/2. The active edge of FSCLKN1/2

is the point at which the data is valid.

2. Slave mode is defined as FSCLKN1/2 and FLRCLKN1/2 driven by an external source.

FSCLKN1

FSCLKN2

T

T

lrts

T

stlr

sclki

FLRCLKN1

FLRCLKN2

40 - ns

10 - ns

10 - ns

5-ns

5-ns

FSDATAN1

FSDATAN2

Figure 13. Digital Audio Input Data, Slave Clock Timing

T

sdsus T

sdhs

22

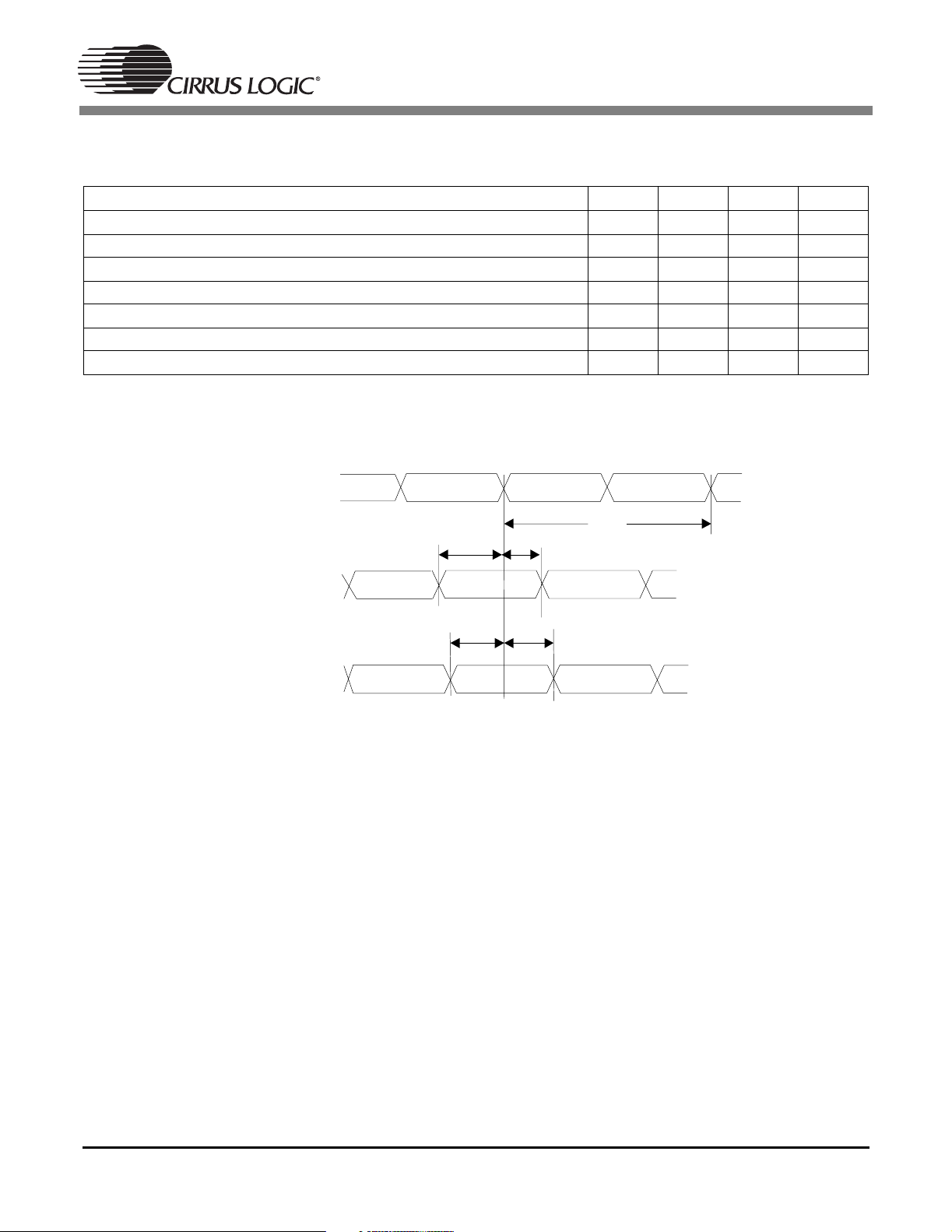

1.15 Switching Characteristics — Serial Audio Input (DSPC)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

Slave Mode

SCLKN period for Slave mode T

sclki

SCLKN duty cycle for Slave mode 45 55 %

Time from active edge of SCLKN to LRCLKN transition T

Time from LRCLKN transition to SCLKN active edge T

SDATAN0 setup to SCLKN transition (Notes 2) T

SDATAN0 hold time after SCLKN transition (Notes 2) T

stlr

lrts

sdsus

sdhs

Notes: 1. Slave mode is defined as SCLKN and LRCLKN being driven by an external source.

2. This timing parameter is defined from the active edge of SCLKN. The active edge of SCLKN is the point

at which the data is valid.

SCLKN

T

sclki

stlr

LRCLKN

T

lrts

T

40 - ns

20 - ns

20 - ns

10 - ns

10 - ns

SDATAN0, 1, 2, 3

Figure 14. Serial Audio Input Data, Slave Clock Timing

T

sdsus T

sdhs

23

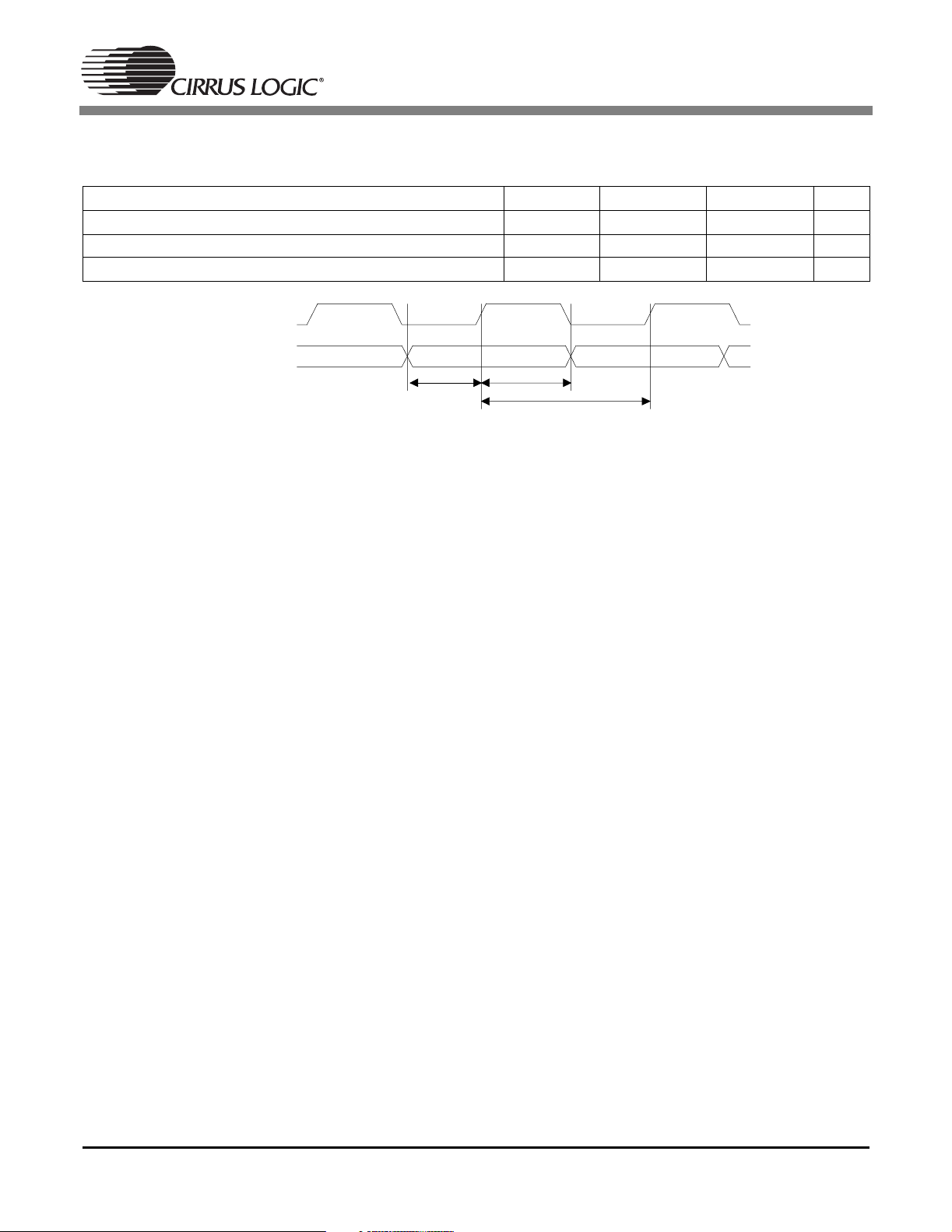

1.16 Switching Characteristics — CMPDAT, CMPCLK (DSPAB)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

Serial compressed data clock CMPCLK frequency T

CMPDAT setup before CMPCLK high T

CMPDAT hold after CMPCLK high T

CMPCLK

CMPDAT

cmpclk

cmpsu

cmphld

-27MHz

10 - ns

10 - ns

T

cmpsu

T

cmpcl k

T

cmphld

Figure 15. Serial Compressed Data Timing

24

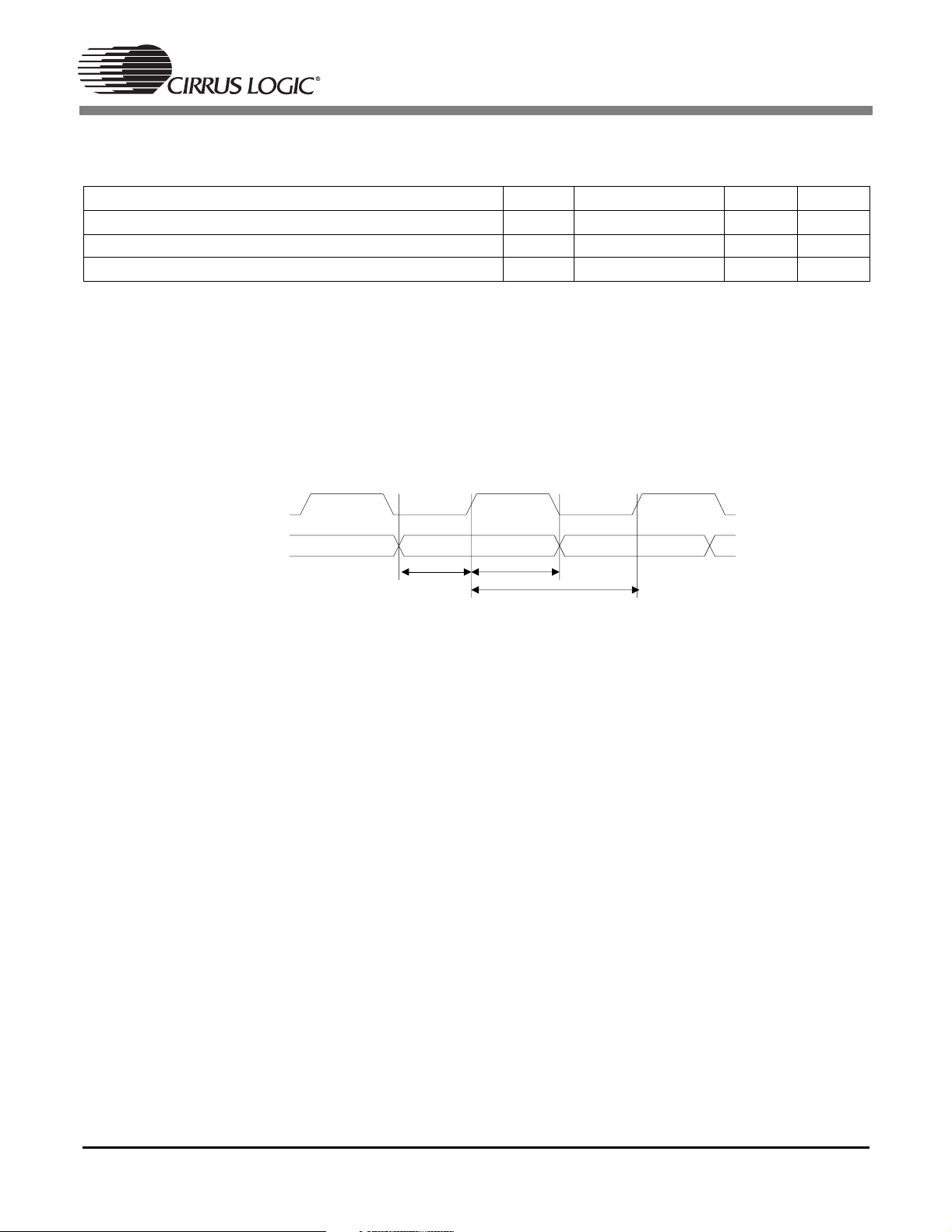

1.17 Switching Characteristics — Parallel Data Input (DSPAB)

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

CMPCLK Period T

FDAT[7:0] setup before CMPCLK high T

FDAT[7:0] hold after CMPCLK high T

cmpclk

cmpsu

cmphld

Notes: 1. Certain timing parameters are normalized to the DSP clock, DCLK, in nanoseconds. The DSP clock can

be defined as follows:

Internal Clock Mode:

DCLK ~ 60MHz before and during boot, i.e. DCLKP ~ 16.6ns

DCLK ~ 86 MHz after boot, i.e. DCLKP ~ 11.6ns

It should be noted that DCLK for the internal clock mode is application specific. The application code

users guide should be checked to confirm DCLK for the particular application.

CMPCLK

FDAT[7:0]

T

cmps u

T

cmpc lk

4*DCLKP + 10 ns

10 ns

10 ns

T

cmphld

Figure 16. Parallel Data Timing

25

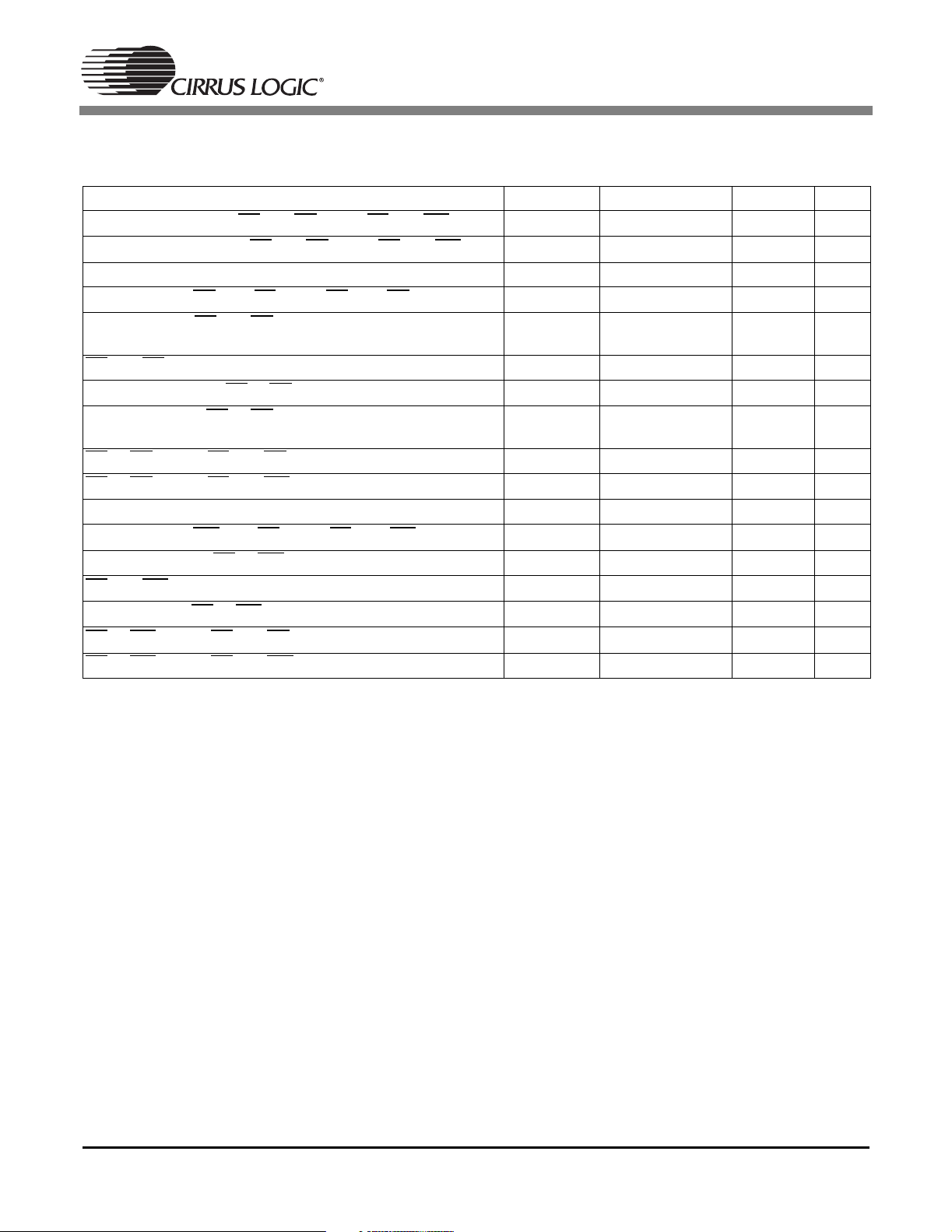

1.18 Switching Characteristics — Digital Audio Output

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

MCLK period T

mclk

MCLK duty cycle 40 60 %

SCLK0, SCLK1 period for Master or Slave mode (Note 2) T

sclk

SCLK0, SCLK1 duty cycle for Master or Slave mode (Note 2) 45 55 %

Master Mode (Output A1 Mode) (Note 2, 3)

SCLK0, SCLK1 delay from MCLK rising edge, MCLK as an

T

sdmi

input

LRCLK0, LRCLK1 delay from SCLK0, SCLK1 transition,

T

lrds

respectively (Note 4)

AUDATA7–0 delay from SCLK0, SCLK1 transition (Note 4) T

adsm

Slave Mode (Output A0 Mode) (Note 5)

Time from active edge of SCLK0, SCLK1 to LRCLK0, LRCLK1

T

stlr

transition

Time from LRCLK0, LRCLK1 transition to SCLK0, SCLK1

T

lrts

active edge

AUDATA7–0 delay from SCLK0, SCLK1 transition (Note 4) T

adss

Notes: 1. DSPC has two Digital Audio Output modules having analogous signal names ending in 0 and 1. Both

DAO ports share a common MCLK but have independent SCLKs and LRCLKs.

2. Master mode timing specifications are characterized, not production tested.

3. Master mode is defined as the CS49400 driving both SCLK0, SCLK1, LRCLK0, and LRCLK1. When

MCLK is an input, it is divided to produce SCLK0, SCLK1, LRCLK0 and LRCLK1.

4. This timing parameter is defined from the non-active edge of SCLK0 and SCLK1. The active edge of

SCLK0 and SCLK1 is the point at which the data is valid.

5. Slave mode is defined as SCLK0, SCLK1, LRCLK0 and LRCLK1 driven by an external source.

40 - ns

40 - ns

15 ns

10 ns

10 ns

10 - ns

10 - ns

15 ns

26

MCLK (Input)

T

mclk

SCLK0,1 (Output)

T

T

sdmo,

sdmi

SCLK 0,1

(Output)

T

sclk

T

lrds

LRCLK 0,1

(Output)

T

adsm

AUDATA7:0

Master Mode (Output A1) Output Clock Timing and Digital Audio

Output Data

SCLK 0,1

(Input)

T

T

lrts

sclk

T

stlr

LRCLK 0,1

(Input)

T

adss

AUDATA7:0

Slave Mode (Output A0) Output Clock Timing and Digital Audio

Output Data

Figure 18. Digital Audio Output Data, Input and Output Clock Timing

27

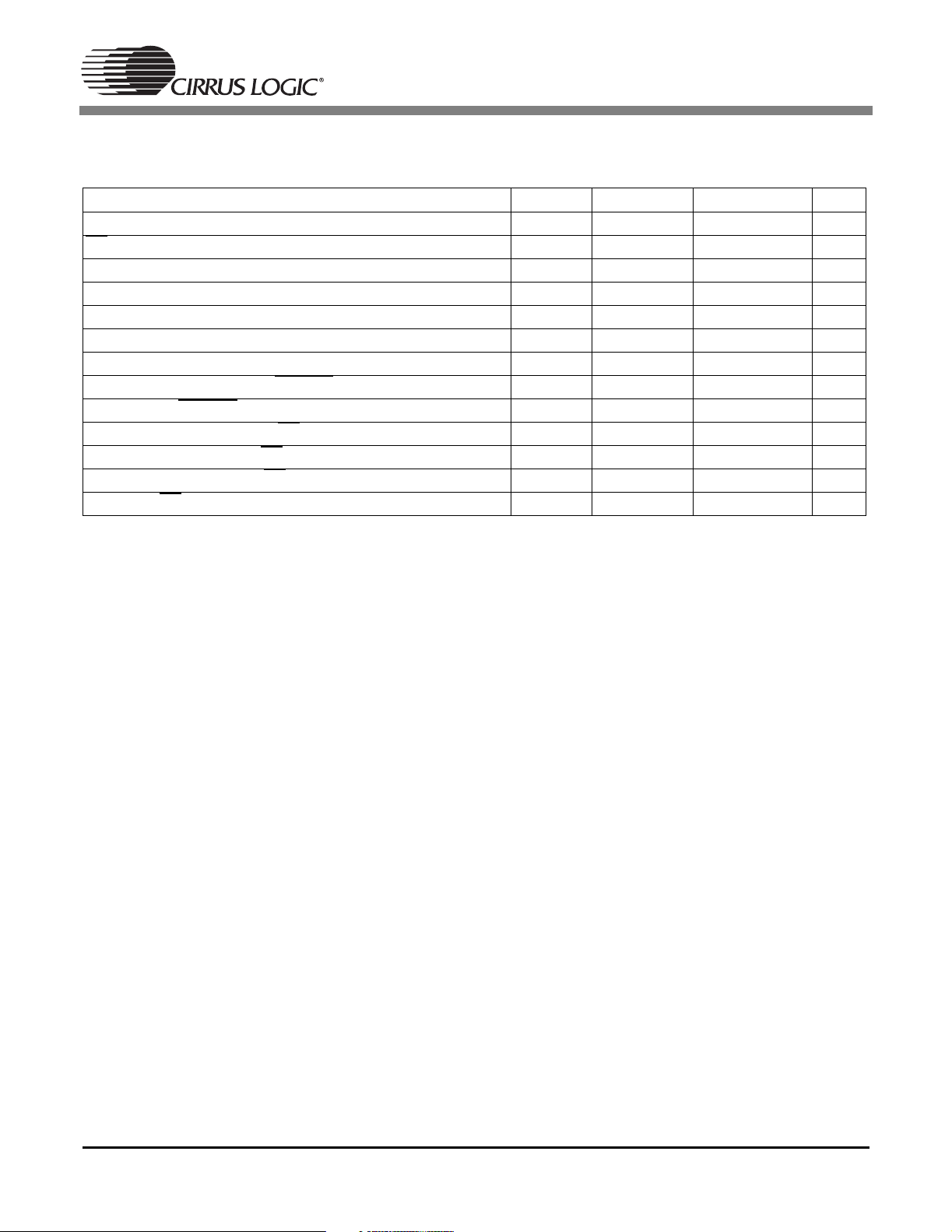

1.19 Switching Characteristics — SRAM/FLASH Interface

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL=20pF)

Parameter Symbol Min Max Unit

Write Cycle

Single Byte Write Cycle T

Data Hold after NV_WE or NV_CS high T

Data Valid after NV_CS and NV_WE low T

Data Strobe T

Read Cycle

Single Byte Read Cycle T

Data Strobe T

Data Hold after NV_WE or NV_CS high T

Data Setup Time T

TA[19:0]

NV_CS

T

wrc

NV_WE

T

ds

wrc

dh

dv

ds

rdc

ds

dh

su

(SRAM_FLASH_WR_CYCLE + 1) * DCLKP

DCLKP-5

DCLKP-5

(SRAM_FLASH_RD_CYCLE + 1) * DCLKP

DCLKP-5

DCLKP+5

DCLKP+5

-ns

-ns

10 ns

-ns

-ns

-ns

-ns

-ns

XTD[7:0]

XTA[19:0]

NV_CS

NV_OE

EXTD[7:0]

T

dv

MSP LSP

T

dh

Figure 19. SRAM/Flash Controller Timing Diagram - Write Cycle

T

rdc

T

su

MSP LSP

T

ds

T

dh

Figure 20. SRAM/Flash Controller Timing Diagram - Read Cycle

28

EXTA[19:0]

NV_CS

NV_WE

NV_OE

Valid

T

wrc

T

dv

T

ds

T

dh

EXTD[7:0]

LSP

Figure 21. SRAM/Flash Controller Timing Diagram - Single Byte Write Cycle

EXTA[19:0]

Valid

NV_CS

T

rdc

T

ds

NV_OE

NV_WE

T

su

T

dh

EXTD[7:0]

LSP

Figure 22. SRAM/Flash Controller Timing Diagram - Single Byte Read Cycle

29

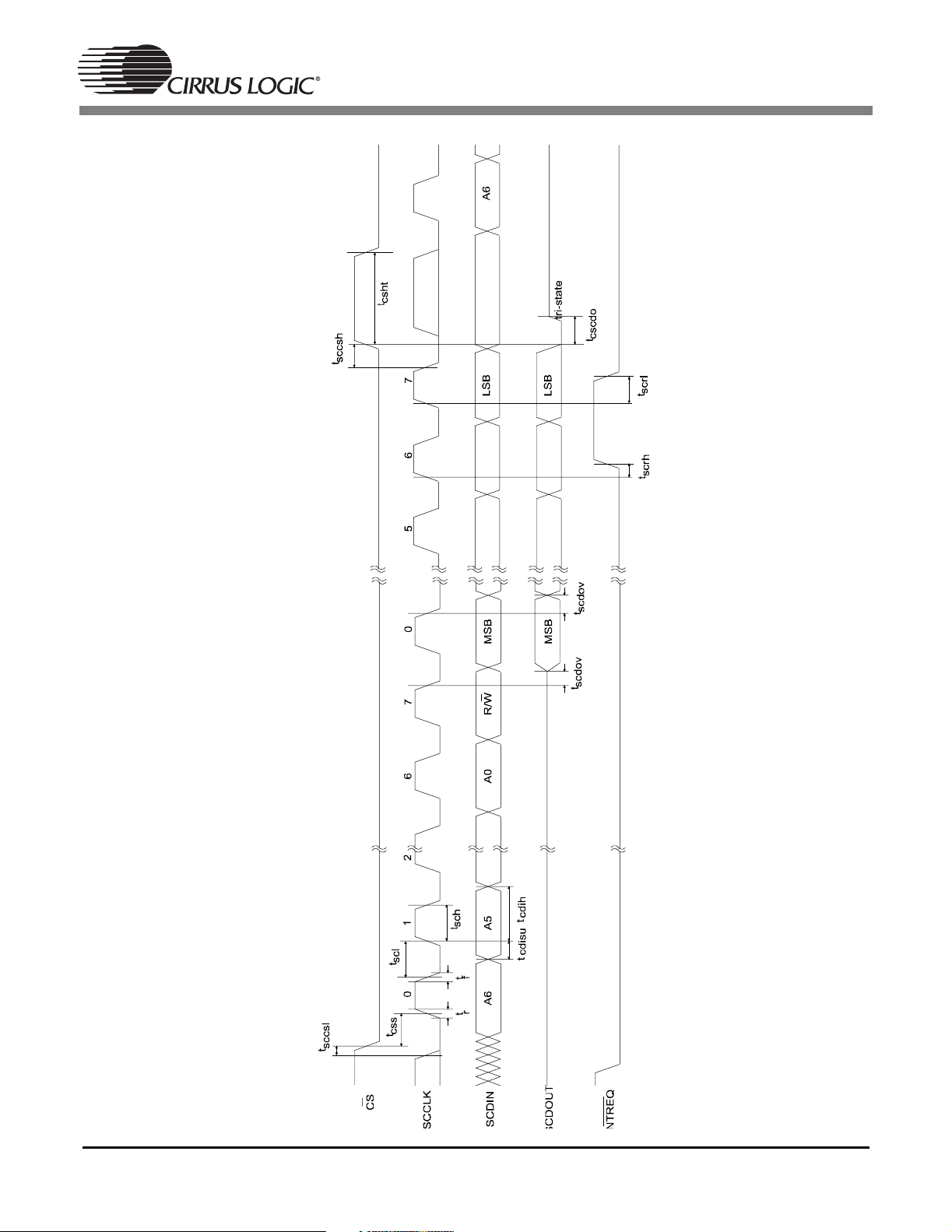

1.20 Switching Characteristics — SDRAM Interface

(TA=25°C; VDD, PLLVDD = 2.5 V; VDDSD = 3.3 V; CL= 20 pF, SD_CLKOUT = SD_CLKIN)

Parameter Symbol Min Max Unit

SD_CLKIN high time t

SD_CLKIN low time t

clk_high

clk_low

SD_CLKOUT rise/fall time t

SD_CLKOUT duty cycle t

SD_CLKOUT rising edge to signal valid t

Signal hold from SD_CLKOUT rising edge t

SD_CLKOUT rising edge to SD_DQMn valid t

SD_DQMn hold from SD_CLKOUT rising edge t

SD_DATA valid setup to SD_CLKIN rising edge t

SD_DATA valid hold to SD_CLKIN rising edge t

SD_CLKOUT rising edge to ADDRn valid t

SD_CLKOUT

clkrf

clkrf

d

h

DQd

DQh

DAs

DAh

d

0.475*DCLKP - ns

0.475*DCLKP - ns

-1ns

45 55 %

-9.8ns

1.0 ns

-7.2ns

1.0 - ns

-8.0ns

8.3 ns

1.0 ns

SSSSDDDD____CCCCSSSS

SSSSDDDD____RRRRAAAASSSS

SSSSDDDD____CCCCAAAASSSS

SSSSDDDD____WWWWEEEE

SD_DQMn

SD_ADDRn

SD_DATAn

t

d

t

h

OPCODE

Figure 23. SDRAM Controller Timing Diagram - Load Mode Register Cycle

30

DQh

t

KOUT

h

t

00 11

Figure 24. SDRAM Controller Timing Diagram - Burst Write Cycle

LSP0 MSP0

d

t

SS

S

SS

S

SS

S

EE

CC

CS

__

_C

D

DD

D_

AA

AS

RR

RA

_

__

_R

AA

AS

CC

CA

_

__

_C

E

WW

WE

__

_W

D

DD

D_

ATAn

DDRn

DQMn

31

LSP3 MSP3

DQh

T

clk_hig h

t

00 11

clkrf

t

DAh

t

LSP0 MSP0

Figure 25. SDRAM Controller Timing Diagram - Burst Read Cycle

DAs

t

32

h

t

d

t

SS

S

SS

S

AA

AS

CC

CS

__

_C

RR

RA

__

_R

DD

D_

S

SS

SD

DD

D_

S

SS

_CLKOUT

SD

SS

S

AA

AS

CC

CA

__

_C

DD

D_

S

SS

SD

EE

E

WW

WE

__

_W

DD

D_

S

SS

SD

DQd

t

D_DQMn

CAS=2

clk_low

t

d

t

D_CLKIN

D_DAT An

D_ADDRn

SD_CLKOUT

SSSSDDDD____CCCCSSSS

SSSSDDDD____RRRRAAAASSSS

SSSSDDDD____CCCCAAAASSSS

SSSSDDDD____WWWWEEEE

SD_DQMn

SD_ADDRn

SD_DATAn

t

d

t

d

t

h

Figure 26. SDRAM Controller Timing Diagram - Auto Refresh Cycle

33

2. OVERVIEW

• HDCD

®

The CS49400 is a 24-bit fixed-point decoder DSP

followed by a 32-bit fixed point programmable

post-processor DSP. The decoder portion of the

CS49400 is referred to as “DSPAB”. The postprocessor DSP is referred to as “DSPC”. Both

DSPAB and DSPC include their own dedicated

peripherals such as serial and parallel control ports,

and serial audio interfaces. DSPC also has a

external memory interface which supports

SRAM/SDRAM/EPROM.

All the decoding/processing algorithms listed

below require delivery of PCM or IEC61937packed compressed data via I2S or LJ formatted

digital audio to the CS49400. Today the CS49400

will support all of the following

decoding/processing standards:

• PCM Pass-Through/PCM Upsampler

• Dolby Digital™(with Dolby Pro Logic)

• Dolby Digital Pro Logic II

• Dolby Digital EX

™

• Dolby Digital EX Pro Logic II

™

™

™

• MPEG-2, Advanced Audio Coding Algorithm

(AAC)

• MPEG Multichannel

• MPEG Multichannel with Dolby Pro Logic II

™

• MPEG-1/2, Layer III (MP3)

All of the above audio decoding/processing

algorithms and the associated application notes

(AN208 and their corresponding appendices) are

available through the Crystal Ware

TM

Software

Licensing Program. Please refer to AN208 for the

latest listing of application codes for DSPAB.

DSPC is unique to DSPAB in the sense that the

designer may choose to just load a standard or

enhanced application code (.ULD file) from the

Crystal Ware Software Library or if they have

access to the Cirrus Framework DSPC

Development Kit, they may choose to build their

own application code from a variety of modules. A

DSPC application code contains all of the

necessary post-processing modules, such as

Crossbar Mixer, Pro Logic Module, Bass Manager

Module, and Audio Manager (Kernel). A module is

just a single processing module, such as Tone

Control, Parametric/Graphic EQ, or Dolby Pro

Logic matrix decoder. DSPC on the CS49400 will

support the following post-processing application

codes and/or modules:

• Standard Post-Processor (includes the follow-

ing modules all compiled into one .ULD file):

Downmixer module, Dualzone module, Crossbar Mixer module, 7.1 Channel Bass Manager

module, Audio Manager module (Volume

Control, Trim Control and Channel Remap),

and Delay module

• DTS Digital Surround™

• DTS 96/24™ (Front-end Decoder)

• DTS Digital Surround™ with

Dolby Pro Logic II™

• DTS-ES Extended Surround

™

(DTS-ES Discrete 6.1 and DTS-ES Matrix 6.1)

• DTS-ES 96/24

• DTS Neo:6

• LOGIC7

™

(Front-end Decoder)

™

®

• SRS Circle Surround™II

34

• Advanced Post-Processor (includes the all of

the standard post-processing modules plus the

Tone Control module, Parametric EQ module,

Re-EQ module in all compiled into one .ULD )

• Dolby Pro Logic

• Dolby Pro Logic II

• SRS Circle Surround II

• DTS Neo:6

• LOGIC7

®

™

™

™

™

• THX®Surround EX™ 7.1 Channel

Post-Processor

• THX®Ultra2 Cinema™7.1 Channel

Post-Processor

• Cirrus Extra Surround

• Cirrus Original Multichannel Surround

™

™

• Virtual Dolby Digital™/Virtual Dolby Digital

Pro Logic II

• VMAx VirtualTheater

• HDCD

™

Virtualizer Module

™

Virtualizer Module

®

Multichannel Decoder

• DVD-Audio/Video and Multichannel SACD

Bass Management

™

• DTS/DTS-ES 96/24

• DTS/DTS-ES 96/24

®

THX

Ultra2 Cinema

Back-End Decoder

™

Back-End Decoder with

™

All of the above audio post-processing applications

codes and/or Cirrus FrameworkTM modules and

the associated application notes (AN209 and the

associated appendices) are available through the

Crystal WareTM Software Licensing Program. All

standard or enhanced post-processing code

modules are only available to customers who

TM

qualify for the Cirrus Framework

CS49400

Family DSPC Programming Kit. Please refer to

AN209 for the latest listing of application codes

and Cirrus FrameworkTM modules available for

DSPC.

2.1 DSPAB

2.2 DSPC

DSPC is a 32-bit, general-purpose, fixed-point

RAM-based processor which includes on-chip

ROM tables. It has been designed with a generous

amount of on-chip program and data RAM, and has

all necessary peripherals required to support the

latest standards in consumer entertainment

products such as AV receivers and DVDAudio/Video players.

DSPC has on-chip data and program RAM, and

both external SDRAM and SRAM memory

interfaces. These interfaces can be used to expand

the data memory. DSPC also has its own 8-channel

digital audio input for post-processing PCM from a

Multichannel Super Audio CD (SACD) input or

DVD-Audio/Video input, via high-performance

A/Ds or from some other type of multichannel

digital input, capable of delivering 4 stereo digital

audio channels such as IEEE1394 (a.k.a. I-Link

or Firewire®). Data can be delivered to this port

using the standard audio formats (I

can be controlled serially using the SPI standard or

via Parallel host control port using the Motorola

or Intel®standard. DSPC has a Digital Audio

output port that has eight stereo serial data outputs

for a total of 16 channels. Data can be delivered

from these outputs in serial I

of these outputs (AUDAT3, AUDAT7) can be

configured as a IEC60958-format S/PDIF

transmitter.

2

S or LJ). DSPC

2

S or LJ format. Two

®

®

DSPAB is an enhanced version of the CS49300. It

was designed to have legacy code support for all

decoder applications developed for the CS49300. It

includes performance enhancements such as the

ability to decode AAC without the need for

external SRAM memory. DSPAB has a Digital

Audio Input (DAI) and a Compressed Data Input

2

(CDI) port for data delivery in either I

SorLJ

format. DSPAB can be controlled serially using the

SPI standard and can also be controlled via a

®

Parallel host control port using the Motorola

®

Intel

communication standards.

or

This document focuses on the electrical features of

the CS49400. The features are described from a

hardware design perspective. It should be

understood that not all of the features portrayed in

this document are supported by all of the versions

of application code available. The application code

user’s guides should be consulted to determine

which hardware features are supported by the

software.

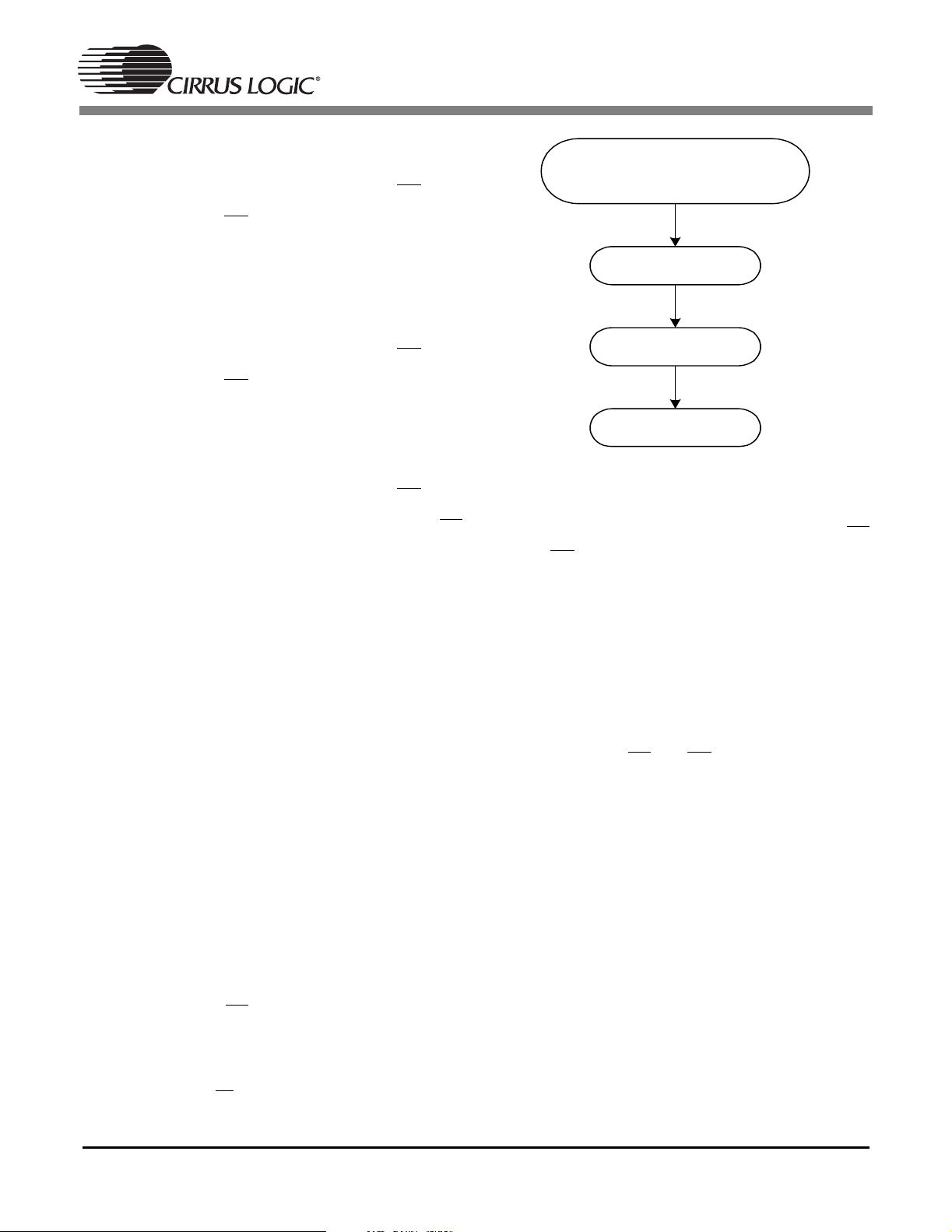

Please note that a download of application software

is required each time the part is powered up. This

term should be interpreted as meaning the transfer of

application code into the internal memory of the part

35

from either an external microcontroller or through

one of the boot procedures listed in Section 8.

3. TYPICAL CONNECTION DIAGRAMS

Four typical connection diagrams have been

presented to illustrate using the part with the

different communication modes available. They

are as follows:

Figure 27, "SPI Control with External Memory 144 Pin Package" on page 38.

®

Figure 28, "Intel

Parallel Control Mode - 144 Pin

Package" on page 39.

®

Figure 29, "Motorola

Parallel Control Mode - 144

Pin Package" on page 40.

The following should be noted when viewing the

typical connection diagrams:

Note: The pins are grouped functionally in each

of the typical connection diagrams. Please be

aware that the CS49400 symbol may appear

differently in each diagram.

The external memory interface is supported

when a serial or parallel communication mode

has been chosen.

3.1 Multiplexed Pins

The CS49400 incorporates a large amount of

flexibility into a 144 pin package. The pins are

internally multiplexed to serve multiple purposes.

Some pins are designed to operate in one mode at

power up, and serve a different purpose when the

DSP is running. Other pins have functionality

which can be controlled by the application running

on the DSP. In order to better explain the behavior

of the part, the pins which are multiplexed have

been given multiple names. Each name is specific

to the pin’s operation in a particular mode.

In this document, pins will be referred to by their

functionality. Section 12 “Pin Description” on

page 86 describes each pin of the CS49400 and lists

all of its names. Please refer to this section when

exact pin numbers are in question.

3.2 Termination Requirements

The CS49400 incorporates open drain pins which

must be pulled high for proper operation.

FINTREQ

and INTREQ are always open drains

which requires a pull-up for proper operation.

Due to the internal, multiplexed design of the pins,

certain signals may or may not require termination

depending on the mode being used. If a parallel

host communication mode is not being used, all

parallel control pins must be terminated or driven

as these pins will come up as high impedance

inputs and will be prone to oscillation if they are

left floating. The specific termination requirements

may vary since the state of some of the GPIO pins

will determine the communication mode at the

rising edge of reset (please see Section 6 “Control”

on page 41 for more information). For the explicit

termination requirements of each communication

mode please see the typical connection diagrams.

Generally a 3.3k Ohm resistor is recommended for

open drain and mode select pins. A 10k Ohm

resistor is sufficient for all other unused inputs.

3.3 Phase Locked Loop Filter

The internal phase locked loop (PLL) of the

CS49400 requires an external filter. The topology

of this filter is shown in the typical connection

diagrams. The component values are shown below.

Care should be taken when laying out the filter

circuitry to minimize trace lengths and to avoid any

high frequency signals. Any noise coupled onto the

filter circuit will be directly coupled into the PLL,

which could affect performance.

Reference Designator Value

C1 2.2uF

C2 1200pF

C3 68pF

R1 3k Ohm

Table 1. PLL Filter Component Values

36

4. POWER

4.2 Analog Power Conditioning

The CS49400 requires a 2.5V digital power supply

for the core logic and 2.5V I/O and a 2.5V analog

power supply for the internal PLL. For systems

with external memory that runs on 3.3V, a 3.3V

digital power supply is required on the VDDSD

pins along with four digital grounds on VSSSD.

There are seven digital power pins, VDD1 through

VDD7, along with seven digital grounds, VSS1

through VSS7. There is one analog power pin,

PLLVDD, and one analog ground, PLLVSS. The

recommendations given below for decoupling and

power conditioning of the CS49400 will help to

ensure reliable performance.

4.1 Decoupling

It is necessary to decouple the power supply by

placing capacitors directly between the power and

ground of the CS49400. Each pair of power/ground

pins (VDD1/VSS1, etc.) should have its own

decoupling capacitors. The recommended

procedure is to place both a 0.1uF and a 1uF

capacitor as close as physically possible to each

power pin. The 0.1uF capacitor should be closest to

the part (typically 5mm or closer).

In order to obtain the best performance from the

CS49400’s internal PLL, the analog power supply

PLLVDD must be as noise-free as possible. A

ferrite bead and two capacitors should be used to

filter the VDD to generate PLLVDD. This power

scheme is shown in the typical connection

diagrams.

4.3 Ground

For two layer circuit boards, care should be taken

to have sufficient ground between the DSP and

parts in which it will be interfacing (DACs, ADCs,

S/PDIF Receivers, microcontrollers, and especially

external memory). Insufficient ground can degrade

noise margins between devices resulting in data

integrity problems.

4.4 Pads

The CS49400 has two different I/O voltage levels.

All signal pins not associated with the External

SRAM/SDRAM memory interface operate from

the 2.5V supply and are 3.3V tolerant. The external

SRAM/SDRAM memory interface operates at

3.3V only. However, if the external memory

interface is not used VDDSD1-4 may be connected

to 2.5V.

37

MICROCONTROLLER

SPI

INTERFACE

ADC OR SPDIF RX

ADC

ADCs

OSCILLATOR

+2.5 VA

C1

C2

NOTE:

1. A capacitor pair (.01uF and 0.1uF) must

be supplied for each power pin.

2. The digital supply (+2.5 VD) is filtered.

to obtain the analog suply (+2.5 VA).

+2.5 VD

3.3K

C

10K

RESISTOR PACK.

+

R1

C3

3456789

10

10K3.3K

3.3K

+

12

1uF

0.1uF

1321520

114

90

100

VDD3

VDD1

144

RESET

3

INTREQ,ABOOT

135

SCS

142

SCCLK

136

SCDIN

140

SCDOUT,SCDIO

16

FINTREQ

FCS

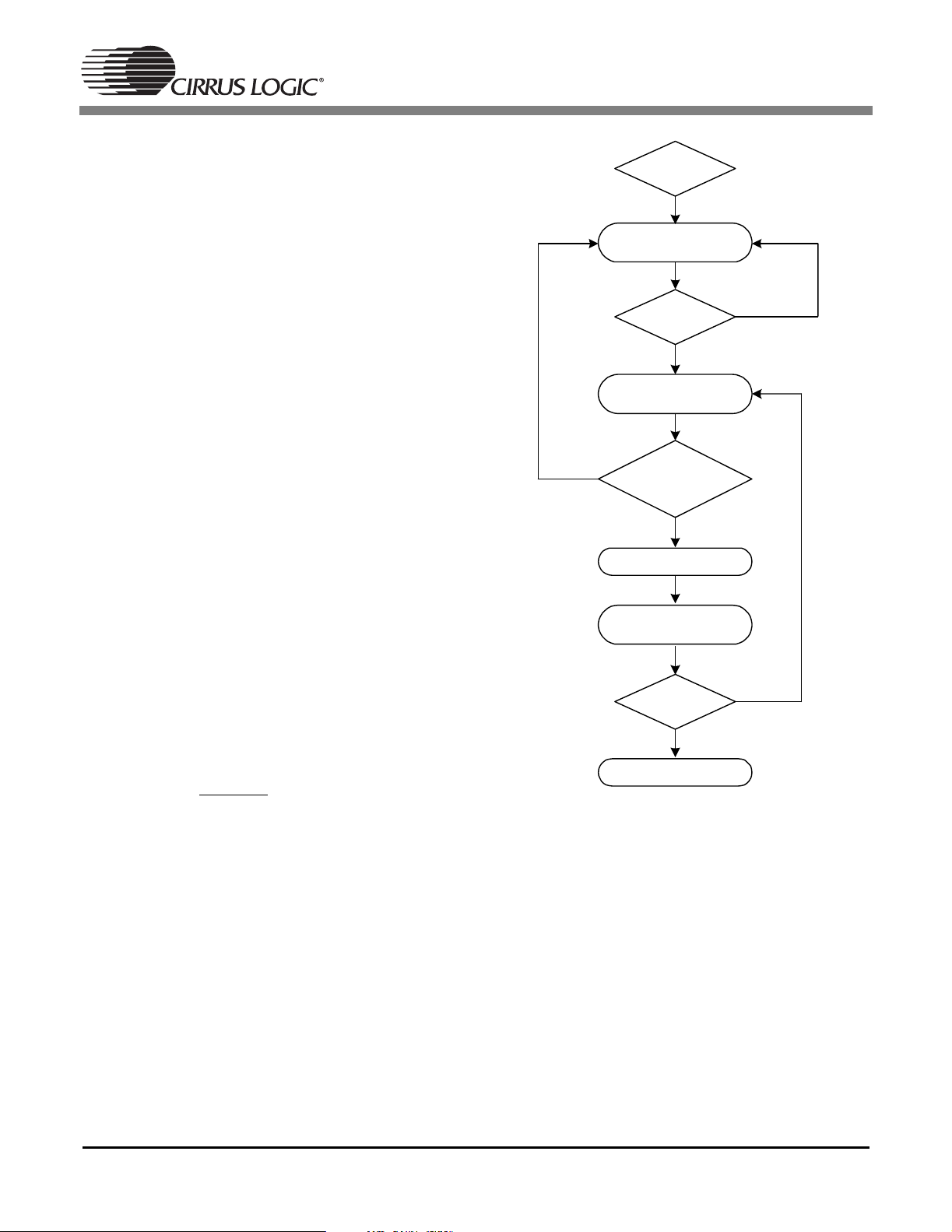

6

FAO,FSCCLK

4

FA1, FSCDIN

7

FHS2,FSCDIO,FSCDOUT

129

CS,GPIO9

141

HINBSY,GPIO8

120

WR,DS,GPIO10

121

RD,R/W,GPIO11

139

A1,GPIO12

130

AO,GPIO13

116

HDATA0,GPIO0

115

HDATA1,GPIO1

112

HDATA2,GPIO2

105

HDATA3,GPIO3

103

HDATA4,GPIO4

97

HDATA5, GPIO5

96

HDATA6,GPIO6

95

HDATA7,GPIO7

12

FHS0,FWR,FDS

13

FHS1,FRD,FR/ W

29

FDAT0

27

FDAT1

24

FDAT2

22

FDAT3

19

FDAT4

18

FDAT5

14

FDAT6

9

FDAT7

99

MCLK

117

CMPREQ,FLRCLKN2

111

CMPCLK,FSCLKN2

118

CMPDAT,FSDATAN2

119

FLRCLKN1

134

FSCLKN1,STCCLK2

131

FSDATAN1

85

LRCLKN, GPIO23

86

SCLKN,GPIO22

82

SDATAN0,GPIO24

81

SDATAN1,GPIO25

80

SDATAN2,GPIO26

79

SDATAN3,GPIO27

127

CLKIN,XTALI

126

CLKOUT,XTAL0

125 94

PLLVDD AUDATA5,GPIO29

123

FILT2

124

FILT1

128

CLKSEL

122

PLLVSS

143

USH2,CS_OUT,GPIO17

2

UHS1,GPIO19

1

UHS0,GPIO18

5

GPIO20

8

GPIO21

10K

VDD2

CS494XX

NC4

NC3

NC5

NC1

NC2

83

84

89

88

48

138

VDD4

VDD5

10

91

VDD6

VSS1

101

47uF 0.1uF

70

VDD7

VSS2

VSS3

113

133

FERRITE BEAD

42

58

51

SD_CS

VDDSD4

VDDSD1

VDDSD2

VDDSD3

SD_CLK_EN

SD_CLK_IN

SD_CLK_OUT

SD_DQM0

SD_DQM1

SD_CAS

SD_RAS

SD_WE

NV_CS,GPIO14

NV_OE,GPIO15

NV_WE,GPIO16

SD_ADDR0, EXTA0

SD_ADDR1, EXTA1

SD_ADDR2,EXTA2