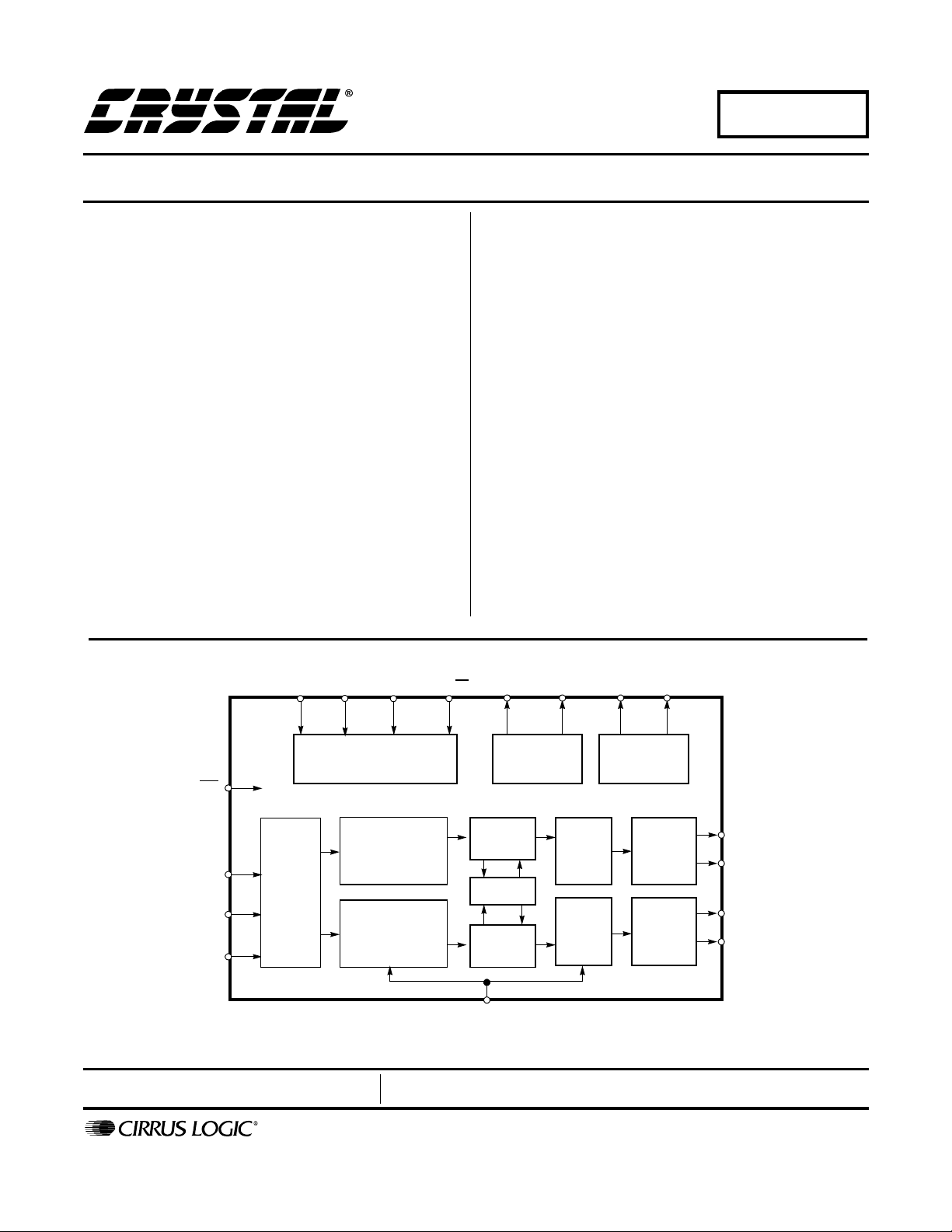

CS4391

24-Bit, 192 kHz Stereo DAC with Volume Control

Features

l Complete Stereo DAC System: Inte rpolation,

D/A, Output Analog Filtering

l 108 dB Dynamic Range

l 94 dB THD+N

l Direct Stream Digital Mode

l Low Clock Jitter Sensitivity

l +5 V to +3 V Power Supply

l ATAPI Mixing

l On-Chip Digital De-emphasis for 32, 44.1,

and 48 kHz

l Volume Control with Sof t Ramp

– 119 dB Attenuation

– 1 dB Step Size

– Zero Crossing Click-Free Transitions

l 36 mW with 3 V supply

l Direct Interface with 5 V to 1.8 V Logic

I

M1

(SDA/CDIN)

M3

M2

(SCL/CCLK) (AD0/CS)

M0

Description

The CS4391 is a comple te stereo digita l-to-analog s ystem including digital interpolation, fourth-order deltasigma digital-to-ana log c onv ers ion , digi tal de -e mph as is,

volume control, channel mixing and analog filtering. The

advantages of this archi tec ture i nc lud e: id eal di fferent ial

linearity, no distortion mechanisms due to resistor

matching errors, no linearity drift over time and temperature and a high tolerance to clock jitter.

The CS4391 accepts PCM data at sample rates from

2 kHz to 192 kHz, DSD audio dat a, consumes very little

power and operates over a wide power supply range.

These features are ideal for DVD, A/V receivers, CD and

set-top box systems.

ORDERING INFORMATION

CS4391-KZ 20-pin TSSOP -10 to 70 °C

CDB4391 Evaluation Board

AMUTEC

CMOUT

FILT+BMUTEC

MODE SELECT

(CONTROL PORT)

RST

SCLK

LRCK

SDATA

SERIAL

PORT

Preliminary Product Information

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

INTERPOLATION

FILTER

INTERPOLATOR

FILTER

MUTE CONTROL

VOLUME

CONTROL

MIXER

VOLUME

CONTROL

MCLK

EXTERNAL

∆Σ

DAC

∆Σ

DAC

REFERENCE

ANALOG

FILTER

ANALOG

FILTER

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright Cirrus Logic, Inc. 2000

(All Rights Reserved)

AOUTA+

AOUTA-

AOUTB+

AOUTB-

APR ‘00

DS335PP3

1

TABLE OF CONTENTS

1. CHARACTERISTICS/SPECIFICATIONS .......................................................................... 5

ANALOG CHARACTERISTICS......................................................................................5

DIGITAL CHARACTERISTICS.......................................................................................7

ABSOLUTE MAXIMUM RATINGS.................................................................................7

RECOMMENDED OPERATING CONDITIONS.............................................................7

SWITCHING CHARACTERISTICS - PCM MODES...................... .................................8

SWITCHING CHARACTERISTICS - DSD........................................... .......................... 9

SWITCHING CHARACTERISTICS - I

SWITCHING CHARACTERISTICS - SPI CONTROL PORT ............... ........................ 11

2. TYPICAL CONNECTION DIAGRAMS ................................... .........................................12

3. REGISTER QUICK REFERENCE .................................... .......................................... ..... 14

3.1 Mode Control 1 (address 01h)................................................................................14

3.2 Volume and Mixing Control (address 02h).............................................................15

3.3 Channel A Volume Control (address 03h)..............................................................15

3.4 Channel B Volume Control (address 04h)..............................................................15

3.5 Mode Control 2 (address 05h)................................................................................16

4. REGISTER DESCRIPTION .......................................... ...................................................17

4.1 Mode Control 1 - Address 01h................................................................................17

4.1.1 Auto-Mute (Bit 7) .............................................................................17

4.1.2 Digital Interface Formats (Bits 6:4) ..................................................17

4.1.3 De-Emphasis Control (Bits 3:2) .......................................................17

4.1.4 Functional Mode (Bits 1:0) ..............................................................17

4.2 Volume and Mixing Control (Address 02h).............................................................18

4.2.1 Channel A Volume = Channel B Volume (Bit 7) ..............................18

4.2.2 Soft Ramp or Zero Cross Enable (Bits 6:5) .....................................18

4.2.3 ATAPI Channel Mixing and Muting (Bits 4:0) ..................................18

4.3 Channel A Volume Control - Address 03h.............................................................. 1 8

4.4 Channel B Volume Control - Address 04h.............................................................. 1 9

4.4.1 Mute (Bit 7) ......................................................................................19

4.4.2 Volume Control (Bits 6:0) ................................................................19

4.5 Mode Control 2 - Address 05h................................................................................19

4.5.1 Invert Signal Polarity (Bits 7:6) ........................................................19

4.5.2 Control Port Enable (Bit 5) ..............................................................19

4.5.3 Power Down (Bit 4) .........................................................................19

4.5.4 AMUTEC = BMUTEC (Bit 3) ...........................................................19

4.5.5 Freeze (Bit 2) ..................................................................................20

4.5.6 Master Clock Divide (Bit 1) ..............................................................20

5. PIN DESCRIPTION - PCM DATA MODE ........................................................................ 21

Reset - RST

Interface Power - VL.....................................................................................................21

..................................................................................................................21

2

C CONTROL PORT........................................10

CS4391

Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at:

http://www.cirrus.com/corporate/contacts/

I2C is a registered trademark of Ph ilips Semiconductors.

Preliminary product inf o rmation describes products whi ch are i n production, but for wh i ch ful l characterization data is not yet available. Advance product infor-

mation describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best effort s to ensure that the information

contained in this document i s accurat e and reli able. However , t he infor mation is subje ct to chang e without noti ce and is provi d ed “AS IS” without warrant y of

any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other ri g ht s

of third parties. This document is the pro perty of Cirrus Logi c, Inc. and i mplie s no licen se under patents, copyrights, tr ademarks, or trade secre ts. No part of

this publication may be copied, reproduced , stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or

otherwise) without the pr i or writ ten consent of Cirrus Logic, Inc. Ite ms f rom any Ci rrus Logic website or disk may be printed for use by the user. However, no

part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical,

photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc.Furthermore, no part of this publication may be used as a basis for manufacture

or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing

in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

2 DS335PP3

Serial Audio Data - SDATA...........................................................................................21

Serial Clock - SCLK ......................................................................................................22

Left / Right Clock - LRCK..............................................................................................22

Master Clock - MCLK....................................................................................................22

Mode Select - M3, M2, M1 and M0 (Stand-alone Mode) .............................................22

Mode Select - M3 (Control Port Mode) ........................................................................22

Serial Control Interface Clock - SCL/CCLK (Control Port Mode).................................23

Serial Control Data I/O - SDA/CDIN (Control Port Mode).............................................23

Address Bit / Chip Select - AD 0 / CS

Positive Voltage Reference - FILT+..............................................................................23

Common Mode Voltage - CMOUT................................................................................23

Channel A and Channel B Mute Control - AMUTEC and BMUTEC .............................23

Differential Analog Output - AOUTB+, AOUTB- and AOUTA+, AOUTA-......................24

Analog Ground - AGND ................................................................................................24

Analog Power - VA........................................................................................................24

6. PIN DESCRIPTION - DSD MODE ....................................................................................25

DSD Audio Data - DSD_A and DSD_B.................................. .... ...................................25

DSD Mode - DSD_Mode...............................................................................................25

Master Clock - MCLK....................................................................................................25

DSD Serial Clock - DSD_SCLK ...................................................................................25

7. APPLICATIONS .............................................................................................................. .32

7.1 Recommended Power-up Sequence for Hardware Mode ....................................32

7.2 Recommended Power-up Sequence and A ccess to Contro l Port Mod e ..............32

7.3 Analog Output and Filtering ..................................................................................32

8. CONTROL PORT INTERFACE ........................................................................................33

8.1 SPI Mode ..............................................................................................................33

8.2 I2C Mode ..............................................................................................................33

9. PARAMETER DEFINITIONS ...........................................................................................37

Total Harmonic Distortion + Noise (THD+N).................................................................37

Dynamic Range.............................................................................................................37

Interchannel Isolation....................................................................................................37

Interchannel Gain Mismatch.........................................................................................37

Gain Error......................................................................................................................37

Gain Drift.......................................................................................................................37

10. REFERENCES ...............................................................................................................37

11. PACKAGE DIMENSIONS ...........................................................................................38

(Control Port Mode)...........................................23

CS4391

DS335PP3 3

LIST OF TABLES

Figure:1. Digital Interface Formats - PCM Modes .......................................................................26

Figure:2. Digital Interface Formats - DSD Mode .........................................................................26

Figure:3. De-Emphasis Mode Selection .....................................................................................26

Figure:4. Functional Mode Selection ...........................................................................................26

Figure:5. Soft Cross or Zero Cross Mode Selection ................................................................... 26

Figure:6. ATAPI Decode ................................... ...... ....... ...... ............................................. ..........27

Figure:7. Digital Volume Control ................................................................................................. 27

Figure:8. Single Speed (4 to 50 kHz sample rates) Common Clock Frequencies ......................28

Figure:9. Double Speed (50 to 100 kHz sample rates) Common Clock Frequencies ................28

Figure:10. Quad Speed (100 to 200 kHz sample rates) Common Clock Frequencies .............. 28

Figure:11. Single Speed (4 to 50 kHz) Digital Interface Format, Stand-Alone Mode Options .....28

Figure:12. Single Speed Only (4 to 50 kHz) De-Emphasis, Stand-Alone Mode Options ............ 28

Figure:13. Double Speed (50 to 100 kHz) Digital Interface Format, Stand-Alone Mode Options 28

Figure:14. Quad Speed (100 to 200 kHz) Digital Interface Format, Stand-Alone Mode Options 29

Figure:15. Direct Stream Digital (DSD), Stand-Alone Mode Options ..........................................29

Figure:16. Memory Address Pointer (MAP) ................................................................................34

LIST OF FIGURES

Figure 1. Serial Mode Input Timing .............................................. ....... ...... ...................................... 8

Figure 2. Direct Stream Digital - Serial Audio Input Timing.............................................................9

Figure 3. I

Figure 4. SPI Control Port Timing ............................. ............................................. ....... ...... ..........11

Figure 5. Typical Connection Diagram - PCM Mode.....................................................................12

Figure 6. Typical Connection Diagram - DSD Mode ..................................................................... 13

Figure 7. Format 0, Left Justified up to 24-Bit Data....................................................................... 30

Figure 8. Format 1, I2S up to 24-Bit Data .....................................................................................30

Figure 9. Format 2, Right Justified 16-Bit Data ............................................................................. 30

Figure 10. Format 3, Right Justified 24-Bit Data ...........................................................................30

Figure 11. Format 4, Right Justified 20-Bit Data. (Available in Control Port Mode only).............. 31

Figure 12. Format 5, Right Justified 18-Bit Data. (Available in Control Port Mode only)............... 31

Figure 13. De-Emphasis Curve.....................................................................................................31

Figure 14. ATAPI Block Diagram ..................................................................................................31

Figure 15. CS4391 Output Filter ................................................................................................... 32

Figure 16. Control Port Timing, SPI mode ....................................................................................34

Figure 17. Control Port Timing, I

Figure 18. Single-Speed Frequency Response ............................................................................35

Figure 19. Single-Speed Transition Band .....................................................................................35

Figure 20. Single-Speed Transition Band .....................................................................................35

Figure 21. Single-Speed Stopband Rejection ............................................................................... 35

Figure 22. Double-Speed Frequency Response...........................................................................35

Figure 23. Double-Speed Transition Band....................................................................................35

Figure 24. Double-Speed Transition Band....................................................................................36

Figure 25. Double-Speed Stopband Rejection..............................................................................36

2

C Control Port Timing.................................................................................................. 10

CS4391

2

C Mode.....................................................................................34

4 DS335PP3

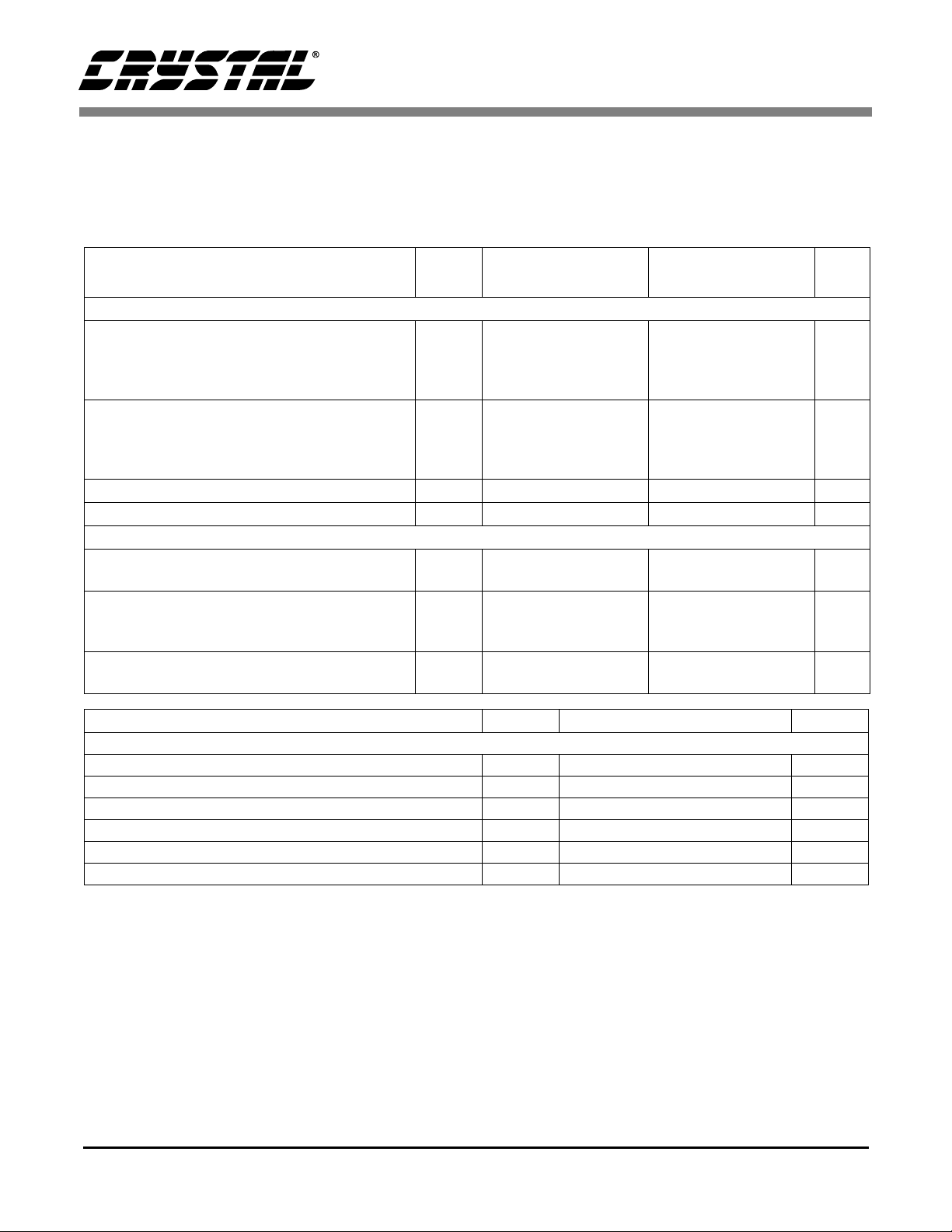

1. CHARACTERISTICS/SPECIFICATIONS

CS4391

ANALOG CHARACTERISTICS (T

put Sine Wave, 997 Hz; MCLK = 12.288 MHz; SCLK = 3.072 MHz, Sample Rate = 48, 96 or 192 kHz, 24-bit data,

Measurement Bandwidth 10 Hz to 20 kHz, unless otherwise specified. Test load R

Parameter

= 25° C; Logic "1" = VL = VA; Logic "0" = AG ND; Full -Scale Ou t-

A

= 5 kΩ, CL = 10 pF)

L

VA = 3 V VA = 5 V

Symbol Min Typ Max Min Typ Max Unit

Dynamic Performance

Dynamic Range (Note 17)

unweighted

A-Weighted

40 kHz Bandwidth A-Weighted

Total Harmonic Distortion + Noise (Note 17,2)

-20 dB

-60 dB

Idle Channel Noise / Signal-to-Noise Ratio - 105 - - 108 - dB

Interchannel Isolation (1 kHz) - 100 - - 100 - dB

THD+N

0 dB

97

100

-

-

-

-

102

105

99

-94

-82

-42

-

-

-

-89

-

-37

100

103

-

-

-

-

105

108

102

-94

-85

-45

-

-

-

-89

-

-40

dB

dB

dB

dB

dB

dB

Power Supplies

Power Supply Current normal operation

power-down state

Power Dissipation

normal operation

power-down

Power Supply Rejection Ratio (1 kHz) (Note 3)

(60 Hz)

IA + I

L

IA + I

L

PSRR -

-

-

-

-

-

12

30

36

0.09

60

40

TBD

-

TBD

-

-

-

-

-

-

-

-

-

17

60

85

0.3

60

40

TBD-mA

µA

TBD-mW

mW

-

-

dB

dB

Parameter Symbol Min Typ Max Units

Analog Output

Full Scale Differential Output Voltage TBD 1.1VA TBD Vpp

Common Mode Voltage CMOUT - 0.5VA - VDC

Interchannel Gain Mismatch - 0.1 - dB

Gain Drift - 100 - ppm/°C

AC-Load Resistance R

Load Capacitance C

DS335PP3 5

L

L

5--kΩ

--100pF

CS4391

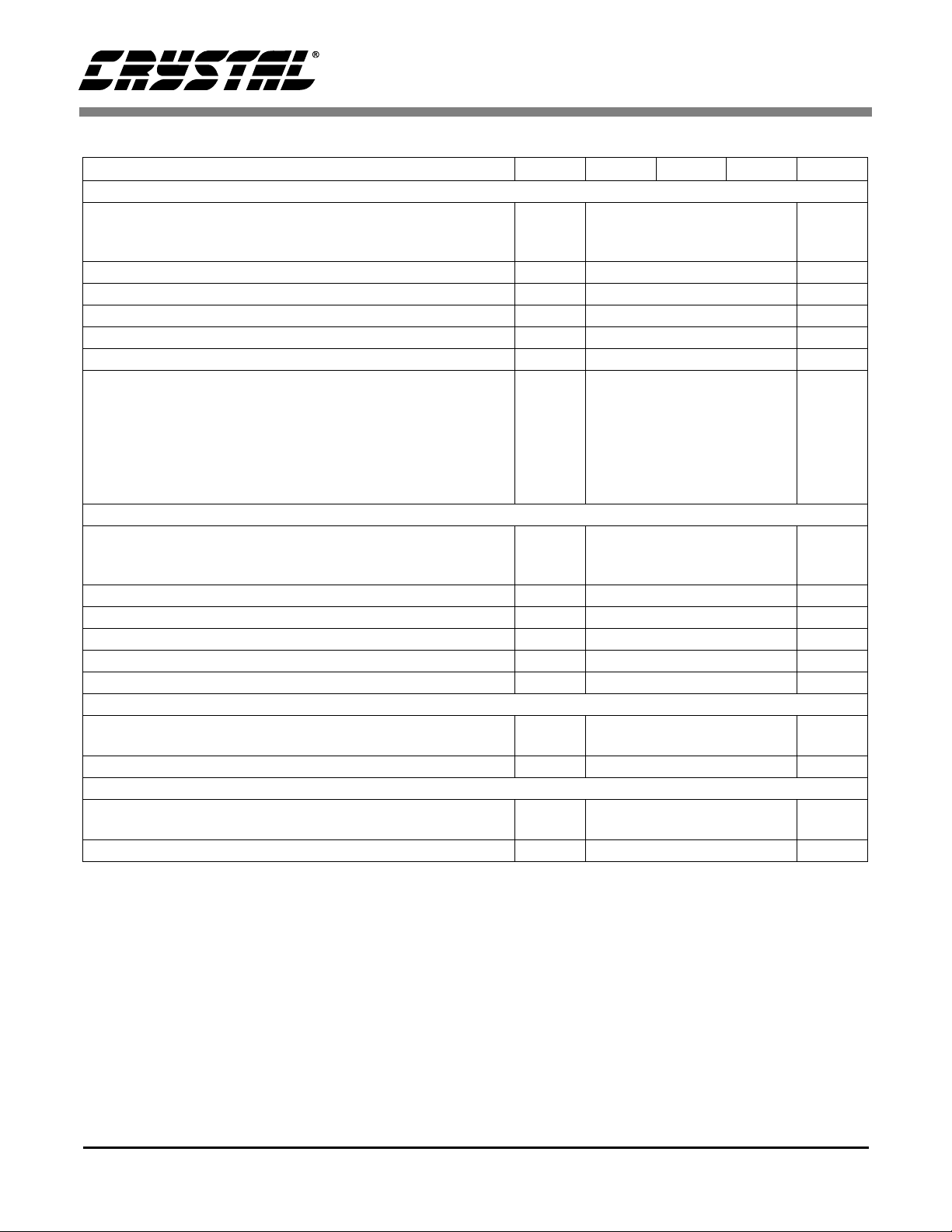

ANALOG CHARACTERISTICS (continued)

Parameter Symbol Min Typ Max Unit

Combined Digital and On-chip Analog Filter Response - Single Speed Mode

Passband (Note 3)

to -0.05 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz -.02 - +.035 dB

StopBand .5465 - - Fs

StopBand Attenuation (Note 5) 50 - - dB

Group Delay tgd - 9/Fs - s

Passband Group Delay Deviation 0 - 20 kHz - ±0.36/Fs - s

De-emphasis Error (Relative to 1 kHz)

Control Port Mode Fs = 32 kHz

Fs = 44.1 kHz

Fs = 48 kHz

Stand-Alone Mode Fs = 32 kHz

Fs = 44.1 kHz

Fs = 48 kHz

Combined Digital and On-chip Analog Filter Response - Double Speed Mode

Passband (Note 4)

to -0.1 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz -0.1 - 0 dB

StopBand .577 - - Fs

StopBand Attenuation (Note 5) 55 - - dB

Group Delay tgd - 9/Fs - s

Passband Group Delay Deviation 0 - 20 kHz - ±0.23/Fs - s

On-chip Analog Filter Response - Quad Speed Mode

Passband (Note 4)

to -3 dB corner 0 - 0.25 Fs

Frequency Response 10 Hz to 20 kHz -0.7 - 0 dB

On-chip Analog Filter Response - DSD Mode

Passband (Note 4)

to -3 dB corner 0 - 1.0 Fs

Frequency Response 10 Hz to 20 kHz -0.7 - 0 dB

0

0

-

-

-

-

-

-

0

0

-

-

-

-

-

-

-

-

-

-

.4535

.4998

+.2/-.1

+.05/-.14

+0/.22

TBD

+.05/-.14

TBD

.4621

.4982

Fs

Fs

dB

dB

dB

dB

dB

dB

Fs

Fs

Notes: 17. Triangular PDF dit h er e d dat a.

18. THD+N specifications for 48 kHz sample rates are made over a 20 kHz Bandwidth.

19. Valid with the recommended capacitor values on FILT+ and CMOUT as shown in Figure 1. Increasing

the capacitance will also increase the PSRR.

20. Response is clock dependent and will scale with Fs. Note that the response plots (Figures 17-24) have

been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs.

21. For Single-Speed Mode, the Measurement Bandwidth is 0.5465 Fs to 3 Fs.

For Double-Speed Mode, the Measurement Bandwidth is 0.577 Fs to 1.4 Fs.

6 DS335PP3

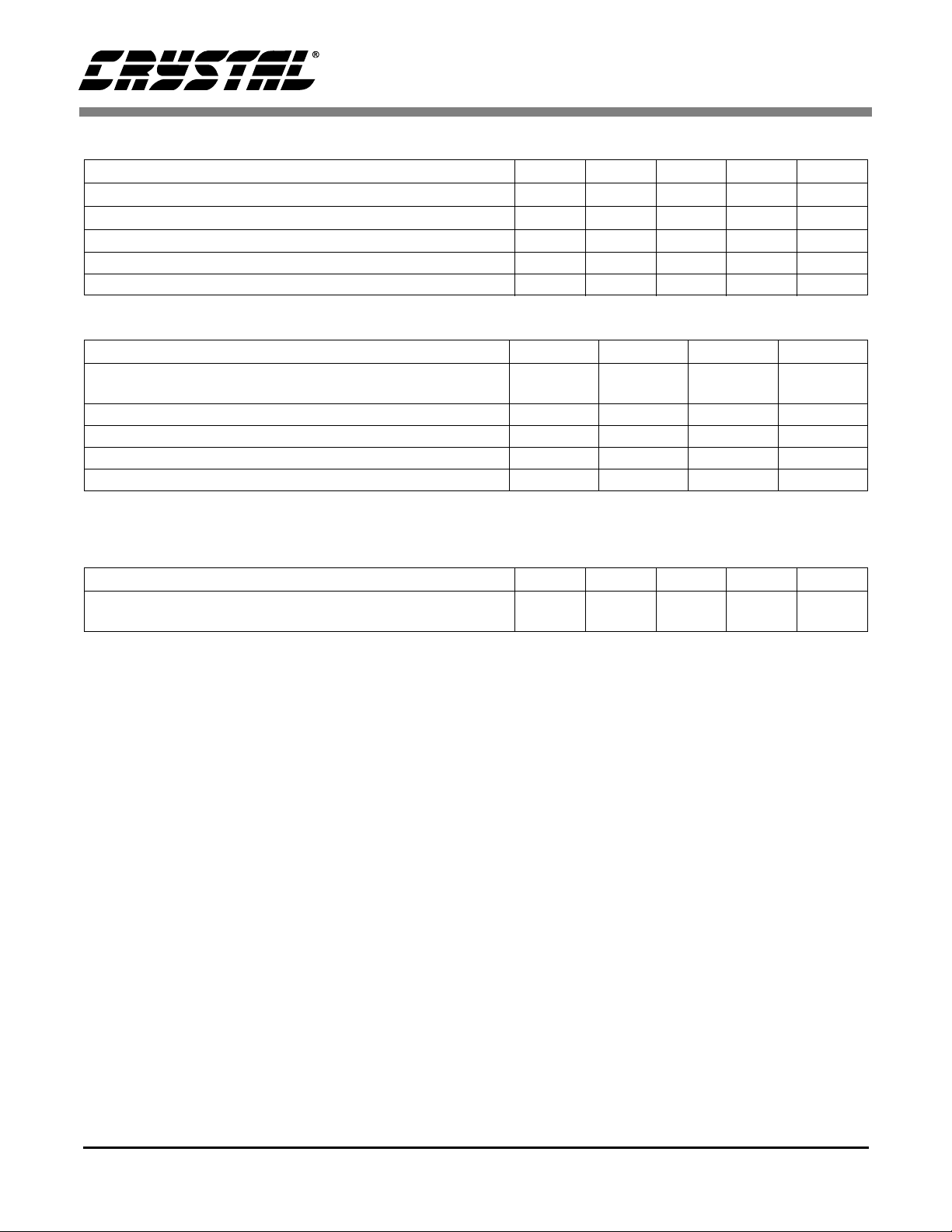

CS4391

DIGITAL CHARACTERISTICS (T

Parameters Symbol Min Typ Max Units

High-Level Input Voltage

Low-Level Input Voltage

Input Leakage Current I

Input Capacitance - 8 - pF

Maximum MUTEC Drive Current - 3 - mA

= 25° C)

A

V

IH

V

IL

in

70% - - VL

- 20% VL

--±10µA

ABSOLUTE MAXIMUM RATINGS (AGND = 0 V; all voltages with respect to ground.)

Parameters Symbol Min Max Units

DC Power Supply VA

VL

Input Current, Any Pin Except Supplies I

Digital Input Voltage V

Ambient Operating Temperature (power applied) T

Storage Temperature T

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is

not guaranteed at these extremes.

in

IND

A

stg

-0.3

-0.3

- ±10 mA

-0.3 VL+0.4 V

-55 125 °C

-65 150 °C

6.0

VA

V

V

RECOMMENDED OPERATING CONDITIONS (AGND = 0V; all voltages with respect to ground.)

Parameters Symbol Min Typ Max Units

DC Power Supply VA

VL

2.7

1.8

5.0

-

5.5

VA

V

V

DS335PP3 7

CS4391

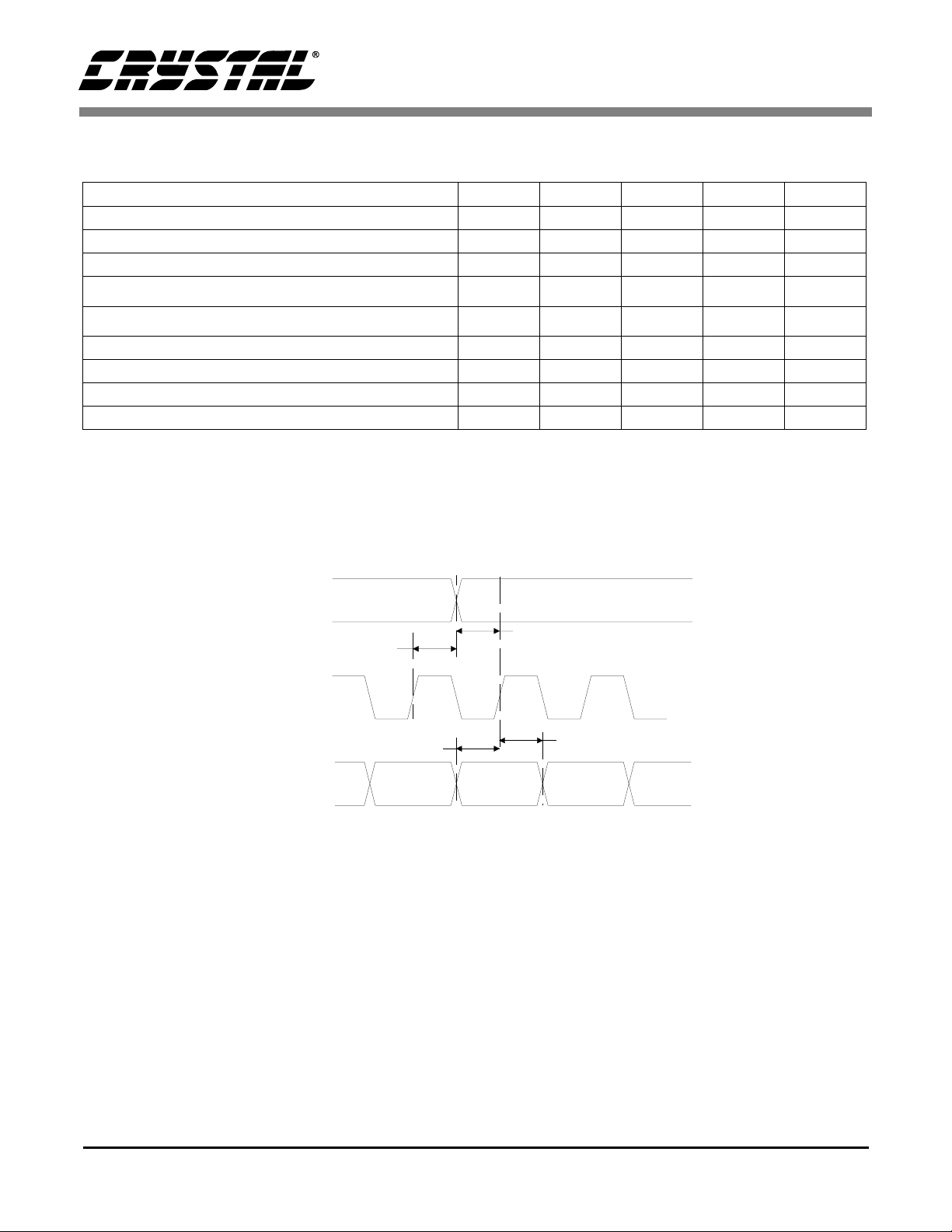

SWITCHING CHARACTERISTICS - PCM MODES (T

= -10 to 70° C; VL = 5.5 to 1.8 Volts;

A

Inputs: Logic 0 = 0 V, Logic 1 = VL, CL = 20 pF)

Parameters Symbol Min Typ Max Units

Input Sample Rate Fs 4 - 200 kHz

LRCK Duty Cycle 45 50 55 %

MCLK Duty Cycle 405060%

SCLK Frequency

SCLK Frequency Note 22

SCLK rising to LRCK edge delay t

SCLK rising to LRCK edge setup time t

SDATA valid to SCLK rising setup time t

SCLK rising to SDATA hold time t

slrd

slrs

sdlrs

sdh

-

20 - - ns

20 - - ns

20 - - ns

20 - - ns

-MCLK/2Hz

-MCLK/4Hz

Notes: 22. This serial clock is available only in Control Port Mode when the MCLK Divide bit is enabled.

LRCK

SCLK

SDATA

t

t

slrd

t

sdlrs

slrs

t

sdh

Figure 1. Serial Mode Input Timing

8 DS335PP3

CS4391

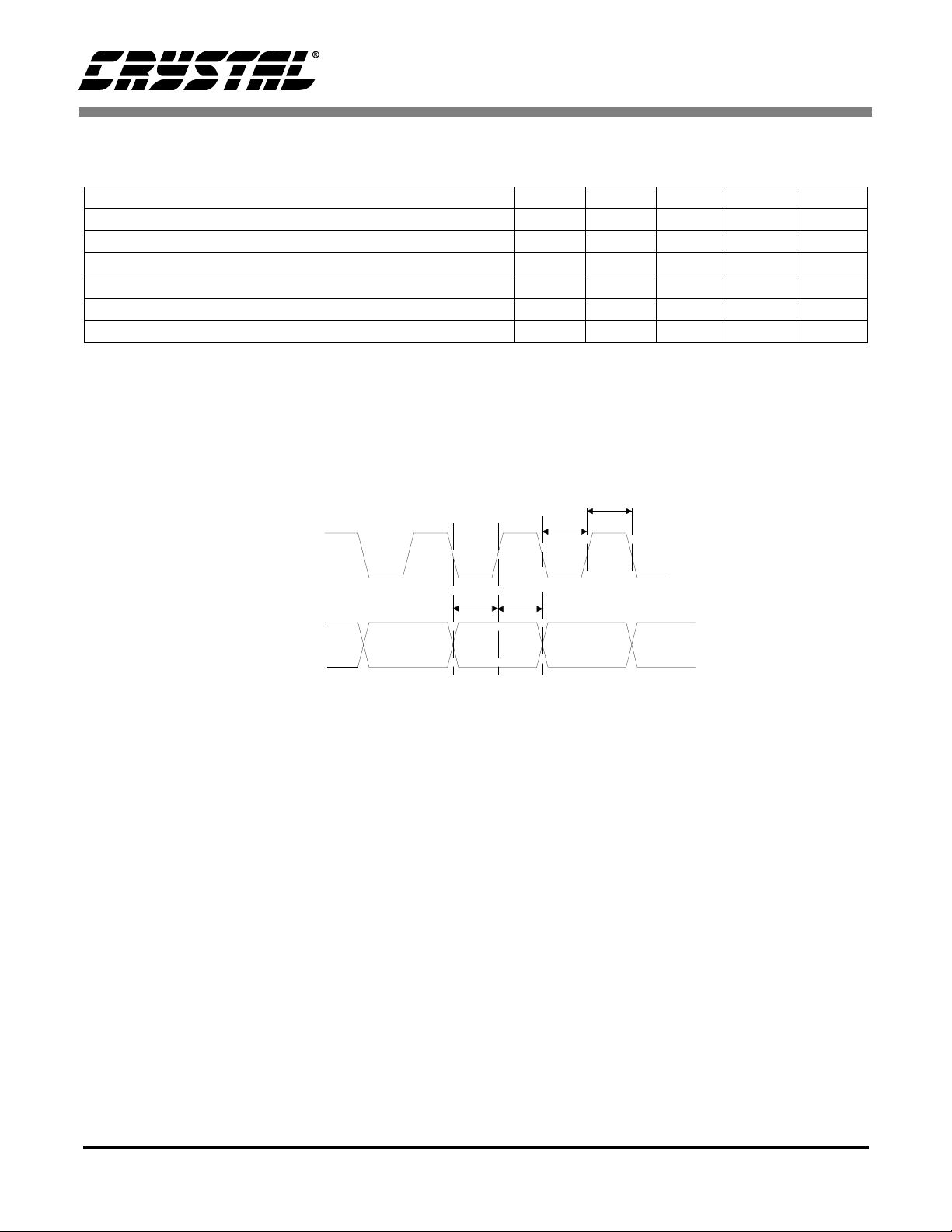

SWITCHING CHARACTERISTICS - DSD (T

Logic 1 = VL = 5.5 to 1.8 Volts; C

=20pF)

L

= -10 to 70° C; Logic 0 = AGND = DGND;

A

Parameter Symbol Min Typ Max Unit

MCLK Duty Cycle 405060%

SCLK Pulse Width Low t

SCLK Pulse Width High t

SCLK Period t

SDIN valid to SCLK rising setup time t

SCLK rising to SDIN hold time t

SCLK

t

sdlrstsdh

sclkl

sclkh

sclkw

sdlrs

sdh

t

sclkl

TBD - - ns

TBD - - ns

TBD

--ns

TBD - - ns

TBD - - ns

t

sclkh

SDATA

Figure 2. Direct Stream Digital - Serial Audio Input Timing

DS335PP3 9

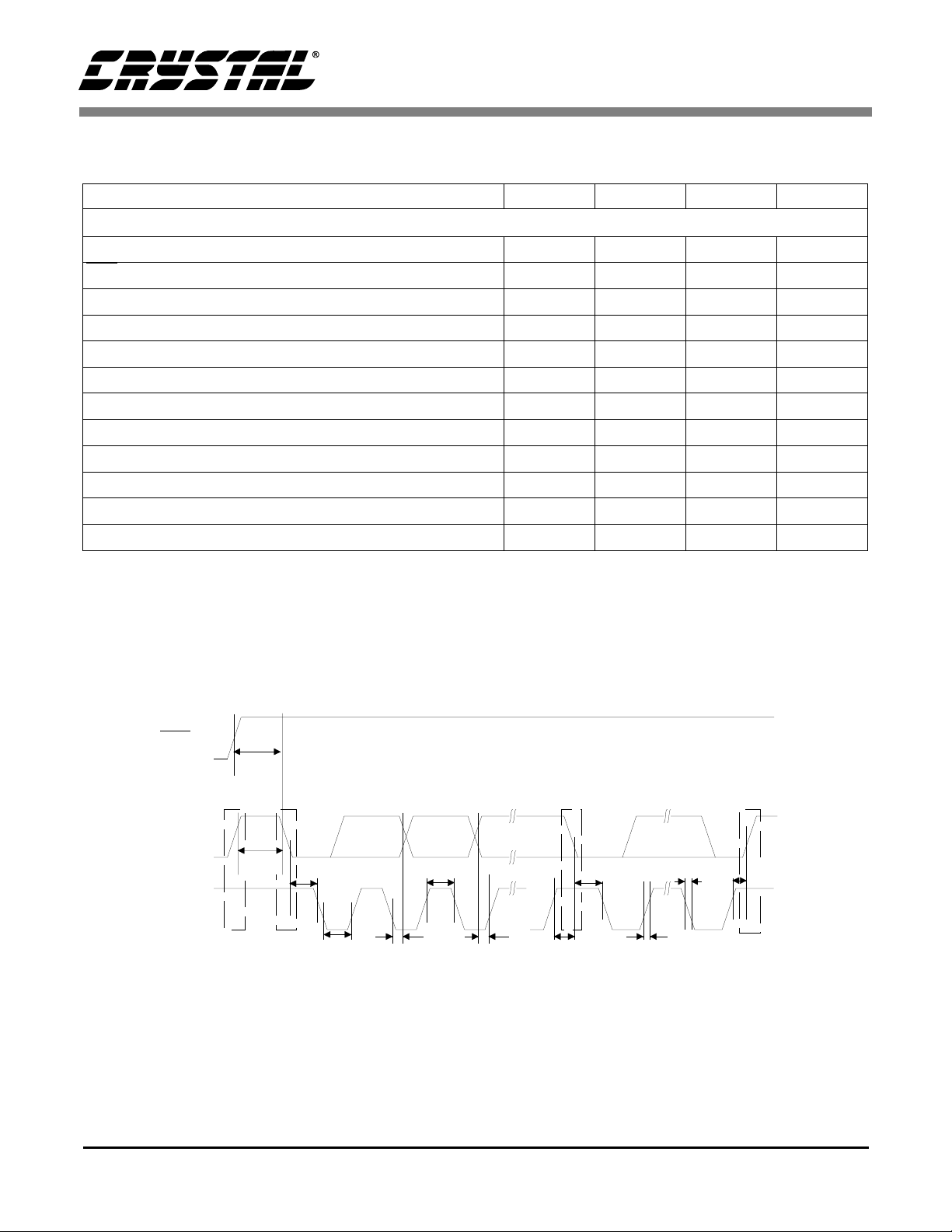

SWITCHING CHARACTERISTICS - I2C CONTROL PORT

(TA = 25° C; VL = 5.5 to 1.8 Volts; Inputs: logic 0 = AGND, logic 1 = VL, CL = 30 pF)

Parameter Symbol Min Max Unit

I2C® Mode

SCL Clock Frequency f

Rising Edge to Start t

RST

Bus Free Time Between Transmissions t

Start Condition Hold Time (prior to first clock pulse) t

Clock Low time t

Clock High Time t

Setup Time for Repeated Start Condition t

SDA Hold Time from SCL Falling (Note 23) t

SDA Setup time to SCL Rising t

Rise Time of Both SDA and SCL Lines t

Fall Time of Both SDA and SCL Lines t

Setup Time for Stop Condition t

scl

irs

buf

hdst

low

high

sust

hdd

sud

r

f

susp

-100KHz

500 - ns

4.7 - µs

4.0 - µs

4.7 - µs

4.0 - µs

4.7 - µs

0-µs

250 - ns

-1µs

-300ns

4.7 - µs

CS4391

Notes: 23. Data must be held for sufficient time to bridge the 300 ns transition time of SCL.

RST

t

SDA

SCL

irs

Stop Start

t

buf

t

t

hdst

low

t

hdd

t

high

t

sud

Repeated

Start

t

sust

t

hdst

t

f

t

r

Figure 3. I2C Control Port Timing

Stop

t

susp

10 DS335PP3

SWITCHING CHARACTERISTICS - SPI CONTROL PORT

(TA = 25° C; VL = 5.5 to 1.8 Volts; Inputs: logic 0 = AGND, logic 1 = VL, CL = 30 pF)

Parameter Symbol Min Max Unit

SPI Mode

CCLK Clock Frequency f

Rising Edge to CS Falling t

RST

CCLK Edge to CS

High Time Between Transmissions t

CS

Falling to CCLK Edge t

CS

Falling (Note 24) t

CCLK Low Time t

CCLK High Time t

CDIN to CCLK Rising Setup Time t

CCLK Rising to DATA Hold Time (Note 25) t

Rise Time of CCLK and CDIN (Note 26) t

Fall Time of CCLK and CDIN (Note 26) t

sclk

srs

spi

csh

css

scl

sch

dsu

dh

r2

f2

-6MHz

500 - ns

500 - ns

1.0 - µs

20 - ns

66 - ns

66 - ns

40 - ns

15 - ns

-100ns

-100ns

CS4391

Notes: 24. t

25. Data must be held for sufficient time to bridge the transition time of CCLK.

26. For F

only needed before first falling edge of CS after RST rising edge. t

spi

< 1 MHz

SCK

RST

CS

CCLK

CDIN

t

srs

t

t

css

spi

tr2t

t

t

scl

t

f2

dsu

sch

t

dh

= 0 at all other times.

spi

t

csh

Figure 4. SPI Control Port Timing

DS335PP3 11

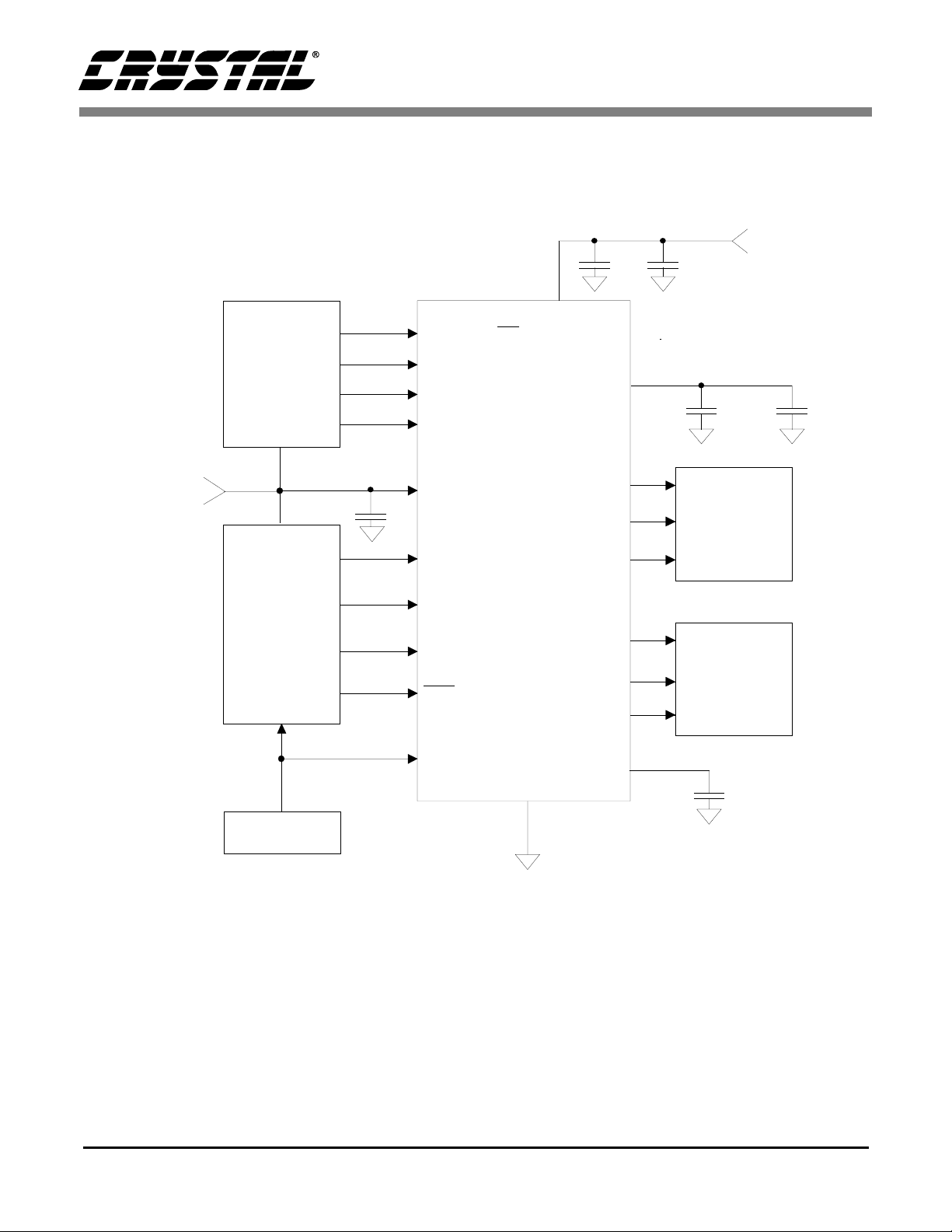

2. TYPICAL CONNECTION DIAGRAMS

10

M0 (AD0/CS)

9

M1 (SDA/

8

M2 (SCL/CC LK)

7

M3

2

VL

5

LRCK

Logic Power

+5V to 1.8V

Mode

Select

(Control Port)

*

0.1 µf

17

CDIN

)

CS4391

VA

FILT+

AOUTA-

AMUTEC

AOUTA+

0.1 µf

11

19

20

18

+

1.0 µf

0.1 µf 1.0 µf

Analog

Conditioning

&

Mute

CS4391

+5V to +3V

Analog

+

Audio

Data

Processor

*

External Clock

Figure 5. Typical Connection Diagram - PCM Mode

* A high logic level for all digital inputs should not exceed VL.

4

3

1

6

SCLK

SDATA

RST

MCLK

AOUTB-

BMUTEC

AOUTB+

CMOUT

AGND

16

14

13

15

12

Analog

Conditioning

&

Mute

1.0 µf

+

12 DS335PP3

Loading...

Loading...