Cirrus Logic CS4382A User Manual

CS4382A

114 dB, 192 kHz 8-Channel D/A Converter

Features

Advanced Multi-bit Delta Sigma Architecture

24-bit Conversion

Up to 192 kHz Sample Rates

114 dB Dynamic Range

-100 dB THD+N

Direct Stream Digital

On-chip 50 kHz Filter

Matched PCM and DSD Analog Output Levels

Selectable Digital Filters

Volume Control with 1 dB Step Size and Soft

Ramp

Low Clock-jitter Sensitivity

+5 V Analog Supply, +2.5 V Digital Supply

Separate 1.8 to 5 V Logic Supplies for the

Control & Serial Ports

®

(DSD™) Mode

Description

The CS4382A is a complete 8-channel digi tal-to-analog

system. This D/A system includes digital de-emphasis,

1 dB step size volume control, ATAPI channel mixing,

selectable fast and slow digital interpolation filters followed by an oversampled, multi-bit delta-sigma

modulator which includes mismatch shaping technology that eliminates distortion due to capacitor mismatch.

Following this stage is a multi-element switched capacitor stage and low-pass filter with differential analog

outputs.

The CS4382A also has a proprietary DSD processor

which allows for 50 kHz on-chip filtering without an intermediate decimation stage. The CS4382A is available

in a 48-pin LQFP package in both Commercial (-40°C to

+85°C) and Automotive grades (-40°C to +105°C). The

CDB4382A Customer Demonstration board is also

available for device evaluation and implementation suggestions. Please see “Ordering Information” on page 48

for complete details.

The CS4382A accepts PCM data at sample rates from

4 kHz to 216 kHz, DSD audio data, and delivers excellent sound quality. These featu res are ideal for multichannel audio systems including SACD players, A/V receivers, digital TV’s, mixing consoles, effects

processors, sound cards, and automotive audio

systems.

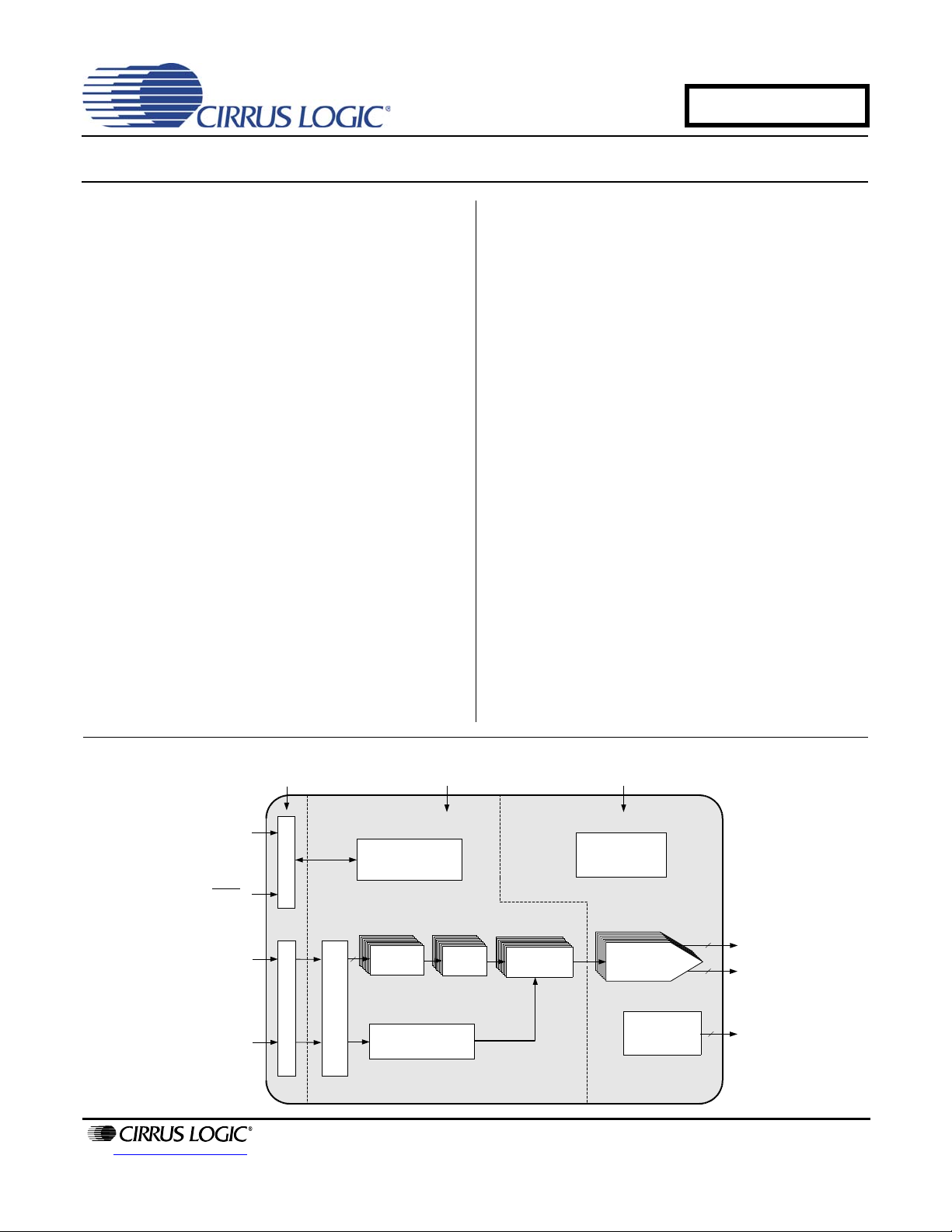

Control & Serial Audio Port

Supplies = 1.8 V to 5 V

Hardware Mode or

2

C/SPI Software Mode

I

Control Data

Reset

PCM Serial

Audio Input

DSD Audio

Inpu t

http://www.cirrus.com

Digital Supply = 2.5 V

Register/Hardware

Configuration

Level Translator

Volume

Controls

8

DSD Processor

Level Translator

Se ria l Inte rface

-50 kH z filter

Copyright © Cirrus Logic, Inc. 2009

Digital

F ilters

(All Rights Reserved)

Multi-bit ∆Σ

Modulators

Analog Supply = 5 V

Inte rnal V olta ge

Reference

Switch-Cap

DAC and

Analog F ilters

E xterna l M ute

Control

8

8

2

Differential

Outputs

Mute Signals

JAN '09

DS618F2

TABLE OF CONTENTS

1. PIN DESCRIPTION ................................................................................................................................. 6

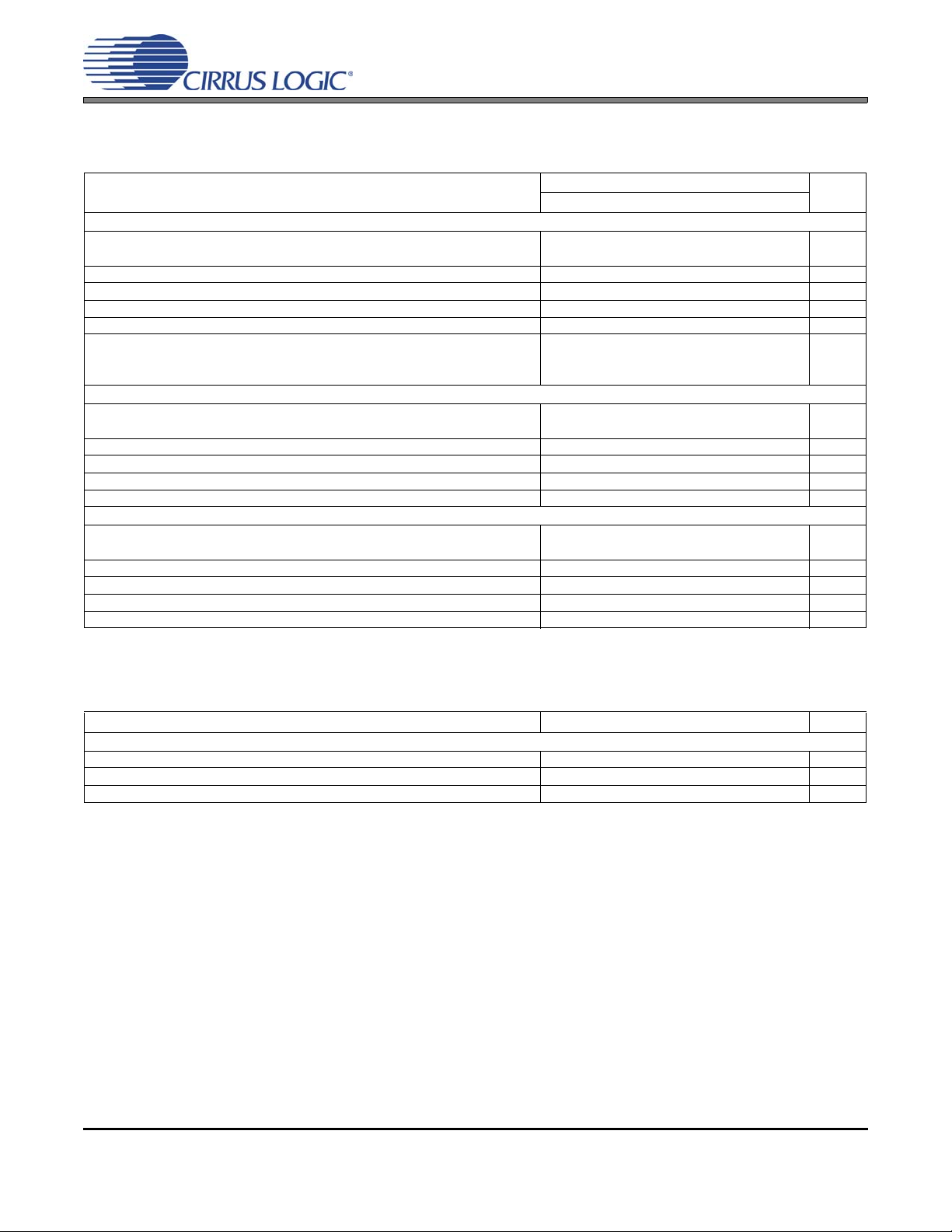

2. CHARACTERISTICS AND SPECIFICATIONS ...................................................................................... 8

RECOMMENDED OPERATING CONDITIONS .................................................................................... 8

ABSOLUTE MAXIMUM RATINGS ........................................................................................................ 8

DAC ANALOG CHARACTERISTICS - COMMERCIAL (-CQZ) ............................................................. 9

DAC ANALOG CHARACTERISTICS - AUTOMOTIVE (-DQZ) ........................................................... 10

POWER AND THERMAL CHARACTERISTICS .................................................................................. 11

COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE ...................................... 12

COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE ...................................... 13

DSD COMBINED DIGITAL & ON-CHIP ANALOG FILTER RESPONSE ............................................ 13

DIGITAL CHARACTERISTICS ...................................................................... ... ... .... ... ... ...................... 14

SWITCHING CHARACTERISTICS - PCM .......................................................................................... 15

SWITCHING CHARACTERISTICS - DSD ........................................................................................... 16

SWITCHING CHARACTERISTICS - CONTROL PORT - I²C FORMAT ............................................. 17

SWITCHING CHARACTERISTICS - CONTROL PORT - SPI FORMAT ................................ ... ... ... ... 18

3. TYPICAL CONNECTION DIAGRAM .................................................................................................. 19

4. APPLICATIONS ................................................................................................................................... 21

4.1 Master Clock .................................................................................................................................. 21

4.2 Mode Select ................................................................................................................................... 21

4.3 Digital Interface Formats ................................................................................................................ 23

4.4 Oversampling Modes ..................................................................................................................... 24

4.5 Interpolation Filter .......................................................................................................................... 24

4.6 De-emphasis .................................................................................................................................. 24

4.7 ATAPI Specification ....................................................................................................................... 25

4.8 Direct Stream Digital (DSD) Mode ................................. ... .... ... ... ... ... .... ... ... ... .... ... ... ... ................... 26

4.9 Grounding and Power Supply Arrangements ................................................................................ 26

4.9.1 Capacitor Placement ............................................................................................................. 26

4.10 Analog Output and Filtering .................. .... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ............................ 26

4.11 Mute Control ............................................................. ... ... .... ... ... ... ... ............................................. 27

4.12 Recommended Power-Up Sequence .......................................................................................... 28

4.12.1 Hardware Mode ................................................................................................................... 28

4.12.2 Software Mode .................................................................................................................... 28

4.13 Recommended Procedure for Switching Operational Modes ...................................................... 29

4.14 Control Port Interface ... ... ... ... .... ... ... ... .......................................................................................... 29

4.14.1 MAP Auto Increment ........................................................................................................... 29

4.14.2 I²C Mode ................................. ... ... .... ... ....................................... ... ... ... .... ............................ 29

4.14.2.1 I²C Write ................................ ... ... ... .... ... ... ... .... ...................................... ... .... ... ......... 29

4.14.2.2 I²C Read ........................... ....................................... ... .... ... ... ................................... 30

4.14.3 SPI Mode ............................................................................................................................. 30

4.14.3.1 SPI Write ............................... ... ... ... .... ... ... ... .... ...................................... ... .... ... ......... 30

4.15 Memory Address Pointer (MAP) ................................................................................................. 31

4.16 INCR (Auto Map Increment Enable) ............................................................................................ 31

4.16.1 MAP4-0 (Memory Address Pointer) .................... ... .... ... ... ... ... .... ......................................... 31

5. REGISTER QUICK REFERENCE ........................................................................................................ 32

6. REGISTER DESCRIPTION .................................................................................................................. 33

6.1 Mode Control 1 (Address 01h) ....................................................................................................... 33

6.1.1 Control Port Enable (CPEN) ............................ ... ... ... ....................................... ... ... .... ... ... ...... 33

6.1.2 Freeze Controls (FREEZE) ................................................................................................... 33

6.1.3 Master Clock Divide Enable (MCLKDIV) ............................ ....................................... ............ 33

6.1.4 DAC Pair Disable (DACx_DIS) ................. ... .... ... ... ... .... ... ... ... ... ....................................... ... ...33

6.1.5 Power Down (PDN) ............................................................................................................... 34

6.2 Mode Control 2 (Address 02h) ....................................................................................................... 34

CS4382A

2 DS618F2

CS4382A

6.2.1 Digital Interface Format (DIF) ................................................................................................ 34

6.3 Mode Control 3 (Address 03h) .................................... ... ... .......................................... ... .... ............ 35

6.3.1 Soft Ramp and Zero Cross Control (SZC) ............ ... .... ... ... ... ... .... ...................................... ... 35

6.3.2 Single Volume Control (SNGLVOL) ...................................................................................... 36

6.3.3 Soft Volume Ramp-Up After Error (RMP_UP) ...................................................................... 36

6.3.4 Mutec Polarity (MUTEC+/-) ................................................................................................... 36

6.3.5 Auto-Mute (AMUTE) .............................................................................................................. 36

6.3.6 Mutec Pin Control (MUTEC) .................................................................................................. 37

6.4 Filter Control (Address 04h) ........................................................................................................... 37

6.4.1 Interpolation Filter Select (FILT_SEL) ...................................................................................37

6.4.2 De-Emphasis Control (DEM) ................................................................................................. 37

6.4.3 Soft Ramp-Down Before Filter Mode Change (RMP_DN) ....... .... ...................................... ... 37

6.5 Invert Control (Address 05h) .......................................................................................................... 38

6.5.1 Invert Signal Polarity (Inv_Xx) ............................................................................................... 38

6.6 Mixing Control Pair 1 (Channels A1 & B1)(Address 06h)

Mixing Control Pair 2 (Channels A2 & B2)(Address 09h)

Mixing Control Pair 3 (Channels A3 & B3)(Address 0Ch)

Mixing Control Pair 4 (Channels A4 & B4)(Address 0Fh) .................................................................... 38

6.6.1 Channel A Volume = Channel B Volume (A=B) .................................................................... 38

6.6.2 ATAPI Channel Mixing and Muting (ATAPI) .......................................................................... 39

6.6.3 Functional Mode (FM) ........................................................................................................... 40

6.7 Volume Control (Addresses 07h, 08h, 0Ah, 0Bh, 0Dh, 0Eh) ........ ... .... ... ... ... ................................ 40

6.7.1 Mute (MUTE) ......................................................................................................................... 40

6.7.2 Volume Control (XX_VOL) .................................................................................................... 41

6.8 Chip Revision (Address 12h) ......................................................................................................... 41

6.8.1 Part Number ID (PART) [Read Only] .................................................................................... 41

6.8.2 Revision ID (REV) [Read Only] ............................................................................................. 41

7. FILTER PLOTS ..................................................................................................................................... 42

8. PARAMETER DEFINITIONS ................................................................................................................ 46

9. PACKAGE DIMENSIONS .................................................................................................................... 47

10. ORDERING INFORMATION ....... .... ... ... ....................................... ... ... ... .... ... ... ... .... ... ... ... ... ................ 48

11. REFERENCES ....................... ... ... .... ... ... ... ... .... ... ... ....................................... ... ... .... ... ... ...................... 48

12. REVISION HISTORY ................................ ... ....................................... ... .... ... ... ... .... ... ......................... 49

DS618F2 3

LIST OF FIGURES

Figure 1.Serial Audio Interface Timing ... ... ... ... .......................................... ... .... ... ... ... .... ... ... ... ................... 15

Figure 2.Direct Stream Digital - Serial Audio Input Timing ........................................................................ 16

Figure 3.Control Port Timing - I²C Format ................................................................. .... ... ......................... 17

Figure 4.Control Port Timing - SPI Format ............................. ... ... .... ... ... ... ................................................ 18

Figure 5.Typical Connection Diagram, Software Mode ................ ............. ............. ............. ............. .........19

Figure 6.Typical Connection Diagram, Hardware Mode ........................................................................... 20

Figure 7.Format 0 - Left-Justified up to 24-bit Data .................................................................................. 23

Figure 8.Format 1 - I²S up to 24-bit Data .................................................................................................. 23

Figure 9.Format 2 - Right-Justified 16-bit Data ......................................................................................... 23

Figure 10.Format 3 - Right-Justified 24-bit Data ....................................................................................... 23

Figure 11.Format 4 - Right-Justified 20-bit Data ....................................................................................... 24

Figure 12.Format 5 - Right-Justified 18-bit Data ....................................................................................... 24

Figure 13.De-Emphasis Curve .................................. ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ............................ 25

Figure 14.ATAPI Block Diagram (x = channel pair 1, 2, 3, or 4) ............... ... .... ... ... ... .... ............................ 25

Figure 15.Full-Scale Output ............... .... ... ... ... ... .... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ......................... 27

Figure 16.Recommended Output Filter ..................................................................................................... 27

Figure 17.Recommended Mute Circuitry ........................ .... ... ... ... .... ... .......................................... ... ......... 28

Figure 18.Control Port Timing, I²C Mode .................................................................................................. 30

Figure 19.Control Port Timing, SPI Mode ................................................................................................. 31

Figure 20.Single-Speed (fast) Stopband Rejection ................................................................................... 42

Figure 21.Single-Speed (fast) Transition Band ......................................................................................... 42

Figure 22.Single-Speed (fast) Transition Band (detail) ............................................................................. 42

Figure 23.Single-Speed (fast) Passband Ripple ....................................................................................... 42

Figure 24.Single-Speed (slow) Stopband Rejection ................................................................................. 42

Figure 25.Single-Speed (slow) Transition Band ........................................................................................ 42

Figure 26.Single-Speed (slow) Transition Band (detail) ............................................................................ 43

Figure 27.Single-Speed (slow) Passband Ripple ...................................................................................... 43

Figure 28.Double-Speed (fast) Stopband Rejection ................................................................................. 43

Figure 29.Double-Speed (fast) Transition Band ........................................................................................ 43

Figure 30.Double-Speed (fast) Transition Band (detail) ............................................................................ 43

Figure 31.Double-Speed (fast) Passband Ripple ...................................................................................... 43

Figure 32.Double-Speed (slow) Stopband Rejection ...... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ...................... 44

Figure 33.Double-Speed (slow) Transition Band ............ .... ... ... ... .... ... ... ....................................... ... ... ...... 44

Figure 34.Double-Speed (slow) Transition Band (detail) .......................................................................... 44

Figure 35.Double-Speed (slow) Passband Ripple .......... .... ... ... ... .... ... ... ....................................... ... ... ...... 44

Figure 36.Quad-Speed (fast) Stopband Rejection . ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ...... 44

Figure 37.Quad-Speed (fast) Transition Band ... .......................................... .... ... ... ... .... ... ... ... ... ................ 44

Figure 38.Quad-Speed (fast) Transition Band (detail) ..........................................................................

Figure 39.Quad-Speed (fast) Passband Ripple ........................................................................................ 45

Figure 40.Quad-Speed (slow) Stopband Rejection ................................................................................... 45

Figure 41.Quad-Speed (slow) Transition Band ......................................................................................... 45

Figure 42.Quad-Speed (slow) Transition Band (detail) ............................................................................. 45

Figure 43.Quad-Speed (slow) Passband Ripple ....................................................................................... 45

CS4382A

.... 45

4 DS618F2

LIST OF TABLES

Table 1. Common Clock Frequencies ....................................................................................................... 21

Table 2. Digital Interface Format, Stand-Alone Mode Options ..... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... ... 22

Table 3. Mode Selection, Stand-Alone Mode Options ........... ... ... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ... .. .22

Table 4. Direct Stream Digital (DSD), Stand-Alone Mode Options ........................................ ... .... ... ... ... ... 22

Table 5. Digital Interface Formats - PCM Mode ........................................................................................ 34

Table 6. Digital Interface Formats - DSD Mode ........................................................................................ 35

Table 7. ATAPI Decode ............................ ... ... ....................................... ... ... .... ... ... ... .... ... ... ...................... 39

Table 8. Example Digital Volume Settings ................................................................................................ 41

CS4382A

DS618F2 5

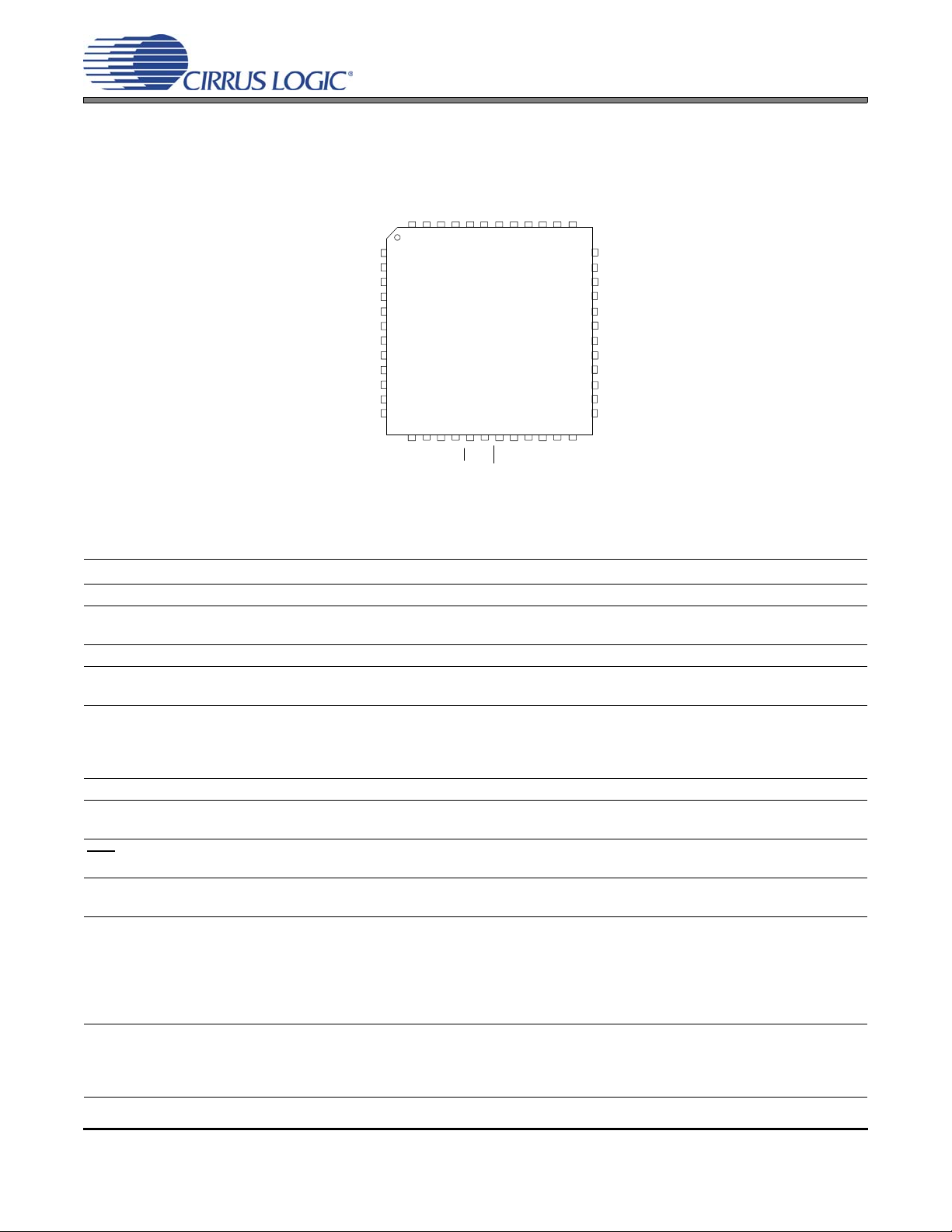

1. PIN DESCRIPTION

DSDA2

DSDB1

DSDA1

GND

MCLK

LRCK(DSD_EN)

SDIN1

SCLK

TST

SDIN2

TST

DSDB4

DSDB3

DSDA3

DSDA4

DSDB2

48 47 46 45 44 43 42 41 40 39 38 37

1

2

3

4

VD

5

6

7

8

9

10

11

2

1

13 14 15 16 17 18 19 20 21 22 23 24

SDIN3

SDIN4

M2(SCL/CCLK)

CS4382A

M0(AD0/CS)

M1(SDA/CDIN)

CS4382A

AOUTB1+

AOUTB1-

AOUTA1-

AOUTA1+

MUTEC1

VLS

M3(DSD_SCLK)

AOUTA2-

36

AOUTA2+

35

AOUTB2+

34

AOUTB2-

33

32

VA

GND

31

30

AOUTA3AOUTA3+

29

AOUTB3+

28

AOUTB3-

27

26

AOUTA4-

25

AOUTA4+

VQ

VLC

RST

FILT+

MUTEC2

AOUTB4-

AOUTB4+

Pin Name # Pin Description

VD 4 Digital Power (Input) - Positive power supply for the digital section.

GND

MCLK 6 Master Clock (Input) - Clock source for the delta-sigma modulator and digital filters.

LRCK 7

SDIN1

SDIN2

SDIN3

SDIN4

SCLK 9 Serial Clock (Input) - Serial clock for the serial audio interface.

VLC 18

RST

FILT+ 20

VQ 21

MUTEC1

MUTEC234

5

Ground (Input) - Ground reference. Should be connected to analog ground.

31

Left Right Clock (Input) - Determines which channel, Left or Right, is currently active on the serial

audio data line. The frequency of the left/right clock must be at the audio sample rate, Fs.

8

11

Serial Audio Data Input (Input) - Input for two’s complement serial audio data.

13

14

Control Port Power (Input) - Determines the required signal level for the Control Port. Refer to the

Recommended Operating Conditions for appropriate voltages.

Reset (Input) - The device enters a low power mode and all internal registers are reset to their default

19

settings when low.

Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling circuits.

Requires the capacitive decoupling to analog ground, as shown in the Typical Connection Diagram.

Quiescent Voltage (Output) - Filter connection for internal quiescent voltage. VQ must be capacitively

coupled to analog ground, as shown in the Typical Connection Diagram. The nominal voltage level is

specified in the Analog Characteristics and Specifications section. VQ presents an appreciable source

impedance and any current drawn from this pin will alter device performance. However, VQ can be

used to bias the analog circuitry assuming there is no AC signal component and the DC current is less

than the maximum specified in the Analog Characteristics and Specifications section.

Mute Control (Output) - These pins are intended to be used as a control for external mute circuits to

41

prevent the clicks and pops that can occur in any single supply system. The use of external mute cir-

22

cuits are not mandatory but may be desired for designs requiring the absolute minimum in extraneous

clicks and pops.

6 DS618F2

CS4382A

Pin Name # Pin Description

AOUTA1 +,AOUTB1 +,AOUTA2 +,AOUTB2 +,AOUTA3 +,AOUTB3 +,AOUTA4 +,AOUTB4 +,-

VA 32 Analog Power (Input) - Positive power supply for the analog section.

VLS 43

TST

Software Mode Definitions

SCL/CCLK 15

SDA/CDIN 16

AD0/CS

Stand-Alone Definitions

M0

M1

M2

M3

DSD Definitions

DSD_SCLK 42 DSD Serial Clock (Input) - Serial clock for the Direct Stream Digital audio interface.

DSD_EN 7 DSD-Enable (Input) - When held at logic ‘1’ the device will enter DSD Mode (Stand-Alone mode only).

DSDA1

DSDB1

DSDA2

DSDB2

DSDA3

DSDB3

DSDA4

DSDB4

39, 40

38, 37

35, 36

34, 33

29, 30

28, 27

25, 26

24, 23

10

12

17

17

16

15

42

3

2

1

48

47

46

45

44

Differential Analog Output (Output) - The full-scale differential analog output level is specified in the

Analog Characteristics specification table.

Serial Audio Interface Power (Input) - Determines the required signal level for the serial audio interface. Refer to the Recommended Operating Conditions for appropriate voltages.

Test - These pins need to be tied to analog ground.

Serial Control Port Clock (Input) - Serial clock for the serial Control Port. Requires an external pull-up

resistor to the logic interface voltage in I²C

Serial Control Data (Input/Output) - SDA is a data I/O line in I²C Mode and requires an external pull-up

resistor to the logic interface voltage, as shown in the Typical Connection Diagram. CDIN is the input

data line for the Control Port interface in SPI

Address Bit 0 (I²C) / Control Port Chip Select (SPI) (Input) - AD0 is a chip address pin in I²C Mode;

CS is the chip select signal for SPI format.

Mode Selection (Input) - Determines the operational mode of the device.

Direct Stream Digital Input (Input) - Input for Direct Stream Digital serial audio data.

®

Mode as shown in the Typical Connection Diagram.

™

Mode.

DS618F2 7

CS4382A

2. CHARACTERISTICS AND SPECIFICATIONS

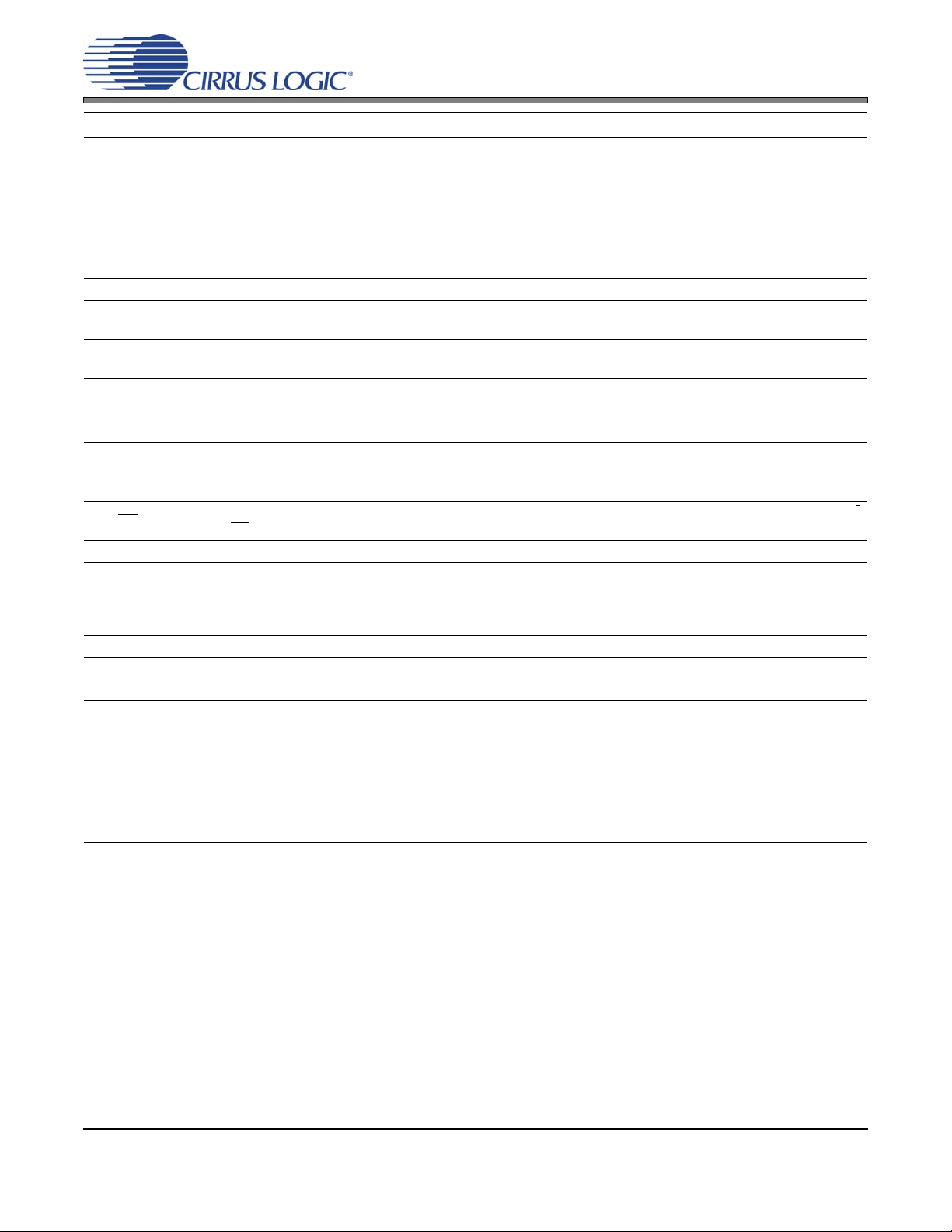

RECOMMENDED OPERATING CONDITIONS

(GND = 0 V; all voltages with respect to ground.)

Parameters Symbol Min Typ Max Units

DC Power Supply Analog Power

Digital Internal Power

Serial Data Port Interface Power

Control Port Interface Power

Ambient Operating Temperature (power applied)

Commercial Grade (-CQZ)

Automotive Grade (-DQZ)

VA

VD

VLS

VLC

T

A

4.75

2.37

1.71

1.71

-40

-40

5.0

2.5

5.0

5.0

5.25

2.63

5.25

5.25

-

-

+85

+105

V

V

V

V

°C

°C

ABSOLUTE MAXIMUM RATINGS

(GND = 0 V; all voltages with respect to ground.)

Parameters Symbol Min Max Units

DC Power Supply Analog Power

Digital Internal Power

Serial Data Port Interface Power

Control Port Interface Power

Input Current Any Pin Except Supplies I

Digital Input Voltage Serial Data Port Interface

Control Port Interface

Ambient Operating Temperature (power applied) T

Storage Temperature T

WARNING:Operation at or beyond these limits may result in permanent damage to the device. Normal operation

is not guaranteed at these extremes.

VLS

VLC

V

V

VA

VD

in

IND-S

IND-C

op

stg

-0.3

-0.3

-0.3

-0.3

-±10mA

-0.3

-0.3

-55 125 °C

-65 150 °C

6.0

3.2

6.0

6.0

VLS+ 0.4

VLC+ 0.4

V

V

V

V

V

V

8 DS618F2

CS4382A

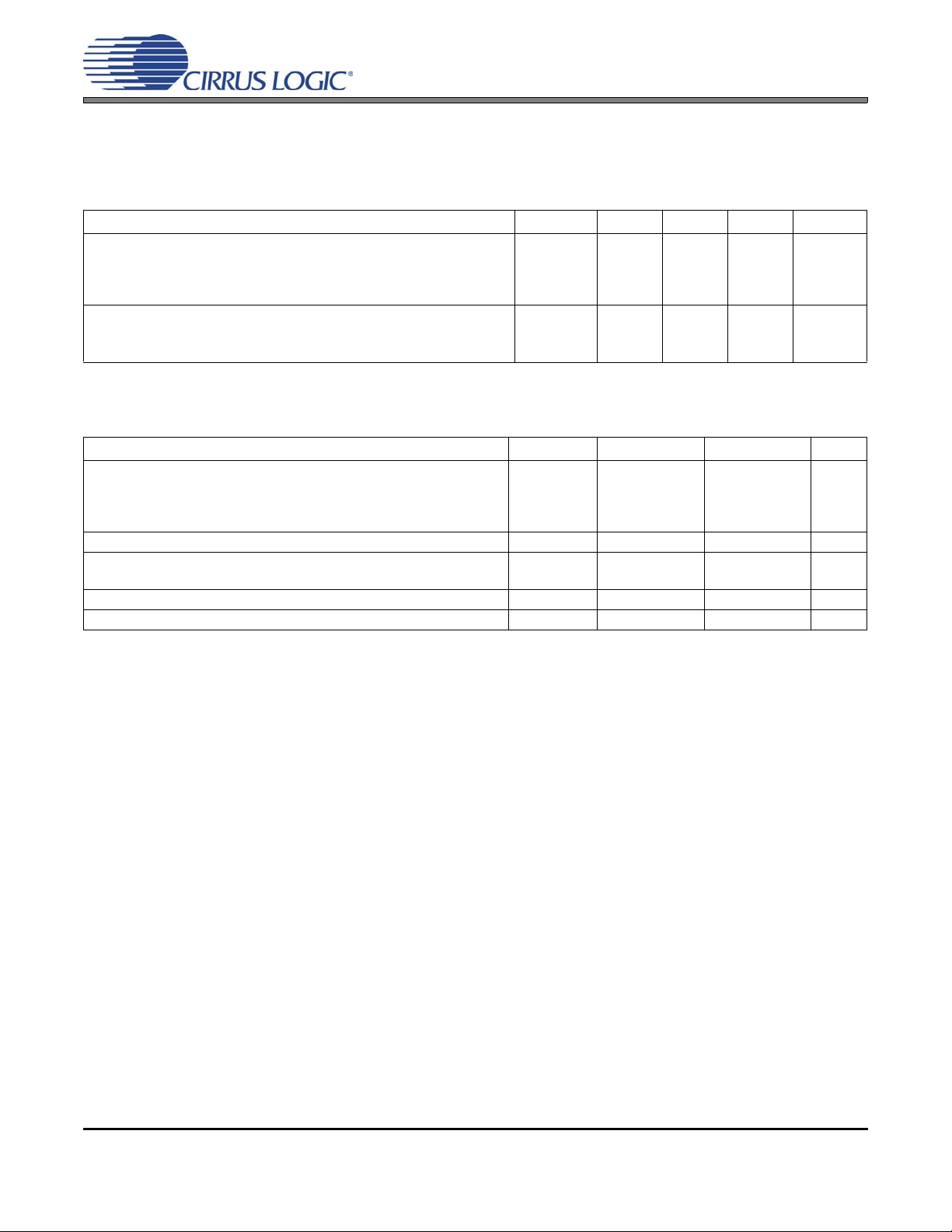

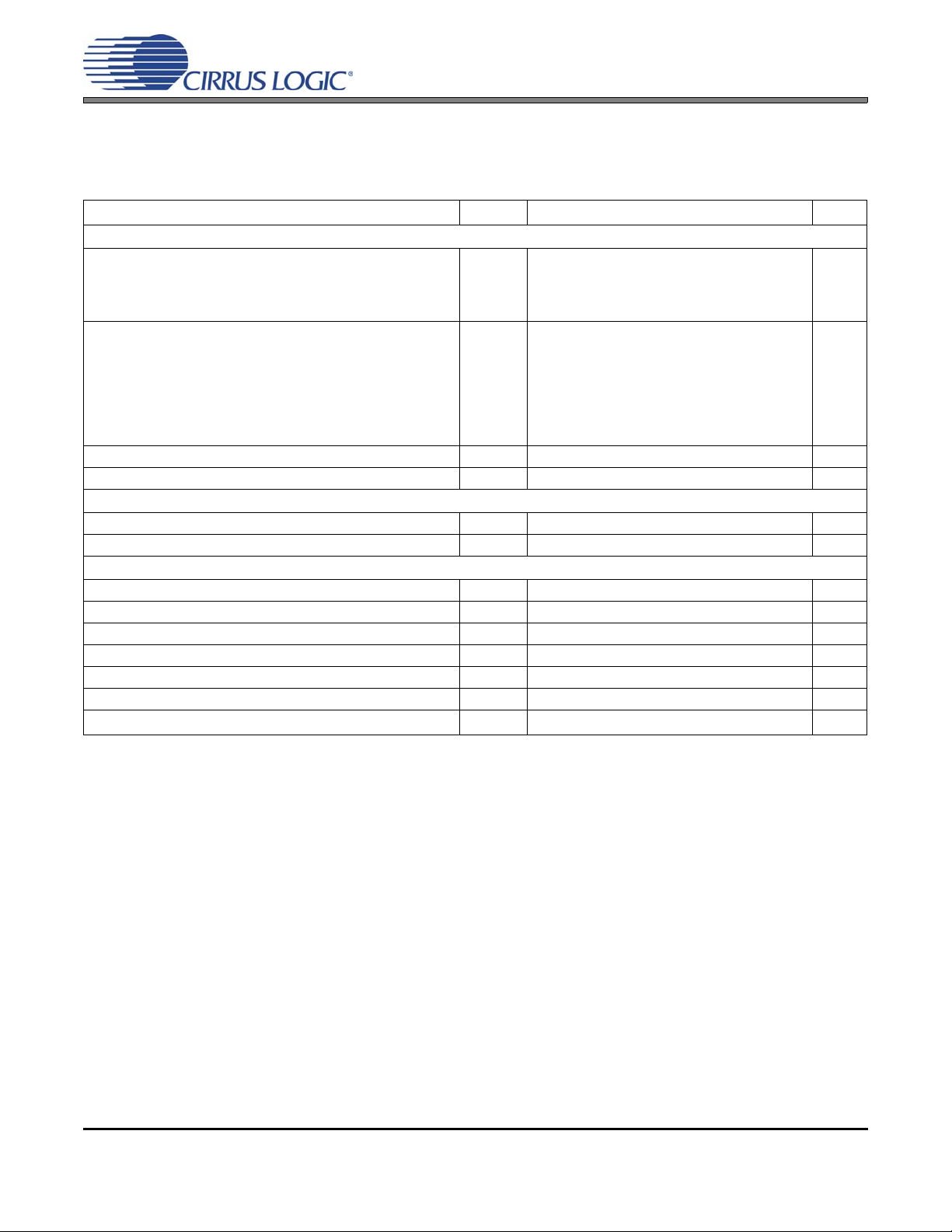

DAC ANALOG CHARACTERISTICS - COMMERCIAL (-CQZ)

Test Conditions (unless otherwise specified): VA = VLS = VLC = 5 V; VD = 2.5 V; TA = 25°C; Full-Scale 997 Hz

input sine wave

“Typical Connection Diagram” on page 19; Measurement Bandwidth 10 Hz to 20 kHz.

FS = 48 kHz, 96 kHz, 192 kHz and DSD

Dynamic Range 24-bit A-weighted

Total Harmonic Distortion + Noise 24-bit

Idle Channel Noise / Signal-to-noise Ratio - 114 - dB

Interchannel Isolation (1 kHz) - 110 - dB

DC Accuracy

Interchannel Gain Mismatch - 0.1 - dB

Gain Drift - 100 - ppm/°C

Analog Output

Full-scale Differential Output Voltage V

Output Impedance (Note 3) Z

Max DC Current Draw From an AOUT Pin I

Min AC-load Resistance R

Max Load Capacitance C

Quiescent Voltage V

Max Current draw from V

(Note 1); Tested under max ac-load resistance; Valid with FILT+ and VQ capacitors as shown in

Parameters Symbol Min Typ Max Unit

16-bit A-weighted

(Note 2) Unweighted

(Note 2) 16-bit 0 dB

Q

Unweighted

0 dB

-20 dB

-60 dB

-20 dB

-60 dB

THD+N

FS

OUT

OUTmax

L

L

Q

I

QMAX

108

105

-

-

-

-

-

-

-

-

128%•V

A

-130-Ω

-1.0-mA

-3-kΩ

-100-pF

- 50%•VA-VDC

-10-µA

114

111

97

94

-100

-91

-51

-94

-74

-34

132%•V

-

-

-

-

-94

-

-45

-

-

-

A

136%•V

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Vpp

A

Notes:

1. One-half LSB of triangular PDF dither is added to data.

2. Performance limited by 16-bit quantization noise.

3. V

is tested under load RL and includes attenuation due to Z

FS

OUT

DS618F2 9

CS4382A

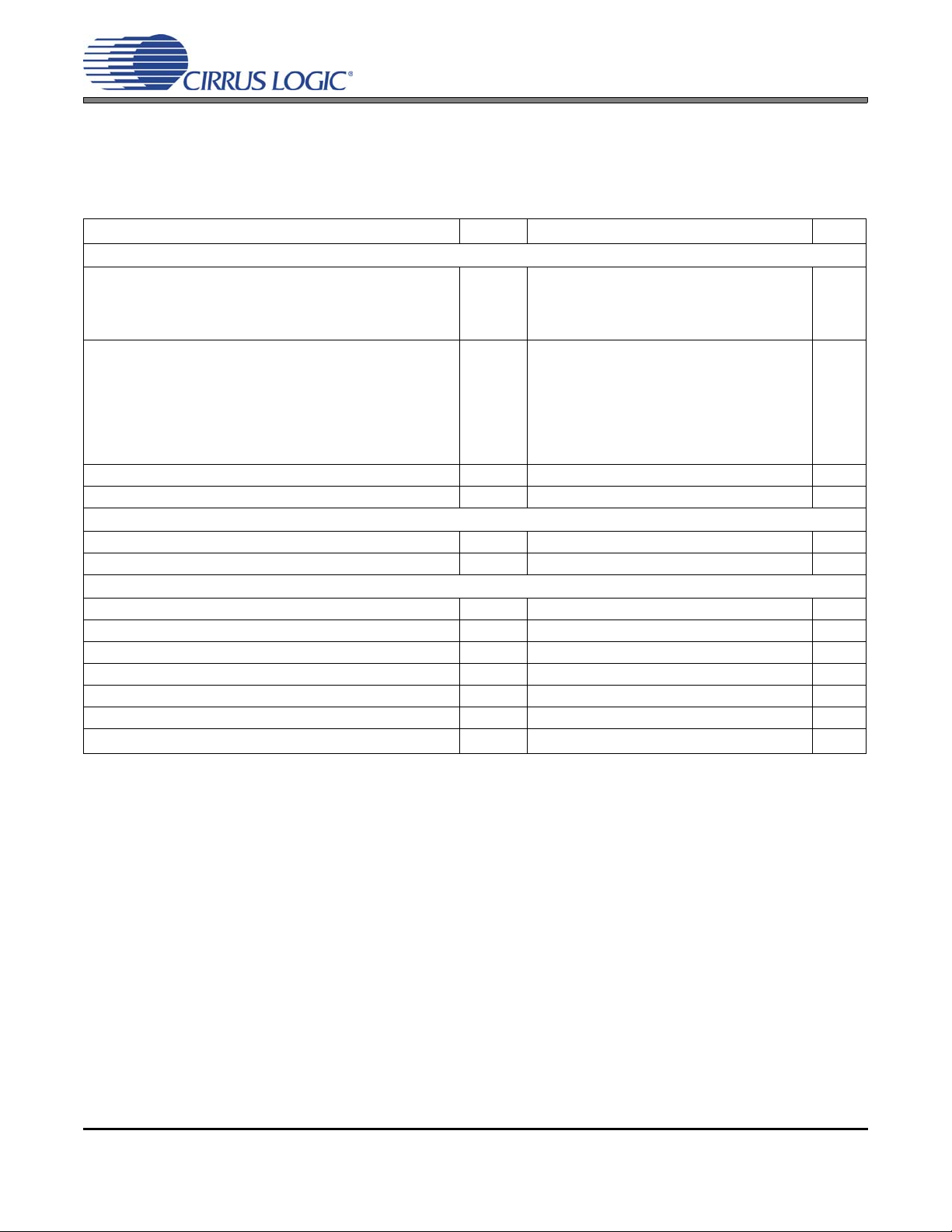

DAC ANALOG CHARACTERISTICS - AUTOMOTIVE (-DQZ)

Test Conditions (unless otherwise specified): VA = 4.75 to 5.25 V; VLS = 1.71 to 5.25 V; VLC = 1.71 to 5.25 V; VD

= 2.37 to 2.63 V; T

tance; Valid with FILT+ and VQ capacitors as shown in “Typical Connection Diagram” on page 19; Measurement

Bandwidth 10 Hz to 20 kHz.

FS = 48 kHz, 96 kHz, 192 kHz and DSD

Dynamic Range 24-bit A-weighted

Total Harmonic Distortion + Noise 24-bit

Idle Channel Noise / Signal-to-noise Ratio - 114 - dB

Interchannel Isolation (1 kHz) - 110 - dB

DC Accuracy

Interchannel Gain Mismatch - 0.1 - dB

Gain Drift - 100 - ppm/°C

Analog Output

Full-scale Differential Output Voltage V

Output Impedance (Note 3) Z

Max DC Current Draw From an AOUT Pin I

Min AC-load Resistance R

Max Load Capacitance C

Quiescent Voltage V

Max Current draw from V

= -40°C to 85°C; Full-Scale 997 Hz input sine wave (Note 1); Tested under max ac-load resis-

A

Parameters Symbol Min Typ Max Unit

16-bit A-weighted

(Note 2) Unweighted

(Note 2) 16-bit 0 dB

Q

Unweighted

0 dB

-20 dB

-60 dB

-20 dB

-60 dB

THD+N

FS

OUT

OUTmax

L

L

Q

I

QMAX

105

102

-

-

-

-

-

-

-

-

128%•V

A

- 130 - Ω

-1.0-mA

-3-kΩ

- 100 - pF

- 50%•V

-10-µA

114

111

97

94

-100

-91

-51

-94

-74

-34

132%•V

-

-

-

-

-91

-

-42

-

-

-

A

A

136%•V

-VDC

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Vpp

A

10 DS618F2

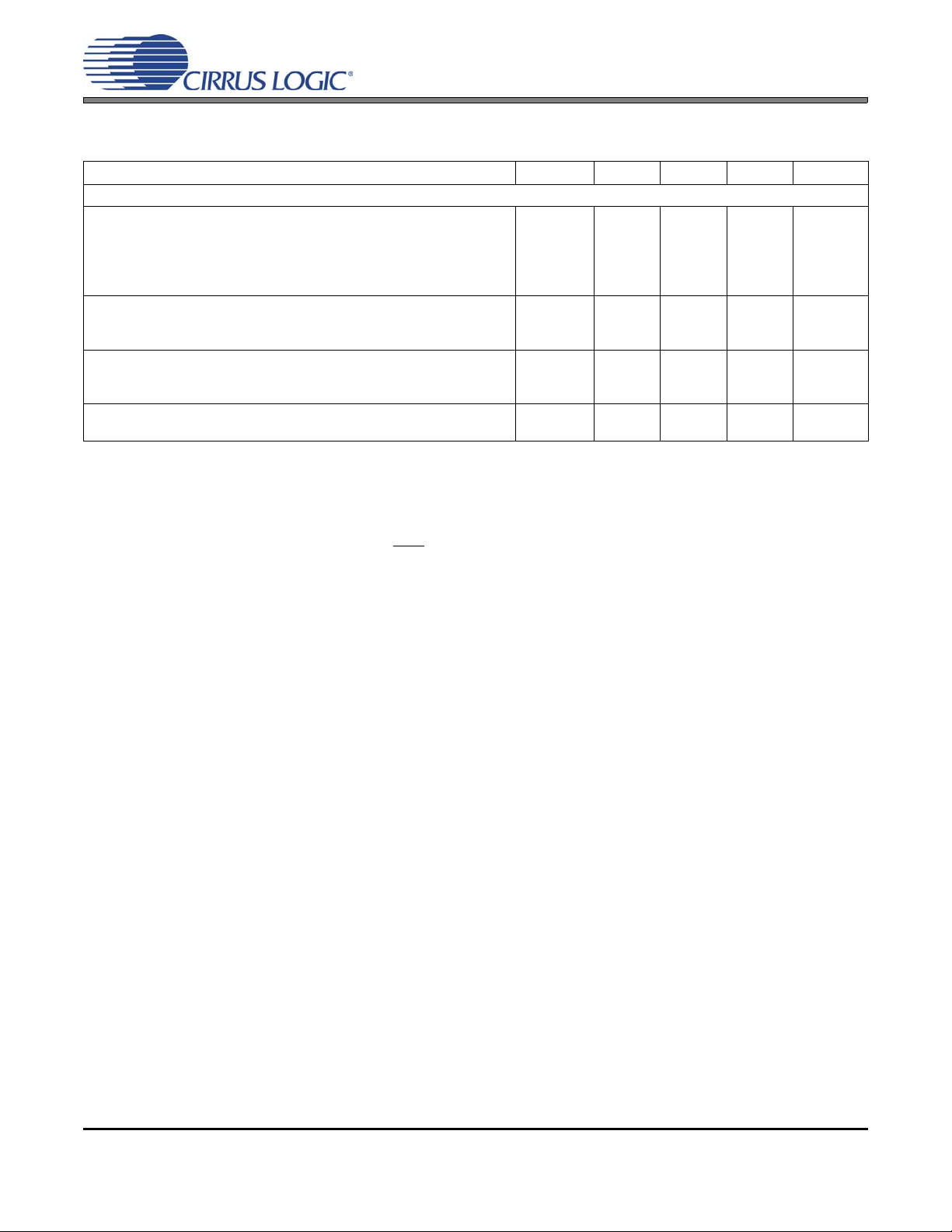

POWER AND THERMAL CHARACTERISTICS

Parameters Symbol Min Typ Max Units

Power Supplies

Power Supply Current Normal Operation, VA= 5 V

(Note 4) VD= 2.5 V

(Note 5) Interface Current, VLC=5 V

VLS=5 V

(Note 6) Power-down State (all supplies)

Power Dissipation (Note 4) VA = 5V, VD = 2.5V

Normal Operation

(Note 6) Power-down

Package Thermal Resistance Multi-layer

Two-layer

Power Supply Rejection Ratio (Note 7) (1 kHz)

(60 Hz)

Notes:

4. Current consumption increases with increasing FS within a given speed mode and is sign al-dependent.

Max values are based on highest FS and highest MCLK.

5. I

6. Power-down Mode is defined as RST

7. Valid with the recommended capacitor values on FILT+ and VQ as shown in Figures 5 and 6.

measured with no external loading on the SDA pin.

LC

pin = Low with all clock and data lines held static.

I

A

I

D

I

LC

I

LS

I

pd

θ

JA

θ

JA

θ

JC

PSRR

CS4382A

-

-

-

-

-

-

-

-

-

-

-

-

84

20

2

75

200

470

1

48

65

15

60

40

91

25

-

-

-

520

-

-

-

-

-

-

mA

mA

µA

µA

µA

mW

mW

°C/Watt

°C/Watt

°C/Watt

dB

dB

DS618F2 11

CS4382A

COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE

The filter characteristics have been norma lized to th e sample rate (Fs) and can be referenced to the desired sample rate by multiplying the given characteristic by Fs.

See Note 12.

Parameter

Combined Digital and On-chip Analog Filter Response - Single-Speed Mode - 48 kHz

Passband (Note 9) to -0.01 dB corner

Frequency Response 10 Hz to 20 kHz -0.01 - +0.01 dB

Stop Band 0.547 - - Fs

Stop-band Attenuation (Note 10) 102 - - dB

Group Delay - 10.4/Fs - s

De-emphasis Error (Note 11) Fs = 32 kHz

(Relative to 1 kHz) Fs = 44.1 kHz

Combined Digital and On-chip Analog Filter Response - Double-Speed Mode - 96 kHz

Passband (Note 9) to -0.01 dB corner

Frequency Response 10 Hz to 20 kHz -0.01 - +0.01 dB

Stop Band .583 - - Fs

Stop-band Attenuation (Note 10) 80 - - dB

Group Delay - 6.15/Fs - s

Combined Digital and On-chip Analog Filter Response - Quad-Speed Mode - 192 kHz

Passband (Note 9) to -0.01 dB corner

Frequency Response 10 Hz to 20 kHz -0.01 - +0.01 dB

Stop Band .635 - - Fs

Stop-band Attenuation (Note 10) 90 - - dB

Group Delay - 7.1/Fs - s

to -3 dB corner

Fs = 48 kHz

to -3 dB corner

to -3 dB corner

0

0

-

-

-

0

0

0

0

Fast Roll-Off

-

-

-

-

-

-

-

-

-

.454

.499

±0.23

±0.14

±0.09

.430

.499

.105

.490

UnitMin Typ Max

Fs

Fs

dB

dB

dB

Fs

Fs

Fs

Fs

Notes:

8. Slow roll-off interpolation filter is only available in Software Mode.

9. Response is clock-dependent and will scale with Fs.

10. For Single-Speed Mode, the Measurement Bandwidth is from stopband to 3 Fs.

For Double-Speed Mode, the Measurement Bandwidth is from stopband to 3 Fs.

For Quad-Speed Mode, the Measurement Bandwidth is from stopband to 1.34 Fs.

11. De-emphasis is available only in Single-Speed Mode; only 44.1 kHz De-emphasis is available in Hardware Mode.

12. Amplitude vs. Frequency plots of this data are available in Section 7. “Filter Plots” on page 42.

12 DS618F2

CS4382A

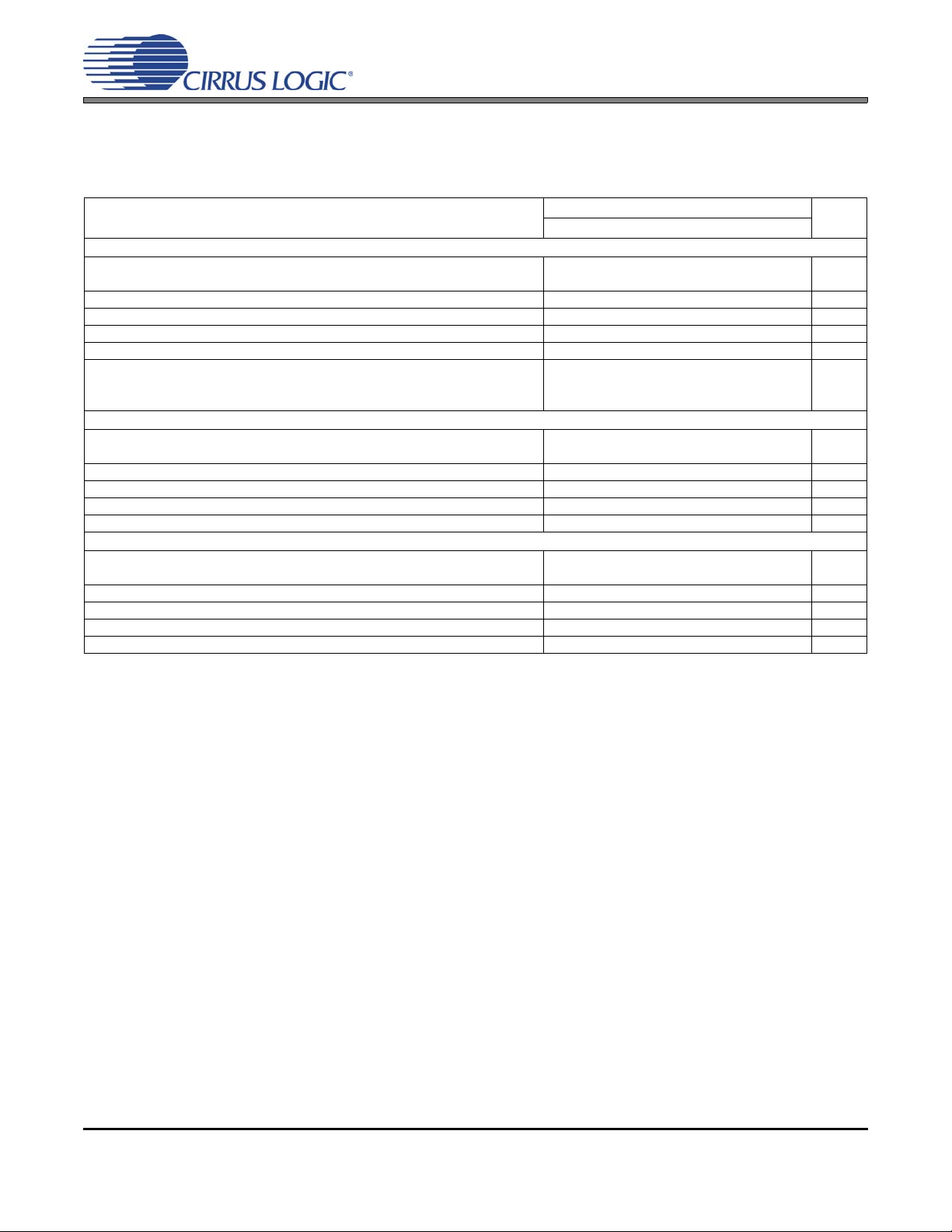

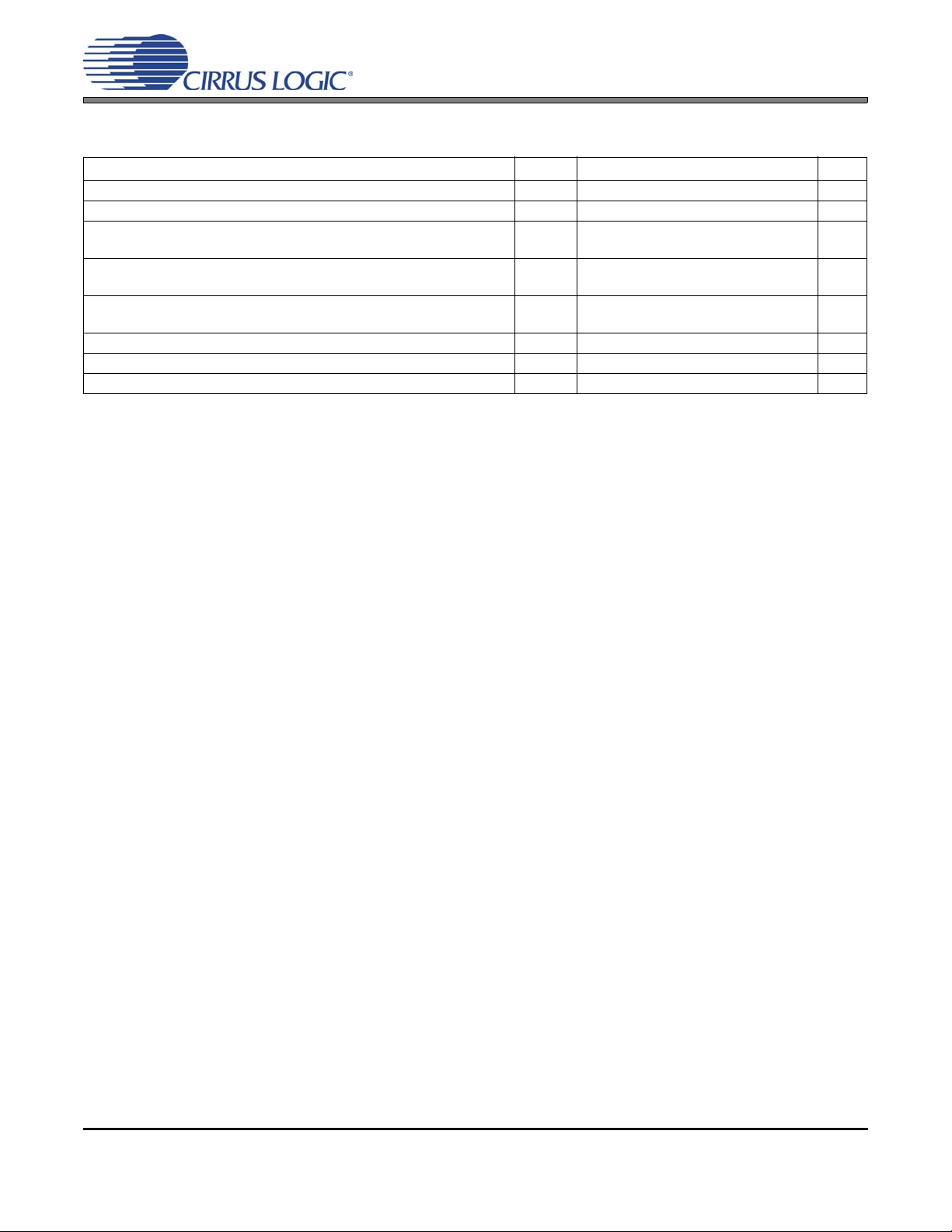

COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE

(CONTINUED)

Slow Roll-Off (Note 8)

Parameter

Single-Speed Mode - 48 kHz

Passband (Note 9) to -0.01 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz -0.01 - +0.01 dB

Stop Band .583 - - Fs

Stop-band Attenuation (Note 10) 64 - - dB

Group Delay - 7.8/Fs - s

De-emphasis Error (Note 11) Fs = 32 kHz

(Relative to 1 kHz) Fs = 44.1 kHz

Fs = 48 kHz

0

0

-

-

-

-

-

-

-

-

0.417

0.499

±0.36

±0.21

±0.14

Double-Speed Mode - 96 kHz

Passband (Note 9) to -0.01 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz -0.01 - +0.01 dB

Stop Band .792 - - Fs

Stop-band Attenuation (Note 10) 70 - - dB

Group Delay - 5.4/Fs - s

0

0

-

-

.296

.499

Quad-Speed Mode - 192 kHz

Passband (Note 9) to -0.01 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz -0.01 - +0.01 dB

Stop Band .868 - - Fs

Stop-band Attenuation (Note 10) 75 - - dB

Group Delay - 6.6/Fs - s

0

0

-

-

.104

.481

UnitMin Typ Max

Fs

Fs

dB

dB

dB

Fs

Fs

Fs

Fs

DSD COMBINED DIGITAL & ON-CHIP ANALOG FILTER RESPONSE

Parameter Min Typ Max Unit

DSD Processor mode

Passband (Note 9) to -3 dB corner 0 - 50 kHz

Frequency Response 10 Hz to 20 kHz -0.05 - +0.05 dB

Roll-off 27 - - dB/Oct

DS618F2 13

CS4382A

DIGITAL CHARACTERISTICS

Parameters Symbol Min Typ Max Units

Input Leakage Current (Note 13) I

in

Input Capacitance - 8 - pF

High-level Input Voltage Serial I/O

Control I/O

Low-level Input Voltage Serial I/O

Control I/O

Low-level Output Voltage (IOL= -1.2 mA) Control I/O = 3.3 V, 5 V

Control I/O = 1.8 V, 2.5 V

Maximum MUTEC Drive Current I

MUTEC High-level Output Voltage V

MUTEC Low-level Output Voltage V

V

V

V

V

V

V

max

IH

IH

IL

IL

OL

OL

OH

OL

13. Any pin except supplies. Transient currents of up to ±100 mA on the input pins will not cause SCR latchup.

--±10µA

70%

70%

-

-

-

-

-

-

-

-

-

-

-

-

30%

30%

20%

25%

-3-mA

-VA-V

-0-V

V

LS

V

LC

V

LS

V

LC

V

LC

V

LC

14 DS618F2

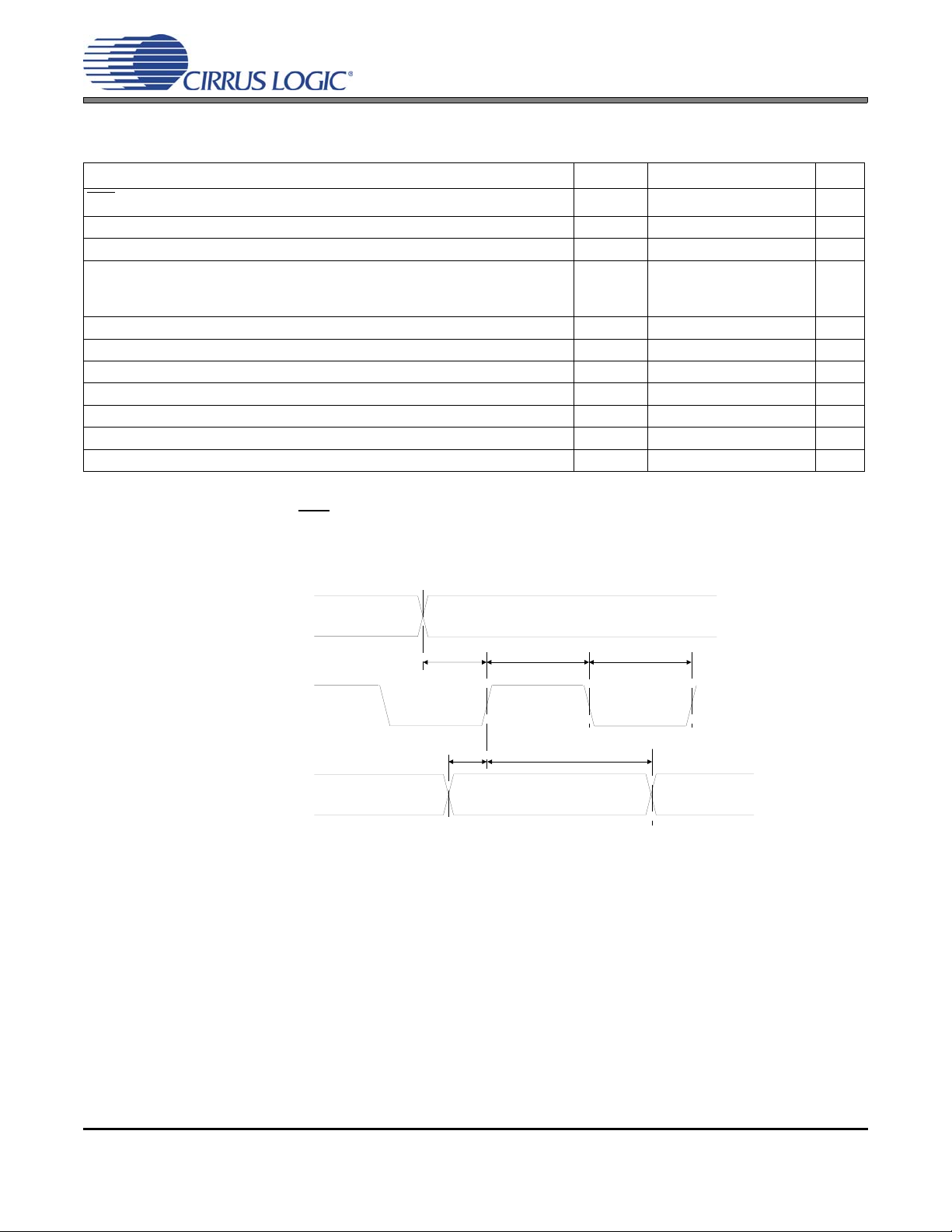

CS4382A

SWITCHING CHARACTERISTICS - PCM

(Inputs: Logic 0 = GND, Logic 1 = VLS, CL = 30 pF)

Parameters Symbol Min Max Units

RST pin Low Pulse Width (Note 14) 1-ms

MCLK Frequency 1.024 55.2 MHz

MCLK Duty Cycle (Note 15) 45 55 %

Input Sample Rate - LRCK Single-speed Mode

Double-speed Mode

Quad-speed Mode

LRCK Duty Cycle 45 55 %

SCLK Duty Cycle 45 55 %

SCLK High Time t

SCLK Low Time t

LRCK Edge to SCLK rising edge t

SDIN Setup Time before SCLK rising edge t

SDIN Hold Time after SCLK rising edge t

Notes:

14. After powering up, RST

should be held low until after the power supplies and clocks are settled.

15. See Table 1 on page 21 for suggested MCLK frequencies.

F

F

F

sckh

sckl

lcks

ds

dh

s

s

s

4

50

100

8-ns

8-ns

5-ns

3-ns

5-ns

54

108

216

kHz

kHz

kHz

LRCK

SCLK

SDINx

t

lcks

t

ds

t

sckh

t

dh

MSB

Figure 1. Serial Audio Interface Timing

t

sckl

MSB-1

DS618F2 15

Loading...

Loading...