Page 1

CS4207

Low-power, 4-in / 6-out HD Audio Codec with Headphone Amp

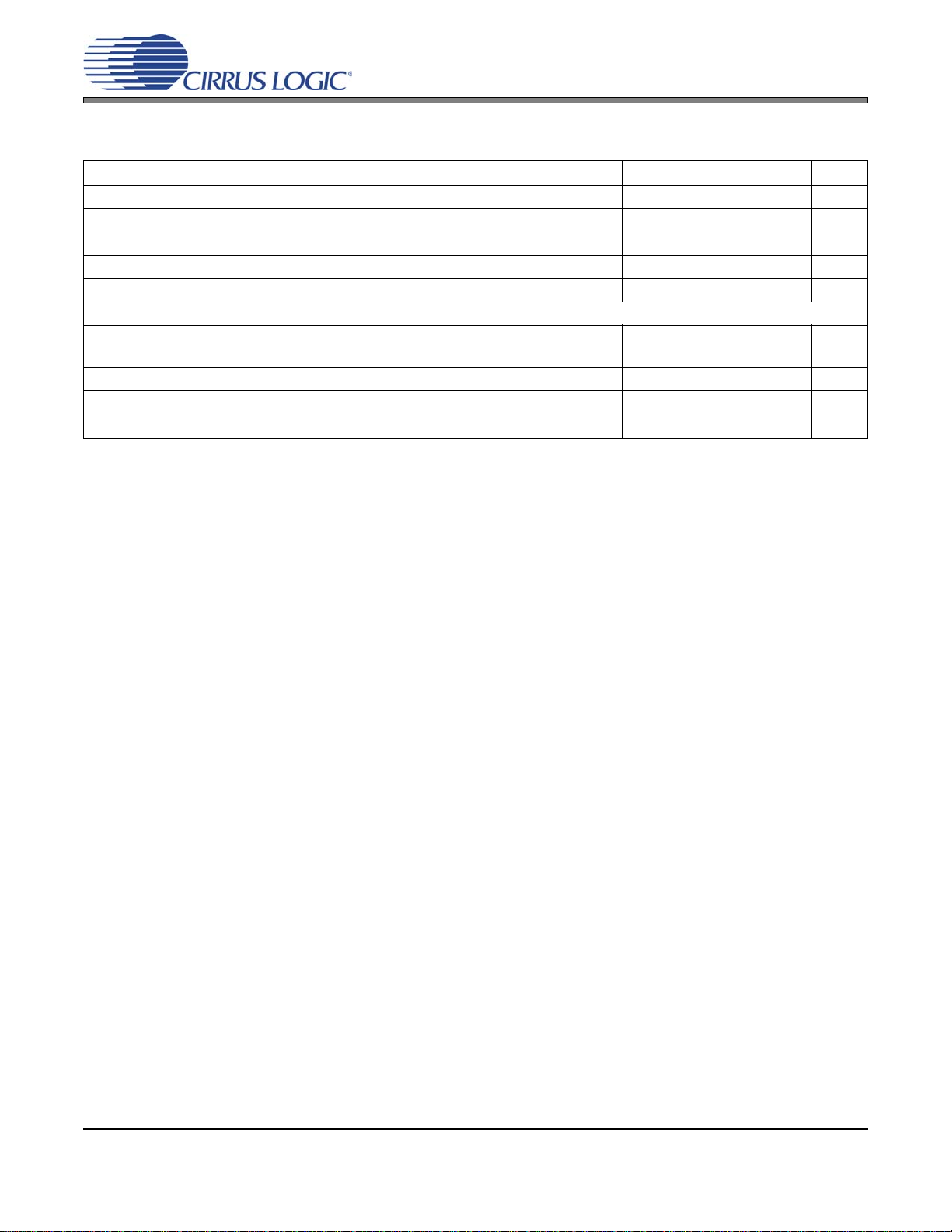

DIGITAL to ANALOG FEATURES

DAC1 (Headphone)

– 101 dB Dynamic Range (A-wtd)

– -89 dB THD+N

Headphone Amplifier - GND Centered

– Integrated Negative-voltage Regulator

– No DC-blocking Capacitor Required

– 50 mW Power/Channel into 16

DAC2 & DAC3 (Line Outs)

– 110 dB Dynamic Range (A-wtd)

– -94 dB THD+N

– Differential Balanced or Single-ended

Each DAC Supports 32 kHz to 192 kHz Sample

Rates Independently.

Digital Volume Control

– +6.0 dB to -57.5 dB in 0.5 dB Steps

– Zero Cross and/or Soft Ramp Transitions

Independent Support of D0 and D3 Power

States for Each DAC

Fast D3 to D0 Transition

– Audio Playback in Less Than 50 ms

ANALOG to DIGITAL FEATURES

ADC1 & ADC2

– 105 dB Dynamic Range (A-wtd)

– -88 dB THD+N

– Differential Balanced or Single-ended

Inputs

– Analog Programmable Gain Amplifier

(PGA) ±12 dB, 1.0 dB Steps, with Zero

Cross Transitions and Mute

MIC Inputs

– Pre-amplifier with Selectable 0 dB, +10 dB,

+20 dB, and +30 dB Gain Settings

– Programmable, Low-noise MIC Bias Level

Each ADC Supports 8 kHz to 96 kHz Sample

Rates Independently

Additional Digital Attenuation Control

– -13.0 dB to -51.0 dB in 1.0 dB steps

– Zero Cross and/or Soft Ramp Transitions

Digital Interface for Two Dual Digital Mic Inputs

Independent Support of D0 and D3 Power

States for Each ADC

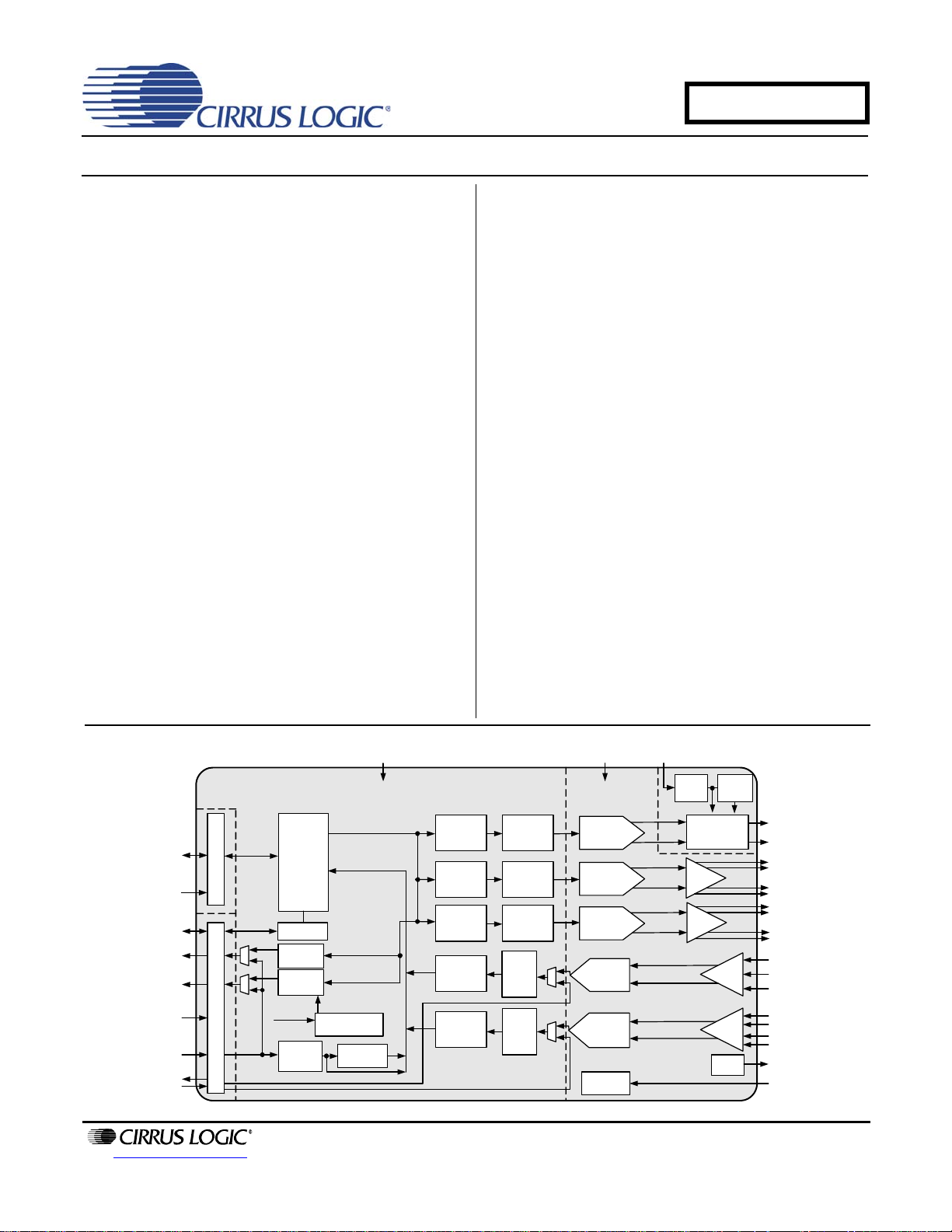

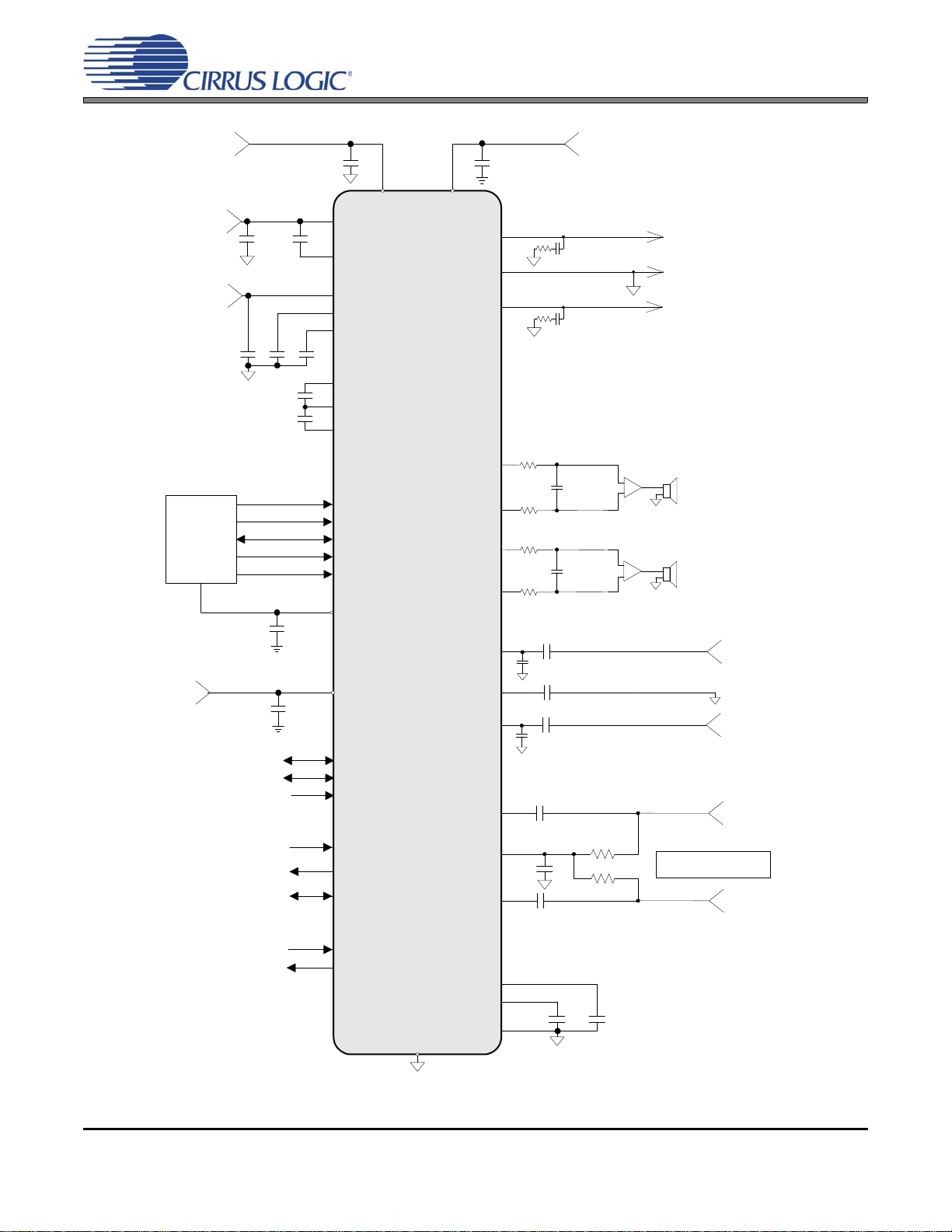

HD Audio

Bus

VL_HD

(1.5 V to 3.3 V)

S/PDIF OUT 2

S/PDIF OUT 1

VL_IF

(3.3 V)

S/PDIF IN

D-Mic Clock

D-Mic In

Level Translator

Level Translator

http://www.cirrus.com

Interface

HD Bus

Fs

HD

Audio

GPIOGPIO

SPDIF

TX 2

SPDIF

TX 1

SPDIF

RX

(1.5 V to 1.8 V)

128Fs Clock

Multiplier

SPDIF

RX SRC

VD

Vol/Mute

Vol/Mute

Vol/Mute

Vol/Boost/

Mute

Vol/Boost/

Mute

SRC &

Multibit

Modulator

SRC &

Multibit

Modulator

SRC &

Multibit

Modulator

Digital

Filter &

SRC

Digital

Filter &

SRC

Copyright Cirrus Logic, Inc. 2012

(All Rights Reserved)

VA, VA_REF

(3.3 V to 5.0 V)

2-Chnl

DAC1

2-Chnl

DAC2

2-Chnl

DAC3

2-Chnl

ADC1

2-Chnl

ADC2

Jack

Sense

VA_HP

(3.3 V to 5.0 V)

Chrg

Pump

Buck

+VHP

Headphone

Amp - GND

Centered

Line

Out

Line

Out

Pump

Invert

PGA

PGA

MIC

Bias

Chrg

-VHP

Left HP Out

Right HP Out

+

Left Line Out

+

Right Line Out

+

Left Line Out

+

Right Line Out

+

Line/Mic In L

-

Line/Mic In R

+

+

Mic/Line In L

+

Mic/Line In R

-

Mic Bias

SENSE_A

AUG '12

DS880F4

Page 2

CS4207

Digital Audio Interface Receiver

Complete EIAJ CP1201, IEC 60958, S/PDIF

Compatible Receiver

32 kHz to 192 kHz Sample Rate Range

Automatic Detection of Compressed Audio

Streams

Integrated Sample Rate Converter

– 128 dB Dynamic Range

– -120 dB THD+N

– Supports Sample Rates up to 192 kHz

– 1:1 Input/Output Sample Rate Ratios

Digital Audio Interface Transmitters

Two Independent EIAJ CP1201, IEC-60958,

S/PDIF Compatible Transmitters

32 kHz to 192 kHz Sample Rate Range

System Features

Very Low D3 Power Dissipation of <7 mW

– Jack Detect Active in D3

– HDA BITCLK Not Required for D3 State

Jack Detect Does Not Require HDA Bus

BITCLK

All Configuration Settings are Preserved in D3

State

Pop/Click Suppression in State Transitions

Detects Wake Event and Generates Power

State Change Request when HDA Bus

Controller is in D3

Variable Power Supplies

– 1.5 V to 1.8 V Digital Core Voltage

– 3.3 V to 5.0 V Analog Core Voltage

– 3.3 V to 5.0 V Headphone Drivers

– 1.5 V to 3.3 V HD Bus Interface Logic

– 3.3 V Interface Logic levels for GPIO,

S/PDIF, and Digital Mic

General Description

The CS4207 is a highly integrated multi-channel lowpower HD Audio Codec featuring 192 kHz DACs,

96 kHz ADCs, 192 kHz S/PDIF Transmitters and Receiver, Microphone pre-amp and bias voltage, and a

ground centered Headphone driver. Based on multi-bit,

delta-sigma modulation, it allows infinite sample rate

adjustment between 32 kHz and 192 kHz.

The ADC input path allows contro l of a number of features. The microphone input path includes a selectable

programmable-gain pre-amplifier stage and a low- noise

MIC bias voltage supply. A PGA is available for line and

microphone inputs and provides analog gain with soft

ramp and zero cross transitions. The ADC also features

an additional digital volume attenuator with soft ramp

transitions.

The stereo headphone amplifier is powered from a separate internally generated positive supply, with an

integrated charge pump providing a negative supply.

This allows a ground-centered analog output with a

wide signal swing and eliminates external DC-blo cking

capacitors.

The integrated digital audio interface receiver and transmitters utilize a 24-bit, high-performance, monolithic

CMOS stereo asynchronous sample rate converter to

clock align the PCM samples to/from the S/PDIF interfaces. Auto detection of non-PCM encoded data

disables the sample rate conversion to preserve bit accuracy of the data.

In addition to its many features, the CS4207 operates

from a low-voltage analog and digital core, making this

part ideal for portable systems that require low power

consumption in a minimal amount of space.

The CS4207 is available in a 48-pin WQFN package in

both Automotive (-40°C to +105°C) and Commercial

(-40°C to +85°C) grades. The CS4207 Customer Demonstration board is also available for device evaluation

and implementation suggestions. Please refer to “Or-

dering Information” on p 147 for complete ordering

information.

Individual Power-down Managed

– ADCs, DACs, PGAs, Headphone Driver,

S/PDIF Receiver, and Transmitters

2 DS880F4

Page 3

TABLE OF CONTENTS

1. PIN DESCRIPTIONS .............................................................................................................................. 8

1.1 CS4207 48-pin QFN Pinout: ....................................... .......................................... ........................... 8

1.2 Digital I/O Pin Characteristics .............................. .... ... ... ... .... ... ... ................................................... 10

2. TYPICAL CONNECTION DIAGRAMS .................................................................................................11

3. CHARACTERISTICS AND SPECIFICATIONS .................................................................................... 13

RECOMMENDED OPERATING CONDITIONS .................................................................................. 13

ABSOLUTE MAXIMUM RATINGS ...................................................................................................... 13

ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ) ......................................................... 14

ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) ......................................................... 15

ADC DIGITAL FILTER CHARACTERISTICS ...................................................................................... 16

ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL - CNZ) ..................................................... 17

ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE - DNZ) ..................................................... 19

COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE ............................. 21

DC ELECTRICAL CHARACTERISTICS . ... ... .... ... ... ... .......................................... ................................ 21

DIGITAL MICROPHONE INTERFACE CHARACTERISTICS ............................................................. 22

DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS .................................................... 23

HD AUDIO BUS SPECIFICATIONS & CHARACTERISTICS .............................................................. 23

S/PDIF TRANSMITTER/RECEIVER SPECIFICATIONS & CHARACTERISTICS .............................. 23

POWER CONSUMPTION ................................................................................................................... 24

4. CODEC RESET AND INITIALIZATION ............................................................................................... 25

4.1 Link Reset ................................................................... .......................................... ......................... 25

4.2 Function Group Reset .................................... ... .......................................... ................................... 25

4.3 Codec Initialization ............................... ... .... ... ... .......................................... ................................... 25

4.4 D3 Lower Power State Support ........ .......................................... .......................................... ......... 26

4.5 Extended Power States Supported (EPSS) ................................................................................... 26

4.6 Power State Settings Reset (PS-SettingsReset) ........................................................................... 28

4.7 Register Settings Across Resets ................................................................................................... 29

5. PRESENCE DETECTION ..................................................................................................................... 31

5.1 Jack Detection Circuit .................................................................................................................... 31

5.1.1 Presence Detection and Unsolicited Response .................................................................... 31

5.1.2 S/PDIF Receiver Presence Detect ........................................................................................ 32

6. HD AUDIO CODEC SUPPORTED VERBS AND RESPONSES ......................................................... 33

6.1 Software Programming Model .......................................................................................................33

6.1.1 Node ID Summary ................................................................................................................. 34

6.1.2 Pin Configuration Register Defaults ......................................................................................35

6.2 Root Node (Node ID = 00h) ........................................................................................................... 36

6.2.1 Vendor and Device ID ..................................................... ... ... ... .... ... ... ................................... 36

6.2.2 Revision ID ............................................................................................................................ 36

6.2.3 Subordinate Node Count ....................................................................................................... 36

6.3 Audio Function Group (Node ID = 01h) ......................................................................................... 37

6.3.1 Subordinate Node Count ....................................................................................................... 37

6.3.2 Function Group Type ............................................................................................................. 37

6.3.3 Audio Function Group Capabilities ........................................................................................37

6.3.4 Supported PCM Size, Rates ...............................................................................................

6.3.5 Support

6.3.6 Supported Power States ....................................................................................................... 39

6.3.7 GPIO Capabilities .................................................................................................................. 40

6.3.8 Power States ......................................................................................................................... 41

6.3.9 GPIO Data ............................................................................................................................. 42

6.3.10 GPIO Enable Mask .............................. .......................................... ...................................... 43

6.3.11 GPIO Direction .......................................... .... ... ... ... .... ... .......................................... ............ 43

6.3.12 GPIO Sticky Mask ............................................ ... ... .... ... ... ... ... ............................................. 43

e

CS4207

.. 38

d Stream Formats ................................................................................................... 39

DS880F4 3

Page 4

CS4207

6.3.13 Implementation Identification ............................................................................................... 44

6.3.14 Function Reset .................................................................................................................... 44

6.4 DAC1, DAC2, DAC3 Output Converter Widgets (Node ID = 02h, 03h, 04h) ................................. 45

6.4.1 Audio Widget Capabilities ........... ... .... ... ... ... .... ... .......................................... ......................... 45

6.4.2 Supported PCM Size, Rates .............. ... ... ... .... ... ... ... .......................................... ................... 46

6.4.3 Supported Stream Formats ...... ... .......................................... .......................................... ...... 46

6.4.4 Supported Power States ................ .......................................... ............................................. 47

6.4.5 Output Amplifier Capabilities ................................................................................................. 47

6.4.6 Power States ......... ... .......................................... .......................................... ......................... 48

6.4.7 Converter Stream, Channel ................................................................................................... 49

6.4.8 Converter Format ............................................ ... ... ... .... ... ... ... ................................................ 49

6.4.9 Amplifier Gain/Mute ..................... .................................... ................................... ................... 51

6.5 ADC1, ADC2 Input Converter Widgets (Node ID = 05h, 06h) ....................................................... 53

6.5.1 Audio Widget Capabilities ........... ... .... ... ... ... .... ... .......................................... ......................... 53

6.5.2 Supported PCM Size, Rates .............. ... ... ... .... ... ... ... .......................................... ................... 54

6.5.3 Supported Stream Formats ...... ... .......................................... .......................................... ...... 54

6.5.4 Input Amplifier Capabilities .............................. .......................................... ............................ 55

6.5.5 Connection List Length ....................... ... ... ... .... ... ... ... .......................................... ................... 55

6.5.6 Supported Power States ................ .......................................... ............................................. 56

6.5.7 ADC1 Connection List Entry ..................................................................................................56

6.5.8 ADC1 Connection Select Control .......................................................................................... 56

6.5.9 ADC2 Connection List Entry ..................................................................................................57

6.5.10 ADC2 Connection Select Control ........... ................................................................. ............57

6.5.11 Power States ....................................................................................................................... 58

6.5.12 Converter Stream, Channel ................................................................................................. 59

6.5.13 Converter Format ................................................................................................................ 59

6.5.14 Amplifier Gain/Mute ............................................................................................................. 61

6.6 S/PDIF Receiver Input Converter Widget (Node ID = 07h) ........................................................... 63

6.6.1 Audio Widget Capabilities ........... ... .... ... ... ... .... ... .......................................... ......................... 63

6.6.2 Supported PCM Size, Rates .............. ... ... ... .... ... ... ... .......................................... ................... 64

6.6.3 Supported Stream Formats ...... ... .......................................... .......................................... ...... 64

6.6.4 Connection List Length ....................... ... ... ... .... ... ... ... .......................................... ................... 65

6.6.5 Supported Power States ................ .......................................... ............................................. 65

6.6.6 Connection List Entry ............................................................................................................ 65

6.6.7 Power States ......... ... .......................................... .......................................... ......................... 66

6.6.8 Converter Stream, Channel ................................................................................................... 67

6.6.9 Converter Format ............................................ ... ... ... .... ... ... ... ................................................ 67

6.6.10 Digital Converter Control ..................................................................................................... 69

6.7 S/PDIF Transmitter 1, S/PDIF Transmitter 2 Output Converter Widgets (Node ID = 08h, 14h) .... 70

6.7.1 Audio Widget Capabilities ........... ... .... ... ... ... .... ... .......................................... ......................... 70

6.7.2 Supported PCM Size, Rates .............. ... ... ... .... ... ... ... .......................................... ................... 71

6.7.3 Supported Stream Formats ...... ... .......................................... .......................................... ...... 72

6.7.4 Supported Power States ................ .......................................... ............................................. 72

6.7.5 Power States ......... ... .......................................... .......................................... ......................... 72

6.7.6 Converter Stream, Channel ................................................................................................... 74

6.7.7 Converter Format ............................................ ... ... ... .... ... ... ... ................................................ 74

6.7.8 Digital Converter Control ....................................................................................................... 76

6.8 Headphone Pin Widget (Node ID = 09h) .......................................................................................78

...

6.8.1 Audio Widget Capabilities ........... ... .... ... ... ... .... ... .......................................... ......................

6.8.2 Pin Capabilities ...................... ... ... ... .... ... ... ... .......................................... ................................ 78

6.8.3 Connection List Length ....................... ... ... ... .... ... ... ... .......................................... ................... 79

6.8.4 Supported Power States ................ .......................................... ............................................. 79

6.8.5 Connection List Entry ............................................................................................................ 80

6.8.6 Power States ......... ... .......................................... .......................................... ......................... 80

78

4 DS880F4

Page 5

CS4207

6.8.7 Pin Widget Control ................................................................................................................ 81

6.8.8 Unsolicited Response Control ............................................................................................... 82

6.8.9 Pin Sense .............................................................................................................................. 83

6.8.10 Configuration Default .............................. .......................................... ................................... 83

6.9 Line Out 1 Pin Widget (Node ID = 0Ah) ...................... .......................................... ......................... 85

6.9.1 Audio Widget Capabilities ..................................................................................................... 85

6.9.2 Pin Capabilities ...................................................................................................................... 86

6.9.3 Connection List Length .......................................................................................................... 86

6.9.4 Supported Power States ....................................................................................................... 87

6.9.5 Connection List Entry ............................................................................................................ 87

6.9.6 Power States ......................................................................................................................... 87

6.9.7 Pin Widget Control ................................................................................................................ 88

6.9.8 Unsolicited Response Control ............................................................................................... 89

6.9.9 Pin Sense .............................................................................................................................. 90

6.9.10 EAPD/BTL Enable ............................................................................................................... 90

6.9.11 Configuration Default .............................. .......................................... ................................... 91

6.10 Line Out 2 Pin Widget (Node ID = 0Bh) ....................................................................................... 92

6.10.1 Audio Widget Capabilities ...................... ... .... ... ... ... .... ... ... ... ... .... ... ... ....... ... ... ... ... .... ... ... . ..... 92

6.10.2 Pin Capabilities .......................... ... .... ... ... ... .... ... .......................................... ......................... 93

6.10.3 Connection List Length ..................................... .......................................... ......................... 93

6.10.4 Connection List Entry ................................................. ... ... ... ... .... ... ... ................................... 94

6.10.5 Pin Widget Control .................... .......................................... ................................................ 94

6.10.6 EAPD/BTL Enable ............................................................................................................... 95

6.10.7 Configuration Default .............................. .......................................... ................................... 96

6.11 Line In 1/Mic In 2, Mic In 1/Line In 2 Pin Widgets (Node ID = 0Ch, 0Dh) .................................... 97

6.11.1 Audio Widget Capabilities ...................... ... .... ... ... ... .... ... ... ... ... .... ... ... ....... ... ... ... ... .... ... ... . ..... 97

6.11.2 Line In 1/Mic In 2 Pin Capabilities .............................................................. ... ... ... ....... ... ...... 97

6.11.3 Mic In 1/Line In 2 Pin Capabilities .............................................................. ... ... ... .... ... ... ...... 98

6.11.4 Input Amplifier Capabilities ............................ ................................... ................................... 99

6.11.5 Supported Power States ..................... .......................................... ...................................... 99

6.11.6 Power States ....... ... .......................................... .......................................... ......................... 99

6.11.7 Line In 1/Mic In 2 Pin Widget Control ......................... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ...... ... . 101

6.11.8 Mic In 1/Line In 2 Pin Widget Control .................. ....... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... .... 101

6.11.9 Unsolicited Response Control ................ ........................................................................... 102

6.11.10 Pin Sense ........................................................................................................................ 103

6.11.11 Mic In 1/Line In 2 EAPD/BTL Enable .............................................................................. 104

6.11.12 Line In 1/Mic In 2 Configuration Default .......................................................................... 104

6.11.13 Mic In 1/Line In 2 Configuration Default ..........................................................................105

6.11.14 Amplifier Gain/Mute ......................................................................................................... 106

6.12 Digital Mic In 1, Digital Mic In 2 Pin Widgets (Node ID = 0Eh, 12h) .... ... ... ... .... .......................... 108

6.12.1 Audio Widget Capabilities ...................... ... .... ... ... ... .... ... ... ... ... ....... ... ... .... ... ... ... ... .... ... ... .... 108

6.12.2 Pin Capabilities .......................... ... .... ... ... ... .... ... .......................................... ....................... 109

..

6.12.3 Input Amplifier Capabilities

6.12.4 Pin Widget Control .................... .......................................... .............................................. 110

6.12.5 Digital Mic In 1 Configuration Default ................................................................................ 110

6.12.6 Digital Mic In 2 Configuration Default ................................................................................ 111

6.12.7 Amplifier Gain/Mute ... ........................................................................................................ 112

6.13 S/PDIF Receiver Input Pin Widget (Node ID = 0Fh) ....... ........................................................... 114

6.13.1 Audio Widget Capabilities ...................... ... .... ... ... ... .... ... ... ... ... .... ... ... ....... ... ... ... ... .... ... ... . ... 114

6.13.2 Pin Capabilities .......................... ... .... ... ... ... .... ... .......................................... ....................... 115

6.13.3 Supported Power States ..................... .......................................... .................................... 115

6.13.4 Power States ....... ... .......................................... .......................................... ....................... 116

6.13.5 Pin Widget Control .................... .......................................... .............................................. 117

6.13.6 Unsolicited Response Control ................ ........................................................................... 117

....................................... ................................... .................... 109

DS880F4 5

Page 6

CS4207

6.13.7 Pin Sense .......................................................................................................................... 118

6.13.8 Configuration Default ......................................................................................................... 119

6.14 S/PDIF Transmitter 1, S/PDIF Transmitter 2 Output Pin Widgets (Node ID = 10h, 15h) ........... 120

6.14.1 Audio Widget Capabilities ................................................................................................. 120

6.14.2 Pin Capabilities .................................................................................................................. 121

6.14.3 Connection List Length ...................................................................................................... 121

6.14.4 S/PDIF Transmitter 1 Connection List Entry ..................................................................... 122

6.14.5 S/PDIF Transmitter 2 Connection List Entry ..................................................................... 122

6.14.6 Pin Widget Control ............................................................................................................ 123

6.14.7 S/PDIF Transmitter 1 Configuration Default ...................................................................... 124

6.14.8 S/PDIF Transmitter 2 Configuration Default ...................................................................... 125

6.15 Vendor Processing Widget (Node ID = 11h) .............................................................................. 126

6.15.1 Audio Widget Capabilities ................................................................................................. 126

6.15.2 Processing Capabilities ..................................................................................................... 126

6.15.3 Processing State ............................................................................................................... 127

6.15.4 Coefficient Index ................................................................................................................ 127

6.15.5 Processing Coefficient ....................................................................................................... 128

6.15.6 Coefficient Registers ......................................................................................................... 128

6.15.6.1 S/PDIF RX/TX Interface Status (CIR = 0000h) .................. ... ... .... ... ... ... ... .... ... ... ... . 129

6.15.6.2 S/PDIF RX/TX Interface Control (CIR = 0001h) ...................................... .... ... ....... 130

6.15.6.3 ADC Configuration (CIR = 0002h) ........................................................................ . 131

6.15.6.4 DAC Configuration (CIR = 0003h) ........................................................................ . 134

6.15.6.5 Beep Configuration (CIR = 0004h) ........................................................................ 135

6.16 Beep Generator Widget (Node ID = 13h) .................................................................................. 136

6.16.1 Audio Widget Capabilities ................................................................................................. 136

6.16.2 Beep Generation Control ........................ ... .... ... ... ... .......................................... ... .............. 137

7. APPLICATIONS ................................................................................................................................. 138

7.1 HD Audio Interface ....................................................................................................................... 138

7.1.1 Multi-Channel Streams ................................ .... ... ... ... .... ... ... .......................................... ....... 138

7.2 Analog Inputs ............................................................................................................................... 139

7.3 Analog Outputs ............................................................................................................................ 142

7.3.1 Output Filter .............................. .......................................... ................................................. 142

7.3.2 Analog Supply Removal ..... ... ... .......................................... .......................................... ... .... 142

7.4 Digital Mic Inputs .......................................................................................................................... 142

7.5 S/PDIF Input and Outputs ............................................................................................................ 143

7.5.1 S/PDIF Receiver SRC .........................................................................................................143

8. PCB LAYOUT CONSIDERATIONS ...................................................................................................144

8.1 Power Supply, Grounding ............................................................................................................ 144

8.2 QFN Thermal Pad ........................................................................................................................144

9. PARAMETER DEFINITIONS .............................................................................................................. 145

10. QFN PACKAGE DIMENSIONS ........................................................................................................ 146

THERMAL CHARACTERISTICS ....................................................................................................... 146

11. ORDERING INFORMATION ............................................................................................................ 147

12. REFERENCES .................................................................................................................................. 147

13. REVISION HISTORY ........................................................................................................................ 148

6 DS880F4

Page 7

LIST OF FIGURES

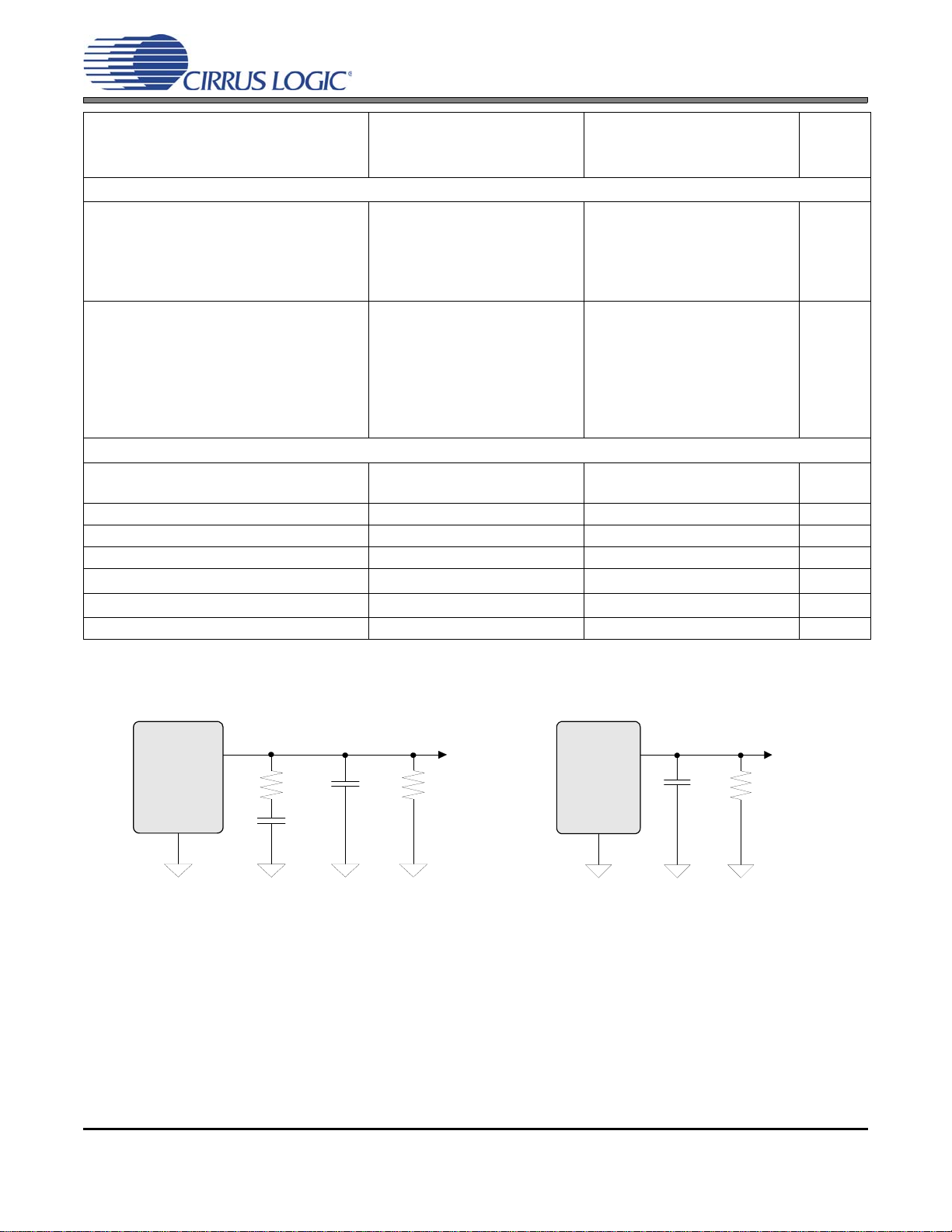

Figure 1.Typical Connection Diagram - Desktop System ......................................................................... 11

Figure 2.Typical Connection Diagram - Portable System ......................................................................... 12

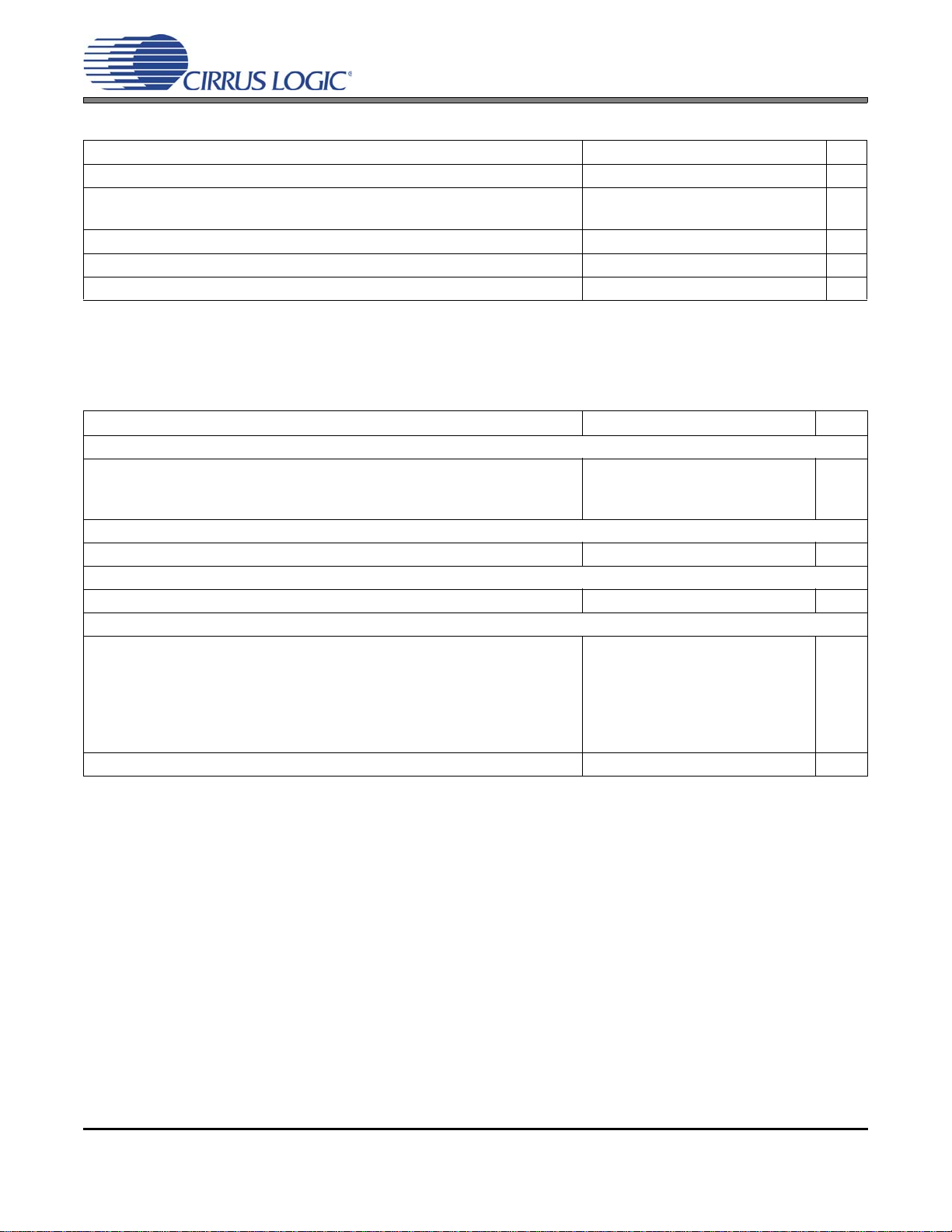

Figure 3.Output Test Load, Headphone Out ............................................................................................. 18

Figure 4.Output Test Load, Line Out ......................................................................................................... 18

Figure 5.Output Test Load, Headphone Out ............................................................................................. 20

Figure 6.Output Test Load, Line Out ......................................................................................................... 20

Figure 7.Digital MIC Interface Timing ........................................................................................................ 22

Figure 8.PS-SettingsReset Behavior ........................................................................................................ 28

Figure 9.Jack Presence Detect Circuit ...................................................................................................... 31

Figure 10.Software Programming Model .................................................................................................. 33

Figure 11.Single-Ended Input Filter ........................................................................................................ 139

Figure 12.Pseudo-Differential Input Filter ............................................................................................... 140

Figure 13.Differential Input Filter ............................................................................................................. 141

Figure 14.Differential to Single-Ended Output Filter ........... ... ... ... .... ...... ... ... .... ... ... ... .... ... ... ... ... .... ... .. ..... 142

Figure 15.Passive Single-Ended Output Filter ........................................................................................ 142

LIST OF TABLES

Table 1. Register Settings Across Reset Conditions ................................................................................ 29

Table 2. Device Node ID Summary ........................... ... .......................................... ................................... 34

Table 3. Pin Configuration Register Defaults ............................................................................................ 35

Table 4. Stream Format Examples ......................................................................................................... 138

Table 5. Line In 1/Mic In 2 Input Topology Register Settings .............................. ............. ............. .......... 139

Table 6. Mic In 1/Line In 2 Input Topology Register Settings .................................................................. 139

CS4207

DS880F4 7

Page 8

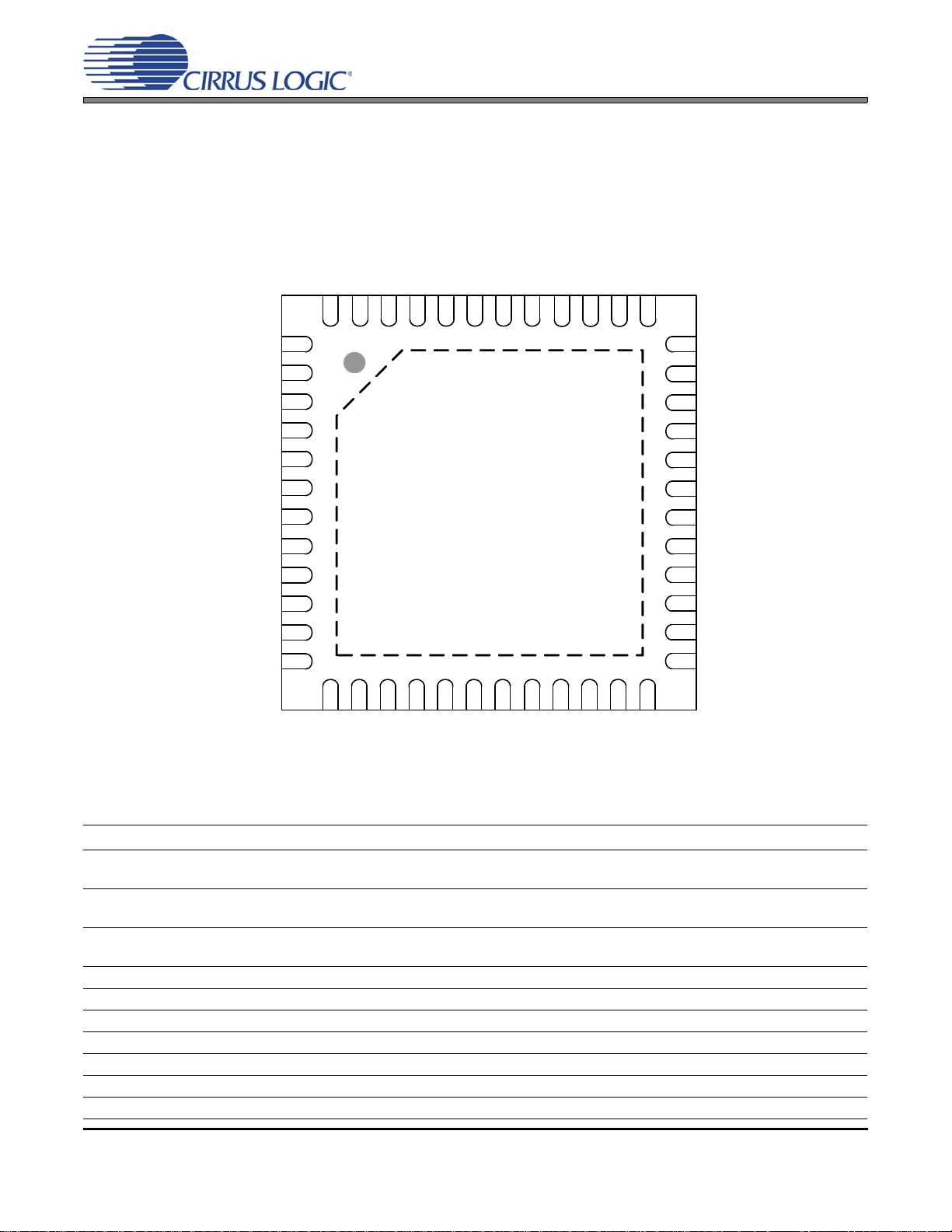

1. PIN DESCRIPTIONS

HPREF

Thermal Pad

1413

8

7

6

5

4

3

2

1

15

16

17 18 19 20

29

30

31

32

33

34

35

36

41

424344

45

464748

37

38

3940

12

11

10

9

21 22 23 24

25

26

27

28

SPDIF_OUT1

SENSE_A

VL_IF

LINEOUT_R1+

Top-Down (Through Package) View

48-Pin QFN Package

LINEOUT_L1+

LINEOUT_L1-

LINEOUT_R2-

LINEOUT_R2+

LINEOUT_L2+

LINEOUT_L2-

VBIAS (DAC)

VCOM

VREF+ (ADC)

AGND

VA

SPDIF_IN

FLYN

FLYC

VHP_FILT-

FLYP

HPOUT_L

HPREF

HPOUT_R

VA_HP

LINEOUT_R1-

GPIO0/DMIC_SDA1

VL_HD

DMIC_SCL

SDO

BITCLK

DGND

SDI

VD

SYNC

RESET#

GPIO1/DMIC_SDA2

/SPDIF_OUT2

MICBIAS

MICIN_L-

MICIN_L+

MICIN_R+

GPIO2

GPIO3

MICIN_R-

LINEIN_L+

LINEIN_C-

LINEIN_R+

VA_REF

VHP_FILT+

HPGND

1.1 CS4207 48-pin QFN Pinout:

CS4207

Pin Name QFN Pin Description

VL_IF 1

GPIO0/

DMIC_SDA1

VL_HD 3

DMIC_SCL 4 Digital Mic Clock (Output) - The high speed clock output to the digital microphone.

SDO 5 Serial Data Input (Input) - Serial data input stream from the HD Audio Bus.

BITCLK 6 Bit Clock (Input) - 24 MHz bit clock from the HD Audio Bus.

DGND 7 Digital Ground (Input) - Ground reference for the internal digital section.

SDI 8 Serial Data Output (Input/Output) - Serial data output stream to the HD Audio Bus.

VD 9 Digital Power (Input) - Positive power for the internal digital section.

SYNC 10 Sync Clock (Input) - 48 kHz sync clock from the HD Audio Bus.

8 DS880F4

2

Digital Interface Signal Level (Input) - Digital supply for the GPIO, S/PDIF and Digital Mic inter-

faces. Refer to the Recommended Operating Conditions for appropriate voltages.

General Purpose I/O (Input/Output) - General purpose input or output line, or

Digital Mic Data Input (Input) - The first data input line from a digital microphone.

Digital Interface Signal Level (Input) - Digital supply for the HD Audio interface. Refer to the

Recommended Operating Conditions for appropriate voltages.

Page 9

CS4207

Pin Name QFN Pin Description

RESET# 11 Reset (Input) - The device enters a low power mode when this pin is driven low.

GPIO1/

DMIC_SDA2/

SPDIF_OUT2

SENSE_A 13 Jack Sense Pin (Input/Output) - Jack sense detect.

GPIO2 14 General Purpose I/O (Input/Output) - General purpose input or output lines.

GPIO3 15 General Purpose I/O (Input/Output) - General purpose input or output lines.

MICBIAS 16

MICIN_L-

MICIN_L+

MICIN_R+

MICIN_R-

LINEIN_L+

LINEIN_CLINEIN_R+

VA_REF

VA

AGND 26 Analog Ground (Input) - Ground reference for the internal analog section.

VREF+ 27 Positive Voltage Reference (Ou

VCOM 28 Quiescent Voltage (Output) - Filter connection for internal quiescent voltage.

VBIAS 29 Positive Voltage Reference (Output) - Positive reference voltage for the internal DACs.

LINEOUT_L2-

LINEOUT_L2+

LINEOUT_R2+

LINEOUT_R2LINEOUT_L1LINEOUT_L1+

LINEOUT_R1+

LINEOUT_R1-

HPOUT_L

HPOUT_R

HPREF 39 Pseudo Diff. Headphone Reference (Input) - Ground reference for the headphone amplifiers.

VHP_FILT- 41

FLYN 42

FLYC 43

VHP_FILT+ 44

FLYP 45

VA_HP 46

SPDIF_IN 47 S/PDIF Input (Input) - Input to internal S/PDIF Receiver.

SPDIF_OUT1 48 S/

HPGND TP

12

17

18

19

20

21

22

23

24

25

30

31

32

33

34

35

36

37

38

40

General Purpose I/O (Input/Output) - General purpose input or output line, or

Digital Mic Data Input (Input) - The second data input line from a digital microphone, or

S/PDIF Output (Output) - Output from internal S/PDIF Transmitter.

Microphone Bias (Output) - Provides a low noise bias supply for an external microphone. Elec-

trical characteristics are specified in the DC Electrical Characteristics table.

Microphone Input Left/Right (Input) - The full-scale level is specified in the ADC Analog Characteristics specification table.

Analog Input (Input) - The full-scale level is specified in the ADC Analog Characteristics specification table.

Analog Power (Input) - Positive power for the internal analog section. VA_REF is the return pin

for the VBIAS cap.

tp

ut) - Positive reference voltage for the internal ADCs.

Analog Audio Output (Output) - The full-scale output level is specified in the DAC Analog Char-

acteristics specification table

Analog Headphone Output (Output) - The full-scale output level is specified in the DAC Analog

Characteristics specification table.

Inverting Charge Pump Filter Connection (Output) - Power suppl y from the inverting charge

pump that provides the negative rail for the headphone amplifier.

Charge Pump Cap Negative Node (Output) - Negative node for the inverting charge pump’s flying capacitor.

Charge Pump Cap Common Node (Output) - Common positive node for the step-down and

inverting charge pumps’ flying capacitor.

Non-Inverting Charge Pump Filter Connection (Output) - Power supply from the step-down

charge pump that provides the positive rail for the headphone amplifier.

Charge Pump Cap Positive Node (Output) - Positive node for the step-down charge pump’s flying capacitor.

Analog Power For Headphone (Input) - Positive power for the internal analog headphone section.

Output (Output) - Output from internal S/PDIF Transmitter.

PDIF

HP Ground (Input) - Ground reference for the internal headphone section. See “QFN Thermal

Pad” on page 144 for more information.

DS880F4 9

Page 10

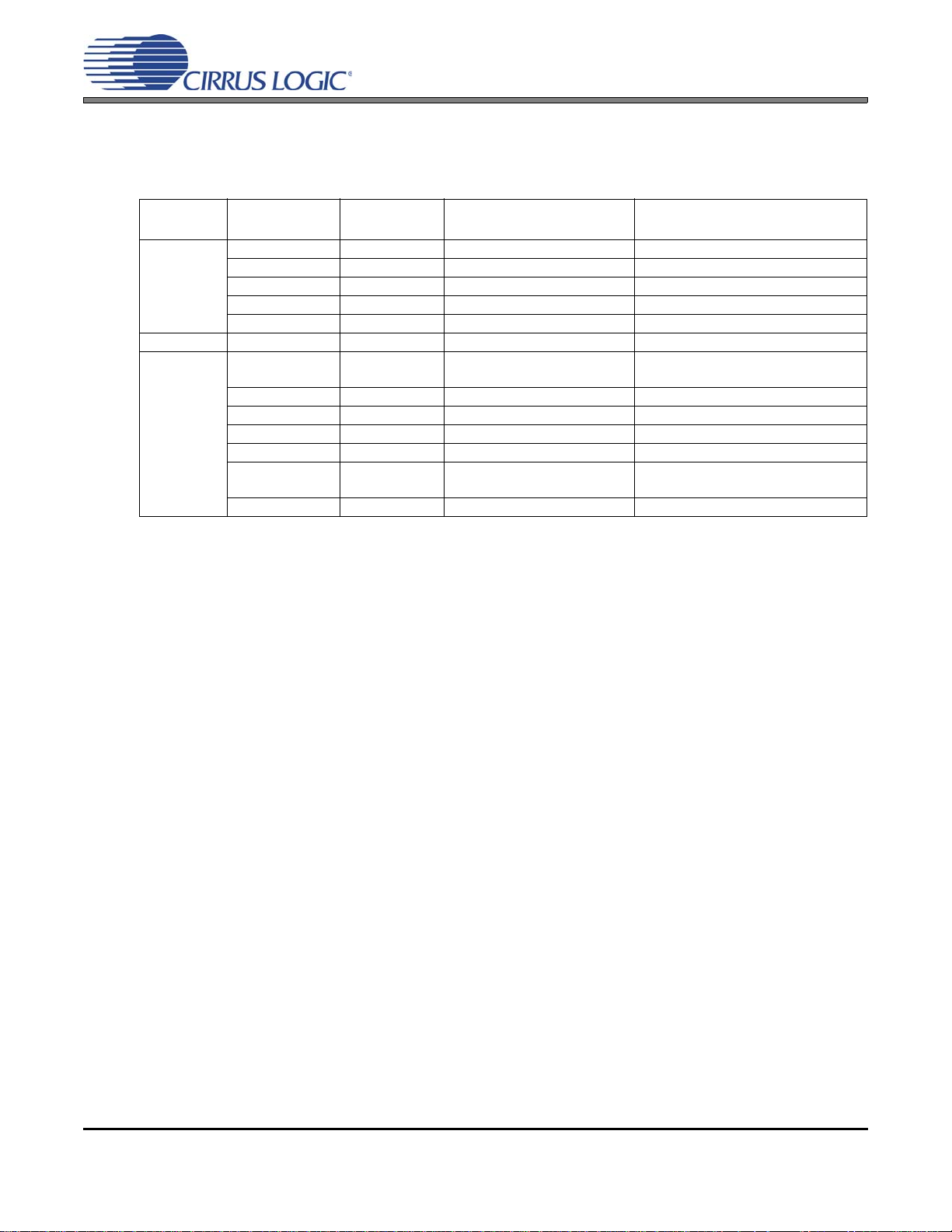

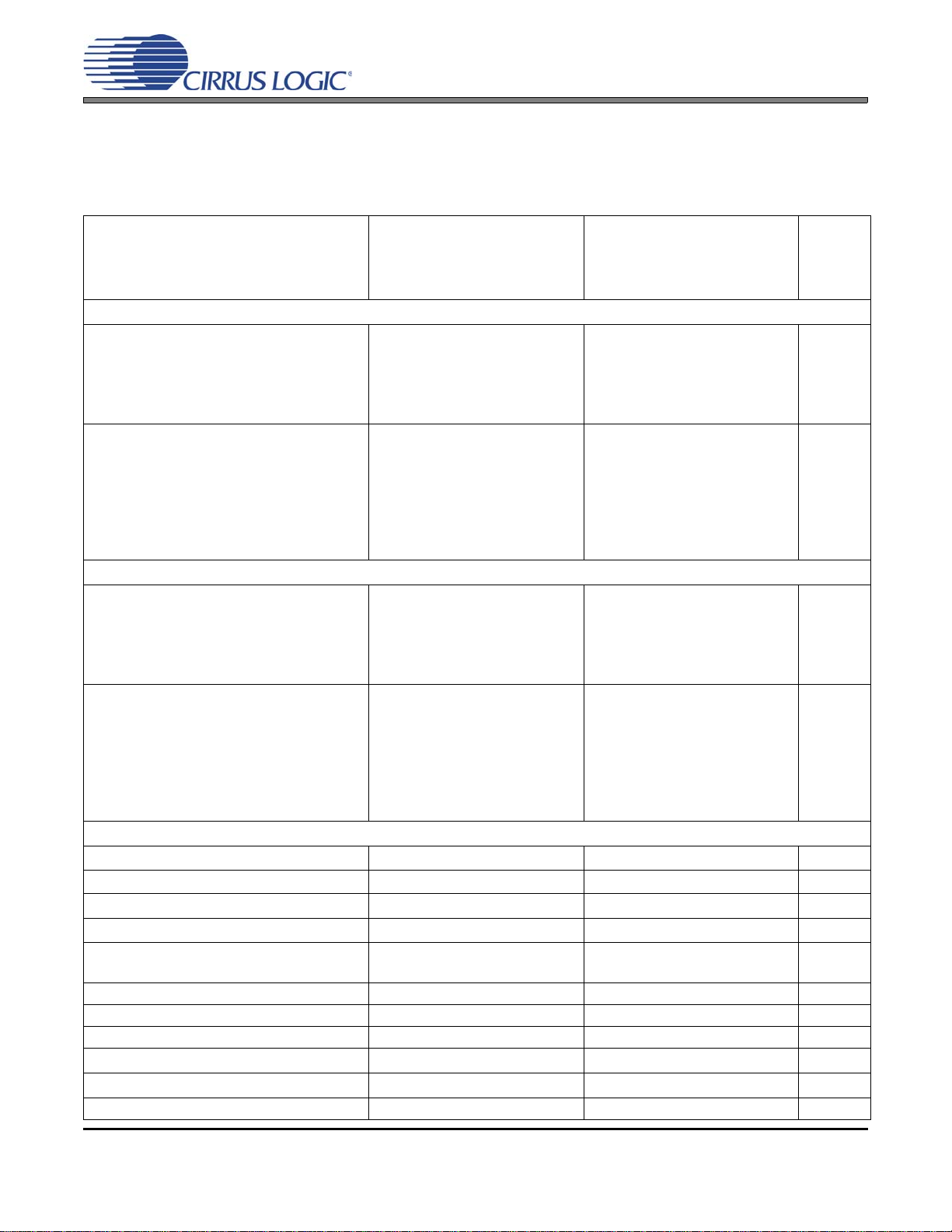

1.2 Digital I/O Pin Characteristics

Input and output levels and associated power supply voltage are shown in the table below. Logic levels

should not exceed the corresponding power supply voltage.

CS4207

Notes:

Power

Supply

VL_HD

VA SENSE_A Input - 3.3 V - 5.0 V

VL_IF

Pin Name

SW/(HW)

RESET# Input - 1.5 V - 3.3 V

SDO Input - 1.5 V - 3.3 V

BITCLK Input - 1.5 V - 3.3 V

SDI (Note 1) Input/Output 1.5 V - 3.3 V 1.5 V - 3.3 V

SYNC Input - 1.5 V - 3.3 V

GPIO1/

DMIC_SDA2

GPIO2 Input/Output 3.3 V 3.3 V

GPIO3 Input/Output 3.3 V 3.3 V

SPDIF_IN Input - 3.3 V

SPDIF_OUT Output 3.3 V -

GPIO0/

DMIC_SDA1

DMIC_SCL Output 3.3 V -

I/O Driver Receiver

Input/Output 3.3 V 3.3 V

Input/Output 3.3 V 3.3 V

1. SDI output functionality also requires the VA and VL_IF rails to be at nominal levels.

10 DS880F4

Page 11

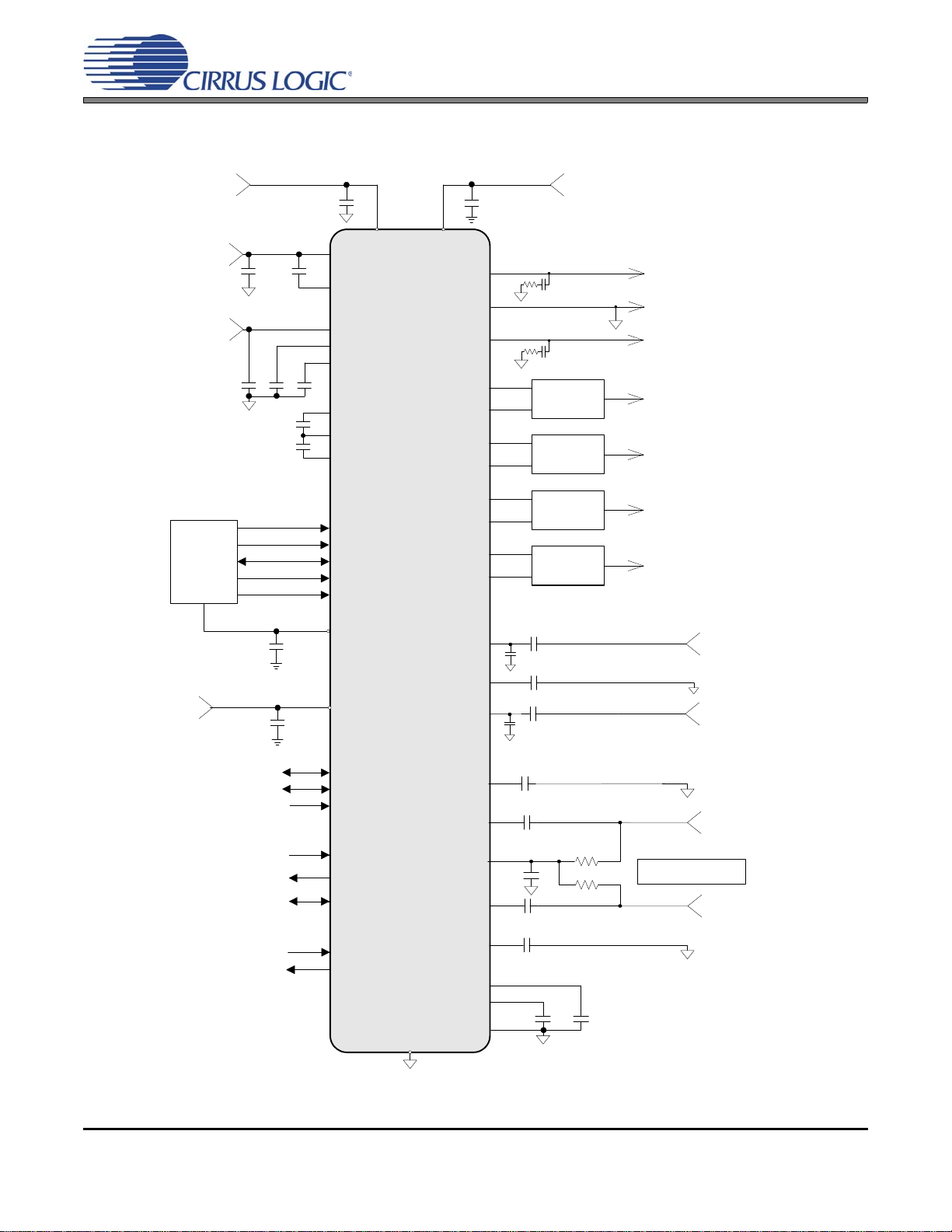

2. TYPICAL CONNECTION DIAGRAMS

1 µF

VREF+

0.1 µF

HP_GND(Thermal Pad)

VL_HD

0.1 µF

+1.5 V to +3.3 V

RESET#

SDI

BITCLK

SYNC

VA

* Capacitors must be C0G or equivalent

MICIN_L+

Differential Mic Left

SDO

CS4207

MICBIAS

HPOUT_L

HPOUT_R

R

L

The value of RL is dictated by

the microphone cartridge.

HD Audio

Bus

Left Headphone

FLYP

VHP_FILT+

2.2 µF

Microphone Bias

1 µF

0.47 µF

10 µF

**

**

** Use low ESR

ceramic capacitors.

LINEOUT_L1+

+Left Line Output 1

LINEOUT_L1-

Right Headphone

LINEOUT_R1+

+Right Line Output 1

LINEOUT_R1-

0.1 µF

33

1 µF

MICIN_L-

1 µF

R

L

Differential Mic Right

1 µF

MICIN_R+

MICIN_R-

LINEOUT_L2+

+Left Line Output 2

LINEOUT_L2-

LINEOUT_R2+

+Right Line Output 2

LINEOUT_R2-

GPIO2

GPIO2

GPIO3

GPIO3

SPDIF_IN

SPDIF_OUT1

S/PDIF TX 1

S/PDIF RX

SENSE_A

SENSE_A

DMIC_SDA1D-Mic In 1

HPREF

0.1 µF

33

Headphone Ground

+5.0 V

Differential to

Single-Ended

Output Filter

Differential to

Single-Ended

Output Filter

Differential to

Single-Ended

Output Filter

Differential to

Single-Ended

Output Filter

VA_HP

2.2 µF

**

FLYN

VHP_FILT-

+1.8 V

0.1 µF

VD

+5.0 V

AGND

10 µF0.1 µF

**

VL_IF

0.1 µF

+3.3 V

FLYC

VCOM

10 µF

‡ Input and Output

filters are optional.

‡

‡

‡

‡

DMIC_SDA2/

SPDIF_OUT2

D-Mic In 2 / S/PDIF TX 2

DMIC_SCL

D-Mic Clk

LINEIN_L+

LINEIN_C-

LINEIN_R+

Left Analog Input

1 µF

1800 pF

*

1 µF

Right Analog Input

1 µF

1800 pF

*

10 µF

VBIAS

+

VA_REF

0.1 µF

+5.0 V

Figure 1. Typical Connection Diagram - Desktop System

*** See Figure 9.

***

CS4207

DS880F4 11

Page 12

CS4207

* Capacitors must be C0G or equivalent

Speaker Driver

2200 pF

560

*

Speaker Driver

2200 pF

560

*

560

560

1 µF

VREF+

0.1 µF

HP_GND(Thermal Pad)

VL_HD

0.1 µF

+1.5 V to +3.3 V

RESET#

SDI

BITCLK

SYNC

VA

MICIN_L+

SDO

CS4207

MICBIAS

HPOUT_L

HPOUT_R

LINEIN_L+

Left Mic In

LINEIN_C-

R

L

The value of RL is dictated by

the microphone cartridge.

HD Audio

Bus

Left Headphone

LINEIN_R+

Right Mic In

FLYP

VHP_FILT+

2.2 µF

Microphone Bias

1 µF

0.47 µF

10 µF

**

**

* *Use low ESR

ceramic capacitors.

LINEOUT_L1+

LINEOUT_L1-

Right Headphone

LINEOUT_R1+

LINEOUT_R1-

0.1 µF

33

MICIN_L-

1 µF

R

L

MICIN_R+

LINEOUT_L2+

LINEOUT_L2-

LINEOUT_R2+

LINEOUT_R2-

GPIO2

GPIO2

GPIO3

GPIO3

SENSE_A

SENSE_A

HPREF

0.1 µF

33

Headphone Ground

+3.3 V

VA_HP

2.2 µF

**

FLYN

VHP_FILT-

+1.8 V

0.1 µF

VD

+3.3 V

AGND

10 µF0.1 µF

**

VL_IF

0.1 µF

+3.3 V

FLYC

VCOM

10 µF

MICIN_R-

Left Analog Input

1 µF

1800 pF

*

1 µF

Right Analog Input

1 µF

1800 pF

*

SPDIF_IN

SPDIF_OUT1

S/PDIF TX 1

S/PDIF RX

DMIC_SDA1

D-Mic In 1

D-Mic In 2 / S/PDIF TX 2

DMIC_SCL

D-Mic Clk

DMIC_SDA2/

SPDIF_OUT2

10 µF

VBIAS

+

VA_REF

0.1 µF

+3.3 V

Figure 2. Typical Connection Diagram - Portable System

*** See Figure 9.

***

12 DS880F4

Page 13

CS4207

3. CHARACTERISTICS AND SPECIFICATIONS

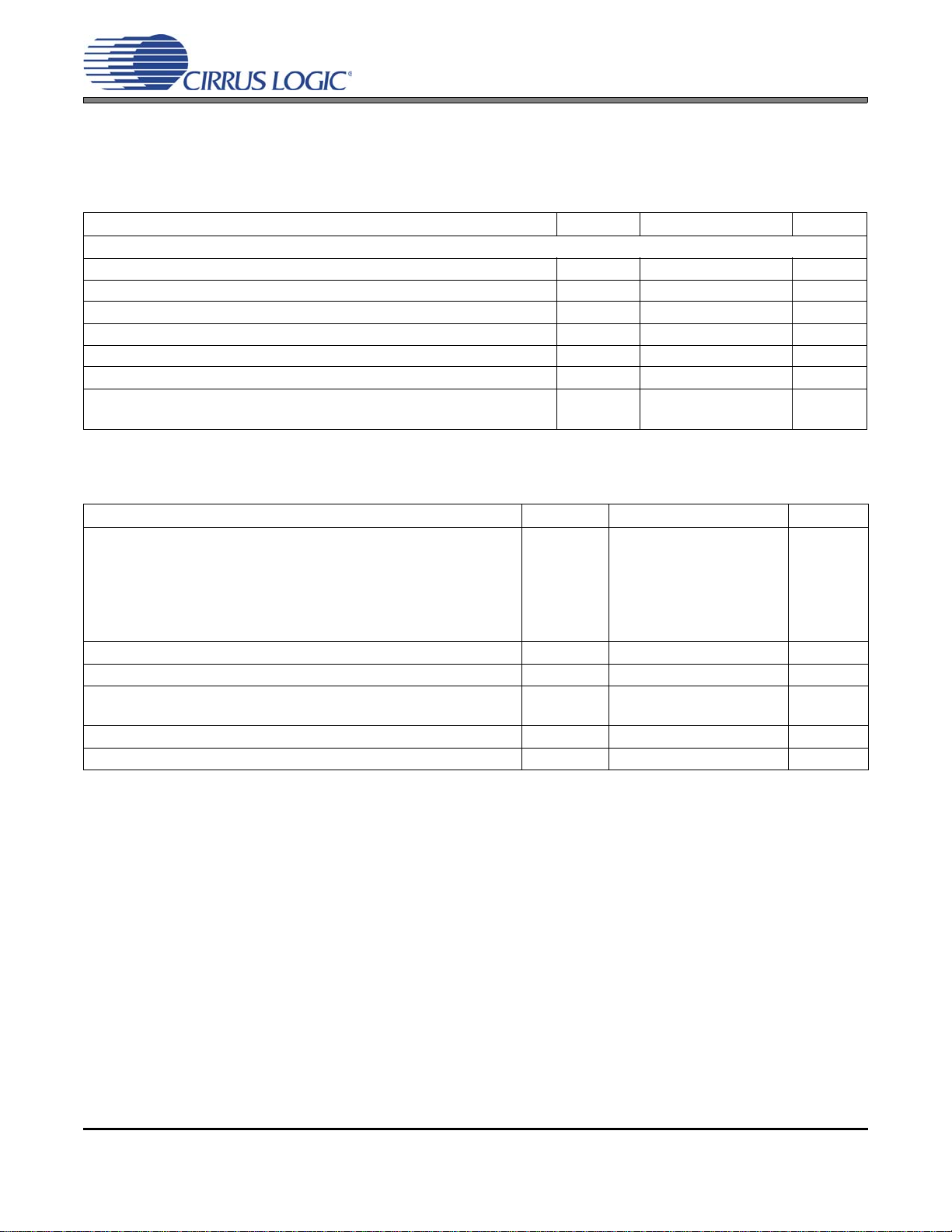

RECOMMENDED OPERATING CONDITIONS

(AGND=DGND=0 V, all voltages with respect to ground.)

Parameters Symbol Min Max Units

DC Power Supply (Note 1)

Analog Core VA 2.97 5.25 V

DAC Reference VA_REF 2.97 5.25 V

Headphone Amplifier VA_HP 2.97 5.25 V

Digital Core VD 1.42 1.89 V

HD Audio Bus Interface VL_HD 1.42 3.47 V

GPIO, S/PDIF and Digital Mic Interface VL_IF 2.97 3.47 V

Ambient Temperature Commercial - CNZ

Automotive - DNZ

T

A

-40

-40

+85

+105

C

C

ABSOLUTE MAXIMUM RATINGS

(AGND = DGND = 0 V; all voltages with respect to ground.)

Parameters Symbol Min Max Units

DC Power Supply Analog Core

DAC Reference

Headphone Amplifier

Digital Core

HD Audio Interface

GPIO, S/PDIF and Digital Mic Interface

Input Current (Note 2) I

Analog Input Voltage (Note 3)

Digital Input Voltage (Note 3) HD Audio Interface

GPIO, S/PDIF and Digital Mic Interface

Ambient Operating T emperature (power applied) T

Storage Temperature T

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation

is not guaranteed at these extremes.

VA

VA_REF

VA_HP

VD

VL_HD

VL_IF

in

V

IN

V

IND

A

stg

-0.3

-0.3

-0.3

-0.3

-0.3

-0.3

-±10mA

AGND-0.7 VA+0.7

-0.3

-0.3

-55 +115 °C

-65 +150 °C

5.5

5.5

5.5

3.0

4.0

4.0

VL_HD+0.4

VL_IF+0.4

V

V

V

V

V

V

V

V

V

Notes:

1. The device will operate properly over the full range of the analog, digital and interface supplies.

2. Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause

SCR latch-up.

3. The maximum over/under voltage is limited by the input current.

DS880F4 13

Page 14

CS4207

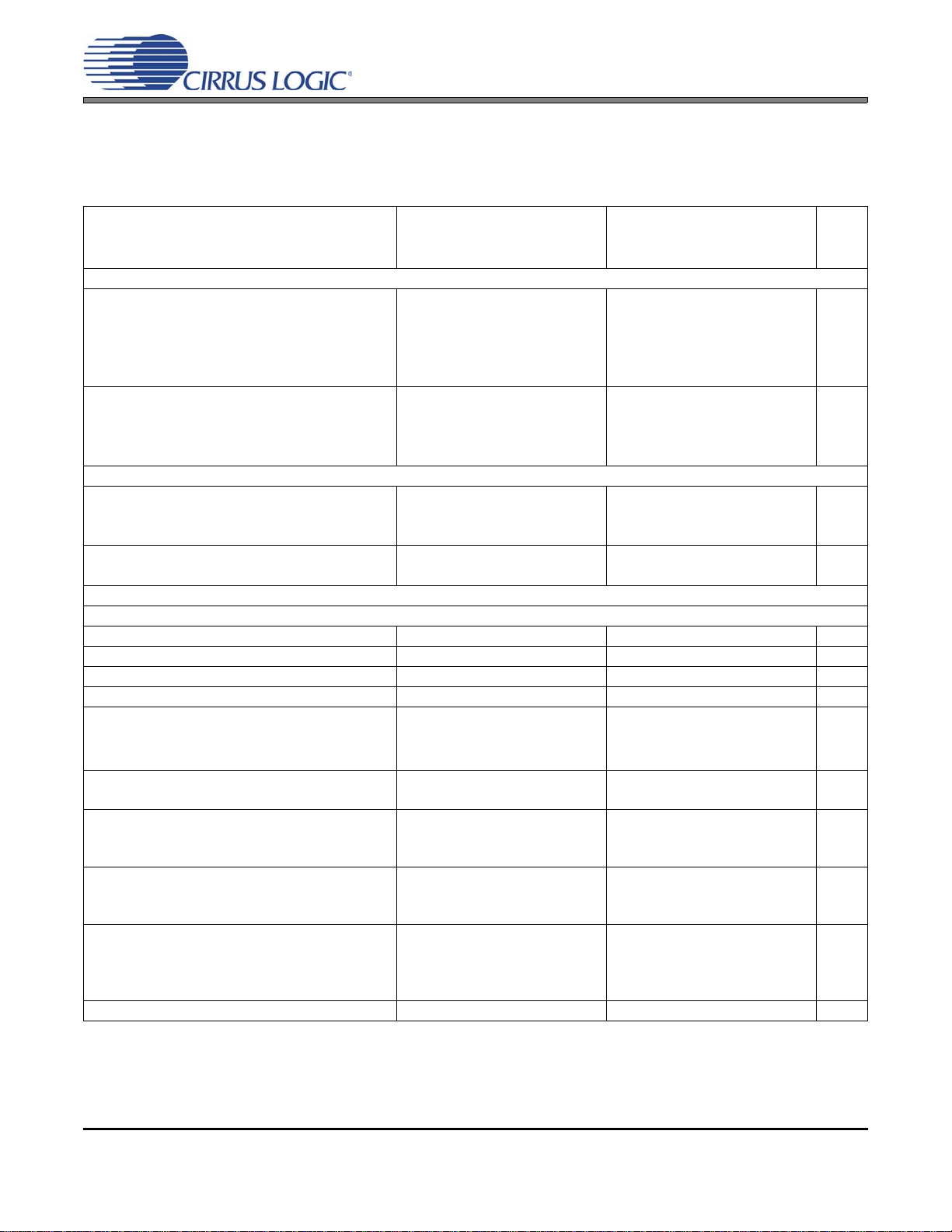

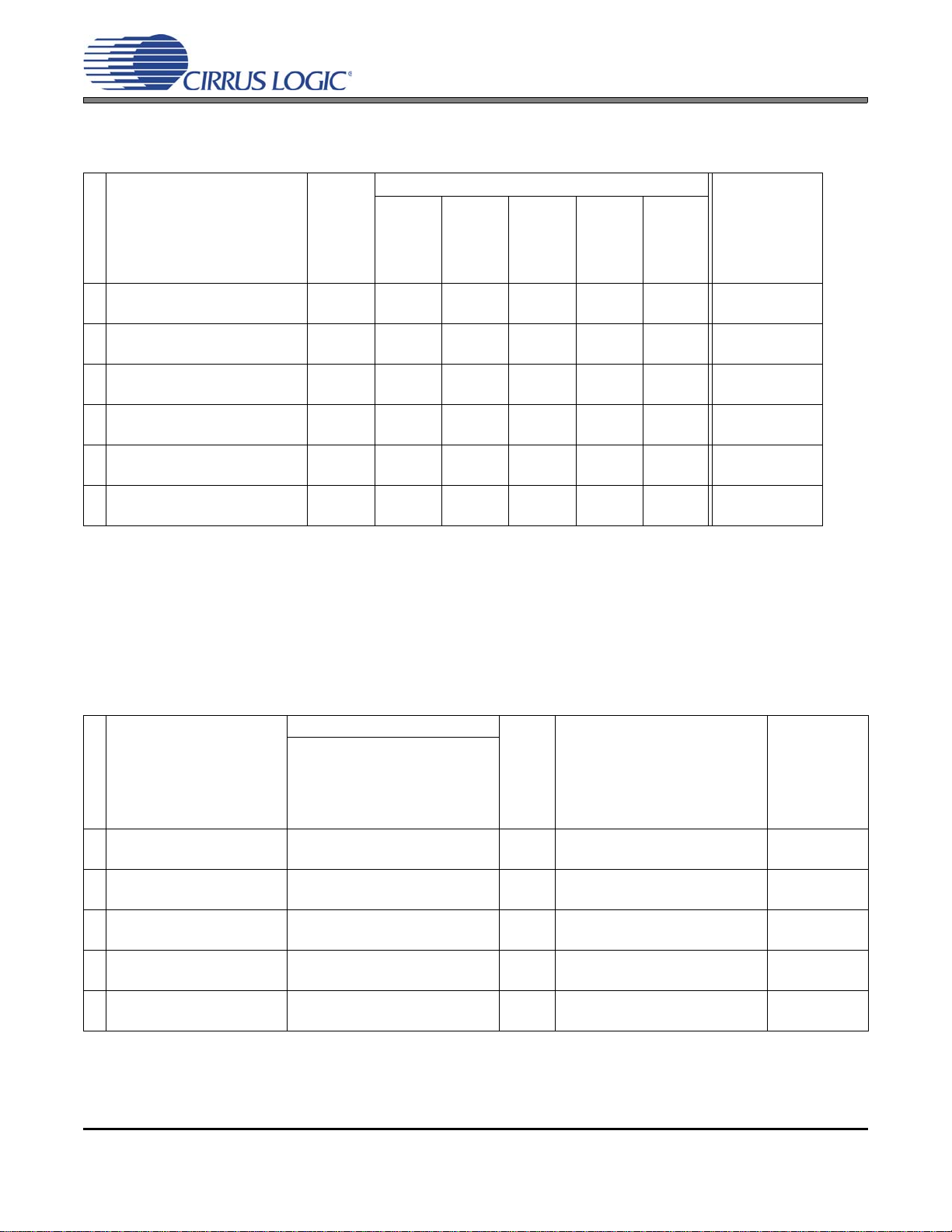

ANALOG INPUT CHARACTERISTICS (COMMERCIAL - CNZ)

(Test Conditions (unless otherwise specified): Input sine wave (relative to digital full-scale): 1 kHz through passive

input filter; VA_HP = VA; VL_HD = VL_IF = 3.3; VD = 1.8 V; T

20 kHz unless otherwise specified. Sample Frequency = 48 kHz)

= +25C; Measurement Bandwidth is 10 Hz to

A

Parameter

(Note 4)

VA, VA_REF = 5.0 V

(Differential/Single-ended)

Min Typ Max Min Typ Max Unit

VA, VA_R EF = 3.3 V

(Differential/Single-ended)

Line In to PGA to ADC (ADC1 or ADC2; differential perf. characteristics only valid for ADC2)

Dynamic Range

PGA Setting: 0 dB A-weighted

unweighted

PGA Setting: +12 dB A-weighted

unweighted

99/96

96/93

95/86

92/83

105/102

102/99

101/92

98/89

-

-

-

-

95/93

92/90

92/83

89/80

101/99

98/96

98/89

95/86

-

-

-

-

dB

dB

dB

dB

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

-60 dBFS

-

-

-88/-88

-42/-39

-82/-82

-36/-33

-

-

-95/-92

-38/-36

-89/-86

-32/-30dBdB

PGA Setting: +12 dB -1 dBFS - -88/-88 -82/-82 - -92/-86 -86/-80 dB

Mic In to PGA to ADC (+20 dB) (ADC1 or ADC2; differential perf. characteristics only valid fo r ADC2 )

Dynamic Range

A-weighted

unweighted

86/78

83/75

92/84

89/81

-

-

83/75

80/72

89/81

86/78

-

-

dB

dB

Total Harmonic Distortion + Noise

-1 dBFS - -89/-82 -83/-76 - -86/-78 -80/-72 dB

Other Analog Characteristics

DC Accuracy

Interchannel Gain Mismatch - 0.2 - - 0.2 - dB

Gain Drift - ±100 - - ±100 -

ppm/°C

Offset Error High Pass Filter On - 352 - - 352 - LSB

Interchannel Isolation - 90 - - 90 - dB

HP Amp to Analog Input Isolation

R

= 10 k

L

= 16

R

L

-

-

100

70

-

-

-

-

100

70

-

-

dB

dB

Full-scale Input Voltage - Line In/Mic In

(Differential Inputs)

PGA(0dB) 1.58•VA 1.66•VA 1.74•VA 1.58•VA 1.66•VA 1.74•VA Vpp

Full-scale Input Voltage - Line In

(Single-ended Inputs) PGA (+12dB)

PGA (0dB)

0.79•VA 0.83•VA

0.21•VA

0.87•VA 0.79•VA 0.83•VA

0.21•VA

0.87•VA Vpp

Vpp

Full-scale Input Voltage - Mic In

PGA+Boost(0dB)

(Single-ended Inputs) PGA+Boost(+20dB)

Input Impedance (Note 5)

Mic In (Differential or Pseudo-Diff)

Line In (Pseudo-Diff, PGA = -12/0/+12 dB)

Mic/Line In (Single-Ended, PGA = -12/0/+12 dB)

Common Mode Rejection (Differential Inputs)

0.79•VA 0.83•VA

0.08•VA

-

-

-

43.5

93/99/103

27/33/37

-60--60-dB

0.87•VA 0.79•VA 0.83•VA

0.08•VA

-

-

-

-

-

-

43.5

93/99/103

27/33/37

0.87•VA Vpp

Vpp

-

-

-

k

k

k

14 DS880F4

Page 15

CS4207

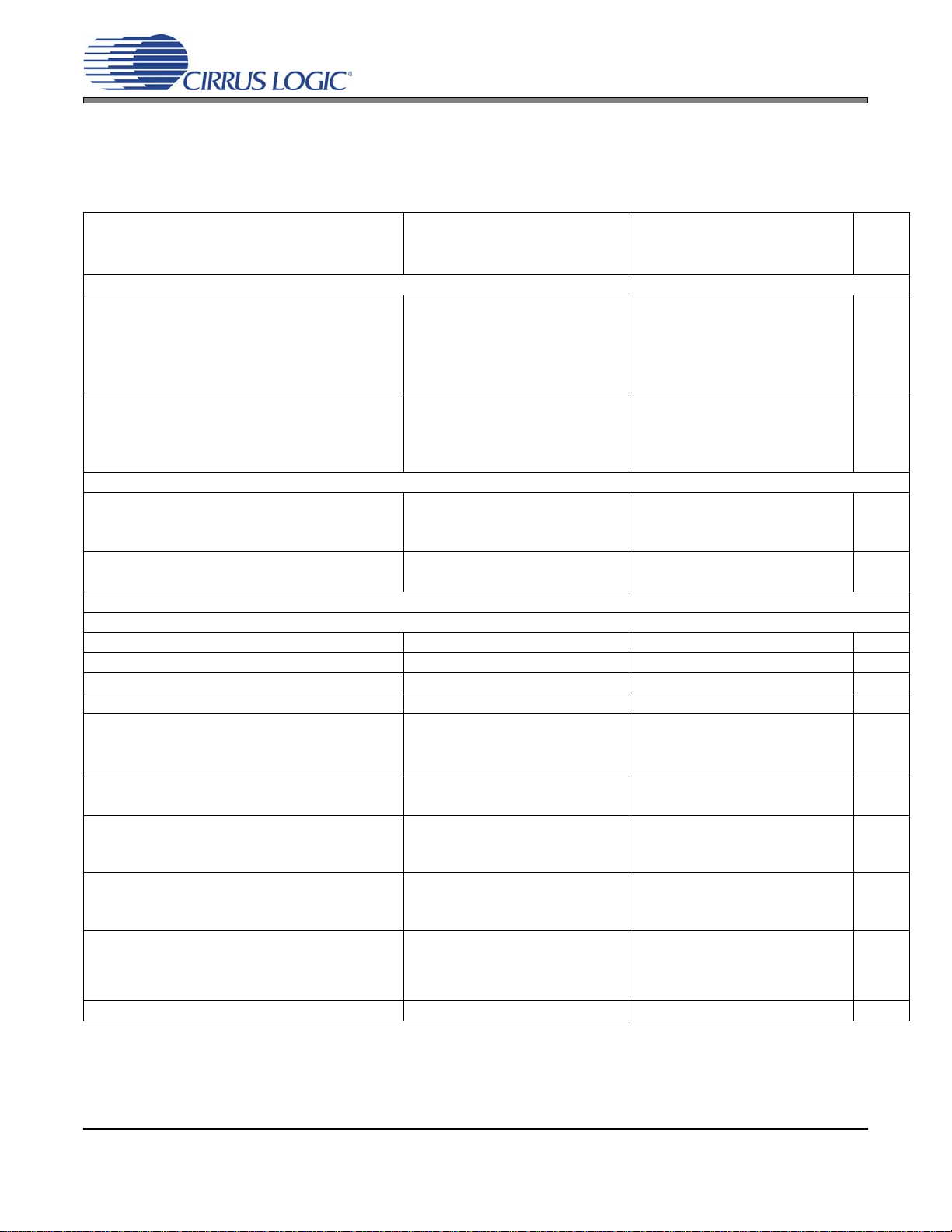

ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE - DNZ)

(Test Conditions (unless otherwise specified): Input sine wave (relative to digital full-scale): 1 kHz through passive

input filter; VA_HP = VA; VL_HD = VL_IF = 3.3; VD = 1.8 V; T

to 20 kHz unless otherwise specified. Sample Frequency = 48 kHz)

= -40 to +85C; Measurement Bandwidth is 10 Hz

A

Parameter

(Note 4)

VA, VA_REF = 5.0 V

(Differential/Single-ended)

Min Typ Max Min Typ Max Unit

VA, VA_REF = 3.3 V

(Differential/Single-ended)

Line In to PGA to ADC (ADC1 or ADC2; differential perf. characteristics only valid for ADC2)

Dynamic Range

PGA Setting: 0 dB A-weighted

unweighted

PGA Setting: +12 dB A-weighted

unweighted

99/96

96/93

95/86

92/83

105/102

102/99

101/92

98/89

-

-

-

-

95/93

92/90

92/83

89/80

101/99

98/96

98/89

95/86

-

-

-

-

dB

dB

dB

dB

Total Harmonic Distortion + Noise

PGA Setting: 0 dB -1 dBFS

-60 dBFS

-

-

-88/-88

-42/-39

-82/-82

-36/-33

-

-

-95/-92

-38/-36

-89/-86

-32/-30

dB

dB

PGA Setting: +12 dB -1 dBFS - -88/-88 -82/-82 - -92/-86 -86/-80 dB

Mic In to PGA to ADC (+20 dB) (ADC1 or ADC2; differential perf. characteristics only valid for ADC2)

Dynamic Range

A-weighted

unweighted

86/78

83/75

92/84

89/81

-

-

83/75

80/72

89/81

86/78

-

-

dB

dB

Total Harmonic Distortion + Noise

-1 dBFS - -89/-82 -83/-76 - -86/-78 -80/-72 dB

Other Analog Characteristics

DC Accuracy

Interchannel Gain Mismatch - 0.2 - - 0.2 - dB

Gain Drift - ±100 - - ±100 -

ppm/°C

Offset Error High Pass Filter On - 352 - - 352 - LSB

Interchannel Isolation - 90 - - 90 - dB

HP Amp to Analog Input Isolation

R

= 10 k

L

R

= 16

L

-

-

100

70

-

-

-

-

100

70

-

-

dB

dB

Full-scale Input Voltage - Line In/Mic In

(Differential Inputs)

PGA(0dB) 1.58•VA 1.66•VA 1.74•VA 1.58•VA 1.66•VA 1.74•VA Vpp

Full-scale Input Voltage - Line In

(Single-ended Inputs) PGA(+12dB)

PGA(0dB)

0.79•VA 0.83•VA

0.21•VA

0.87•VA 0.79•VA 0.83•VA

0.21•VA

0.87•VA Vpp

Full-scale Input Voltage - Mic In

PGA+Boost(0dB)

(Single-ended Inputs) PGA+Boost(+20dB)

Input Impedance (Note 5)

Mic In (Differential or Pseudo-Diff)

Line In (Pseudo-Diff, PGA = -12/0/+12 dB)

Mic/Line In (Single-Ended, PGA = -12/0/+12 dB)

0.79•VA 0.83•VA

0.08•VA

-

43.5

93/99/103

27/33/37

0.87•VA 0.79•VA 0.83•VA

0.08•VA

--

43.5

93/99/103

27/33/37

0.87•VA Vpp

-

Common Mode Rejection (Differential Inputs) - 60 - - 60 - dB

4. Referred to the typical full-scale voltage. Applies to all THD+N and Dynamic Range values in the table.

5. Measured between [LINE/MIC]IN_[L/R]+ and [LINE/MIC]IN_[C/L/R]- for differential and pseudo-differential inputs, and between [LINE/MIC]IN_[L/R]+ and AGND for single-ended inputs.

DS880F4 15

Vpp

Vpp

k

k

k

Page 16

CS4207

ADC DIGITAL FILTER CHARACTERISTICS

Parameter (Note 6) Min Typ Max Unit

Passband (Frequency Response) to -0.1 dB corner 0 - .4535 Fs

Passband Ripple -0.09 - 0.17 dB

Stopband 0.6 - - Fs

Stopband Attenuation 70 - - dB

Total Group Delay - 7.6/Fs - s

High-Pass Filter Characteristics

Frequency Response -3.0 dB

Phase Deviation @ 20 Hz - 10 - Deg

Passband Ripple - - 0.17 dB

Filter Settling Time

6. Response is clock dependent and will scale with Fs.

(48 kHz Fs)

-0.13 dB

-

-

-

10

3.6

24.2

5

/Fs

-

-

0s

Hz

Hz

16 DS880F4

Page 17

CS4207

ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL - CNZ)

(Test conditions (unless otherwise specified): Input test signal is a full-scale 997 Hz sine wave; VD = 1.8 V;

VL_HD = VL_IF = 3.3V; T

for the line output and test load R

= +25C; Measurement bandwidth is 10 Hz to 20 kHz; test load RL = 10 k CL= 10 pF

A

= 16 CL = 10 pF for the headphone output (see Figure 3); DAC Gain = 0 dB).

L

Parameter

(Note 4)

VA, VA_REF = 5.0 V

VA_HP = 5.0 V

(Single-ended)

Min Typ Max Min Typ Max Unit

VA, VA_REF = 3.3 V

VA_HP = 3.3 V

(Single-ended)

DAC1; RL = 16 ; DAC Gain = -5 dB

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

95

92

101

98

-

-

93

90

-

-

-

-

93

90

99

96

-

-

93

90

-

-

-

-

dB

dB

dB

dB

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

DAC1; R

= 10 k

L

-

-

-

-

-

-

-89

-78

-38

-89

-70

-30

-83

-72

-32

-

-

-

-

-

-

-

-

-

-93

-76

-36

-90

-70

-30

-87

-70

-30

-

-

-

dB

dB

dB

dB

dB

dB

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

100

97

-

-

106

103

96

93

-

-

-

-

98

95

104

101

-

-

96

93

-

-

-

-

dB

dB

dB

dB

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

Other Characteristics for DAC1; R

Full-scale Output Voltage, R

Output Power, THD+N = -75 dB, RL = 16

= 10 k 0.80•VA 0.84•VA 0.88•VA 0.80•VA 0.84•VA 0.88•VA Vpp

L

= 16 or 10 k

L

Output Power, THD+N = 1%, RL = 16 -50- -23-mW

Output Power,THD+N = 10%, RL = 16 -74- -35-mW

Interchannel Isolation (1 kHz) 16

10 k

-

-

-

-

-

-

-38- -17-mW

-

-

-88

-83

-43

-88

-73

-33

80

95

-82

-77

-37

-

-

-

-

-

-

-

-

-

-

-

-

-

-90

-81

-41

-90

-73

-33

80

93

-84

-75

-35

-

-

-

-

-

dB

dB

dB

dB

dB

dB

rms

rms

rms

dB

dB

Interchannel Gain Mismatch - 0.1 0.25 - 0.1 0.25 dB

Output Offset Volt age DAC to HPOUT - 2 4 - 2 4 mV

Gain Drift - ±100 - - ±100 - ppm/°C

AC-Load Resistance (R

Load Capacitance (C

) (Note 7) 16 - - 16 - -

L

) (Note 7) - - 150 - - 150 pF

L

Output Impedance - 300 - - 300 - m

DS880F4 17

Page 18

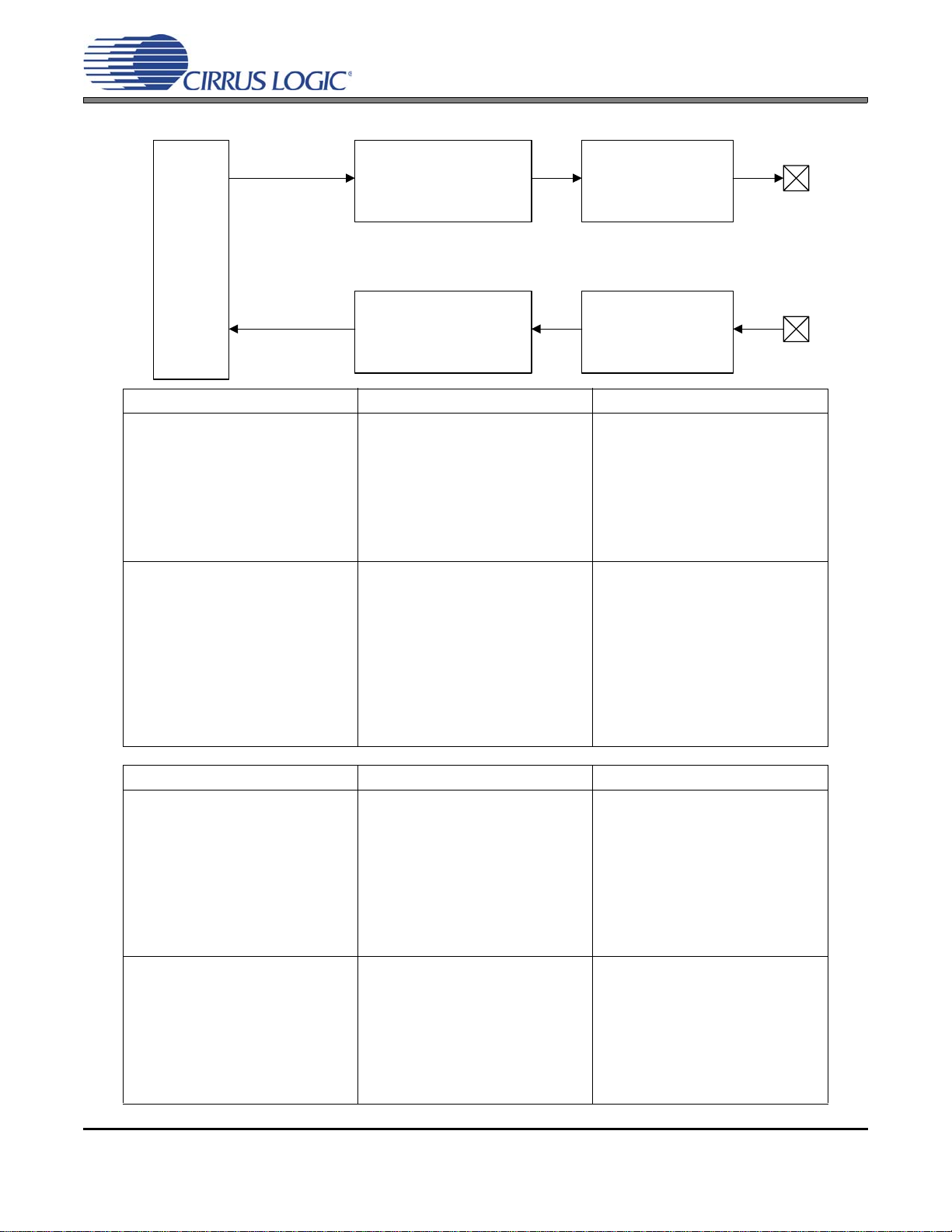

CS4207

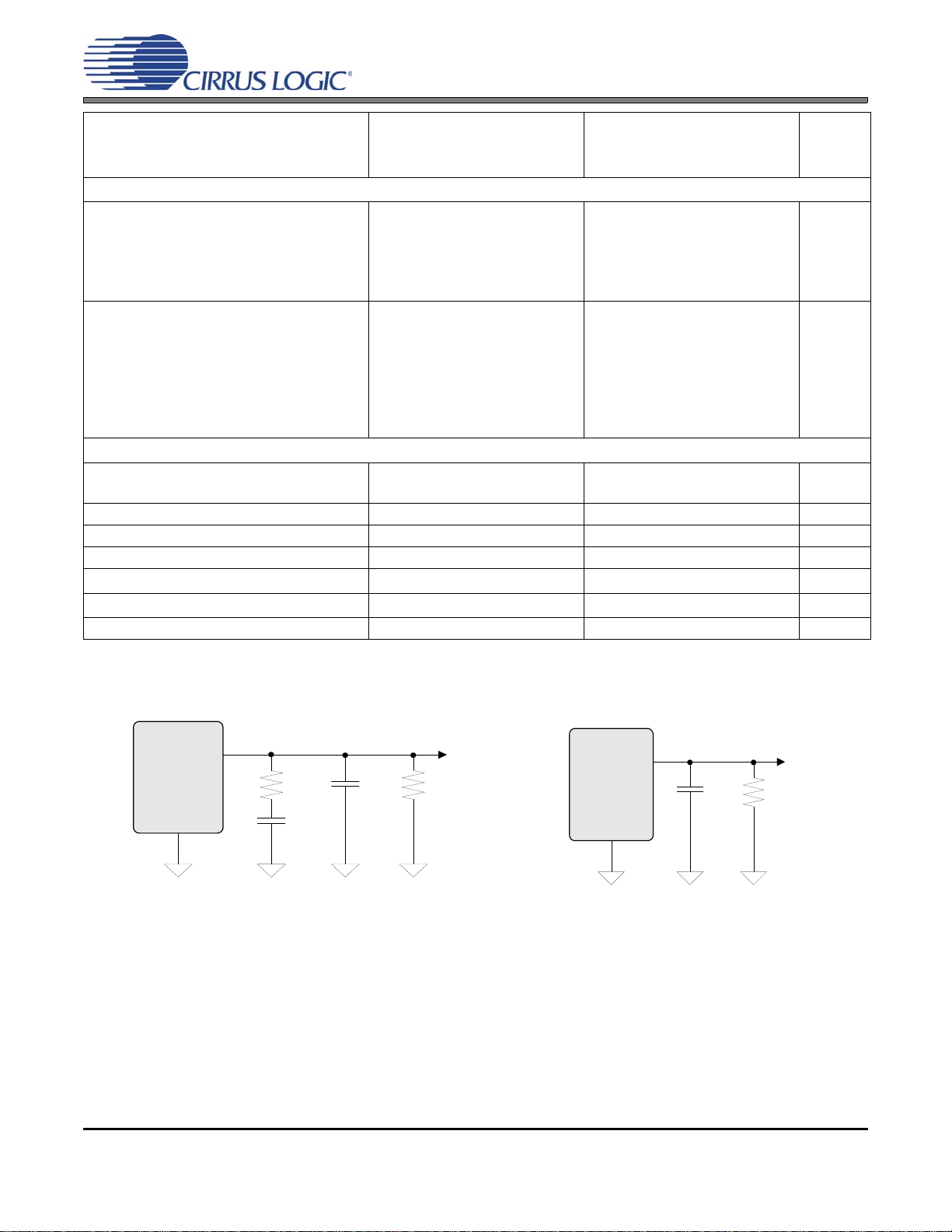

AGND

R

L

C

L

0.1 F

33

HPOUT_L/R

AGND

R

L

C

L

LINEOUT_L/R

Figure 3. Output Test Load, Headphone Out Figure 4. Output Test Load, Line Out

Parameter

(Note 4)

VA, VA_REF = 5.0 V

(Differential/Single-ended)

Min Typ Max Min Typ Max Unit

VA, VA_REF = 3.3 V

(Differential/Single-ended)

DAC2/DAC3; RL = 10 k

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

104/100

101/97

-

-

110/106

107/103

96

93

-

-

-

-

101/97

98/94

-

-

107/103

104/100

96

93

-

-

-

-

dB

dB

dB

dB

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

Other Characteristics for DAC2/DAC3; R

Full-scale Output Voltage

-

-

-

-

-

-

= 10 k

L

1.60•VA/

0.80•VA

-94/-91

-87/-83

-47/-43

-92

-73

-33

1.68•VA/

0.84•VA

-88/-85

-81/-77

-41/-37

-

-

-

1.76•VA/

0.88•VA

-

-

-

-

-

-

1.60•VA/

0.80•VA

-96/-94

-84/-80

-44/-40

-92

-73

-33

1.68•VA/

0.84•VA

-90/-88

-78/-74

-38/-34

-

-

-

1.76•VA/

0.88•VA

dB

dB

dB

dB

dB

dB

Vpp

Interchannel Isolation (1 kHz) - 100 - - 100 - dB

Interchannel Gain Mismatch - 0.1 0.25 - 0.1 0.25 dB

Gain Drift - ±100 - - ±100 - ppm/°C

AC-Load Resistance (R

Load Capacitance (C

) (Note 7) 3--3--k

L

) (Note 7) --100--100pF

L

Output Impedance - 100 - - 100 -

7. See Figure 3 and Figure 4. RL and CL reflect the recommended minimum resistance and maximum capacitance required for the internal op-amp's stability and signal integrity.

18 DS880F4

Page 19

CS4207

ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE - DNZ)

(Test conditions (unless otherwise specified): Input test signal is a full- scale 997 Hz sine wave; VD = 1.8 V ; VL_HD

= VL_IF = 3.3V; T

for the line output and test load R

= -40 to +85C; Measurement bandwidth is 10 Hz to 20 kHz; test load RL = 10 k CL= 10 pF

A

= 16 CL = 10 pF for the headphone output (see Figure 5); DAC Gain = 0 dB).

L

Parameter

(Note 4)

VA, VA_REF = 5.0 V

VA_HP = 5.0 V

(Single-ended)

Min Typ Max Min Typ Max Unit

VA, VA_REF = 3.3 V

VA_HP = 3.3 V

(Single-ended)

DAC1; RL = 16 ; DAC Gain = -5 dB

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

95

92

101

98

-

-

93

90

-

-

-

-

93

90

99

96

-

-

93

90

-

-

-

-

dB

dB

dB

dB

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

DAC1; R

= 10 k

L

-

-

-

-

-

-

-89

-78

-38

-89

-70

-30

-83

-72

-32

-

-

-

-

-

-

-

-

-

-93

-76

-36

-90

-70

-30

-87

-70

-30

-

-

-

dB

dB

dB

dB

dB

dB

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

100

97

-

-

106

103

96

93

-

-

-

-

98

95

104

101

-

-

96

93

-

-

-

-

dB

dB

dB

dB

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

Other Characteristics for DAC1; R

Full-scale Output Voltage, R

Output Power, THD+N = -75 dB, RL = 16

= 10 k 0.80•VA 0.84•VA 0.88•VA 0.80•VA 0.84•VA 0.88•VA Vpp

L

= 16 or 10 k

L

Output Power, THD+N = 1%, RL = 16 -50- -23-mW

Output Power,THD+N = 10%, RL = 16 -74- -35-mW

Interchannel Isolation (1 kHz) 16

10 k

-

-

-

-

-

-

-38- -17-mW

-

-

-88

-83

-43

-88

-73

-33

80

95

-82

-77

-37

-

-

-

-

-

-

-

-

-

-

-

-

-

-90

-81

-41

-90

-73

-33

80

93

-84

-75

-35

-

-

-

-

-

dB

dB

dB

dB

dB

dB

rms

rms

rms

dB

dB

Interchannel Gain Mismatch - 0.1 0.25 - 0.1 0.25 dB

Output Offset Volt age DAC to HPOUT - 2 5 - 2 5 mV

Gain Drift - ±100 - - ±100 - ppm/°C

AC-Load Resistance (R

Load Capacitance (C

) (Note 8) 16 - - 16 - -

L

) (Note 8) - - 150 - - 150 pF

L

Output Impedance - 300 - - 300 - m

DS880F4 19

Page 20

CS4207

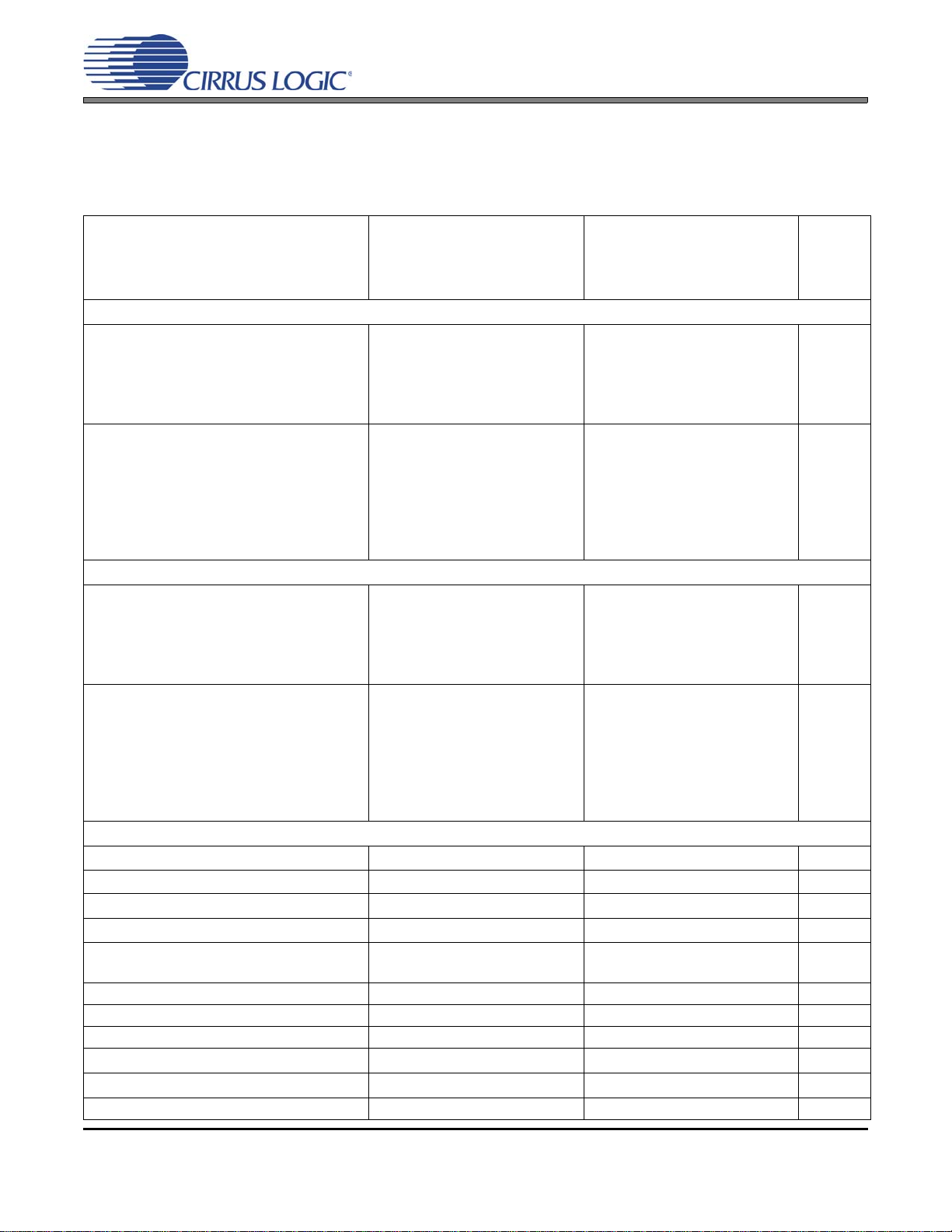

AGND

R

L

C

L

0.1 F

33

HPOUT_L/R

AGND

R

L

C

L

LINEOUT_L/R

Figure 5. Output Test Load, Headphone Out Figure 6. Output Test Load, Line Out

Parameter

(Note 4)

VA, VA_REF = 5.0 V

(Differential/Single-ended)

Min Typ Max Min Typ Max Unit

VA, VA_REF = 3.3 V

(Differential/Single-ended)

DAC2/DAC3; RL = 10 k

Dynamic Range

18 to 24-Bit A-weighted

unweighted

16-Bit A-weighted

unweighted

104/100

101/97

-

-

110/106

107/103

96

93

-

-

-

-

101/97

98/94

-

-

107/103

104/100

96

93

-

-

-

-

dB

dB

dB

dB

Total Harmonic Distortion + Noise

18 to 24-Bit 0 dB

-20 dB

-60 dB

16-Bit 0 dB

-20 dB

-60 dB

Other Characteristics for DAC2/DAC3; R

Full-scale Output Voltage

-

-

-

-

-

-

= 10 k

L

1.60•VA/

0.80•VA

-94/-91

-87/-83

-47/-43

-92

-73

-33

1.68•VA/

0.84•VA

-88/-85

-81/-77

-41/-37

-

-

-

1.76•VA/

0.88•VA

-

-

-

-

-

-

1.60•VA/

0.80•VA

-96/-94

-84/-80

-44/-40

-92

-73

-33

1.68•VA/

0.84•VA

-88/-88

-78/-74

-38/-34

-

-

-

1.76•VA/

0.88•VA

dB

dB

dB

dB

dB

dB

Vpp

Interchannel Isolation (1 kHz) - 100 - - 100 - dB

Interchannel Gain Mismatch - 0.1 0.25 - 0.1 0.25 dB

Gain Drift - ±100 - - ±100 - ppm/°C

AC-Load Resistance (R

Load Capacitance (C

) (Note 8) 3--3--k

L

) (Note 8) --100--100pF

L

Output Impedance - 100 - - 100 -

8. See Figure 5 and Figure 6. RL and CL reflect the recommended minimum resistance and maximum capacitance required for the internal op-amp's stability and signal integrity.

20 DS880F4

Page 21

CS4207

COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE

Parameter Min Typ Max Unit

Frequency Response 10 Hz to 20 kHz -0.01 - +0.01 dB

Passband to -0.01 dB corner

to -3 dB corner

StopBand - 26256 - Hz

StopBand Attenuation (Note 9) - 102 - dB

Total Group Delay - 0.196 - ms

9. Measurement Bandwidth is from Stopband to 100 kHz.

0

0

-

-

21792

23952

Hz

Hz

DC ELECTRICAL CHARACTERISTICS

(AGND = 0 V; all voltages with respect to ground.)

Parameters Min Typ Max Units

VCOM Characteristics

Nominal Voltage

Output Impedance

DC Current Source/Sink (Note 10)

VHP_FILT+ Characteristics

Nominal Voltage - 0.5•VA_HP - V

VHP_FILT- Characteristics

Nominal Voltage - -0.5•VA_HP - V

MIC BIAS Characteristics

Nominal Voltage VREFE = 000b

VREFE = 001b

VREFE = 010b

VREFE = 100b

DC Current Source (VA=5.0V)

(VA=3.3V)

Power Supply Rejection Ratio (PSRR) (Note 11) 1 kHz - 60 - dB

-

-

-

-

-

-

-

-

-

0.5•VA

23

-

Hi-Z

0.5•VA

GND

0.8•VA

5

3

10

-

-

-

-

-

-

-

-

V

k

A

V

V

V

V

mA

mA

10. The DC current draw represents the allowed current draw from the VCOM pin due to typical leakage

through electrolytic de-coupling capacitors.

11. Valid with the recommended capacitor values on VBIAS. Increasing the capacitance will also increase

the PSRR.

DS880F4 21

Page 22

CS4207

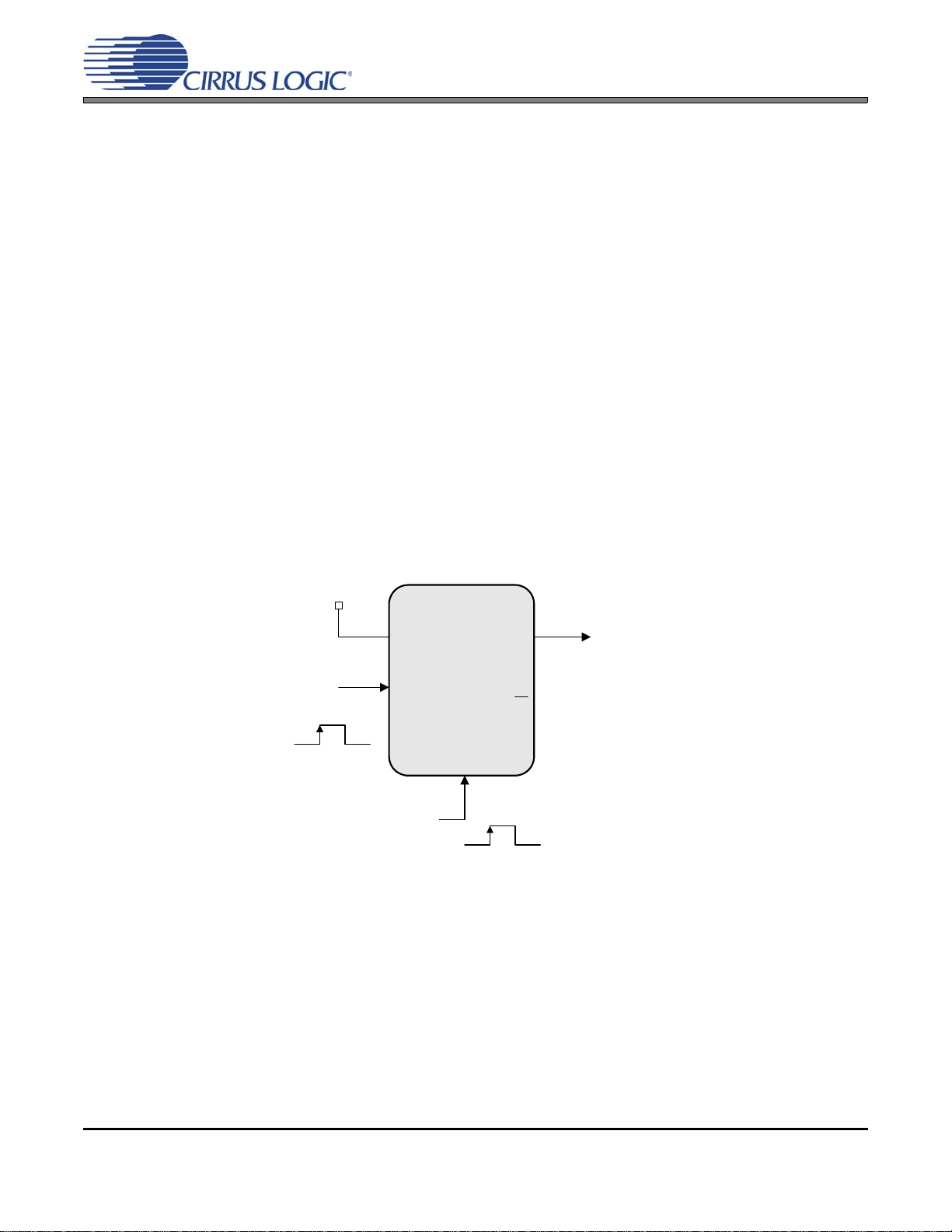

DMIC_SCL

DMIC_SDA

t

h(CLKR-SD)

t

P

t

r

t

f

t

h(CLKF-SD)

t

s(SD-CLKR)

t

s(SD-CLKF)

Right

(B, DATA2)

Channel Data

Left

(A, DATA1)

Channel Data

Left

(A, DATA1)

Channel Data

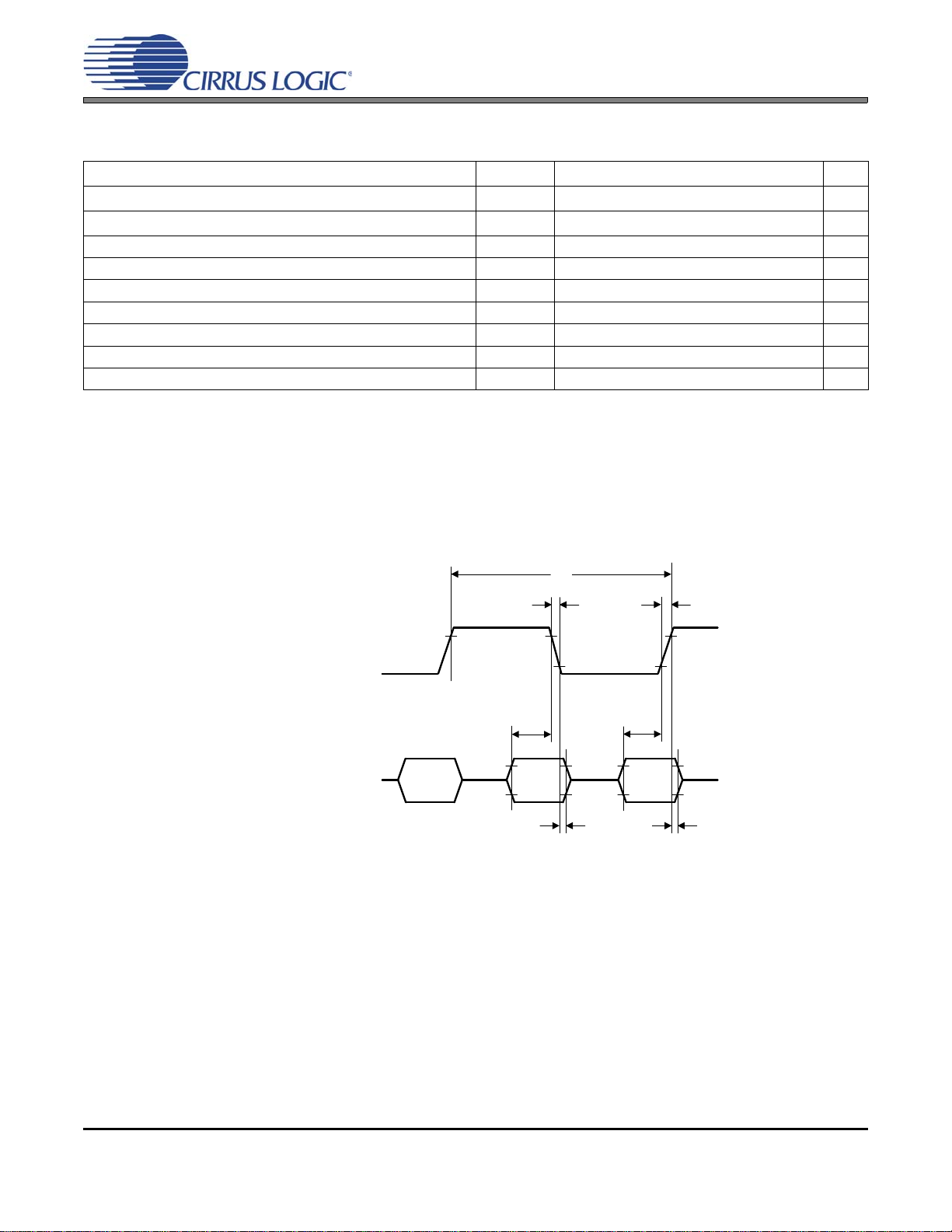

DIGITAL MICROPHONE INTERFACE CHARACTERISTICS

Test conditions: Inputs: Logic 0 = GND = 0 V, Logic 1 = VL_IF; TA = +25 C; C

Parameters Symbol Min Typ Max Units

DMIC_SCL Period (Fs

DMIC_SCL Period (Fs

DMIC_SCL Duty Cycle - 45 - 55 %

DMIC_SCL Rise Time (Note 13) t

DMIC_SCL Fall Time (Note 13) t

DMIC_SDA Setup Time Before DMIC_SCL Rising Edge t

DMIC_SDA Hold Time After DMIC_SCL Rising Edge t

DMIC_SDA Setup Time Before DMIC_SCL Falling Edge t

DMIC_SDA Hold Time After DMIC_SCL Falling Edge t

>= 44.1 kHz) (Note 12)

ADC

<= 32.0 kHz) (Note 12)

ADC

t

P

t

P

r

f

s(SD-CLKR)

h(CLKR-SD)

s(SD-CLKF)

h(CLKF-SD)

Notes:

12. The output clock frequency will follow the Bit Clock (BITCLK) frequency divided by 8 or 12, depending on

the sample rate of the ADC. Any deviation of the Bit Clock source from the nominal supported rates will be

directly imparted to the output clock rate by the same factor (e.g. +100 ppm offset in the frequency of BITCLK will become a +100 ppm offset in DMIC_SCL). For the nominal value of T_cyc reference HDA024-A

(see Note 4 in “References” on page 147).

13. Rise and fall times are measured from 0.1 • VL_IF to 0.9 • VL_IF.

= 30 pF.

LOAD

- 8 • T_cyc

- 12 • T_cyc

- - 10 ns

- - 10 ns

40 - - ns

5--ns

40 - - ns

6--ns

-

-

ns

ns

22 DS880F4

Figure 7. Digital MIC Interface Timing

Page 23

DIGITAL INTERFACE SPECIFICATIONS & CHARACTERISTICS

Parameters (Note 14) Symbol Min Max Units

Input Leakage Current I

Input Pin Capacitance C

VL_HD = 1.5 V

High-Level Input Voltage V

Low-Level Input Voltage V

High-Level Output Voltage (I

Low-Level Output Voltage (I

= -500 A) V

OUT

= 1500 A) V

OUT

VL_HD = 3.3 V

High-Level Input Voltage V

Low-Level Input Voltage V

High-Level Output Voltage (I

Low-Level Output Voltage (I

= -500 A) V

OUT

= 1500 A) V

OUT

VL_IF = 3.3 V

High-Level Input Voltage V

Low-Level Input Voltage V

High-Level Output Voltage (I

Low-Level Output Voltage (I

= -100 A) V

OH

= 100 A) V

OL

in

in

IH

IL

OH

OL

IH

IL

OH

OL

IH

IL

OH

OL

-±10A

-7.5pF

0.60•VL_HD - V

- 0.40•VL_HD V

0.90•VL_HD - V

- 0.10•VL_HD V

0.65•VL_HD - V

- 0.35•VL_HD V

0.90•VL_HD - V

- 0.10•VL_HD V

0.65•VL_IF - V

-0.35•VL_IFV

VL_IF - 0.2 - V

-0.2V

CS4207

14. See “Digital I/O Pin Characteristics” on p 10 for HD Audio I/F and control power rails.

HD AUDIO BUS SPECIFICATIONS & CHARACTERISTICS

Parameter Symbol Min Typ Max Units

BITCLK Period T

BITCLK High Time T

BITCLK Low Time T

CYC

HIGH

LOW

41.163 41.67 42.171 ns

17.50 24.16 ns

17.50 24.16 ns

BITCLK Jitter 150 500 ps

SDI Valid After BITCLK Rising T

SDO Setup Time T

SDO Hold Time T

TCO

SU

H

311ns

5ns

5ns

S/PDIF TRANSMITTER/RECEIVER SPECIFICATIONS & CHARACTERISTICS

Parameter Symbol Min Typ Max Units

Transmitter Specifications & Characteristics

AES3 Transmitter Output Jitter T

Receiver Specifications & Characteristics

PLL Clock Recovery Sample Rate Range f

Input Jitter Tolerance T

JIT(rms)

rec

JIT(rms)

meets IEC 60958-3 ps

kHz

meets IEC 60958-3 ps

DS880F4 23

Page 24

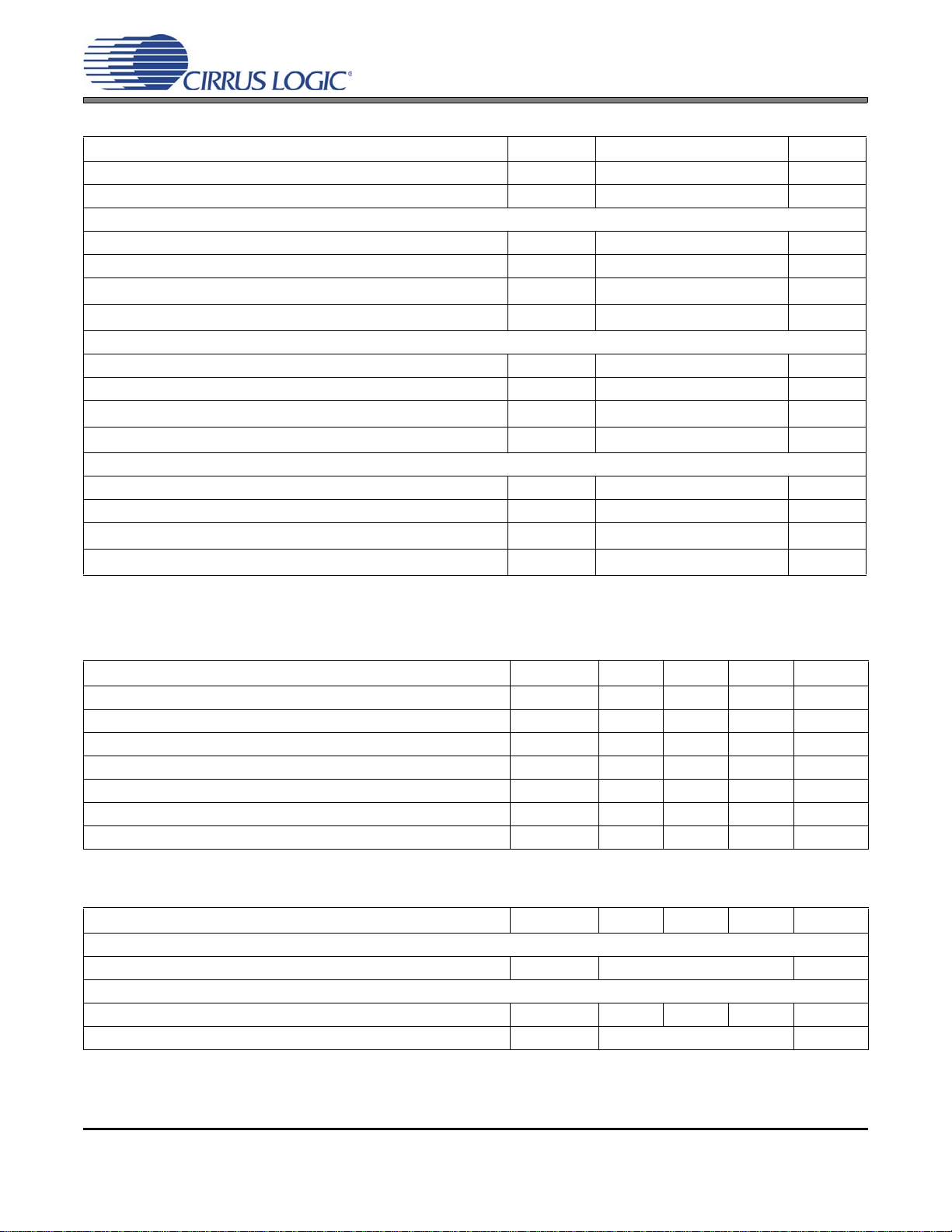

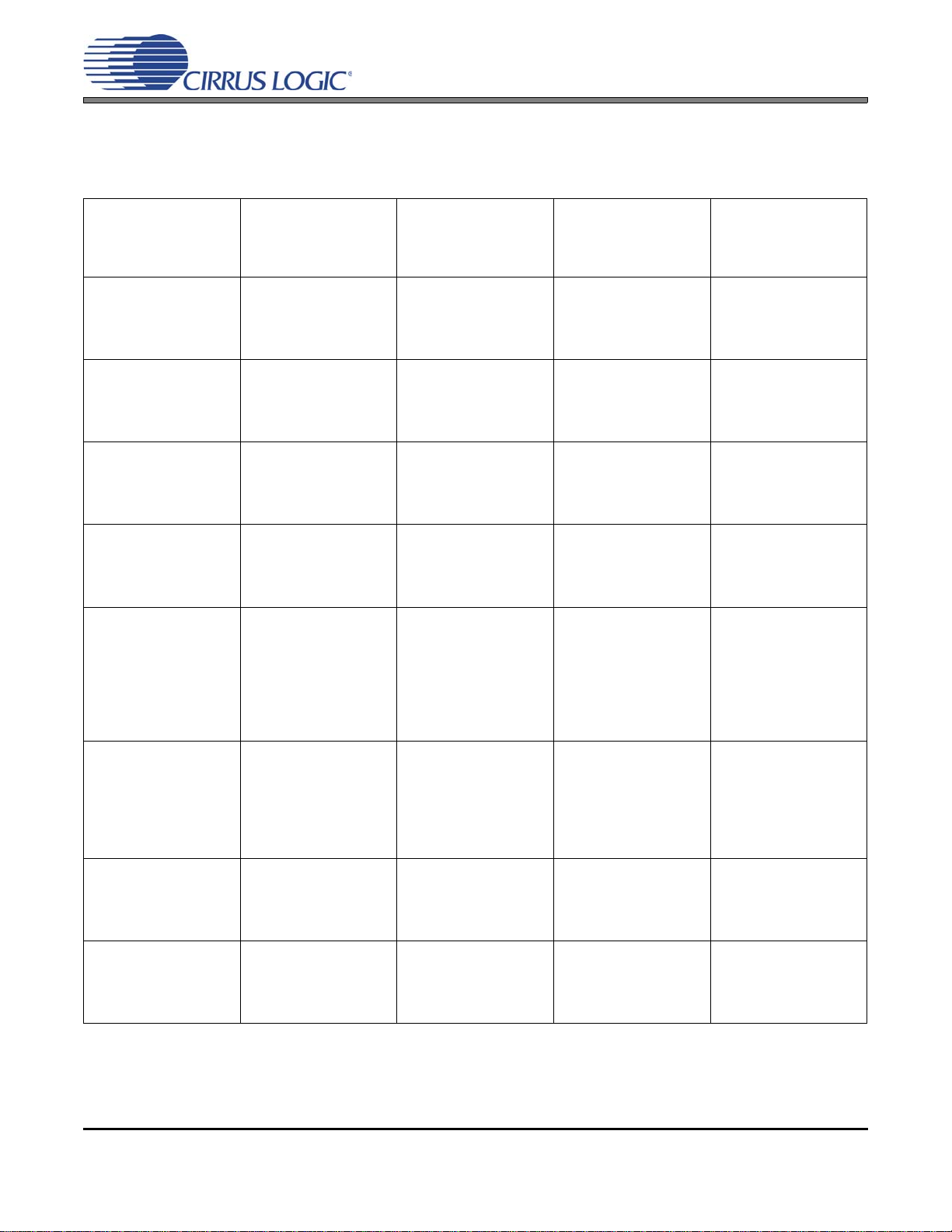

POWER CONSUMPTION

(This table represents the power consumption for individual circuit blocks within the codec) (See ( N o te 15 ))

Typical Current (mA)

CS4207

Individual Block Operation

Codec D3 State- unsolicited

1

response capable (Note 16)

ADC1 or ADC2 with PGA oper-

2

ation and Pseudo-Diff Inputs

DAC1 with Headphone/Line

3

Out (Note 17)

DAC2 or DAC3 with Differen-

4

tial Line Out (Note 18)

S/PDIF transmitter with SRC

5

function

S/PDIF receiver with SRC

6

function

i

VA

VA/

VA_ HP

3.3 0.94 0.00

5.0 1.20 0.00 12.24

3.3 5.47 0.00

5.0 6.23 0.00 44.80

3.3 11.08 1.51

5.0 14.06 1.76 95.12

3.3 10.72 0.00

5.0 13.59 0.00 83.84

3.3 0.84 0.00

5.0 1.10 0.00 22.51

3.3 0.84 0.00

5.0 1.10 0.00 28.64