Page 1

CS3302A

High-Z, Programmable Gain, Differential Amplifier

Features & Description

z Signal Bandwidth: DC to 2 kHz

z

Selectable Gain: x1, x2, x4, x8, x16, x32, x64

z

Differential Inputs, Differential Outputs

• Multiplexed inputs: INA, INB, 800Ω termination

• Rough / fine charge outputs for CS5371A / 72A / 73A

• Max signal amplitude: 5 V

• Ultra-low input bias: < 1 pA

z

Excellent Noise Performance

•1µV

• 8.5 nV/ √Hz

Low Total Harmonic Distortion

z

• -118 dB THD typical (0.000126%)

• -112 dB THD maximum (0.000251%)

Low Power Consumption

z

• Normal operation: 5 mA

• Power down: 10 µA

Dual Power Supply Configuration

z

• VA+ = +2.5 V; VA- = -2.5 V;VD = +3.3V

between 0.1 Hz and 10 Hz

p-p

from 200 Hz to 2 kHz

differential

pp

Description

The CS3302A is a high input-impedance, differential input, differential output amplifier with programmable

gain, optimized for amplifying signals from high-impedance sensors such as hydrophones. The gain settings

are binary weighted (x1, x2, x4, x8, x16, x32, x64) an d

are selected using simple pin settings. Two sets of external inputs, INA and INB, simplify system design as

inputs from a sensor and test DAC. An internal 80 0Ω

termination can also be selected for noise tests.

Amplifier input impedance is very high, requiring less

than 1 pA of input current. Nois e performance is very

good at 1 µ

density of 8.5 nV/ √Hz

width. Distortion performance is also extrem ely good,

typically -118 dB THD. Low input current, low noise, and

low total harmonic distortion make this amplifier ideal for

high-impedance differential sensors requiring maximum

dynamic range.

ORDERING INFORMATION

See page 15.

V

between 0.1 Hz and 10 Hz, and a noise

p-p

over the 200 Hz to 2 kHz band-

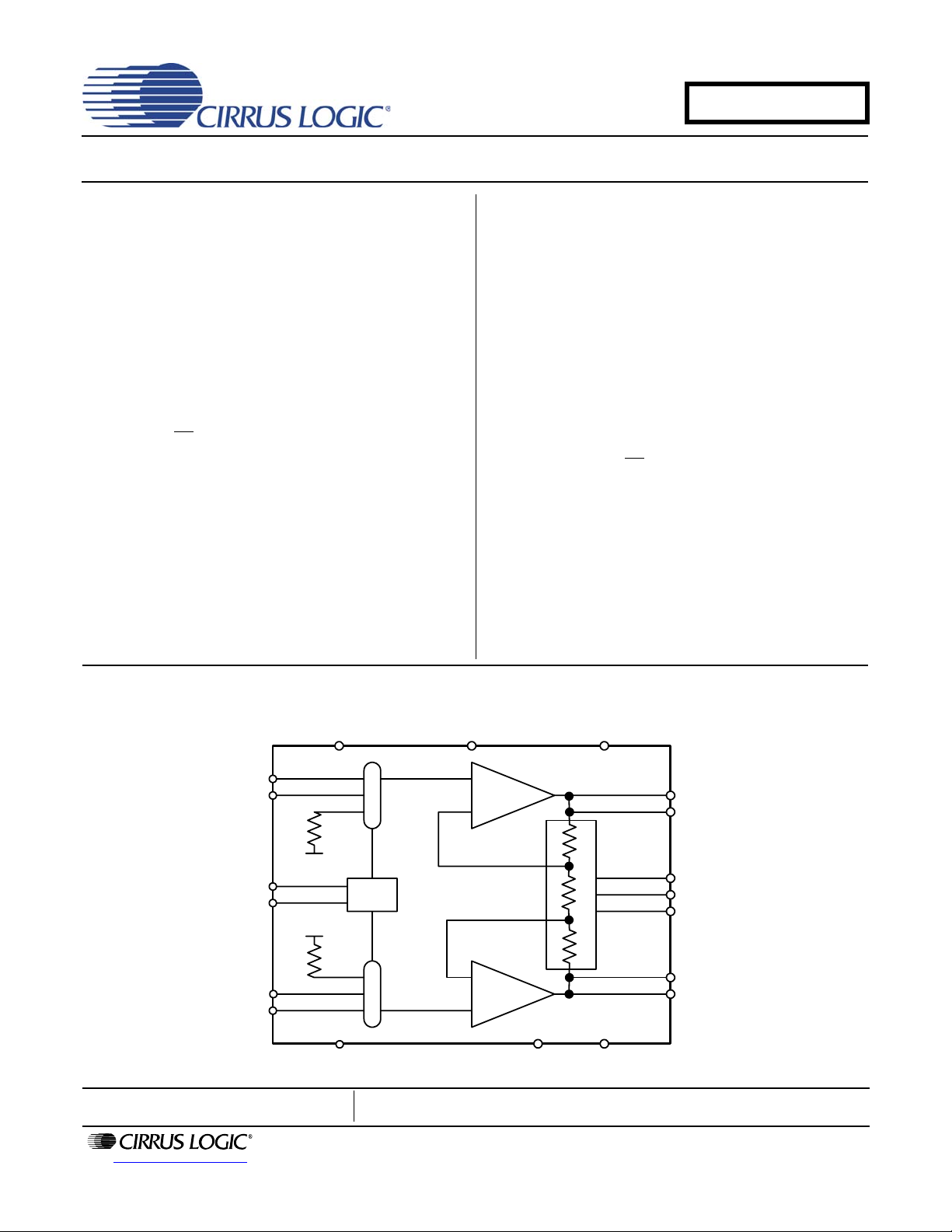

VA+

INA+

INB+

MUX0

MUX1

400 Ω 400 Ω

INAINB-

VA-

Preliminary Product Information

http://www.cirrus.com

GUARD

+

-

-

+

PWDN

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright © Cirrus Logic, Inc. 2007

(All Rights Reserved)

VD

OUTR+

OUTF+

GAIN0

GAIN1

GAIN2

OUTFOUTR-

GND

NOV '07

DS765PP1

Page 2

CS3302A

TABLE OF CONTENTS

1. CHARACTERISTICS AND SPECIFICATIONS ....................................................................... 4

SPECIFIED OPERATING CONDITIONS ................................................................................ 4

ABSOLUTE MAXIMUM RATINGS .......................................................................................... 4

THERMAL CHARACTERISTICS ............................................................................................. 5

ANALOG CHARACTERISTICS ....................... ................................ ................................... ..... 5

DIGITAL CHARACTERISTICS ........................ ................................... ................................ ..... 8

POWER SUPPLY CHARACTERISTICS ................................................................................. 9

2. GENERAL DESCRIPTION..................................................................................................... 10

2.1. Analog Signals..............................................................................................................10

2.2.1.Analog Inputs....................................................................................................... 10

2.3.2.Analog Outputs .................................................................................................... 11

2.4.3.Differential Signals ............................................................................................... 11

2.5.4.Guard Output ....................................................................................................... 11

2.6. Digital Signals ............................................................................................................... 12

2.7.1.Gain Selection...................................................................................................... 12

2.8.2.Mux Selection....................................................................................................... 12

2.9.3.Power Down Selection......................................................................................... 12

2.10. Power Supplies.......................... ............................................. ... ... .... ............................12

2.11.1.Analog Power Supplies................................ ... ... .... ... ... ... ... .... ... ... ...................... 12

2.12.2.Digital Power Supplies . ... ... ... ... .... ... ... ... .... ... ............................................. ... ... ... 12

2.13. Connection Diagram ..................................................................................................... 13

3. PIN DESCRIPTION...................... .... ... ... ... ... .... ... ... ... .............................................. ............... 14

4. ORDERING INFORMATION .... ... .... ... ............................................. ...................................... 15

5. ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION ........................... 15

6. PACKAGE DIMENSIONS...................................................................................................... 16

DS765PP1

CS3302A

LIST OF FIGURES

Figure 1. CS3302A Noise Performance.......................................................................................... 5

Figure 2. Digital Input Rise and Fall Times .....................................................................................8

Figure 3. System Architecture....................................................................................................... 10

Figure 4. System Architecture....................................................................................................... 11

Figure 5. CS3302A Amplifier Connections.................................................................................... 13

Figure 6. CS3302A Pin Assignments............................................................................................ 14

LIST OF TABLES

Table 1. Digital Selection for Gain and Input Mux Control ........................... .... ... ... ... .... ... ... ... ... .... . 8

Table 2. Pin Descriptions ............................................................................................................. 14

2 DS765PP1

Page 3

CS3302A

DS765PP1

REVISION HISTORY

Revision Date Changes

PP1 NOV 2007 Initial release.

CS3302A

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find one nearest you go to www.cirrus.com

IMPORTANT NOTI CE

"Preliminary" product information describes products that are in production, but for which full characterization data is not yet available.

Cirrus Logic, Inc. and its subsidiaries (“Cirrus”) believe that the information contained i n thi s doc umen t is ac cur at e an d r el i able. However, the information is subject

to change without not ice and is pr ovided “AS IS ” without warr anty of any k ind (expres s or implie d). Custo mers are advi sed to obtai n the late st versio n of releva nt

information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale

supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus

for the use of this information, inclu ding use of th is inform ation as the b asis for ma nufactur e or sale of any item s, or for in fringement of patents or other rights of third

parties. This document is the property of Cir rus an d by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of t he information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent

does not extend to other copying such as copying for gen eral distribution, advertising or promotional purp oses, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE N OT DESIGNED, AUTHO RIZED OR WARRANT ED FOR USE

IN AIRCRAFT SYSTEMS, MILITARY APP LICATI ONS, PRODUCTS SURGICALL Y IMPLANTED INTO THE B ODY, AUTOMOT IVE SAFET Y OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD

TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANT Y, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE

IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED

IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER

AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEY S' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH

THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and pr oduct nam es in this document may be trademarks

or service marks of their respective owners.

DS765PP1 3

Page 4

CS3302A

DS765PP1

CS3302A

1. CHARACTERISTICS AND SPECIFICATIONS

• Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions.

• Typical performance characteristics and specifications are derived from measurements taken at nominal supply voltages and T

= 25°C.

A

• GND = 0 V, all voltages with respect to 0 V.

• Device connected as shown in Figure 5 on page 12 unless otherwise noted.

SPECIFIED OPERATING CONDITIONS

Parameter Symbol Min Nom Max Unit

Bipolar Power Supplies

Positive Analog +

Negative Analog (Note 1) +

Positive Digital (Note 2) +

Thermal

Ambient Operating Temperature Industrial (-IS, -ISZ) T

Notes: 1. VA- must be the most negative voltage to avoid potential SCR latch-up conditions.

2. VD must conform to Digital Supply Differential under Absolute Maximum Ratings.

2% VA+ 2.45 2.50 2.55 V

2% V A- -2.55 -2.50 -2.45 V

3% VD 3.20 3.30 3.40 V

A

-40 25 85 °C

ABSOLUTE MAXIMUM RATINGS

CS3302A

Parameter Symbol

DC Power Supplies Positive Analog

Negative Analog

Digital

Analog Supply Differential [(VA+) - (VA-)] VA

Digital Supply Differential [(VD) - (VA-)] VD

Input Current, Any Pin Except Supplies (Note 3)I

Input Current, Power Supplies (Note 3)I

Output Current (Note 3)I

Power Dissipation PD - 500 mW

Analog Input Voltages V

Digital Input Voltages V

Storage Temperature Range T

WARNING: Operation at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

Notes: 3. Transient currents up to 100mA will not cause SCR latch-up.

VA+

VA-

VD

DIFF

DIFF

IN

PWR

OUT

INA

IND

STG

-0.3

-6.8

-0.3

-6.8V

-6.8V

-+10 mA

-+50 mA

-+25 mA

(VA-)-0.5 (VA+)+0.5 V

-0.5 (VD)+0.5 V

-65 150 ºC

6.8

0.3

6.8

UnitMin Max

V

V

V

4 DS765PP1

Page 5

CS3302A

DS765PP1

CS3302A

THERMAL CHARACTERISTICS

CS3302A

Parameter Symbol

Storage Temperature Range T

STR

-65 - 150 ºC

UnitMin Typ Max

Allowable Junction Temperature - - 125 ºC

Junction to Ambient Thermal Impedance Θ

Ambient Operating Temperature T

JA

A

-

65

-40 - +85 ºC

-

ºC / W

ANALOG CHARACTERISTICS

CS3302A

Parameter Symbol

Noise Performance

Input Voltage Noise f

Input Voltage Noise Density f0 = 200 Hz to 2 kHz VN

Input Current Noise Density (Note 4)IN

= 0.1 Hz to 10 Hz VN

0

PP

D

D

Distortion Performance

Total Harmonic Distortion (Note 5) x1

x2

x4

THD

x8

x16

x32

x64

Linearity (Note 5) x1

x2

x4

LIN

x8

x16

x32

x64

-1 3µV

-8.5 12

-20 -

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-118

-119

-119

-119

-118

-115

-112

0.0001259

0.0001122

0.0001122

0.0001122

0.0001259

0.0001778

0.0002512

-112

-

-

-

-

-

-

0.0002512

-

-

-

-

-

-

UnitMin Typ Max

nV/ Hz

fA/ Hz

pp

dB

%

Notes: 4. Guaranteed by design and/or characterization.

5. Tested with a 31.25 Hz sine wave at -1 dB amplitude.

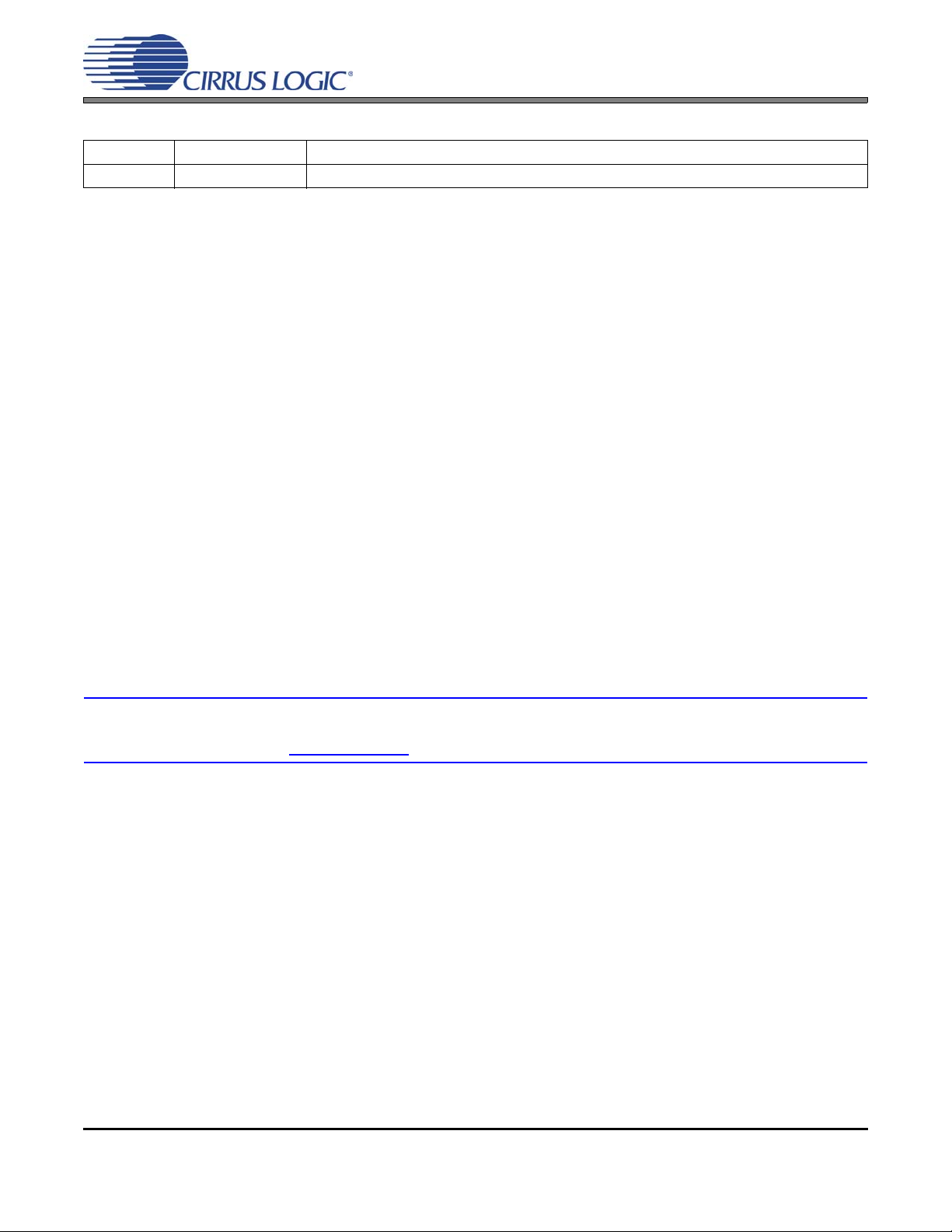

CS3302A In-Band Noise

20

15

10

5

0

0 200 400 600 800 1000 1200 1400 1600 1800 2000

Noise Density (nV/rtHz)

Frequency (Hz)

300

250

200

150

100

50

0

0.1 1 10 100 1000 10000 100000 1E+06

Noise Density (nV/rtHz )

CS3302A Wide Band Noise

Frequency (Hz)

Figure 1. CS3302A Noise Performance

DS765PP1 5

Page 6

CS3302A

DS765PP1

ANALOG CHARACTERISTICS (CONT.)

CS3302A

Parameter Symbol

Gain

Gain, Differential GAIN x1 - x64

Gain, Common Mode (Note 6) GAIN

Gain Accuracy , Absolute (Note 7)GAIN

Gain Accuracy , Relative (Note 8) x2

x4

x8

x16

x32

x64

Gain Drift (Note 4, 9) GAIN

Offset

Offset Voltage, Input Referred (Note 10)OFST - +

Offset After Calibration, Absolute (Note 11)OFST

Offset Calibration Range (Note 12)OFST

Offset Voltage Drift (Note 4, 9)OFST

CM

ABS

LIN

TC

CAL

RNG

TC

-x1-

-±1±2 %

-0.4

-

-

-

-

-

-5-ppm/ºC

-+1- µV

-100-% F.S.

-1-µV/ºC

-0.2

-0.2

-0.2

-0.2

-0.2

-0.2

250 +750 µV

0

-

-

-

-

-

CS3302A

UnitMin Typ Max

%

Notes: 6. Common mode signals pass unchanged through t he differential amplifier a rchitecture and are rejected

by the CS5371A / 72A / 73A modulator CMRR.

7. Absolute gain accuracy tests the matching of x1 gain across multiple CS3302A devices.

8. Relative gain accuracy tests the tracking of x1,x2, x4,x16,x32,x64 gain relative to x1 gain on a single

CS3302A device.

9. Specification is for the parameter over the specified temperature r ange and is for the CS3302A de vice

only. It does not include the effects of external components.

10. Offset voltage is tested with the amplifier inputs connected to the internal 800Ω termination.

11. The absolute offset after calibration sp ecification applies to the effective offse t voltage of the CS3302A

output when used with the CS5371A / 72A / 73A modulator and the CS5376A / 78 digital filter, and is

measured from the digitally calibrated output codes of the CS5376A / 78.

12. The CS3302A offset calibration is performed digitally with the CS5371A / 72A / 73A modulator and

CS5376A / 78 digital filter and includes the full scale signal range. Calibration offsets o f gr eater than +

5% of full scale will begin to subtract from system dynamic range.

6 DS765PP1

Page 7

CS3302A

DS765PP1

CS3302A

ANALOG CHARACTERISTIC (Cont.)

CS3302A

Parameter Symbol

Analog Input Characteristics

Input Signal Frequencies BW DC - 2000 Hz

Input Voltage Range (Signal + Vcm) x1

x2 - x64

Full Scale Input, Differential x1

V

x2

x4

x8

x16

x32

x64

Input Impedance, Differential Z

Input Impedance, Common Mode Z

Input Bias Current I

V

IN

INFS

INDIFF

INCM

IN

(VA-)+0.7

(VA-)+0.7

-

-

-

-

-

-

-

-1, 20- TΩ, pF

- 0.5, 40 - TΩ, pF

- 1 40 pA

-

-

-

-

-

-

-

-

-

(VA+)-1.25

(VA+)-1.75

5

2.5

1.25

625

312.5

156.25

78.125

Crosstalk, Multiplexed Inputs (Note 4)XT - -130 - dB

Common to Differential Mode Rejection (Note 4, 13)CDMR 90 100 - dB

Analog Output Characteristics

Full Scale Output, Differential V

Output Voltage Range (Signal + Vcm) V

Output Impedance (Note 14)Z

Output Impedance Drift (Note 14)Z

Output Current I

Load Capacitance C

OUT

RNG

OUT

TC

OUT

L

--5V

(VA-)+0.5

(VA+)-0.5

-

-40- Ω

-0.38- Ω/°C

--+25 mA

--100nF

Guard Output Characteristics

Guard Output Voltage V

GUARD

Guard Output Impedance ZG

Guard Output Current IG

Guard Load Capacitance CG

OUT

OUT

L

-

V

cm

-500- Ω

-40- µA

--100pF

-

UnitMin Typ Max

V

V

V

mV

mV

mV

mV

V

p-p

p-p

p-p

p-p

p-p

p-p

p-p

pp

V

V

Notes: 13. Ratio of common mode input amplitude vs. differ ential mode output amplitude for a perfectly matched

common mode input signal. Characterized with a 50 Hz, 500 mV

common mode sine wave applied

peak

to the analog inputs.

14. Output impedance characteristics are approximate and can vary up to +/- 30% depending on process

parameters.

DS765PP1 7

Page 8

CS3302A

DS765PP1

DIGITAL CHARACTERISTICS

Parameter Symbol

Digital Characteristics

High-level Input Drive Voltage (Note 15)V

Low-level Input Drive Voltage (Note 15)V

Input Leakage Current I

Digital Input Capacitance C

Rise Times t

Fall Times t

Notes: 15. Device is intended to be driven with CMOS logic levels.

t

rise

IH

IL

IN

IN

RISE

FALL

CS3302A

CS3302A

UnitMin Typ Max

0.6*VD - VD V

0.0 - 0.8 V

-+1+10 µA

-9- pF

--100ns

--100ns

t

fall

0.9 * VD

0.1 * VD

Figure 2. Digital Input Rise and Fall Times

Input Selection MUX1 MUX0

800 Ω termination 0 0

INA only 1 0

INB only 0 1

INA + INB 1 1

Table 1. Digital Selection for Gain and Input Mux Control

Gain Selection GAIN2 GAIN1 GAIN0

x1 0 0 0

x2 0 0 1

x4 0 1 0

x8 0 1 1

x16 1 0 0

x32 1 0 1

x64 1 1 0

Reserved 1 1 1

8 DS765PP1

Page 9

CS3302A

DS765PP1

CS3302A

POWER SUPPLY CHARACTERISTICS

CS3302A

Parameter Symbol

Power Supply Current, Normal Mode

Analog Power Supply Current (Note 16)I

Digital Power Supply Current (Note 16)I

Power Supply Current, Power Down Mode

Analog Power Supply Current, PWDN = 1 (Note 16)I

Digital Power Supply Current, PWDN = 1 (Note 16)I

Power Supply Rejection

Power Supply Rejection Ratio (Note 4, 17) PSRR 95 120 - dB

Notes: 16. All outputs unloaded. Analog inputs connected to the internal 800 Ω termination. Digital inputs forced

to VD or GND respectively.

17. Power supply rejection characterized with a 50 Hz, 400 mV

supply.

A

D

A

D

-5.05.75mA

-0.10.2mA

-911µA

-28 µA

sine wave applied separately to each

pp

UnitMin Typ Max

DS765PP1 9

Page 10

CS3302A

DS765PP1

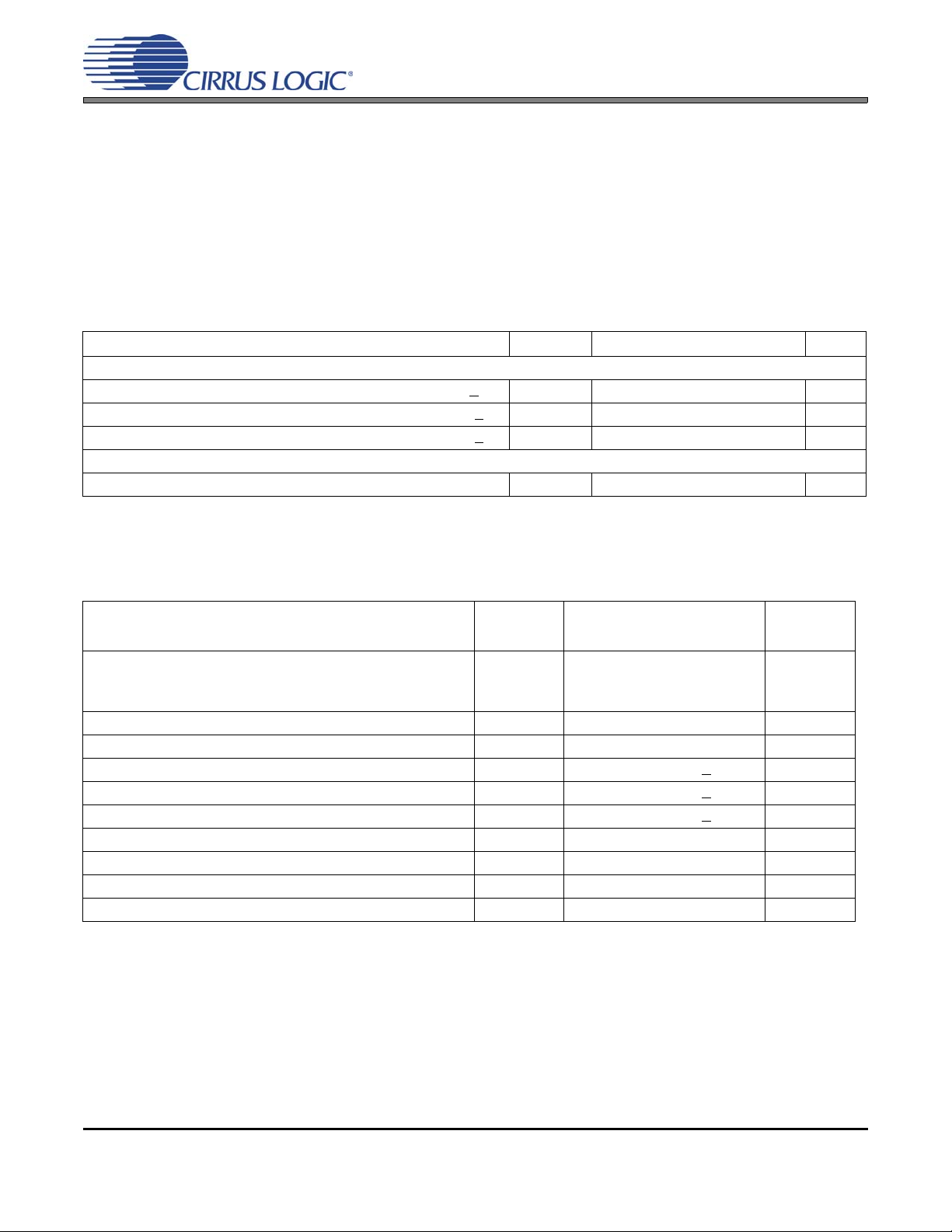

2. GENERAL DESCRIPTION

The CS3302A is a high-impedance, low-noise

CMOS differential input, differential output amplifier for precision analog signals between DC and

2 kHz. It has multiplexed inputs, rough/fine charge

outputs, and programmable gains of x1, x2, x4, x8,

x16, x32, and x64.

The performance of this amplifier makes it ideal

for low-frequency, high-dynamic-range applications requiring low distortion and minimal power

consumption. It is optimized for use in acquisition

systems designed around the CS5371A/72A single/dual ∆Σ modulators and the CS5376A quad

digital filter or the CS5373A ∆Σ modulator and

CS5378 digital filter. Figure 3 shows the system-

level architecture of a 4-channel acquisition system

using four CS3302A, two CS5372A, one

CS4373A, and one CS5376A. Figure 4 shows the

CS3302A

system architecture of a single channel acquisition

system using a CS3302A, CS5373A, and CS5378.

2.1 Analog Signals

2.1.1 Analog Inputs

The amplifier analog inputs are designed for highimpedance differential sensors. Input multiplexing

simplifies system connections by providing separate inputs for a sensor and test DAC (INA, INB) as

well as an internal termination for noise tests. The

MUX0, MUX1 digital pins determine which multiplexed input is connected to the amplifier.

2.1.2 Analog Outputs

The amplifier analog outputs are separated into rough

charge / fine charge signals to easily connect to the

CS5371A/72A/73A inputs. Each differential output

Geophone

or

Hydrophone

Sensor

Geophone

or

Hydrophone

Sensor

Geophone

or

Hydrophone

Sensor

Geophone

or

Hydrophone

Sensor

CS3301A

AMP

AMP

AMP

AMP

CS3302A

CS3301A

CS3302A

CS3301A

CS3302A

CS3301A

CS3302A

Switch

Switch

MUX

MUX

CS5371A

CS5372A

∆Σ

Modulator

CS5371A

CS5372A

∆Σ

Modulator

CS5376A

Digital Filter

CS4373A

Test

DAC

System Telemetry

µContr olle r

or

Configura tio n

EEPROM

Communication

Interface

M

U

X

M

U

X

M

U

X

M

U

X

Figure 3. System Architecture

10 DS765PP1

Page 11

CS3302A

DS765PP1

CS5373A

AMP

CS3301A

CS3302A

Figure 4. System Architecture

Differential

Sensor

M

U

X

requires two series resistors and a differential capacitor to create the modulator anti-alias RC filter.

2.1.3 Differential Signals

Analog signals into and out of the CS3302A are

differential, consisting of two halves with equal but

opposite magnitude varying about a common mode

voltage.

A full scale 5 Vpp differential signal centered on a

-0.15 V common mode can have:

SIG+ = -0.15 V + 1.25 V = 1.1 V

SIG- = -0.15 V - 1.25 V = -1.4 V

SIG+ is +2.5 V relative to SIG-

For the reverse case:

SIG+ = -0.15 V - 1.25 V = -1.4 V

SIG- = -0.15 V + 1.25 V = 1.1 V

SIG+ is -2.5 V relative to SIG-

The total swing for SIG+ relative to SIG- is

(+2.5 V) - (-2.5 V) = 5 V

. A similar calculation

pp

can be done for SIG- relative to SIG+. Note that a

5Vpp differential signal centered on a -0.15 V

common mode voltage never exceeds 1.1 V and

never drops below -1.4 V on either half of the signal.

CS3302A

µController

or

CS5378

∆Σ

Modulator

Test

DAC

Digital Filter

By definition, differential voltages are to be measured with respect to the opposite half, not relative

to ground. A multimeter differentially measuring

between SIG+ and SIG- in the above example

would properly read 1.767 V

2.1.4 Guard Output

rms

The GUARD pin outputs the common mode voltage of the currently selected analog signal input. It

can be used to drive the cable shield between a

high-impedance sensor and the amplifier inputs.

Driving the cable shield with the analog signal

common mode voltage minimizes leakage and improves signal integrity from high-impedance sensors.

The GUARD output is defined as the midpoint

voltage between the + and - halves of the currently

selected differential input signal, and will vary as

the signal common mode varies. The GUARD output will not drive a significant load, it only provides a shielding voltage.

2.2 Digital Signals

2.2.1 Gain Selection

The CS3302A supports gain ranges of x1, x2, x4,

x8, x16, x32, and x64. They are selected using the

GAIN0, GAIN1, and GAIN2 pins as shown in

Table 1 on page 8.

Configuration

EEPROM

System

Telemetry

, or 5 Vpp.

DS765PP1 11

Page 12

CS3302A

DS765PP1

2.2.2 Mux Selection

The analog inputs to the amplifier are multiplexed,

with external signals applied to the INA+, INA- or

INB+, INB- pins. An internal termination is also

available for noise tests. Input mux selection is

made using the MUX0 and MUX1 pins as shown

in Table 1 on page 8.

Although a mux selection is provided to enable the

INA and INB switches simultaneously, significant

current should not be driven through them in this

mode. The CS3302A mux switches will maintain

good linearity only with minimal signal current.

2.2.3 Power Down Selection

A power-down mode is available to shut down the

amplifier when not in use. When enabled, all internal circuitry is disabled, the analog inputs and outputs go high-impedance, and the device enters a

micro-power state. Power down mode is selected

using the PWDN pin, which is active high.

CS3302A

2.3 Power Supplies

2.3.1 Analog Power Supplies

The analog power pins of the CS3302A are to be

supplied with a total of 5 V between VA+ and VA. This voltage is typically from a bipolar ±2.5 V

supply. When using bipolar supplies the analog

signal common mode voltage should be biased to 0

V. The analog power supplies are recommended to

be bypassed to system ground using 0.1 µF X7R

type capacitors.

The VA- supply is connected to the CMOS substrate and as such must remain the most negative

applied voltage to prevent potential latch-up conditions. It is recommended to clamp the VA- supply

to system ground using a reverse biased Schottky

diode to prevent possible latch-up conditions related to mismatched supply rail initialization.

2.3.2 Digital Power Supplies

The digital power supply across the VD and GND

pins is specified for a +3.3 V power supply. The

digital power supply should be bypassed to system

ground using a 0.01 µF X7R type capacitor.

12 DS765PP1

Page 13

CS3302A

DS765PP1

CS3302A

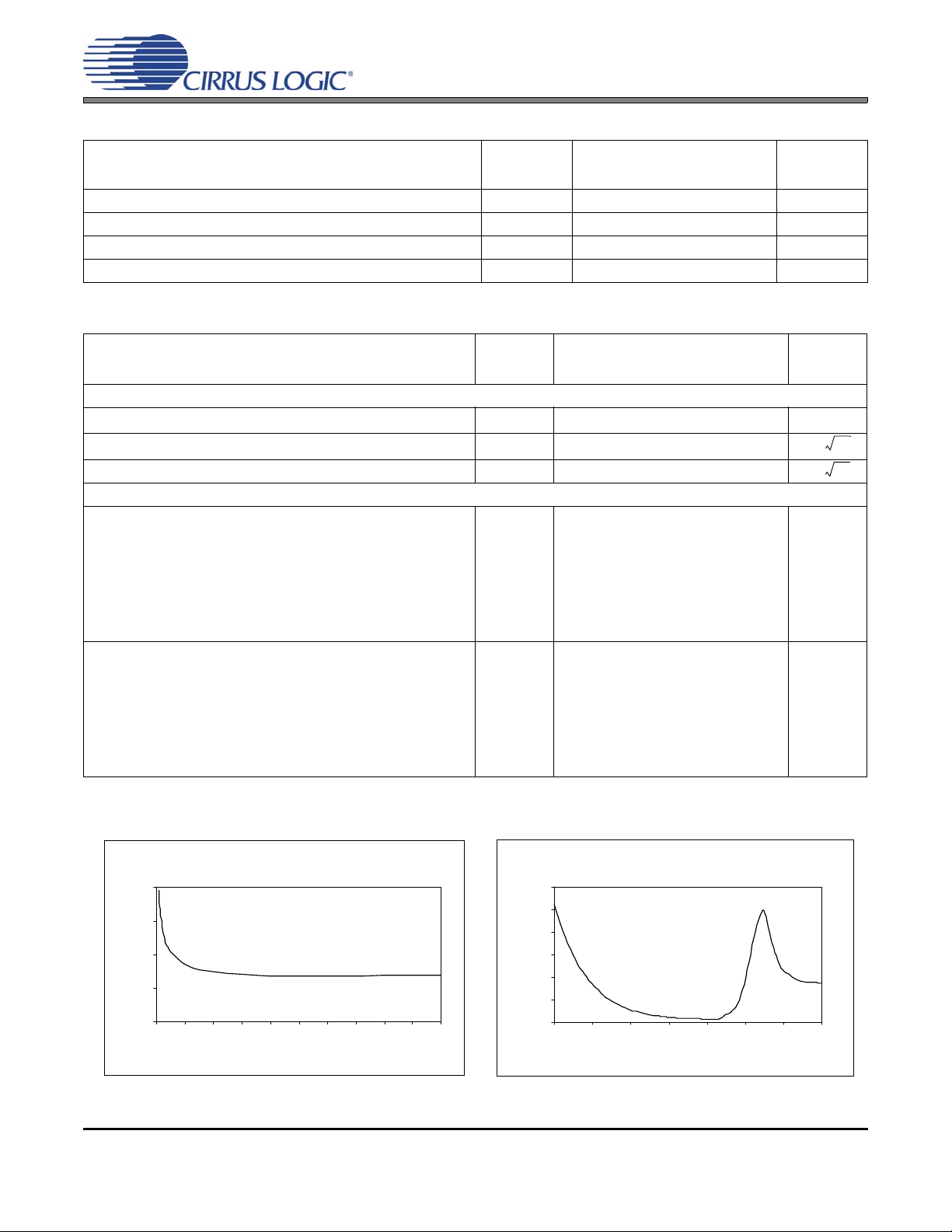

2.4 Connection Diagram

Figure 5 shows a connection diagram for the CS3302A amplifier when used with the CS5372A dual ∆Σ

modulator, the CS4373A test DAC and the CS5376A digital filter. The diagram shows differential sensors,

a test DAC, and analog outputs with anti-alias capacitors; power supply connections including recommended bypassing; and digital control connections back to the CS5376A GPIO pins.

680

2.5 V

680

0.02µF

Ω

680

0.02

680

GPIO ( x3 )

GPIO ( x2 )

GPIO

VD

0.01

Ω

C0G

Ω

µF µ F

C0G

Ω

VD

0.01

VA+

µF µF

0.1 0.01

µF

VA+

INR+

INF+

µF

0.02

C0G

INFINR-

VREF+

∆Σ Modulator

VREF-

INRINF-

0.02

C0G

INF+

INR+

VA-VDGND

µF

VA-

To CS5376A

Digital Control

CS5372A

µF

0.1

A

MDATA1

MFLAG1

PWDN1

MCLK

MSYNC

LPWR

OFST

MDATA2

MFLAG2

PWDN2

A

VD

VA+

µF

0.1

VA-

µF

0.1

Differential

Sensor

Differential

Sensor

VA+

µF

0.1

VA-

µF

0.1

3

GAIN MUX PWDN

VA+

CS3302A

Differential

Amplifie r

VA-

GUARD

GUARD

INB+INA+ INA- INB- OUTF -OUTR- OUTF+ OUTR+

INB+INA+ INA- INB- OUTF -OUTR- OUTF+ OUTR+

VA+

CS3302A

Differential

Amplifie r

VA-

GAIN MUX PWDN

2

CS4373A

Test

DAC

680

680

680

680

VD

GND

Ω

Ω

Reference

Ω

Ω

VD

GND

3

2

GPIO

GPIO ( x2 )

GPIO ( x3 )

To CS5376A

Digital Control

Figure 5. CS3302A Amplifier Connections

DS765PP1 13

Page 14

CS3302A

3. PIN DESCRIPTION

Pin Name Pin # I/O

VA+

VAVD

GND

INA+, INAINB+, INBGUARD

OUTR+, OUTROUTF+, OUTFGAIN0, GAIN1,

GAIN2

PWDN

MUX0, MUX1

TEST0

TEST1, TEST2

TESTOUT

1 I Positive analog supply voltage.

4 I Negative analog supply voltage.

16 I Positive digital supply voltage.

15, 18 I Ground.

5, 6 I Channel A differential analog inputs. Selected via MUX pins.

8, 7 I Channel B differential analog inputs. Selected via MUX pins.

13 O Guard voltage output.

11, 2 O Rough charge differential analog outputs.

10, 3 O Fine charge differential analog outputs.

22, 21, 20I Gain range select. See Gain Selection table in Digital Characteristics section.

19 I Power down mode enable. Active high.

24, 23 I Analog input select. See Input Selection table in Digital Characteristics section.

12 I Test mode select, factory use only. Connect to VA- during normal operation.

17, 14 I

9O

DS765PP1

Pin Description

CS3302A

Test mode select, factory use only. Connect to GND during normal operation.

Test mode output, factory use only. Do not connect during normal operation.

Table 2. Pin Descriptions

Positive Analog Power Supply VA+

Negative Analog Rough Output OUTR-

Negative Analog Fine Output OUTF-

Negative Analog Power Supply VA-

Non-Inverting Input A INA+

Inverting Input A INA-

Inverting Input B INB-

Non-Inverting Input B INB+

Test Mode Output TESTOUT

Positive Analog Fine Output OUTF+

Positive Analog Rough Output OUTR+

Test Mode Select TEST0

Figure 6. CS3302A Pin Assignments

1

2

3

4

5

6

7

817

9

10

11

12 13

MUX0 Input Mux Select

24

MUX1 Input Mux Select

23

GAIN0 Gain Range Select

22

GAIN1 Gain Range Select

21

GAIN2 Gain Range Select

20

PWDN Power Down Mode Enable

19

GND Ground

18

TEST1 Test Mode Select

VD Positive Digital Power Supply

16

GND Ground

15

TEST2 Test Mode Select

14

GUARD Guard Voltage Output

14 DS765PP1

Page 15

CS3302A

DS765PP1

CS3302A

4. ORDERING INFORMATION

Model Temperature Package

CS3302A-IS

CS3302A-ISZ, lead (Pb) free

-40 to +85 °C 24-pin SSOP

5. ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION

Model Number Peak Reflow Temp MSL Rating* Max Floor Life

CS3302A-IS

CS3302A-ISZ, lead (Pb) free

* MSL (Moisture Sensitivity Level) as specified by IPC/JEDEC J-STD-020.

240 °C 2 365 Days

260 °C 3 7 Days

DS765PP1 15

Page 16

CS3302A

DS765PP1

CS3302A

6. PACKAGE DIMENSIONS

24 PIN SSOP PACKAGE DRAWING

N

D

1

23

TOP VIEW

E

e

INCHES MILLIMETERS

DIM MIN MAX MIN MAX

A -- 0.084 -- 2.13

A1 0.002 0.010 0.05 0.25

A2 0.064 0.074 1.62 1.88

b 0.009 0.015 0.22 0.38 2,3

D 0.311 0.335 7.90 8.50 1

E 0.291 0.323 7.40 8.20

E1 0.197 0.220 5.00 5.60 1

e 0.024 0.027 0.61 0.69

L 0.025 0.040 0.63 1.03

∝

0° 8° 0° 8°

2

b

SIDE VIEW

A2

A1

A

SEATING

PLANE

L

Notes: 1. “D” and “E1” are reference datums and do not included mo ld flash or protrusions, but do include mold

mismatch and are measured at the parting line, mold flash or protrusions shall not exceed 0.20 mm per

side.

2. Dimension “b” does not include dambar protrusion/intrusion. Allowable dambar protrusion shall be

0.13 mm total in excess of “b” dimension at maximum material condition. Dambar intrusion shall not

reduce dimension “b” by more than 0.07 mm at least material condition.

3. These dimensions apply to the flat section of the lead between 0.10 and 0.25 mm from lead tips.

1

E1

END VIEW

NOTE

16 DS765PP1

Loading...

Loading...