Page 1

CS3002

Hz

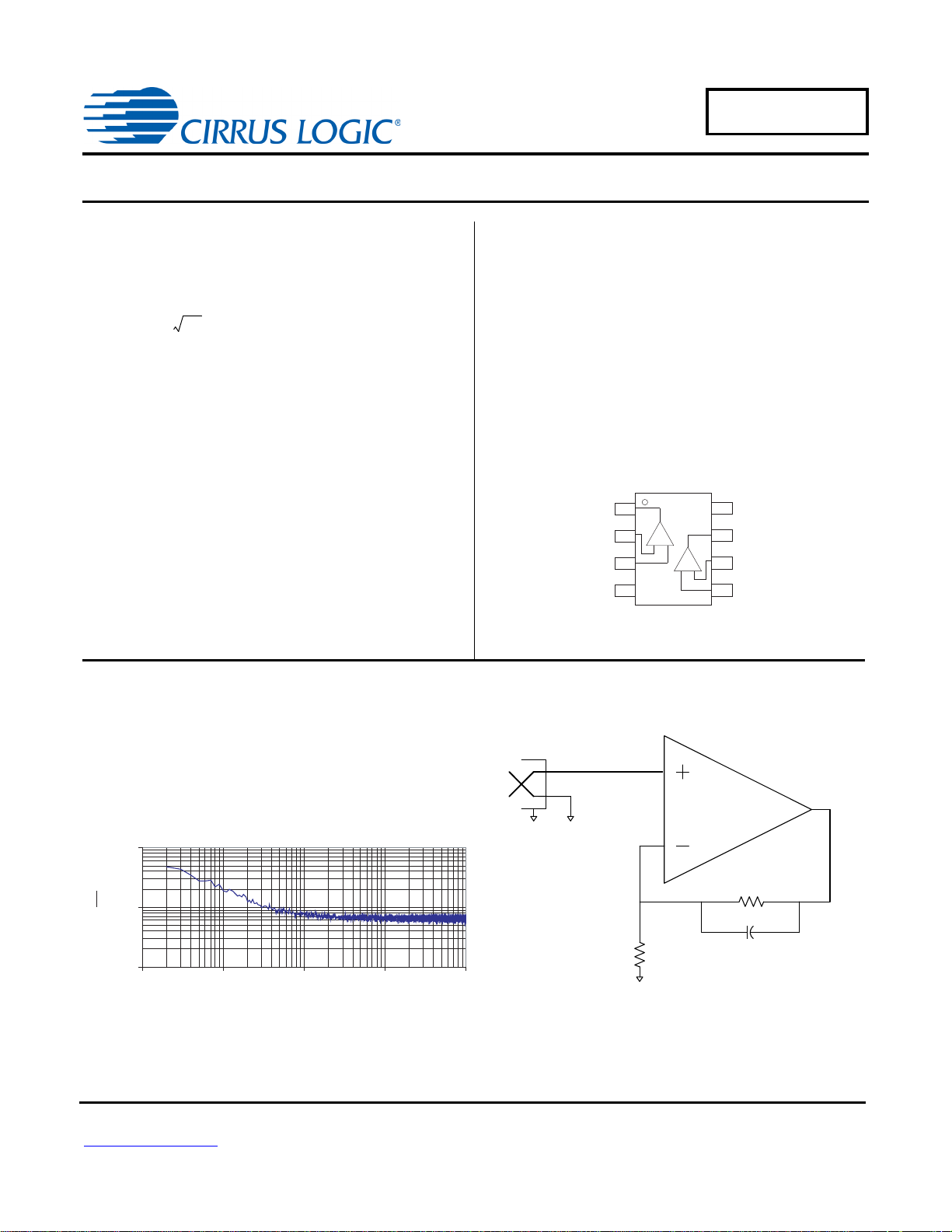

Out A

-In A

+In A

V-

V+

Out B

-In B

+In B

A

B

-

-

+

+

1

2

3

4

8

7

6

5

CS3002

8-lead SOIC

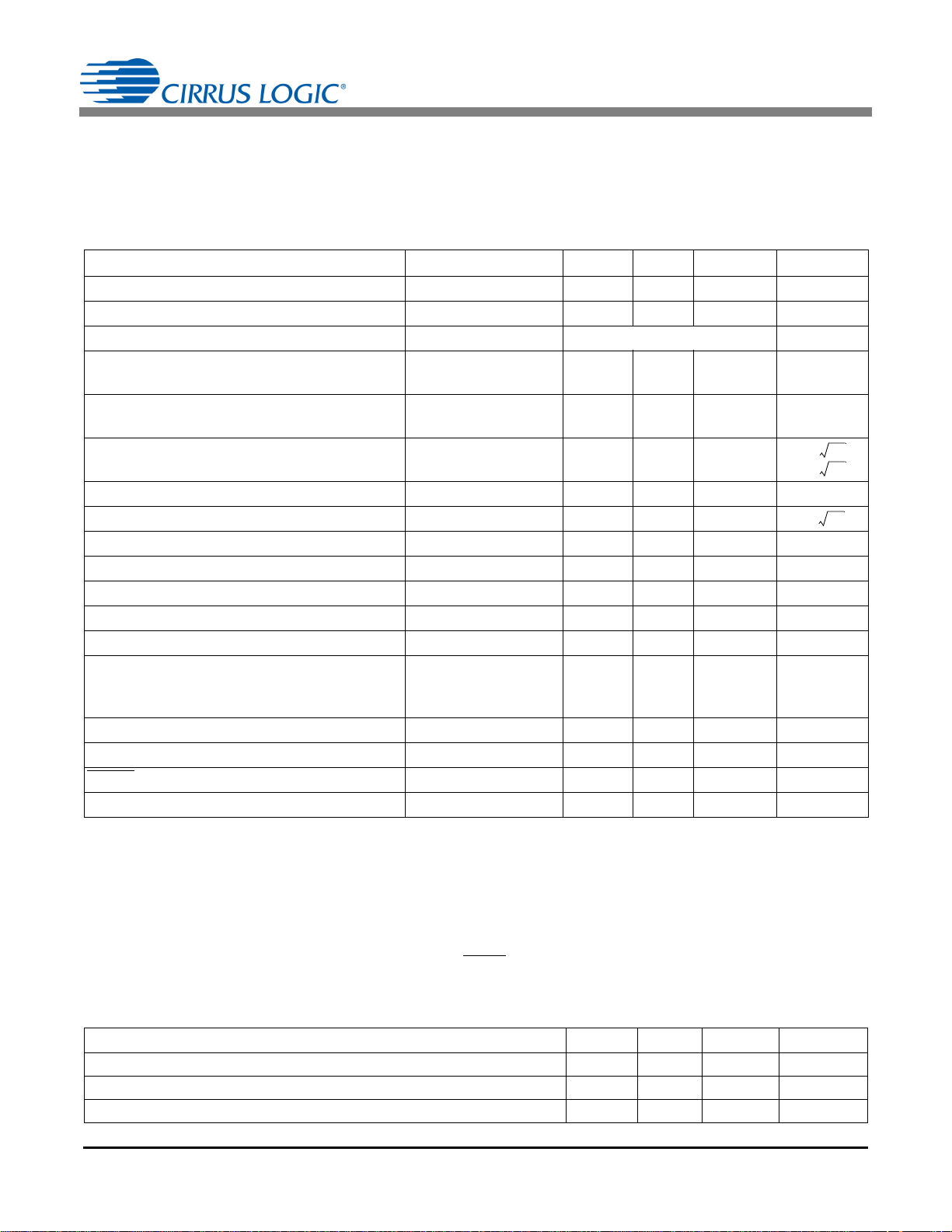

Noise vs. Frequency (Measured)

1

10

100

0.001 0.01 0.1 1 10

Freque ncy (Hz)

nV/√Hz

CS3002

R1

100

R2

64.9k

C2

0.015F

Dexter Research

Thermophile 1M

Precision Low-voltage Amplifier; DC to 2kHz

Features & Description

• Low Offset: 10V Max

• Low Drift: 0.05V/°C Max

• Low Noise

- 6nV/ @ 0.5Hz

- 0.1 to 10Hz = 125 nVpp

- 1/f corner @ 0.08Hz

• Open-loop Voltage Gain

- 300dB Typical

- 200dB Minimum

• Rail-to-rail Output Swing

• Slew Rate: 5V/s

Applications

• Thermocouple/Thermopile Amplifiers

• Load Cell and Bridge Transducer Amplifiers

• Precision Instrumentation

• Battery-powered Systems

Description

The CS3002 dual amplifier is designed for precision amplification of low-level signals and is ideally suited for

applications that require very high closed-loop gains.

These amplifiers achieve excellent offset stability, superhigh open-loop gain, and low noise over time and temperature. The devices also exhibit excellent CMRR and

PSRR. The common mode input range includes the negative supply rail. The amplifiers operate with any total

supply voltage from 2.7V to 6.7V (±1.35 V to ±3.35 V).

Pin Configuration

Cirrus Logic, Inc.

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2012

(All Rights Reserved)

DEC ‘12

DS490F10

Page 2

CS3002

TABLE OF CONTENTS

1. Characteristics and Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.1 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1.2 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2. Typical Performance Plots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.1 Open-loop Gain and Phase Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.2 Open-loop Gain and Stability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.2.1 Discussion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.2.2 Gain Calculation Recommendations . . . . . . . . . . . . . . . . . . . . . . . . . 11

Calculate the Compensation Capacitor Value: . . . . . . . . . . . . . . . . . 11

Verify the Op Amp Compensation: . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.3 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

4. Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

6. Environmental, Manufacturing, & Handling Information . . . . . . . . . . . . . . . . . . 13

7. Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

LIST OF FIGURES

Figure 1. Noise vs. Frequency (Measured)................................................................................... 4

Figure 2. Noise vs. Frequency ...................................................................................................... 4

Figure 3. 0.01Hz to 10Hz Noise ................................................................................................... 4

Figure 4. Offset Voltage Stability (DC to 3.2Hz) ........................................................................... 4

Figure 5. Supply Current vs. Temperature.................................................................................... 4

Figure 6. Supply Current vs. Supply Voltage ................................................................................ 4

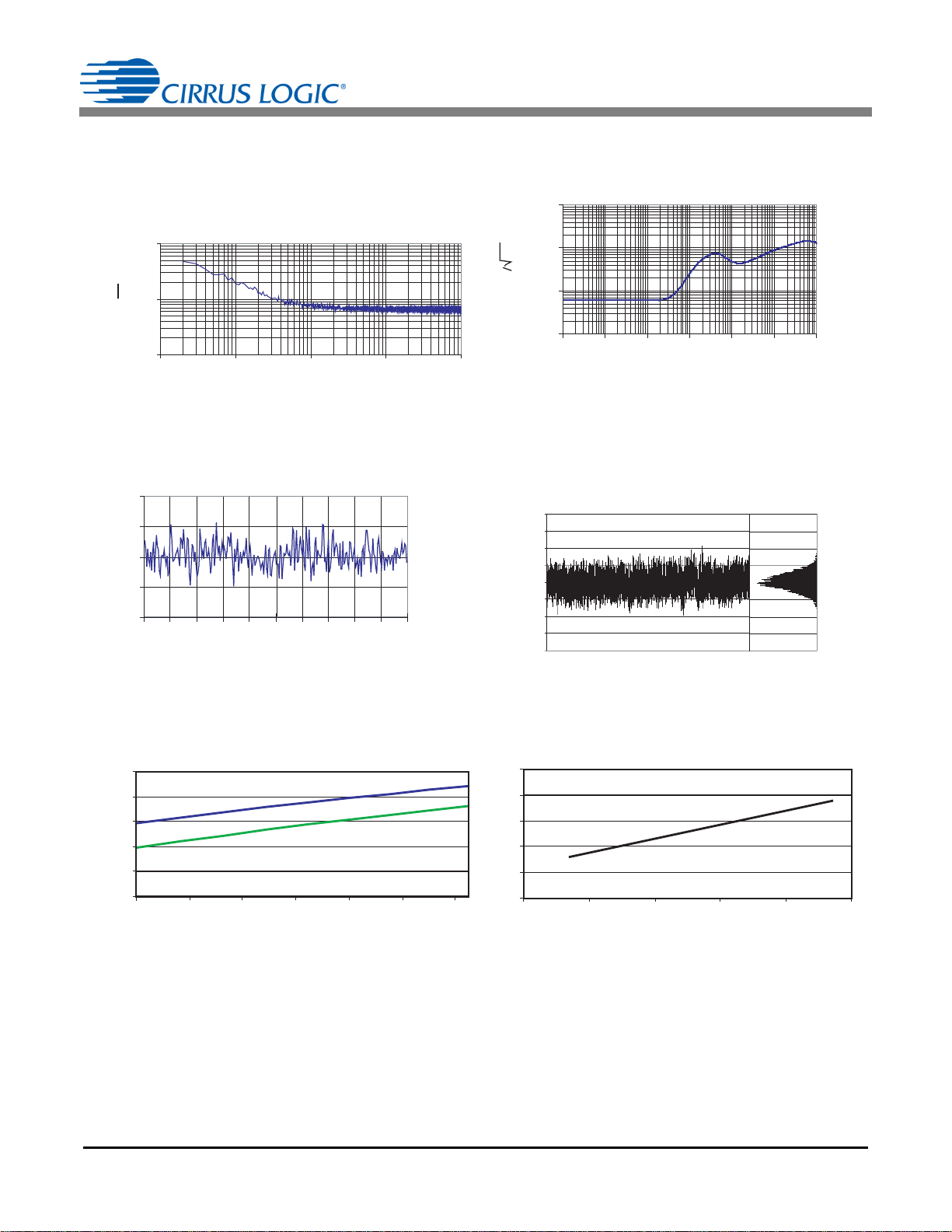

Figure 7. Open-loop Gain and Phase vs. Frequency.................................................................... 5

Figure 8. Open-loop Gain and Phase vs. Frequency (Expanded) ................................................ 5

Figure 9. Input Bias Current vs. Supply Voltage ........................................................................... 6

Figure 10. Input Bias Current vs. Common Mode Voltage ........................................................... 6

Figure 11. Voltage Swing vs. Output Current ............................................................................... 7

Figure 12. Voltage Swing vs. Output Current (5V) ....................................................................... 7

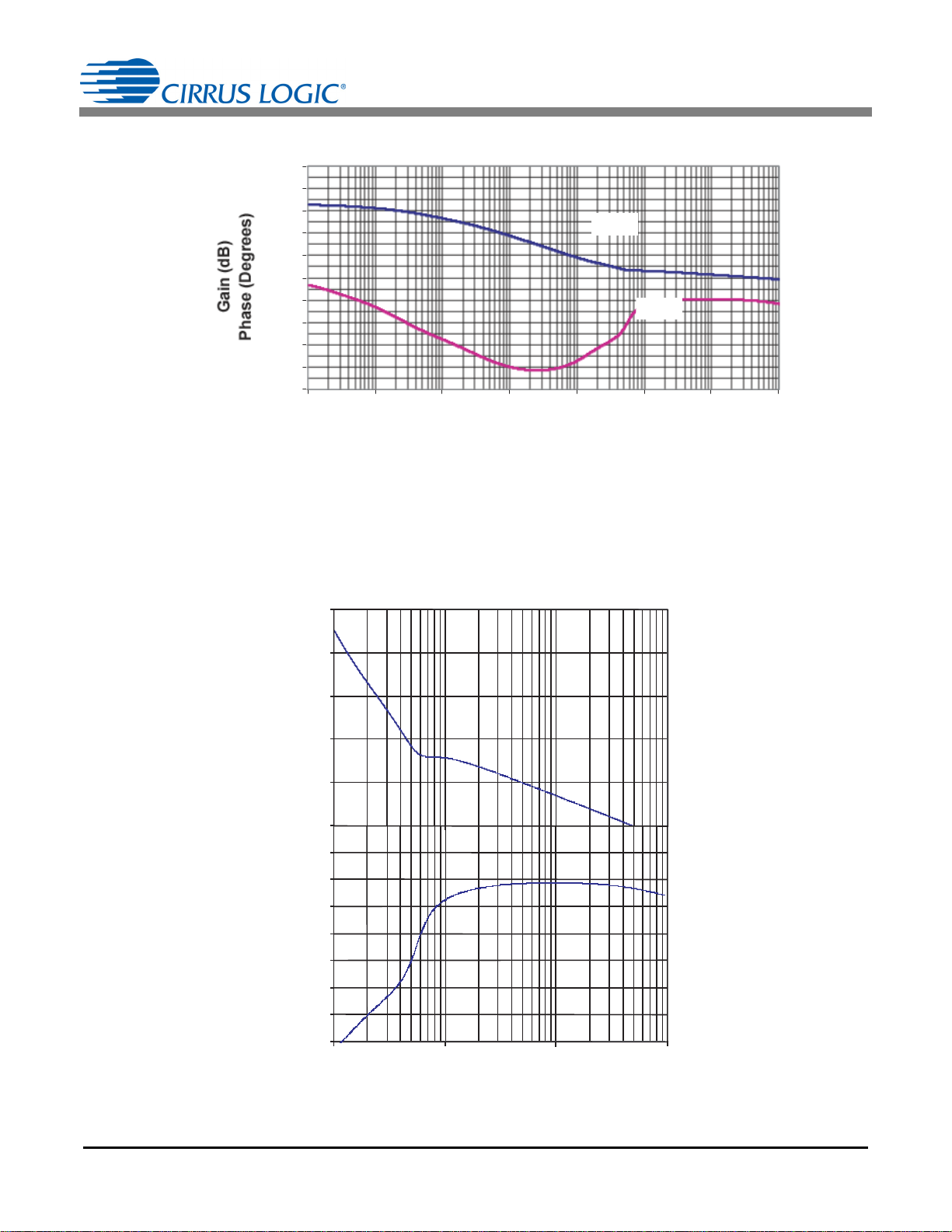

Figure 13. Open-loop Gain and Phase Response ........................................................................ 8

Figure 14. Non-inverting Gain Configuration ................................................................................ 9

Figure 15. Non-inverting Gain Configuration with Compensation................................................. 9

Figure 16. Loop Gain Plot: Unity Gain and with Pole-zero Compensation ................................. 10

Figure 17. Thermopile Amplifier with a Gain of 650V/ V ............................................................. 12

Figure 18. Load Cell Bridge Amplifier and A/D Converter .......................................................... 12

2 DS490F10

Page 3

1. CHARACTERISTICS AND SPECIFICATIONS

nV/ Hz

nV/ Hz

fA/ Hz

1.1 Electrical Characteristics

Typical characteristics conditions:

=25°C, V+=+5V, V-=0V, VCM=2.5V

•T

A

• All voltages are measured with respect to V-

CS3002

Minimum/Maximum characteristics conditions:

•TJ=-40°Cto+125°C, V+=+5V, V-=0V, VCM=2.5V

Parameter

Condition

Min Typ Max Unit

Input Offset Voltage (Note 1)--±10µV

Average Input Offset Drift (Note 1) - ±0.01 ±0.05 µV/ºC

Long Term Input Offset Voltage Stability (Note 2)

Input Bias Current T

Input Offset Current

R

= 100, f0 = 1Hz

Input Noise Voltage Density

Input Noise Voltage

S

R

= 100, f0 = 1kHz

S

0.1 to 10Hz - 125 nV

Input Noise Current Density

Input Noise Current

0.1 to 10Hz - 1.9 pA

= 25ºC

A

T

= 25ºC

A

-

-

-

-

-

-

= 1Hz - 100

f

0

±100

-

±200

-

6

6

-

±1000

-

±2000

pA

pA

pA

pA

pp

p-p

Input Common Mode Voltage Range -0.1 - (V+)-1.25 V

Common Mode Rejection Ratio (DC) (Note 3) 115 120 - dB

Power Supply Rejection Ratio 120 136 - dB

Large Signal Voltage Gain (Note 4)R

Output Voltage Swing

= 2k to V+/2 200 300 - dB

L

= 2k to V+/2

R

L

R

= 100k to V+/2

L

+4.7 -

+4.99

-

V

V

= 2k, 100pF 5 - V/µs

Slew Rate

R

L

Overload Recovery Time - 100 - µs

PWDN

Threshold (Note 5) (V+) -1.0 - - V

Start-up Time (Note 5)-912ms

Notes: 1. This parameter is guaranteed by design and laboratory characterization. Thermocouple effects prohibit accurate

measurement of these parameters in automatic test systems.

2. 1000-hour life test data @ 125 °C indicates randomly distributed variation approximately equal to measurement

repeatability of 1µV.

3. Measured within the specified common mode range limits.

4. Guaranteed within the output limits of (V+ - 0.3V) to (V- + 0.3V). Tested with proprietary production test method.

5. The device has a controlled start-up behavior due to its complex open-loop gain characteristics. Start-up time

applies when supply voltage is applied or when PDWN

is released.

1.2 Absolute Maximum Ratings

Parameter Min Typ Max Unit

Supply Voltage [(V+) - (V-)] 6.8 V

Input Voltage (V-) - 0.3 (V+) + 0.3 V

Storage Temperature Range -65 +150 ºC

DS490F10 3

Page 4

2. TYPICAL PERFORMANCE PLOTS

Noise vs. Frequency (Measured)

1

10

100

0.001 0.01 0.1 1 10

Frequency (Hz)

nV/√Hz

1

10

100

1000

10 100 1K 10K 100K 1M 10M

Frequency (Hz)

-100

-50

0

50

100

TIM E (Se c)

0

1

2

34 5

6

78

9

10

Time (1 Hour)

-100

-75

-50

-25

0

25

50

75

100

nV

= 13 nVσ

Tempe rature (°C)

Supply Current (mA)

2.7 V

6.7 V

2.0

2.5

3.0

3.5

4.0

4.5

-40 -20 0 20 40 60 80

1.5

1.6

1.7

1.8

1.9

2

234567

Supply Voltage (V)

Supply Current (mA)

CS3002

Figure 1. Noise vs. Frequency (Measured)

nV

Figure 3. 0.01Hz to 10Hz Noise

Figure 2. Noise vs. Frequency

Figure 4. Offset Voltage Stability (DC to 3.2Hz)

Figure 5. Supply Current vs. Temperature

4 DS490F10

Figure 6. Supply Current vs. Supply Voltage

Page 5

CS3002

-500

-400

-300

-200

-100

0

100

200

300

400

500

Figure 7. Open-loop Gain and Phase vs. Frequency

1 10 100 1k 10k 1M 10M

Frequency (Hz)

100k

GAIN

PHASE

1M

M

Gain (dB)

100

Figure 8. Open-loop Gain and Phase vs. Frequency (Expanded)

80

60

40

20

0

-45

-90

-135

-180

-225

-270

Phase (Degrees)

-315

-360

10K

100K

10

DS490F10 5

Page 6

S

)

-15

0

Figure 9. Input Bias Current vs. Supply Voltage

-3

-2

-1

0

1

2

3

012345

Common Mode Voltage (Vs = 5V)

Bias Current

Normalized to CM = 2.5 V

Figure 10. Input Bias Current vs. Common Mode Voltage

-100

-50

-50

CS3002

A1A1+

B1-

A2+

0

B1+

A2-

-100

Input Bias Current (pA

-150

-200

CM = 0 V

±1.35

±2

upply V oltage (±V)

±2.5 ±3.35

B2B2+

6 DS490F10

Page 7

CS3002

-200

-150

-250

-100

-50

V+

V–

+50

+100

+150

+200

+250

01234 5

Output Curre nt (m A)

Output Voltage (mV)

+125°C

-40°C

+125°C

+25

°C

+25°C

-40°C

-200

-150

-250

-100

-50

V+

V–

+50

+100

+150

+200

+250

01234 5

Output Curre nt (m A)

Output Voltage (mV)

+125°C

-40°C

+125°C

+25

°C

+25°C

-40°C

Figure 11. Voltage Swing vs. Output Current

Figure 12. Voltage Swing vs. Output Current (5V)

DS490F10 7

Page 8

3. OVERVIEW

1M

Gain (dB)

100

Figure 13. Open-loop Gain and Phase Response

The CS3002 amplifiers are designed for precision

measurement of signals from DC to 2kHz when

operating from a supply voltage of +2.7V to +6.7V

(1.35V to 3.35V). The amplifiers are designed with

a patented architecture that utilizes multiple amplifier

stages to yield very high open-loop gain at frequencies

of 10 kHz and below.

The amplifiers yield low noise and low offset drift while

consuming relatively low supply current. An increase in

noise floor above 2kHz is the result of intermediate

stages of the amplifier being operated at very low

currents. The amplifiers are intended for amplifying

CS3002

small signals with large gains in applications where the

output of the amplifier can be band-limited to

frequencies below 2kHz.

3.1 Open-loop Gain and Phase Response

Figure 13 illustrates the open-loop gain and phase

response of the CS3002. The gain slope of the amplifier

is approximately -100dB/decade between 500 Hz and

60kHz and transitions to -20dB/decade between 60kHz

and its unity gain crossover frequency at approximately

4.8MHz. Phase margin at unity gain is about 70

the gain margin is approximately 20dB.

and

80

60

40

20

0

-45

-90

-135

-180

-225

-270

Phase (Degrees)

-315

-360

10K

-100 dB/ dec

100K

-20 dB/ dec

10M

8 DS490F10

Page 9

CS3002

f

1

2RC

in

--------------------------

=

[Eq. 1]

R2 C2 R1 Cin

[Eq. 2]

R1

R2

Vin

Vo

R

S

CS3002

Figure 14. Non-inverting Gain Configuration

50 pF

50 pF

R1

R2

Vin

Vo

C2

C

in

C

in

Choose C2 so that R2 C2 R1 C

in

CS3002

Figure 15. Non-inverting Gain Configuration with Compensation

Ts

1

s

Z

1

------

+

–

1

s

P

1

------

+

------------------------ -

A

ol

=

[Eq. 3]

3.2 Open-loop Gain and Stability

3.2.1 Discussion

The CS3002 achieves ultra-high open-loop gain.

Figure 14 illustrates the amplifier in a non-inverting gain

configuration. The open-loop gain and phase plots

indicate that the amplifier is stable for closed-loop gains

less than 50V/V and R1 100

phase margin is between 40 and 60 depending upon

the loading conditions. As shown in Figure 15, on

page 9, the operational amplifier has an input

capacitance at the + and – signal inputs of typically

50pF. This capacitance adds an additional pole in the

loop gain transfer function at a frequency defined using

Equation 1:

where

R = R1 R2; the parallel combination of R1 and R2

. For a gain of 50, the

A higher value for R produces a pole at a lower

frequency, thus reducing the phase margin. Resistor R1

is recommended to be less than or equal to 100

,

which results in a pole at 30MHz or higher. If a higher

value of R1 is desired, compensation capacitor C2

should be added in parallel with resistor R2. Capacitor

C2 should be chosen using Equation 2:

The feedback capacitor C2 is required for closed-loop

gains greater than 50V/V. The capacitor introduces a

pole P

and a zero Z1 in the loop gain transfer function

1

T(s), see Equation 3

DS490F10 9

Page 10

CS3002

Z

1

1

2 AR1C2

--------------------------------------------------

=

[Eq. 4]

Z

1

1

2 R2 C2

-----------------------------------

=

[Eq. 5]

P

1

1

2 R1 R2

C2

-----------------------------------------------------

1

2 R1 C2

-----------------------------------

=

[Eq. 6]

C2

1

2 R1 P

1

--------------------------------- -

=

[Eq. 7]

|

Figure 16. Loop Gain Plot: Unity Gain and with Pole-zero Compensation

Equation 4 is used to determine transfer function zero

Z

1.

where

|A| = R2/ R1

Substituting A into Equation 4 then zero Z

1

is:

Equation 6 is used to determine the transfer function

pole P

.

1

where

R2>> R1

This indicates that the separation of the pole and the

zero is governed by the closed loop gain. It is required

that the zero falls on the steep slope (-100dB/decade)

of the loop gain plot so that there is some gain higher

than 0dB (typically 20dB) at the hand-over frequency

(the frequency at which the slope changes

from -100dB/decade to -20dB/decade). The loop gain

plot shown in Figure 16 illustrates the unity gain

configuration, and indicates how this is modified when

using the amplifier in a higher gain configuration with

compensation. If it is configured for higher gain, for

example, 60dB, the x-axis will move up by 60dB (line

B). Capacitor C2 adds a zero and a pole. The modified

plot indicates the effects of introducing the pole and

zero due to capacitor C2. The pole can be located at any

frequency higher than the hand-over frequency, the

zero has to be at a frequency lower than the hand-over

frequency so as to provide adequate gain margin. The

separation between the pole and the zero is governed

by the closed loop gain. The zero (Z

) occurs at the

1

intersection of the -100dB/decade and -80dB/decade

slopes. The point X in the figure should be at closed

loop gain plus 20dB gain margin. The value for

capacitor C2 is determined by Equation 7. Setting the

pole of the filter to P

= 1 MHz works very well and is

1

independent of gain. As the closed loop gain is

changed, the zero location is also modified if R1

remains fixed. Capacitor C2 can be increased in value

to limit the amplifier’s rising noise above 2kHz.

-100 dB/dec

z

1

p

T| (Log gain)

-20 dB/dec

FREQUENCY

-80 dB/dec

X

Margin

50kHz 1MHz 5MHz

1

Desired Closed

Loop Gain

B

10 DS490F10

Page 11

CS3002

C2

R1 Cin

R2

---------------------------

[Eq. 8]

C2

1

2 R1 R2

P

1

---------------------------------------------------

=

[Eq. 9]

C2

R1 Cin

R2

---------------------------

[Eq. 10]

P

1

1

2 R1 R2

C2

-----------------------------------------------

=

[Eq. 11]

Z

1

1

2 R2 C2

----------------------------------

=

[Eq. 12]

3.2.2 Gain Calculation Recommendations

Condition 1: |Av| 50 and R1 100

The op amp is inherently stable for |Av| 50 and

R1 100 . Capacitor C2 is not required for

compensation across resistor R2.

1) |Av| = 1 configuration has 70° phase margin and

20dB gain margin.

2) |Av| = 50 configuration has phase margin between

40° for C

Condition 2: |Av| 50 and R1 100

Compensation capacitor C2 across resistor R2 is

required. Calculate C2 using Equation 8:

where

C

=50pF

in

Condition 3: |Av| 50

Compensation capacitor C2 across resistor R2 is

required. Calculate and verify a value for C2 using the

following steps.

Calculate the Compensation Capacitor Value:

1) Calculate a value for C2 using Equation 9:

100 pF and 60° for C

LOAD

LOAD

0pF.

To simplify the calculation, set the pole of the filter to

P

= 1 MHz. Pole P1 must be set higher than the

1

op amp’s internal 50kHz crossover frequency.

2) Calculate a second value for C2 using Equation 10:

where

C

=50pF

in

3) Use the larger of the two values calculated in steps

1 and 2.

Verify the Op Amp Compensation:

Verify the op amp compensation using the open-loop

gain and phase response Bode plot in Figure 13. Plot

the calculated closed loop gain transfer function and

verify the following design criteria are met:

1) Pole P

frequency

where

P

To simplify the calculation, set the pole to P

2) Z1 < op amp internal 50 kHz crossover frequency

> op amp internal 50kHz crossover

1

=1MHz

1

=1MHz.

1

where

P

1

=1MHz

3) Gain margin above the open-loop gain transfer

function is required. A gain margin of +20dB above

the open-loop gain transfer function is optimal.

DS490F10 11

Page 12

CS3002

CS3002

R1

100

R2

64.9k

C2

0.015F

Figure 17. Thermopile Amplifier with a Gain of 650 V/V

+5 V

1 mV/V

-

+

350

+

-

-

+

x768

140 k

365

140 k

100

100

0.22F

0.22

F

0.047

F

0.1

F

A

A

CS

SDO

SCLK

CS5510/12

C

+5 V +5 V

Counter/Timer

SCLK = 10 kHz to 100

(32.768

SCLK = 10 kHz to 100 kHz

(32.768 nominal)

CS3002

CS3002

Figure 18. Load Cell Bridge Amplifier and A/D Converter

3.3 Applications

The CS3002 amplifiers are optimum for applications

that require high gain and low drift. Figure 17 illustrates

a thermopile amplifier with a gain of 650V/V. The

thermopile outputs only a few millivolts when subjected

to infrared radiation. The amplifier is compensated and

bandlimited by capacitor C2 in combination with resistor

R2.

VA

Figure 18, on page 12 illustrates a load cell bridge

amplifier with a gain of 768V/V. The load cell is excited

with +5V and has a 1mV/V sensitivity. Its full scale

output signal is amplified to produce a fully differential

3.8V into the CS5510/12 A/D converter. This circuit

operates from +5V.

V+

VREF

IN+

IN1

V-

12 DS490F10

Page 13

4. PACKAGE DRAWING

8L SOIC (150 MIL BODY) PACKAGE DRAWING

D

H

E

e

b

A1

A

c

L

SEATING

PLANE

1

CS3002

INCHES MILLIMETERS

DIM MIN MAX MIN MAX

A 0.053 0.069 1.35 1.75

A1 0.004 0.010 0.10 0.25

B 0.013 0.020 0.33 0.51

C 0.007 0.010 0.19 0.25

D 0.189 0.197 4.80 5.00

E 0.150 0.157 3.80 4.00

e 0.040 0.060 1.02 1.52

H 0.228 0.244 5.80 6.20

L 0.016 0.050 0.40 1.27

0° 8° 0° 8°

JEDEC #: MS-012

5. ORDERING INFORMATION

Model Container Temperature Package

CS3002-ISZ (lead free) Bulk

CS3002-ISZR (lead free) Tape & Reel

6. ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION

-40 to +85 °C 8-pin SOIC (Lead Free)

Model Number Peak Reflow Temp MSL Rating* Max Floor Life

CS3002-ISZ (lead free) 260 °C 2 365 Days

* MSL (Moisture Sensitivity Level) as specified by IPC/JEDEC J-STD-020.

DS490F10 13

Page 14

7. REVISION HISTORY

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find the one nearest to you go to www.cirrus.com

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries (“Cirrus”) believe that the information contained in this document is accurate and reliable. However, the information is subject

to change without notice and is provided “AS IS” without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant

information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale

supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third

parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives

consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This

consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR

USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK

AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER

OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE,

TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks

or service marks of their respective owners.

Revision Date Changes

F3 OCT 2004 Added lead-free device ordering information.

F4 AUG 2005 Added MSL specifications. Updated legal notice. Added leaded (Pb) devices.

F5 AUG 2006 Updated Typical Performance Plots.

F6 SEP 2006 Corrected error in Ordering Information section.

F7 NOV 2007 Added additional information regarding open-loop and gain stability compensation.

F8 OCT 2008 Minor, cosmetic correction to caption for Figure 10.

F9 JUL 2009 Removed lead-containing devices from ordering information.

F10 DEC 2012 Removed CS3001 and corrected typographical errors.

CS3002

14 DS490F10

Loading...

Loading...