Page 1

5

www.teknisi-indonesia.com

4

IH81Y-MHS

3

H81MDV5

2

REV:6.2

1

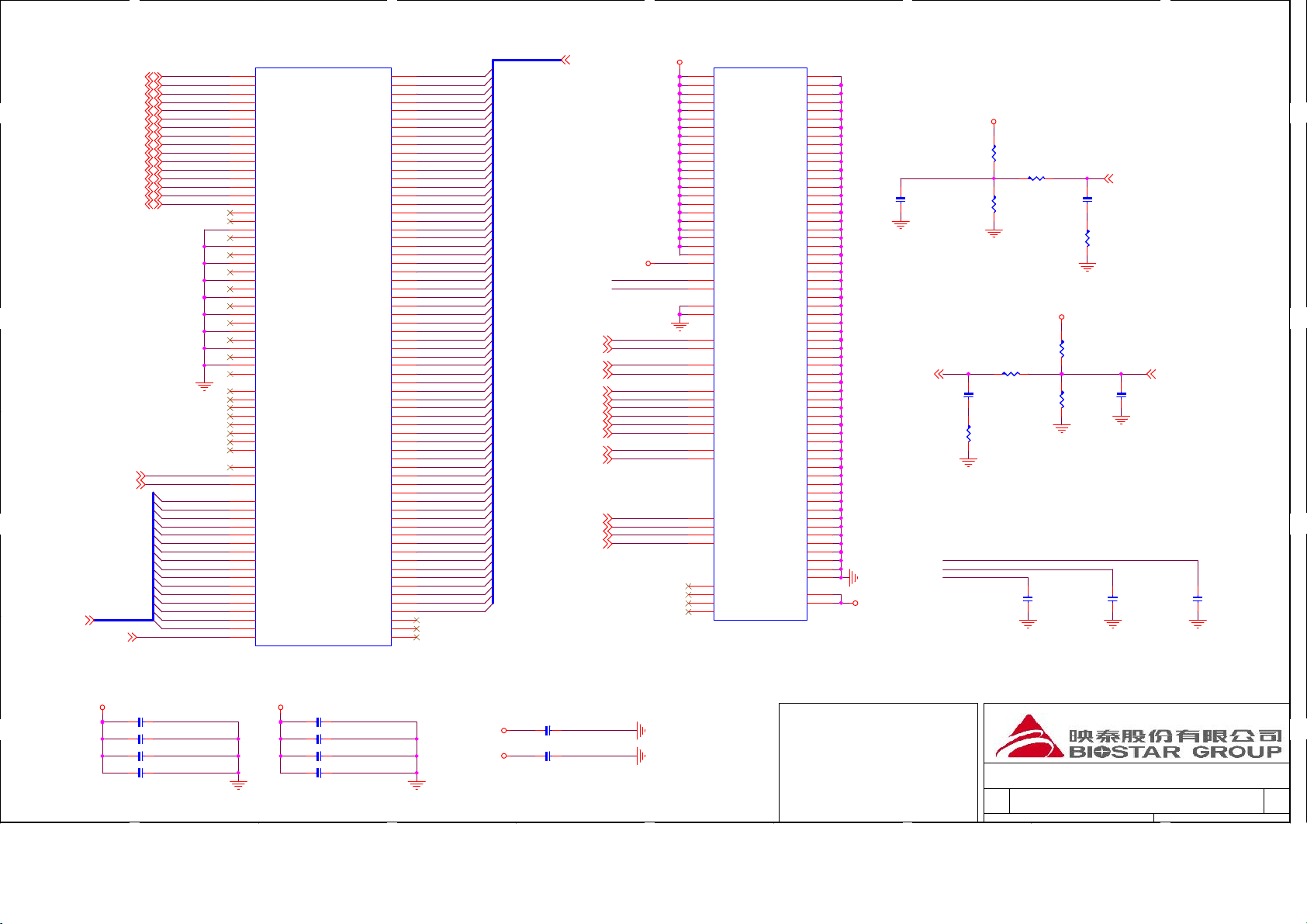

CPU:

PAGE

D D

C C

B B

1

2

3

4

5

6

7

8

9 CPU POWER/GND

10 DDR3 DIMMA1

11 DDR3 DIMMB1

12 PCH DMI/PCIE/USB

13 PCH CL INK/SATA/CPU HOST

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

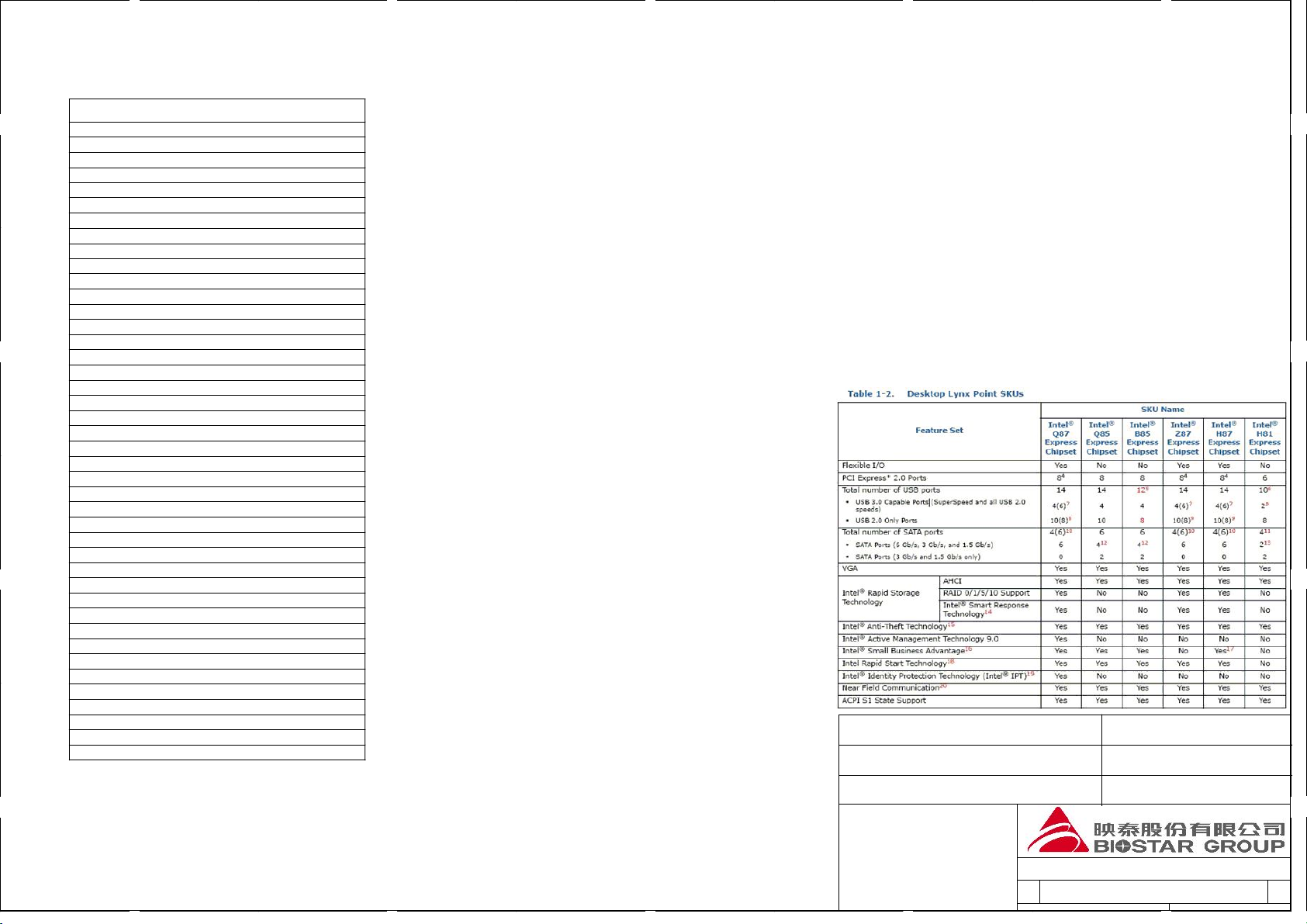

CONTENTS

INDEX

BLOCK DIAGRAM

POW ER DELIVERY

CHANGE LIS T

CPU PCIEX1 6/DMI

CPU DDR CHANNEL A

CPU DDR CHANNEL B

CPU MISC

PCH LPC/HDA/SPI/MISC

PCH NVRAM

PCH FDI LINK

PCH VGA/DISPLA Y PORT

PCH CL OCK BUFFER

PCH POWER

PCH GND

SPI ROM/BA T

PCIEX 16 S LOT1& 2

PCIEX 1 SL OT 1&2

VGA/DVI CO NNECTOR

AUDIO CODEC ALC8 92

AUDIO CONNECTOR

LAN RTL8111F

SUPERIO ITE8 728FEX

SUPERIO PS2/CO M

PCI BRIDGE ASM1083

PCI SLOT

FRONT USB & FAN

USB CONNECTOR

24PIN POW ER CONN& FP

RESUME RESET LOG IC

ACPI POW ER CONTROL

LINEA R POWER

MEMORY DC-DC Conver

ISL95820 PW M

AMT POWER

OVER VOLTAGE/TES T POINT

BOM

A A

LGA1150

System Chipset:

LYNXPOINT-H81

Main Memory:

Dual Channel/DDR-III*2(Max 32GB)

1600/ 1333 /1066

Onboard Device:

Super I/O IT8728F-EX

LAN Realtek 8106E

HD Codec ALC662

Power solution:

CPU Voltage Regulators:4Phase by ISL95812

DDR Voltage Regulators:1Phase by UP1514

Expansion Slots:

PCI EXPRESS 16X SLOT*1

PCI EXPRESS 1X SLOT*1

REAR IO:

PS/2 Keyboard + Mouse Ports

VGA Port

DVI Port

2 layer USB2.0 Ports

Gb RJ-45 +2 USB2.0 Ports

Audio Jackets

Front I/O:

SATA3 * 2 SATA2*2

USB 2.0 Header * 2

USB 3.0 (2.0) Header * 1

CPU /System1 FAN

Front Audio Header

Serial Header

HW Engineer:

HW Leader1:

HW Leader2:

◇

BIOSTAR'S PROPRIETA RY

INFORMATION

◆

◇

Any un authoriz ed use , repro duction,

duplicatio n, o r disc losur e o f this do cument

will be subjec t to the applicable c ivil

and/orc riminal penaltie s.

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Date:

Date:

Date:

INDEX

INDEX

INDEX

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

6.0

6.0

1 39Monday, March 31, 2014

1 39Monday, March 31, 2014

1 39Monday, March 31, 2014

6.0

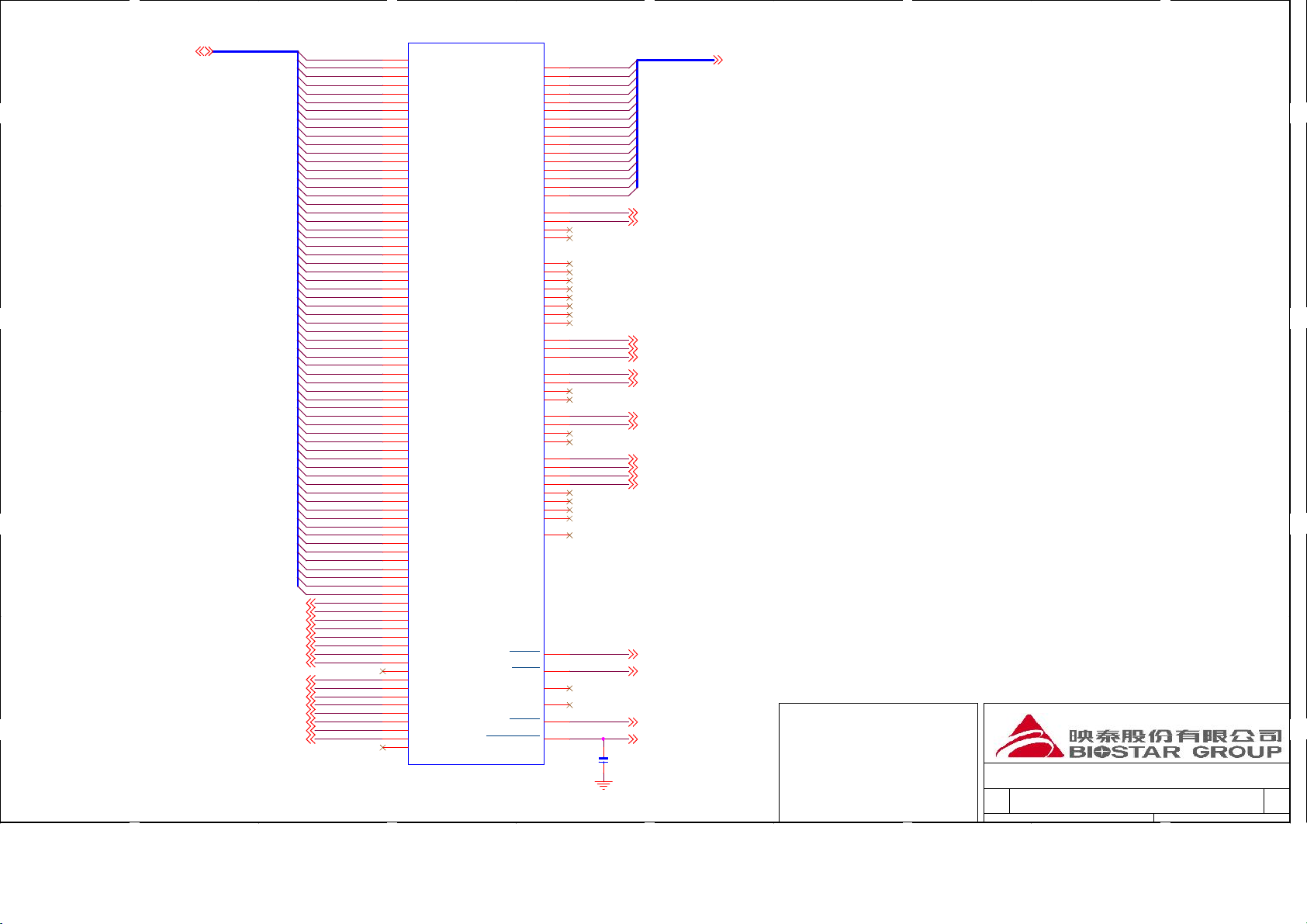

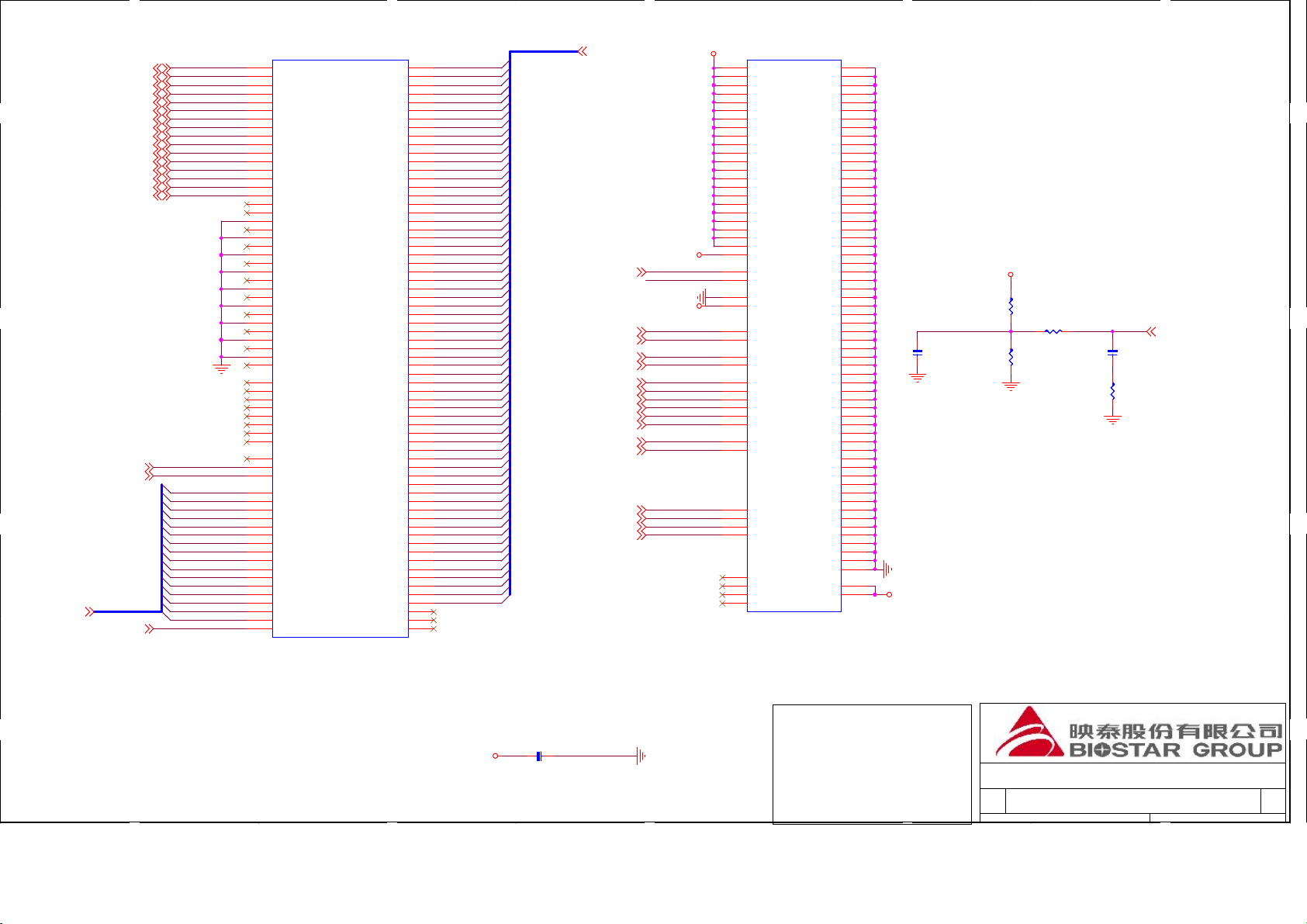

Page 2

5

www.teknisi-indonesia.com

4

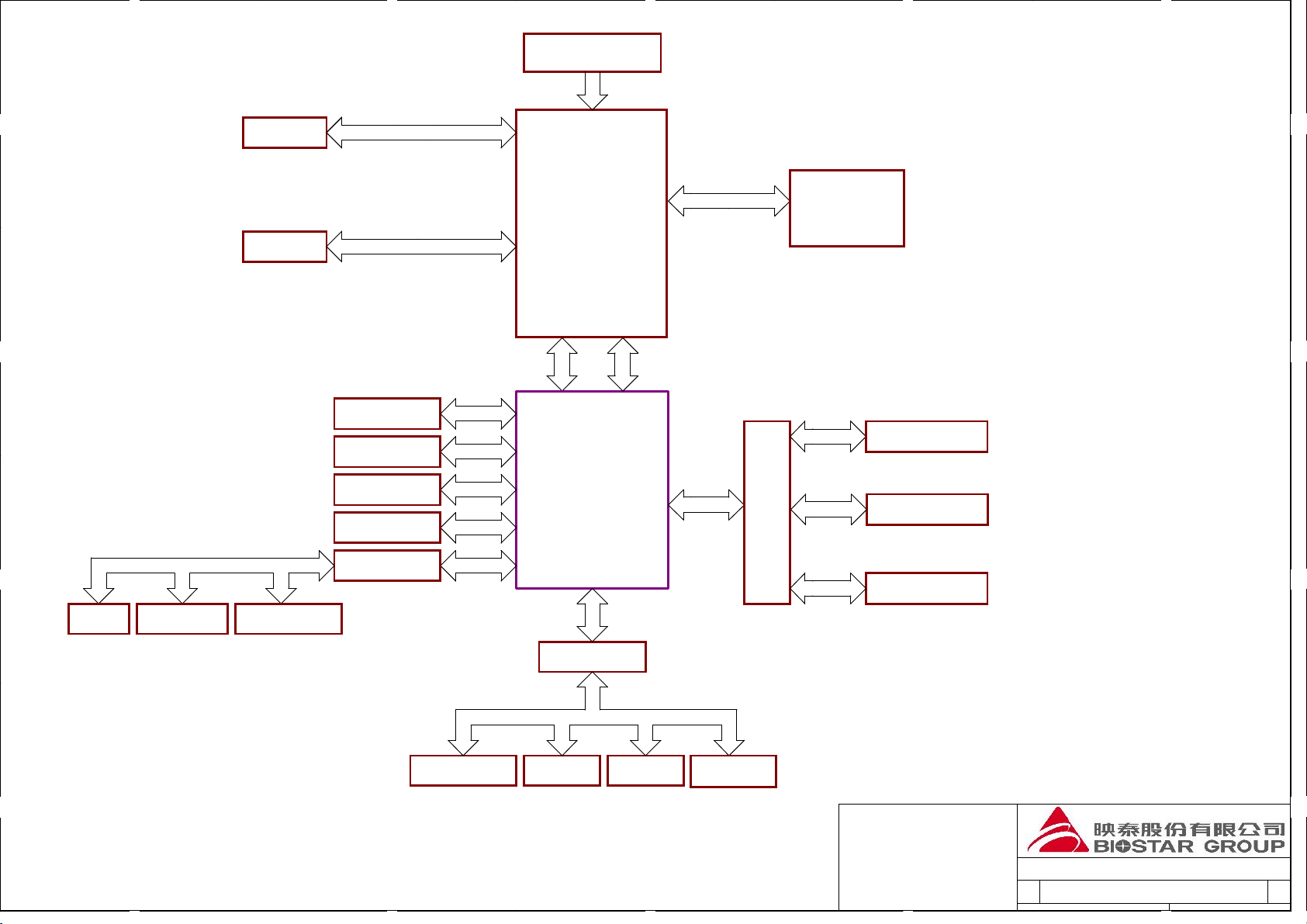

VR12.5

ISL95812-3 Phase

3

2

1

D D

PEG X16 CONN

X16 SLOT *1

PCIE GEN3 X16

Haswell

Dual Channel DDR3

Channel A DIMM X2

Channel B DIMM X2

5GT/s

8 PCIE2.0 PORTS

T-Topology

GIGA LAN RTL8111G

PEG X1 SLOT*2

MINI PEG X1 SLOT*1

DVI

PORT

CPU

PORT B

uLGA 1150 SOCKET

DDR3 1600

C C

USB 2.0 PORTS *8

USB 3.0 PORTS *2

SATA3.0 PORTS*2

VGA PORT

SPI FLASH 64M

5.1CH HD Codec

B B

ALC662

DMI FDI

LPT

Lynx Point

708 PIN

LPC

3JACKS

SPDIF OUT PORT Front Audio Header

CPU SMART FAN X1

SYSTEM FAN X1

SUPER I/O

IT8728F-EX

PS2 KB/MS Serial header

Parallel header

A A

◇

BIOSTAR'S PROPRIETA RY

INFORMATION

◆

◇

Any un authoriz ed use , repro duction,

duplicatio n, o r disc losur e o f this do cument

will be subjec t to the applicable c ivil

and/orc riminal penaltie s.

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

2 39Friday, March 28, 2014

2 39Friday, March 28, 2014

2 39Friday, March 28, 2014

6.0

6.0

6.0

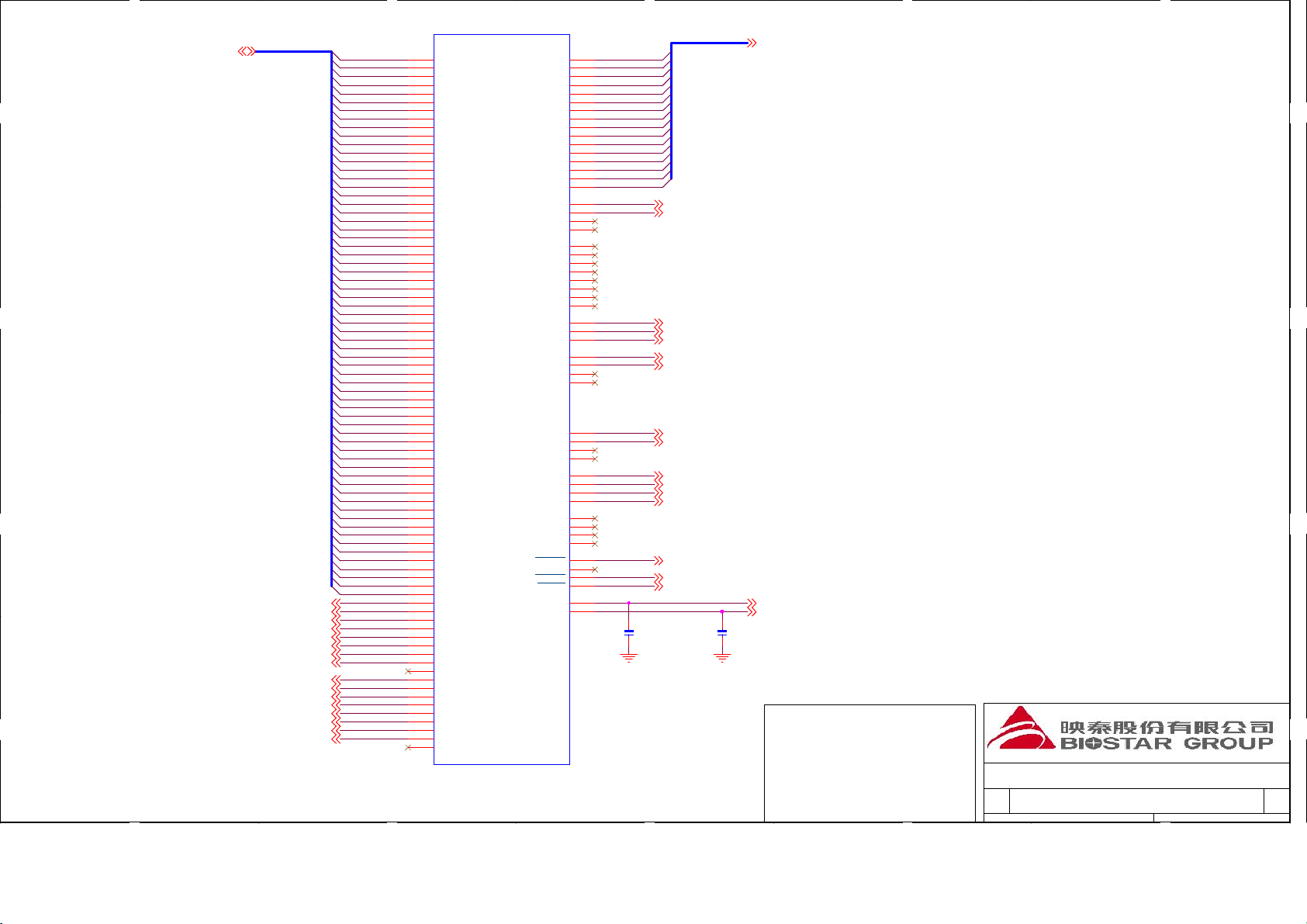

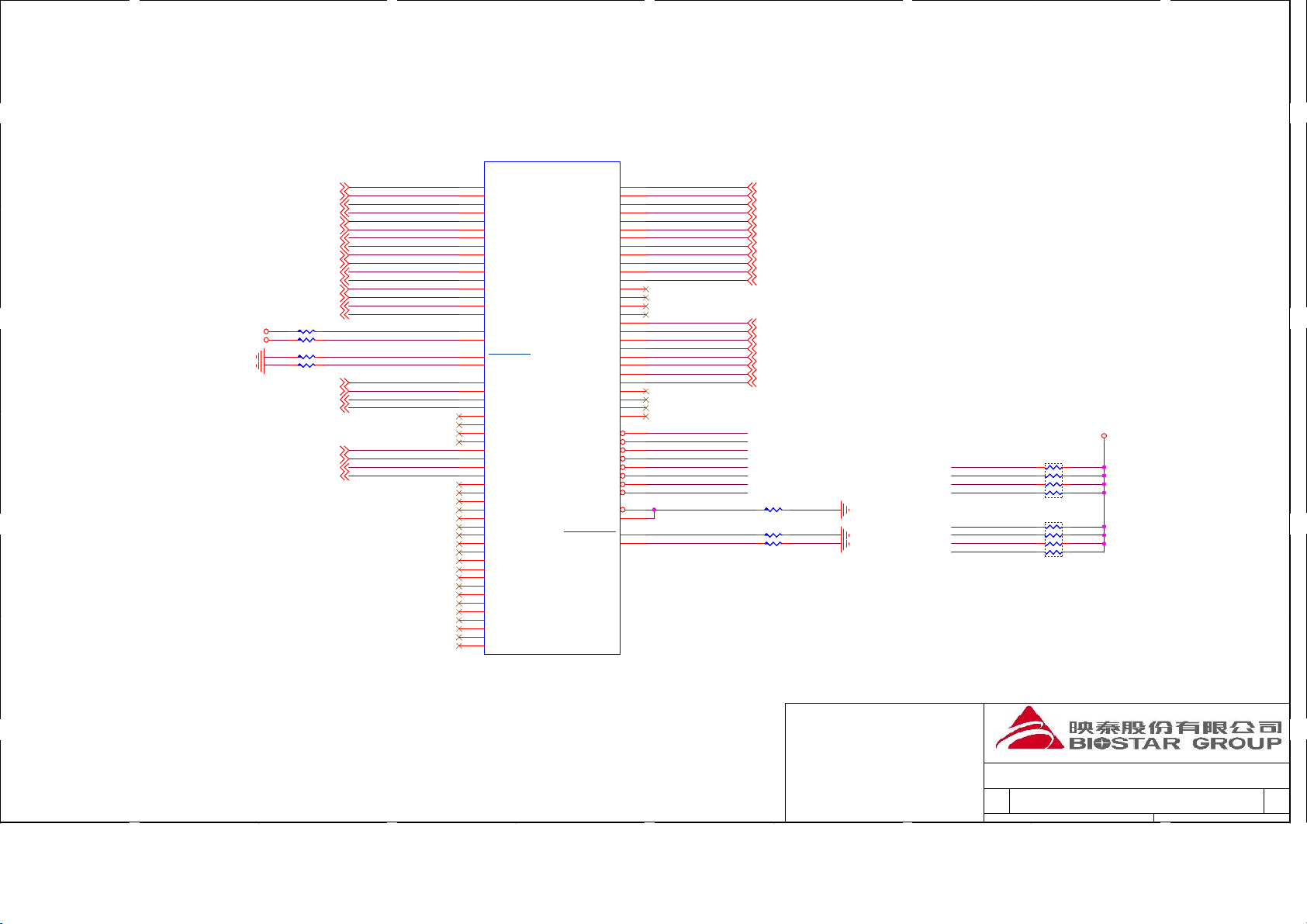

Page 3

5

www.teknisi-indonesia.com

4

3

2

1

D D

C C

B B

A A

◇

BIOSTAR'S PROPRIETARY

INFORMATION

◆

◇

Any unaut horized us e, reproductio n,

duplication, o r disclosu re of this do cument

will be s ubject to t he applicable civil

and/orc riminal penalties .

◆

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: S heet of

Date: S heet of

Date: S heet of

POWER DELIVERY

POWER DELIVERY

POWER DELIVERY

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

3 39Frid ay, March 28, 2014

3 39Frid ay, March 28, 2014

3 39Frid ay, March 28, 2014

6.0

6.0

6.0

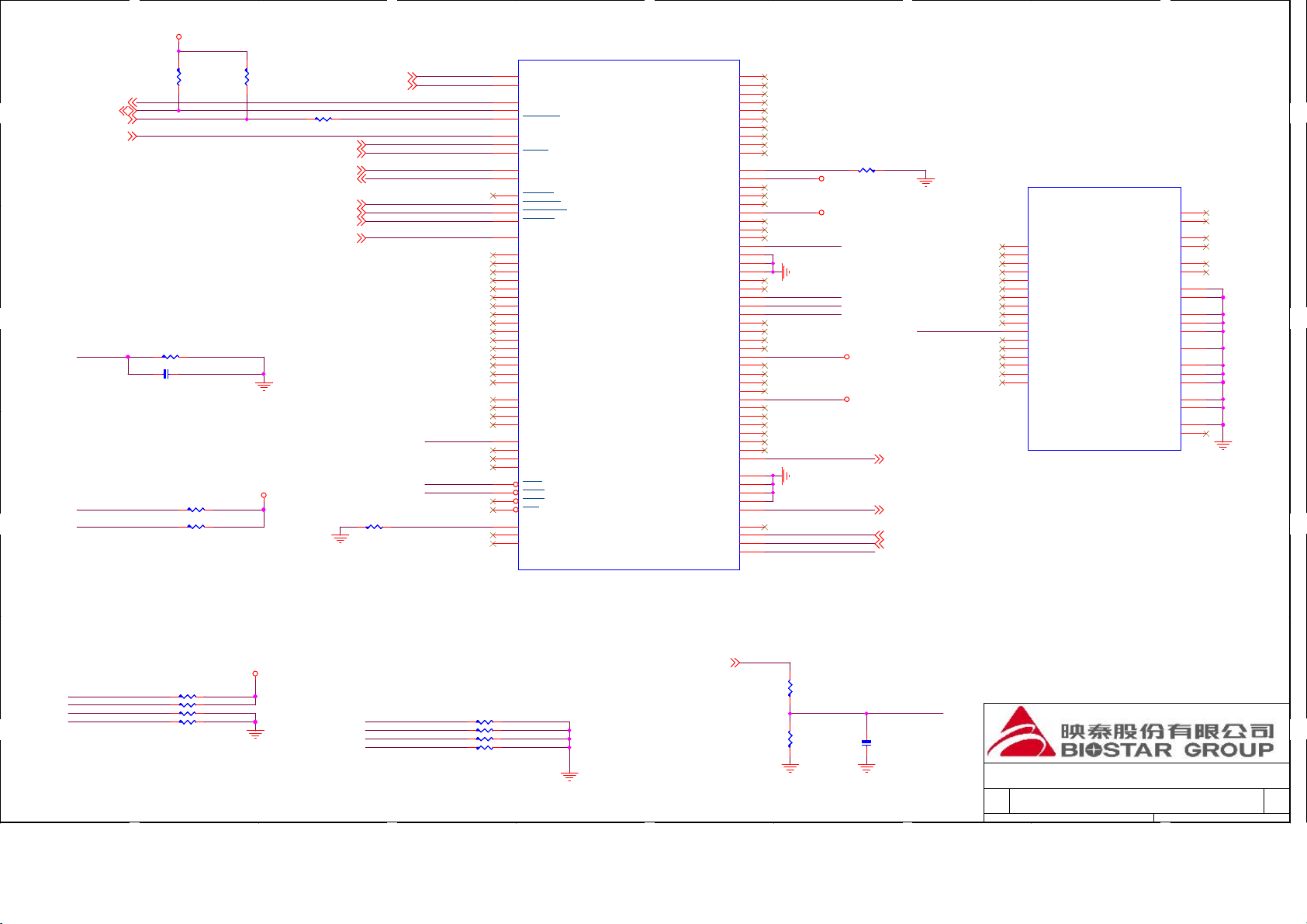

Page 4

2014/02/06

www.teknisi-indonesia.com

5

4

3

2

1

1.ADD S3

2.Rear U3

改為

Front U3

3.Lan Chip RTL 8111G---> RTL 8106E

4.VSM MOS USE SM4377N DFN 5X6

5.10UF 10V Y5V 0805 -->10UF 6.3V X5R

6.560 UF ---> 560UF-S 6.3V 24M 6.3X9 APAQ

D D

7.BEAD 0805 ---> BEAD 60 0603

8.USB 3.0 Use FUSE 0805 2A 49mOHM& FUSE 0805 1.1A 0.12OHM

2014/02/07

1.100UF 16V 6.3X5 2.5mm colay 22UF 6.3V X5R 0805

2.AC37 /AC35 10UF 10V 0805 Y5V --->10UF 6.3V X5R

3.Add S3 ACPI_LED Function

4.PC7/PC52 4.7UF 16V Y5V 0805 --->10UF 6.3V X5R

5.Add AZ1117 +5V_DAUL to 3V3_DUAL POWER

6.AC37/AC35 10UF 10V 0805 Y5V --->10UF 6.3V X5R

7.C57 22UF 6.3V X5R 0805 --->10UF 6.3V X5R

8.C79 1UF10V X5R 0402 --->1UF 6.3V X5R 0402

9.MU1 VCC INPUT VCC12 & +5V_STBY

C C

10.MU2 VIN VCC5 ---> +5V_DUAL

B B

A A

◇

BIOSTAR' S PROPRIETARY

INFORMATION

◇

duplication, or disclosure of this document

will be subject to the applicable civil

and/orcriminal penalties.

5

4

3

◆

Any unauthorized use, reproduction,

◆

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

CHANGELIST

CHANGELIST

CHANGELIST

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

4 39Friday, March 28, 2014

4 39Friday, March 28, 2014

4 39Friday, March 28, 2014

1

6.0

6.0

6.0

Page 5

5

www.teknisi-indonesia.com

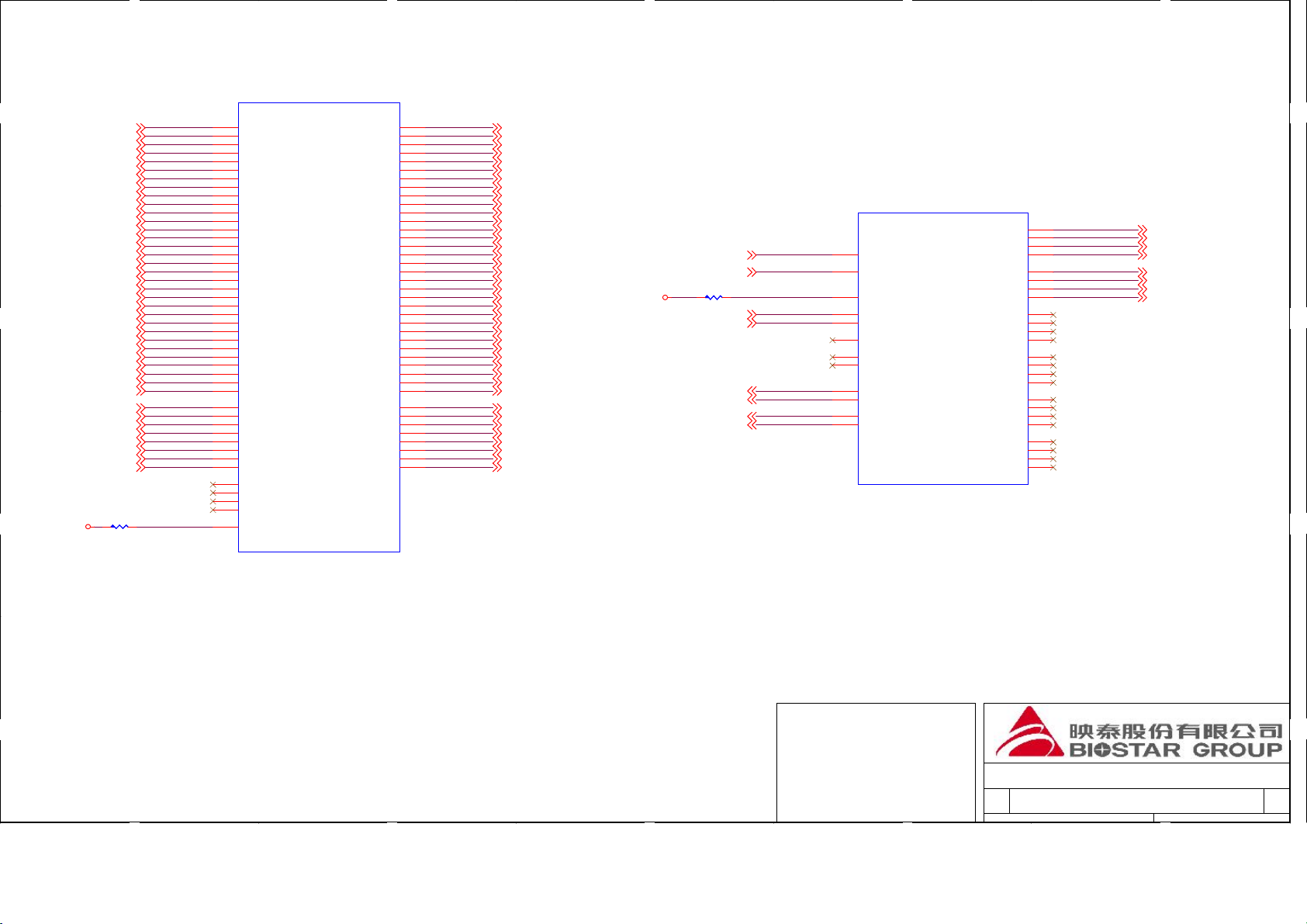

CPU1C

CPU1C

D D

C C

V_VCCIOA_LOAD

B B

EXP_A_RX_0_DP22

EXP_A_RX_0_DN22

EXP_A_RX_1_DP22

EXP_A_RX_1_DN22

EXP_A_RX_2_DP22

EXP_A_RX_2_DN22

EXP_A_RX_3_DP22

EXP_A_RX_3_DN22

EXP_A_RX_4_DP22

EXP_A_RX_4_DN22

EXP_A_RX_5_DP22

EXP_A_RX_5_DN22

EXP_A_RX_6_DP22

EXP_A_RX_6_DN22

EXP_A_RX_7_DP22

EXP_A_RX_7_DN22

EXP_A_RX_8_DP22

EXP_A_RX_8_DN22

EXP_A_RX_9_DP22

EXP_A_RX_9_DN22

EXP_A_RX_10_DP22

EXP_A_RX_10_DN22

EXP_A_RX_11_DP22

EXP_A_RX_11_DN22

EXP_A_RX_12_DP22

EXP_A_RX_12_DN22

EXP_A_RX_13_DP22

EXP_A_RX_13_DN22

EXP_A_RX_14_DP22

EXP_A_RX_14_DN22

EXP_A_RX_15_DP22

EXP_A_RX_15_DN22

DMI_IT_MR_0_DP12

DMI_IT_MR_0_DN12

DMI_IT_MR_1_DP12

DMI_IT_MR_1_DN12

DMI_IT_MR_2_DP12

DMI_IT_MR_2_DN12

DMI_IT_MR_3_DP12

DMI_IT_MR_3_DN12

CR1

CR1

24.9 1% 0402

24.9 1% 0402

PEG_RCOMP

E15

PEG_RX[0 ]

F15

PEG_RX# [0]

D14

PEG_RX[1 ]

E14

PEG_RX# [1]

E13

PEG_RX[2 ]

F13

PEG_RX# [2]

D12

PEG_RX[3 ]

E12

PEG_RX# [3]

E11

PEG_RX[4 ]

F11

PEG_RX# [4]

F10

PEG_RX[5 ]

G10

PEG_RX# [5]

E9

PEG_RX[6 ]

F9

PEG_RX# [6]

F8

PEG_RX[7 ]

G8

PEG_RX# [7]

D3

PEG_RX[8 ]

D4

PEG_RX# [8]

E4

PEG_RX[9 ]

E5

PEG_RX# [9]

F5

PEG_RX[1 0]

F6

PEG_RX# [10]

G4

PEG_RX[1 1]

G5

PEG_RX# [11]

H5

PEG_RX[1 2]

H6

PEG_RX# [12]

J4

PEG_RX[1 3]

J5

PEG_RX# [13]

K5

PEG_RX[1 4]

K6

PEG_RX# [14]

L4

PEG_RX[1 5]

L5

PEG_RX# [15]

U3

DMI_RX[0 ]

T3

DMI_RX#[ 0]

U1

DMI_RX[1 ]

V1

DMI_RX#[ 1]

W2

DMI_RX[2 ]

V2

DMI_RX#[ 2]

Y3

DMI_RX[3 ]

W3

DMI_RX#[ 3]

D1

RSVD_TP_D1

C2

RSVD_TP_C2

B3

RSVD_TP_B3

A4

RSVD_TP_A4

P3

PEG_RCOMP

LGA 1150 SOCKET

LGA 1150 SOCKET

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

PEGX16

PEGX16

DMI

DMI

3 OF 10

3 OF 10

PEG_TX[0]

PEG_TX#[0 ]

PEG_TX[1]

PEG_TX#[1 ]

PEG_TX[2]

PEG_TX#[2 ]

PEG_TX[3]

PEG_TX#[3 ]

PEG_TX[4]

PEG_TX#[4 ]

PEG_TX[5]

PEG_TX#[5 ]

PEG_TX[6]

PEG_TX#[6 ]

PEG_TX[7]

PEG_TX#[7 ]

PEG_TX[8]

PEG_TX#[8 ]

PEG_TX[9]

PEG_TX#[9 ]

PEG_TX[10 ]

PEG_TX#[1 0]

PEG_TX[11 ]

PEG_TX#[1 1]

PEG_TX[12 ]

PEG_TX#[1 2]

PEG_TX[13 ]

PEG_TX#[1 3]

PEG_TX[14 ]

PEG_TX#[1 4]

PEG_TX[15 ]

PEG_TX#[1 5]

DMI_TX[0]

DMI_TX#[0 ]

DMI_TX[1]

DMI_TX#[1 ]

DMI_TX[2]

DMI_TX#[2 ]

DMI_TX[3]

DMI_TX#[3 ]

4

A12

B12

B11

C11

C10

D10

B9

C9

C8

D8

B7

C7

A6

B6

B5

C5

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

M2

M3

L1

L2

AA4

AA5

AB3

AB4

AC5

AC4

AC1

AC2

EXP_A_TX_0_DP 22

EXP_A_TX_0_DN 22

EXP_A_TX_1_DP 22

EXP_A_TX_1_DN 22

EXP_A_TX_2_DP 22

EXP_A_TX_2_DN 22

EXP_A_TX_3_DP 22

EXP_A_TX_3_DN 22

EXP_A_TX_4_DP 22

EXP_A_TX_4_DN 22

EXP_A_TX_5_DP 22

EXP_A_TX_5_DN 22

EXP_A_TX_6_DP 22

EXP_A_TX_6_DN 22

EXP_A_TX_7_DP 22

EXP_A_TX_7_DN 22

EXP_A_TX_8_DP 22

EXP_A_TX_8_DN 22

EXP_A_TX_9_DP 22

EXP_A_TX_9_DN 22

EXP_A_TX_10_DP 22

EXP_A_TX_10_DN 22

EXP_A_TX_11_DP 22

EXP_A_TX_11_DN 22

EXP_A_TX_12_DP 22

EXP_A_TX_12_DN 22

EXP_A_TX_13_DP 22

EXP_A_TX_13_DN 22

EXP_A_TX_14_DP 22

EXP_A_TX_14_DN 22

EXP_A_TX_15_DP 22

EXP_A_TX_15_DN 22

DMI_MT_IR_0_DP 12

DMI_MT_IR_0_DN 12

DMI_MT_IR_1_DP 12

DMI_MT_IR_1_DN 12

DMI_MT_IR_2_DP 12

DMI_MT_IR_2_DN 12

DMI_MT_IR_3_DP 12

DMI_MT_IR_3_DN 12

V_VCCIOA_LOAD

3

FDI_INT16 DDSP_B_TX_2_DP 24

CR3 24.9 1% 0402CR3 24.9 1% 0402

CK_DP_135M_DN18

CK_DP_135M_DP18

DP_COMP:

W/S:20/25.

Within 100mils from PIN.

FDI_TX_0_DN16

FDI_TX_0_DP16

FDI_TX_1_DN16

FDI_TX_1_DP16

DP_RCOMP

CPU1D

CPU1D

D16

FDI_CSY NC

D18

FDI_INT

R4

DP_COMP

U5

SSC_DPL L_REF_CLK#

U6

SSC_DPL L_REF_CLK

E16

EDP_DISP _UTIL

K11

RSVD_TP_K11

J12

RSVD_TP_J1 2

B14

FDI0_TX0 #[0]

A14

FDI0_TX0 [0]

C13

FDI0_TX0 #[1]

B13

FDI0_TX0 [1]

LGA 1150 SOCKET

LGA 1150 SOCKET

2

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

4 OF 10

4 OF 10

DDIB_TXB[0 ]

DDIB_TXB# [0]

DDIB_TXB[1 ]

DDIB_TXB# [1]

DDIB_TXB[2 ]

DDIB_TXB# [2]

DDIB_TXB[3 ]

DDIB_TXB# [3]

DDIC_TXC[0 ]

DDIC_TXC#[ 0]

DDIC_TXC[1 ]

DDIC_TXC#[ 1]

DDIC_TXC[2 ]

DDIC_TXC#[ 2]

DDIC_TXC[3 ]

DDIC_TXC#[ 3]

DDID_TXD[0 ]

DDID_TXD#[ 0]

DDID_TXD[1 ]

DDID_TXD#[ 1]

DDID_TXD[2 ]

DDID_TXD#[ 2]

DDID_TXD[3 ]

DDID_TXD#[ 3]

E17

F17

F18

G18

G19

H19

F20

G20

D19

E19

C20

D20

D21

E21

C22

D22

B15

C15

A16

B16

B17

C17

A18

B18

DVI PORT

1

DDSP_B_TX_0_DP 24

DDSP_B_TX_0_DN 24

DDSP_B_TX_1_DP 24

DDSP_B_TX_1_DN 24FDI_CSYNC16

DDSP_B_TX_2_DN 24

DDSP_B_TX_3_DP 24

DDSP_B_TX_3_DN 24

A A

◇

BIOSTAR' S PROPRIETARY

INFORMATION

◇

duplication, or disclosure of this document

will be subject to the applicable civil

and/orcriminal penalties.

5

4

3

◆

Any unauthorized use, reproduction,

◆

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU PCIEX16/DMI/FDI

CPU PCIEX16/DMI/FDI

CPU PCIEX16/DMI/FDI

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

5 39Friday, March 28, 2014

5 39Friday, March 28, 2014

5 39Friday, March 28, 2014

1

6.0

6.0

6.0

Page 6

5

www.teknisi-indonesia.com

M_DATA_A[0..63]10

D D

C C

B B

A A

M_DATA_A[0..63]

M_DQS_A_DP010

M_DQS_A_DP110

M_DQS_A_DP210

M_DQS_A_DP310

M_DQS_A_DP410

M_DQS_A_DP510

M_DQS_A_DP610

M_DQS_A_DP710

M_DQS_A_DN010

M_DQS_A_DN110

M_DQS_A_DN210

M_DQS_A_DN310

M_DQS_A_DN410

M_DQS_A_DN510

M_DQS_A_DN610

M_DQS_A_DN710

M_DATA_A0

M_DATA_A1

M_DATA_A2

M_DATA_A3

M_DATA_A4

M_DATA_A5

M_DATA_A6

M_DATA_A7

M_DATA_A8

M_DATA_A9

M_DATA_A10

M_DATA_A11

M_DATA_A12

M_DATA_A13

M_DATA_A14

M_DATA_A15

M_DATA_A16

M_DATA_A17

M_DATA_A18

M_DATA_A19

M_DATA_A20

M_DATA_A21

M_DATA_A22

M_DATA_A23

M_DATA_A24

M_DATA_A25

M_DATA_A26

M_DATA_A27

M_DATA_A28

M_DATA_A29

M_DATA_A30

M_DATA_A31

M_DATA_A32

M_DATA_A33

M_DATA_A34

M_DATA_A35

M_DATA_A36

M_DATA_A37

M_DATA_A38

M_DATA_A39

M_DATA_A40

M_DATA_A41

M_DATA_A42

M_DATA_A43

M_DATA_A44

M_DATA_A45

M_DATA_A46

M_DATA_A47

M_DATA_A48

M_DATA_A49

M_DATA_A50

M_DATA_A51

M_DATA_A52

M_DATA_A53

M_DATA_A54

M_DATA_A55

M_DATA_A56

M_DATA_A57

M_DATA_A58

M_DATA_A59

M_DATA_A60

M_DATA_A61

M_DATA_A62

M_DATA_A63

5

4

AD38

AD39

AF38

AF39

AD37

AD40

AF37

AF40

AH40

AH39

AK38

AK39

AH37

AH38

AK37

AK40

AM40

AM39

AP38

AP39

AM37

AM38

AP37

AP40

AV37

AW37

AU35

AV35

AT37

AU37

AT35

AW35

AY6

AU6

AV4

AU4

AW6

AV6

AW4

AY4

AR1

AR4

AN3

AN4

AR2

AR3

AN2

AN1

AL1

AL4

AJ3

AJ4

AL2

AL3

AJ2

AJ1

AG1

AG4

AE3

AE4

AG2

AG3

AE2

AE1

AE39

AJ39

AN39

AV36

AV5

AP3

AK3

AF3

AV32

AE38

AJ38

AN38

AU36

AW5

AP2

AK2

AF2

AU32

4

CPU1A

CPU1A

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_DQS[8]

SA_DQS#[0 ]

SA_DQS#[1 ]

SA_DQS#[2 ]

SA_DQS#[3 ]

SA_DQS#[4 ]

SA_DQS#[5 ]

SA_DQS#[6 ]

SA_DQS#[7 ]

SA_DQS#[8 ]

LGA 1150 SOCKET

LGA 1150 SOCKET

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

SA_ECC_CB[ 0]

SA_ECC_CB[ 1]

SA_ECC_CB[ 2]

SA_ECC_CB[ 3]

SA_ECC_CB[ 4]

SA_ECC_CB[ 5]

SA_ECC_CB[ 6]

SA_ECC_CB[ 7]

RSVD_AW1 2

RSVD_AW2 7

SM_DRAMRST

1 OF 10

1 OF 10

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CKE[0]

SA_CKE[1]

SA_CKE[2]

SA_CKE[3]

SA_CS#[0 ]

SA_CS#[1 ]

SA_CS#[2 ]

SA_CS#[3 ]

SA_CK[0]

SA_CK#[0 ]

SA_CK[1]

SA_CK#[1 ]

SA_CK[2]

SA_CK#[2 ]

SA_CK[3]

SA_CK#[3 ]

SA_RAS

SA_WE

RSVD_AV20

SA_CAS

AU13

AV16

AU16

AW17

AU17

AW18

AV17

AT18

AU18

AT19

AW11

AV19

AU19

AY10

AT20

AU21

AW10

AY8

AW9

AU8

AW33

AV33

AU31

AV31

AT33

AU33

AT31

AW31

AV12

AY11

AT21

AV22

AT23

AU22

AU23

AU14

AV9

AU10

AW8

AY15

AY16

AW15

AV15

AV14

AW14

AW13

AY13

AW12

AU12

AU11

AV20

AW27

AU9

AK22

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

3

M_MAA_A[0..15]

M_ODT_A0 10

M_ODT_A1 10

M_SBS_A0 10

M_SBS_A1 10

M_SBS_A2 10

M_SCKE_A0 10

M_SCKE_A1 10

M_SCS_A_N0 10

M_SCS_A_N1 10

CK_M_DDR0_A_DP 10

CK_M_DDR0_A_DN 10

CK_M_DDR1_A_DP 10

CK_M_DDR1_A_DN 10

M_RAS_A_N 10

M_WE_A_N 10

M_CAS_A_N 10

DDR3_DRAMRST_N 10,11

CC1

CC1

0.1UF 16V X7R 0402

0.1UF 16V X7R 0402

3

M_MAA_A[0..15] 10

2

◇

BIOSTAR' S PROPRIETARY

INFORMATION

◇

duplication, or disclosure of this document

will be subject to the applicable civil

and/orcriminal penalties.

◆

Any unauthorized use, reproduction,

◆

2

1

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU DDR CHANNEL A

CPU DDR CHANNEL A

CPU DDR CHANNEL A

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

6 39Friday, March 28, 2014

6 39Friday, March 28, 2014

6 39Friday, March 28, 2014

1

6.0

6.0

6.0

Page 7

5

www.teknisi-indonesia.com

M_DATA_B[0..63]11

M_DATA_B[0..63]

D D

C C

B B

M_DQS_B_DP011

M_DQS_B_DP111

M_DQS_B_DP211

M_DQS_B_DP311

M_DQS_B_DP411

M_DQS_B_DP511

M_DQS_B_DP611

M_DQS_B_DP711

M_DQS_B_DN011

M_DQS_B_DN111

M_DQS_B_DN211

M_DQS_B_DN311

M_DQS_B_DN411

M_DQS_B_DN511

A A

M_DQS_B_DN611

M_DQS_B_DN711

5

M_DATA_B0

M_DATA_B1

M_DATA_B2

M_DATA_B3

M_DATA_B4

M_DATA_B5

M_DATA_B6

M_DATA_B7

M_DATA_B8

M_DATA_B9

M_DATA_B10

M_DATA_B11

M_DATA_B12

M_DATA_B13

M_DATA_B14

M_DATA_B15

M_DATA_B16

M_DATA_B17

M_DATA_B18

M_DATA_B19

M_DATA_B20

M_DATA_B21

M_DATA_B22

M_DATA_B23

M_DATA_B24

M_DATA_B25

M_DATA_B26

M_DATA_B27

M_DATA_B28

M_DATA_B29

M_DATA_B30

M_DATA_B31

M_DATA_B32

M_DATA_B33

M_DATA_B34

M_DATA_B35

M_DATA_B36

M_DATA_B37

M_DATA_B38

M_DATA_B39

M_DATA_B40

M_DATA_B41

M_DATA_B42

M_DATA_B43

M_DATA_B44

M_DATA_B45

M_DATA_B46

M_DATA_B47

M_DATA_B48

M_DATA_B49

M_DATA_B50

M_DATA_B51

M_DATA_B52

M_DATA_B53

M_DATA_B54

M_DATA_B55

M_DATA_B56

M_DATA_B57

M_DATA_B58

M_DATA_B59

M_DATA_B60

M_DATA_B61

M_DATA_B62

M_DATA_B63

4

4

AE34

AE35

AG35

AH35

AD34

AD35

AG34

AH34

AL34

AL35

AK31

AL31

AK34

AK35

AK32

AL32

AN34

AP34

AN31

AP31

AN35

AP35

AN32

AP32

AM29

AM28

AR29

AR28

AL29

AL28

AP29

AP28

AR12

AP12

AL13

AL12

AR13

AP13

AM13

AM12

AR9

AP9

AR6

AP6

AR10

AP10

AR7

AP7

AM9

AL9

AL6

AL7

AM10

AL10

AM6

AM7

AH6

AH7

AE6

AE7

AJ6

AJ7

AF6

AF7

AF35

AL33

AP33

AN28

AN12

AP8

AL8

AG7

AN25

AF34

AK33

AN33

AN29

AN13

AR8

AM8

AG6

AN26

LGA 1150 SOCKET

LGA 1150 SOCKET

CPU1B

CPU1B

SB_DQ[0 ]

SB_DQ[1 ]

SB_DQ[2 ]

SB_DQ[3 ]

SB_DQ[4 ]

SB_DQ[5 ]

SB_DQ[6 ]

SB_DQ[7 ]

SB_DQ[8 ]

SB_DQ[9 ]

SB_DQ[1 0]

SB_DQ[1 1]

SB_DQ[1 2]

SB_DQ[1 3]

SB_DQ[1 4]

SB_DQ[1 5]

SB_DQ[1 6]

SB_DQ[1 7]

SB_DQ[1 8]

SB_DQ[1 9]

SB_DQ[2 0]

SB_DQ[2 1]

SB_DQ[2 2]

SB_DQ[2 3]

SB_DQ[2 4]

SB_DQ[2 5]

SB_DQ[2 6]

SB_DQ[2 7]

SB_DQ[2 8]

SB_DQ[2 9]

SB_DQ[3 0]

SB_DQ[3 1]

SB_DQ[3 2]

SB_DQ[3 3]

SB_DQ[3 4]

SB_DQ[3 5]

SB_DQ[3 6]

SB_DQ[3 7]

SB_DQ[3 8]

SB_DQ[3 9]

SB_DQ[4 0]

SB_DQ[4 1]

SB_DQ[4 2]

SB_DQ[4 3]

SB_DQ[4 4]

SB_DQ[4 5]

SB_DQ[4 6]

SB_DQ[4 7]

SB_DQ[4 8]

SB_DQ[4 9]

SB_DQ[5 0]

SB_DQ[5 1]

SB_DQ[5 2]

SB_DQ[5 3]

SB_DQ[5 4]

SB_DQ[5 5]

SB_DQ[5 6]

SB_DQ[5 7]

SB_DQ[5 8]

SB_DQ[5 9]

SB_DQ[6 0]

SB_DQ[6 1]

SB_DQ[6 2]

SB_DQ[6 3]

SB_DQS[0 ]

SB_DQS[1 ]

SB_DQS[2 ]

SB_DQS[3 ]

SB_DQS[4 ]

SB_DQS[5 ]

SB_DQS[6 ]

SB_DQS[7 ]

SB_DQS[8 ]

SB_DQS# [0]

SB_DQS# [1]

SB_DQS# [2]

SB_DQS# [3]

SB_DQS# [4]

SB_DQS# [5]

SB_DQS# [6]

SB_DQS# [7]

SB_DQS# [8]

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_ECC_ CB[0]

SB_ECC_ CB[1]

SB_ECC_ CB[2]

SB_ECC_ CB[3]

SB_ECC_ CB[4]

SB_ECC_ CB[5]

SB_ECC_ CB[6]

SB_ECC_ CB[7]

SB_BS[0 ]

SB_BS[1 ]

SB_BS[2 ]

SB_CKE[ 0]

SB_CKE[ 1]

SB_CKE[ 2]

SB_CKE[ 3]

SB_CS# [0]

SB_CS# [1]

SB_CS# [2]

SB_CS# [3]

SB_CK[0 ]

SB_CK# [0]

SB_CK[1 ]

SB_CK# [1]

SB_CK[2 ]

SB_CK# [2]

SB_CK[3 ]

SB_CK# [3]

RSVD_AL20

SA_DIMM_VREFDQ

SB_DIMM_VRE FDQ

2 OF 10

2 OF 10

SB_CAS

SB_RAS

SB_W E

AL19

AK23

AM22

AM23

AP23

AL23

AY24

AV25

AU26

AW25

AP18

AY25

AV26

AR15

AV27

AY28

AM17

AL16

AM16

AK15

AM26

AM25

AP25

AP26

AL26

AL25

AR26

AR25

AK17

AL18

AW28

AW29

AY29

AU28

AU29

AP17

AN15

AN17

AL15

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AP16

AL20

AM18

AK16

AB39

AB40

3

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

M_MAA_B14

M_MAA_B15

CC30

CC30

0.1UF 16V X7R 0402

0.1UF 16V X7R 0402

3

M_MAA_B[0..15]

M_ODT_B0 11

M_ODT_B1 11

M_SBS_B0 11

M_SBS_B1 11

M_SBS_B2 11

M_SCKE_B0 11

M_SCKE_B1 11

M_SCS_B_N0 11

M_SCS_B_N1 11

CK_M_DDR0_B_DP 11

CK_M_DDR0_B_DN 11

CK_M_DDR1_B_DP 11

CK_M_DDR1_B_DN 11

M_CAS_B_N 11

M_RAS_B_N 11

M_WE_B_N 11

CC29

CC29

0.1UF 16V X7R 0402

0.1UF 16V X7R 0402

M_MAA_B[0..15] 11

DIMM_DQ_CPU_VREF_A 10

DIMM_DQ_CPU_VREF_B 11

◇

BIOSTAR' S PROPRIETARY

INFORMATION

◇

duplication, or disclosure of this document

will be subject to the applicable civil

and/orcriminal penalties.

◆

Any unauthorized use, reproduction,

2

Title

Title

Title

◆

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU DDR CHANNEL A

CPU DDR CHANNEL A

CPU DDR CHANNEL A

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

2

1

6.0

6.0

6.0

7 39Friday, March 28, 2014

7 39Friday, March 28, 2014

7 39Friday, March 28, 2014

1

Page 8

5

www.teknisi-indonesia.com

V_CPU_VCCIO

H_VIDSCK have PU at PWM side.

CR4

CR4

110 1% 0402

110 1% 0402

H_VIDSCK38

D D

H_VIDSOUT38

H_VIDALERT_N38

H_DRAMPWRGD14

CR5

CR5

75 1% 0402

75 1% 0402

CR6 44.2 1% 0402CR6 44.2 1% 0402

H_PWRGD14,34

PLTRST_CPU_N13

H_PM_SYNC_013

EC_PECI29

H_PROCHOT_R_N29

H_THERMTRIP_N13

H_SKTOCC_N34

CPU_SM_VREF10

CK_PE_100M_MCP_DN18

CK_PE_100M_MCP_DP18

C C

H_PWRGD

PWR_DEBUG

B B

H_THERMTRIP_N

CR42 For Future processor.

CR50 10K 0402CR50 10K 0402

CC5 0.01UF 25V X7R 0402CC5 0.01UF 25V X7R 0402

NEAR CPU

V_1P05_PCH

CR43 150 1% 0402CR43 150 1% 0402

CR42 1K 0402CR42 1K 0402

CR38 49.9 1% 0402CR38 49.9 1% 0402

4

H_VIDSCK

H_VIDSOUT

H_VIDALERT#

CPU_DRAMPWROK

H_PWRGD

PLTRST_CPU_N

H_PROCHOT_N

H_THERMTRIP_N

CPU_SM_VREF

H_TCK

H_TRST_N

H_PRDY_N

TESTLOW_2

CPU1E

CPU1E

V4

BCLK#

V5

BCLK

C38

VIDSCLK

C37

VIDSOUT

B37

VIDALERT

AK21

SM_DRAMPW ROK

AB35

PWRGOO D

M39

RESET

P36

PM_SYNC

N37

PECI

M36

CATERR

K38

PROCHOT

F37

THERMTRIP

D38

SKTOCC

AB38

SM_VREF

AA37

CFG[0] / EAR

Y38

CFG[1] / PCHLESS_MO DE

AA36

CFG[2] / PEG_LANE_RE VERSAL

W38

CFG[3]

V39

CFG[4] / DP PRESE NSE

U39

CFG[5] / PEXCONFIG1

U40

CFG[6] / PEXCONFIG0

V38

CFG[7] / PEG_DEF ER_TRAINING

T40

CFG[8] / CFG_UNLOCK

Y35

CFG[9] / DISABLESVID

AA34

CFG[10] / SAFE MODE BOOT

V37

CFG[11] / DMI_AC_C OUPLED

Y34

CFG[12] / DPCLK _120_ 135

U38

CFG[13] / PLL SETTING

W34

CFG[14]

V35

CFG[15]

Y36

CFG[17]

Y37

CFG[16]

V36

CFG[19]

W36

CFG[18]

D39

TCK

F38

TDI

F39

TDO

E39

TMS

E37

TRST

L39

PRDY

L37

PREQ

G40

DBR

N5

TESTLOW_ N5

K8

RSVD_K8

J10

RSVD_J10

LGA 1150 SOCKET

LGA 1150 SOCKET

3

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

CPU_VRING_VOL_REF

CPU_CORE0_ VOL_REF

CPU_CORE1_ VOL_REF

CPU_CORE2_ VOL_REF

CPU_CORE3_ VOL_REF

5 OF 10

5 OF 10

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

RSVD_T35

RSVD_M38

TESTLOW_ P6

RSVD_K9

RSVD_H15

RSVD_J9

RSVD_H14

VCC_M8

RSVD_AV2

RSVD_J16

RSVD_H16

PWR_ DEBUG

VSS_N39

VSS_V7

VSS_AB6

RSVD_TP_K13

RSVD_TP_J8

SM_RCOMP[0 ]

SM_RCOMP[1 ]

SM_RCOMP[2 ]

RSVD_AB36

RSVD_TP_AW 2

RSVD_TP_AV1

RSVD_AC8

VCOMP_OUT

RSVD_U8

CPU_VSA_VOL_REF

RSVD_Y8

RSVD_W 8

CPU_VGT_VOL_REF

RSVD_P33

VCC_SENSE

VSS_N33

VSS_J11

VSS_M9

VSS_J7

VSS_SENSE

RSVD_N35

DPLL_R EF_CLK #

DPLL_R EF_CLK

CFG_RCOMP

G39

J39

G38

H37

H38

J38

K39

K37

T35

M38

TESTLOW_1

P6

K9

H15

J9

H14

M8

AV2

J16

H16

PWR_DEBUG

N40

N39

V7

AB6

K13

J8

DDR_RCOMP_0

R1

DDR_RCOMP_1

P1

DDR_RCOMP_2

R2

AB36

AW2

AV1

AC8

P4

U8

AB33

T8

Y8

CPU_CORE0_VOL

M10

L10

M11

L12

W8

R33

P33

E40

N33

J11

M9

J7

F40

N35

W6

W5

HSW_CFG_RCOMP

H40

HSW_CFG_RCOMP:

W/S=12/15 mils,

Length=0.4" Max.

CR9 49.9 1% 0402CR9 49.9 1% 0402

VCCST

V_CPU_CORE

V_VCCIOA_LOAD

CPU_CORE0_VOL

VCC_SENSE 38

VSS_SENSE 38

CK_DPNS_DN 18

CK_DPNS_DP 18

2

VCCST_PWRGD

AY18

AW24

AW23

AV29

AV24

AU39

AU27

AU1

AT40

AK20

T34

R34

J40

J17

J15

H12

Y7

CPU1H

CPU1H

RSVD_AY18

RSVD_AW2 4

RSVD_AW2 3

RSVD_AV29

RSVD_AV24

RSVD_AU39

RSVD_AU27

RSVD_AU1

RSVD_AT40

RSVD_AK20

RSVD_Y7

RSVD_T34

RSVD_R34

RSVD_J40

RSVD_J17

RSVD_J15

RSVD_H12

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

8 OF 10

8 OF 10

LGA 1150 SOCKET

LGA 1150 SOCKET

RSVD_TP_K12

RSVD_TP_J1 3

RSVD_TP_P37

RSVD_TP_N38

RSVD_TP_N36

1

IVR_ERROR

IST_TRIGGER

VSS_U35

VSS_P40

VSS_R38

VSS_T37

VSS_V34

VSS_R39

VSS_T38

VSS_U36

VSS_P39

VSS_T36

VSS_R37

VSS_J14

K12

J13

P37

N38

R36

C39

U35

P40

R38

T37

V34

R39

T38

U36

P39

T36

R37

J14

N36

V_CPU_VCCIO

H_PROCHOT_N

H_PRDY_N

H_TRST_N

H_TCK

CR55 51 0402CR55 51 0402

CR46 51 0402CR46 51 0402

CR59 51 0402CR59 51 0402

A A

5

DDR_RCOMP:

W=12 mils,

own=20mils,other=25mils.

Length=0.5" Max.

DDR_RCOMP_0

DDR_RCOMP_1

DDR_RCOMP_2

HSW_CFG_RCOMP

CR51 100 1% 0402CR51 100 1% 0402CR60 51 0402CR60 51 0402

CR53 75 1% 0402CR53 75 1% 0402

CR54 100 1% 0402CR54 100 1% 0402

CR56 49.9 1% 0402CR56 49.9 1% 0402

4

PWRGD_3V13,14,29,34,35

CR7

CR7

13.7K 1% 0402

13.7K 1% 0402

CR8

CR8

7.5K 1% 0402

7.5K 1% 0402

3

VCCST_PWRGD

CC28

CC28

0.01UF 25V X7R 0402

0.01UF 25V X7R 0402

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU MISC

CPU MISC

CPU MISC

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

8 39Friday, March 28, 2014

8 39Friday, March 28, 2014

8 39Friday, March 28, 2014

1

6.0

6.0

6.0

Page 9

5

www.teknisi-indonesia.com

www.teknisi-indonesia.com

For 2014 CPU only

VCCST

CC6

CC20

CC20

10UF 6.3V X5R

10UF 6.3V X5R

D D

C C

B B

A A

CC6

1UF 6.3V X5R 0402 /NI

1UF 6.3V X5R 0402 /NI

V_CPU_VCCIO2PCH

V_1P05_PCH

CPU1G

CPU1G

AP11

VSS_AP11

AP14

VSS_AP14

AP15

VSS_AP15

AP24

VSS_AP24

AP27

VSS_AP27

AP30

VSS_AP30

AP36

VSS_AP36

AP4

VSS_AP4

AP5

VSS_AP5

AR11

VSS_AR11

AR14

VSS_AR14

AR16

VSS_AR16

AR17

VSS_AR17

AR18

VSS_AR18

AR19

VSS_AR19

AR20

VSS_AR20

AR21

VSS_AR21

AR22

VSS_AR22

AR23

VSS_AR23

AR24

VSS_AR24

AR27

VSS_AR27

AR30

VSS_AR30

AR31

VSS_AR31

AR32

VSS_AR32

AR33

VSS_AR33

AR34

VSS_AR34

AR35

VSS_AR35

AR36

VSS_AR36

AR37

VSS_AR37

AR38

VSS_AR38

AR39

VSS_AR39

AR40

VSS_AR40

AR5

VSS_AR5

AT1

VSS_AT1

AT10

VSS_AT10

AT11

VSS_AT11

AT12

VSS_AT12

AT13

VSS_AT13

AT14

VSS_AT14

AT15

VSS_AT15

AT16

VSS_AT16

AT2

VSS_AT2

AT24

VSS_AT24

AT25

VSS_AT25

AT26

VSS_AT26

AT27

VSS_AT27

AT28

VSS_AT28

AT29

VSS_AT29

AT3

VSS_AT3

AT30

VSS_AT30

AT32

VSS_AT32

AT34

VSS_AT34

AT36

VSS_AT36

AT38

VSS_AT38

AT39

VSS_AT39

AT4

VSS_AT4

AT5

VSS_AT5

AT6

VSS_AT6

AT7

VSS_AT7

AT8

VSS_AT8

AT9

VSS_AT9

AU2

VSS_AU2

AU25

VSS_AU25

AU3

VSS_AU3

AU30

VSS_AU30

AU34

VSS_AU34

AU38

VSS_AU38

AU5

VSS_AU5

AU7

VSS_AU7

AV21

VSS_AV21

AV28

VSS_AV28

AV3

VSS_AV3

AV30

VSS_AV30

AV34

VSS_AV34

AV38

VSS_AV38

AV7

VSS_AV7

AW26

VSS_AW26

AW3

VSS_AW3

AW30

VSS_AW30

CC7

CC7

1UF 6.3V X5R 0402

1UF 6.3V X5R 0402 CC50

V_CPU_CORE

V_CPU_VCCIO

VCCST

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

7 OF 10

7 OF 10

LGA 1150 SOCKET

LGA 1150 SOCKET

CR63 0 0402 /NICR63 0 0402 /NI

VSS_AW32

VSS_AW34

VSS_AW36

VSS_AW7

VSS_AY17

VSS_AY23

VSS_AY26

VSS_AY27

VSS_AY30

VSS_AY5

VSS_AY7

VSS_B24

VSS_B26

VSS_B28

VSS_B30

VSS_B34

VSS_B36

VSS_B4

VSS_B8

VSS_C4

VSS_C6

VSS_C12

VSS_C14

VSS_C16

VSS_C18

VSS_C19

VSS_C21

VSS_C23

VSS_C36

VSS_B10

VSS_B23

VSS_C3

VSS_D9

VSS_D11

VSS_D13

VSS_D15

VSS_D17

VSS_D2

VSS_D23

VSS_D24

VSS_D26

VSS_D28

VSS_D30

VSS_D34

VSS_D36

VSS_D37

VSS_D5

VSS_D6

VSS_D7

VSS_E7

VSS_E8

VSS_E10

VSS_E18

VSS_E3

VSS_E20

VSS_E22

VSS_E23

VSS_E36

VSS_E38

VSS_B32

VSS_E6

VSS_F1

VSS_F32

VSS_F12

VSS_F14

VSS_F16

VSS_F19

VSS_F21

VSS_F22

VSS_F24

VSS_F26

VSS_F28

VSS_F30

VSS_F34

VSS_F36

VSS_F4

VSS_D32

VSS_F7

VSS_G9

VSS_G11

5

AW32

AW34

AW36

AW7

AY17

AY23

AY26

AY27

AY30

AY5

AY7

B24

B26

B28

B30

B34

B36

B4

B8

C4

C6

C12

C14

C16

C18

C19

C21

C23

C36

B10

B23

C3

D9

D11

D13

D15

D17

D2

D23

D24

D26

D28

D30

D34

D36

D37

D5

D6

D7

E7

E8

E10

E18

E3

E20

E22

E23

E36

E38

B32

E6

F1

F32

F12

F14

F16

F19

F21

F22

F24

F26

F28

F30

F34

F36

F4

D32

F7

G9

G11

CR61

CR61

0 0402

0 0402

CR62

CR62

0 0402

0 0402

V_CPU_CORE

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

VCCIO2PCH

AA33

AA35

AA38

AB34

AB37

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

AD33

AD36

AE33

AE36

AE37

AE40

AF33

AF36

AG33

AG36

AG37

AG38

AG39

AG40

AH33

AH36

AJ11

AJ14

AJ16

AJ18

AJ19

AJ22

AJ23

AJ26

AJ27

AJ30

AJ31

AJ32

AJ33

C31

A11

A13

A15

A17

A23

AA3

AA6

AA7

AA8

AB5

AB7

AC3

AC6

AC7

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AE5

AE8

AF1

AF4

AF5

AF8

AG5

AG8

AH1

AH2

AH3

AH4

AH5

AH8

A5

A7

C33

VCC_C31

VCC_P8P8VCCIO2PCH/2014_NI

L40

L16

L15

VCC_L16

VCC_C33

VCCIO_OUT

AB8

CPU1I

CPU1I

VSS_A5

VSS_A7

VSS_A11

VSS_A13

VSS_A15

VSS_A17

VSS_A23

VSS_AA3

VSS_AA6

VSS_AA7

VSS_AA8

VSS_AA33

VSS_AA35

VSS_AA38

VSS_AB5

VSS_AB7

VSS_AB34

VSS_AB37

VSS_AC3

VSS_AC6

VSS_AC7

VSS_AC33

VSS_AC34

VSS_AC35

VSS_AC36

VSS_AC37

VSS_AC38

VSS_AC39

VSS_AC40

VSS_AD1

VSS_AD2

VSS_AD3

VSS_AD4

VSS_AD5

VSS_AD6

VSS_AD7

VSS_AD8

VSS_AD33

VSS_AD36

VSS_AE5

VSS_AE8

VSS_AE33

VSS_AE36

VSS_AE37

VSS_AE40

VSS_AF1

VSS_AF4

VSS_AF5

VSS_AF8

VSS_AF33

VSS_AF36

VSS_AG5

VSS_AG8

VSS_AG33

VSS_AG36

VSS_AG37

VSS_AG38

VSS_AG39

VSS_AG40

VSS_AH1

VSS_AH2

VSS_AH3

VSS_AH4

VSS_AH5

VSS_AH8

VSS_AH33

VSS_AH36

VSS_AJ11

VSS_AJ14

VSS_AJ16

VSS_AJ18

VSS_AJ19

VSS_AJ22

VSS_AJ23

VSS_AJ26

VSS_AJ27

VSS_AJ30

VSS_AJ31

VSS_AJ32

VSS_AJ33

J35

VCC_L15

J21

H35

H33

VCC_J35

VCC_H35

VCC_H33

VCC_L18

VCC_L31

L18

L31

L17

BIOSTAR-D

BIOSTAR-D

HASWELL REV:1.1

HASWELL REV:1.1

LGA 1150 SOCKET

LGA 1150 SOCKET

J22

VCC_J21

VCC_L17

J33

J23

J24

VCC_J23

VCC_J22

VCC_J33

VCC_A24

A24

A25

VSS_AJ34

VSS_AJ35

VSS_AJ36

VSS_AJ37

VSS_AJ40

VSS_AK10

VSS_AK11

VSS_AK12

VSS_AK13

VSS_AK14

VSS_AK18

VSS_AK19

VSS_AK24

VSS_AK25

VSS_AK26

VSS_AK27

VSS_AK28

VSS_AK29

VSS_AK30

VSS_AK36

VSS_AL11

VSS_AL14

VSS_AL17

VSS_AL21

VSS_AL22

VSS_AL24

VSS_AL27

VSS_AL30

VSS_AL36

VSS_AL37

VSS_AL38

VSS_AL39

VSS_AL40

VSS_AM11

VSS_AM14

VSS_AM15

VSS_AM19

VSS_AM24

VSS_AM27

VSS_AM30

VSS_AM31

VSS_AM32

VSS_AM33

VSS_AM34

VSS_AM35

VSS_AM36

VSS_AN10

VSS_AN11

VSS_AN14

VSS_AN16

VSS_AN18

VSS_AN19

VSS_AN22

VSS_AN23

VSS_AN24

VSS_AN27

VSS_AN30

VSS_AN36

VSS_AN37

VSS_AN40

9 OF 10

9 OF 10

J25

J26

VCC_J24

VCC_J25

VCC_J26

VCC_A25

VCC_A26

VCC_A27

A26

A27

VSS_AJ5

VSS_AJ8

VSS_AK1

VSS_AK4

VSS_AK5

VSS_AK6

VSS_AK7

VSS_AK8

VSS_AK9

VSS_AL5

VSS_AM1

VSS_AM2

VSS_AM3

VSS_AM4

VSS_AM5

VSS_AN5

VSS_AN6

VSS_AN7

VSS_AN8

VSS_AN9

VSS_AP1

4

J28

J27

J32

J30

J29

J34

VCC_J28

VCC_J27

VCC_J32

VCC_J30

VCC_J29

VCC_J34

VCC_A29

VCC_A28

VCC_G33

VCC_B25

VCC_A30

VCC_B27

A29

A28

B25

A30

B27

G33

AJ5

AJ8

AJ34

AJ35

AJ36

AJ37

AJ40

AK1

AK4

AK5

AK6

AK7

AK8

AK9

AK10

AK11

AK12

AK13

AK14

AK18

AK19

AK24

AK25

AK26

AK27

AK28

AK29

AK30

AK36

AL5

AL11

AL14

AL17

AL21

AL22

AL24

AL27

AL30

AL36

AL37

AL38

AL39

AL40

AM1

AM2

AM3

AM4

AM5

AM11

AM14

AM15

AM19

AM24

AM27

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AN5

AN6

AN7

AN8

AN9

AN10

AN11

AN14

AN16

AN18

AN19

AN22

AN23

AN24

AN27

AN30

AN36

AN37

AN40

AP1

M13

L19

L20

L21

L22

L25

L24

G3

G6

G7

H1

H4

H7

H8

H9

J3

J6

K1

K4

K7

L3

L6

L7

L8

L9

M1

K33

VCC_M13

VCC_C25

C26

K35

VCC_K33

VCC_K35

VCC_C26

VCC_C27

C27

CPU1J

CPU1J

VSS_G3

VSS_G6

VSS_G7

VSS_G12

VSS_G13

VSS_G14

VSS_G15

VSS_G16

VSS_G17

VSS_G21

VSS_G36

VSS_G37

VSS_H1

VSS_H4

VSS_H7

VSS_H8

VSS_H9

VSS_H10

VSS_H11

VSS_H13

VSS_H17

VSS_H18

VSS_H20

VSS_H21

VSS_H22

VSS_H24

VSS_H26

VSS_H28

VSS_H30

VSS_H32

VSS_H34

VSS_H36

VSS_H39

VSS_J3

VSS_J6

VSS_J18

VSS_J19

VSS_J20

VSS_J36

VSS_J37

VSS_K1

VSS_K4

VSS_K7

VSS_K10

VSS_K14

VSS_K17

VSS_K18

VSS_K20

VSS_K22

VSS_K24

VSS_K26

VSS_K28

VSS_K30

VSS_K34

VSS_K36

VSS_K40

VSS_L3

VSS_L6

VSS_L7

VSS_L8

VSS_L9

VSS_L11

VSS_L13

VSS_L14

VSS_L35

VSS_L38

VSS_M1

VSS_M12

VSS_M14

VSS_M16

VSS_M18

VSS_M20

VSS_M22

VSS_M24

VSS_M26

VSS_M28

VSS_M30

VSS_M32

VSS_M34

VSS_M37

C28

VCC_L19

VCC_L20

VCC_L21

VCC_L22

VCC_C29

VCC_C28

VCC_C30

VCC_C32

C29

C30

C32

HASWELL REV:1.1

HASWELL REV:1.1

L23

VCC_L25

VCC_L24

VCC_L23

VCC_C35

VCC_D25

VCC_C34

C35

D25

C34

BIOSTAR-D

BIOSTAR-D

VSS_NCTF_AU40

VSS_NCTF_AV39

VSS_NCTF_AW38

VSS_NCTF_AY3

VSS_NCTF_B38

VSS_NCTF_B39

VSS_NCTF_C40

VSS_NCTF_D40

10 OF 10

10 OF 10

LGA 1150 SOCKET

LGA 1150 SOCKET

K19

K21

K23

K25

K29

K27

K31

VCC_K19

VCC_K21

VCC_K23

VCC_K25

VCC_K29

VCC_K27

VCC_K31

VCC_B29

VCC_B31

VCC_J31

VCC_B33

VCC_B35

VCC_G31

VCC_C24

J31

B29

B31

B33

B35

C24

C25

G31

G12

G13

G14

G15

G16

G17

G21

G36

G37

H10

H11

H13

H17

H18

H20

H21

H22

H24

H26

H28

H30

H32

H34

H36

H39

J18

J19

J20

J36

J37

K10

K14

K17

K18

K20

K22

K24

K26

K28

K30

K34

K36

K40

L11

L13

L14

L35

L38

M12

M14

M16

M18

M20

M22

M24

M26

M28

M30

M32

M34

M37

L26

D27

VCC_L26

VCC_D27

L27

L28

VCC_L27

VCC_D29

D29

D31

L29

L30

VCC_L29

VCC_L28

VCC_L30

VCC_D33

VCC_D31

VCC_E33

D33

E33

VSS_K15

VSS_K16

VSS_K32

VSS_L36

VSS_M4

VSS_M5

VSS_M6

VSS_M7

VSS_M35

VSS_M40

VSS_N1

VSS_N2

VSS_N3

VSS_N4

VSS_N6

VSS_N7

VSS_N8

VSS_N34

VSS_P2

VSS_P5

VSS_P7

VSS_P34

VSS_P35

VSS_P38

VSS_R3

VSS_R5

VSS_R6

VSS_R7

VSS_R8

VSS_R35

VSS_R40

VSS_T1

VSS_T2

VSS_T4

VSS_T5

VSS_T6

VSS_T7

VSS_T33

VSS_T39

VSS_U2

VSS_U4

VSS_U7

VSS_U33

VSS_U34

VSS_U37

VSS_V3

VSS_V6

VSS_V8

VSS_V33

VSS_V40

VSS_W1

VSS_W4

VSS_W7

VSS_W33

VSS_W35

VSS_W37

VSS_Y4

VSS_Y5

VSS_Y6

VSS_Y33

M17

M19

M15

M21

L32

L33

VCC_L32

VCC_L33

VCC_M17

VCC_M19

VCC_M15

VCC_E31

VCC_D35

VCC_E24

VCC_E26

VCC_E25

E31

D35

E24

E26

E25

E27

K15

K16

K32

L36

M4

M5

M6

M7

M35

M40

N1

N2

N3

N4

N6

N7

N8

N34

P2

P5

P7

P34

P35

P38

R3

R5

R6

R7

R8

R35

R40

T1

T2

T4

T5

T6

T7

T33

T39

U2

U4

U7

U33

U34

U37

V3

V6

V8

V33

V40

W1

W4

W7

W33

W35

W37

Y4

Y5

Y6

Y33

AU40

AV39

AW38

AY3

B38

B39

C40

D40

4

3

M23

M25

M29

M27

M33

AJ12

AJ15

AJ13

AJ20

AJ17

VCC_M23

VCC_M21

VCC_M25

VCC_M29

VCC_M27

VCC_M33

VDDQ_AJ12

VDDQ_AJ15

VDDQ_AJ13

VDDQ_AJ20

VDDQ_AJ17

VCC_E28

VCC_E27

VCC_E29

VCC_E30

VCC_E32

VCC_E34

VCC_F23

VCC_F25

VCC_F29

VCC_F27

VCC_E35

VCC_F31

F23

F25

F29

F27

E28

E29

F31

E30

E32

E34

E35

AT22

AT17

AU15

AU24

AU20

AV10

AJ9

AJ21

AJ25

AJ24

AJ28

AJ29

VDDQ_AJ9

VDDQ_AJ21

VDDQ_AJ25

VDDQ_AJ24

VDDQ_AJ28

VDDQ_AJ29

VDDQ_AT22

VDDQ_AT17

VDDQ_AU15

VDDQ_AU24

VDDQ_AU20

VDDQ_AV10

VCC_F33

VCC_F35

VCC_G22

VCC_G23

VCC_G24

VCC_G25

VCC_G27

VCC_G26

VCC_G28

VCC_G30

VCC_G29

VCC_G32

F33

F35

G22

G23

G24

G25

G27

G26

G28

G30

G29

G32

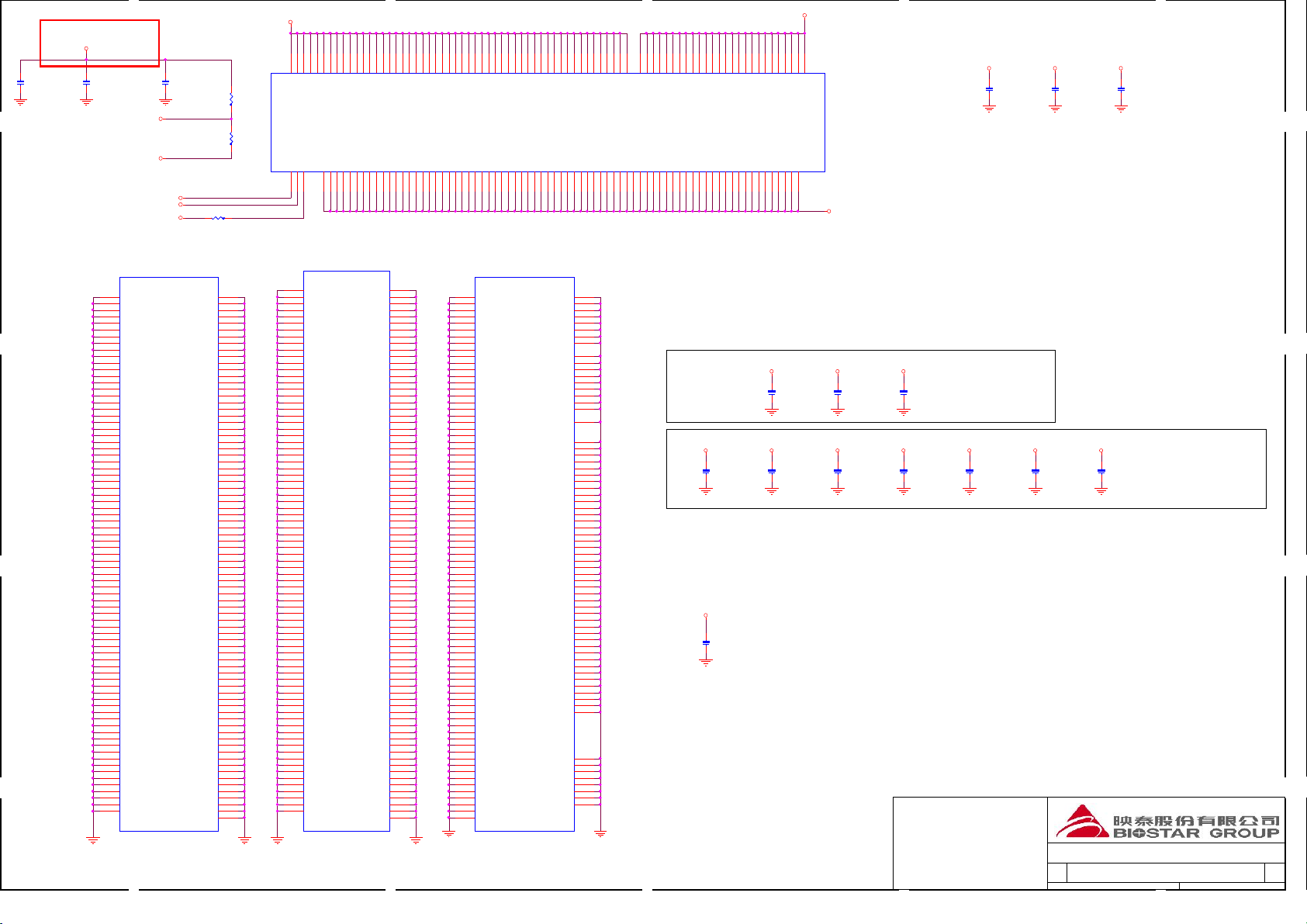

18 x 0805 MLCC CAPs inside TOP SOCKET(95W)

CC14

CC14

10UF 6.3V X5R

10UF 6.3V X5R

V_CPU_VCCIO

CC31

CC31

10UF 6.3V X5R

10UF 6.3V X5R

3

V_SM

2

1

8 x 0805 MLCC CAPs inside TOP

AV11

AV13

AV18

AV23

AY12

AY14

AV8

AY9

AW16

CPU1F

CPU1F

LGA 1150 SOCKET

LGA 1150 SOCKET

6 OF 10

VDDQ_AV8

VDDQ_AV11

VDDQ_AV13

VDDQ_AV18

VDDQ_AV23

VCC_G35

VCC_G34

VCC_H23

VCC_H25

VCC_H27

H23

H25

H27

G35

G34

CC19

CC19

10UF 6.3V X5R

10UF 6.3V X5R

CC15

CC15

10UF 6.3V X5R

10UF 6.3V X5R

6 OF 10

VDDQ_AY9

VDDQ_AY12

VDDQ_AY14

VDDQ_AW16

VCC_H29

VCC_H31

VCC_L34

L34

H29

H31

V_CPU_CORE

V_CPU_CORE V_CPU_COREV_CPU_CORE

CC10

CC10

10UF 6.3V X5R

10UF 6.3V X5R

CC16

CC16

10UF 6.3V X5R

10UF 6.3V X5R

SOCKET

CC11

CC11

10UF 6.3V X5R

10UF 6.3V X5R

CC17

CC17

10UF 6.3V X5R

10UF 6.3V X5R

◇

BIOS TAR'S PROP RIETARY

INFOR MATION

◇

Any u nauthorize d use,

reproduc tion, dupl ication, or

disclo sure of t his document

will be subject to the

applicable civi l and/orcr iminal

penaltie s.

V_SM

CC48

CC48

10UF 6.3V X5R

10UF 6.3V X5R

CC12 /13 REMOVE

V_CPU_CORE V_CPU_COREV_CPU_CORE V_CPU_CORE V_CPU_COREV_CPU_COREV_CPU_CORE

CC18

CC18

10UF 6.3V X5R

10UF 6.3V X5R

◆

◆

2

V_SM

CC45

CC45

10UF 6.3V X5R

10UF 6.3V X5R

CPU

左側入口

CC8

CC8

10UF 6.3V X5R

10UF 6.3V X5R

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet

V_SM

CC50

10UF 6.3V X5R

10UF 6.3V X5R

CC9

CC9

10UF 6.3V X5R

10UF 6.3V X5R

CPU POWER/GND

CPU POWER/GND

CPU POWER/GND

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

1

CPU

內部

CC25 REMOVE

of

9 39Friday, March 28, 2014

9 39Friday, March 28, 2014

9 39Friday, March 28, 2014

6.0

6.0

6.0

Page 10

5

www.teknisi-indonesia.com

4

3

2

1

MEMORY PART: M+Reference

DDR3_A1A

M_DQS_A_DN06

M_DQS_A_DP06

M_DQS_A_DN16

M_DQS_A_DP16

D D

M_DQS_A_DN26

M_DQS_A_DP26

M_DQS_A_DN36

M_DQS_A_DP36

M_DQS_A_DN46

M_DQS_A_DP46

M_DQS_A_DN56

M_DQS_A_DP56

M_DQS_A_DN66

M_DQS_A_DP66

M_DQS_A_DN76

M_DQS_A_DP76

M_DQS_A_DN0

M_DQS_A_DP0

M_DQS_A_DN1

M_DQS_A_DP1

M_DQS_A_DN2

M_DQS_A_DP2

M_DQS_A_DN3

M_DQS_A_DP3

M_DQS_A_DN4

M_DQS_A_DP4

M_DQS_A_DN5

M_DQS_A_DP5

M_DQS_A_DN6

M_DQS_A_DP6

M_DQS_A_DN7

M_DQS_A_DP7

C C

SMB_DATA_MAIN11,34

SMB_CLK_MAIN11,34

B B

M_MAA_A[0..15]6

M_MAA_A[0..15]

M_SBS_A26

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

M_SBS_A2

DDR3_A1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DQS9

126

DQS9-

134

DQS10

135

DQS10-

143

DQS11

144

DQS11-

152

DQS12

153

DQS12-

203

DQS13

204

DQS13-

212

DQS14

213

DQS14-

221

DQS15

222

DQS15-

230

DQS16

231

DQS16-

161

DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10

55

A11

174

A12

196

A13

172

A14

171

A15

52

A16/BA2

DDR3-240 PIN-YL-D

DDR3-240 PIN-YL-D

BLACK

BLACK

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

234

233

228

227

115

114

109

108

225

224

219

218

106

105

100

99

216

215

210

209

97

96

91

90

207

206

201

200

88

87

82

81

156

155

150

149

37

36

31

30

147

146

141

140

28

27

22

21

138

137

132

131

19

18

13

12

129

128

123

122

10

9

4

3

68

53

167

M_DATA_A63

M_DATA_A62

M_DATA_A61

M_DATA_A60

M_DATA_A59

M_DATA_A58

M_DATA_A57

M_DATA_A56

M_DATA_A55

M_DATA_A54

M_DATA_A53

M_DATA_A52

M_DATA_A51

M_DATA_A50

M_DATA_A49

M_DATA_A48

M_DATA_A47

M_DATA_A46

M_DATA_A45

M_DATA_A44

M_DATA_A43

M_DATA_A42

M_DATA_A41

M_DATA_A40

M_DATA_A39

M_DATA_A38

M_DATA_A37

M_DATA_A36

M_DATA_A35

M_DATA_A34

M_DATA_A33

M_DATA_A32

M_DATA_A31

M_DATA_A30

M_DATA_A29

M_DATA_A28

M_DATA_A27

M_DATA_A26

M_DATA_A25

M_DATA_A24

M_DATA_A23

M_DATA_A22

M_DATA_A21

M_DATA_A20

M_DATA_A19

M_DATA_A18

M_DATA_A17

M_DATA_A16

M_DATA_A15

M_DATA_A14

M_DATA_A13

M_DATA_A12

M_DATA_A11

M_DATA_A10

M_DATA_A9

M_DATA_A8

M_DATA_A7

M_DATA_A6

M_DATA_A5

M_DATA_A4

M_DATA_A3

M_DATA_A2

M_DATA_A1

M_DATA_A0

M_DATA_A[0..63]

DDR3_DRAMRST_N6,11

M_SCS_A_N06

M_SCS_A_N16

CK_M_DDR1_A_DN6

CK_M_DDR1_A_DP6

CK_M_DDR0_A_DN6

CK_M_DDR0_A_DP6

M_DATA_A[0..63] 6

M_SCKE_A06

M_SCKE_A16

M_SBS_A06

M_SBS_A16

M_WE_A_N6

M_RAS_A_N6

M_CAS_A_N6

M_ODT_A06

M_ODT_A16

VCC3_3

DIMM_CA_VREF_AB

DIMM_DQ_VREF_A

M_SBS_A0

M_SBS_A1

DDR3_DRAMRST_N

M_WE_A_N

M_RAS_A_N

M_CAS_A_N

V_SM

DDR3_A1B

DDR3_A1B

51

VDDQ1 (P)

54

VDDQ2 (P)

57

VDDQ3 (P)

60

VDDQ4 (P)

62

VDDQ5 (P)

65

VDDQ6 (P)

66

VDDQ7 (P)

69

VDDQ8 (P)

72

VDDQ9 (P)

75

VDDQ10 (P)

78

VDDQ11 (P)

170

VDD1 (P)

173

VDD2 (P)

176

VDD3 (P)

179

VDD4 (P)

182

VDD5 (P)

183

VDD6 (P)

186

VDD7(P)

189

VDD8(P)

191

VDD9(P)

194

VDD10(P)

197

VDD11(P)

236

VDDSPD(P)

67

VREFCA

1

VREFDQ

117

SA0

237

SA1

50

CKE0

169

CKE1

71

BA0

190

BA1

168

RESET

73

WE-

192

RAS-

74

CAS-

193

S-0

76

S-1

195

ODT0

77

ODT1

64

CK-1

63

CK1

185

CK-0

184

CK0

48

FREE1

49

FREE2

187

FREE3

198

FREE4

DDR3-240 PIN-YL-D

DDR3-240 PIN-YL-D

VSS1(P)

VSS2(P)

VSS3(P)

VSS4(P)

VSS5(P)

VSS6(P)

VSS7(P)

VSS8(P)

VSS9(P)

VSS10(P)

VSS11(P)

VSS12(P)

VSS13(P)

VSS60(P)

VSS14(P)

VSS15(P)

VSS16(P)

VSS17(P)

VSS18(P)

VSS19(P)

VSS20(P)

VSS21(P)

VSS22(P)

VSS23(P)

VSS24(P)

VSS25(P)

VSS26(P)

VSS27(P)

VSS28(P)

VSS29(P)

VSS30(P)

VSS31(P)

VSS32(P)

VSS33(P)

VSS34(P)

VSS35(P)

VSS36(P)

VSS37(P)

VSS38(P)

VSS39(P)

VSS40(P)

VSS41(P)

VSS42(P)

VSS43(P)

VSS44(P)

VSS45(P)

VSS46(P)

VSS47(P)

VSS48(P)

VSS49(P)

VSS50(P)

VSS51(P)

VSS52(P)

VSS53(P)

VSS54(P)

VSS55(P)

VSS56(P)

VSS57(P)

VSS58(P)

VSS59(P)

VTT

VTT

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

92

95

98

101

104

107

110

113

116

119

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

199

202

205

208

211

214

217

220

223

226

229

232

235

239

89

120

240

CPU_SM_VREF8

V_SM_VTT

DIMM_DQ_VREF_A

MC8

MC8

0.1UF 16V X7R 0402

0.1UF 16V X7R 0402

DDR3_DRAMRST_N

SMB_DATA_MAIN

SMB_CLK_MAIN

V_SM

MR3

MR3

1K 1% 0402

1K 1% 0402

MR1 2.2 0402MR1 2.2 0402

MR2

MR2

1K 1% 0402

1K 1% 0402

MR36 2.2 0402MR36 2.2 0402

MC20

MC20

22NF 16V X7R 0402

22NF 16V X7R 0402

MR10

MR10

24.9 1% 0402

24.9 1% 0402

MC24

MC24

100P 50V NPO 0402

100P 50V NPO 0402

V_SM

DIMM_DQ_CPU_VREF_A 7

MC10

MC10

22NF 16V X7R 0402

22NF 16V X7R 0402

MR4

MR4

24.9 1% 0402

24.9 1% 0402

MR5

MR5

1K 1% 0402

1K 1% 0402

MR6

MR6

1K 1% 0402

1K 1% 0402

DIMM_CA_VREF_AB 11

MC4

MC4

0.1UF 16V X7R 0402

0.1UF 16V X7R 0402

MC27

MC27

100P 50V NPO 0402

100P 50V NPO 0402

MC36

MC36

100P 50V NPO 0402

100P 50V NPO 0402

V_SM V_SM

MC22 0.1UF 16V Y5V 0402MC22 0.1UF 16V Y5V 0402

A A

MC3 0.1UF 16V Y5V 0402MC3 0.1UF 16V Y5V 0402

MC5 0.1UF 16V Y5V 0402MC5 0.1UF 16V Y5V 0402

MC7 0.1UF 16V Y5V 0402MC7 0.1UF 16V Y5V 0402

5

MC25 0.1UF 16V Y5V 0402MC25 0.1UF 16V Y5V 0402

MC15 0.1UF 16V Y5V 0402MC15 0.1UF 16V Y5V 0402

MC18 0.1UF 16V Y5V 0402MC18 0.1UF 16V Y5V 0402

MC17 0.1UF 16V Y5V 0402MC17 0.1UF 16V Y5V 0402

4

V_SM_VTT

VCC3_3

Near DDR3_A1

MC12 0.1UF 16V Y5V 0402MC12 0.1UF 16V Y5V 0402

MC16 0.1UF 16V Y5V 0402MC16 0.1UF 16V Y5V 0402

◇

BIOSTAR' S PROPRIETARY

INFORMATION

◇

duplication, or disclosure of this document

will be subject to the applicable civil

and/orcriminal penalties.

3

◆

Any unauthorized use, reproduction,

◆

2

Title

Title

Title

DDR3 DIMMA1/A2

DDR3 DIMMA1/A2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

DDR3 DIMMA1/A2

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

10 39Friday, March 28, 2014

10 39Friday, March 28, 2014

10 39Friday, March 28, 2014

1

6.0

6.0

6.0

Page 11

5

www.teknisi-indonesia.com

4

3

2

1

MEMORY PART: M+Reference

VCC3_3

VCC3_3

V_SM

DDR3_B1B

DDR3_B1B

51

VDDQ1 (P)

54

VDDQ2 (P)

57

VDDQ3 (P)

60

VDDQ4 (P)

62

VDDQ5 (P)

65

VDDQ6 (P)

66

VDDQ7 (P)

69

VDDQ8 (P)

72

VDDQ9 (P)

75

VDDQ10 (P)

78

VDDQ11 (P)

170

VDD1 (P)

173

VDD2 (P)

176

VDD3 (P)

179

VDD4 (P)

182

VDD5 (P)

183

VDD6 (P)

186

VDD7(P)

189

VDD8(P)

191

VDD9(P)

194

VDD10(P)

197

VDD11(P)

236

VDDSPD(P)

67

VREFCA

1

VREFDQ

117

SA0

237

SA1

50

CKE0

169

CKE1

71

BA0

190

BA1

168

RESET

73

WE-

192

RAS-

74

CAS-

193

S-0

76

S-1

195

ODT0

77

ODT1

64

CK-1

63

CK1

185

CK-0

184

CK0

48

FREE1

49

FREE2

187

FREE3

198

FREE4

DDR3-240 PIN-YL-D

DDR3-240 PIN-YL-D

VSS1(P)

VSS2(P)

VSS3(P)

VSS4(P)

VSS5(P)

VSS6(P)

VSS7(P)

VSS8(P)

VSS9(P)

VSS10(P)

VSS11(P)

VSS12(P)

VSS13(P)

VSS60(P)

VSS14(P)

VSS15(P)

VSS16(P)

VSS17(P)

VSS18(P)

VSS19(P)

VSS20(P)

VSS21(P)

VSS22(P)

VSS23(P)

VSS24(P)

VSS25(P)

VSS26(P)

VSS27(P)

VSS28(P)

VSS29(P)

VSS30(P)

VSS31(P)

VSS32(P)

VSS33(P)

VSS34(P)

VSS35(P)

VSS36(P)

VSS37(P)

VSS38(P)

VSS39(P)

VSS40(P)

VSS41(P)

VSS42(P)

VSS43(P)

VSS44(P)

VSS45(P)

VSS46(P)

VSS47(P)

VSS48(P)

VSS49(P)

VSS50(P)

VSS51(P)

VSS52(P)

VSS53(P)

VSS54(P)

VSS55(P)

VSS56(P)

VSS57(P)

VSS58(P)

VSS59(P)

VTT

VTT

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

92

95

98

101

104

107

110

113

116

119

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

199

202

205

208

211

214

217

220

223

226

229

232

235

239

89

120

240

V_SM_VTT

DIMM_DQ_VREF_B

MC11

MC11

0.1UF 16V X7R 0402

0.1UF 16V X7R 0402

V_SM

MR7

MR7

1K 1% 0402

1K 1% 0402

MR9 2.2 0402MR9 2.2 0402

MR8

MR8

1K 1% 0402

1K 1% 0402

Near DIMM SLOT

DIMM_DQ_CPU_VREF_B 7

MC23

MC23

22NF 16V X7R 0402

22NF 16V X7R 0402

MR11

MR11

24.9 1% 0402

24.9 1% 0402

DDR3_B1A

M_DQS_B_DN07

M_DQS_B_DP07

M_DQS_B_DN17

M_DQS_B_DP17

M_DQS_B_DN27

D D

M_DQS_B_DP27

M_DQS_B_DN37

M_DQS_B_DP37

M_DQS_B_DN47

M_DQS_B_DP47

M_DQS_B_DN57

M_DQS_B_DP57

M_DQS_B_DN67

M_DQS_B_DP67

M_DQS_B_DN77

M_DQS_B_DP77

M_DQS_B_DN0

M_DQS_B_DP0

M_DQS_B_DN1

M_DQS_B_DP1

M_DQS_B_DN2

M_DQS_B_DP2

M_DQS_B_DN3

M_DQS_B_DP3

M_DQS_B_DN4

M_DQS_B_DP4

M_DQS_B_DN5

M_DQS_B_DP5

M_DQS_B_DN6

M_DQS_B_DP6

M_DQS_B_DN7

M_DQS_B_DP7

C C

SMB_DATA_MAIN10,34

SMB_CLK_MAIN10,34

B B

M_MAA_B[0..15]7

M_MAA_B[0..15]

M_SBS_B27

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

M_MAA_B14

M_MAA_B15

M_SBS_B2

DDR3_B1A

6

DQS0-

7

DQS0

15

DQS1-

16

DQS1

24

DQS2-

25

DQS2

33

DQS3-

34

DQS3

84

DQS4-

85

DQS4

93

DQS5-

94

DQS5

102

DQS6-

103

DQS6

111

DQS7-

112

DQS7

42

DQS8-

43

DQS8

125

DQS9

126

DQS9-

134

DQS10

135

DQS10-

143

DQS11

144

DQS11-

152

DQS12

153

DQS12-

203

DQS13

204

DQS13-

212

DQS14

213

DQS14-

221

DQS15

222

DQS15-

230

DQS16

231

DQS16-

161

DQS17

162

DQS17-

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

79

RSVD

238

SDA

118

SCL

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10

55

A11

174

A12

196

A13

172

A14

171

A15

52

A16/BA2

DDR3-240 PIN-YL-D

DDR3-240 PIN-YL-D

BLACK

BLACK

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC/PAR_IN

NC/ERR_OUT

NC/TEST4

234

233

228

227

115

114

109

108

225

224

219

218

106

105

100

99

216

215

210

209

97

96

91

90

207

206

201

200

88

87

82

81

156

155

150

149

37

36

31

30

147

146

141

140

28

27

22

21

138

137

132

131

19

18

13

12

129

128

123

122

10

9

4

3

68

53

167

M_DATA_B63

M_DATA_B62

M_DATA_B61

M_DATA_B60

M_DATA_B59

M_DATA_B58

M_DATA_B57

M_DATA_B56

M_DATA_B55

M_DATA_B54

M_DATA_B53

M_DATA_B52

M_DATA_B51

M_DATA_B50

M_DATA_B49

M_DATA_B48

M_DATA_B47

M_DATA_B46

M_DATA_B45

M_DATA_B44

M_DATA_B43

M_DATA_B42

M_DATA_B41

M_DATA_B40

M_DATA_B39

M_DATA_B38

M_DATA_B37

M_DATA_B36

M_DATA_B35

M_DATA_B34

M_DATA_B33

M_DATA_B32

M_DATA_B31

M_DATA_B30

M_DATA_B29

M_DATA_B28

M_DATA_B27

M_DATA_B26

M_DATA_B25

M_DATA_B24

M_DATA_B23

M_DATA_B22

M_DATA_B21

M_DATA_B20

M_DATA_B19

M_DATA_B18

M_DATA_B17

M_DATA_B16

M_DATA_B15

M_DATA_B14

M_DATA_B13

M_DATA_B12

M_DATA_B11

M_DATA_B10

M_DATA_B9

M_DATA_B8

M_DATA_B7

M_DATA_B6

M_DATA_B5

M_DATA_B4

M_DATA_B3

M_DATA_B2

M_DATA_B1

M_DATA_B0

M_DATA_B[0..63]

DIMM_CA_VREF_AB10

DDR3_DRAMRST_N6,10

CK_M_DDR1_B_DN7

CK_M_DDR1_B_DP7

CK_M_DDR0_B_DN7

CK_M_DDR0_B_DP7

M_DATA_B[0..63] 7

M_SCKE_B07

M_SCKE_B17

M_SBS_B07

M_SBS_B17

M_WE_B_N7

M_RAS_B_N7

M_CAS_B_N7

M_SCS_B_N07

M_SCS_B_N17

M_ODT_B07

M_ODT_B17

DIMM_CA_VREF_AB

DIMM_DQ_VREF_B

M_SBS_B0

M_SBS_B1

DDR3_DRAMRST_N

M_WE_B_N

M_RAS_B_N

M_CAS_B_N

A A

V_SM_VTT

5

4

Near DDR3_B1

MC21 0.1UF 16V Y5V 0402MC21 0.1UF 16V Y5V 0402

◇

BIOSTAR' S PROPRIETARY

INFORMATION

◇

duplication, or disclosure of this document

will be subject to the applicable civil

and/orcriminal penalties.

3

◆

Any unauthorized use, reproduction,

◆

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

DDR3 DIMMB1/B2

DDR3 DIMMB1/B2

DDR3 DIMMB1/B2

IH81Y-MHS

IH81Y-MHS

IH81Y-MHS

11 39Friday, March 28, 2014

11 39Friday, March 28, 2014

11 39Friday, March 28, 2014

1

6.0

6.0

6.0

Page 12

5

www.teknisi-indonesia.com

4

3

2

1

PCH PART: Y+Reference

D D

PCH1B

PCH1B

BIOSTAR-D

BIOSTAR-D

Lynx Point Rev:1.0

DMI_MT_IR_0_DN5

DMI_MT_IR_0_DP5

DMI_IT_MR_0_DN5

DMI_IT_MR_0_DP5

DMI:85 ohm.

Length=9" max

C C

DMI_RCOMP

W=8 mils,

length=0.32''max

V_1P5_PCH

V_1P5_PCH

PCI-E X1 SLOT

GBE 8111G

DMI_MT_IR_1_DN5

DMI_MT_IR_1_DP5

DMI_IT_MR_1_DN5

DMI_IT_MR_1_DP5

DMI_MT_IR_2_DN5

DMI_MT_IR_2_DP5

DMI_IT_MR_2_DN5

DMI_IT_MR_2_DP5

DMI_MT_IR_3_DN5

DMI_MT_IR_3_DP5

DMI_IT_MR_3_DN5

DMI_IT_MR_3_DP5

YR1 7.5K 1% 0402YR1 7.5K 1% 0402

YR2 7.5K 1% 0402YR2 7.5K 1% 0402

YR87 10K 0402YR87 10K 0402

YR86 10K 0402YR86 10K 0402

HSI1_DN23

HSI1_DP23

HSO1_DN23

HSO1_DP23

GBEA_RXN28

GBEA_RXP28

GBEA_TXN28

GBEA_TXP28

DMI_RCOMP

PCIE_RCOMP

100M_DMI_PCH_DN

100M_DMI_PCH_DP

B B

L24

K24

C20

B20

G24

H24

D21

B21

F26

G26

B22

C22

K26

L26

A24

B24

B19

C13

G22

F22

L14

K14

B12

B11

F14

G14

D11

C11

F11

H11

J11

L11

B9

A9

B8

C8

G9

F9

B7

A7

F7

H7

E1

D2

K6

K8

G3

G5

J2

J3

H2

H1

Lynx Point Rev:1.0

DMI_RXN0

DMI_RXP0

DMI_TXN0

DMI_TXP0

DMI_RXN1

DMI_RXP1

DMI_TXN1

DMI_TXP1

DMI_RXN2

DMI_RXP2

DMI_TXN2

DMI_TXP2

DMI_RXN3

DMI_RXP3

DMI_TXN3

DMI_TXP3

DMI_RCOMP

PCIE_RCOMP

CLKIN_DMI

CLKIN_DMI_ P

PERn1 / USB3 Rn2

PERp1 / USB3 Rp2

PETn1 / USB3Tn2

PETp1 / USB3Tp2

PERn2 / USB3 Rn3

PERp2 / USB3 Rp3

PETn2 / USB3Tn3

PETp2 / USB3Tp3

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PCI-E

PCI-E

PETP4

PERN5

PERP5

PETN5

PETP5

PERN6

PERP6

PETN6

PETP6

PERN7

PERP7

PETN7

PETP7

PERN8

PERP8

PETN8

PETP8

LYNXPOINT-H81