ATMEL T5743P6-TGQ, T5743P6-TG, T5743P3-TG, T5743P3-TGQ Datasheet

Features

• Tw o Different IF Receiving Bandwidth V ersions Are Available (B

• 5 V to 20 V Automotive Compatible Data Interface

• IC Condition Indicator, Sleep or Active Mode

• Low Power Consumption Due to Configurable Self Polling with a Programmable

Timeframe Check

• High Sensitivity, Especially at Low Data Rates

• Data Clock Available for Manchester- and Bi-phase-coded Signals

• Minimal External Circuitry Requirements, no RF Components on the PC Board Except

Matching to the Receiver Antenna

• Sensitivity Reduction Possible Even While Receiving

• Fully Integrated VCO

• SO20 Package

• Supply Voltage 4.5 V to 5.5 V, Operating Temperature Range -40°C to +105°C

• Single-ended RF Input for Easy Adaptation to λ/4 Antenna or Prin ted Antenna on PCB

• Low-cost Solution Due to High Integration Level

• ESD Protection According to MIL-STD. 883 (4KV HBM)

• High Image Frequency Suppression Due to 1 MHz IF in Conjunction with a SAW Front-

end Filter. Up to 40 dB is Thereby Achievable With State-of-the-art SAWs.

• Communication to Microcontroller Possible Via a Single, Bi-directional Data Line

• Power Management (Polling) Is Also Possible by Means of a Separate Pin Via the

Microcontroller

• Programmable Digital Noise Suppression

= 300 kHz or 600 kHz)

IF

UHF ASK/FSK

Receiver

T5743

Preliminary

Description

The T5743 is a multi-chip PLL receiver device supplied in an SO20 package. It has

been especially developed for the demands of RF low-cost data transmission systems

with data rates from 1 kBaud to 10 k Baud in Manchester or Bi -phase code. The

receiver is well suit ed to op erate with A tmel's P LL RF transmitter U2741B. Its main

applications are in the areas of telemeteri ng, security tec hnology and keyless-entry

systems. It can be used in the frequency receiving range of f

= 300 MH z to 450 MHz

0

for ASK or F SK da ta tr ansm issi on. All t he s tate men ts m ade bel o w refer to 43 3.9 2 MHz

and 315 MHz applications.

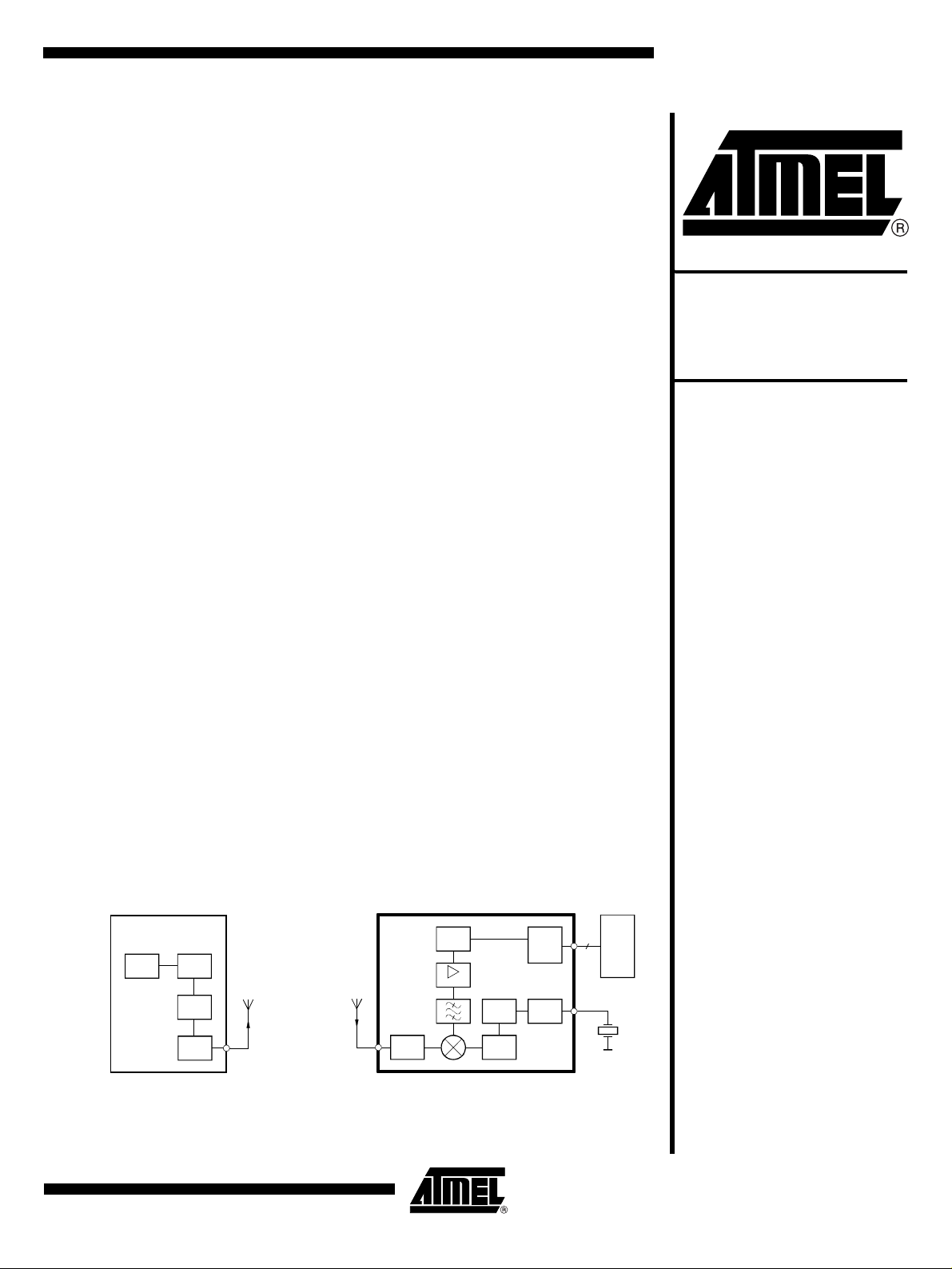

System Block Diagram

Figure 1. System Block Diagram

UHF ASK/FSK

Remote control transmitter

U2741B

XTO

PLL

VCO

Power

amp.

Antenna

T5743

Antenna

LNA VCO

UHF ASK/FSK

Remote control receiver

Demod.

IF Amp

PLL XTO

Control

1...5

µC

Rev. 4569A–RKE–12/02

1

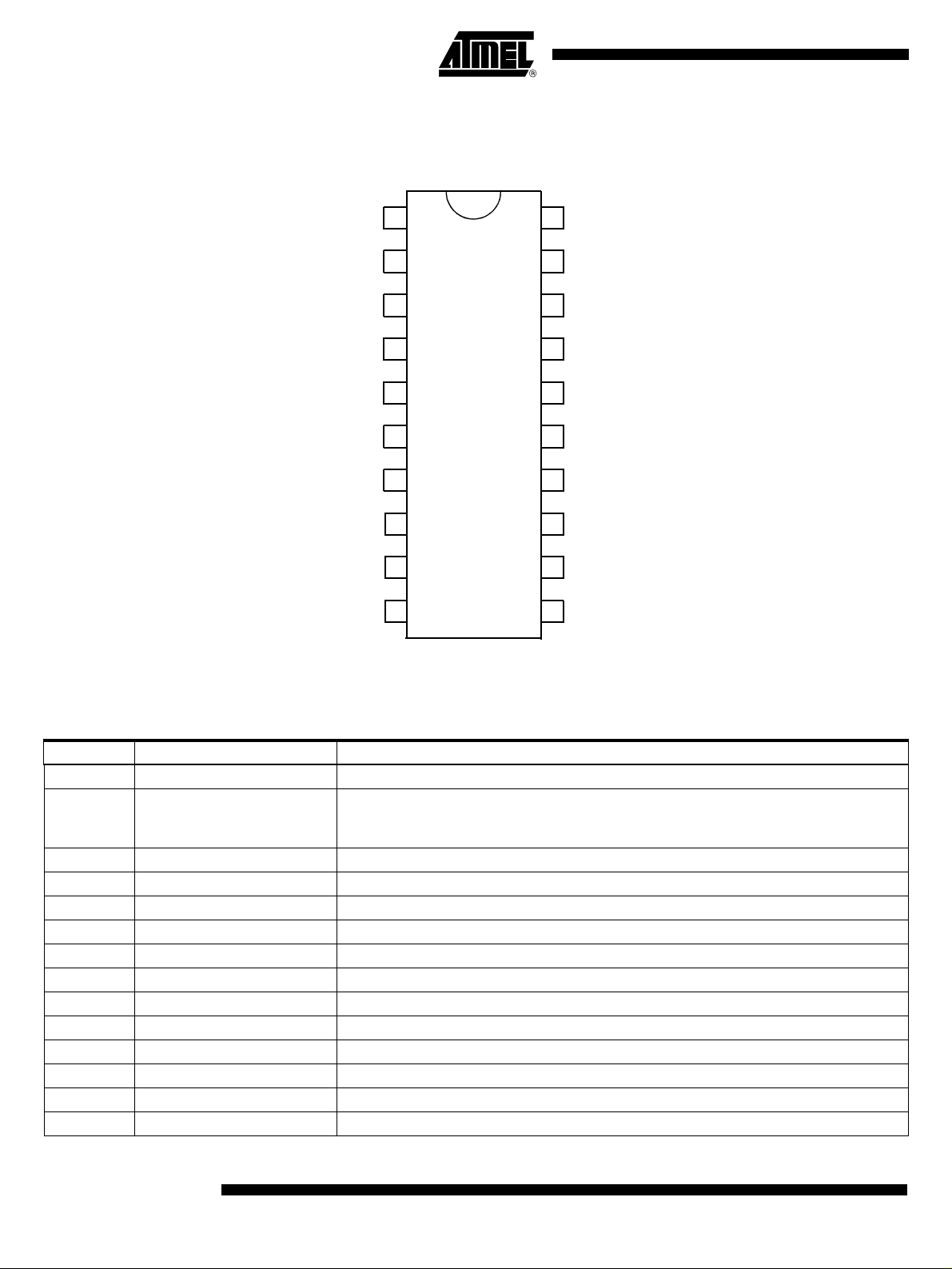

Pin Configuration

Figure 2. Pinning SO20

SENS

IC_ACTIVE

CDEM

AVCC

TEST

AGND

MIXVCC

LNAGND

LNA_IN

n.c.

1

2

3

4

5

20

DATA

19

POLLING/_ON

18

DGND

17

DATA_CLK

16

MODE

T5743

6

7

8

9

10

15

14

13

12

11

DVCC

XTO

LFGND

LF

LFVCC

Pin Description

Pin Symbol Function

1 SENS Sensitivity-control resistor

2 IC_ACTIVE IC condition indicator

Low = sleep mode

High = active mode

3 CDEM Lower cut-off frequency data filter

4 AVCC Analog power supply

5 TEST Test pin, during operation at GND

6 AGND Analog ground

7 MIXVCC Power supply mixer

8 LNAGND High-frequency ground LNA and mixer

9 LNA_IN RF input

10 n.c. Not connected

11 LFVCC Power supply VCO

12 LF Loop filter

13 LFGND Ground VCO

14 XTO Crystal oscillator

2

T5743

4569A–RKE–12/02

Pin Description (Continued)

Pin Symbol Function

15 DVCC Digital power supply

16 MODE Selecting 433.92 MHz/315 MHz

Low: f

High: f

17 DATA_CLK Bit clock of data stream

18 DGND Digital ground

19 POLLING/_ON Selects polling or receiving mode

Low: receiving mode

High: polling mode

20 DATA Data output/configuration input

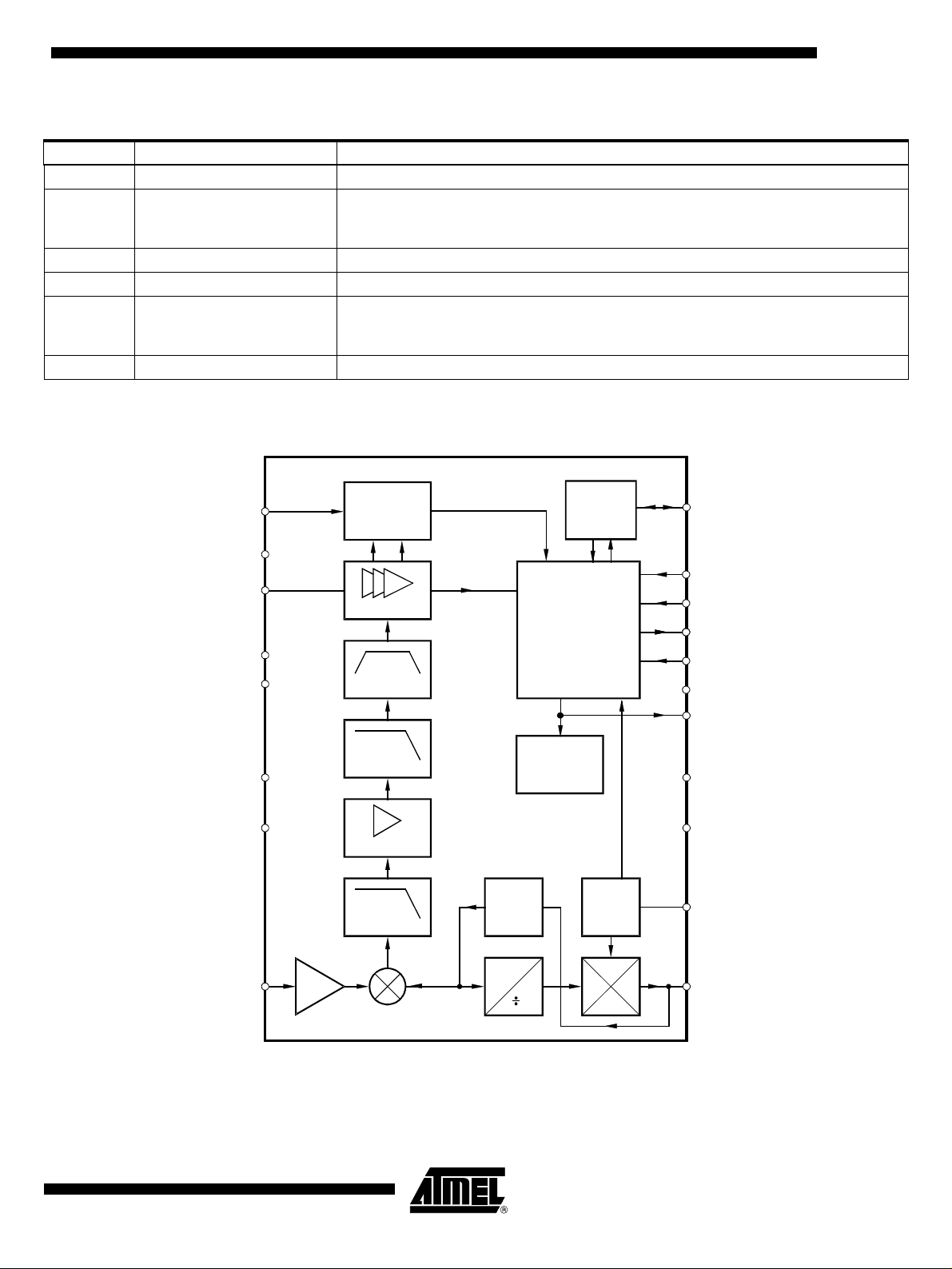

Figure 3. Block Diagram

= 4.90625 MHz (USA)

XT0

= 6.76438 MHz (Europe)

XT0

T5743

CDEM

AVCC

SENS

AGND

DGND

MIXVCC

LNAGND

FSK/ASK-

Demodulator

and data filter

Limiter outRSSI

IF Amp

4. Order

LPF

3 MHz

IF Amp

LPF

3 MHz

Dem_out

Sensitivity

reduction

Data

interface

Polling circuit

and

control logic

FE CLK

Standby logic

VCO XTO

DATA

POLLING/_ON

TEST

DATA_CLK

MODE

DVCC

IC_ACTIVE

LFGND

LFVCC

XTO

4569A–RKE–12/02

LNA_IN

LNA

f

LF

64

3

RF Front-end The RF front-end of the receiv er is a heter odyne conf iguration that c onverts the inp ut

signal into a 1 MHz IF signal. According to F igure 3, the fr ont-end consists of an LNA

(low-noise amplifier), LO (local oscillator), a mixer and an RF amplifier.

The LO generates the carrier frequency for the mixer via a PLL synthesizer. The XTO

(crystal oscillator) generate s the refe rence fr equency f

oscillator) generates the drive voltage frequency f

the voltage at Pin LF. f

f

by the phase frequency detector. The current out put of the phas e frequency detec-

XTO

is divided by fac tor 6 4. T he divid ed f req uency is c ompa red to

LO

LO

tor is connected to a passive loop filter and thereby generates the control voltage V

the VCO. By mean s of th at co n fi g ur at i on V

f

. If f

XTO

is determined, f

LO

can be calculated using the following formula: f

XTO

is controlled in a way th at fLO/64 is equal to

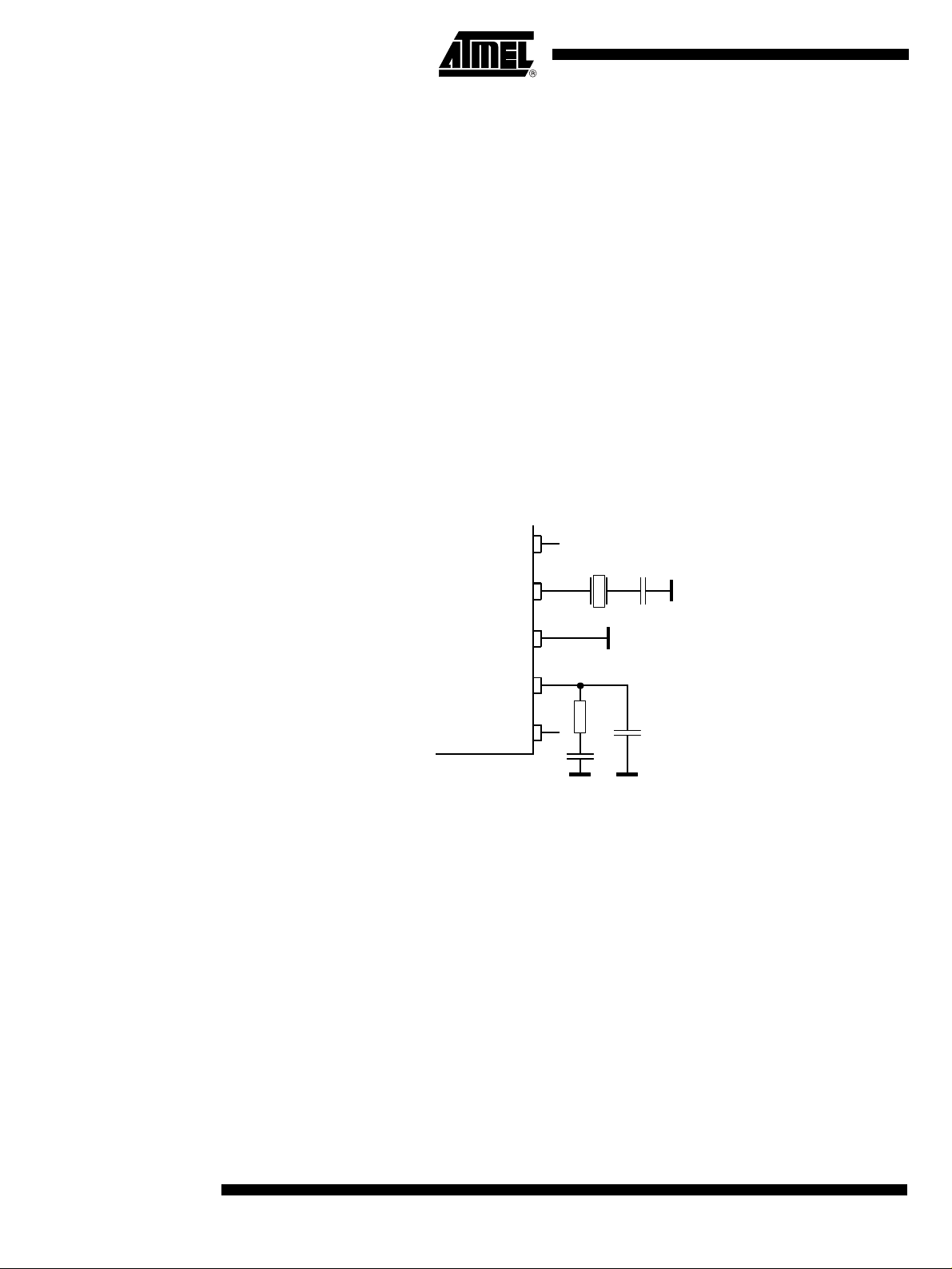

LF

The XTO is a one-pin oscillator that operates at the series resonance of the quartz crystal. According to Figure 4, the crystal should be connected to GND via a capacitor CL.

The value of that capacitor is recommended by the crystal supplier. The value of CL

should be optimized for the individual board layout to achieve the exact value of f

hereby of f

. When designing the system in terms of receiving bandwidth, the accuracy

LO

of the crystal and the XTO must be considered.

Figure 4. PLL Peripherals

V

S

DVCC

C

XTO

. The VCO (voltage-contr olled

XTO

for the mixe r. fLO is dependent on

LF

= fLO/64.

XTO

and

XTO

L

for

LFGND

R1 = 820 W

C9 = 4.7 nF

LF

LFVCC

R1

V

S

C9

C10 = 1 nF

C10

The passive loop filter connected to Pin LF is designed for a loop bandwidth of

BLoop = 100 kHz. This va lue for BL oop exhibi ts the best possib le noise perfor manc e of

the LO. Figure 4 shows the appropriate lo op filter compo nents to achiev e the desired

loop bandwidth. If the filter components are changed for any reason please notify that

the maximum capacitive load at Pin LF is limited. If the capacitive load is exceeded, a bit

check may no longer be possible since f

cannot settle in time before the bit check

LO

starts to evaluate the inc omi ng data s tream. Self polling do es th erefor e al so not work i n

that case.

f

is determined by the RF input frequency fRF and the IF frequency fIF using the fol lo w -

LO

ing formula: f

= fRF - f

LO

IF

To determine fLO, the construction of the IF filter must be considered at this point. The

nominal IF frequency is f

quencies, the filter is tuned by the crystal frequency f

fixed relation between f

= 1 MHz. To achieve a good accuracy of the filter’s corner fre-

IF

and fLO. This relation is dependent on the logic level at Pin

IF

. This means that there is a

XTO

MODE.

4

T5743

4569A–RKE–12/02

T5743

This is described by the following formulas:

f

LO

MODE 0 (USA) : f

MODE 1 (Europe) : f

The relation is designed to achieve the nominal IF frequency of f

applications. For applications where f

case of f

= 433.92 MHz, MODE must be set to ‘1’. For other RF frequencies, fIF is

RF

not equal to 1 MHz. f

----------==

IF

314

f

LO

------------------==

IF

432.92

= 1 MHz for most

= 315 MHz, MODE must be set to ‘0’. In the

RF

is then dependent on the logical level at Pin MODE and on fRF.

IF

IF

Table 1 summarizes the different conditions.

The RF input either from an antenna or from a generator must be transformed to the RF

input Pin LNA_ IN. T he in put i mpedan ce o f that pin is p rovide d in the e lectri cal parameters. The parasitic board inductances and capacitances also influence the input

matching. The RF receiv er T5743 exhib its its highest sens itivity at the best signal-tonoise ratio in the LNA. Hence, noise matching is the best choice for designing the transformation network.

A good practice when designin g the netwo rk is to star t with power m atching. Fr om that

starting point, the values of the components can be varied to some extent to achieve the

best sensitivity.

If a SAW is implemented into the input network a mirror frequency suppression of

DP

= 40 dB can be achiev ed. There are SAWs availab le that exh ibit a notch a t

Ref

Df = 2 MHz. These SAWs work best for an intermediate frequency of f

= 1 MHz. T he

IF

selectivity of the receiver is also imp roved by us ing a SAW. In ty pical auto motive ap plications, a SAW is used.

Figure 5 shows a typical input matching network, for f

= 315 MHz and fRF=

RF

433.92 M Hz using a SAW. Figur e 6 illustrate s an accor ding input matching to 50 W

without a SAW. The input matching networks shown in Figure 6 are the reference networks for the parameters given in the electrical characteristics.

Table 1. Calculation of LO and IF Frequency

Conditions Local Oscillator Frequency Intermediate Frequency

fRF = 315 MHz, MO DE = 0 fLO = 314 MHz fIF = 1 MHz

= 433.92 MHz, MODE = 1 fLO = 432.92 MHz fIF = 1 MHz

f

RF

300 MHz < f

MODE = 0

365 MHz < f

MODE = 1

< 365 MHz,

RF

< 450 MHz,

RF

f

f

LO

f

LO

RF

-------------------= f

1

1

----------+

314

f

RF

----------------------------= f

1

------------------+

1

432.92

f

LO

----------=

IF

314

f

LO

------------------=

IF

432.92

4569A–RKE–12/02

5

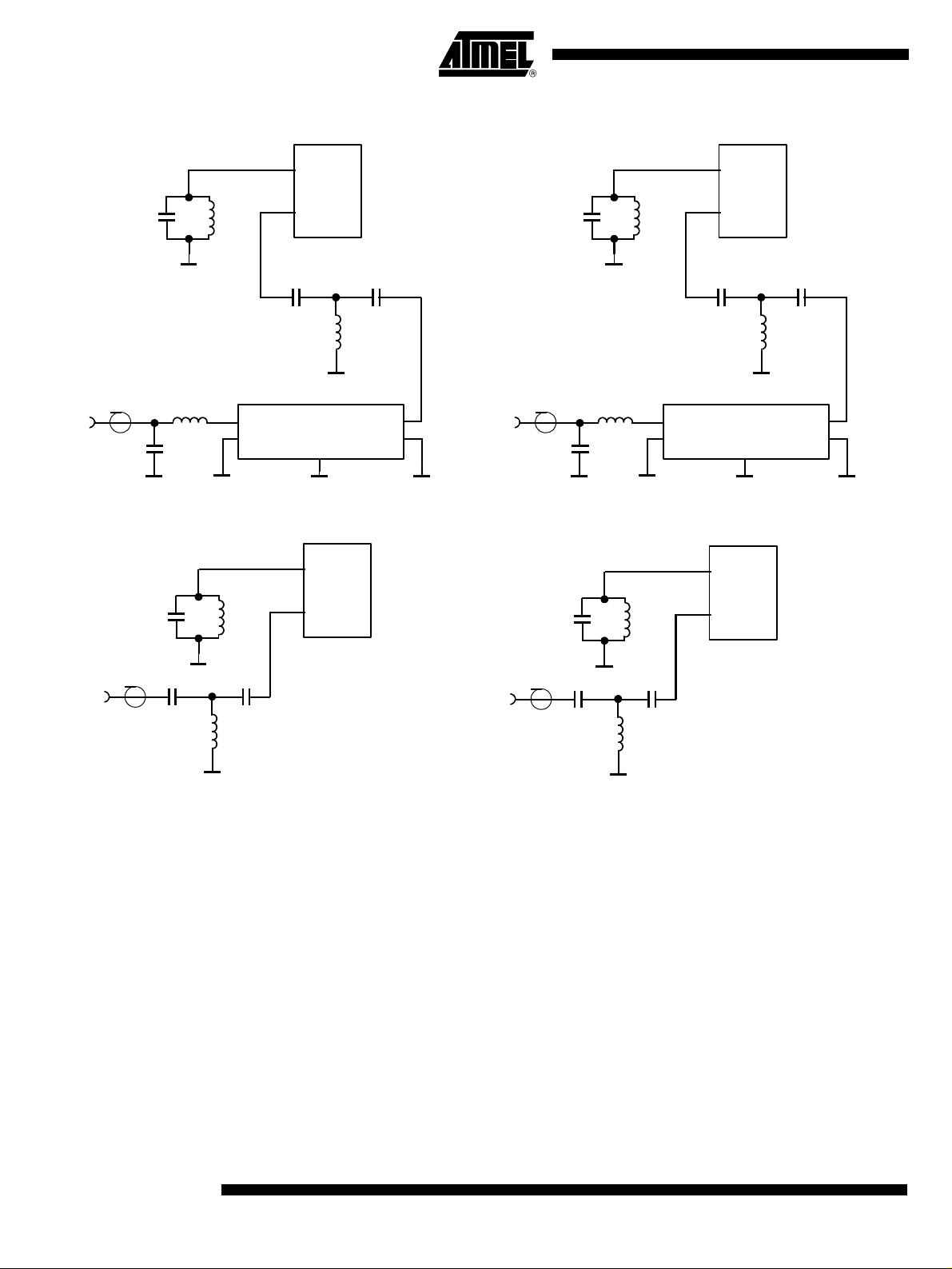

Figure 5. Input Matching Network with SAW Filter

8

LNAGND

T5743

IN

IN_GND

9

LNA_IN

C16

100p

27n

B3555

CASE_GND

3,4 7,8

L3

C17

8.2p

TOKO LL2012

F27NJ

OUT

OUT_GND

5

6

C3

22p

fRF = 433.92 MHz

RF

IN

TOKO LL2012

C2

8.2p

L2

F33NJ

33n

L

25n

1

2

Figure 6. Input Matching Network without SAW Filter

fRF = 433.92 MHz

15p

25n

8

9

LNAGND

T5743

LNA_IN

C3

47p

fRF = 315 MHz

RF

IN

TOKO LL2012

C2

10p

fRF = 315 MHz

33p

L2

F82NJ

82n

25n

L

25n

1

2

IN

IN_GND

8

LNAGND

9

LNA_IN

C16

100p

CASE_GND

8

LNAGND

9

LNA_IN

T5743

L3

47n

B3551

3,4 7,8

T5743

C17

22p

TOKO LL2012

F47NJ

OUT

OUT_GND

5

6

RFIN

3.3p

22n

100p

TOKO LL2012

F22NJ

RF

IN

3.3p

39n

100p

TOKO LL2012

F39NJ

Please notify that fo r all coup ling c onditions (see Fi gure 5 and F igure 6), th e bond w ire

inductivity of the LNA ground is compensated. C3 forms a series resonance circuit

together with the bond wire. L = 25 nH is a feed inductor to establish a DC path. Its

value is not critical but mu st be lar ge en oug h not to detun e the s er ies r esonan ce circuit.

For cost reduction this inductor can be easily printed on the PCB. This configuration

improves the sensitivity of the receiver by about 1 dB to 2 dB.

6

T5743

4569A–RKE–12/02

Analog Signal Processing

T5743

IF Amplifier

The signals coming from the RF front-end are filtered by the fully integrated 4th-order IF

filter. The IF center frequency is f

f

= 433 .92 MHz is used. For other RF inpu t frequenc ies refer to Table 1 to d etermine

RF

= 1 MHz for applications where fRF= 315 MHz or

IF

the center frequency.

The T5743 is available with two different IF bandwidths. T5743P3, the vers ion with

B

= 30 0 kHz, is well su ited for ASK sy stem s where Atme l’s PLL tr ansm itter U2 741B is

IF

used. The receiver T5743P6 employs an IF bandwidth of B

= 600 kHz. Both versions

IF

can be used together with the U2741B in ASK and FSK mode. If used in ASK applications, it allows higher tolerances for the receiv er and PLL transmitter crystals. SAW

transmitters ex hibit muc h higher tran smit freq euncy toleranc es compare d to PLL tr ansmitters. Generally, it is necessary to use B

= 600 kHz together with such transmitters.

IF

RSSI Amplifier The subsequent RSSI amplifier enhances the output signal of the IF amplifier before it is

fed into the demodulator. The dynamic range of this amplifier is DR

RSSI amplifier is operated within its linear range, the best S/N ratio is maintained in ASK

mode. If the dynamic range is exceeded by the transmitter signal, the S/N ratio is

defined by the ratio of the maximum RSSI output voltage and the RSSI output voltage

due to a disturber. The dynamic ran ge of the RSSI am plifier is exceede d if the RF input

signal is about 60 dB higher compared to the RF input signal at full sensitivity.

In FSK mode the S/N ratio is not affected by the dynamic range of the RSSI amplifier.

The output voltage of the RSSI amplifier is internally compared to a threshold voltage

V

. V

Th_red

nected between Pin S ENS a nd G ND or V

is determined by the value of th e external res istor R

Th_red

. The output of the c om par at or is f ed into the

S

digital control logic. By this means it is possible to operate the receiver at a lower

sensitivity.

= 60 dB. If the

RSSI

. R

Sens

Sens

is con-

If R

If R

sitivity is defined by the value of R

is connected to GND, the receiver operates at full sensitivity.

Sens

is connected to VS, the receiver operates at a lower sensitivity. The reduced sen-

Sens

, the maximum sensitivity by the signal-to-noise

Sens

ratio of the LNA input. The reduced sensitivity depends on the signal strength at the output of the RSSI amplifier.

Since different RF in put netw orks may ex hibit sli ghtly di fferent val ues for the LN A gain,

the sensitivit y values giv en in the elect rical chara cteristics r efer to a specif ic input

matching. This matching is illustrated in Figure 6 and exhibits the best possible

sensitivity.

R

can be connected to VS or GND via a mic rocontrolle r. The receiver can be

Sens

switched from full sensitivity to reduced sensitivity or vice versa at any time. In polling

mode, the receiver will not wake up if the R F input signal doe s not exceed the se lected

sensitivity. If the receiver is already active, the data stream at Pin DATA will disappear

when the input signal is lower than defined by the reduced sensitivity. Instead of the

data stream, the pattern according to Figure 7 is issued at Pin DATA to indicate that the

receiver is still active (see also figure 34).

Figure 7. Steady L State Limited DATA Output Pattern

DATA

t

DATA_min

t

DATA_L_max

4569A–RKE–12/02

7

FSK/ASK Demodulator

and Data Filter

The signal coming from the RSSI amplifier is converted into the raw data signal by the

ASK/FSK demodulator. The operating mode of the demodulator is set via the bit

ASK/_FSK in the OPMODE register. Logic ‘L’ sets the demodulator to FSK, applying ‘H’

to ASK mode.

In ASK mode, an automatic threshold control circuit (ATC) is used to set the detection

reference volt age t o a v alue wh ere a go od s ignal- to-no ise r atio is a chiev ed. T his c ircui t

effectively suppre ss es any ki nd o f inband noise signals o r comp eti ng tr an sm itte r s. If the

S/N (ratio to suppress inban d noise signals) exceeds 10 dB, the data signal c an be

detected properly.

The FSK demodulator is intended to be used for an FSK dev iation of 10 kHz £ Df £

100 kHz. In FSK mode the data signal can be detected i f the S/N (ratio to suppress

inband noise signals) exceeds 2 dB. This value is guaranteed for all modulation

schemes of a disturber signal.

The output signal of the demo dulator is filtered by the data filter befo re it is fed in to the

digital signal processing circuit. The data filter improves the S/N r atio as its passband

can be adopted to the characteristics of the data signal. The data filter consists of a

st

1

-order highpass and a 2nd-order lowpass filter.

The highpass filter cut-off frequency is defined by an external capacitor connected to Pin

CDEM. The cut-off frequency of the highpass filter is defined by the following formula:

fcu_DF

In self-polling mode , the data fil ter mu st settle very rapidly to ac hie ve a lo w cu r rent c onsumption. Therefore, CDEM cannot be increased to very high values if self-polling is

used. On the other hand, CDEM must be large enough to meet the data filter requirements according to the d ata signal. Reco mmended val ues for CDEM ar e given in th e

electrical character isti cs .

-----------------------------------------------------------=

2 p 30 kW´ CDEM´´

1

Receiving

Characteristics

The cut-off frequenc y of the lowpass fi lter is define d by the selecte d baud-rate ra nge

(BR_Range). The BR_Range is defined i n the OPMODE registe r (refer to se ction ‘ Configuration of the Receiver’). The BR_Range must be set in accordance to the used baud

rate.

The T5743 is designed to operate with data coding where the DC level of the data signal

is 50%. This is valid for Manchest er and Bi -phase c oding. If ot her modula tion sc hemes

are used, the DC level should always remain withi n the range of V

V

Each BR_Range is also defined by a minimum and a maximum edge-to-edge time

(t

exceeded to maintain full sensitivity of the receiver.

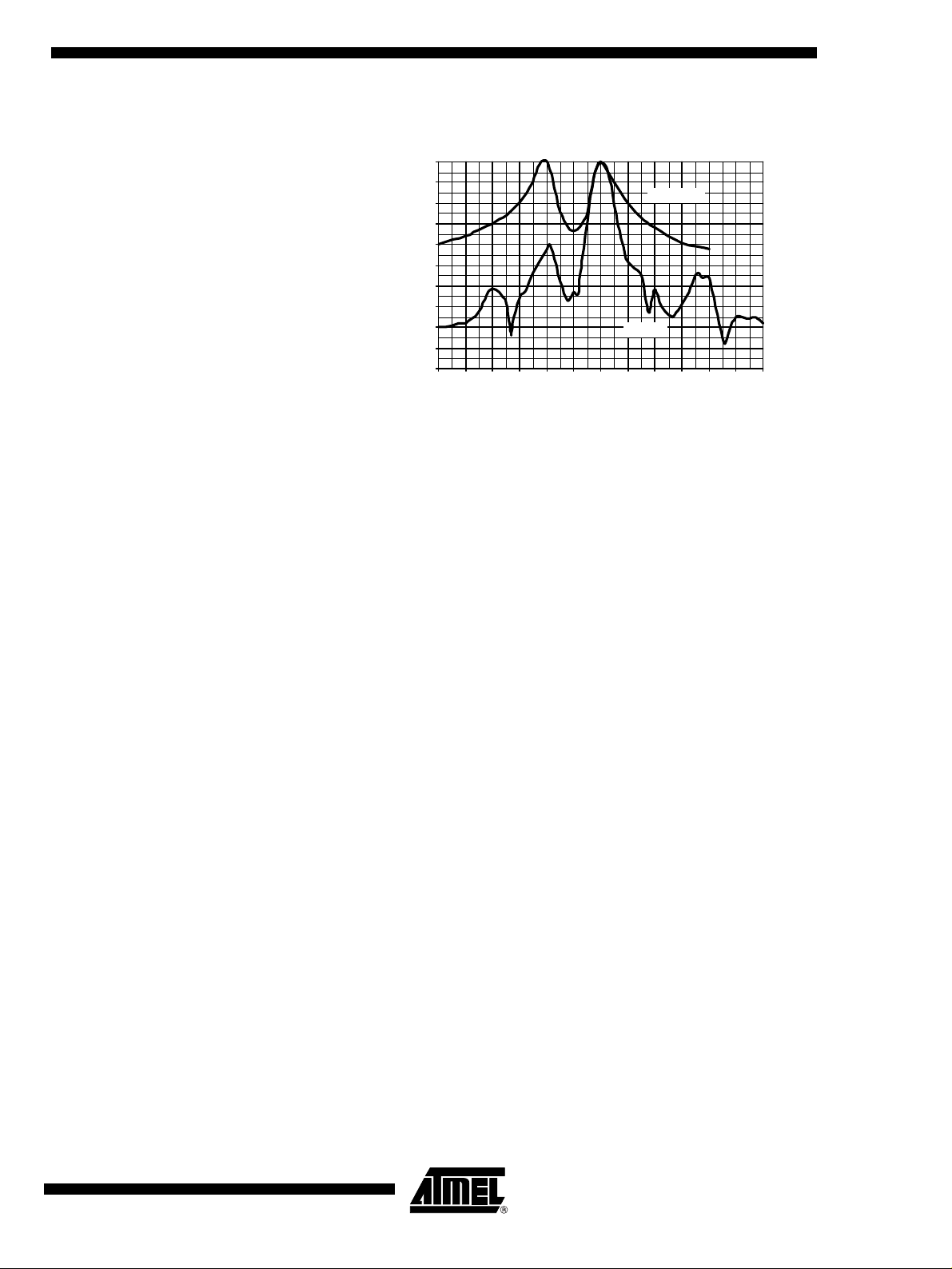

The RF receiver T5743 can be operat ed with and without a SAW front-end filter. In a

typical automotive application, a SAW filter is used to achieve better selectivity. The

selectivity with and without a SAW front-end filter is illustrated in Figure 8. This example

relates to ASK mode an d the 300-kHz bandwid th versi on of the T5743 . FSK mod e and

the 600-kHz bandwidth version of the rec eiver exhibits simi lar behavior. Note that the

mirror frequency is reduced by 40 dB. The plots are printed relatively to the maximum

sensitivity. If a SAW filter is used, an insertion loss of about 4 dB must be considered.

= 66%. The sensitivity may be reduced by up to 2 dB in that condition.

DC_max

). These limits are defined in the electrical characteristics. They should not be

ee_sig

DC_min

= 33% and

8

T5743

4569A–RKE–12/02

T5743

Figure 8. Receiving Frequency Response

0.0

-10.0

-20.0

-30.0

-40.0

-50.0

-60.0

dP (dB)

-70.0

-80.0

-90.0

-100.0

-6.0 -5.0 -4.0 -3.0 -2.0 -1.0 0.0 1.0 2.0 3.0 4.0 5.0 6.0

df (MHz)

When designing the system in terms of receiving bandwidth, the LO deviation must be

considered as it also determines the IF center frequency. The total LO deviation is calculated to be the sum of the deviation of the crystal and the XTO deviation of the T5743.

Low-cost crystals are sp ecifi ed to be withi n ±100 ppm. The XT O deviat ion of the T 5743

is an additional d eviation due t o the XTO c ircuit. This de viation is spe cified to be

±30 ppm. If a crystal of ±100 ppm is use d, the to tal deviatio n is ±130 ppm in tha t case.

Note that the receiving bandwidth a nd the IF-filter bandwidth are e quivalent in ASK

mode but not in FSK mode.

without SAW

with SAW

Polling Circuit and

Control Logic

Basic Clock Cycle of the

Digital Circuitry

The receiver is designed to consume less than 1 mA while being sensitive to signals

from a corresponding transmitter. This is achieved via the polling circuit. This circuit

enables the signal path per iodicall y for a short time. Dur ing this time the bit-check logic

verifies the presence of a valid transmitter signal. Only if a valid signal is detected the

receiver remains ac tive and trans fers the d ata to the connec ted mi crocon troller . If there

is no valid signal pres ent the receive r is in sleep mode most of the tim e resulting in low

current consumpt ion . T hi s c ond iti on is c al led polling mode. A c on nec ted mi cr o con troll er

is disabled during that time.

All relevant parameters of the polling logic can be configured by the connected microcontroller. This flexibility enables the user to meet the specifications in terms of current

consumption, system response time, data rate etc.

Regarding the number of con nection wires to the microcontroll er, the receiver is ve ry

flexible. It can be ei ther op erated by a singl e bi-dir ectiona l line to save p orts to the connected microcontroller or it can be operated by up to five uni-directional ports.

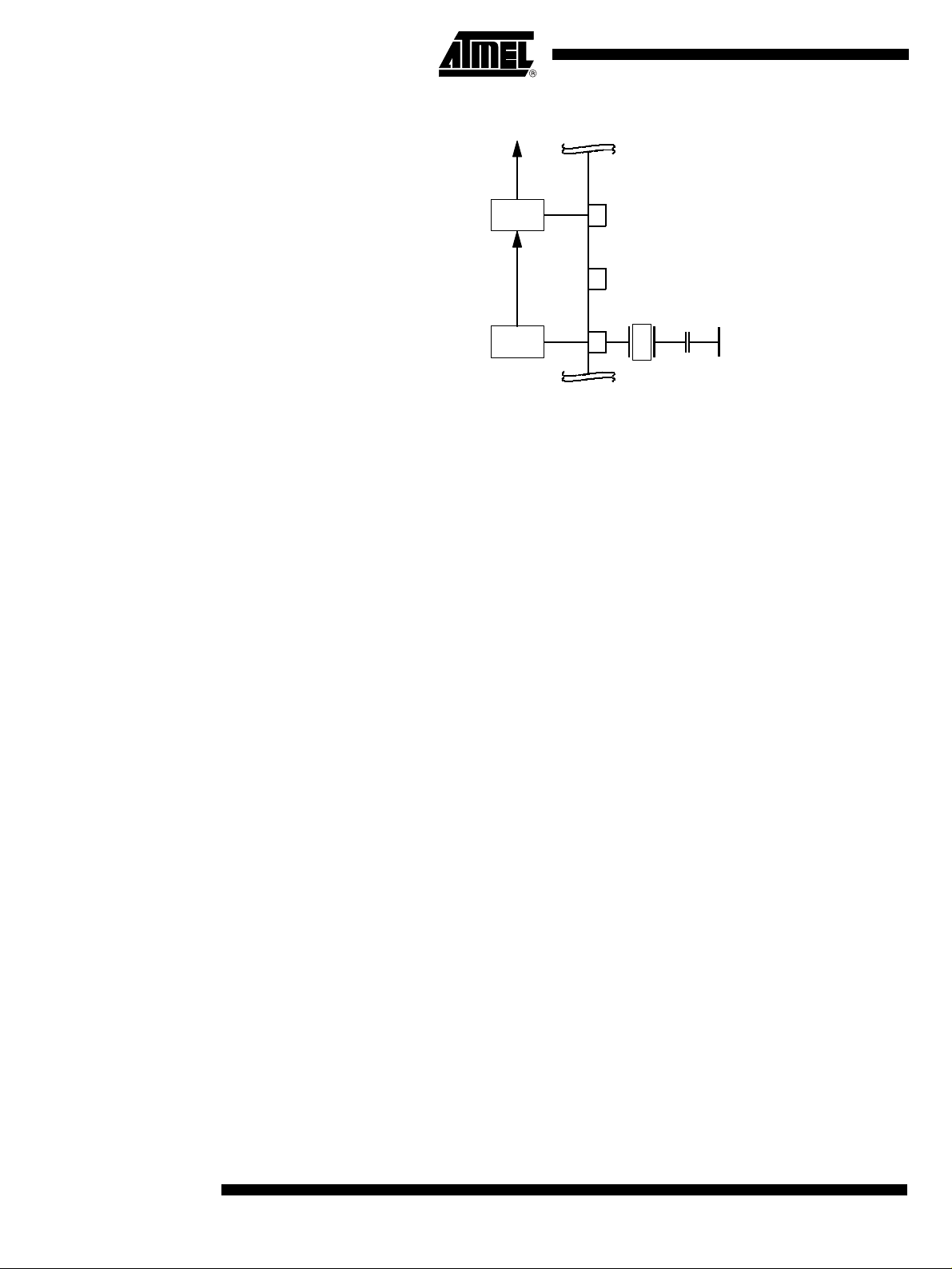

The complete timing of the digital circuitry and the analog filtering is derived from one

clock. According to Figure 9, th is clock cycle T

is derived from the c rystal osc illator

Clk

(XTO) in combination with a di vide r. The di vision factor i s cont rolled by the l ogical s tate

at Pin MODE. According to section “RF Front-end”, the frequency of the crystal oscillator

(f

) is defined by the RF input signal (f

XTO

of the local oscillator (f

LO

).

) which also defines the operating frequency

RFin

4569A–RKE–12/02

9

Figure 9. Generation of the Basic Clock Cycle

T

Clk

Divider

:14/:10

MODE

16

L : USA(:10)

H: Europe(:14)

f

XTO

XTO

Pin MODE can now be se t in accord ance with t he de sired c lock c ycle T

DVCC

15

XTO

14

Clk

. T

controls

Clk

the following application relevant parameters:

• Timing of the polling circuit including bit check

• Timing of the analog and digital signal processing

• Timing of the register programming

• Frequency of the reset marker

• IF filter center frequency (f

Most applications ar e dominated by two trans missio n frequencies : f

mainly used in USA, f

= 433.92 MHz in Europe. In order to ease the usage of all T

Send

IF0

)

= 315 MHz is

Send

Clk

dependent parameters on this electrical characteristics display three conditions for each

parameter.

• Application USA (f

• Application Europe (f

• Other applications (T

The electrical characteristic is given as a function of T

= 4.90625 MHz, MODE = L, T

XTO

= 6.76438 MHz, MODE = H, T

XTO

is dependent on f

Clk

XTO

= 2.0383 µs)

Clk

= 2.0697 µs)

Clk

and on the logical state of Pin MODE.

).

Clk

The clock cycle of some function blocks depends on the selected baud-rate range

(BR_Range) which is define d in the OPMODE reg ister. T his cloc k cycl e T

is defined

XClk

by the following formulas for further reference:

-

BR_Range = BR_Range0: T

BR_Range1: T

BR_Range2: T

BR_Range3: T

XClk

XClk

XClk

XClk

= 8 ´ T

= 4 ´ T

= 2 ´ T

= 1 ´ T

Clk

Clk

Clk

Clk

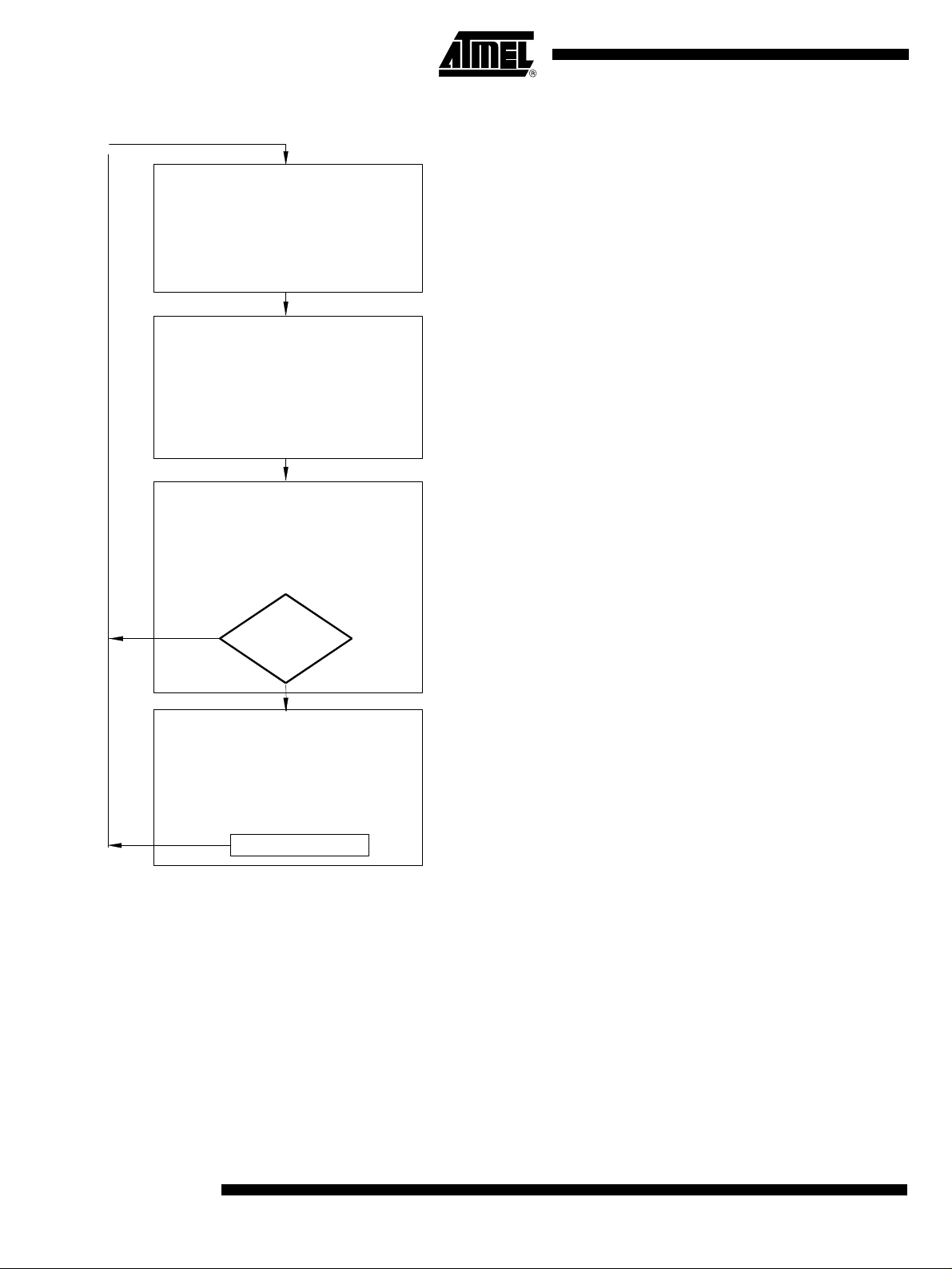

Polling Mode According to Figure 10, the receiver stays in polling mode in a continuous cycle of three

different modes. In sleep mode the signal processi ng circuitry is disabled for the time

10

T5743

period T

all signal processing circuits are enabled and settled. In the following bit-check mode,

the incoming data stream is analyzed bit by bit contra a valid transmitter signal. If no

valid signal is present, the receiver is set back to sleep mode after the period T

This period varies check by check as it is a statistical process. An average value for

T

Bit-check

consumption is I

The average curre nt co nsu mpt ion i n p o llin g mode is dependent on the duty cycle of the

active mode and can be calculated as:

while consuming low current of IS=I

Sleep

. During the start-up perio d, T

Soff

is given in the electrical characteristics. During T

=I

S

. The condition of the receiver is indicated on Pin IC_ACTIVE.

Son

Startup

and T

the current

Bit-check

4569A–RKE–12/02

Startup

Bit-check

,

.

T5743

I

I

Spoll

During T

SoffTSleepISon

--------------------------------------------------------------------------------------------------------------=

Sleep

T

SleepTStartupTBit-check

and T

Startup

tee the reception o f a tran sm itte d command the trans mi tte r mus t st ar t th e t ele gr am wi th

an adequate preburst. The required length of the preburst depends on the polling

parameters T

(T

Start,µC

). Thus, T

Sleep

, T

Startup

Bit-check

to be tested.

The following formula indicates how to calculate the preburst length.

T

Preburst

³ T

Sleep

+ T

Startup

Sleep Mode The length of period T

the extension factor XSleep (according to Table 9), and the basic clock cycle T

calculated to be:

T

= Sleep ´ X

Sleep

In US- and European applications, the maximum value of T

is set to 1. The time resolutio n is about 2 ms in that case. The s leep time can be

extended to almost half a second by setting XSleep to 8. XSleep can be set to 8 by bit

XSleep

Std

to 1.

According to Tabl e 8, the hi gh es t reg is ter va lue o f s le ep sets th e re ce iv er i nto a p er manent sleep condition. The receiver remains in that condition until another value for Sleep

is programmed into the O PMODE register. This function is desirable wher e several

devices share a singl e data line and may als o be used for micr ocontroll er polling — vi a

Pin POLLING/_ON, the receiver can be switched on and off.

Sleep

T

+()´+´

StartupTBit-check

++

the receiver i s no t sensi tive to a tra nsm itter s ignal . To gu aran-

, T

depends on the actual bit rate and the number of bits (N

+ T

is defined by the 5-bit word Sleep of the OPMODE register,

Sleep

´ 1024 ´ T

and the start-up time of a connected mi crocontr oller

Bit-check

+ T

Bit-check

Clk

Start_µC

is about 60 ms if XSleep

Sleep

Bit-check

Clk

)

. It is

4569A–RKE–12/02

11

Figure 10. Poll ing Mode Flow Chart

Sleep mode:

Sleep mode:

Sleep mode:

All circuits for signal processing are

All circuits for signal processing are

All circuits for signal processing are

disabled. Only XTO and Polling logic is

disabled. Only XTO and Polling logic is

disabled. Only XTO and Polling logic is

enabled.

enabled.

enabled.

Output level on Pin IC_ACTIVE => low

Output level on Pin IC_ACTIVE => low

Output level on Pin IC_ACTIVE => low

= I

= I

I

I

= I

I

S

Soff

S

Soff

S

Soff

= Sleep ´ X

= Sleep ´ X

T

T

= Sleep ´ X

T

Sleep

Sleep

Sleep

Start-up mode:

Start-up mode:

Start-up mode:

The signal processing circuits are

The signal processing circuits are

The signal processing circuits are

enabled. After the start-up time (T

enabled. After the start-up time (T

enabled. After the start-up time (T

all circuits are in stable

all circuits are in stable

all circuits are in stable

condition and ready to receive.

condition and ready to receive.

condition and ready to receive.

Output level on Pin IC_ACTIVE => high

Output level on Pin IC_ACTIVE => high

Output level on Pin IC_ACTIVE => high

IS = I

IS = I

IS = I

Son

Son

Son

T

T

T

Startup

Startup

Startup

Bit-check mode:

Bit-check mode:

Bit-check mode:

The incomming data stream is

The incomming data stream is

The incomming data stream is

analyzed. If the timing indicates a valid

analyzed. If the timing indicates a valid

analyzed. If the timing indicates a valid

transmitter signal, the receiver is set to

transmitter signal, the receiver is set to

transmitter signal, the receiver is set to

receiving mode. Otherwise it is set to

receiving mode. Otherwise it is set to

receiving mode. Otherwise it is set to

Sleep mode.

Sleep mode.

Sleep mode.

Output level on Pin IC_ACTIVE => high

Output level on Pin IC_ACTIVE => high

Output level on Pin IC_ACTIVE => high

IS = I

IS = I

IS = I

Son

Son

Son

T

T

T

Bit-check

Bit-check

Bit-check

NO

NO

NO

´ 1024 T

´ 1024 T

´ 1024 T

Sleep

Sleep

Sleep

Bit-check

Bit-check

Bit-check

OK ?

OK ?

OK ?

Clk

Clk

Clk

Startup

Startup

Startup

Sleep: 5-bit word defined by Sleep0 to

Sleep: 5-bit word defined by Sleep0 to

Sleep: 5-bit word defined by Sleep0 to

XSleep: Extension factor defined by

XSleep: Extension factor defined by

XSleep: E xtension factor defin ed by

T

T

T

Clk

Clk

Clk

T

T

T

Startup

Startup

)

)

)

Startup

T

T

T

Bit-check

Bit-check

Bit-check

number of bits to be checked (N

number of bits to be checked (N

number of bits to be checked (N

Sleep4 in OPMODE register

Sleep4 in OPMODE register

Sleep4 in OPMODE register

according to Table 9

XSleep

XSleep

: Basic clock cycle defined by f

: Basic clock cycle defined by f

XSleep

: Basic clock cycle defined by f

and Pin MODE

and Pin MODE

and Pin MODE

: Is defined by the selected baud rate

: Is defined by the selected baud rate

: Is defined by the selected baud rate

range and T

range and T

range and TClk. The baud-rate range is

defined by Baud0 and Baud1 in the

defined by Baud0 and Baud1 in the

defined by Baud0 and Baud1 in the

OPMODE register.

OPMODE register.

OPMODE register.

: Depends on the result of the bit check.

: Depends on the result of the bit check.

: Depends on the result of the bit check.

If the bit check is ok, T

If the bit check is ok, T

If the bit check is ok, T

the utilized data rate.

the utilized data rate.

the utilized data rate.

according to Table 9

according to Table 9

Std

Std

Std

. The baud-rate range is

. The baud-rate range is

Clk

Clk

Bit-check

Bit-check

Bit-check

XTO

XTO

XTO

depends on the

depends on the

depends on the

Bit-check

Bit-check

Bit-check

) and on

) and on

) and on

YES

YES

Receiving mode:

Receiving mode:

Receiving mode:

The receiver is turned on permanently

The receiver is turned on permanently

The receiver is turned on permanently

and passes the data stream to the

and passes the data stream to the

and passes the data stream to the

connected microcontroller.

connected microcontroller.

connected mC.

It can be set to Sleep mode through an

It can be set to Sleep mode through an

It can be set to Sleep mode through an

OFF command via Pin DATA or

OFF command via Pin DATA or

OFF command via Pin DATA or

POLLING/_ON.

POLLING/_ON.

POLLING/_ON.

Output level on Pin IC_ACTIVE => high

Output level on Pin IC_ACTIVE => high

Output level on Pin IC_ACTIVE => high

IS = I

IS = I

IS = I

Son

Son

Son

YES

OFF command

OFF command

OFF command

If the bit check fails, the average time period

If the bit check fails, the average time period

If the bit check fails, the average time period

for that check depends on the selected baud-

for that check depends on the selected baud-

for that check depends on the selected baud-

rate range and on T

rate range and on T

rate range and on T

defined by Baud0 and Baud1 in the OPMODE register

defined by Baud0 and Baud1 in the OPMODE register

defined by Baud0 and Baud1 in the OPMODE register

. The baud-rate range is

. The baud-rate range is

. The baud-rate range is

Clk

Clk

Clk

12

T5743

4569A–RKE–12/02

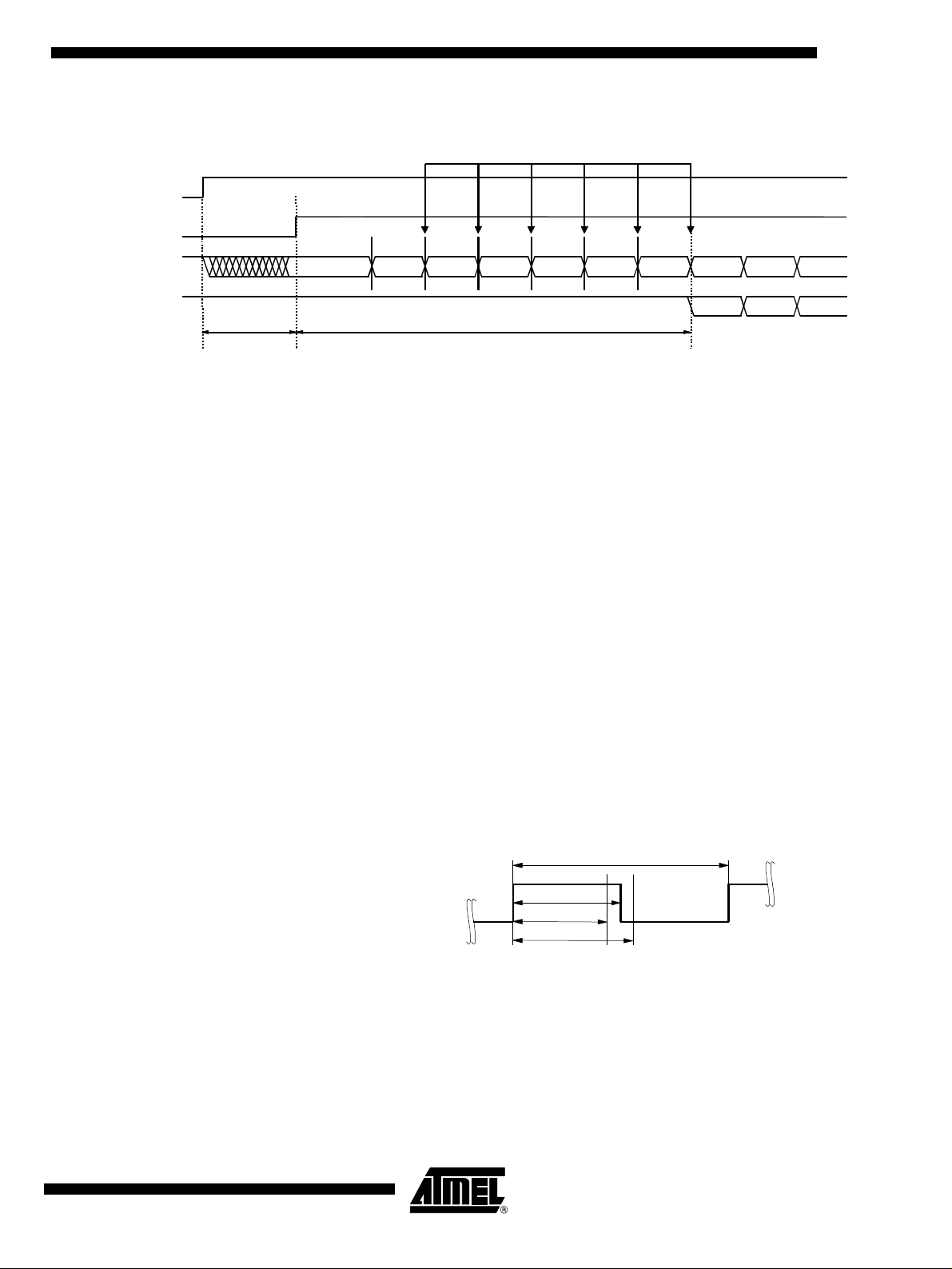

Figure 11. Timing Diagram for Complete Successful Bit Check

T5743

( Number of checked Bits: 3 )

IC_ACTIVE

Bit check

Dem_out

Data_out (DATA)

Start-up mode

T

Start-up

1/2 Bit

1/2 Bit

T

Bit-check

Bit-check mode

Bit check ok

1/2 Bit 1/2 Bit 1/2 Bit 1/2 Bit

Receiving mode

Bit-check Mode In bit-check mode the incomin g data stream is examine d to distinguis h between a vali d

signal from a corresponding transmitter and signals due to noise. This is done by subsequent time frame checks where the distances between two signal edges are

continuously compared to a programmable time window. The maximum count of this

edge-to-edge te sts before the receiver switches to receiv ing mode is also

programmable.

Configuring the Bit Check Assuming a modulation sche me that contains two edg es per bit, two tim e frame ch ecks

are verifying one bit. This is valid for Manchester, Bi-phase and most other modulation

schemes. The maximum count of bits to be checked can be set to 0, 3, 6 or 9 bits via the

variable N

Bit-check

checks respectively. If N

in the OPMODE r egister. T his implie s 0, 6, 1 2 and 18 edge to edge

Bit-check

is set to a higher value, the receiv er is less likely to

switch to receiv ing mode due to noise. In the presenc e of a valid tr ansmit ter signal, the

bit check takes less time if N

time is not dependent on N

Bit–check

Bit-check

is set to a lower value. In polling mode, the bit-check

. Figure 11 shows a n example where 3 bits are te ste d

successfully and the data signal is transferred to Pin DATA.

According to Figure 12, the time window for the bit check is defined by two separate

time limits. If the edge-to-edge time t

the upper bit-check limit T

T

Lim_min

or tee exceeds T

Lim_max

Lim_max

is in between the lower bit-check limit T

ee

Lim_min

and

, the check will be continued. If tee is smaller than

, the bit check will be terminated and the receiver

switches to sleep mode.

Figure 12. Valid Time Window for Bit Check

1/f

Sig

t

Dem_out

For best noise immunity it is recomme nded to use a low span between T

T

. This is achieved using a fixed frequency at a 50% duty cycle for the transmitter

Lim_max

T

Lim_min

T

Lim_max

ee

and

Lim_min

preburst. A “11111...” or a “10101...” sequence in Manchester or Bi-phase is a good

choice concerning that advice. A good compromise between receiver sensitivity and

susceptibility to noise is a time window of ±25% regarding the expected edge-to-edge

time t

. Using pre-burst patterns that contain various edge-to-edge ti me periods, the

ee

bit-check limits must be programmed according to the required span.

The bit-check limits are determined by means of the formula below.

4569A–RKE–12/02

13

Loading...

Loading...