Page 1

Atmel SAM D21E / SAM D21G / SAM D21J

SMART ARM-Based Microcontroller

DATASHEET

Description

The Atmel® | SMART™ SAM D21 is a series of low-power microcontrollers using the 32-bit

®

ARM

Cortex®-M0+ processor, and ranging from 32- to 64-pins with up to 256KB Flash and

32KB of SRAM. The SAM D21 devices operate at a maximum frequency of 48MHz and reach

2.46 CoreMark/MHz. They are designed for simple and intuitive migration with identical

peripheral modules, hex compatible code, identical linear address map and pin compatible

migration paths between all devices in the product series. All devices include intelligent and

flexible peripherals, Atmel Event System for inter-peripheral signaling, and support for capacitive

touch button, slider and wheel user interfaces.

The Atmel SAM D21 devices provide the following features: In-system programmable Flash,

twelve-channel direct memory access (DMA) controller, 12 channel Event System,

programmable interrupt controller, up to 52 programmable I/O pins, 32-bit real-time clock and

calendar, up to five 16-bit Timer/Counters (TC) and three 24-bit Timer/Counters for Control

(TCC), where each TC can be configured to perform frequency and waveform generation,

accurate program execution timing or input capture with time and frequency measurement of

digital signals. The TCs can operate in 8- or 16-bit mode, selected TCs can be cascaded to form

a 32-bit TC, and three timer/counters have extended functions optimized for motor, lighting and

other control applications. The series provide one full-speed USB 2.0 embedded host and device

interface; up to six Serial Communication Modules (SERCOM) that each can be configured to act

as an USART, UART, SPI, I

interface; up to twenty-channel 350ksps 12-bit ADC with programmable gain and optional

oversampling and decimation supporting up to 16-bit resolution, one 10-bit 350ksps DAC, two

analog comparators with window mode, Peripheral Touch Controller supporting up to 256

buttons, sliders, wheels and proximity sensing; programmable Watchdog Timer, brown-out

detector and power-on reset and two-pin Serial Wire Debug (SWD) program and debug interface.

2

C up to 3.4MHz, SMBus, PMBus, and LIN slave; two-channel I2S

SMART

All devices have accurate and low-power external and internal oscillators. All oscillators can be

used as a source for the system clock. Different clock domains can be independently configured

to run at different frequencies, enabling power saving by running each peripheral at its optimal

clock frequency, and thus maintaining a high CPU frequency while reducing power consumption.

The SAM D21 devices have two software-selectable sleep modes, idle and standby. In idle mode

the CPU is stopped while all other functions can be kept running. In standby all clocks and

functions are stopped expect those selected to continue running. The device supports

SleepWalking. This feature allows the peripheral to wake up from sleep based on predefined

conditions, and thus allows the CPU to wake up only when needed, e.g. when a threshold is

crossed or a result is ready. The Event System supports synchronous and asynchronous events,

allowing peripherals to receive, react to and send events even in standby mode.

The Flash program memory can be reprogrammed in-system through the SWD interface. The

same interface can be used for non-intrusive on-chip debug of application code. A boot loader

running in the device can use any communication interface to download and upgrade the

application program in the Flash memory.

The Atmel SAM D21 devices are supported with a full suite of program and system development

tools, including C compilers, macro assemblers, program debugger/simulators, programmers and

evaluation kits

.

Atmel-42181G–SAM-D21_Datasheet–09/2015

Page 2

Features

z Processor

z ARM Cortex-M0+ CPU running at up to 48MHz

z Single-cycle hardware multiplier

z Micro Trace Buffer (MTB)

z Memories

z 32/64/128/256KB in-system self-programmable Flash

z 4/8/16/32KB SRAM Memory

z System

z Power-on reset (POR) and brown-out detection (BOD)

z Internal and external clock options with 48MHz Digital Frequency Locked Loop (DFLL48M) and 48MHz to 96MHz Fractional

Digital Phase Locked Loop (FDPLL96M)

z External Interrupt Controller (EIC)

z 16 external interrupts

z One non-maskable interrupt

z Two-pin Serial Wire Debug (SWD) programming, test and debugging interface

z Low Power

z Idle and standby sleep modes

z SleepWalking peripherals

z Peripherals

z 12-channel Direct Memory Access Controller (DMAC)

z 12-channel Event System

z Up to five 16-bit Timer/Counters (TC), configurable as either:

z One 16-bit TC with compare/capture channels

z One 8-bit TC with compare/capture channels

z One 32-bit TC with compare/capture channels, by using two TCs

z Three 24-bit Timer/Counters for Control (TCC), with extended functions:

z Up to four compare channels with optional complementary output

z Generation of synchronized pulse width modulation (PWM) pattern across port pins

z Deterministic fault protection, fast decay and configurable dead-time between complementary output

z Dithering that increase resolution with up to 5 bit and reduce quantization error

z 32-bit Real Time Counter (RTC) with clock/calendar function

z Watchdog Timer (WDT)

z CRC-32 generator

z One full-speed (12Mbps) Universal Serial Bus (USB) 2.0 interface

z Embedded host and device function

z Eight endpoints

z Up to six Serial Communication Interfaces (SERCOM), each configurable to operate as either:

z USART with full-duplex and single-wire half-duplex configuration

2

z I

C up to 3.4MHz

z SPI

z LIN slave

z One two-channel Inter-IC Sound (I

z One 12-bit, 350ksps Analog-to-Digital Converter (ADC) with up to 20 channels

z Differential and single-ended input

z 1/2x to 16x programmable gain stage

z Automatic offset and gain error compensation

z Oversampling and decimation in hardware to support 13-, 14-, 15- or 16-bit resolution

z 10-bit, 350ksps Digital-to-Analog Converter (DAC)

z Two Analog Comparators (AC) with window compare function

z Peripheral Touch Controller (PTC)

z 256-Channel capacitive touch and proximity sensing

z I/O

z Up to 52 programmable I/O pins

z Drop in compatible with SAM D20

z Packages

z 64-pin TQFP, QFN, UFBGA

z 48-pin TQFP, QFN, WLCSP

z 32-pin TQFP, QFN, WLCSP

z Operating Voltage

z 1.62V – 3.63V

2

S) interface

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

2

Page 3

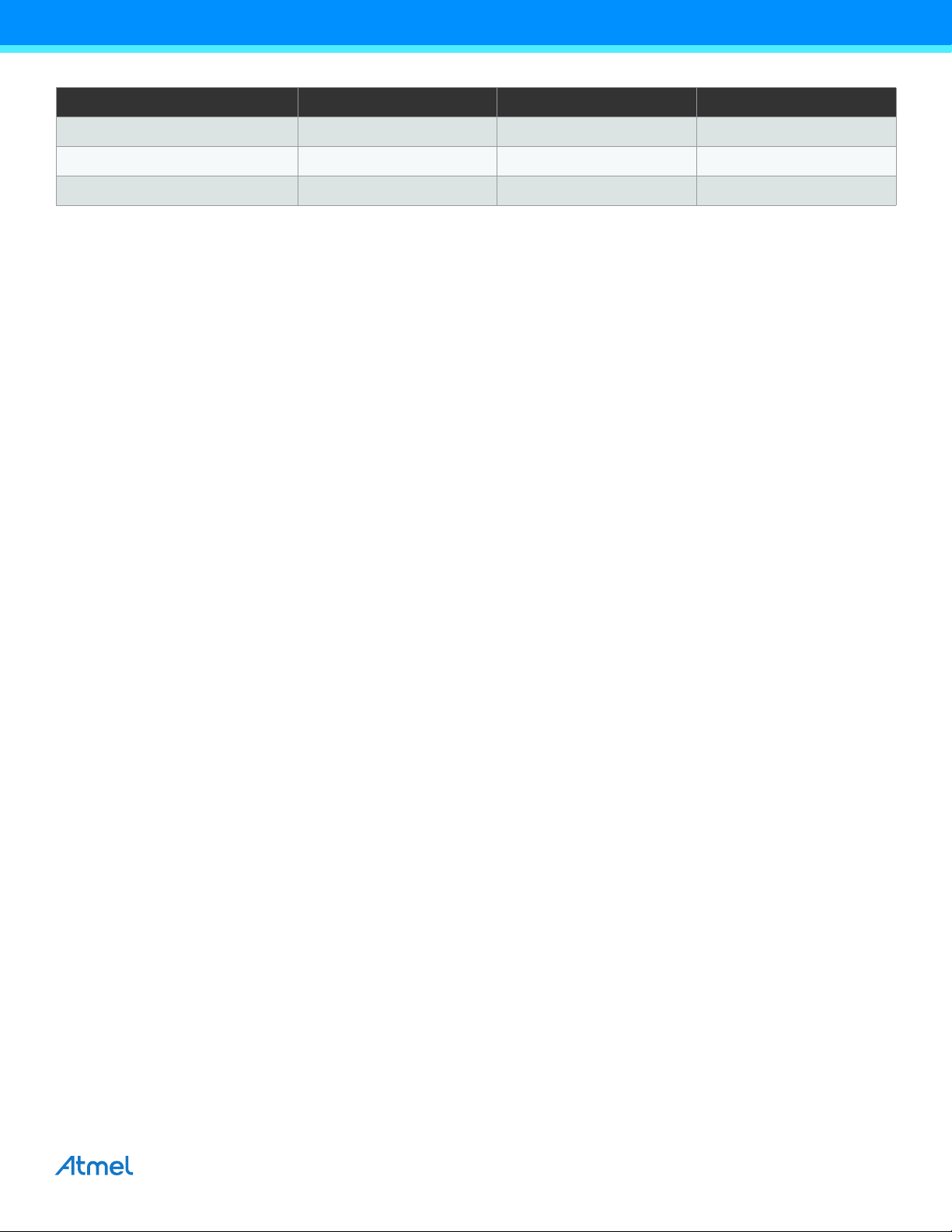

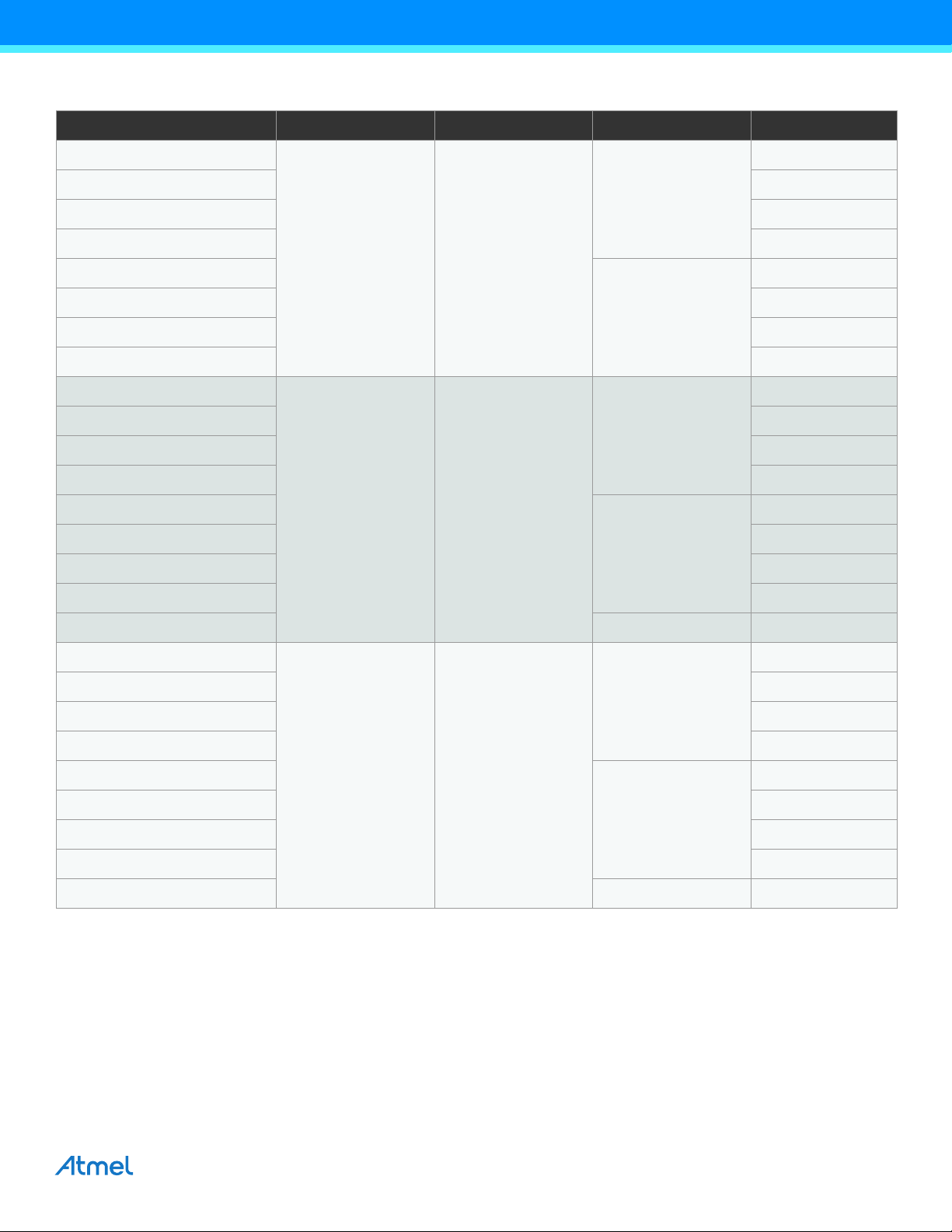

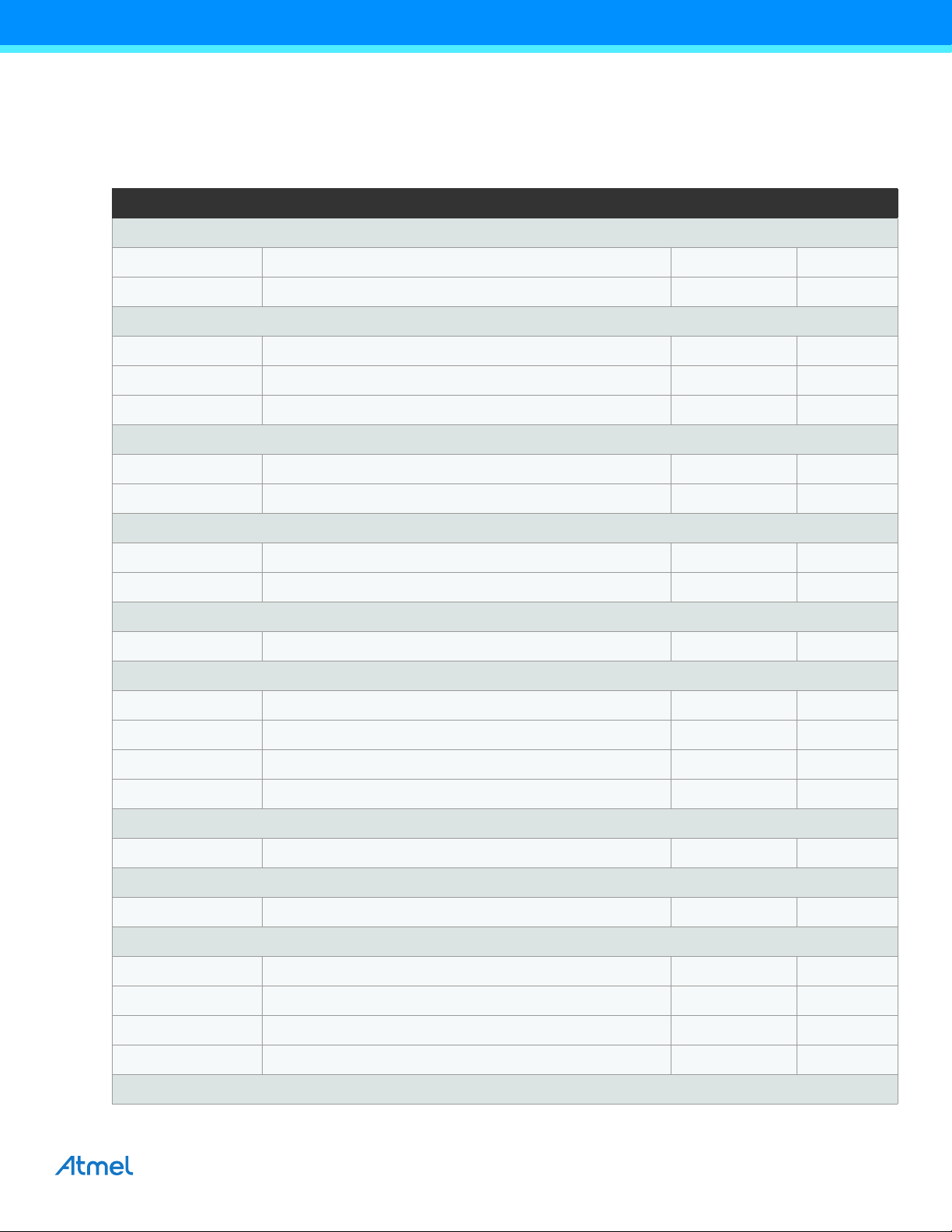

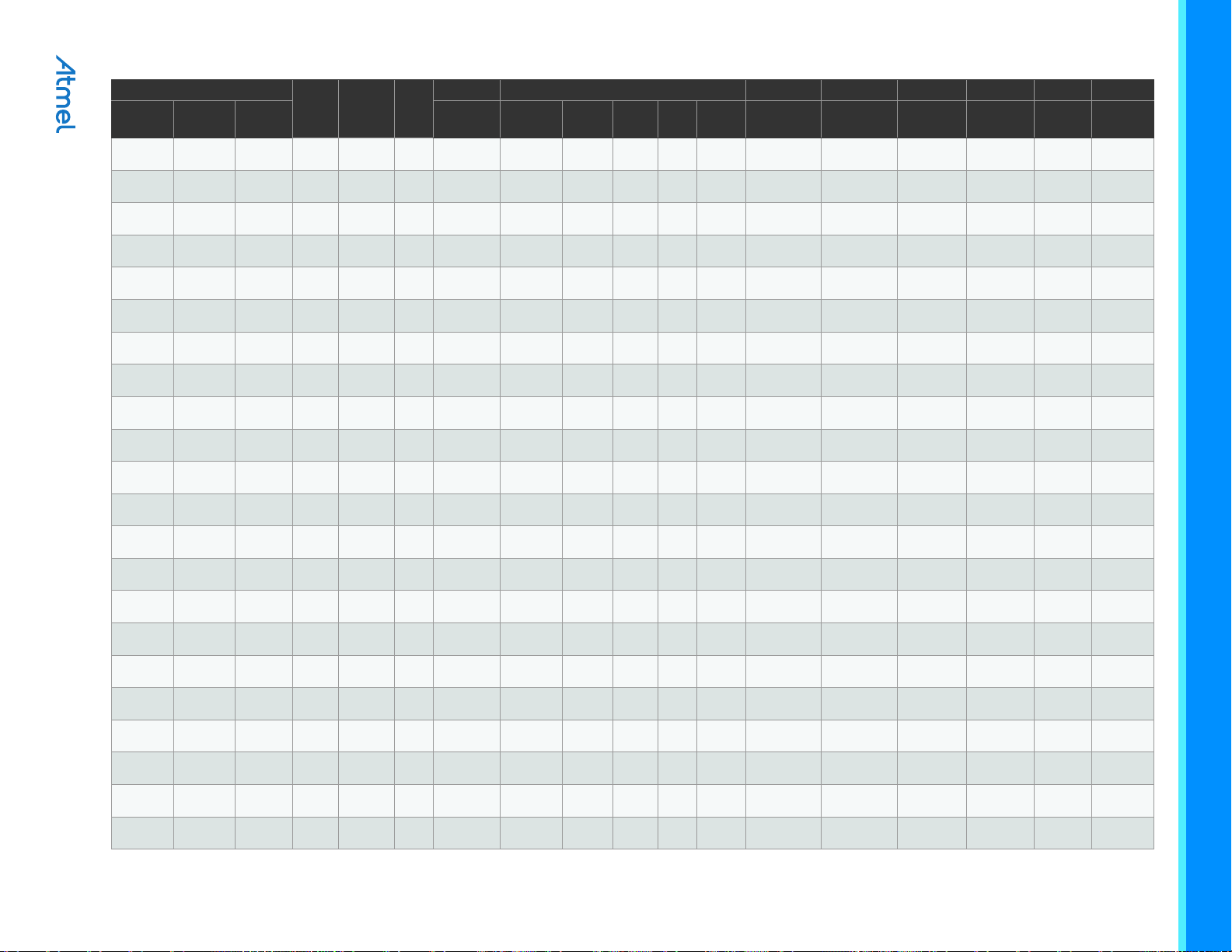

1. Configuration Summary

SAM D21J SAM D21G SAM D21E

Pins 64 48 32

General Purpose I/O-pins (GPIOs) 52 38 26

Flash 256/128/64/32KB 256/128/64/32KB 256/128/64/32KB

SRAM 32/16/8/4KB 32/16/8/4KB 32/16/8/4KB

Timer Counter (TC) instances 5 3 3

Waveform output channels per TC

instance

Timer Counter for Control (TCC)

instances

Waveform output channels per TCC 8/4/2 8/4/2 6/4/2

DMA channels 12 12 12

USB interface 1 1 1

Serial Communication Interface

(SERCOM) instances

Inter-IC Sound (I2S) interface 1 1 1

Analog-to-Digital Converter (ADC)

channels

Analog Comparators (AC) 2 2 2

Digital-to-Analog Converter (DAC)

channels

Real-Time Counter (RTC) Yes Yes Yes

RTC alarms 1 1 1

RTC compare values

2 2 2

3 3 3

6 6 4

20 14 10

1 1 1

1 32-bit value or

2 16-bit values

1 32-bit value or

2 16-bit values

1 32-bit value or

2 16-bit values

External Interrupt lines 16 16 16

Peripheral Touch Controller (PTC) X

and Y lines

Maximum CPU frequency 48MHz

Packages

Oscillators

16x16 12x10 10x6

QFN

TQFP

UFBGA

32.768kHz crystal oscillator (XOSC32K)

0.4-32MHz crystal oscillator (XOSC)

32.768kHz internal oscillator (OSC32K)

32kHz ultra-low-power internal oscillator (OSCULP32K)

8MHz high-accuracy internal oscillator (OSC8M)

48MHz Digital Frequency Locked Loop (DFLL48M)

96MHz Fractional Digital Phased Locked Loop (FDPLL96M)

QFN

TQFP

WLCSP

QFN

TQFP

WLCSP

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

3

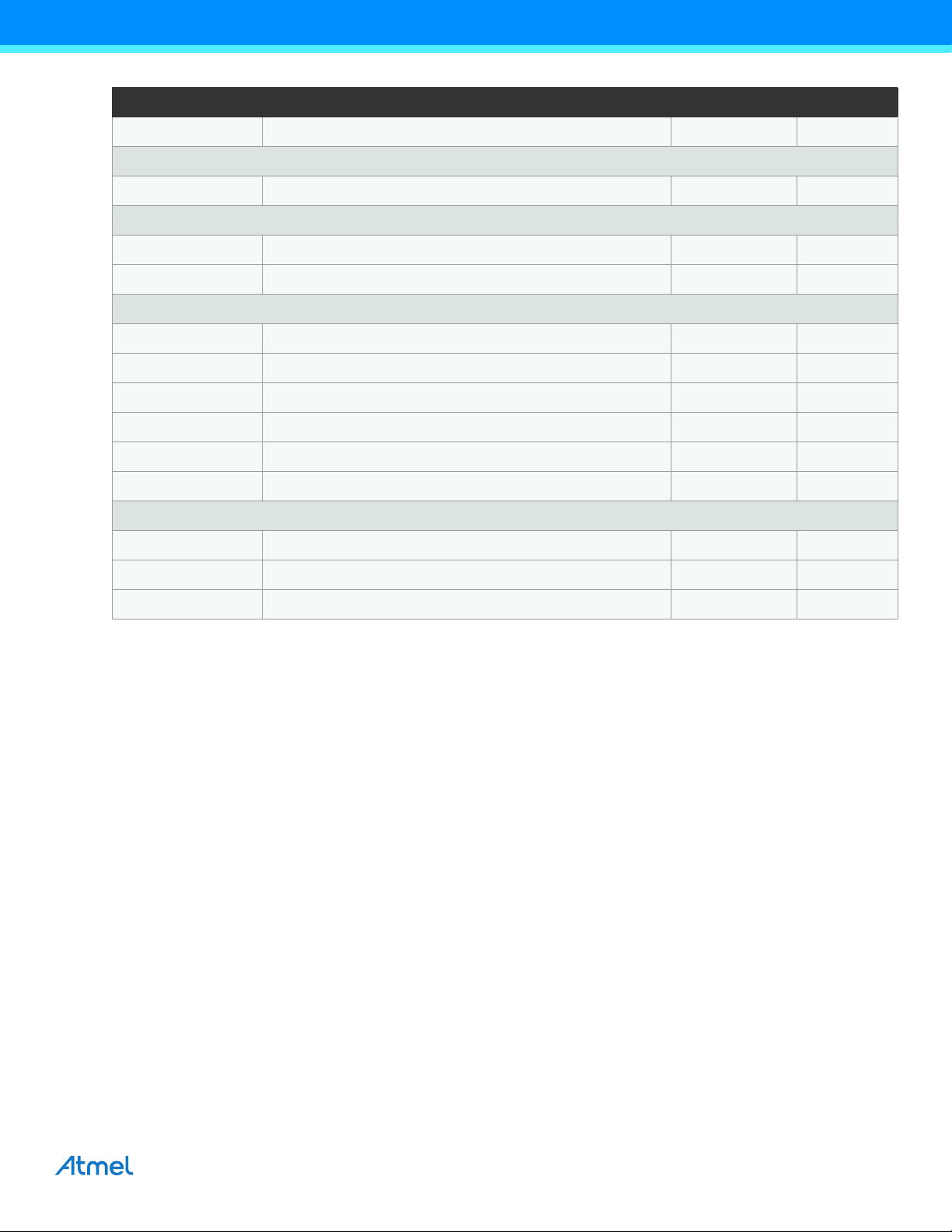

Page 4

SAM D21J SAM D21G SAM D21E

Event System channels 12 12 12

SW Debug Interface Yes Yes Yes

Watchdog Timer (WDT) Yes Yes Yes

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

4

Page 5

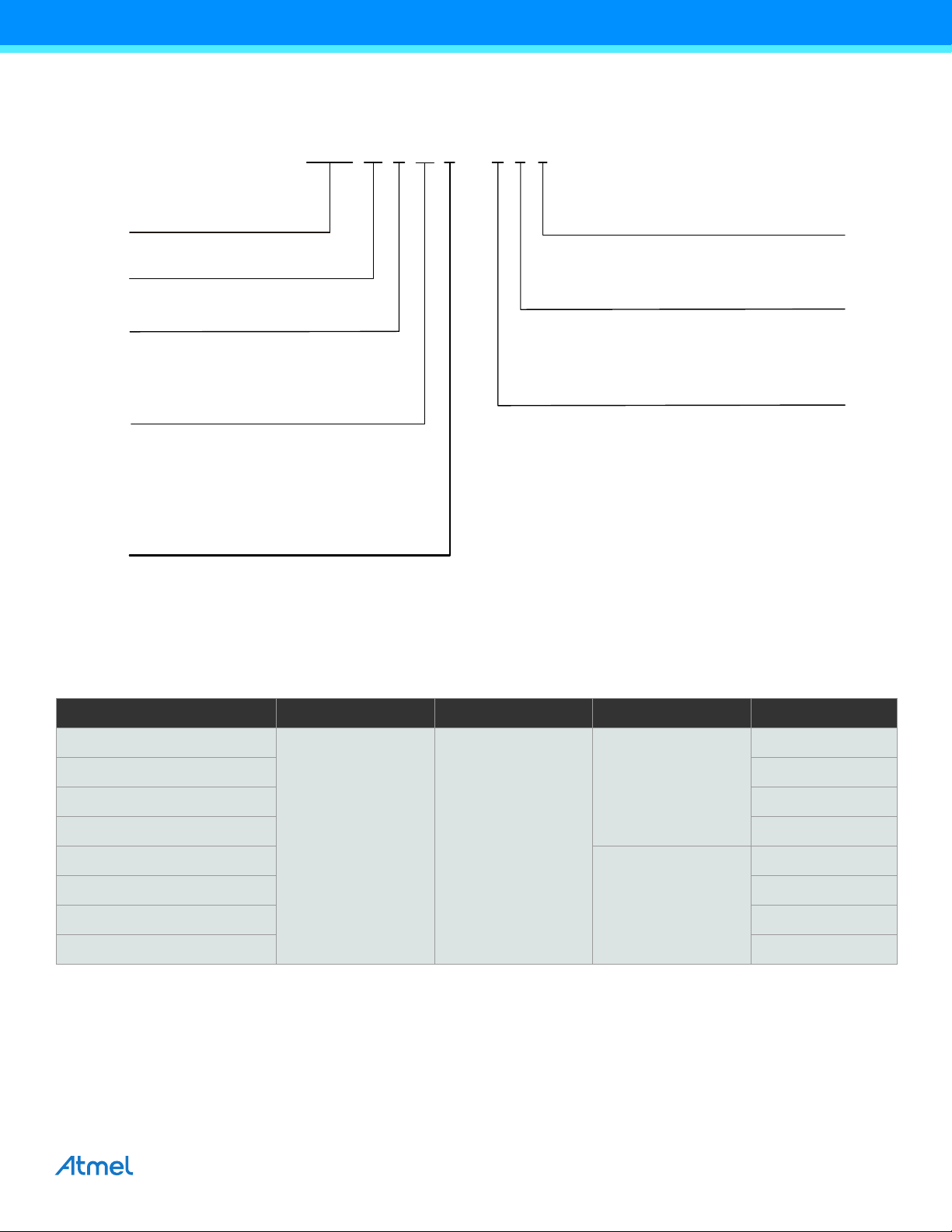

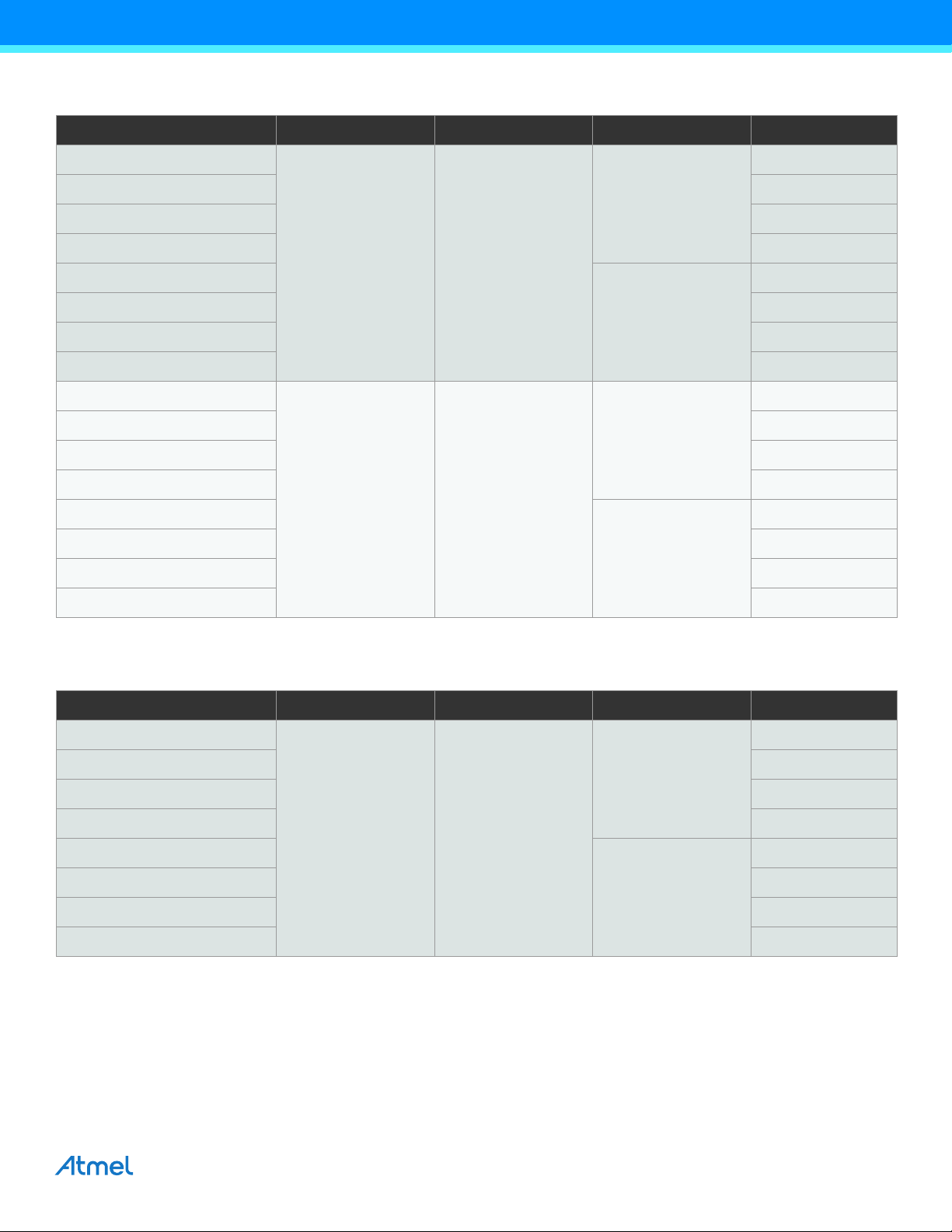

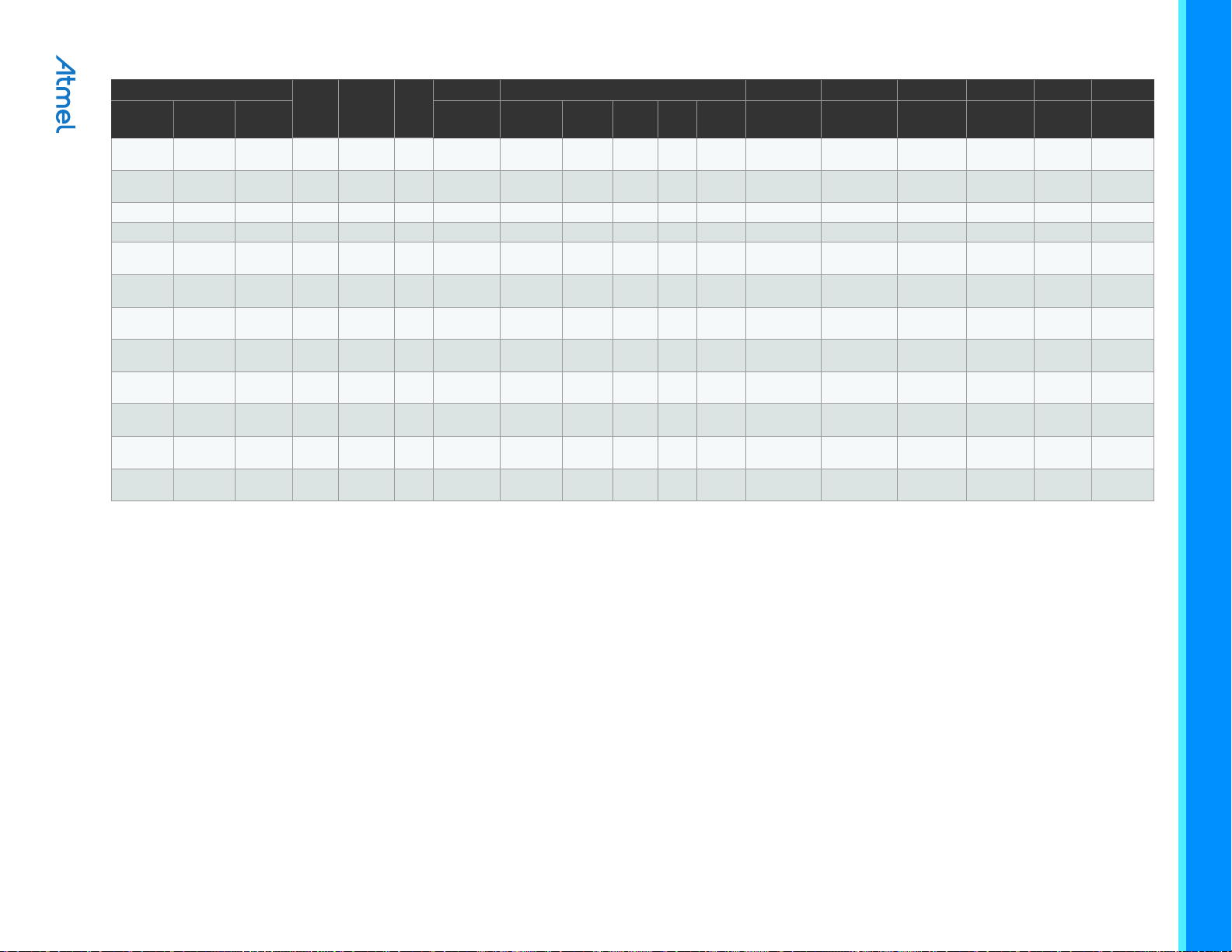

2. Ordering Information

SAMD 21 E 15 A - M U T

Product Family

SAMD = General Purpose Microcontroller

21 = Cortex M0 + CPU, Basic Feature Set

E = 32 Pins

G = 48 Pins

J = 64 Pins

No character = Tray (Default)

T = Tape and Reel

U = -40 - 85

O

C Matte Sn Plating

F = -40 - 125

O

C Matte Sn Plating

A = TQFP

M = QFN

U = WLCSP

C = UFBGA

+ DMA + USB

Product Series

Flash Memory Density

Device Variant

A = Default Variant

B = Added RWW support for 32KB and 64KB memory options

Pin Count

Package Carrier

Package Grade

Package Type

18 = 256KB

17 = 128KB

16 = 64KB

15 = 32KB

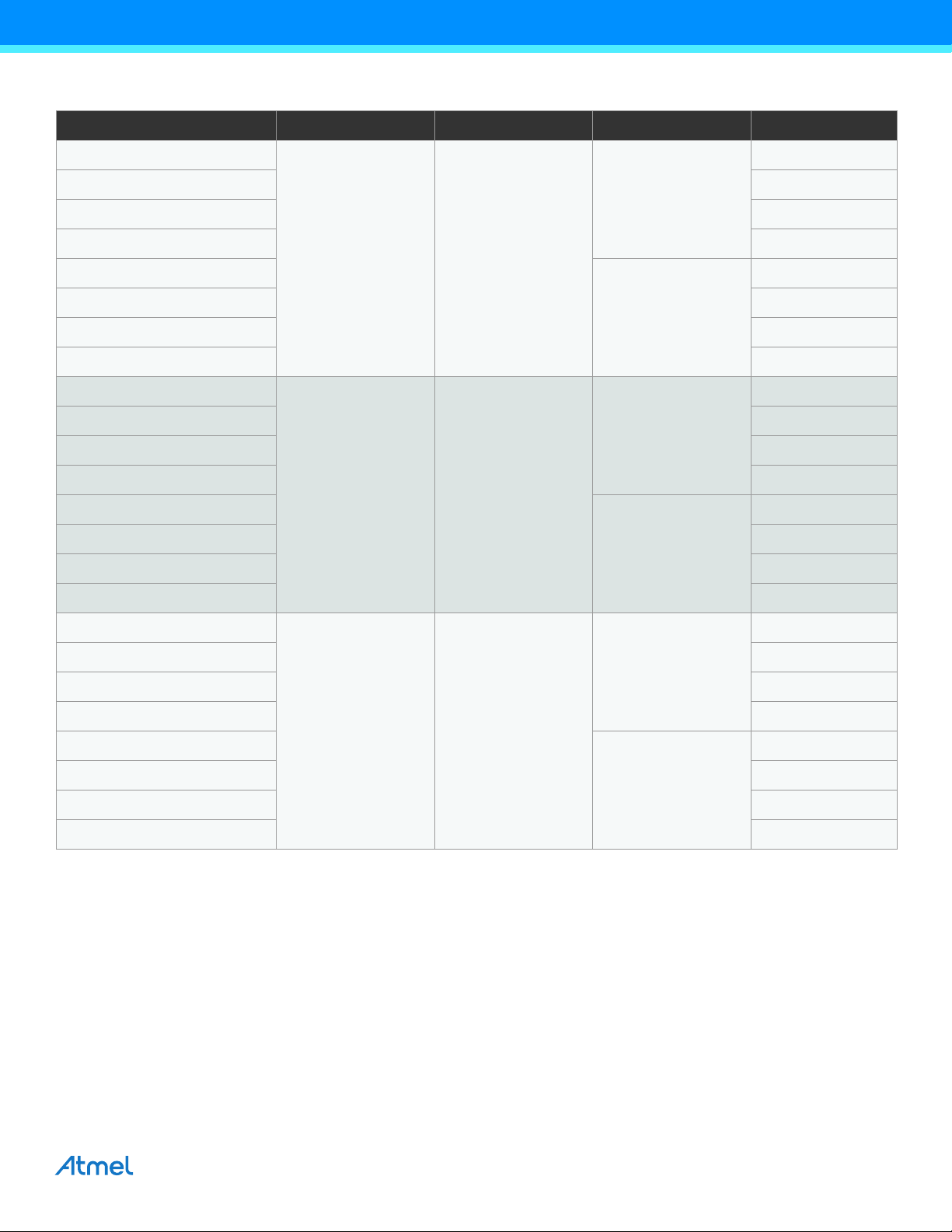

2.1 SAM D21E

2.1.1 Device Variant A

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21E15A-AU

ATSAMD21E15A-AUT Tape & Reel

ATSAMD21E15A-AF Tray

ATSAMD21E15A-AFT Tape & Reel

ATSAMD21E15A-MU

ATSAMD21E15A-MUT Tape & Reel

ATSAMD21E15A-MF Tray

ATSAMD21E15A-MFT Tape & Reel

32K 4K

TQFP32

QFN32

Tray

Tray

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

5

Page 6

2.1.1 Device Variant A (Continued)

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21E16A-AU

Tray

ATSAMD21E16A-AUT Tape & Reel

TQFP32

ATSAMD21E16A-AF Tray

ATSAMD21E16A-AFT Tape & Reel

64K 8K

ATSAMD21E16A-MU

Tray

ATSAMD21E16A-MUT Tape & Reel

QFN32

ATSAMD21E16A-MF Tray

ATSAMD21E16A-MFT Tape & Reel

ATSAMD21E17A-AU

Tray

ATSAMD21E17A-AUT Tape & Reel

TQFP32

ATSAMD21E17A-AF Tray

ATSAMD21E17A-AFT Tape & Reel

128K 16K

ATSAMD21E17A-MU

Tray

ATSAMD21E17A-MUT Tape & Reel

QFN32

ATSAMD21E17A-MF Tray

ATSAMD21E17A-MFT Tape & Reel

ATSAMD21E18A-AU

Tray

ATSAMD21E18A-AUT Tape & Reel

TQFP32

ATSAMD21E18A-AF Tray

ATSAMD21E18A-AFT Tape & Reel

256K 32K

ATSAMD21E18A-MU

Tray

ATSAMD21E18A-MUT Tape & Reel

QFN32

ATSAMD21E18A-MF Tray

ATSAMD21E18A-MFT Tape & Reel

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

6

Page 7

2.1.2 Device Variant B

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21E15B-AU

ATSAMD21E15B-AUT Tape & Reel

TQFP32

ATSAMD21E15B-AF Tray

ATSAMD21E15B-AFT Tape & Reel

32K 4K

ATSAMD21E15B-MU

ATSAMD21E15B-MUT Tape & Reel

QFN32

ATSAMD21E15B-MF Tray

ATSAMD21E15B-MFT Tape & Reel

ATSAMD21E15B-UUT 32K 4K WLCSP35 Tape & Reel

ATSAMD21E16B-AU

ATSAMD21E16B-AUT Tape & Reel

TQFP32

ATSAMD21E16B-AF Tray

ATSAMD21E16B-AFT Tape & Reel

64K 8K

ATSAMD21E16B-MU

ATSAMD21E16B-MUT Tape & Reel

QFN32

ATSAMD21E16B-MF Tray

Tray

Tray

Tray

Tray

ATSAMD21E16B-MFT Tape & Reel

ATSAMD21E16B-UUT 64K 8K WLCSP35 Tape & Reel

2.2 SAM D21G

2.2.1 Device Variant A

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21G15A-AU

ATSAMD21G15A-AUT Tape & Reel

TQFP48

ATSAMD21G15A-AF Tray

ATSAMD21G15A-AFT Tape & Reel

32K 4K

ATSAMD21G15A-MU

ATSAMD21G15A-MUT Tape & Reel

QFN48

ATSAMD21G15A-MF Tray

ATSAMD21G15A-MFT Tape & Reel

Tray

Tray

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

7

Page 8

2.2.1 Device Variant A (Continued)

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21G16A-AU

Tray

ATSAMD21G16A-AUT Tape & Reel

TQFP48

ATSAMD21G16A-AF Tray

ATSAMD21G16A-AFT Tape & Reel

64K 8K

ATSAMD21G16A-MU

Tray

ATSAMD21G16A-MUT Tape & Reel

QFN48

ATSAMD21G16A-MF Tray

ATSAMD21G16A-MFT Tape & Reel

ATSAMD21G17A-AU

Tray

ATSAMD21G17A-AUT Tape & Reel

TQFP48

ATSAMD21G17A-AF Tray

ATSAMD21G17A-AFT Tape & Reel

ATSAMD21G17A-MU

128K 16K

Tray

ATSAMD21G17A-MUT Tape & Reel

QFN48

ATSAMD21G17A-MF Tray

ATSAMD21G17A-MFT Tape & Reel

ATSAMD21G17A-UUT WLCSP45 Tape & Reel

ATSAMD21G18A-AU

Tray

ATSAMD21G18A-AUT Tape & Reel

TQFP48

ATSAMD21G18A-AF Tray

ATSAMD21G18A-AFT Tape & Reel

ATSAMD21G18A-MU

256K 32K

Tray

ATSAMD21G18A-MUT Tape & Reel

QFN48

ATSAMD21G18A-MF Tray

ATSAMD21G18A-MFT Tape & Reel

ATSAMD21G18A-UUT WLCSP45 Tape & Reel

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

8

Page 9

2.2.2 Device Variant B

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21G15B-AU

ATSAMD21G15B-AUT Tape & Reel

TQFP48

ATSAMD21G15B-AF Tray

ATSAMD21G15B-AFT Tape & Reel

32K 4K

ATSAMD21G15B-MU

ATSAMD21G15B-MUT Tape & Reel

QFN48

ATSAMD21G15B-MF Tray

ATSAMD21G15B-MFT Tape & Reel

ATSAMD21G16B-AU

ATSAMD21G16B-AUT Tape & Reel

TQFP48

ATSAMD21G16B-AF Tray

ATSAMD21G16B-AFT Tape & Reel

64K 8K

ATSAMD21G16B-MU

ATSAMD21G16B-MUT Tape & Reel

QFN48

ATSAMD21G16B-MF Tray

ATSAMD21G16B-MFT Tape & Reel

Tray

Tray

Tray

Tray

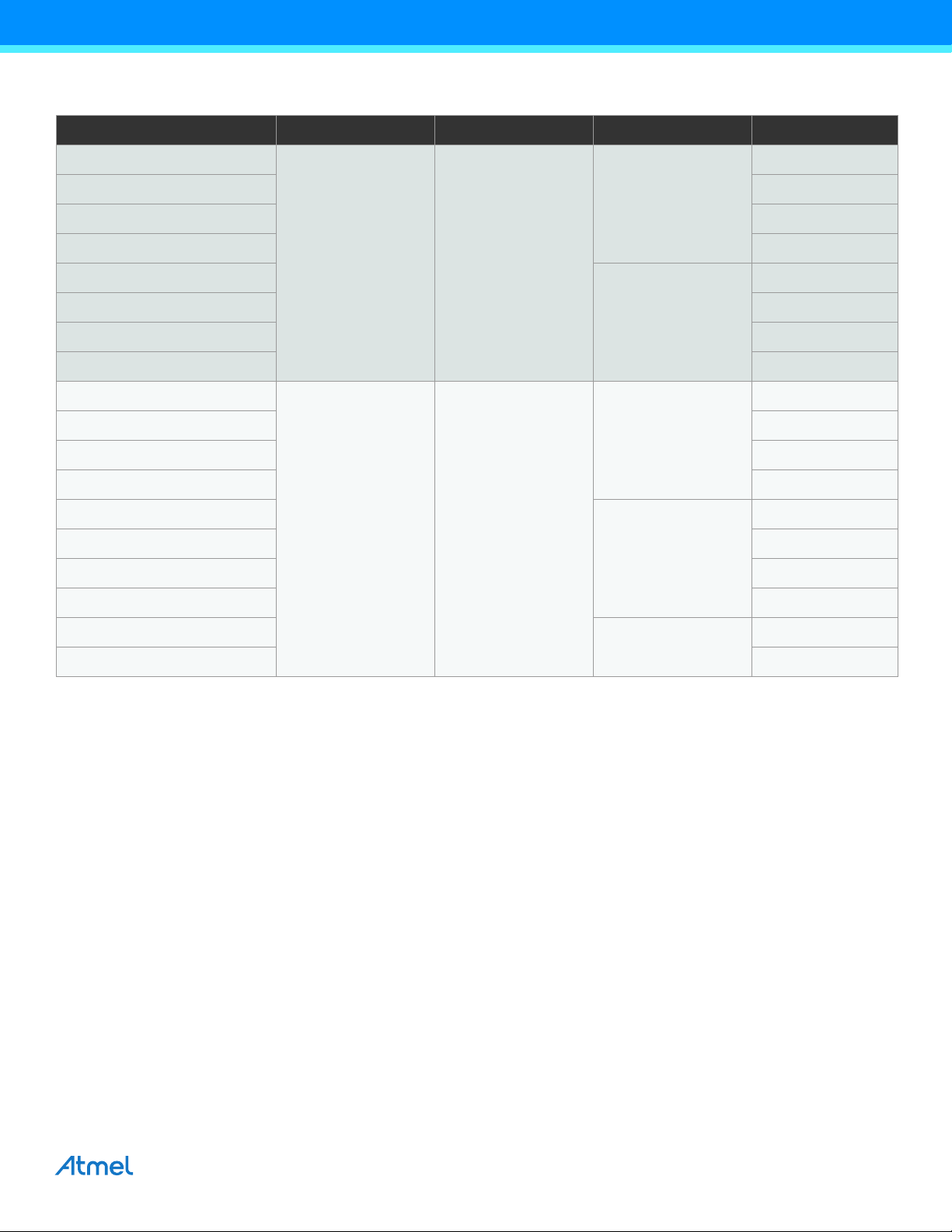

2.3 SAM D21J

2.3.1 Device Variant A

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21J15A-AU

ATSAMD21J15A-AUT Tape & Reel

TQFP64

ATSAMD21J15A-AF Tray

ATSAMD21J15A-AFT Tape & Reel

32K 4K

ATSAMD21J15A-MU

ATSAMD21J15A-MUT Tape & Reel

QFN64

ATSAMD21J15A-MF Tray

ATSAMD21J15A-MFT Tape & Reel

Tray

Tray

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

9

Page 10

2.3.1 Device Variant A (Continued)

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21J16A-AU

Tray

ATSAMD21J16A-AUT Tape & Reel

TQFP64

ATSAMD21J16A-AF Tray

ATSAMD21J16A-AFT Tape & Reel

ATSAMD21J16A-MU

Tray

64K 8K

ATSAMD21J16A-MUT Tape & Reel

QFN64

ATSAMD21J16A-MF Tray

ATSAMD21J16A-MFT Tape & Reel

ATSAMD21J16A-CU

Tray

UFBGA64

ATSAMD21J16A-CUT Tape & Reel

ATSAMD21J17A-AU

Tray

ATSAMD21J17A-AUT Tape & Reel

TQFP64

ATSAMD21J17A-AF Tray

ATSAMD21J17A-AFT Tape & Reel

ATSAMD21J17A-MU

Tray

128K 16K

ATSAMD21J17A-MUT Tape & Reel

QFN64

ATSAMD21J17A-MF Tray

ATSAMD21J17A-MFT Tape & Reel

ATSAMD21J17A-CU

Tray

UFBGA64

ATSAMD21J17A-CUT Tape & Reel

ATSAMD21J18A-AU

Tray

ATSAMD21J18A-AUT Tape & Reel

TQFP64

ATSAMD21J18A-AF Tray

ATSAMD21J18A-AFT Tape & Reel

ATSAMD21J18A-MU

Tray

256K 32K

ATSAMD21J18A-MUT Tape & Reel

QFN64

ATSAMD21J18A-MF Tray

ATSAMD21J18A-MFT Tape & Reel

ATSAMD21J18A-CU

Tray

UFBGA64

ATSAMD21J18A-CUT Tape & Reel

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

10

Page 11

2.3.2 Device Variant B

Ordering Code FLASH (bytes) SRAM (bytes) Package Carrier Type

ATSAMD21J15B-AU

Tray

ATSAMD21J15B-AUT Tape & Reel

TQFP64

ATSAMD21J15B-AF Tray

ATSAMD21J15B-AFT Tape & Reel

32K 4K

ATSAMD21J15B-MU

Tray

ATSAMD21J15B-MUT Tape & Reel

QFN64

ATSAMD21J15B-MF Tray

ATSAMD21J15B-MFT Tape & Reel

ATSAMD21J16B-AU

Tray

ATSAMD21J16B-AUT Tape & Reel

TQFP64

ATSAMD21J16B-AF Tray

ATSAMD21J16B-AFT Tape & Reel

ATSAMD21J16B-MU

Tray

64K 8K

ATSAMD21J16B-MUT Tape & Reel

QFN64

ATSAMD21J16B-MF Tray

ATSAMD21J16B-MFT Tape & Reel

ATSAMD21J16B-CU

Tray

UFBGA64

ATSAMD21J16B-CUT Tape & Reel

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

11

Page 12

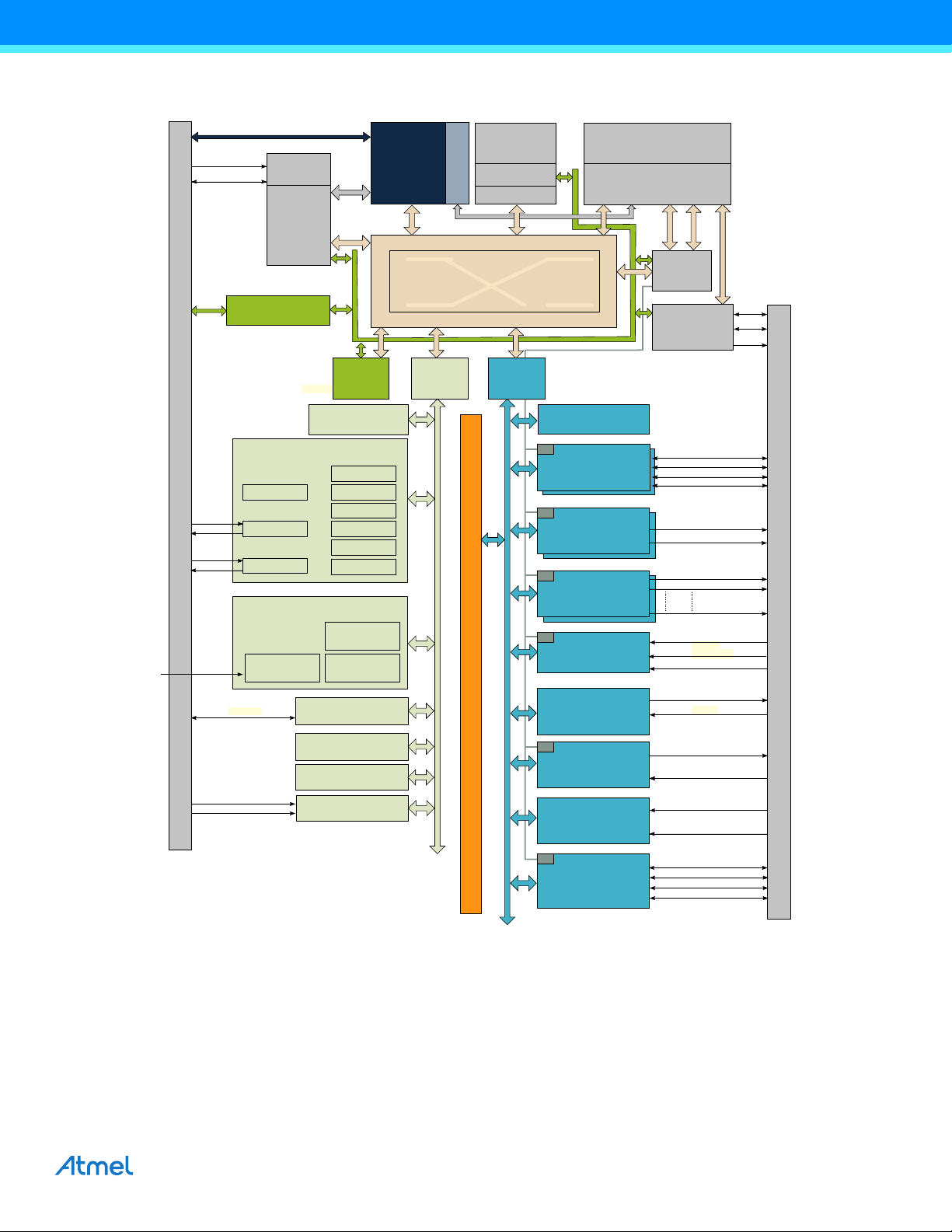

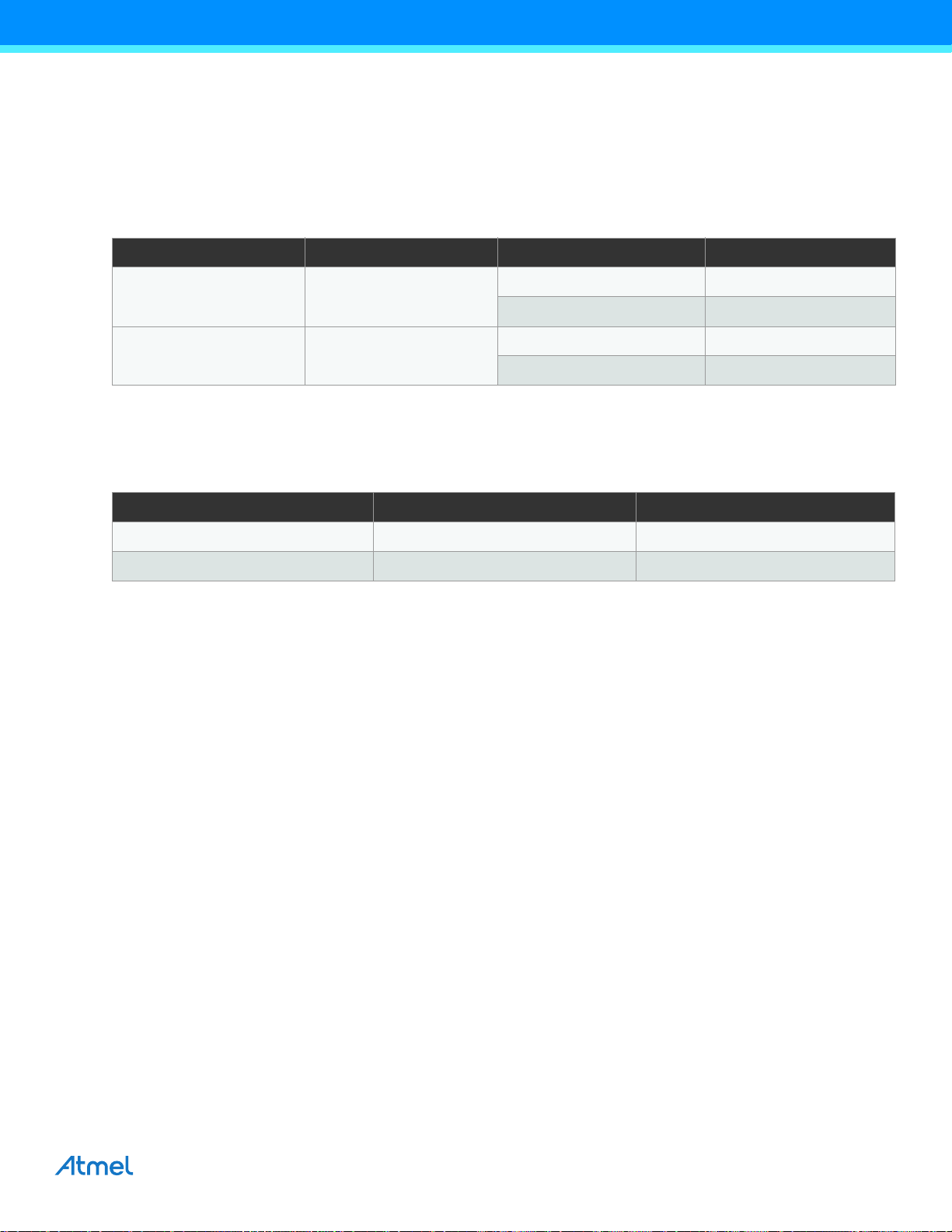

3. Block Diagram

6 x SERCOM

8 x Timer Counter

REAL TIME

COUNTER

AHB-APB

BRIDGE C

M

M

HIGH SPEED

BUS MATRIX

PORT

PORT

WATCHDOG

TIMER

SERIAL

WIRE

SWDIO

S

CORTEX-M0+

PROCESSOR

Fmax 48 MHz

SWCLK

DEVICE

SERVICE

UNIT

AHB-APB

BRIDGE A

20-CHANNEL

12-bit ADC 350KSPS

AIN[19..0]

VREFA

AIN[3..0]

S

SRAM

CONTROLLER

32/16/8/4KB

RAM

M

RESET

CONTROLLER

SLEEP

CONTROLLER

CLOCK

CONTROLLER

POWER MANAGER

RESETN

5 x TIMER / COUNTER

EVENT SYSTEM

S

6 x SERCOM

2 ANALOG

COMPARATORS

SYSTEM CONTROLLER

XOUT

XIN

XOUT32

XIN32

OSCULP32K

OSC32K

OSC8M

DFLL48M

BOD33

XOSC32K

XOSC

VREF

X[15..0]

Y[15..0]

PERIPHERAL

TOUCH

CONTROLLER

PERIPHERAL

ACCESS CONTROLLER

AHB-APB

BRIDGE B

VREFA

VOUT

10-bit DAC

EXTERNAL INTERRUPT

CONTROLLER

PERIPHERAL

ACCESS CONTROLLER

PERIPHERAL

ACCESS CONTROLLER

EXTINT[15..0]

NMI

GCLK_IO[7..0]

S

PAD0

WO1

PAD1

PAD2

PAD3

WO0

VREFB

256/128/64/32KB

NVM

NVM

CONTROLLER

Cache

S

DMA

USB FS

DEVICE

MINI-HOST

DP

DM

3x TIMER / COUNTER

FOR CONTROL

WOn

IOBUS

FDPLL96M

DMA

DMA

DMA

DMA

DMA

MCK[1..0]

SCK[1..0]

INTER-IC

SOUND

CONTROLLER

SD[1..0]

FS[1..0]

DMA

MICRO

TRACE BUFFER

SOF 1KHZ

WO0

WO1

(2)

GENERIC CLOCK

CONTROLLER

CMP[1..0]

1. Some products have different number of SERCOM instances, Timer/Counter instances, PTC signals and ADC sig-

2. The three TCC instances have different configurations, including the number of Waveform Output (WO) lines. Refer

nals. Refer to “Peripherals Configuration Summary” on page 48 for details.

to Table 30-1 on page 651 for details.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

12

Page 13

4. Pinout

PA00

1

PA01

2

PA02

3

PA03

4

PB04

5

PB05

6

GNDANA

7

VDDANA

8

PB06

9

PB07

10

PB08

11

PB09

12

PA04

13

PA05

14

PA06

15

PA07

16

PA08

17

PA09

18

PA10

19

PA11

20

VDDIO

21

GND

22

PB10

23

PB11

24

PB12

25

PB13

26

PB14

27

PB15

28

PA12

29

PA13

30

PA14

31

PA15

32

VDDIO48

GND47

PA2546

PA2445

PA2344

PA2243

PA2142

PA2041

PB1740

PB1639

PA1938

PA1837

PA1736

PA1635

VDDIO34

GND33

PB22

49

PB23

50

PA27

51

RESETN

52

PA28

53

GND

54

VDDCORE

55

VDDIN

56

PA30

57

PA31

58

PB30

59

PB31

60

PB00

61

PB01

62

PB02

63

PB03

64

DIGITAL PIN

ANALOG PIN

OSCILLATOR

GROUND

INPUT SUPPLY

REGULATED OUTPUT SUPPLY

RESET PIN

4.1 SAM D21J

4.1.1 QFN64 / TQFP64

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

13

Page 14

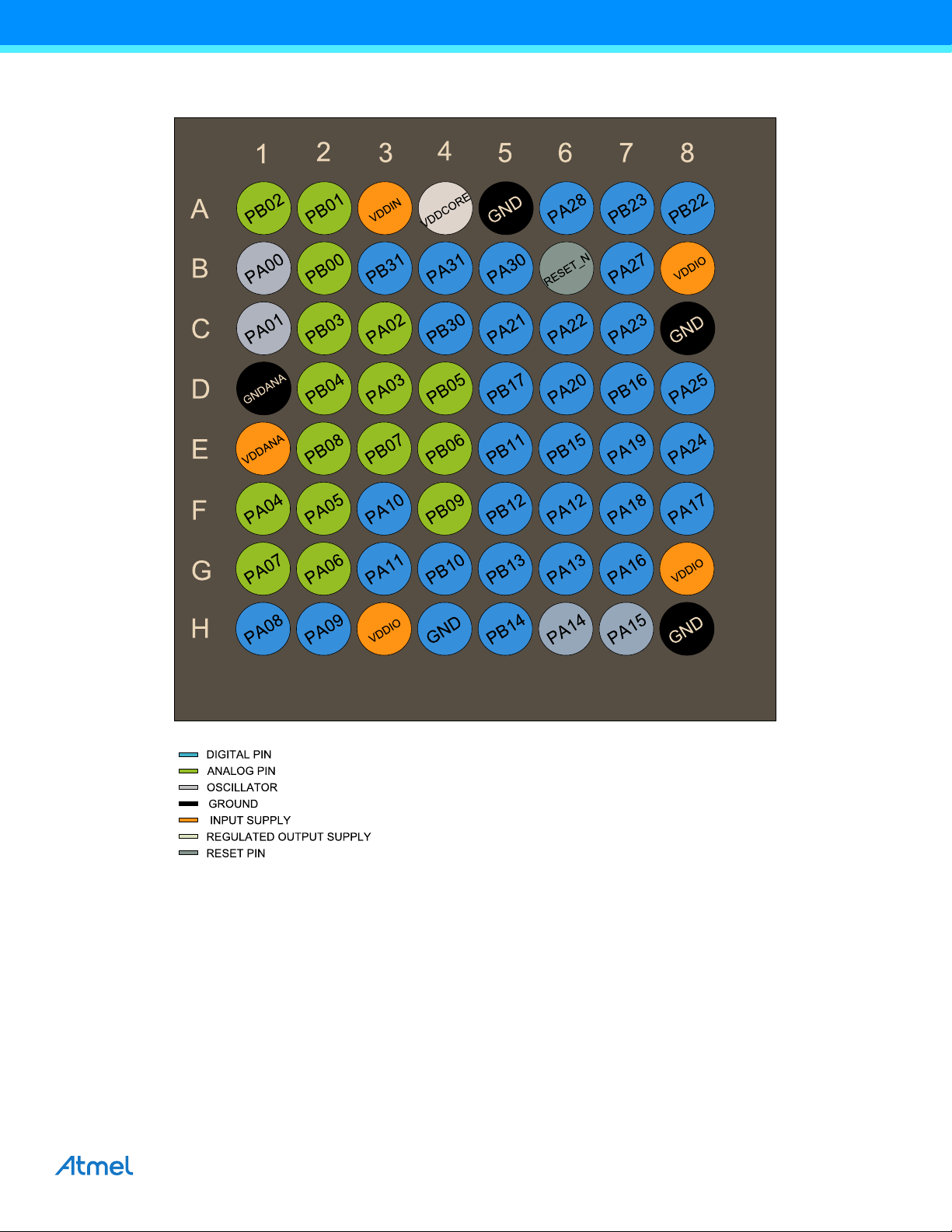

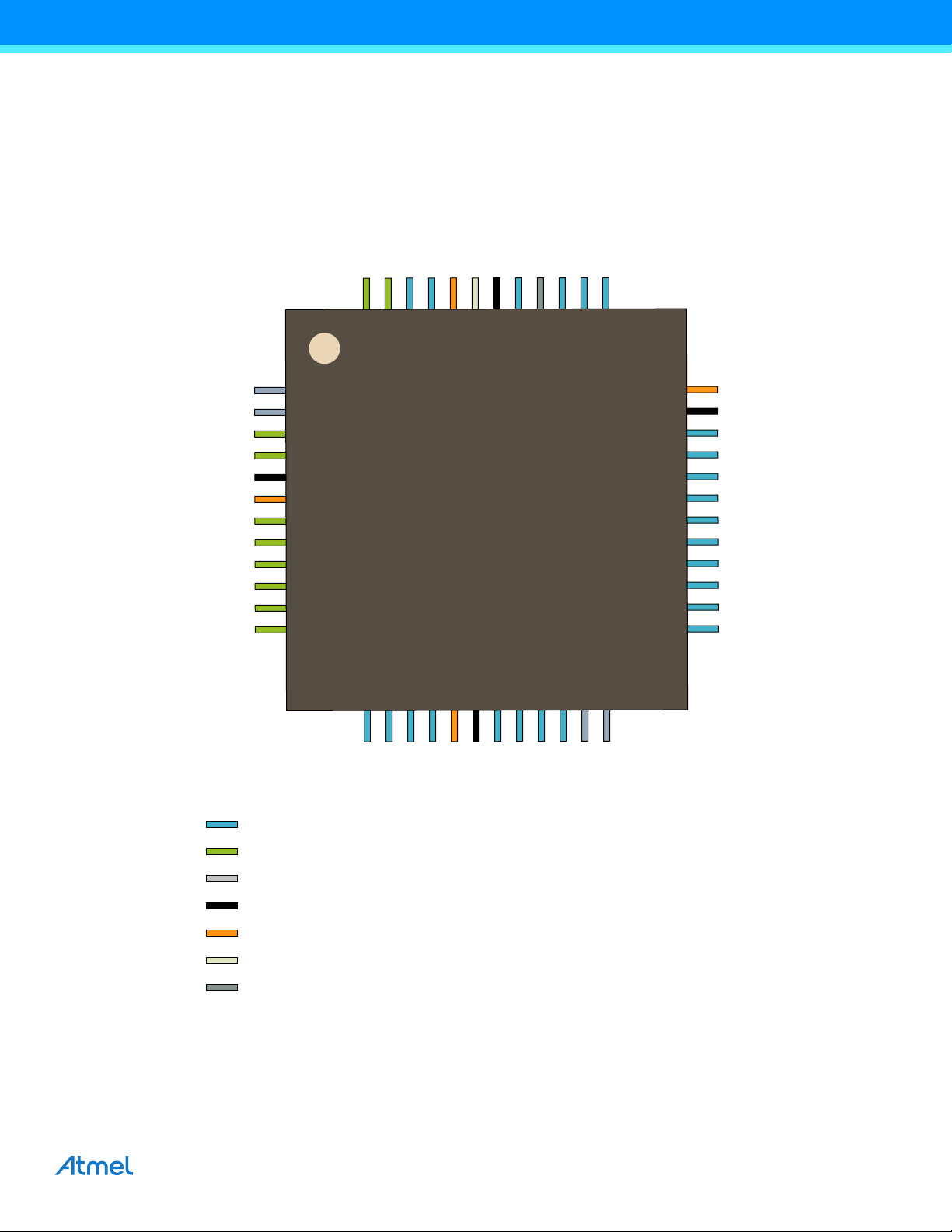

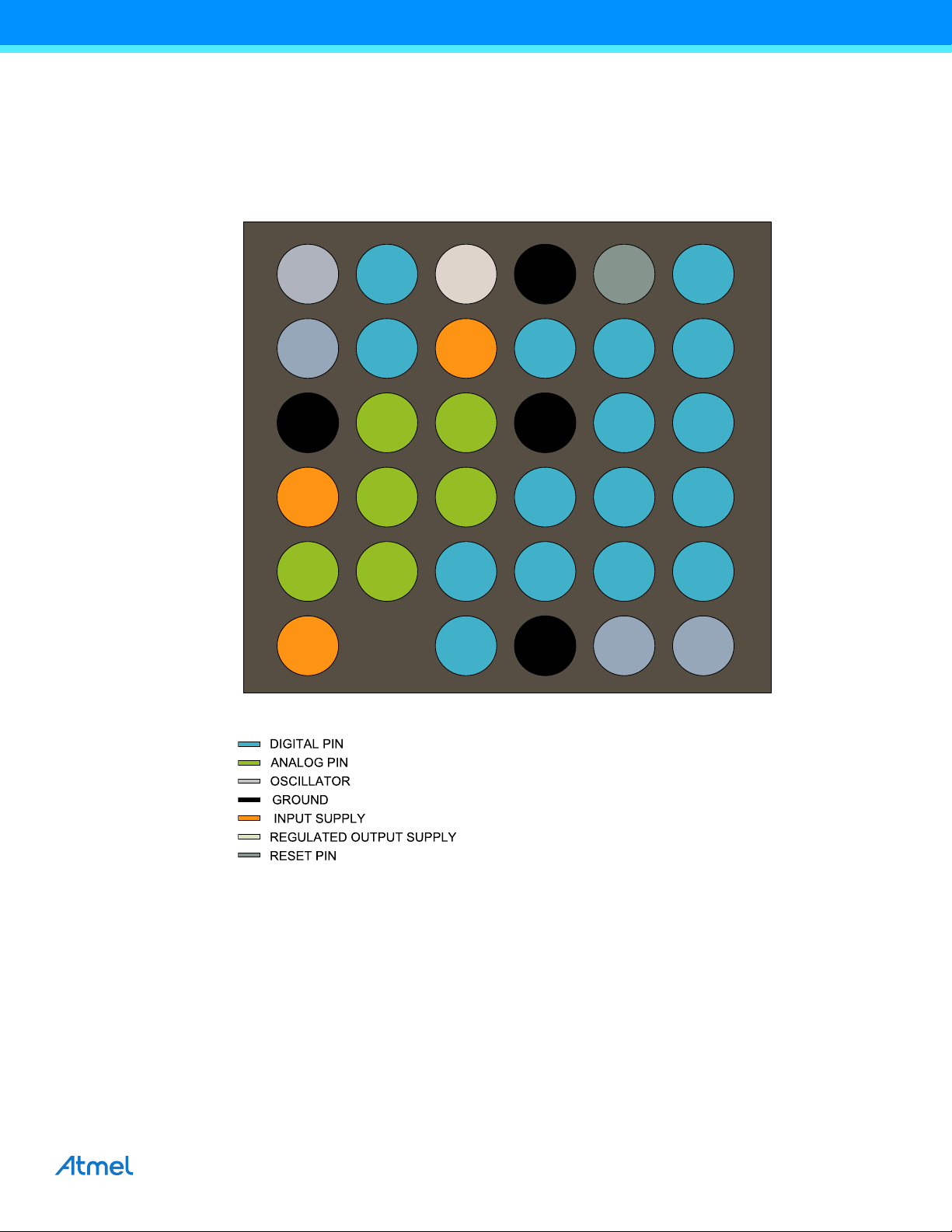

4.1.2 UFBGA64

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

14

Page 15

4.2 SAM D21G

PA21

PA00

1

PA01

2

PA02

3

PA03

4

GNDANA

5

VDDANA

6

PB08

7

PB09

8

PA04

9

PA05

10

PA06

11

PA07

12

PA08

13

PA09

14

PA10

15

PA11

16

VDDIO

17

GND

18

PB10

19

PB11

20

PA12 21

PA13

22

PA14

23

PA15

24

VDDIO36

GND35

PA2534

PA2433

PA2332

PA2231

30

PA2029

PA1928

PA1827

PA1726

PA1625

PB22

37

PB23

38

PA27

39

RESETN

40

PA28

41

GND

42

VDDCORE

43

VDDIN

44

PA30

45

PA31

46

PB02

47

PB03

48

DIGITAL PIN

ANALOG PIN

OSCILLATOR

GROUND

INPUT SUPPLY

REGULATED OUTPUT SUPPLY

RESET PIN

4.2.1 QFN48 / TQFP48

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

15

Page 16

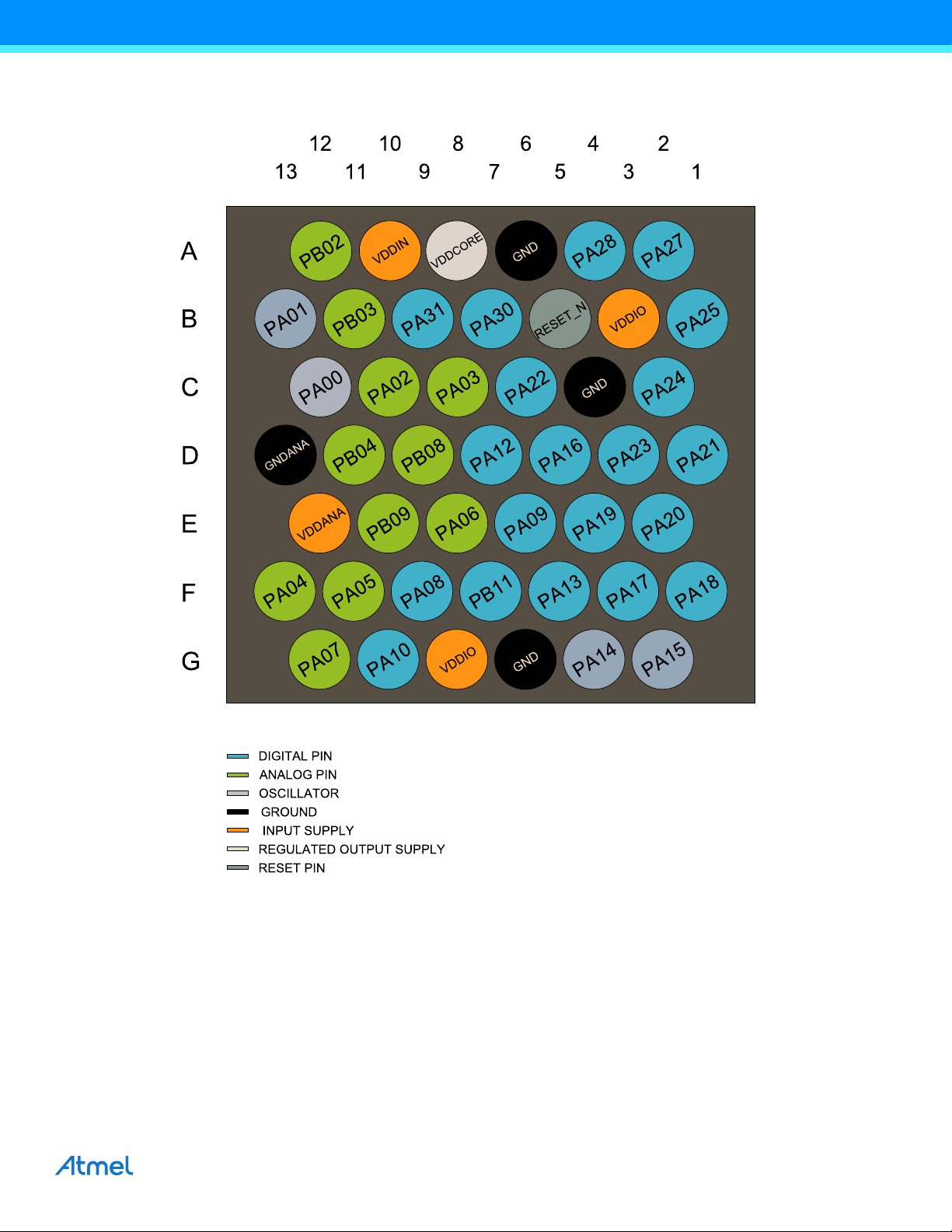

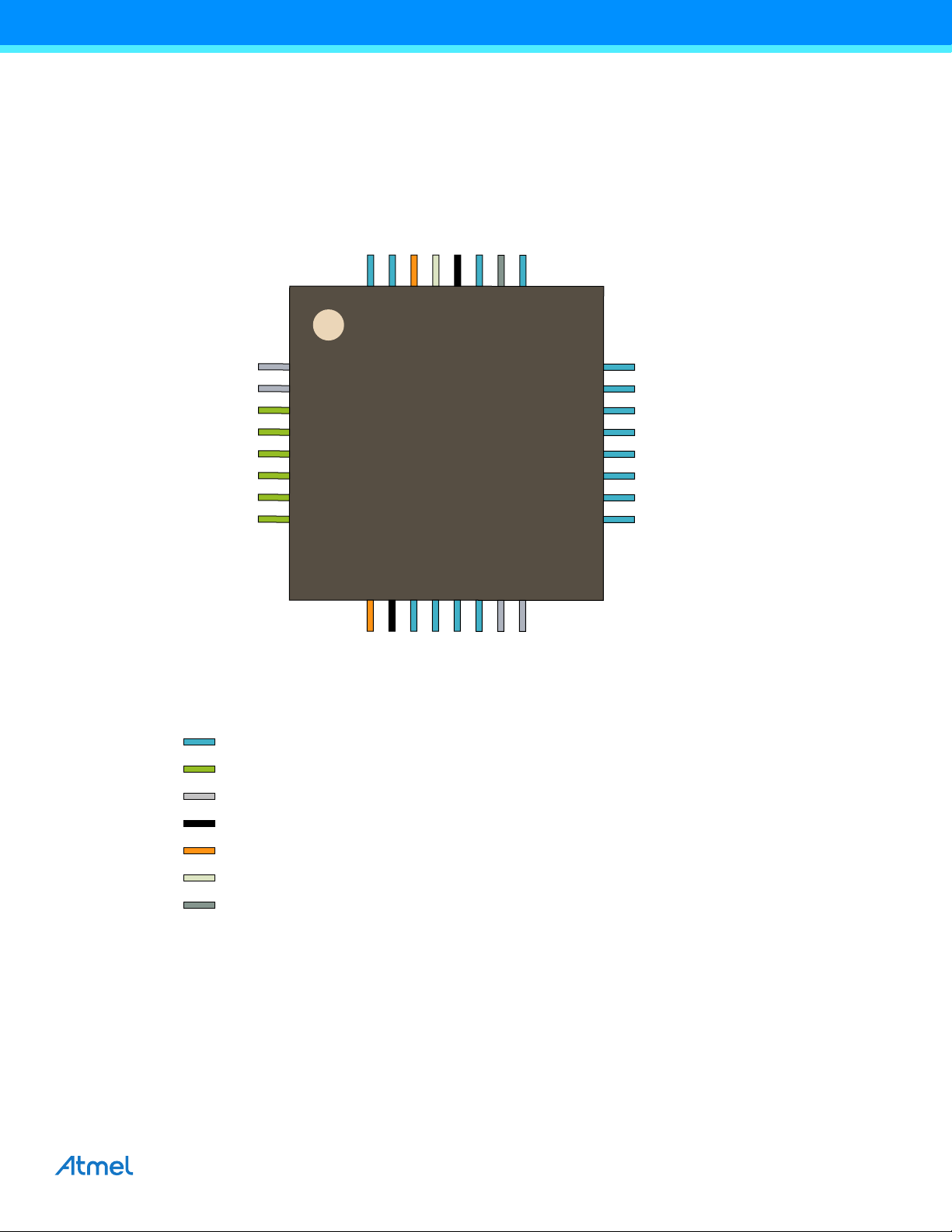

4.2.2 WLCSP45

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

16

Page 17

4.3 SAM D21E

PA00

1

PA01

2

PA02

3

PA03

4

PA04

5

PA05

6

PA06

7

PA07

8

VDDANA

9

GND

10

PA08

11

PA09

12

PA10

13

PA11

14

PA14

15

PA15

16

PA25

24

PA24

23

PA23

22

PA22

21

PA19

20

PA18

19

PA17

18

PA16

17

PA27

25

RESETN

26

PA28

27

GND

28

VDDCORE

29

VDDIN

30

PA30

31

PA31

32

DIGITAL PIN

ANALOG PIN

OSCILLATOR

GROUND

INPUT SUPPLY

REGULATED OUTPUT SUPPLY

RESET PIN

4.3.1 QFN32 / TQFP32

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

17

Page 18

4.3.2 WLCSP35

PA00

PA01

GNDANA

VDDANA

PA06

VDDIO

PA15

PA18

PA19

PA23

PA24

PA25

PA14

PA16

PA17

PA22

PA27

RESET_N

PA03

PA05

PA10

PA08

VDDIN

VDDCORE

PA02

PA04

PA07

PA31

PA30

PA11

PA09

PA28

GND

GND

GND

1

2

3

4

5

6

ABCDEF

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

18

Page 19

5. Signal Descriptions List

The following table gives details on signal names classified by peripheral.

Signal Name Function Type Active Level

Analog Comparators - AC

AIN[3:0] AC Analog Inputs Analog

CMP[:0] AC Comparator Outputs Digital

Analog Digital Converter - ADC

AIN[19:0] ADC Analog Inputs Analog

VREFA ADC Voltage External Reference A Analog

VREFB ADC Voltage External Reference B Analog

Digital Analog Converter - DAC

VOUT DAC Voltage output Analog

VREFA DAC Voltage External Reference Analog

External Interrupt Controller

EXTINT[15:0] External Interrupts Input

NMI External Non-Maskable Interrupt Input

Generic Clock Generator - GCLK

GCLK_IO[7:0] Generic Clock (source clock or generic clock generator output) I/O

Inter-IC Sound Controller - I2S

MCK[1..0] Master Clock I/O

SCK[1..0] Serial Clock I/O

FS[1..0] I2S Word Select or TDM Frame Sync I/O

SD[1..0] Serial Data Input or Output I/O

Power Manager - PM

RESETN Reset Input Low

Serial Communication Interface - SERCOMx

PAD[3:0] SERCOM I/O Pads I/O

System Control - SYSCTRL

XIN Crystal Input Analog/ Digital

XIN32 32kHz Crystal Input Analog/ Digital

XOUT Crystal Output Analog

XOUT32 32kHz Crystal Output Analog

Timer Counter - TCx

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

19

Page 20

Signal Name Function Type Active Level

WO[1:0] Waveform Outputs Output

Timer Counter - TCCx

WO[1:0] Waveform Outputs Output

Peripheral Touch Controller - PTC

X[15:0] PTC Input Analog

Y[15:0] PTC Input Analog

General Purpose I/O - PORT

PA25 - PA00 Parallel I/O Controller I/O Port A I/O

PA28 - PA27 Parallel I/O Controller I/O Port A I/O

PA31 - PA30 Parallel I/O Controller I/O Port A I/O

PB17 - PB00 Parallel I/O Controller I/O Port B I/O

PB23 - PB22 Parallel I/O Controller I/O Port B I/O

PB31 - PB30 Parallel I/O Controller I/O Port B I/O

Universal Serial Bus - USB

DP DP for USB I/O

DM DM for USB I/O

SOF 1kHz USB Start of Frame I/O

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

20

Page 21

Atmel-42181G–SAM-D21_Datasheet–09/2015

[DATASHEET]

21

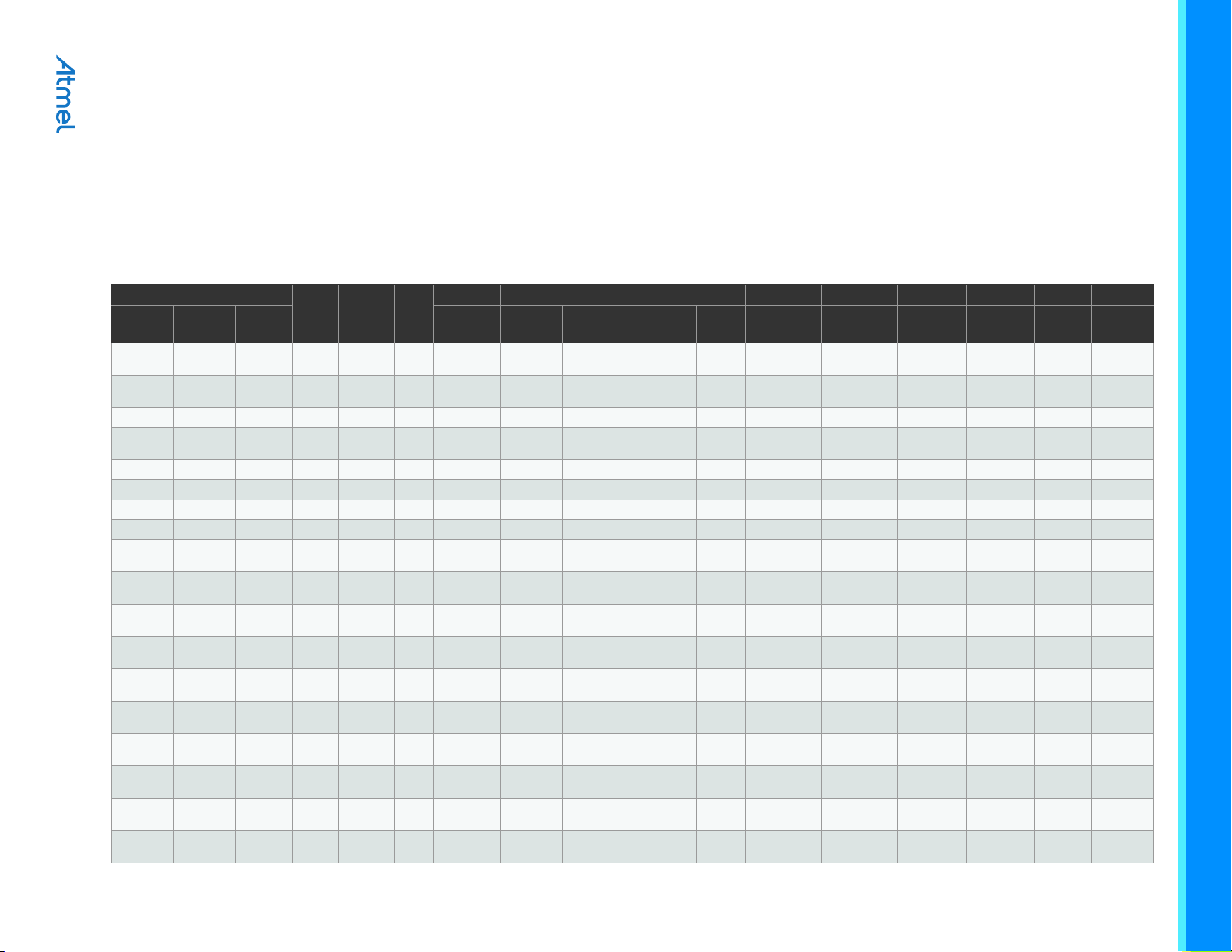

6. I/O Multiplexing and Considerations

6.1 Multiplexed Signals

Each pin is by default controlled by the PORT as a general purpose I/O and alternatively it can be assigned to one of the peripheral functions A, B, C,

D, E, F, G or H. To enable a peripheral function on a pin, the Peripheral Multiplexer Enable bit in the Pin Configuration register corresponding to that pin

(PINCFGn.PMUXEN, n = 0-31) in the PORT must be written to one. The selection of peripheral function A to H is done by writing to the Peripheral

Multiplexing Odd and Even bits in the Peripheral Multiplexing register (PMUXn.PMUXE/O) in the PORT.

Table 5-1 on page 11 describes the peripheral signals multiplexed to the PORT I/O pins.

Table 6-1. PORT Function Multiplexing

(1)

Pin

SAMD21E SAMD21GSAMD21J EIC REF ADC AC PTC DAC SERCOM

1 1 1 PA0 0 VDDANA EXTINT[0]

2 2 2 PA0 1 VDDANA EXTINT[1]

3 3 3 PA02 VDDANA EXTINT[2] AIN[0] Y[0] VOUT

4 4 4 PA03 VDDANA EXTINT[3]

7 11 PB08 VDDANA EXTINT[8] AIN[2] Y[14]

8 12 PB09 VDDANA EXTINT[9] AIN[3] Y[15]

5 9 13 PA0 4 VDDANA EXTINT[4]

6 10 14 PA 05 VDDANA EXTINT[5] AIN[5] AIN[1] Y[3]

7 11 15 PA 06 VDDANA EXTINT[6] AIN[6] AIN[2] Y[4]

8 12 16 PA 07 VDDANA EXTINT[7] AIN[7] AIN[3] Y[5]

11 13 17 PA 08 VDDIO I2C NMI AIN[16] X[0]

12 14 18 PA0 9 VDDIO I2C EXTINT[9] AIN[17] X[1]

13 15 19 PA1 0 VDDIO EXTINT[10] AIN[18] X[2]

14 16 20 PA11 VDDIO EXTINT[11] AIN[19] X[3]

I/O Pin Supply Typ e

5 PB04 VDDANA EXTINT[4] AIN[12] Y[10]

6 PB05 VDDANA EXTINT[5] AIN[13] Y[11]

9 PB06 VDDANA EXTINT[6] AIN[14] Y[12]

10 PB07 VDDANA EXTINT[7] AIN[15] Y[13]

A B

ADC/VREFA

DAC/VREFA

ADC/VREFB

(2)(3)

AIN[1] Y[1]

AIN[4] AIN[0] Y[2]

C D E F G H

SERCOM0/

PAD [0]

SERCOM0/

PAD [1]

SERCOM0/

PAD [2]

SERCOM0/

PAD [3]

(2)(3)

SERCOM-

ALT

SERCOM1/

PAD [0]

SERCOM1/

PAD [1]

SERCOM4/

PAD [0]

SERCOM4/

PAD [1]

SERCOM0/

PAD [0]

SERCOM0/

PAD [1]

SERCOM0/

PAD [2]

SERCOM0/

PAD [3]

SERCOM2/

PAD [0]

SERCOM2/

PAD [1]

SERCOM2/

PAD [2]

SERCOM2/

PAD [3]

(4)

TC

/TCC TCC COM AC/GCLK

TCC2/WO[0]

TCC2/WO[1]

TC4/WO[0]

TC4/WO[1]

TCC0/WO[0]

TCC0/WO[1]

TCC1/WO[0]

TCC1/WO[1] I2S/SD[0]

TCC0/WO[0]

TCC0/WO[1]

TCC1/WO[0]

TCC1/WO[1]

TCC1/

WO[2]

TCC1/

WO[3]

TCC0/

WO[2]

TCC0/

WO[3]

I2S/SD[1]

I2S/

MCK[0]

I2S/

SCK[0]

I2S/FS[0] GCLK_IO[5]

GCLK_IO[4]

Page 22

Atmel-42181G–SAM-D21_Datasheet–09/2015

[DATASHEET]

22

Table 6-1. PORT Function Multiplexing (Continued)

(1)

Pin

SAMD21E SAMD21GSAMD21J EIC REF ADC AC PTC DAC SERCOM

19 23 PB10 VDDIO EXTINT[10]

20 24 PB11 VDDIO EXTINT[11]

21 29 PA 12 VDDIO I2C EXTINT[12]

22 30 PA 13 VDDIO I2C EXTINT[13]

15 23 31 PA1 4 VDDIO EXTINT[14]

16 24 32 PA1 5 VDDIO EXTINT[15]

17 25 35 PA1 6 VDDIO I2C EXTINT[0] X[4]

18 26 36 PA1 7 VDDIO I2C EXTINT[1] X[5]

19 27 37 PA1 8 VDDIO EXTINT[2] X[6]

20 28 38 PA1 9 VDDIO EXTINT[3] X[7]

29 41 PA 20 VDDIO EXTINT[4] X[8]

30 42 PA 21 VDDIO EXTINT[5] X[9]

21 31 43 PA2 2 VDDIO I2C EXTINT[6] X[10]

22 32 44 PA2 3 VDDIO I2C EXTINT[7] X[11]

23 33 45 PA2 4 VDDIO EXTINT[12]

24 34 46 PA2 5 VDDIO EXTINT[13]

I/O Pin Supply Typ e

25 PB12 VDDIO I2C EXTINT[12] X[12]

26 PB13 VDDIO I2C EXTINT[13] X[13]

27 PB14 VDDIO EXTINT[14] X[14]

28 PB15 VDDIO EXTINT[15] X[15]

39 PB16 VDDIO I2C EXTINT[0]

40 PB17 VDDIO I2C EXTINT[1]

A B

(2)(3)

C D E F G H

SERCOM4/

PAD [0]

SERCOM4/

PAD [1]

SERCOM4/

PAD [2]

SERCOM4/

PAD [3]

SERCOM2/

PAD [0]

SERCOM2/

PAD [1]

SERCOM2/

PAD [2]

SERCOM2/

PAD [3]

SERCOM1/

PAD [0]

SERCOM1/

PAD [1]

SERCOM1/

PAD [2]

SERCOM1/

PAD [3]

SERCOM5/

PAD [0]

SERCOM5/

PAD [1]

SERCOM5/

PAD [2]

SERCOM5/

PAD [3]

SERCOM3/

PAD [0]

SERCOM3/

PAD [1]

SERCOM3/

PAD [2]

SERCOM3/

PAD [3]

(2)(3)

SERCOM-

ALT

SERCOM4/

PAD [2]

SERCOM4/

PAD [3]

SERCOM4/

PAD [0]

SERCOM4/

PAD [1]

SERCOM4/

PAD [2]

SERCOM4/

PAD [3]

SERCOM3/

PAD [0]

SERCOM3/

PAD [1]

SERCOM3/

PAD [2]

SERCOM3/

PAD [3]

SERCOM3/

PAD [2]

SERCOM3/

PAD [3]

SERCOM5/

PAD [0]

SERCOM5/

PAD [1]

SERCOM5/

PAD [2]

SERCOM5/

PAD [3]

(4)

TC

/TCC TCC COM AC/GCLK

TC5/WO[0]

TC5/WO[1]

TC4/WO[0]

TC4/WO[1]

TC5/WO[0] GCLK_IO[0]

TC5/WO[1] GCLK_IO[1]

TCC2/WO[0]

TCC2/WO[1]

TC3/WO[0]

TC3/WO[1]

TCC2/WO[0] TCC0/WO[6] GCLK_IO[2]

TCC2/WO[1] TCC0/WO[7] GCLK_IO[3]

TC3/WO[0]

TC3/WO[1]

TC6/WO[0]

TC6/WO[1]

TC7/WO[0]

TC7/WO[1]

TC4/WO[0]

TC4/WO[1]

TC5/WO[0]

TC5/WO[1]

TCC0/

WO[4]

TCC0/

WO[5]

TCC0/

WO[6]

TCC0/

WO[7]

TCC0/

WO[6]

TCC0/

WO[7]

TCC0/

WO[4]

TCC0/

WO[5]

TCC0/

WO[2]

TCC0/

WO[3]

TCC0/

WO[4]

TCC0/

WO[5]

TCC0/

WO[6]

TCC0/

WO[7]

TCC0/

WO[4]

TCC0/

WO[5]

TCC1/

WO[2]

TCC1/

WO[3]

I2S/

I2S/

I2S/

I2S/

1kHz

GCLK_IO[4]

GCLK_IO[5]

GCLK_IO[7]

AC/CMP[0]

AC/CMP[1]

GCLK_IO[0]

GCLK_IO[1]

AC/CMP[0]

GCLK_IO[3]

GCLK_IO[4]

GCLK_IO[6]

GCLK_IO[7]

MCK[1]

SCK[1]

I2S/FS[1] GCLK_IO[6]

I2S/SD[0] AC/CMP[1]

I2S/SD[1] GCLK_IO[2]

MCK[0]

SCK[0]

I2S/FS[0] GCLK_IO[5]

USB/SOF

USB/DM

USB/DP

Page 23

Table 6-1. PORT Function Multiplexing (Continued)

(1)

Pin

SAMD21E SAMD21GSAMD21J EIC REF ADC AC PTC DAC SERCOM

37 49 PB22 VDDIO EXTINT[6]

38 50 PB23 VDDIO EXTINT[7]

25 39 51 PA2 7 VDDIO EXTINT[15] GCLK_IO[0]

27 41 53 PA2 8 VDDIO EXTINT[8] GCLK_IO[0]

31 45 57 PA3 0 VDDIO EXTINT[10]

32 46 58 PA3 1 VDDIO EXTINT[11]

47 63 PB02 VDDANA EXTINT[2] AIN[10] Y[8]

48 64 PB03 VDDANA EXTINT[3] AIN[11] Y[9]

Notes: 1. Use the SAMD21J pinout muxing for WLCSP45 package.

2. All analog pin functions are on peripheral function B. Peripheral function B must be selected to disable the digital control of the pin.

3. Only some pins can be used in SERCOM I

characteristics.

4. Note that TC6 and TC7 are not supported on the SAM D21E and G devices. Refer to “Configuration Summary” on page 3 for details.

5. This function is only activated in the presence of a debugger.

I/O Pin Supply Typ e

59 PB30 VDDIO I2C EXTINT[14]

60 PB31 VDDIO I2C EXTINT[15]

61 PB00 VDDANA EXTINT[0] AIN[8] Y[6]

62 PB01 VDDANA EXTINT[1] AIN[9] Y[7]

2

C mode. See the Type column for using a SERCOM pin in I2C mode. Refer to “Electrical Characteristics” on page 935 for details on the I2C pin

A B

(2)(3)

C D E F G H

SERCOM-

(2)(3)

ALT

SERCOM5/

PAD [2]

SERCOM5/

PAD [3]

SERCOM1/

PAD [2]

SERCOM1/

PAD [3]

SERCOM5/

PAD [0]

SERCOM5/

PAD [1]

SERCOM5/

PAD [2]

SERCOM5/

PAD [3]

SERCOM5/

PAD [0]

SERCOM5/

PAD [1]

(4)

TC

/TCC TCC COM AC/GCLK

TC7/WO[0] GCLK_IO[0]

TC7/WO[1] GCLK_IO[1]

TCC1/WO[0] SWCLK GCLK_IO[0]

TCC1/WO[1] SWDIO

TCC0/WO[0]

TCC0/WO[1]

TC7/WO[0]

TC7/WO[1]

TC6/WO[0]

TC6/WO[1]

TCC1/

WO[2]

TCC1/

WO[3]

(5)

Atmel-42181G–SAM-D21_Datasheet–09/2015

[DATASHEET]

23

Page 24

6.2 Other Functions

6.2.1 Oscillator Pinout

The oscillators are not mapped to the normal PORT functions and their multiplexing are controlled by registers in the

System Controller (SYSCTRL).

Oscillator Supply Signal I/O Pin

XOSC VDDIO

XOSC32K VDDANA

6.2.2 Serial Wire Debug Interface Pinout

Only the SWCLK pin is mapped to the normal PORT functions. A debugger cold-plugging or hot-plugging detection will

automatically switch the SWDIO port to the SWDIO function.

Signal Supply I/O Pin

SWCLK VDDIO PA30

SWDIO VDDIO PA31

XIN PA1 4

XOUT PA1 5

XIN32 PA0 0

XOUT32 PA01

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

24

Page 25

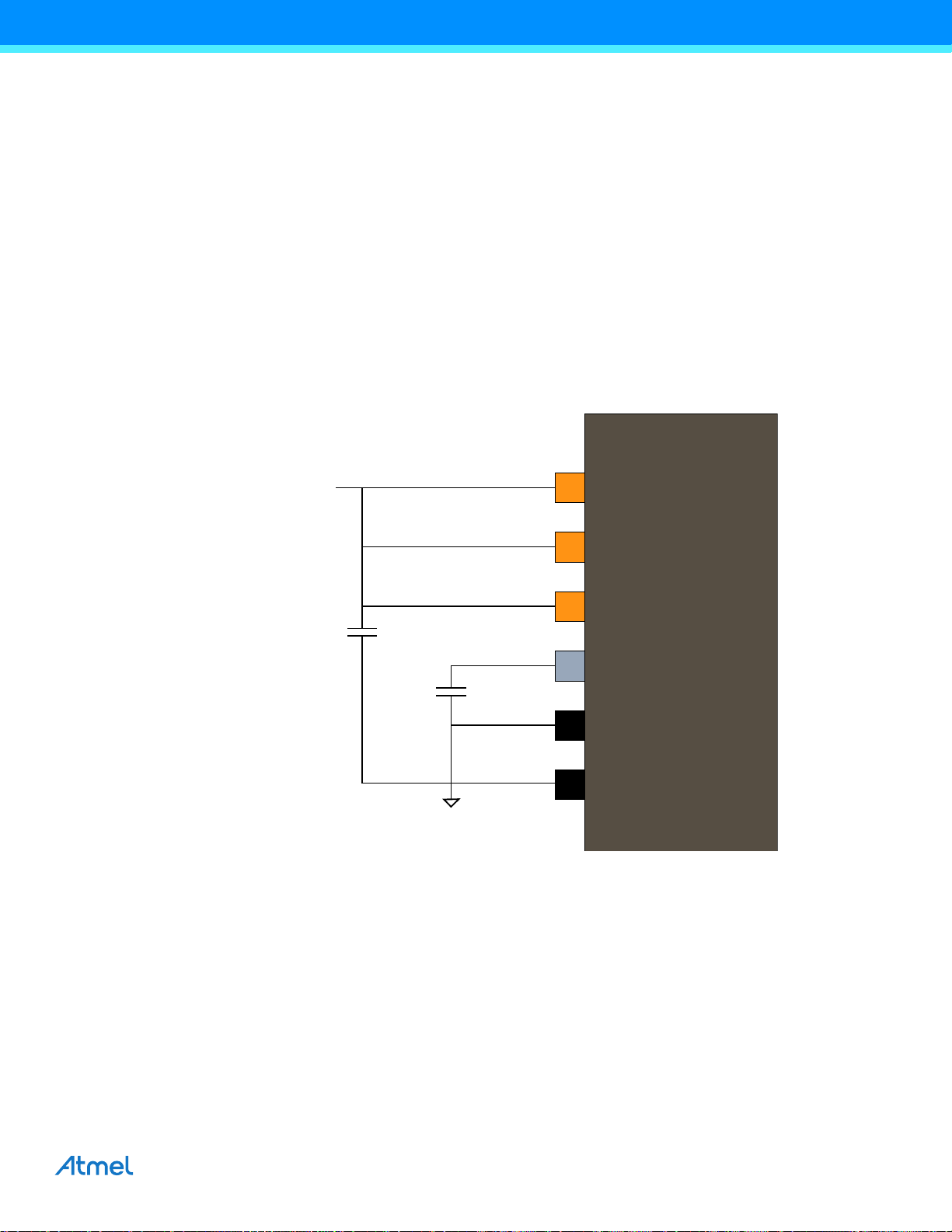

7. Power Supply and Start-Up Considerations

VOLTAGE

REGULATOR

VDDIN

VDDCORE

GND

ADC

AC

DAC

PTC

XOSC32K

OSC32K

VDDANA

GNDANA

PA[7:2]

PB[9:0]

PA[1:0]

Digital Logic

(CPU, peripherals)

DFLL48M

VDDIO

OSC8M

XOSC

OSCULP32K

PA[31:16]

PB[31:10]

PA[15:14]

BOD33

POR

PA[13:8]

BOD12

FDPLL96M

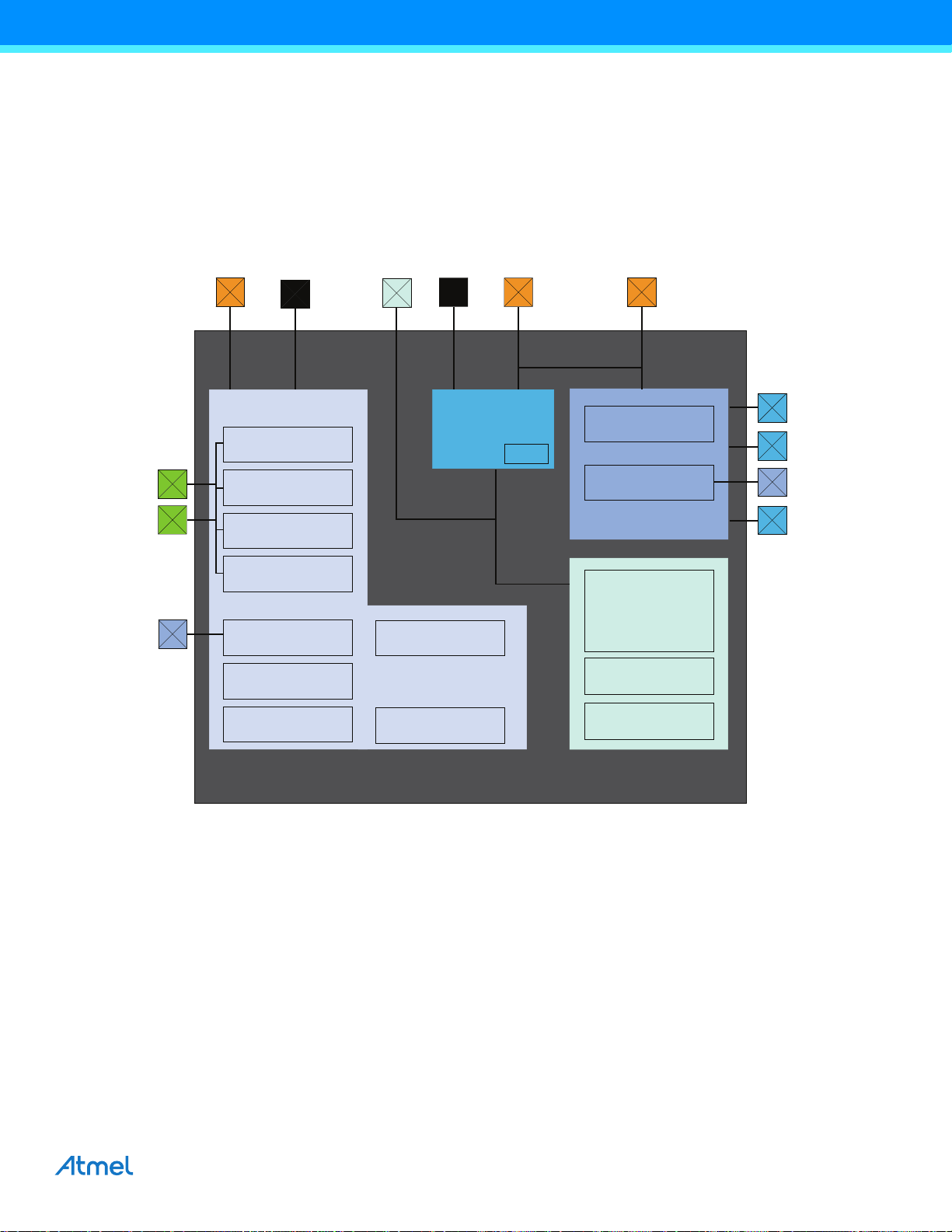

7.1 Power Domain Overview

7.2 Power Supply Considerations

7.2.1 Power Supplies

The Atmel® SAM D21 has several different power supply pins:

z VDDIO: Powers I/O lines, OSC8M and XOSC. Voltage is 1.62V to 3.63V.

z VDDIN: Powers I/O lines and the internal regulator. Voltage is 1.62V to 3.63V.

z VDDANA: Powers I/O lines and the ADC, AC, DAC, PTC, OSCULP32K, OSC32K, XOSC32K. Voltage is 1.62V to

3.63V.

z VDDCORE: Internal regulated voltage output. Powers the core, memories, peripherals, DFLL48M and

FDPLL96M. Voltage is 1.2V.

The same voltage must be applied to both VDDIN, VDDIO and VDDANA. This common voltage is referred to as V

the datasheet.

DD

in

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

25

Page 26

The ground pins, GND, are common to VDDCORE, VDDIO and VDDIN. The ground pin for VDDANA is GNDANA.

(1.62V — 3.63V)

Main Supply

VDDIO

VDDANA

VDDIN

VDDCORE

GND

GNDANA

SAM D21

For decoupling recommendations for the different power supplies, refer to the schematic checklist.

Refer to “Schematic Checklist” on page 1008 for details.

7.2.2 Voltage Regulator

The SAM D21 voltage regulator has two different modes:

z Normal mode: To be used when the CPU and peripherals are running

z Low Power (LP) mode: To be used when the regulator draws small static current. It can be used in standby mode

7.2.3 Typical Powering Schematics

The SAM D21 uses a single supply from 1.62V to 3.63V.

The following figure shows the recommended power supply connection.

Figure 7-1. Power Supply Connection

7.2.4 Power-Up Sequence

7.2.4.1 Minimum Rise Rate

7.2.4.2 Maximum Rise Rate

The integrated power-on reset (POR) circuitry monitoring the VDDANA power supply requires a minimum rise rate. Refer

to the “Electrical Characteristics” on page 935 for details.

The rise rate of the power supply must not exceed the values described in Electrical Characteristics. Refer to the

“Electrical Characteristics” on page 935 for details.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

26

Page 27

7.3 Power-Up

This section summarizes the power-up sequence of the SAM D21. The behavior after power-up is controlled by the

Power Manager. Refer to “PM – Power Manager” on page 117 for details.

7.3.1 Starting of Clocks

After power-up, the device is set to its initial state and kept in reset, until the power has stabilized throughout the device.

Once the power has stabilized, the device will use a 1MHz clock. This clock is derived from the 8MHz Internal Oscillator

(OSC8M), which is divided by eight and used as a clock source for generic clock generator 0. Generic clock generator 0

is the main clock for the Power Manager (PM).

Some synchronous system clocks are active, allowing software execution.

Refer to the “Clock Mask Register” section in “PM – Power Manager” on page 117 for the list of default peripheral clocks

running. Synchronous system clocks that are running are by default not divided and receive a 1MHz clock through

generic clock generator 0. Other generic clocks are disabled except GCLK_WDT, which is used by the Watchdog Timer

(WDT).

7.3.2 I/O Pins

After power-up, the I/O pins are tri-stated.

7.3.3 Fetching of Initial Instructions

After reset has been released, the CPU starts fetching PC and SP values from the reset address, which is 0x00000000.

This address points to the first executable address in the internal flash. The code read from the internal flash is free to

configure the clock system and clock sources. Refer to “PM – Power Manager” on page 117, “GCLK – Generic Clock

Controller” on page 95 and “SYSCTRL – System Controller” on page 148 for details. Refer to the ARM Architecture

Reference Manual for more information on CPU startup (http://www.arm.com).

7.4 Power-On Reset and Brown-Out Detector

The SAM D21 embeds three features to monitor, warn and/or reset the device:

z POR: Power-on reset on VDDANA

z BOD33: Brown-out detector on VDDANA

z BOD12: Voltage Regulator Internal Brown-out detector on VDDCORE. The Voltage Regulator Internal BOD is

calibrated in production and its calibration configuration is stored in the NVM User Row. This configuration should

not be changed if the user row is written to assure the correct behavior of the BOD12.

7.4.1 Power-On Reset on VDDANA

POR monitors VDDANA. It is always activated and monitors voltage at startup and also during all the sleep modes. If

VDDANA goes below the threshold voltage, the entire chip is reset.

7.4.2 Brown-Out Detector on VDDANA

BOD33 monitors VDDANA. Refer to “SYSCTRL – System Controller” on page 148 for details.

7.4.3 Brown-Out Detector on VDDCORE

Once the device has started up, BOD12 monitors the internal VDDCORE.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

27

Page 28

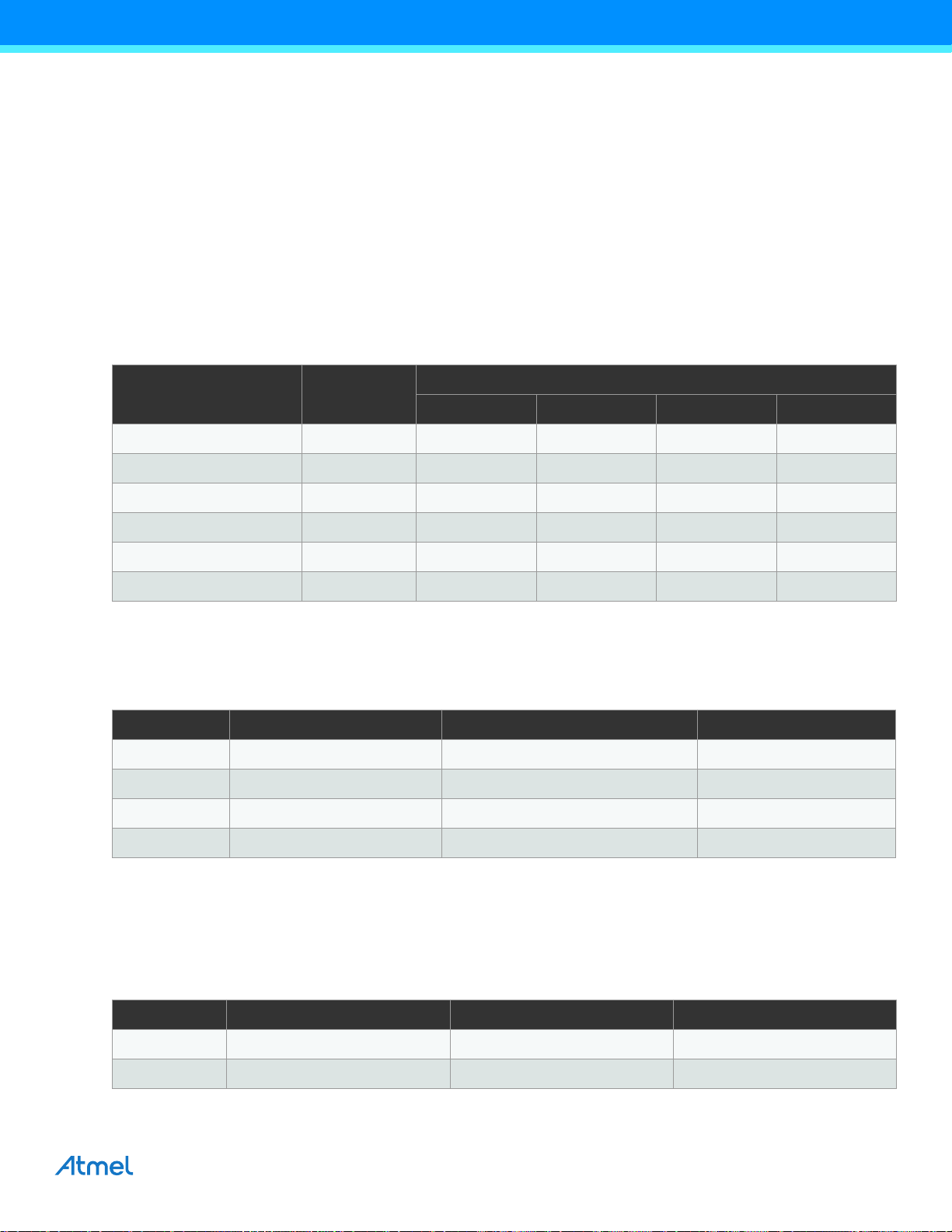

8. Product Mapping

Code

SRAM

Undefined

Peripherals

Reserved

Undefined

Global Memory Space

0x00000000

0x20000000

0x20008000

0x40000000

0x43000000

0x60000000

Internal SRAM

SRAM

AHB-APB

Bridge A

AHB-APB

Bridge B

AHB-APB

Bridge C

AHB-APB

Internal Flash

Reserved

Code

0x00000000

0x00040000

0x1FFFFFFF

0x20000000

0x20007FFF

0x40000000

0x41000000

0x42000000

0x42FFFFFF

Reserved

PAC0

PM

SYSCTRL

GCLK

WDT

RTC

EIC

AHB-APB Bridge A

0x40000000

0x40000400

0x40000800

0x40000C00

0x40001000

0x40001400

0x40001800

0x40FFFFFF

0x40001C00

AHB-APB Bridge B

Reserved

PAC1

DSU

NVMCTRL

PORT

0x41000000

0x41002000

0x41004000

0x41004400

0x41FFFFFF

0x41007000

SERCOM5

PAC2

EVSYS

SERCOM0

SERCOM1

SERCOM2

SERCOM3

SERCOM4

AHB-APB Bridge C

TC7

TCC0

TCC1

TCC2

TC3

TC4

TC5

TC6

ADC

AC

0x42000000

0x42000400

0x42000800

0x42000C00

0x42001000

0x42001400

0x42001800

0x42002000

0x42001C00

0x42003000

0x42003400

0x42003800

0x42003C00

0x42004000

0x42004400

0x42004800

Reserved

0x42FFFFFF

0x60000200

0xFFFFFFFF

Reserved

System

0xE0000000

DAC

0x42004C00

0x42002400

0x42002800

0x42002C00

PTC

0x42005400

0x42005000

I2S

DMAC

USB

MTB

0x41004800

0x41005000

0x41006000

0xE0000000

0xE000E000

0xE000F000

0xE00FF000

0xE0100000

0xFFFFFFFF

System

Reserved

SCS

Reserved

ROMTable

Reserved

Internal Flash

0x00000000

0x00400000

0x1FFFFFFF

Internal

RWW section

Device Variant A

Device Variant B

Figure 8-1. Atmel | SMART SAM D21 Product Mapping

This figure represents the full configuration of the Atmel® SAM D21 with maximum flash and SRAM capabilities and a full

set of peripherals. Refer to the “Configuration Summary” on page 3 for details.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

28

Page 29

9. Memories

9.1 Embedded Memories

z Internal high-speed flash with Read-While-Write (RWW) capability on section of the array (Device Variant B).

z Internal high-speed flash

z Internal high-speed RAM, single-cycle access at full speed

9.2 Physical Memory Map

The High-Speed bus is implemented as a bus matrix. All High-Speed bus addresses are fixed, and they are never

remapped in any way, even during boot. The 32-bit physical address space is mapped as follow:

Table 9-1. SAM D21 physical memory map

Memory Start address

Internal Flash 0x00000000 256Kbytes 128Kbytes 64Kbytes 32Kbytes

Internal RWW section

Internal SRAM 0x20000000 32Kbytes 16Kbytes 8Kbytes 4Kbytes

Peripheral Bridge A 0x40000000 64Kbytes 64Kbytes 64Kbytes 64Kbytes

Peripheral Bridge B 0x41000000 64Kbytes 64Kbytes 64Kbytes 64Kbytes

Peripheral Bridge C 0x42000000 64Kbytes 64Kbytes 64Kbytes 64Kbytes

(2)

0x00010000 - - 2Kbytes 1Kbytes

(1)

Size

SAMD21x18 SAMD21x17 SAMD21x16 SAMD21x15

Notes: 1. x = G, J or E. Refer to “Ordering Information” on page 5 for details.

2. Only applicable for Device Variant B.

Table 9-2. Flash memory parameters

Device Flash size Number of pages Page size

SAMD21x18 256Kbytes 4096 64 bytes

SAMD21x17 128Kbytes 2046 64 bytes

(1)

SAMD21x16 64Kbytes 1024 64 bytes

SAMD21x15 32Kbytes 512 64 bytes

Note: 1. x = G, J or E. Refer to “Ordering Information” on page 5 for details.

2. The number of pages (NVMP) and page size (PSZ) can be read from the NVM Pages and Page Size bits in

the NVM Parameter register in the NVMCTRL (PARAM.NVMP and PARAM.PSZ, respectively). Refer to

PARAM for details.

Table 9-3. RWW section parameters

Device Flash size Number of pages Page size

SAMD21x16B 2Kbytes 32 64 bytes

SAMD21x15B 1Kbytes 16 64 bytes

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

29

Page 30

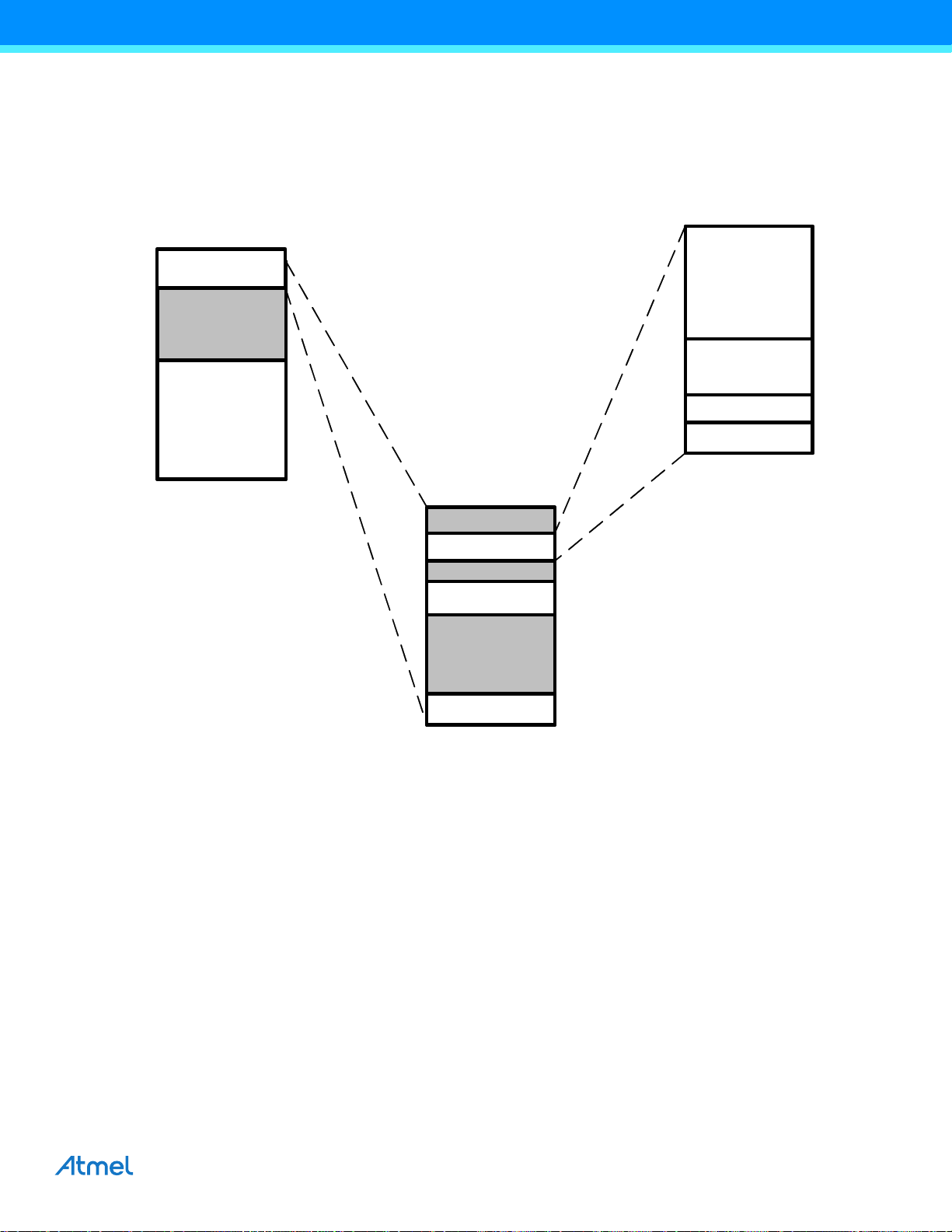

9.3 NVM Calibration and Auxiliary Space

0x00800000

AUX0 offset address

Automatic calibration

row

Calibration and auxiliary

space address offset

AUX0 – NVM User

Row

AUX1

0x00804000

0x00806000

AUX1 offset address

0x00806000

Area 3 offset ad

Area 1: Reserved (64 bits)

Area 2: Device configuration

area (64 bits)

Area 1 address

Area 2 offset ad

Area 3: Reserved

(128bits)

Area 4: Software

calibration area (256bits)

0x00806008

0x00806010

0x00806020

Area 4 offset add

AUX1

0x00806040

000000

NVM base address

+ NVM size

NVM main address

space

NVM Base Address

Calibration and

auxiliary space

NVM base address +

0x00800000

The device calibration data are stored in different sections of the NVM calibration and auxiliary space presented in Figure

9-1.

Figure 9-1. Calibration and Auxiliary Space

The values from the automatic calibration row are loaded into their respective registers at startup.

9.3.1 NVM User Row Mapping

The NVM User Row contains calibration data that are automatically read at device power on.

The NVM User Row can be read at address 0x804000.

To write the NVM User Row refer to “NVMCTRL – Non-Volatile Memory Controller” on page 355.

Note that when writing to the user row the values do not get loaded by the other modules on the device until a device

reset occurs.

Atmel | SMART SAM D21 [DATASHEET]

30

Atmel-42181G–SAM-D21_Datasheet–09/2015

Page 31

Table 9-4. NVM User Row Mapping

Bit Position Name Usage

2:0 BOOTPROT

3 Reserved

6:4 EEPROM

7 Reserved

13:8 BOD33 Level

14 BOD33 Enable BOD33 Enable at power on . Refer to BOD33 register. Default value = 1.

16:15 BOD33 Action BOD33 Action at power on. Refer to BOD33 register. Default value = 1.

24:17 Reserved

25 WDT Enable

26 WDT Always-On

30:27 WDT Period

34:31 WDT Window

Used to select one of eight different bootloader sizes. Refer to “NVMCTRL –

Non-Volatile Memory Controller” on page 355. Default value = 7.

Used to select one of eight different EEPROM sizes. Refer to “NVMCTRL –

Non-Volatile Memory Controller” on page 355. Default value = 7.

BOD33 Threshold Level at power on. Refer to BOD33 register.

Default value = 7.

Voltage Regulator Internal BOD (BOD12) configuration. These bits are written

in production and must not be changed. Default value = 0x70.

WDT Enable at power on. Refer to WDT CTRL register.

Default value = 0.

WDT Always-On at power on. Refer to WDT CTRL register.

Default value = 0.

WDT Period at power on. Refer to WDT CONFIG register.

Default value = 0x0B.

WDT Window mode time-out at power on. Refer to WDT CONFIG register.

Default value = 0x05.

38:35 WDT EWOFFSET

39 WDT WEN

40 BOD33 Hysteresis

41 Reserved

47:42 Reserved

63:48 LOCK

9.3.2 NVM Software Calibration Area Mapping

The NVM Software Calibration Area contains calibration data that are measured and written during production test.

These calibration values should be read by the application software and written back to the corresponding register.

The NVM Software Calibration Area can be read at address 0x806020.

The NVM Software Calibration Area can not be written.

WDT Early Warning Interrupt Time Offset at power on. Refer to WDT

EWCTRL register. Default value = 0x0B.

WDT Timer Window Mode Enable at power on. Refer to WDT CTRL register.

Default value = 0.

BOD33 Hysteresis configuration at power on. Refer to BOD33 register.

Default value = 0.

Voltage Regulator Internal BOD(BOD12) configuration. This bit is written in

production and must not be changed. Default value = 0.

NVM Region Lock Bits. Refer to “NVMCTRL – Non-Volatile Memory

Controller” on page 355.

Default value = 0xFFFF.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

31

Page 32

Table 9-5. NVM Software Calibration Area Mapping

Bit Position Name Description

2:0 Reserved

14:3 Reserved

26:15 Reserved

34:27 ADC LINEARITY ADC Linearity Calibration. Should be written to CALIB register.

37:35 ADC BIASCAL ADC Bias Calibration. Should be written to CALIB register.

44:38 OSC32K CAL OSC32KCalibration. Should be written to OSC32K register.

49:45 USB TRANSN USB TRANSN calibration value. Should be written to PADCAL register.

54:50 USB TRANSP USB TRANSP calibration value. Should be written to PADCAL register.

57:55 USB TRIM USB TRIM calibration value. Should be written to the PADCAL register.

63:58 DFLL48M COARSE CAL DFLL48M Coarse calibration value. Should be written to DFLLVAL register.

73:64 DFLL48M FINE CAL DFLL48M Fine calibration value. Should be written to DFLLVAL register.

127:74 Reserved

9.3.3 Serial Number

Each device has a unique 128-bit serial number which is a concatenation of four 32-bit words contained at the following

addresses:

Word 0: 0x0080A00C

Word 1: 0x0080A040

Word 2: 0x0080A044

Word 3: 0x0080A048

The uniqueness of the serial number is guaranteed only when using all 128 bits.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

32

Page 33

10. Processor And Architecture

10.1 Cortex M0+ Processor

The Atmel | SMART SAM D21 implements the ARM® Cortex™-M0+ processor, based on the ARMv6 Architecture and

Thumb®-2 ISA. The Cortex M0+ is 100% instruction set compatible with its predecessor, the Cortex-M0 core, and

upward compatible to Cortex-M3 and M4 cores. The ARM Cortex-M0+ implemented is revision r0p1. For more

information refer to www.arm.com.

10.1.1 Cortex M0+ Configuration

Table 10-1. Cortex M0+ Configuration

Features Configurable option

Interrupts External interrupts 0-32 28

Data endianness Little-endian or big-endian Little-endian

SysTick timer Present or absent Present

Number of watchpoint comparators 0, 1, 2 2

Number of breakpoint comparators 0, 1, 2, 3, 4 4

Halting debug support Present or absent Present

Atmel | SMART SAM D21

configuration

Multiplier Fast or small Fast (single cycle)

Single-cycle I/O port Present or absent Present

Wake-up interrupt controller Supported or not supported Not supported

Vector Table Offset Register Present or absent Present

Unprivileged/Privileged support Present or absent Absent

Memory Protection Unit Not present or 8-region Not present

Reset all registers Present or absent Absent

Instruction fetch width 16-bit only or mostly 32-bit 32-bit

Note: 1. All software run in privileged mode only.

The ARM Cortex-M0+ core has two bus interfaces:

z Single 32-bit AMBA-3 AHB-Lite system interface that provides connections to peripherals and all system

memory, which includes flash and RAM.

z Single 32-bit I/O port bus interfacing to the PORT with 1-cycle loads and stores.

10.1.2 Cortex-M0+ Peripherals

z System Control Space (SCS)

z The processor provides debug through registers in the SCS. Refer to the Cortex-M0+ Technical Reference

Manual for details (www.arm.com).

z System Timer (SysTick)

z The System Timer is a 24-bit timer that extends the functionality of both the processor and the NVIC. Refer

to the Cortex-M0+ Technical Reference Manual for details (www.arm.com).

(1)

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

33

Page 34

z Nested Vectored Interrupt Controller (NVIC)

z External interrupt signals connect to the NVIC, and the NVIC prioritizes the interrupts. Software can set the

priority of each interrupt. The NVIC and the Cortex-M0+ processor core are closely coupled, providing low

latency interrupt processing and efficient processing of late arriving interrupts. Refer to “Nested Vector

Interrupt Controller” on page 34 and the Cortex-M0+ Technical Reference Manual for details

(www.arm.com).

z System Control Block (SCB)

z The System Control Block provides system implementation information, and system control. This includes

configuration, control, and reporting of the system exceptions. Refer to the Cortex-M0+ Devices Generic

User Guide for details (www.arm.com).

z Micro Trace Buffer (MTB)

z The CoreSight MTB-M0+ (MTB) provides a simple execution trace capability to the Cortex-M0+ processor.

Refer to section “Micro Trace Buffer” on page 36 and the CoreSight MTB-M0+ Technical Reference Manual

for details (www.arm.com).

10.1.3 Cortex-M0+ Address Map

Table 10-2. Cortex-M0+ Address Map

Address Peripheral

0xE000E000 System Control Space (SCS)

0xE000E010 System Timer (SysTick)

0xE000E100 Nested Vectored Interrupt Controller (NVIC)

0xE000ED00 System Control Block (SCB)

0x41006000 (see also “Product Mapping” on page 28) Micro Trace Buffer (MTB)

10.1.4 I/O Interface

10.1.4.1 Overview

Because accesses to the AMBA® AHB-Lite™ and the single cycle I/O interface can be made concurrently, the CortexM0+ processor can fetch the next instructions while accessing the I/Os. This enables single cycle I/O accesses to be

sustained for as long as needed. Refer to “CPU Local Bus” on page 381 for more information.

10.1.4.2 Description

Direct access to PORT registers.

10.2 Nested Vector Interrupt Controller

10.2.1 Overview

The Nested Vectored Interrupt Controller (NVIC) in the SAM D21 supports 32 interrupt lines with four different priority

levels. For more details, refer to the Cortex-M0+ Technical Reference Manual (www.arm.com).

10.2.2 Interrupt Line Mapping

Each of the 28 interrupt lines is connected to one peripheral instance, as shown in the table below. Each peripheral can

have one or more interrupt flags, located in the peripheral’s Interrupt Flag Status and Clear (INTFLAG) register. The

interrupt flag is set when the interrupt condition occurs. Each interrupt in the peripheral can be individually enabled by

writing a one to the corresponding bit in the peripheral’s Interrupt Enable Set (INTENSET) register, and disabled by

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

34

Page 35

writing a one to the corresponding bit in the peripheral’s Interrupt Enable Clear (INTENCLR) register. An interrupt request

is generated from the peripheral when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt

requests for one peripheral are ORed together on system level, generating one interrupt request for each peripheral. An

interrupt request will set the corresponding interrupt pending bit in the NVIC interrupt pending registers

(SETPEND/CLRPEND bits in ISPR/ICPR). For the NVIC to activate the interrupt, it must be enabled in the NVIC interrupt

enable register (SETENA/CLRENA bits in ISER/ICER). The NVIC interrupt priority registers IPR0-IPR7 provide a priority

field for each interrupt.

Table 10-3. Interrupt Line Mapping

Peripheral Source NVIC Line

EIC NMI – External Interrupt Controller NMI

PM – Power Manager 0

SYSCTRL – System Control 1

WDT – Watchdog Timer 2

RTC – Real Time Counter 3

EIC – External Interrupt Controller 4

NVMCTRL – Non-Volatile Memory Controller 5

DMAC - Direct Memory Access Controller 6

USB - Universal Serial Bus 7

EVSYS – Event System 8

SERCOM0 – Serial Communication Interface 0 9

SERCOM1 – Serial Communication Interface 1 10

SERCOM2 – Serial Communication Interface 2 11

SERCOM3 – Serial Communication Interface 3 12

SERCOM4 – Serial Communication Interface 4 13

SERCOM5 – Serial Communication Interface 5 14

TCC0 – Timer Counter for Control 0 15

TCC1 – Timer Counter for Control 1 16

TCC2 – Timer Counter for Control 2 17

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

35

Page 36

Table 10-3. Interrupt Line Mapping (Continued)

Peripheral Source NVIC Line

TC3 – Timer Counter 3 18

TC4 – Timer Counter 4 19

TC5 – Timer Counter 5 20

TC6 – Timer Counter 6 21

TC7 – Timer Counter 7 22

ADC – Analog-to-Digital Converter 23

AC – Analog Comparator 24

DAC – Digital-to-Analog Converter 25

PTC – Peripheral Touch Controller 26

I2S - Inter IC Sound 27

10.3 Micro Trace Buffer

10.3.1 Features

z Program flow tracing for the Cortex-M0+ processor

z MTB SRAM can be used for both trace and general purpose storage by the processor

z The position and size of the trace buffer in SRAM is configurable by software

z CoreSight compliant

10.3.2 Overview

When enabled, the MTB records changes in program flow, reported by the Cortex-M0+ processor over the execution

trace interface shared between the Cortex-M0+ processor and the CoreSight MTB-M0+. This information is stored as

trace packets in the SRAM by the MTB. An off-chip debugger can extract the trace information using the Debug Access

Port to read the trace information from the SRAM. The debugger can then reconstruct the program flow from this

information.

The MTB simultaneously stores trace information into the SRAM, and gives the processor access to the SRAM. The

MTB ensures that trace write accesses have priority over processor accesses.

The execution trace packet consists of a pair of 32-bit words that the MTB generates when it detects the processor PC

value changes non-sequentially. A non-sequential PC change can occur during branch instructions or during exception

entry. See the CoreSight MTB-M0+ Technical Reference Manual for more details on the MTB execution trace packet

format.

Tracing is enabled when the MASTER.EN bit in the Master Trace Control Register is 1. There are various ways to set the

bit to 1 to start tracing, or to 0 to stop tracing. See the CoreSight Cortex-M0+ Technical Reference Manual for more

details on the Trace start and stop and for a detailed description of the MTB’s MASTER register. The MTB can be

programmed to stop tracing automatically when the memory fills to a specified watermark level or to start or stop tracing

by writing directly to the MASTER.EN bit. If the watermark mechanism is not being used and the trace buffer overflows,

then the buffer wraps around overwriting previous trace packets.

The base address of the MTB registers is 0x41006000; this address is also written in the CoreSight ROM Table. The

offset of each register from the base address is fixed and as defined by the CoreSight MTB-M0+ Technical Reference

Manual. The MTB has 4 programmable registers to control the behavior of the trace features:

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

36

Page 37

z POSITION: Contains the trace write pointer and the wrap bit,

z MASTER: Contains the main trace enable bit and other trace control fields,

z FLOW: Contains the WATERMARK address and the AUTOSTOP and AUTOHALT control bits,

z BASE: Indicates where the SRAM is located in the processor memory map. This register is provided to enable

auto discovery of the MTB SRAM location, by a debug agent.

See the CoreSight MTB-M0+ Technical Reference Manual for a detailed description of these registers.

10.4 High-Speed Bus System

10.4.1 Features

High-Speed Bus Matrix has the following features:

z Symmetric crossbar bus switch implementation

z Allows concurrent accesses from different masters to different slaves

z 32-bit data bus

z Operation at a one-to-one clock frequency with the bus masters

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

37

Page 38

10.4.2 Configuration

CM0+ 0

DSU 1

High-Speed Bus SLAVES

Internal Flash

0

AHB-APB Bridge A

1

AHB-APB Bridge B

2

AHB-APB Bridge C

3

MTB

Multi-Slave

MASTERS

USB

DMAC WB

DMAC Fetch

CM0+

4

DMAC Data

DSU

6

SRAM

DSU 1

MTB

USB

DMAC WB

DMAC Fetch

Priviledged SRAM-access

MASTERS

DSU 2

DMAC Data

4

5

0123

65

SLAVE ID

SRAM PORT ID

MASTER ID

Table 10-4. Bus Matrix Masters

Bus Matrix Masters Master ID

CM0+ - Cortex M0+ Processor 0

DSU - Device Service Unit 1

DMAC - Direct Memory Access Controller / Data Access 2

Table 10-5. Bus Matrix Slaves

Bus Matrix Slaves Slave ID

Internal Flash Memory 0

AHB-APB Bridge A 1

AHB-APB Bridge B 2

AHB-APB Bridge C 3

SRAM Port 4 - CM0+ Access 4

SRAM Port 5 - DMAC Data Access 5

SRAM Port 6 - DSU Access 6

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

38

Page 39

Table 10-6. SRAM Port Connection

SRAM Port Connection Port ID Connection Type

MTB - Micro Trace Buffer 0 Direct

USB - Universal Serial Bus 1 Direct

DMAC - Direct Memory Access Controller - Write-Back Access 2 Direct

DMAC - Direct Memory Access Controller - Fetch Access 3 Direct

CM0+ - Cortex M0+ Processor 4 Bus Matrix

DMAC - Direct Memory Access Controller - Data Access 5 Bus Matrix

DSU - Device Service Unit 6 Bus Matrix

10.4.3 SRAM Quality of Service

To ensure that masters with latency requirements get sufficient priority when accessing RAM, the different masters can

be configured to have a given priority for different type of access.

The Quality of Service (QoS) level is independently selected for each master accessing the RAM. For any access to the

RAM the RAM also receives the QoS level. The QoS levels and their corresponding bit values for the QoS level

configuration is shown in Table 10-7.

Table 10-7. Quality of Service

Value Name Description

00 DISABLE Background (no sensitive operation)

01 LOW Sensitive Bandwidth

10 MEDIUM Sensitive Latency

11 HIGH Critical Latency

If a master is configured with QoS level 0x00 or 0x01 there will be minimum one cycle latency for the RAM access.

The priority order for concurrent accesses are decided by two factors. First the QoS level for the master and then a static

priority given by table nn-mm (table: SRAM port connection) where the lowest port ID has the highest static priority.

The MTB has fixed QoS level 3 and the DSU has fixed QoS level 1.

The CPU QoS level can be written/read at address 0x41007110, bits [1:0]. Its reset value is 0x0.

Refer to different master QOSCTRL registers for configuring QoS for the other masters (USB, DMAC).

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

39

Page 40

10.5 AHB-APB Bridge

T0 T1 T2 T3

Addr 1

Data 1

PADDR

PWRITE

PCLK

PSEL

PENABLE

PWDATA

PREADY

T0 T1 T2 T3

Addr 1

Data 1

PADDR

PWRITE

PCLK

PSEL

PENABLE

PWDATA

PREADY

T4 T5

Wait statesNo wait states

The AHB-APB bridge is an AHB slave, providing an interface between the high-speed AHB domain and the low-power

APB domain. It is used to provide access to the programmable control registers of peripherals (see “Product Mapping” on

page 28).

AHB-APB bridge is based on AMBA APB Protocol Specification V2.0 (ref. as APB4) including:

z Wait state support

z Error reporting

z Transaction protection

z Sparse data transfer (byte, half-word and word)

Additional enhancements:

z Address and data cycles merged into a single cycle

z Sparse data transfer also apply to read access

to operate the AHB-APB bridge, the clock (CLK_HPBx_AHB) must be enabled. See “PM – Power Manager” on page 117

for details.

Figure 10-1. APB Write Access.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

40

Page 41

Figure 10-2. APB Read Access.

T0 T1 T2 T3

Addr 1

Data 1

PADDR

PWRITE

PCLK

PSEL

PENABLE

PRDATA

PREADY

T0 T1 T2 T3

Addr 1

Data 1

PADDR

PWRITE

PCLK

PSEL

PENABLE

PRDATA

PREADY

T4 T5

Wait statesNo wait states

10.6 PAC – Peripheral Access Controller

10.6.1 Overview

There is one PAC associated with each AHB-APB bridge. The PAC can provide write protection for registers of each

peripheral connected on the same bridge.

The PAC peripheral bus clock (CLK_PACx_APB) can be enabled and disabled in the Power Manager. CLK_PAC0_APB

and CLK_PAC1_APB are enabled are reset. CLK_PAC2_APB is disabled at reset. Refer to “PM – Power Manager” on

page 117 for details. The PAC will continue to operate in any sleep mode where the selected clock source is running.

Write-protection does not apply for debugger access. When the debugger makes an access to a peripheral, writeprotection is ignored so that the debugger can update the register.

Write-protect registers allow the user to disable a selected peripheral’s write-protection without doing a read-modify-write

operation. These registers are mapped into two I/O memory locations, one for clearing and one for setting the register

bits. Writing a one to a bit in the Write Protect Clear register (WPCLR) will clear the corresponding bit in both registers

(WPCLR and WPSET) and disable the write-protection for the corresponding peripheral, while writing a one to a bit in the

Write Protect Set (WPSET) register will set the corresponding bit in both registers (WPCLR and WPSET) and enable the

write-protection for the corresponding peripheral. Both registers (WPCLR and WPSET) will return the same value when

read.

If a peripheral is write-protected, and if a write access is performed, data will not be written, and the peripheral will return

an access error (CPU exception).

The PAC also offers a safety feature for correct program execution, with a CPU exception generated on double writeprotection or double unprotection of a peripheral. If a peripheral n is write-protected and a write to one in WPSET[n] is

detected, the PAC returns an error. This can be used to ensure that the application follows the intended program flow by

always following a write-protect with an unprotect, and vice versa. However, in applications where a write-protected

peripheral is used in several contexts, e.g., interrupts, care should be taken so that either the interrupt can not happen

while the main application or other interrupt levels manipulate the write-protection status, or when the interrupt handler

needs to unprotect the peripheral, based on the current protection status, by reading WPSET.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

41

Page 42

10.6.2 Register Description

Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and

the 8-bit halves of a 16-bit register can be accessed directly.

Refer to “Product Mapping” on page 28 for PAC locations.

10.6.2.1 PAC0 Register Description

Write Protect Clear

Name: WPCLR

Offset: 0x00

Reset: 0x00000000

Property: -

Bit3130292827262524

AccessRRRRRRRR

Reset00000000

Bit2322212019181716

AccessRRRRRRRR

Reset00000000

Bit151413121110 9 8

AccessRRRRRRRR

Reset00000000

Bit76543210

EIC RTC WDT GCLK SYSCTRL PM

Access R R/W R/W R/W R/W R/W R/W R

Reset00000000

z Bits 31:7 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to

zero when this register is written. These bits will always return zero when read.

z Bits 6:1 – EIC, RTC, WDT, GCLK, SYSCTRL, PM: Write Protect Disable

0: Write-protection is disabled.

1: Write-protection is enabled.

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bits for the corresponding peripherals.

z Bit 0 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write this bit to zero

when this register is written. This bit will always return zero when read.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

42

Page 43

Write Protect Set

Name: WPSET

Offset: 0x04

Reset: 0x00000000

Property: -

Bit 3130292827262524

AccessRRRRRRRR

Reset00000000

Bit 2322212019181716

AccessRRRRRRRR

Reset00000000

Bit 15 14 13 12 11 10 9 8

AccessRRRRRRRR

Reset00000000

Bit76543210

EIC RTC WDT GCLK SYSCTRL PM

Access R R/W R/W R/W R/W R/W R/W R

Reset00000000

z Bits 31:7 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to

zero when this register is written. These bits will always return zero when read.

z Bits 6:1 – EIC, RTC, WDT, GCLK, SYSCTRL, PM: Write Protect Enable

0: Write-protection is disabled.

1: Write-protection is enabled.

Writing a zero to these bits has no effect.

Writing a one to these bits will set the Write Protect bit for the corresponding peripherals.

z Bit 0 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write this bit to zero

when this register is written. This bit will always return zero when read.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

43

Page 44

10.6.2.2 PAC1 Register Description

Write Protect Clear

Name: WPCLR

Offset: 0x00

Reset: 0x00000002

Property: -

Bit3130292827262524

AccessRRRRRRRR

Reset00000000

Bit2322212019181716

AccessRRRRRRRR

Reset00000000

Bit151413121110 9 8

AccessRRRRRRRR

Reset00000000

Bit76543210

MTB USB DMAC PORT NVMCTRL DSU

Access R R/W R/W R/W R/W R/W R/W R

Reset00000010

z Bits 31:7 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to

zero when this register is written. These bits will always return zero when read.

z Bits 6:1 – MTB, USB, DMAC, PORT, NVMCTRL, DSU: Write Protect

0: Write-protection is disabled.

1: Write-protection is enabled.

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

z Bit 0 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write this bit to zero

when this register is written. This bit will always return zero when read.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

44

Page 45

Write Protect Set

Name: WPSET

Offset: 0x04

Reset: 0x00000002

Property: -

Bit 3130292827262524

AccessRRRRRRRR

Reset00000000

Bit 2322212019181716

AccessRRRRRRRR

Reset00000000

Bit 15 14 13 12 11 10 9 8

AccessRRRRRRRR

Reset00000000

Bit76543210

MTB USB DMAC PORT NVMCTRL DSU

Access R R/W R/W R/W R/W R/W R/W R

Reset00000010

z Bits 31:7 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to

zero when this register is written. These bits will always return zero when read.

z Bits 6:1 – MTB, USB, DMAC, PORT, NVMCTRL, DSU: Write Protect

0: Write-protection is disabled.

1: Write-protection is enabled.

Writing a zero to these bits has no effect.

Writing a one to these bits will set the Write Protect bit for the corresponding peripherals.

z Bit 0 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write this bit to zero

when this register is written. This bit will always return zero when read.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

45

Page 46

10.6.2.3 PAC2 Register Description

Write Protect Clear

Name: WPCLR

Offset: 0x00

Reset: 0x00800000

Property: -

Bit3130292827262524

AccessRRRRRRRR

Reset00000000

Bit2322212019181716

AC1 I2S PTC DAC AC ADC

Access R R R/W R/W R/W R/W R/W R/W

Reset10000000

Bit151413121110 9 8

TC7 TC6 TC5 TC4 TC3 TCC2 TCC1 TCC0

Access R/W R/W R/W R/W R/W R/W R/W R/W

Reset00000000

Bit76543210

SERCOM5 SERCOM4 SERCOM3 SERCOM2 SERCOM1 SERCOM0 EVSYS

Access R/W R/W R/W R/W R/W R/W R/W R

Reset00000000

z Bits 31:21 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to

reset value when this register is written. These bits will always return reset value when read.

z Bits 20:1 – I2S, PTC, DAC, AC, ADC, TC7, TC6, TC5, TC4, TC3, TCC2, TCC1, TCC0, SERCOM5, SERCOM4,

SERCOM3, SERCOM2, SERCOM1, SERCOM0, EVSYS: Write Protect

0: Write-protection is disabled.

1: Write-protection is enabled.

Writing a zero to these bits has no effect.

Writing a one to these bits will clear the Write Protect bit for the corresponding peripherals.

z Bit 0 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write this bit to zero

when this register is written. This bit will always return zero when read.

Atmel | SMART SAM D21 [DATASHEET]

Atmel-42181G–SAM-D21_Datasheet–09/2015

46

Page 47

Write Protect Set

Name: WPSET

Offset: 0x04

Reset: 0x00800000

Property: -

Bit3130292827262524

AccessRRRRRRRR

Reset00000000

Bit2322212019181716

AC1 I2S PTC DAC AC ADC

Access R R R/W R/W R/W R/W R/W R/W

Reset10000000

Bit151413121110 9 8

TC7 TC6 TC5 TC4 TC3 TCC2 TCC1 TCC0

Access R/W R/W R/W R/W R/W R/W R/W R/W

Reset00000000

Bit76543210

SERCOM5 SERCOM4 SERCOM3 SERCOM2 SERCOM1 SERCOM0 EVSYS

Access R/W R/W R/W R/W R/W R/W R/W R

Reset00000000

z Bits 31:21 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to

reset value when this register is written. These bits will always return reset value when read.

z Bits 20:1 – I2S, PTC, DAC, AC, ADC, TC7, TC6, TC5, TC4, TC3, TCC2, TCC1, TCC0, SERCOM5, SERCOM4,

SERCOM3, SERCOM2, SERCOM1, SERCOM0, EVSYS: Write Protect

0: Write-protection is disabled.