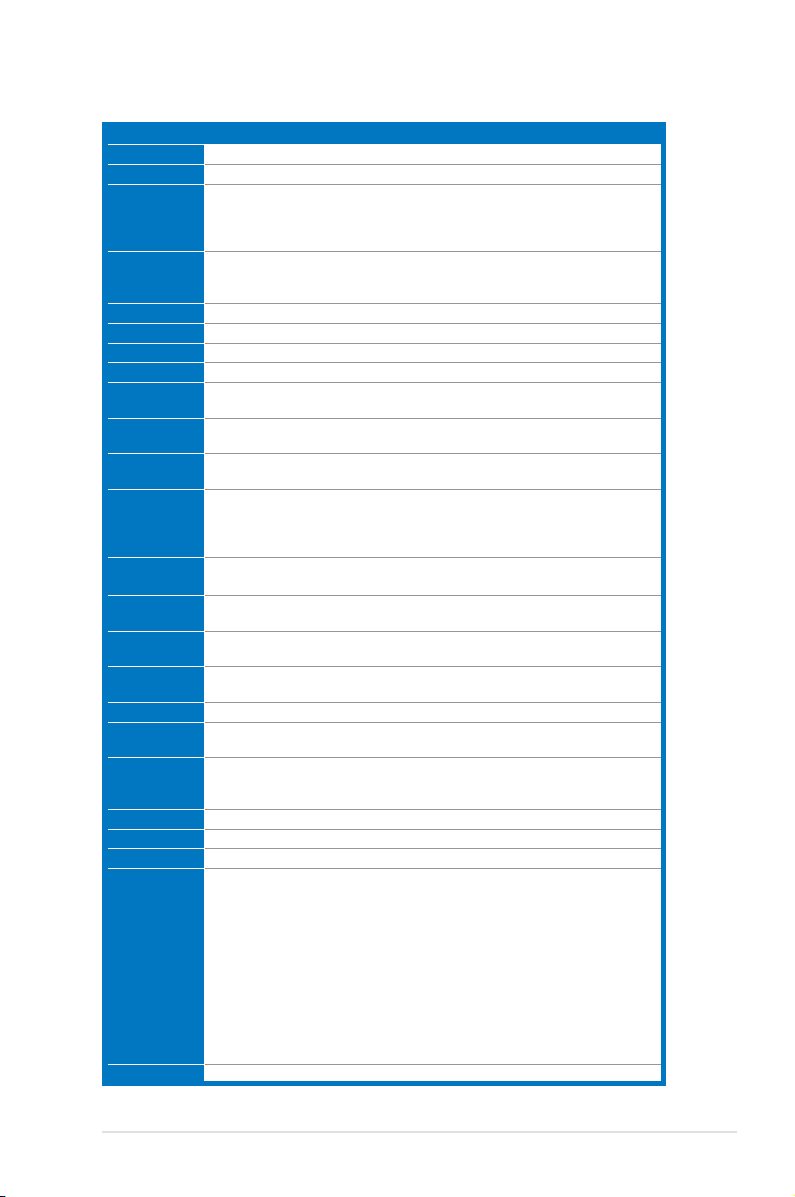

Asus Crosshair User Manual

Debug Code Table

Code Description

CPU INIT CPU Initiation

DET CPU Test CMOS R/W functionality.

CHIPINIT

DET DRAM

DC FCODE Expand compressed BIOS code to DRAM

EFSHADOW Call chipset hook to copy BIOS back to E000 & F000 shadow RAM.

DC XCODE Expand the Xgroup codes locating in physical address 1000:0

INIT IO Initial Superio_Early_Init switch.

CLR SCRN

INIT8042

ENABLEKB

DIS MS

R/W FSEG

DET FLASH

TESTCMOS

PRG CHIP

INIT CLK Initial Early_Init_Onboard_Generator switch.

CHECKCPU

INTRINIT

REC MPS Initial EARLY_PM_INIT switch.

Reserved Load keyboard matrix (notebook platform)

Reserved HPM initialization (notebook platform)

SET FDD

INITINT9 Initialize INT 09 buffer

Early chipset initialization:

-Disable shadow RAM

-Disable L2 cache (socket 7 or below)

-Program basic chipset registers

Detect memory

-Auto-detection of DRAM size, type and ECC.

-Auto-detection of L2 cache (socket 7 or below)

1. Blank out screen

2. Clear CMOS error ag

1. Clear 8042 interface

2. Initialize 8042 self-test

1. Test special keyboard controller for Winbond 977 series Super I/O chips.

2. Enable keyboard interface.

1. Disable PS/2 mouse interface (optional).

2. Auto detect ports for keyboard & mouse followed by a port & interface

swap (optional).

3. Reset keyboard for Winbond 977 series Super I/O chips.

Test F000h segment shadow to see whether it is R/W-able or not. If test

fails, keep beeping the speaker.

Auto detect ash type to load appropriate ash R/W codes into the run time

area in F000 for ESCD & DMI support.

Use walking 1’s algorithm to check out interface in CMOS circuitry. Also set

real-time clock power status, and then check for override.

Program chipset default values into chipset. Chipset default values are

MODBINable by OEM customers.

Detect CPU information including brand, SMI type (Cyrix or Intel) and CPU

level (586 or 686).

Initial interrupts vector table. If no special specied, all H/W

interrupts are directed to SPURIOUS_INT_HDLR & S/W interrupts to

SPURIOUS_soft_HDLR.

1. Check validity of RTC value:

e.g. a value of 5Ah is an invalid value for RTC minute.

2. Load CMOS settings into BIOS stack. If CMOS checksum fails, use

default value instead.

3. Prepare BIOS resource map for PCI & PnP use. If ESCD is valid, take

into consideration of the ESCD’s legacy information.

4. Onboard clock generator initialization. Disable respective clock resource

to empty PCI & DIMM slots.

5. Early PCI initialization:

-Enumerate PCI bus number

-Assign memory & I/O resource

-Search for a valid VGA device & VGA BIOS, and put it nto C000:0.

Debug Code Table 1

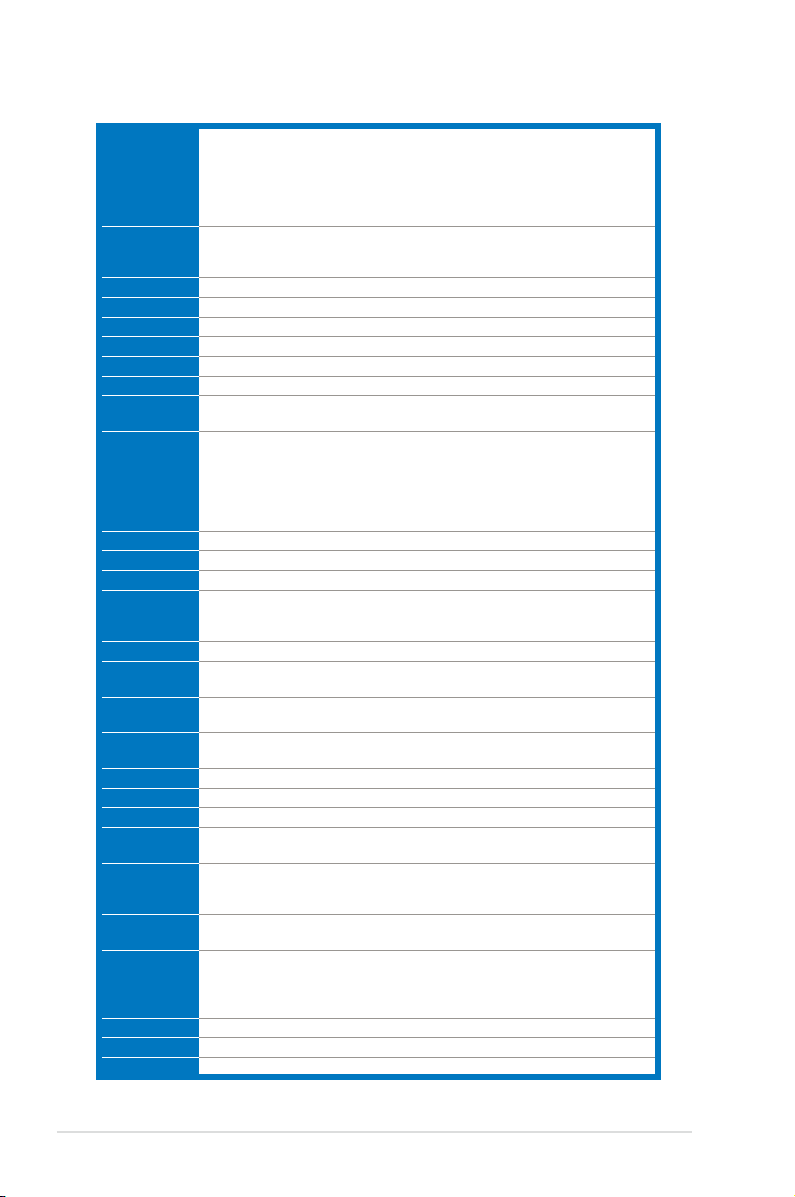

1. Program CPU internal MTRR (P6 & PII) for 0-640K memory address.

2. Initialize the APIC for Pentium class CPU.

CPUSPEED

TESTVRAM

RESET KB Reset keyboard except Winbond 977 series Super I/O chips.

8254TEST

8259MSK1 Test 8259 interrupt mask bits for channel 1.

8259MSK2 Test 8259 interrupt mask bits for channel 2.

8259TEST Test 8259 functionality.

Reserved Initialize EISA slot

COUNTMEM

MP INIT

USB INIT Initialize USB

TEST MEM Test all memory (clear all extended memory to 0)

SHOW MP Display number of processors (multi-processor platform)

PNP LOGO

Reserved Initialize the combined Trend Anti-Virus code.

SHOW EZF

ONBD IO

EN SETUP

MSINSTAL Initialize PS/2 Mouse

CHK ACPI Prepare memory size information for function call: INT 15h ax=E820h

EN CACHE Turn on L2 cache

SET CHIP

AUTO CFG

INIT FDC

CUTIRQ12

DET IDE Detect & install all IDE devices: HDD, LS120, ZIP, CDROM…..

COM/LPT Detect serial ports & parallel ports.

DET FPU Detect & install co-processor

3. Program early chipset according to CMOS setup. Example: onboard IDE

controller.

4. Measure CPU speed.

5. Invoke video BIOS.

1. Initialize multi-language

2. Put information on screen display, including Award title, CPU type, CPU

speed .

Test 8254

1. Calculate total memory by testing the last double word of each 64K page.

2. Program write allocation for AMD K5 CPU.

1. Program MTRR of M1 CPU

2. Initialize L2 cache for P6 class CPU & program CPU with proper

cacheable range.

3. Initialize the APIC for P6 class CPU.

4. On MP platform, adjust the cacheable range to smaller one in case the

cacheable ranges between each CPU are not identical.

1. Display PnP logo

2. Early ISA PnP initialization

-Assign CSN to every ISA PnP device.

(Optional Feature)

Show message for entering AWDFLASH.EXE from FDD (optional)

1. Initialize Init_Onboard_Super_IO switch.

2. Initialize Init_Onbaord_AUDIO switch.

Okay to enter Setup utility; i.e. not until this POST stage can users enter the

CMOS setup utility.

Program chipset registers according to items described in Setup & Auto-

conguration table.

1. Assign resources to all ISA PnP devices.

2. Auto assign ports to onboard COM ports if the corresponding item in

Setup is set to “AUTO”.

1. Initialize oppy controller

2. Set up oppy related elds in 40:hardware.

(Optional Feature)

Enter AWDFLASH.EXE if :

-AWDFLASH is found in oppy drive.

-ALT+F2 is pressed

2 Debug Code Table

Loading...

Loading...