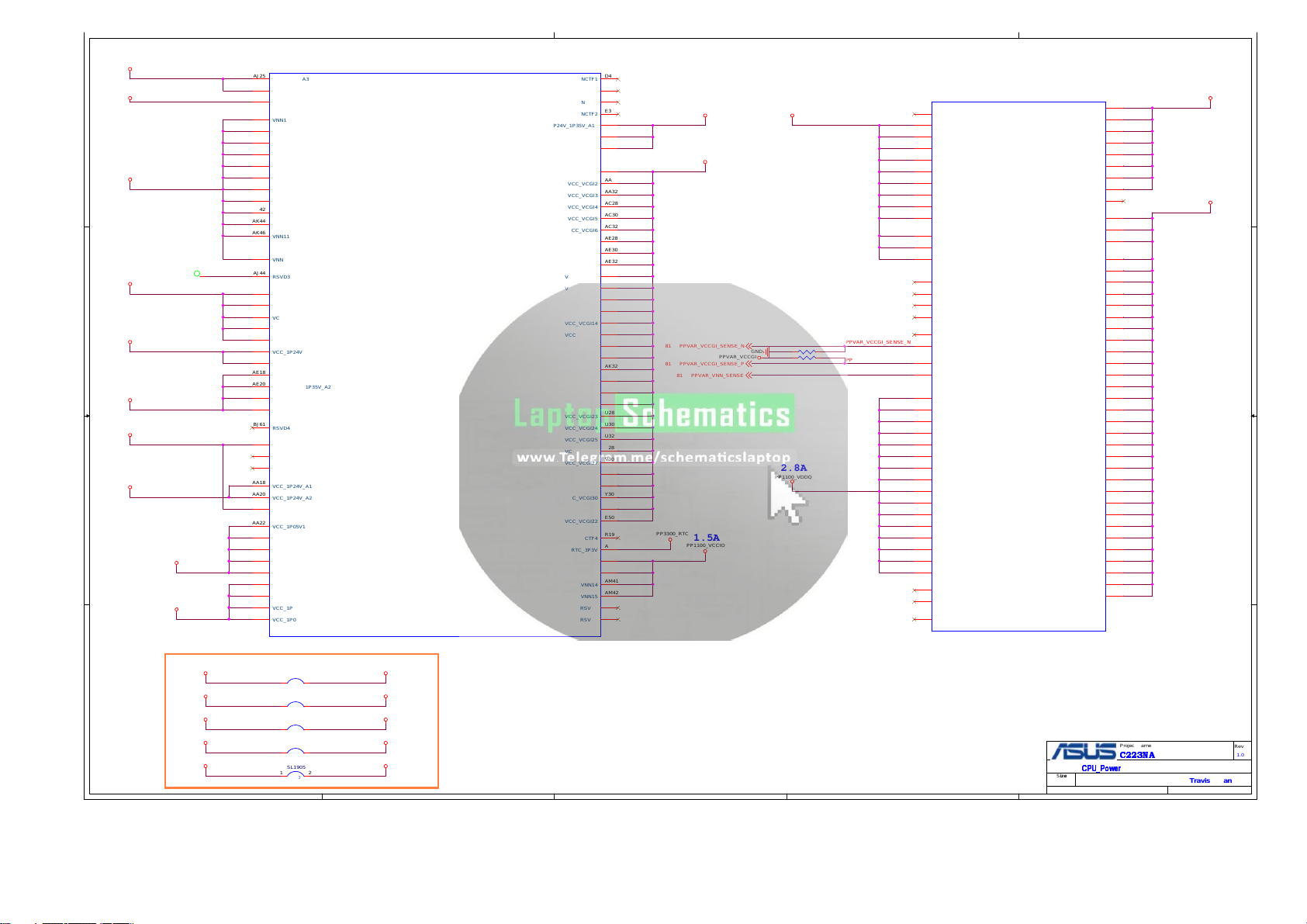

Asus Chromebook C423NA Schematic

5

4

3

2

1

SYSTEM PAGE REF.

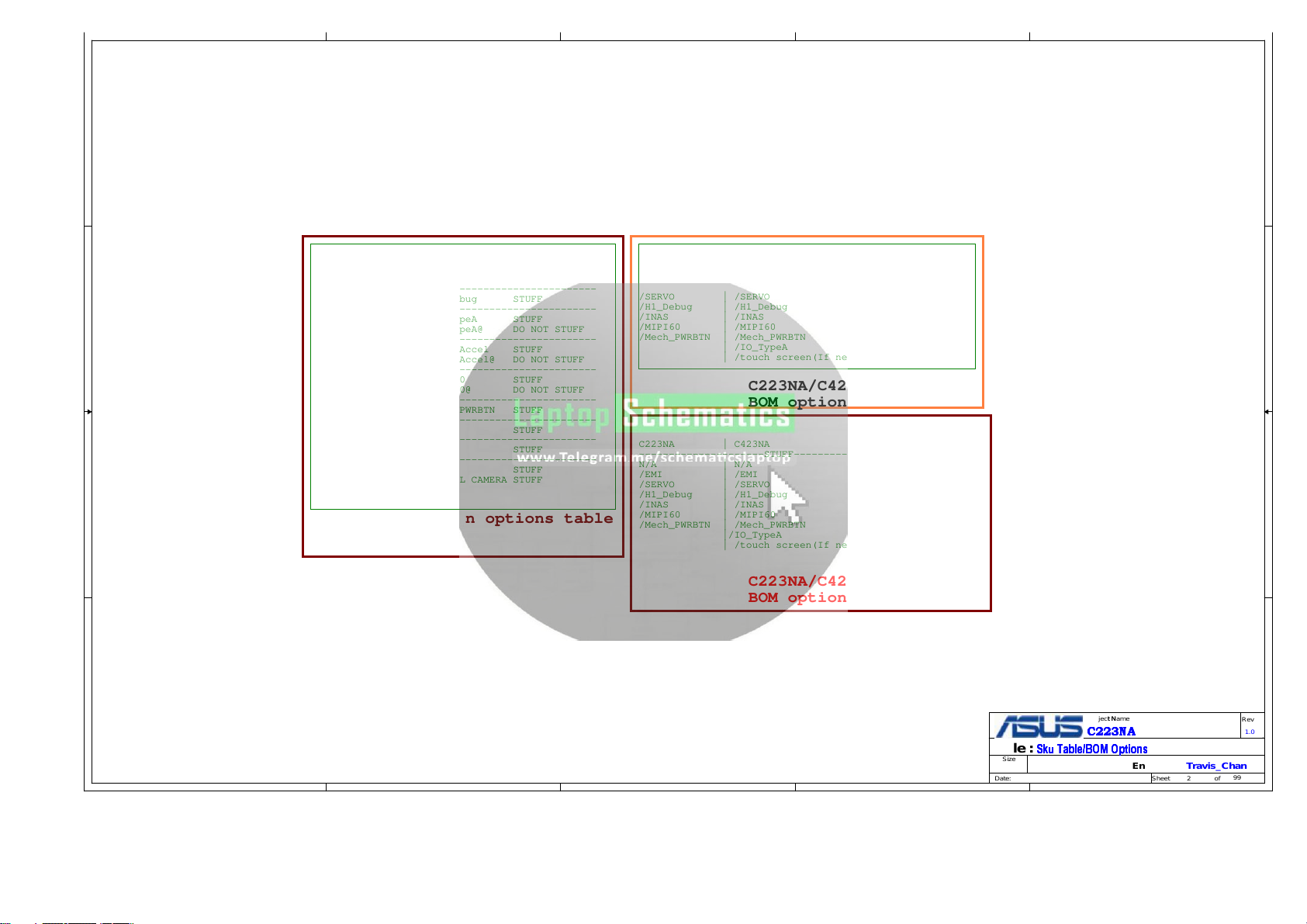

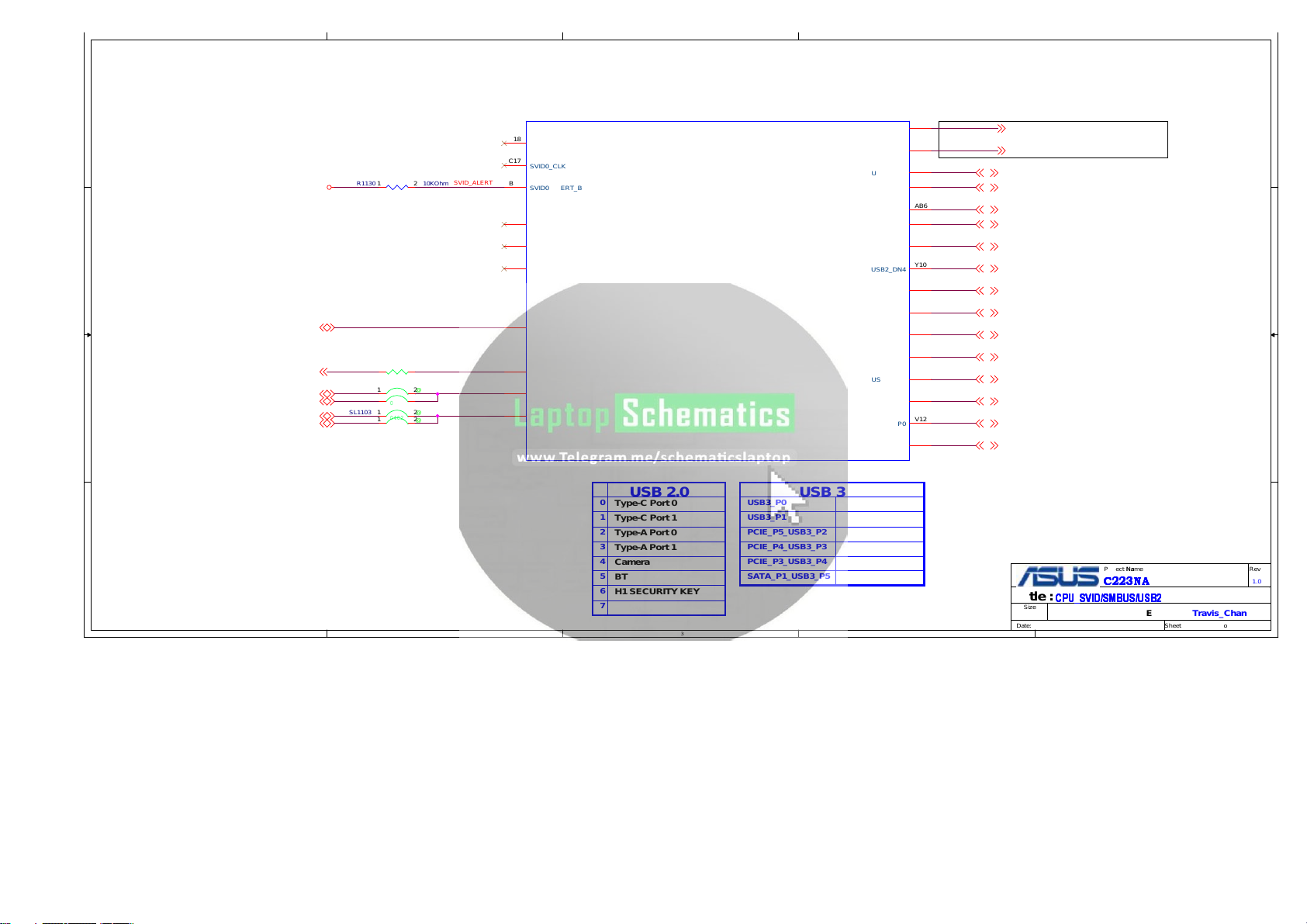

C223NA/C423NA/C523NA

PAGE Content

1 Block Diagram

D D

2 Sku Table/BOM Option

3 Power Flow Chart

5 CPU_LPDDR4

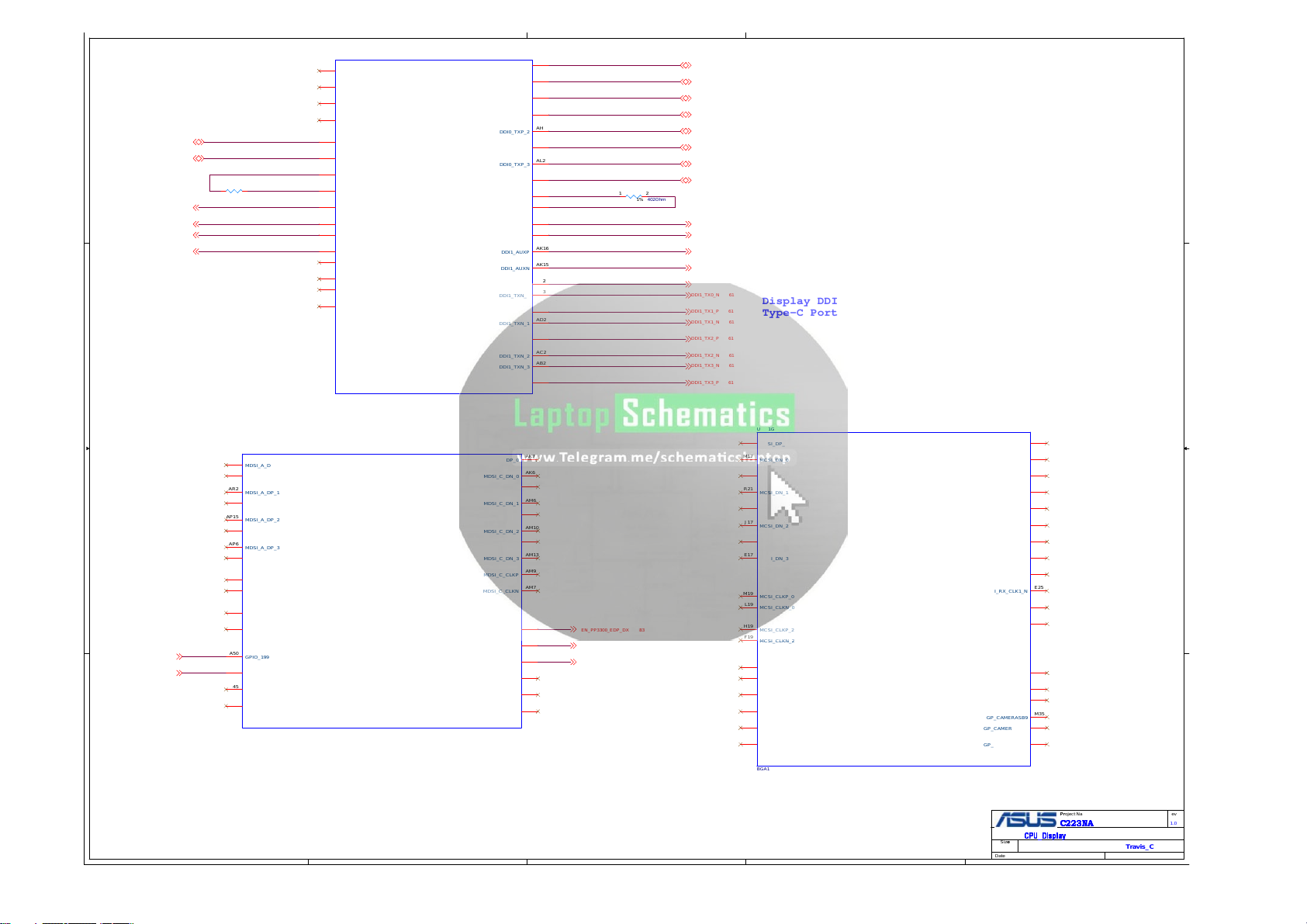

6 CPU_DISPLAY

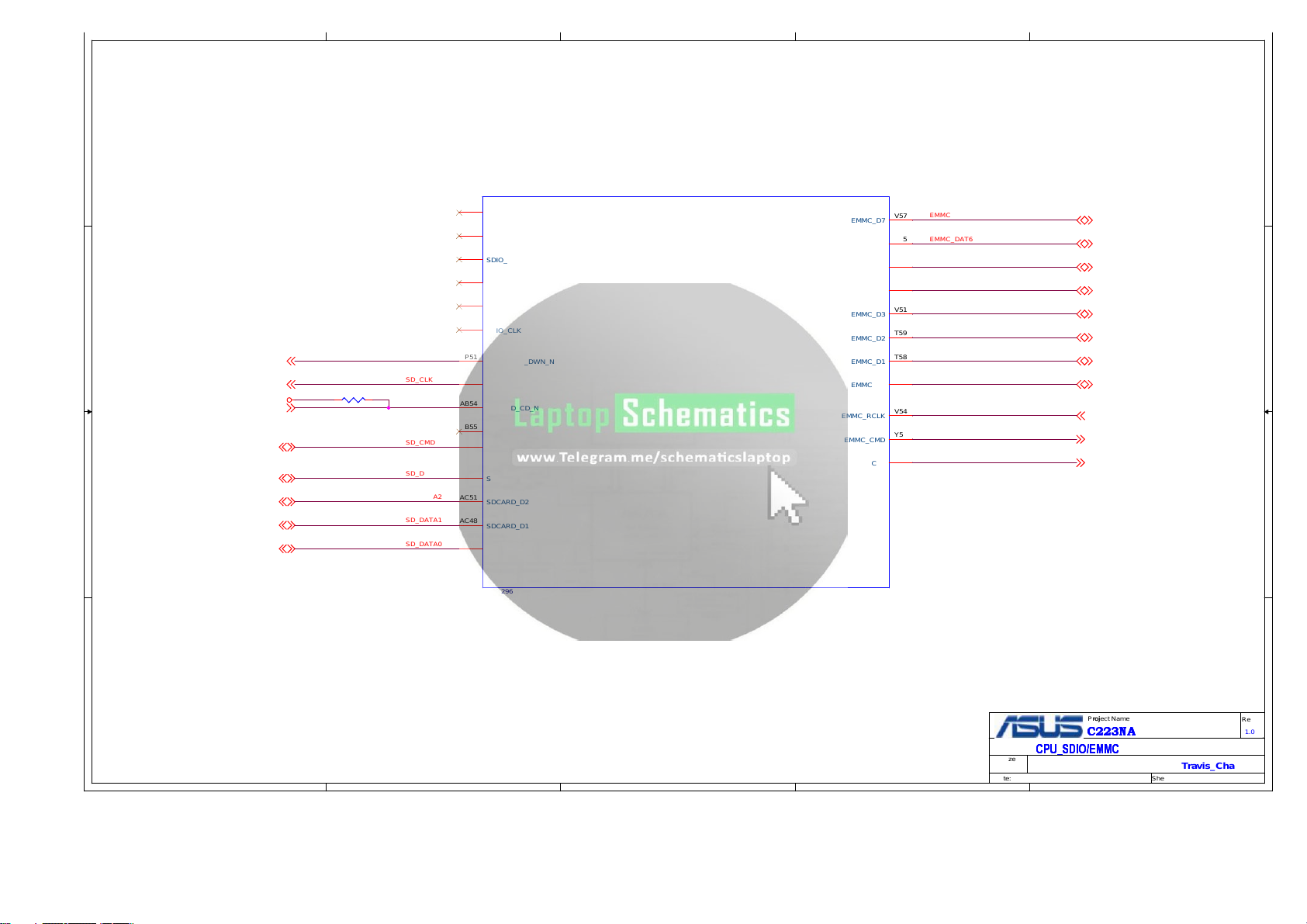

7 CPU_SDIO/EMMC

8 CPU_USB3/PCIE

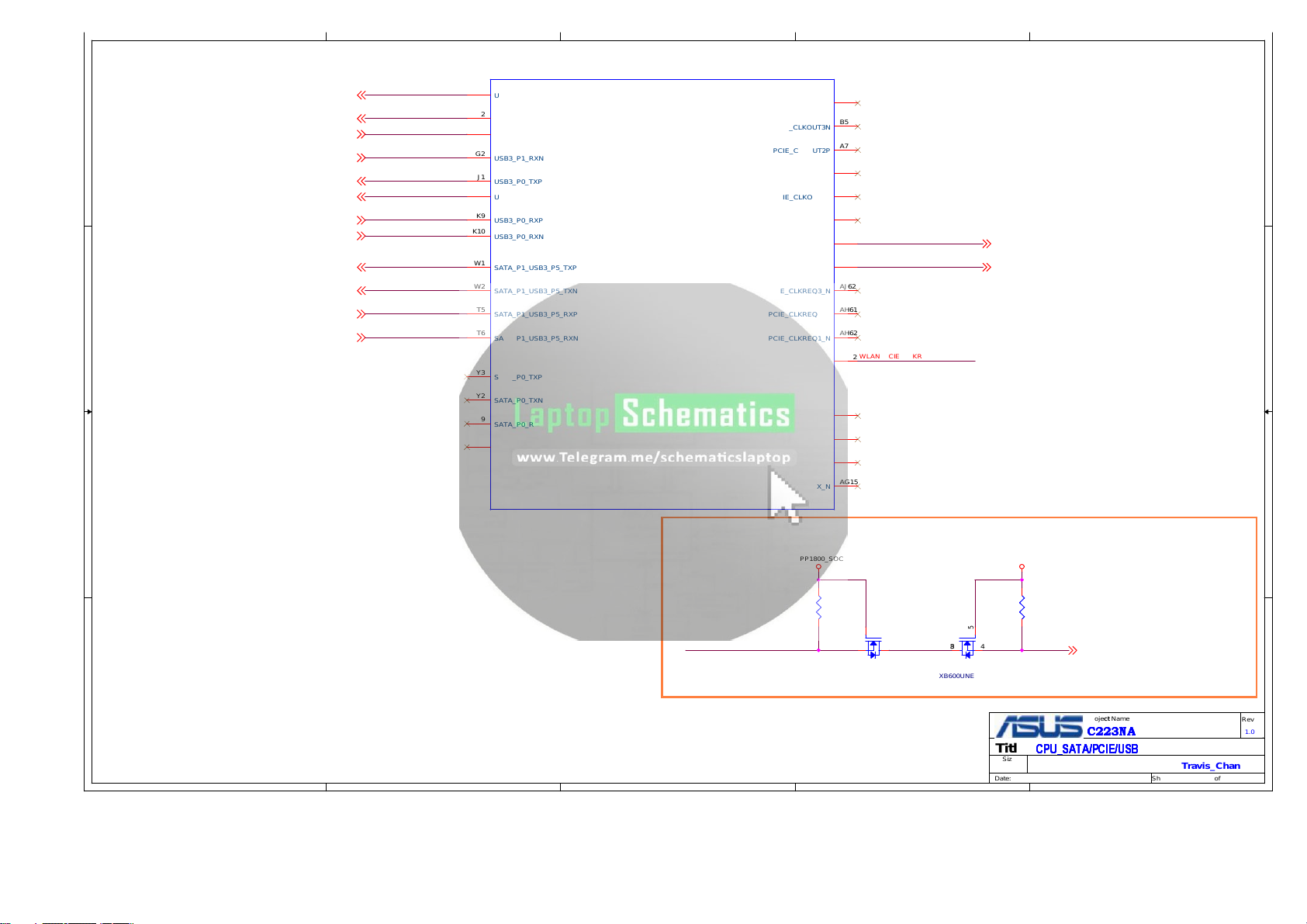

9 CPU_SATA/PCIE/USB

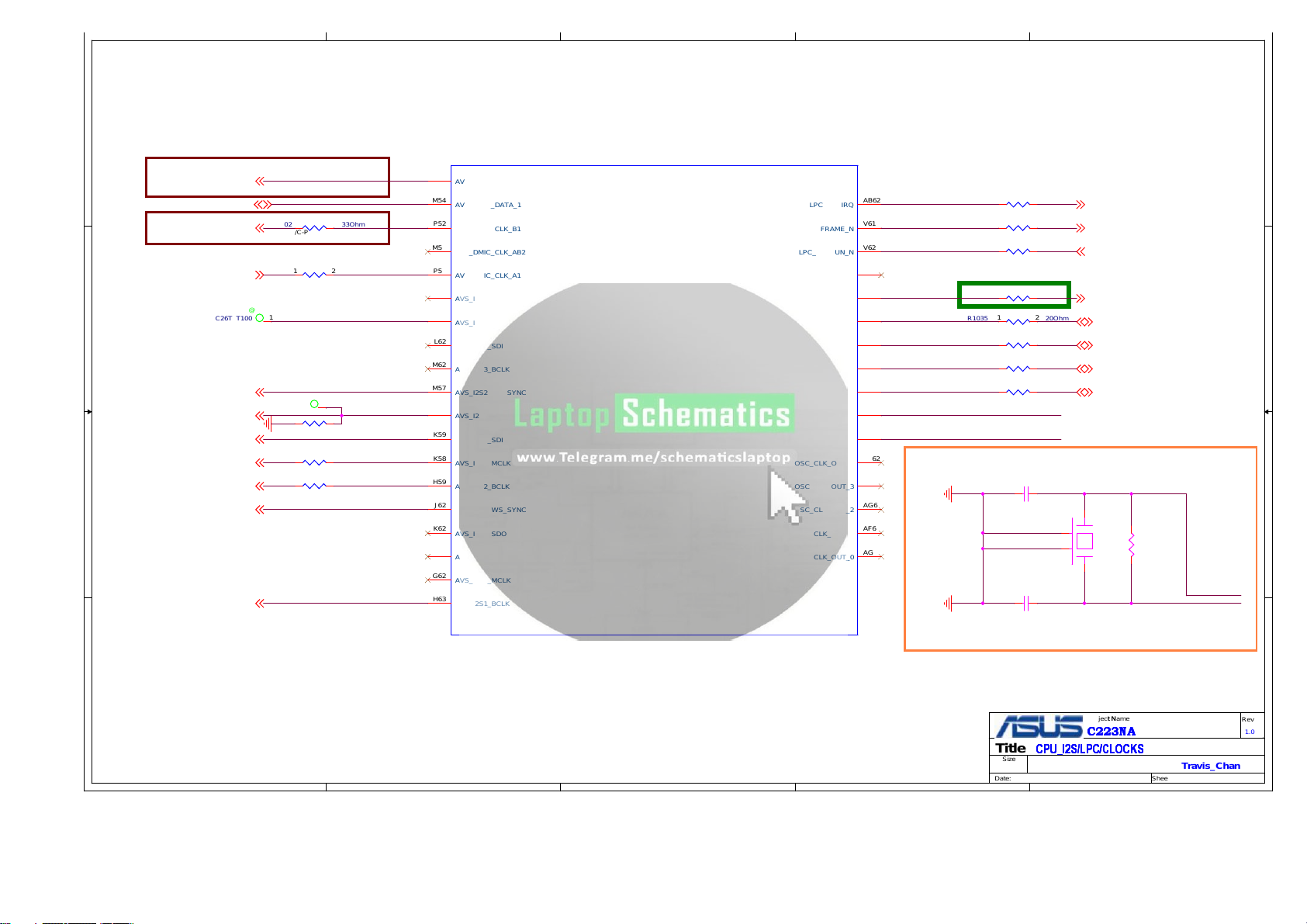

10 CPU_I2S/LPC/CLOCKS

11 CPU_SVID/SMBUS/USB2

12 CPU_SPI/I2C

13 CPU_PMU/UART

14 CPU_GPIO

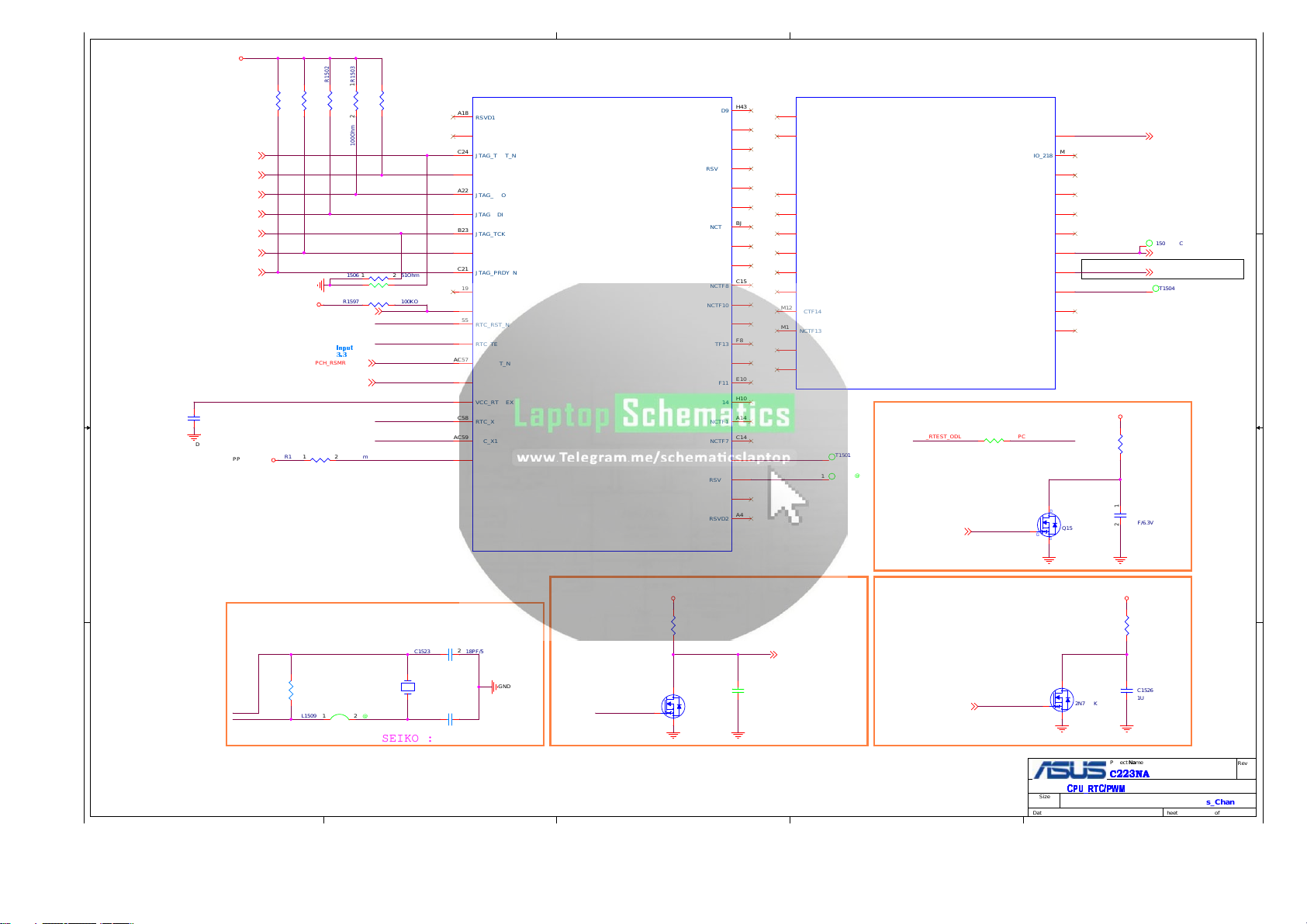

15 CPU_RTC/PWM

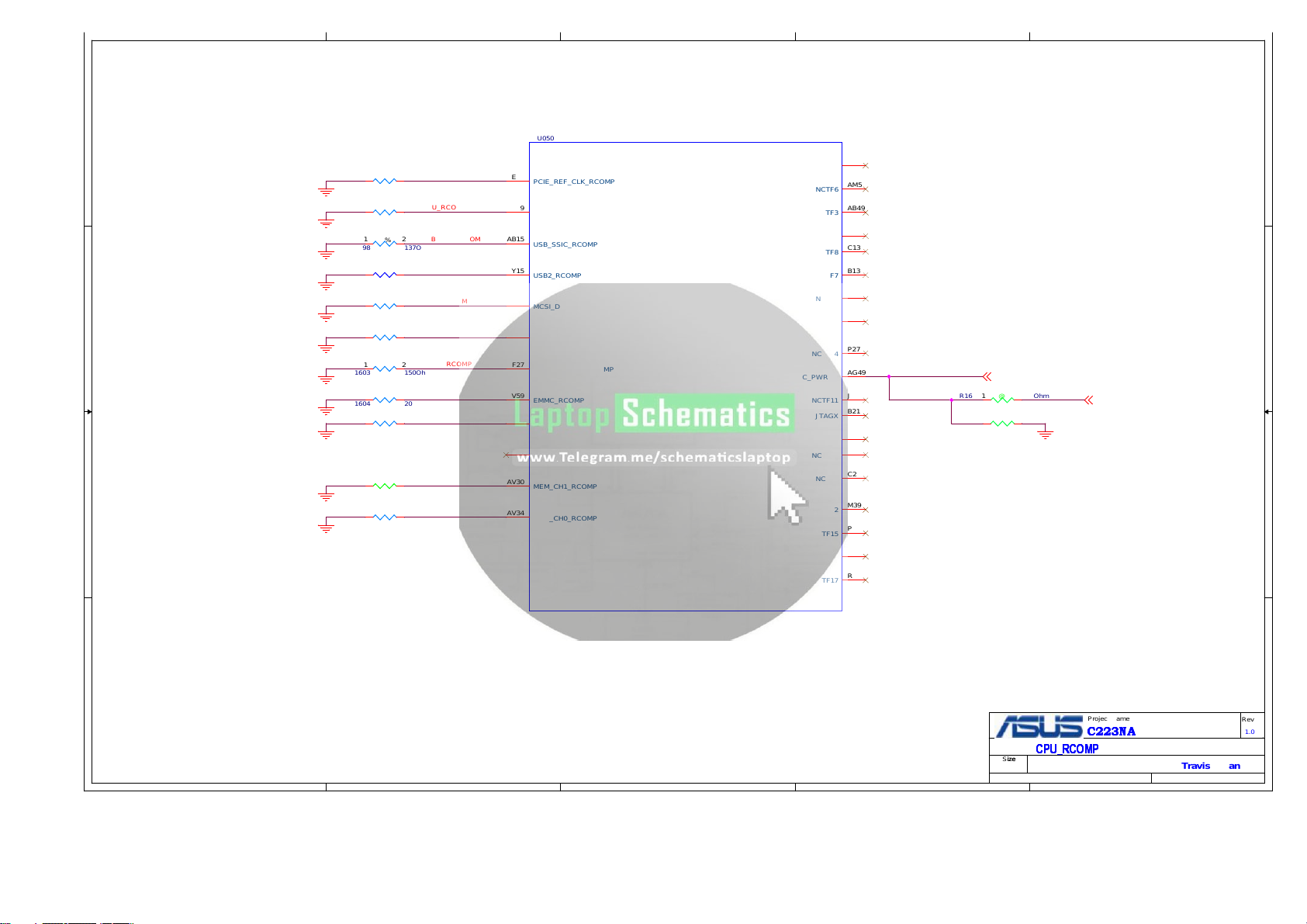

16 CPU_RCOMP

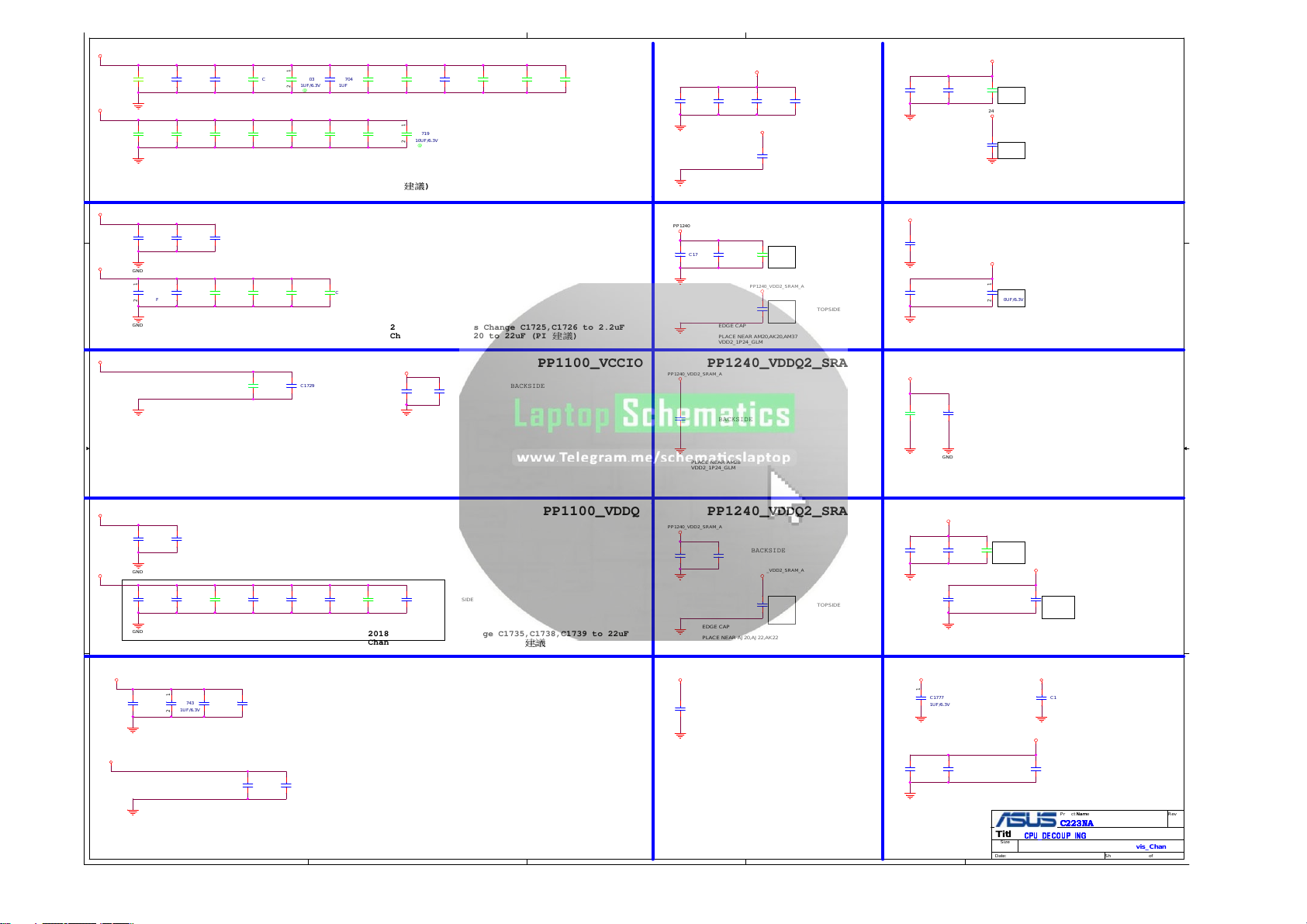

17 CPU_DECOUPLING

C C

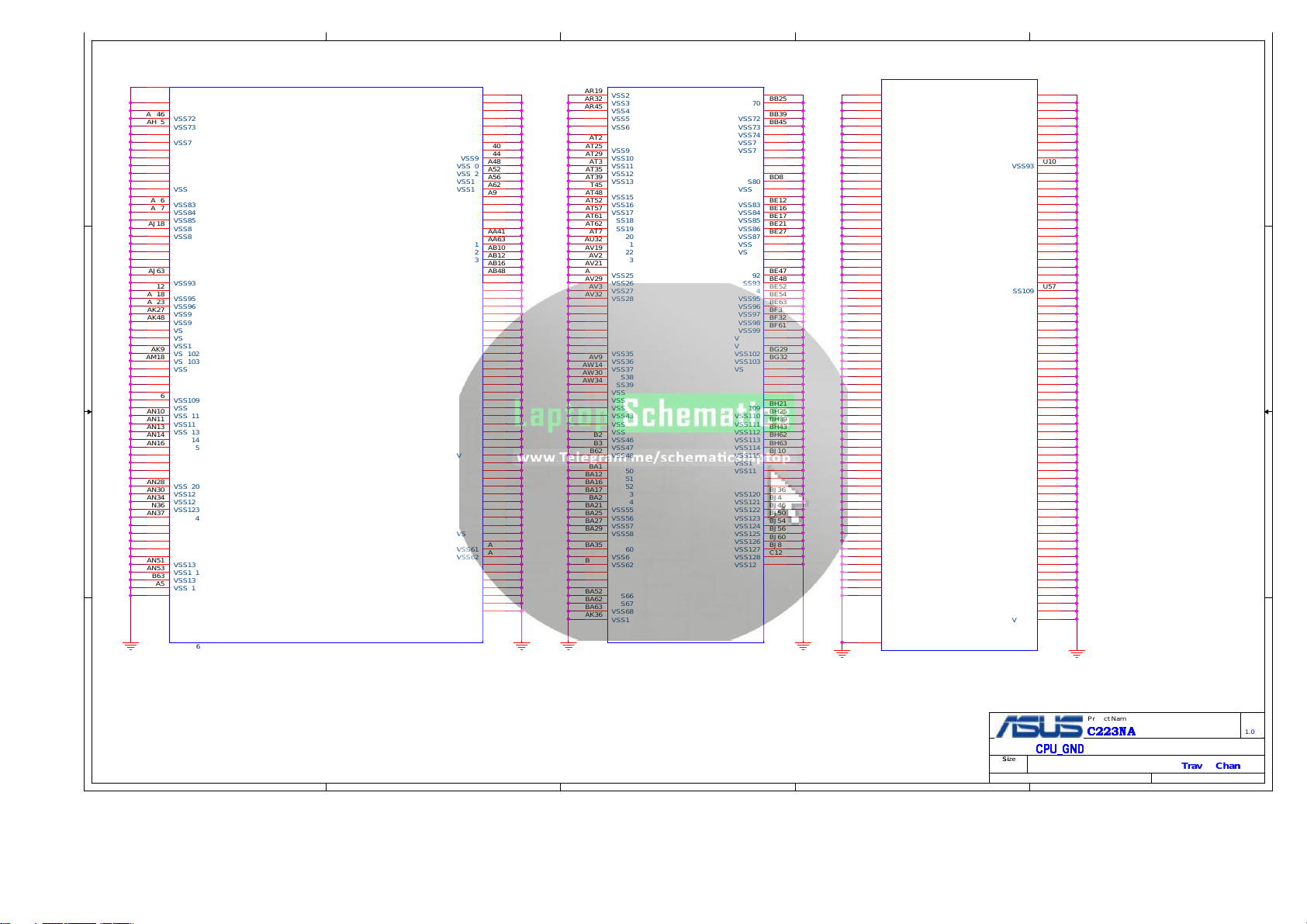

18 CPU_GND

19 CPU_POWER

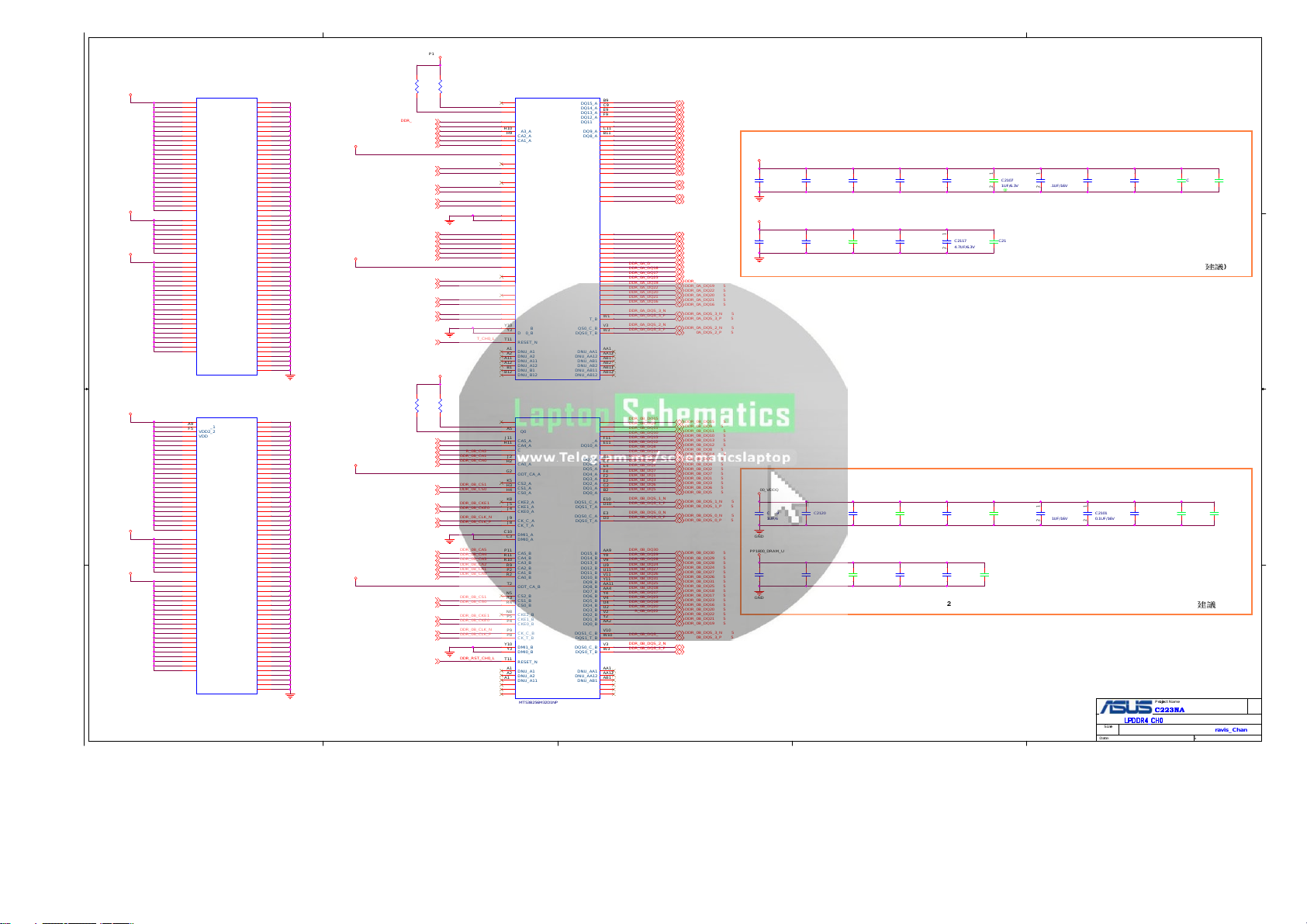

21 LPDDR4_CH0

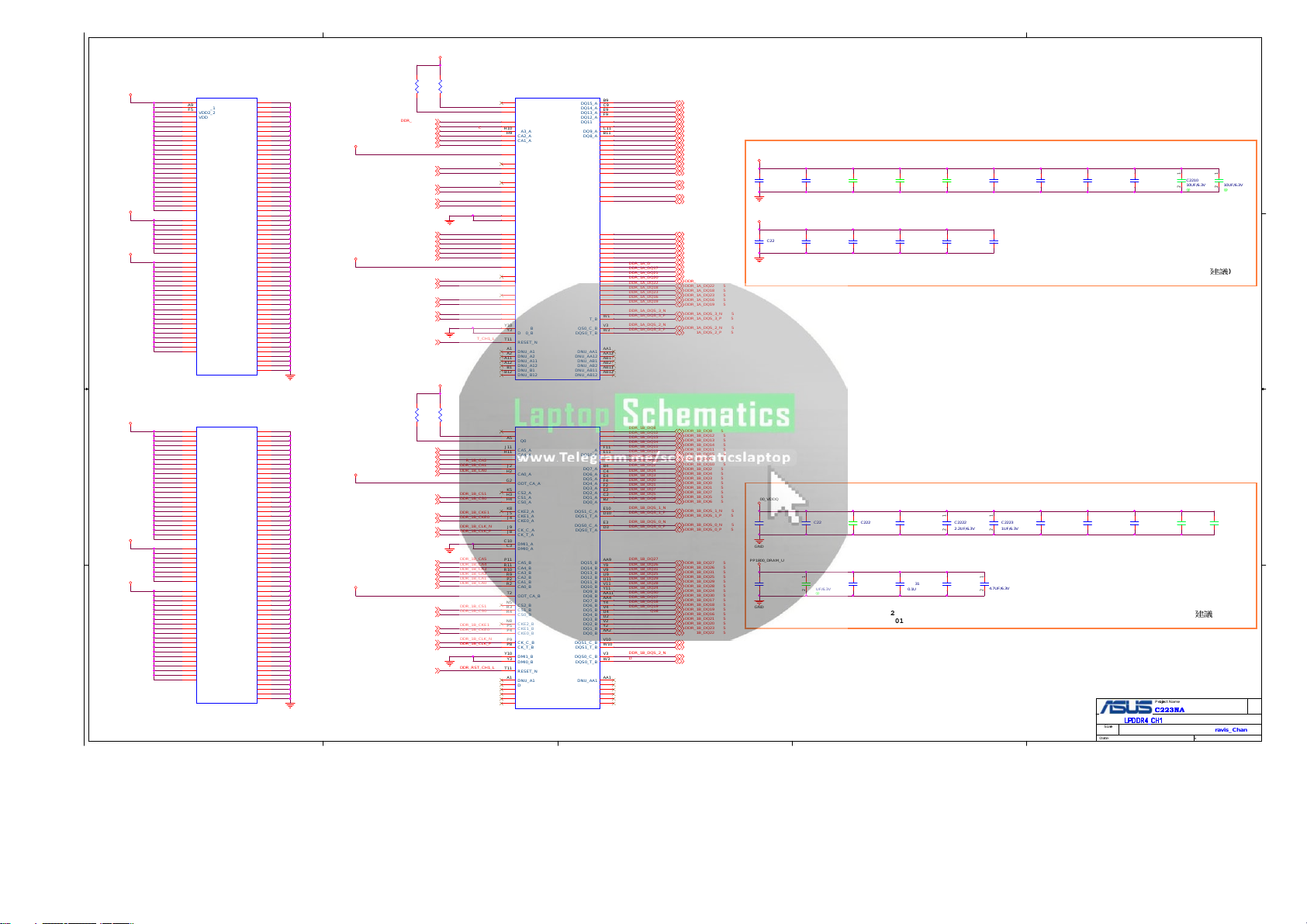

22 LPDDR4_CH1

28 SPI ROM

29 MIPI60 Debug

30 EC_NPCX586GA0BX

31 KB_TP

32 SERVO Debug

34 INAs

35 H1 SECURE

36 Audio Codec_DA7219

40 uSD

41 Type-C MUX

42 Type-C PWR

B B

43 Type-C Conn

44 Type-A Conn

45 EDP/CAM/TCH

46 PEN/CAM2

48 GYRO+ACCEL+COMPASS/LED

49 EMI

51 eMMC

52 Type-A Conn

53 WLAN

60 Battery Conn

61 B-to-B Conn

65 SCREW HOLE

67 IO_B-to-B Conn

68 IO_TypeC

A A

69 IO_TypeA

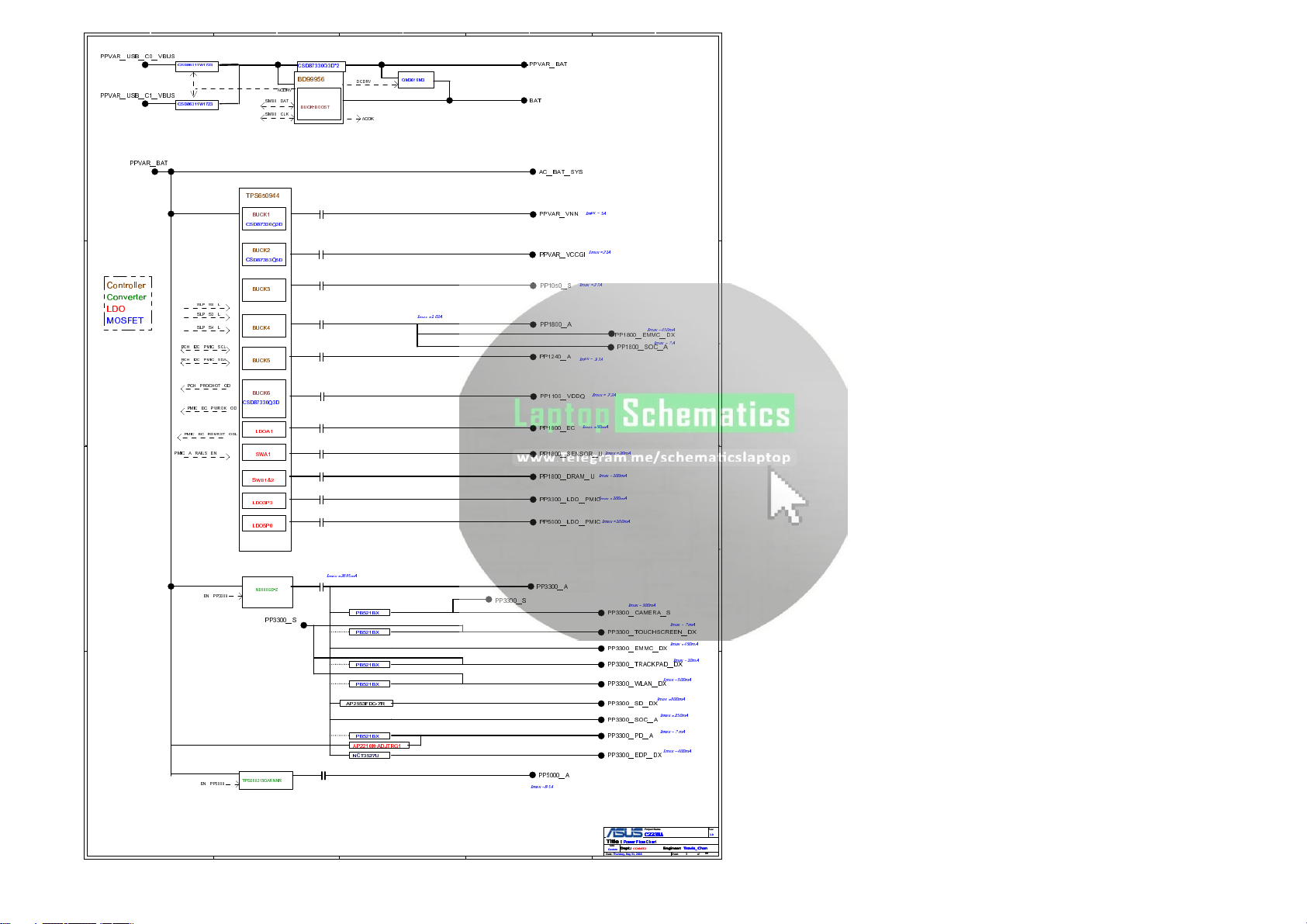

80 POWER-PMIC LOGIC

81 POWER-PMIC RAILS

83 POWER-LOAD SWITCHES

87 PW_+3VADSW/+5VSUS

89 POWER-CHARGER

5

IO Board

BLOCK DIAGRAM

LPDDR4 4GB

eMMC

uSD

SPI ROM

MIPI60

Debug Conn.

combo-Jack

Page 36

INT.SPEAKER

Page 36

SPI ROM

Keyboard

Audio Codec

DA7219-02VB6

SPEAKER AMP

MAX98357AETE+

Page 28

Page 31

ࣰ࣭ࣦ

ࣦ࣏࣠ࢽ࣍ ࣦ࣏࣠ࢽ࣍ ࣦ࣏࣠ࢽ࣎ ࣦ࣏࣠ࢽ࣐

TYPE-C

Page 42

4

Page 51

Page 40

Page 28

Page 29

Page 36

Page 36

NPCX586GA0BX

TYPE-C DB

SCHEMATIC Revision 1.2

࣭࣡

ࣦ࣡࣡ࢽ࣍

ࣦ࣡࣡ࢽ࣎

ࣰࣲࣟࢽ࣐࣋࣍

ࣰࣲࣟࢽ࣏࣋࣍

ࣦ࣏࣠ࢽ࣑

Page21/22

ࣩ࣭࣯࣑࣡࣡

ࣦ࣭ࣦ࣓࣪࣍

ࣰࣦ࣏

ࣰࣦ࣏

ࣰ࣭ࣦ

࣪࣪࣠

ࣰ࣡

CPU

Apollo Lake

Touch Pad

Page 48

ࣩ࣭࣠

Charger

EC SERVO

Page 30

Gyro & Accl & Compass

Sensor

BMI 160 + BMM 150

ࣰ࣭ࣦ

Debug Conn.

Page 89Page 68

R1.1

3

USB 3.0 Type C

/W BC1.2

ࣦ࣏࣠ࢽ࣏

Page 31

EDP Panel

Page 45

Type-C Port 0

Type-C Port 1

࣭ࢽ࣍ ࣭ࢽ࣒

Page 41

࣭ࢽ࣍ ࣭ࢽ࣎

࣭ࢽ࣓

H1

Page 35

ࣦ࣏࣠ࢽ࣐

Touch Screen

࣭ࣦ࣠ࢽ࣑

Page 32

2

MUX

Page 42

Page 68

࣭ࢽ࣑

USB 3.0 Type A

/W BC1.2

Page 45

Page 52

࣭ࢽ࣏

࣭ࢽ࣒

ࣦ࣏࣠ࢽ࣒

WLAN

BT

Combo Module

USB 3.0 Type C

/W BC1.2

PEN

Page 46

Page 53

USB 3.0 Type A

/W BC1.2

Page 68

࣭ࢽ࣑

CAMERA

Page 45

Camera Module

R1.1

Project Name

Project Name

Project Name

C223NA

C223NA

Block Diagram

Block Diagram

Block Diagram

CCNB/EE2

CCNB/EE2

CCNB/EE2

Dept.:

Dept.:

Dept.:

C223NA

1

Title :

Title :

Title :

Size

Size

Size

Custom

Custom

Custom

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

IO Board

࣭ࢽ࣎

Page 69

࣭ࢽ࣐

࣭ࢽࣔ

CAMERA 2

Page 46

Camera Module

Engineer:

Engineer:

Engineer:

R1.1

Travis_Chan

Travis_Chan

Travis_Chan

1

1

1

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

D D

4

3

2

1

Function options

-----------------------------------------------Touch screen | /touch screen STUFF

| /touch screen@ DO NOT STUFF

------------------------------------------------

H1 SuzyQ | /H1_Debug STUFF

------------------------------------------------

C C

B B

IO_TypeA | /IO_TypeA STUFF

| /IO_TypeA@ DO NOT STUFF

------------------------------------------------

Gyro+Accel | /Gyro+Accel STUFF

| /Gyro+Accel@ DO NOT STUFF

------------------------------------------------

MIPI60 | /MIPI60 STUFF

| /MIPI60@ DO NOT STUFF

------------------------------------------------

ME PWRBTN | /Mech_PWRBTN STUFF

------------------------------------------------

INAS | /INAS STUFF

------------------------------------------------

SERVO Board | /SERVO STUFF

------------------------------------------------

Convertible | /Flip STUFF

2ND camera |/C-PANEL CAMERA STUFF

Pen sensor | /PEN

Function options table

C223NA | C423NA | C523NA

---------------------STUFF---------------------------N/A | N/A | N/A

/EMI | /EMI | /EMI

/SERVO | /SERVO | /SERVO

/H1_Debug | /H1_Debug | /H1_Debug

/INAS | /INAS | /INAS

/MIPI60 | /MIPI60 | /MIPI60

/Mech_PWRBTN | /Mech_PWRBTN | /Mech_PWRBTN

| /IO_TypeA | /IO_TypeA

| /touch screen(If need) |

C223NA/C423NA/C523NA

BOM option table (NPI)

C223NA | C423NA | C523NA

---------------------STUFF---------------------------N/A | N/A | N/A

/EMI | /EMI | /EMI

/SERVO | /SERVO | /SERVO

/H1_Debug | /H1_Debug | /H1_Debug

/INAS | /INAS | /INAS

/MIPI60 | /MIPI60 | /MIPI60

/Mech_PWRBTN | /Mech_PWRBTN | /Mech_PWRBTN

|/IO_TypeA | /IO_TypeA

| /touch screen(If need) |

C223NA/C423NA/C523NA

BOM option table (R1.1)

A A

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

Title :

Title :

Title :

Sku Table/BOM Options

Sku Table/BOM Options

Sku Table/BOM Options

Size

Size

Size

B

B

B

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

5

4

3

2

Thursday, May 31, 2018

Dept.:

Dept.:

Dept.:

CCNB/EE2

CCNB/EE2

CCNB/EE2

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

2

2

2

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

339$586%&9%86

339$586%&9%86

D D

&6':

&6':

339$5%$7

4

%'

%8&.%2267

3

2

1

400

736

&6'4'

%8&.

&6'4'

&RQWUROOHU

&RQYHUWHU

/'2

026)(7

C C

6/36/

6/36/

6/36/

3&+,&30,&6&/

3&+,&30,&6'$

3&+352&+272'

%8&.

%8&.

%8&.

%8&.

&6'4'

/'2$

6:$

Imax =1.02A

6:%

/'23

/'23

B B

Imax = 5A

336

Imax =21A

Imax =2.7A

33$

Imax = 1.3A

339''4

Imax =50mA

33(&

336(16258

33'5$08

33/'230,&

33/'230,&

33(00&';

3362&$

Imax = 7.2A

Imax =20mA

Imax =100mA

Imax =100mA

Imax =100mA

Imax =450mA

Imax =?A

Imax =2695mA

3%%;

3%%;

(133

336

3%%;

3%%;

$3)'&5

3%%;

A A

7362$5115

(133

5

4

$3.$'-75*

1&78

3

336

33$

Imax =8.5A

2

Imax =300mA

33&$0(5$6

33728&+6&5((1';

33(00&';

3375$&.3$'';

33:/$1';

336'';

3362&$

333'$

33('3';

Title :

Power Flow Chart

Title :

Power Flow Chart

Title :

Power Flow Chart

Size

Size

Size

Dept.:

Dept.:

Dept.:

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Thursday, May 31, 2 018

Thursday, May 31, 2 018

Thursday, May 31, 2 018

CCNB/EE2

CCNB/EE2

CCNB/EE2

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

Imax =500mA

Imax =800mA

Imax =150mA

Imax =?mA

Imax =400mA

Engineer:

Engineer:

Engineer:

1

Imax =?mA

Imax =450mA

Imax =10mA

Travis_Chan

Travis_Chan

Travis_Chan

3

3

3

Rev

Rev

Rev

99

99

99

of

of

of

1.0

1.0

1.0

5

D D

C C

4

3

2

1

B B

A A

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

Title :

Title :

Title :

Size

Size

Size

B

B

B

Date: Sheet of

Thursday, May 31, 2018

Thursday, May 31, 2018

Thursday, May 31, 2018

Date: Sheet

5

4

3

2

Date: Sheet

Dept.:

Dept.:

Dept.:

CCNB/EE2

CCNB/EE2

CCNB/EE2

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

4

4

4

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

of

of

5

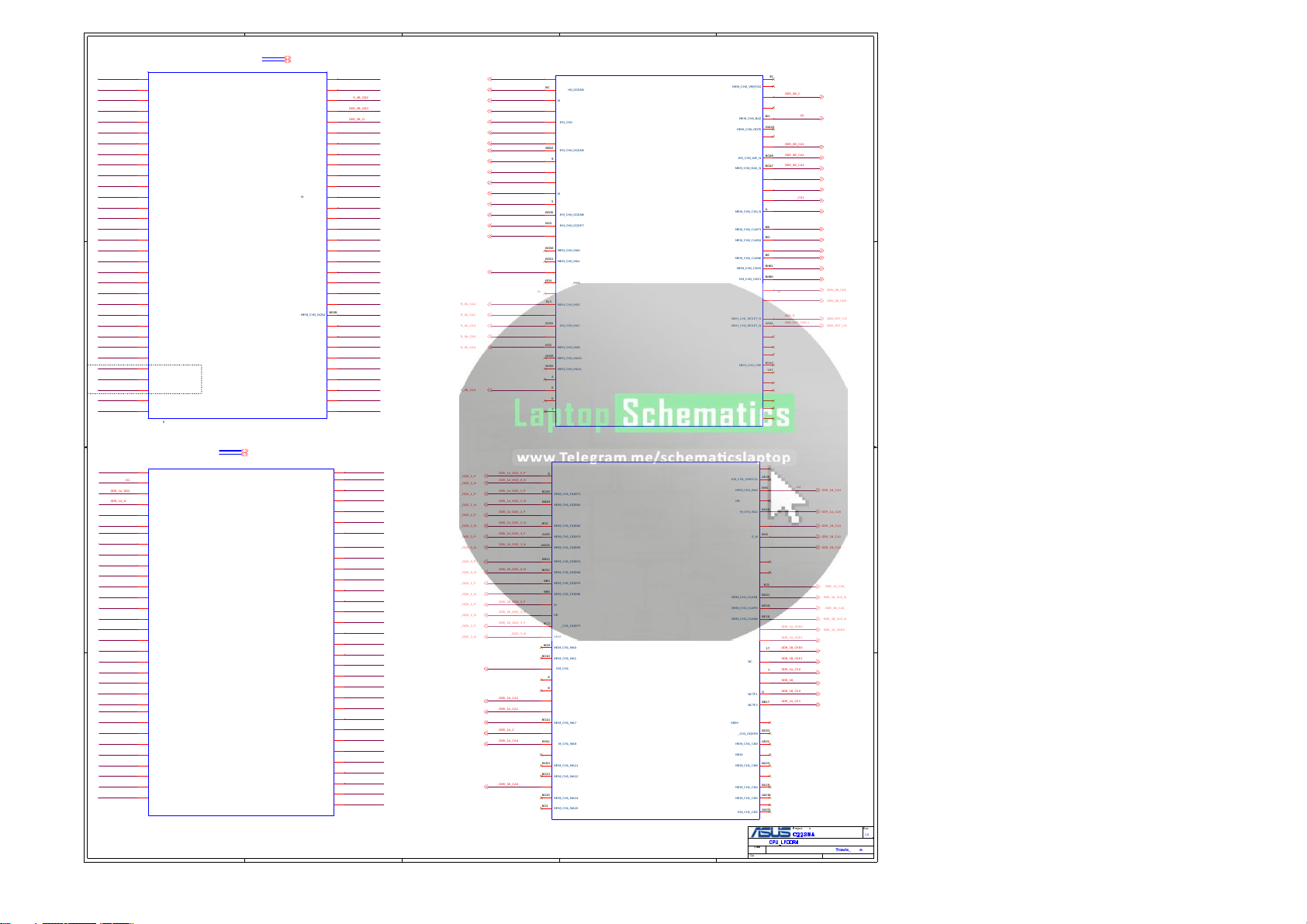

U0501A

DDR_0A_DQ0

AY62

MEM_CH0_DQ0

DDR_0A_DQ1

AY61

MEM_CH0_DQ1

DDR_0A_DQ2

BE62

MEM_CH0_DQ2

DDR_0A_DQ3

BG62

MEM_CH0_DQ3

DDR_0A_DQ4

BD63

MEM_CH0_DQ4

DDR_0A_DQ5

AW62

D D

C C

B B

A A

MEM_CH0_DQ5

DDR_0A_DQ6

AW63

MEM_CH0_DQ6

DDR_0A_DQ7

BD62

MEM_CH0_DQ7

DDR_0A_DQ8

AV59

MEM_CH0_DQ8

DDR_0A_DQ9

AU63

MEM_CH0_DQ9

DDR_0A_DQ10

AU62

MEM_CH0_DQ10

DDR_0A_DQ11

AV58

MEM_CH0_DQ11

DDR_0A_DQ12

AV57

MEM_CH0_DQ12

DDR_0A_DQ13

AT55

MEM_CH0_DQ13

DDR_0A_DQ14

AT54

MEM_CH0_DQ14

DDR_0A_DQ15

AY59

MEM_CH0_DQ15

DDR_0A_DQ16

AY57

MEM_CH0_DQ16

DDR_0A_DQ17

BB57

MEM_CH0_DQ17

DDR_0A_DQ18

BD59

MEM_CH0_DQ18

DDR_0A_DQ19

BF59

MEM_CH0_DQ19

DDR_0A_DQ20

AV54

MEM_CH0_DQ20

DDR_0A_DQ21

AY55

MEM_CH0_DQ21

DDR_0A_DQ22

AV52

MEM_CH0_DQ22

DDR_0A_DQ23

BD58

MEM_CH0_DQ23

DDR_0A_DQ24

BE56

MEM_CH0_DQ24

DDR_0A_DQ25

BD54

MEM_CH0_DQ25

DDR_0A_DQ26

BF58

MEM_CH0_DQ26

DDR_0A_DQ27

BE50

MEM_CH0_DQ27

DDR_0A_DQ29

BB50

MEM_CH0_DQ29

DDR_0A_DQ28

BD50

MEM_CH0_DQ28

DDR_0A_DQ30

BA50

MEM_CH0_DQ30

DDR_0A_DQ31

BB54

MEM_CH0_DQ31

BGA1296

DDR_1A_DQ[31:0] 22

U0501C

DDR_1A_DQ0 DDR_1B_DQ0

BJ26

MEM_CH1_DQ0

DDR_1A_DQ1

BG30

MEM_CH1_DQ1

DDR_1A_DQ2

BH31

MEM_CH1_DQ2

DDR_1A_DQ3

BG31

MEM_CH1_DQ3

DDR_1A_DQ4

BH27

MEM_CH1_DQ4

DDR_1A_DQ5

BG27

MEM_CH1_DQ5

DDR_1A_DQ6

BG26

MEM_CH1_DQ6

DDR_1A_DQ7

BJ30

MEM_CH1_DQ7

DDR_1A_DQ8

BA30

MEM_CH1_DQ8

DDR_1A_DQ9

BB30

MEM_CH1_DQ9

DDR_1A_DQ10

BE30

MEM_CH1_DQ10

DDR_1A_DQ11

BD30

MEM_CH1_DQ11

DDR_1A_DQ12

BE25

MEM_CH1_DQ12

DDR_1A_DQ13

BB27

MEM_CH1_DQ13

DDR_1A_DQ14

BD25

MEM_CH1_DQ14

DDR_1A_DQ15

BD27

MEM_CH1_DQ15

DDR_1A_DQ16

BG24

MEM_CH1_DQ16

DDR_1A_DQ17

BJ20

MEM_CH1_DQ17

DDR_1A_DQ18

BH23

MEM_CH1_DQ18

DDR_1A_DQ19

BJ24

MEM_CH1_DQ19

DDR_1A_DQ20

BG20

MEM_CH1_DQ20

DDR_1A_DQ21

BG21

MEM_CH1_DQ21

DDR_1A_DQ22

BH19

MEM_CH1_DQ22

DDR_1A_DQ23

BG25

MEM_CH1_DQ23

DDR_1A_DQ24

AT27

MEM_CH1_DQ24

DDR_1A_DQ25

AW29

MEM_CH1_DQ25

DDR_1A_DQ26

AR27

MEM_CH1_DQ26

DDR_1A_DQ27

AT23

MEM_CH1_DQ27

DDR_1A_DQ28

AV27

MEM_CH1_DQ28

DDR_1A_DQ29

AR25

MEM_CH1_DQ29

DDR_1A_DQ30

AR23

MEM_CH1_DQ30

DDR_1A_DQ31

AW27

MEM_CH1_DQ31

BGA1296

5

DDR_1B_DQ[31:0] 22

4

CHA: LPDDR4

DDR_0A_DQ[31:0] 21

DDR_0B_DQ[31:0] 21

AR39

MEM_CH0_DQ32

AV37

MEM_CH0_DQ33

AW37

MEM_CH0_DQ34

AR37

MEM_CH0_DQ35

AT37

MEM_CH0_DQ36

AT41

MEM_CH0_DQ37

AR41

MEM_CH0_DQ38

AW35

MEM_CH0_DQ39

BJ44

MEM_CH0_DQ40

BG39

MEM_CH0_DQ41

BG40

MEM_CH0_DQ42

BJ40

MEM_CH0_DQ43

BG43

MEM_CH0_DQ44

BG44

MEM_CH0_DQ45

BH45

MEM_CH0_DQ46

BH41

MEM_CH0_DQ47

BA34

MEM_CH0_DQ48

BE34

MEM_CH0_DQ49

BD34

MEM_CH0_DQ50

BD37

MEM_CH0_DQ51

BB37

MEM_CH0_DQ52

BE39

MEM_CH0_DQ53

BD39

MEM_CH0_DQ54

BB34

MEM_CH0_DQ55

BJ38

MEM_CH0_DQ56

BG34

MEM_CH0_DQ57

BG33

MEM_CH0_DQ58

BH33

MEM_CH0_DQ59

BG38

MEM_CH0_DQ60

BH37

MEM_CH0_DQ61

BG37

MEM_CH0_DQ62

BJ34

MEM_CH0_DQ63

CHB:LPDDR4

BF6

MEM_CH1_DQ32

BD10

MEM_CH1_DQ33

BE14

MEM_CH1_DQ34

BB10

MEM_CH1_DQ35

BA14

MEM_CH1_DQ36

BB14

MEM_CH1_DQ37

BD14

MEM_CH1_DQ38

BE8

MEM_CH1_DQ39

AV12

MEM_CH1_DQ40

BD6

MEM_CH1_DQ41

BD5

MEM_CH1_DQ42

BB7

MEM_CH1_DQ43

AV10

MEM_CH1_DQ44

AY9

MEM_CH1_DQ45

AY7

MEM_CH1_DQ46

BF5

MEM_CH1_DQ47

AU2

MEM_CH1_DQ48

AT10

MEM_CH1_DQ49

AT9

MEM_CH1_DQ50

AU1

MEM_CH1_DQ51

AY5

MEM_CH1_DQ52

AV5

MEM_CH1_DQ53

AV6

MEM_CH1_DQ54

AV7

MEM_CH1_DQ55

AY2

MEM_CH1_DQ56

BD2

MEM_CH1_DQ57

BD1

MEM_CH1_DQ58

BE2

MEM_CH1_DQ59

AW1

MEM_CH1_DQ60

AW2

MEM_CH1_DQ61

AY3

MEM_CH1_DQ62

BG2

MEM_CH1_DQ63

4

DDR_0B_DQ0

DDR_0B_DQ1

DDR_0B_DQ2

DDR_0B_DQ3

DDR_0B_DQ4

DDR_0B_DQ5

DDR_0B_DQ6

DDR_0B_DQ7

DDR_0B_DQ8

DDR_0B_DQ9

DDR_0B_DQ10

DDR_0B_DQ11

DDR_0B_DQ12

DDR_0B_DQ13

DDR_0B_DQ14

DDR_0B_DQ15

DDR_0B_DQ16

DDR_0B_DQ17

DDR_0B_DQ18

DDR_0B_DQ19

DDR_0B_DQ20

DDR_0B_DQ21

DDR_0B_DQ22

DDR_0B_DQ23

DDR_0B_DQ24

DDR_0B_DQ25

DDR_0B_DQ26

DDR_0B_DQ27

DDR_0B_DQ28

DDR_0B_DQ29

DDR_0B_DQ30

DDR_0B_DQ31

DDR_1B_DQ1

DDR_1B_DQ2

DDR_1B_DQ3

DDR_1B_DQ4

DDR_1B_DQ5

DDR_1B_DQ6

DDR_1B_DQ7

DDR_1B_DQ8

DDR_1B_DQ9

DDR_1B_DQ10

DDR_1B_DQ11

DDR_1B_DQ12

DDR_1B_DQ13

DDR_1B_DQ14

DDR_1B_DQ15

DDR_1B_DQ16

DDR_1B_DQ17

DDR_1B_DQ18

DDR_1B_DQ19

DDR_1B_DQ20

DDR_1B_DQ21

DDR_1B_DQ22

DDR_1B_DQ23

DDR_1B_DQ24

DDR_1B_DQ25

DDR_1B_DQ26

DDR_1B_DQ27

DDR_1B_DQ28

DDR_1B_DQ29

DDR_1B_DQ30

DDR_1B_DQ31

3

DDR_0A_DQS_0_P21

DDR_0A_DQS_0_N21

DDR_0A_DQS_1_P21

DDR_0A_DQS_1_N21

DDR_0A_DQS_2_P21

DDR_0A_DQS_2_N21

DDR_0A_DQS_3_P21

DDR_0A_DQS_3_N21

DDR_0B_DQS_0_P21

DDR_0B_DQS_0_N21

DDR_0B_DQS_1_P21

DDR_0B_DQS_1_N21

DDR_0B_DQS_2_P21

DDR_0B_DQS_2_N21

DDR_0B_DQS_3_P21

DDR_0B_DQS_3_N21

DDR_1A_DQS_0_P22

DDR_1A_DQS_0_N22

DDR_1A_DQS_1_P22

DDR_1A_DQS_1_N22

DDR_1A_DQS_2_P22

DDR_1A_DQS_2_N22

DDR_1A_DQS_3_P22

DDR_1A_DQS_3_N22

DDR_1B_DQS_0_P22

DDR_1B_DQS_0_N22

DDR_1B_DQS_1_P22

DDR_1B_DQS_1_N22

DDR_1B_DQS_2_P22

DDR_1B_DQS_2_N22

DDR_1B_DQS_3_P22

DDR_1B_DQS_3_N22

DDR_1B_CA522

DDR_1A_CA222

DDR_1A_CA122

DDR_1A_CA322

DDR_1A_CA022

DDR_1A_CA422

DDR_1B_CA022

DDR_0A_DQS_0_P

DDR_0A_DQS_0_N

DDR_0A_DQS_1_P

DDR_0A_DQS_1_N

DDR_0A_DQS_2_P

DDR_0A_DQS_2_N

DDR_0A_DQS_3_P

DDR_0A_DQS_3_N

DDR_0B_DQS_0_P

DDR_0B_DQS_0_N

DDR_0B_DQS_1_P

DDR_0B_DQS_1_N

DDR_0B_DQS_2_P

DDR_0B_DQS_2_N

DDR_0B_DQS_3_P

DDR_0B_DQS_3_N

DDR_0B_CA5

DDR_0B_CA521

DDR_0A_CA2

DDR_0A_CA221

DDR_0A_CA1

DDR_0A_CA121

DDR_0A_CA3

DDR_0A_CA321

DDR_0A_CA0

DDR_0A_CA021

DDR_0A_CA4

DDR_0A_CA421

DDR_0B_CA0

DDR_0B_CA021

DDR_1A_DQS_0_P

DDR_1A_DQS_0_N

DDR_1A_DQS_1_P

DDR_1A_DQS_1_N

DDR_1A_DQS_2_P

DDR_1A_DQS_2_N

DDR_1A_DQS_3_P

DDR_1A_DQS_3_N

DDR_1B_DQS_0_P

DDR_1B_DQS_0_N

DDR_1B_DQS_1_P

DDR_1B_DQS_1_N

DDR_1B_DQS_2_P

DDR_1B_DQS_2_N

DDR_1B_DQS_3_P

DDR_1B_DQS_3_N

DDR_1B_CA5

DDR_1A_CA2

DDR_1A_CA1

DDR_1A_CA3

DDR_1A_CA0

DDR_1A_CA4

DDR_1B_CA0

3

U0501B

BB63

MEM_CH0_DQSP0

BC62

MEM_CH0_DQSN0

AT59

MEM_CH0_DQSP1

AT58

MEM_CH0_DQSN1

BB59

MEM_CH0_DQSP2

BB58

MEM_CH0_DQSN2

BD52

MEM_CH0_DQSP3

BB52

MEM_CH0_DQSN3

AV39

MEM_CH0_DQSP4

AW39

MEM_CH0_DQSN4

BJ42

MEM_CH0_DQSP5

BG42

MEM_CH0_DQSN5

BB35

MEM_CH0_DQSP6

BD35

MEM_CH0_DQSN6

BG36

MEM_CH0_DQSP7

BH35

MEM_CH0_DQSN7

BG50

MEM_CH0_MA0

BG51

MEM_CH0_MA1

BH51

MEM_CH0_MA2

BD41

NC

MEM_CH0_MA3

BE41

NC

MEM_CH0_MA4

BJ52

MEM_CH0_MA5

BG53

MEM_CH0_MA6

BG55

MEM_CH0_MA7

BH53

MEM_CH0_MA8

BG52

MEM_CH0_MA9

BH49

MEM_CH0_MA10

BH55

MEM_CH0_MA11

BG54

MEM_CH0_MA12

BG46

MEM_CH0_MA13

BG56

MEM_CH0_MA14

BG57

MEM_CH0_MA15

BGA1296

U0501D

BG28

MEM_CH1_DQSP0

BH29

MEM_CH1_DQSN0

BD29

MEM_CH1_DQSP1

BB29

MEM_CH1_DQSN1

BJ22

MEM_CH1_DQSP2

BG22

MEM_CH1_DQSN2

AV25

MEM_CH1_DQSP3

AW25

MEM_CH1_DQSN3

BB12

MEM_CH1_DQSP4

BD12

MEM_CH1_DQSN4

BB5

MEM_CH1_DQSP5

BB6

MEM_CH1_DQSN5

AT5

MEM_CH1_DQSP6

AT6

MEM_CH1_DQSN6

BC2

MEM_CH1_DQSP7

BB1

MEM_CH1_DQSN7

BG9

MEM_CH1_MA0

BG10

MEM_CH1_MA1

BH9

MEM_CH1_MA2

BD16

MEM_CH1_MA3

BB16

MEM_CH1_MA4

BG11

MEM_CH1_MA5

BJ12

MEM_CH1_MA6

BG14

MEM_CH1_MA7

BG12

MEM_CH1_MA8

BH11

MEM_CH1_MA9

BG7

MEM_CH1_MA10

BH13

MEM_CH1_MA11

BG13

MEM_CH1_MA12

BH3

MEM_CH1_MA13

BG15

MEM_CH1_MA14

BG16

MEM_CH1_MA15

BGA1296

2

VCCIOA

Notes:

1. Please tie VCCIOA to

VNN_SVID for DDR3L and

LPDDR3 designs

2. Please tie VCCIOA to

VDDQ for LPDDR4

designs

2

AR35

MEM_CH0_VREFCA

AT34

MEM_CH0_VREFDQ

BJ48

MEM_CH0_BA0

BG49

MEM_CH0_BA1

BH57

MEM_CH0_BA2

AW43

MEM_CH0_ODT0

AW41

MEM_CH0_ODT1

BH47

MEM_CH0_CAS_N

BG48

MEM_CH0_WE_N

BG47

MEM_CH0_RAS_N

AT43

NCTF1

BB41

NCTF2

BA41

MEM_CH0_CS1_N

AR43

MEM_CH0_CS0_N

BB48

MEM_CH0_CLKP1

BD48

MEM_CH0_CLKN1

BD45

MEM_CH0_CLKP0

BE45

MEM_CH0_CLKN0

BH61

MEM_CH0_CKE0

BH60

MEM_CH0_CKE1

BH58

NCTF3

BJ58

NCTF4

AR30

MEM_CH1_RESET_N

AR34

MEM_CH0_RESET_N

BD47

MEM_CH0_DQSP8

BB47

MEM_CH0_DQSN8

BA45

MEM_CH0_CB7

BD43

MEM_CH0_CB6

AV47

MEM_CH0_CB5

AV48

MEM_CH0_CB4

AW45

MEM_CH0_CB3

BB43

MEM_CH0_CB2

AW47

MEM_CH0_CB1

AW48

MEM_CH0_CB0

AT30

MEM_CH1_VREFDQ

AR29

MEM_CH1_VREFCA

BH6

MEM_CH1_BA0

BG8

MEM_CH1_BA1

BH15

MEM_CH1_BA2

BJ6

MEM_CH1_RAS_N

BH4

MEM_CH1_CAS_N

BH7

MEM_CH1_WE_N

AW16

MEM_CH1_ODT0

AV16

MEM_CH1_ODT1

BB21

MEM_CH1_CLKP1

BD21

MEM_CH1_CLKN1

BD19

MEM_CH1_CLKP0

BE19

MEM_CH1_CLKN0

BG18

MEM_CH1_CKE0

BG17

MEM_CH1_CKE1

BH17

NCTF3

BJ16

NCTF4

CS0_0A

BD17

MEM_CH1_CS0_N

AW17

CS2_1B

MEM_CH1_CS1_N

AV17

CS1_0B

NCTF1

BB17

CS3_1A

NCTF2

BE23

MEM_CH1_DQSN8

BD23

MEM_CH1_DQSP8

AR21

MEM_CH1_CB0

AT21

MEM_CH1_CB1

BA23

MEM_CH1_CB6

AW21

MEM_CH1_CB3

BA19

MEM_CH1_CB4

AW19

MEM_CH1_CB5

BB23

MEM_CH1_CB7

AW23

MEM_CH1_CB2

Title :

CPU_LPDDR4

Title :

CPU_LPDDR4

Title :

CPU_LPDDR4

Size

Size

Size

Dept.:

Dept.:

Dept.:

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Thursday, May 31, 2018

Thursday, May 31, 2018

Thursday, May 31, 2018

B4

A5

B1

B2

B3

1A

1B

CS1_0B

CS0_0A

0A

1A

0B

1B

DDR_1B_CA4

DDR_1A_CA5

DDR_1B_CA3

DDR_1B_CA1

DDR_1B_CA2

DDR_1A_CLK_P

DDR_1A_CLK_N

DDR_1B_CLK_P

DDR_1B_CLK_N

DDR_1A_CKE0

DDR_1A_CKE1

DDR_1B_CKE0

DDR_1B_CKE1

DDR_1A_CS0

DDR_1B_CS1

DDR_1B_CS0

DDR_1A_CS1

CCNB/EE2

CCNB/EE2

CCNB/EE2

1

DDR_0B_CA4

DDR_0A_CA5

DDR_0B_CA1

DDR_0B_CA2

DDR_0B_CA3

DDR_0A_CS1

DDR_0B_CS0

DDR_0B_CS1

DDR_0A_CS0

DDR_0A_CLK_P

DDR_0A_CLK_N

DDR_0B_CLK_P

DDR_0B_CLK_N

DDR_0A_CKE0

DDR_0A_CKE1

DDR_0B_CKE0

DDR_0B_CKE1

DDR_RST_CH1_L

DDR_RST_CH0_L

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

1

DDR_1B_CA4 22

DDR_1A_CA5 22

DDR_1B_CA3 22

DDR_1B_CA1 22

DDR_1B_CA2 22

DDR_1A_CLK_N 22

DDR_1B_CLK_N 22

DDR_1A_CKE0 22

DDR_1A_CKE1 22

DDR_1B_CKE0 22

DDR_1B_CKE1 22

DDR_1A_CS0 22

DDR_1B_CS1 22

DDR_1B_CS0 22

DDR_1A_CS1 22

Engineer:

Engineer:

Engineer:

DDR_0B_CA4 21

DDR_0A_CA5 21

DDR_0B_CA1 21

DDR_0B_CA2 21

DDR_0B_CA3 21

DDR_0A_CS1 21

DDR_0B_CS0 21

DDR_0B_CS1 21

DDR_0A_CS0 21

DDR_0A_CLK_P 21

DDR_0A_CLK_N 21

DDR_0B_CLK_P 21

DDR_0B_CLK_N 21

DDR_0A_CKE0 21

DDR_0A_CKE1 21

DDR_0B_CKE0 21

DDR_0B_CKE1 21

DDR_RST_CH1_L 22

DDR_RST_CH0_L 21

DDR_1A_CLK_P 22

DDR_1B_CLK_P 22

Travis_Chan

Travis_Chan

Travis_Chan

5

5

5

Rev

Rev

Rev

99

99

99

of

of

of

1.0

1.0

1.0

5

U0501E

B49

DDI0_DDC_SCL

C49

DDI0_DDC_SDA

A54

DDI1_DDC_SCL

C54

DDI1_DDC_SDA

AH10

AG12

AG10

AH9

AG5

AG6

AG7

AG9

AC6

AC5

AC7

AC9

EDP_AUXP

EDP_AUXN

EDP_RCOMP_N

EDP_RCOMP_P

EDP_TXP_0

EDP_TXN_0

EDP_TXP_1

EDP_TXN_1

EDP_TXP_2

EDP_TXN_2

EDP_TXP_3

EDP_TXN_3

BGA1296

EDP

USB_C1_HPD _1V8_ODL30,61

USB_C0_HPD _1V8_ODL30,41

EDP_AUX_P45

EDP_AUX_N45

EDP_TX0_P45

EDP_TX0_N45

EDP_TX1_P45

EDP_TX1_N45

R0603 402Ohm1%

1 2

AP12

AP10

AR2

AR1

AP15

AP13

AP6

AP5

AP2

AP3

B51

C51

A50

C50

M45

M43

U0501F

MDSI_A_DP_0

MDSI_A_DN_0

MDSI_A_DP_1

MDSI_A_DN_1

MDSI_A_DP_2

MDSI_A_DN_2

MDSI_A_DP_3

MDSI_A_DN_3

MDSI_A_CLKP

MDSI_A_CLKN

MIPI_I2C_SDA

MIPI_I2C_SCL

GPIO_199

GPIO_200

MDSI_A_TE

MDSI_C_TE

BGA1296

EDP_RCOMP_N

EDP_RCOMP_P

D D

C C

B B

A A

4

AK3

DDI0_TXP_0

AK2

DDI0_TXN_0

AM3

DDI0_TXP_1

AM2

DDI0_TXN_1

AH3

DDI0_TXP_2

AH2

DDI0_TXN_2

AL2

DDI0_TXP_3

AL1

DDI0_TXN_3

DDI0_RCOMP_P

DDI0_RCOMP_N

DDI0_AUXP

DDI0_AUXN

DDI1_AUXP

DDI1_AUXN

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_TXP_2

DDI1_TXN_2

DDI1_TXN_3

DDI1_TXP_3

MDSI_C_DP_0

MDSI_C_DN_0

MDSI_C_DP_1

MDSI_C_DN_1

MDSI_C_DP_2

MDSI_C_DN_2

MDSI_C_DP_3

MDSI_C_DN_3

MDSI_C_CLKP

MDSI_C_CLKN

PNL0_VDDEN

PNL0_BKLTEN

PNL0_BKLTCTL

PNL1_VDDEN

PNL1_BKLTEN

PNL1_BKLTCTL

AK7

AK6

AM5

AM6

AM12

AM10

AK13

AM13

AM9

AM7

C47

B47

C46

C52

B53

C53

AG1

AG2

AM16

AM15

AK16

AK15

AF2

AF3

AD3

AD2

AC1

AC2

AB2

AB3

DDI0_RCOMP_P

DDI0_RCOMP_N

EN_PP3300_EDP_D X 83

SOC_EDP_BKLT EN 45

SOC_EDP_BKLT CTL_1V8 45

1 2

R0604 402Ohm1%

3

DDI0_TX0_P 41

DDI0_TX0_N 4 1

DDI0_TX1_P 41

DDI0_TX1_N 4 1

DDI0_TX2_P 41

DDI0_TX2_N 4 1

DDI0_TX3_P 41

DDI0_TX3_N 4 1

DDI0_AUX_P 41

DDI0_AUX_N 41

DDI1_AUX_P 61

DDI1_AUX_N 61

DDI1_TX0_P 61

DDI1_TX0_N 6 1

DDI1_TX1_P 61

DDI1_TX1_N 6 1

DDI1_TX2_P 61

DDI1_TX2_N 6 1

DDI1_TX3_N 6 1

DDI1_TX3_P 61

ALL 1.8V

Display DDI 0

Type-C PORT 0

Display DDI 1

Type-C Port 1

U0501G

P17

MCSI_DP_0

M17

MCSI_DN_0

P21

MCSI_DP_1

R21

MCSI_DN_1

L17

MCSI_DP_2

J17

MCSI_DN_2

F17

MCSI_DP_3

E17

MCSI_DN_3

M19

MCSI_CLKP_0

L19

MCSI_CLKN_0

H19

MCSI_CLKP_2

F19

MCSI_CLKN_2

L37

GP_CAMERASB0

P34

GP_CAMERASB1

J34

GP_CAMERASB2

H30

GP_CAMERASB3

M37

GP_CAMERASB4

F30

GP_CAMERASB5

BGA1296

2

MCSI_RX_DATA0_P

MCSI_RX_DATA0_N

MCSI_RX_CLK0_P

MCSI_RX_CLK0_N

MCSI_RX_DATA1_P

MCSI_RX_DATA1_N

MCSI_RX_DATA2_P

MCSI_RX_DATA2_N

MCSI_RX_CLK1_P

MCSI_RX_CLK1_N

MCSI_RX_DATA3_P

MCSI_RX_DATA3_N

GP_CAMERASB6

GP_CAMERASB7

GP_CAMERASB8

GP_CAMERASB9

GP_CAMERASB10

GP_CAMERASB11

1

M23

P23

L23

J23

J21

H21

M25

L25

F25

E25

H25

J25

R35

L34

M34

M35

R34

E30

Project Name

Project Name

Project Name

C223NA

C223NA

CPU_Display

CPU_Display

CPU_Display

CCNB/EE2

CCNB/EE2

CCNB/EE2

Dept.:

Dept.:

Dept.:

C223NA

1

Engineer:

Engineer:

Engineer:

Title :

Title :

Title :

Size

Size

Size

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Thursday, May 31, 2018

Thursday, May 31, 2018

5

4

3

2

Thursday, May 31, 2018

Travis_Chan

Travis_Chan

Travis_Chan

of

of

of

6

6

6

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

D D

C C

EN_SD_SOCKET_PWR_L83

SD_CLK40

PP1800_S

SD_CD_OD32,40

SD_CMD40

uSD

B B

SD_DATA340

SD_DATA240

SD_DATA140

SD_DATA040

1 2

R0703 100KOhm

SD_CLK

SD_CD_OD

SD_CMD

SD_DATA3

SD_DATA2

SD_DATA1

SD_DATA0

4

U0501H

T55

SDIO_D3

T54

SDIO_D2

P57

SDIO_D1

T52

SDIO_D0

T57

SDIO_CMD

P58

SDIO_CLK

P51

SDIO_PWR_DWN_N

AB58

SDCARD_CLK

AB54

SDCARD_CD_N

AB55

SDCARD_LVL_WP

AC52

SDCARD_CMD

AB51

SDCARD_D3

AC51

SDCARD_D2

AC48

SDCARD_D1

AC49

SDCARD_D0

3

EMMC_D7

EMMC_D6

EMMC_D5

EMMC_D4

EMMC_D3

EMMC_D2

EMMC_D1

EMMC_D0

EMMC_RCLK

EMMC_CMD

EMMC_CLK

V57

V55

Y49

V52

V51

T59

T58

V58

V54

Y51

Y58

2

EMMC_DAT7

EMMC_DAT6

EMMC_DAT5

EMMC_DAT4

EMMC_DAT3

EMMC_DAT2

EMMC_DAT1

EMMC_DAT0

EMMC_RCLK

EMMC_CMD

EMMC_CLK

EMMC_DAT7 51

EMMC_DAT6 51

EMMC_DAT5 51

EMMC_DAT4 51

EMMC_DAT3 51

EMMC_DAT2 51

EMMC_DAT1 51

EMMC_DAT0 51

EMMC_RCLK 51

EMMC_CMD 51

EMMC_CLK 51

1

eMMC

BGA1296

A A

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

Title :

Title :

Title :

CPU_SDIO/EMMC

CPU_SDIO/EMMC

CPU_SDIO/EMMC

Size

Size

Size

B

B

B

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

5

4

3

2

Thursday, May 31, 2018

Dept.:

Dept.:

Dept.:

CCNB/EE2

CCNB/EE2

CCNB/EE2

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

7

7

7

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

D D

4

U0501I

L2

PCIE_P5_USB3_P2_TXP

L1

PCIE_P5_USB3_P2_TXN

K7

PCIE_P5_USB3_P2_RXP

M7

PCIE_P5_USB3_P2_RXN

3

PCIE_P2_TXP

PCIE_P2_TXN

PCIE_P2_RXP

PCIE_P2_RXN

T2

T3

M5

M6

2

1

PCIE_PCH4TX_WLANRX_P53

WLAN

C C

U3 Type-A Port 0

B B

A A

5

PCIE_PCH4TX_WLANRX_N53

PCIE_PCH4RX_WLANTX_P53

PCIE_PCH4RX_WLANTX_N53

USB3_4_A0_TX_P44

USB3_4_A0_TX_N44

USB3_4_A0_RX_P44

USB3_4_A0_RX_N44

PCIE_USB3_RCOMP_P

1 2

R0810 402Ohm1%

PCIE_USB3_RCOMP_N

4

N2

PCIE_P4_USB3_P3_TXP

M2

PCIE_P4_USB3_P3_TXN

H5

PCIE_P4_USB3_P3_RXP

H6

PCIE_P4_USB3_P3_RXN

P3

PCIE_P3_USB3_P4_TXP

P2

PCIE_P3_USB3_P4_TXN

P12

PCIE_P3_USB3_P4_RXP

P10

PCIE_P3_USB3_P4_RXN

F6

PCIE2_USB3_SATA3_RCOMP_P

F5

PCIE2_USB3_SATA3_RCOMP_N

BGA1296

PCIE_P1_TXP

PCIE_P1_TXN

PCIE_P1_RXP

PCIE_P1_RXN

PCIE_P0_TXP

PCIE_P0_TXN

PCIE_P0_RXP

PCIE_P0_RXN

PCIE_WAKE3_N

PCIE_WAKE2_N

PCIE_WAKE1_N

PCIE_WAKE0_N

PP1800_SOC_A PP3300_WLAN_DX

12

R0803

10KOhm

WLAN_PCIE_WAKE_1V8_ODL WLAN_Q2

3

R1

R2

T10

T12

V3

V2

P7

P6

N62

P61

P62

R62

2

61 7

Q0804A

PMDXB600UNE

WLAN_PCIE_WAKE_1V8_ODL

5

3 48

Q0804B

PMDXB600UNE

2

WLAN WAKE

Level Shift

12

R0804

10KOhm

WLAN_PCIE_WAKE_3V3_ODL 53

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

Title :

Title :

Title :

CPU_USB3/PCIE

CPU_USB3/PCIE

CPU_USB3/PCIE

Size

Size

Size

B

B

B

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Dept.:

Dept.:

Dept.:

CCNB/EE2

CCNB/EE2

CCNB/EE2

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

8

8

8

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

USB3_1_A1_TX_P61

U3 Type-A Port 1

D D

U3 Type-C Port 0

U3 Type-C Port 1

C C

B B

USB3_1_A1_TX_N61

USB3_1_A1_RX_P61

USB3_1_A1_RX_N61

USB3_0_C0_TX_P41

USB3_0_C0_TX_N41

USB3_0_C0_RX_P41

USB3_0_C0_RX_N41

USB3_5_C1_TX_P61

USB3_5_C1_TX_N61

USB3_5_C1_RX_P61

USB3_5_C1_RX_N61

4

U0501J

K3

USB3_P1_TXP

K2

USB3_P1_TXN

F2

USB3_P1_RXP

G2

USB3_P1_RXN

J1

USB3_P0_TXP

J2

USB3_P0_TXN

K9

USB3_P0_RXP

K10

USB3_P0_RXN

W1

SATA_P1_USB3_P5_TXP

W2

SATA_P1_USB3_P5_TXN

T5

SATA_P1_USB3_P5_RXP

T6

SATA_P1_USB3_P5_RXN

Y3

SATA_P0_TXP

Y2

SATA_P0_TXN

T9

SATA_P0_RXP

T7

SATA_P0_RXN

BGA1296

3

PCIE_CLKOUT3P

PCIE_CLKOUT3N

PCIE_CLKOUT2P

PCIE_CLKOUT2N

PCIE_CLKOUT1P

PCIE_CLKOUT1N

PCIE_CLKOUT0P

PCIE_CLKOUT0N

PCIE_CLKREQ3_N

PCIE_CLKREQ2_N

PCIE_CLKREQ1_N

PCIE_CLKREQ0_N

USB_SSIC_0_TX_P

USB_SSIC_0_TX_N

USB_SSIC_0_RX_P

USB_SSIC_0_RX_N

B7

B5

A7

B8

C10

A10

C11

B11

AJ62

AH61

AH62

WLAN_PCIE_CLKREQ_1V8_ODL

AK62

AH13

AH12

AG16

AG15

2

WLAN_PCIE_CLK_P 53

WLAN_PCIE_CLK_N 53

1

PCIE WLAN CLK

WLAN CLKREQ

PP1800_SOC_A PP3300_WLAN_DX

12

R0901

10KOhm

2

WLAN_PCIE_CLKREQ_1V8_ODL WLAN_Q1

A A

5

4

3

61 7

Q0901A

PMDXB600UNE

PMDXB600UNE

2

5

3 48

Q0901B

12

R0902

10KOhm

Title :

Title :

Title :

CPU_SATA/PCIE/USB

CPU_SATA/PCIE/USB

CPU_SATA/PCIE/USB

Size

Size

Size

Dept.:

Dept.:

Dept.:

B

B

B

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Level Shift

WLAN_PCIE_CLKREQ_3V3_ODL 53

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

CCNB/EE2

CCNB/EE2

CCNB/EE2

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

9

9

9

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

D D

R1.1

DMIC_CAM2_DATA

1 2

/C-PANEL CAMERA

DMIC_CLK2_R

R1.1

DMIC_CAM2_DATA46

DMIC_DATA45 LPC_SERIRQ 30

DMIC_CLK246

R1002 33Ohm

2ND CAMERA DMIC

1 2

DMIC_CLK145

C C

I2S_SFRM_HP36

I2S_PCH_TX_HP_RX36

I2S_PCH_RX_HP_TX36

Audio Codec

B B

I2S_MCLK_HP36

I2S_SCLK_HP36

SPK_PA_EN36

PCH_WP_OD28

R1029 33Ohm

@

1

T1001TPC26T

T1002TPC26T @

R1039 2.2KOhm

GND

R1027 20Ohm

R1001 20Ohm

1

1 2

1 2

1 2

DMIC_CLK1_R

GPIO_92

I2S_MCLK_HP_R

I2S_SCLK_HP_R

SPK_PA_EN

PCH_WP_OD

4

U0501K

M52

AVS_DMIC_DATA_2

M54

AVS_DMIC_DATA_1

P52

AVS_DMIC_CLK_B1

M55

AVS_DMIC_CLK_AB2

P54

AVS_DMIC_CLK_A1

M61

AVS_I2S3_WS_SYNC

L63

AVS_I2S3_SDO

L62

AVS_I2S3_SDI

M62

AVS_I2S3_BCLK

M57

AVS_I2S2_WS_SYNC

M58

AVS_I2S2_SDO

K59

AVS_I2S2_SDI

K58

AVS_I2S2_MCLK

H59

AVS_I2S2_BCLK

J62

AVS_I2S1_WS_SYNC

K62

AVS_I2S1_SDO

K61

AVS_I2S1_SDI

G62

AVS_I2S1_MCLK

H63

AVS_I2S1_BCLK

3

LPC_AD3

LPC_AD2

LPC_AD1

LPC_AD0

OSCOUT

OSCIN

AB62

V61

V62

AA62

AB61

W63

W62

Y62

Y61

P29

R27

AF62

AE60

AG63

AF61

AG62

LPC_SERIRQ

LPC_FRAME_N

LPC_CLKRUN_N

LPC_CLKOUT1

LPC_CLKOUT0

OSC_CLK_OUT_4

OSC_CLK_OUT_3

OSC_CLK_OUT_2

OSC_CLK_OUT_1

OSC_CLK_OUT_0

2

LPC_SERIRQ_R

LPC_FRAME_L_R

LPC_CLKRUN_L_R

LPC_CLKOUT0_R

LPC_AD3_R

LPC_AD2_R

LPC_AD1_R

LPC_AD0_R

GND

GND

1

1 2

R1030 20Ohm

1 2

R1036 20Ohm

1 2

R1031 20Ohm

LPC_FRAME_L 30

LPC_CLKRUN_L 30

2018/5/08 Travis Change R1037 to 0 ohm

1 2

R1037 0Ohm

1 2

R1035 20Ohm

1 2

R1034 20Ohm

1 2

R1033 20Ohm

1 2

R1032 20Ohm

OSCOUT

OSCIN

LPC_CLKOUT0 30

LPC_AD3 30

LPC_AD2 30

LPC_AD1 30

LPC_AD0 30

EC

XTAL 19.2 MHZ

1 2

C1014 5.6PF/50V

13

X1001

19.2MHZ

2

4

1 2

C1015 5.6PF/50V

12

R1026

200KOhm

OSCIN

OSCOUT

BGA1296

A A

5

4

3

2

TXC : 07G010211920

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

Title :

Title :

Title :

CPU_I2S/LPC/CLOCKS

CPU_I2S/LPC/CLOCKS

CPU_I2S/LPC/CLOCKS

Size

Size

Size

B

B

B

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Dept.:

Dept.:

Dept.:

CCNB/EE2

CCNB/EE2

CCNB/EE2

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

10

10

10

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

4

3

2

1

D D

USB_TYPEC_OC_ODL

21

21

USB_TYPEA_OC_ODL

21

21

SVID_ALERT_L

USB2_OTG_ID

1 2

PP1050_S

C C

USB2_OTG_VBUSSENSE30

TRACKPAD_INT_GATE30,31

U2 Type-C OC

B B

U2 Type-A OC

USB_C0_OC_ODL42

USB_C1_OC_ODL42

USB_A0_OC_ODL44

USB_A1_OC_ODL44

R1130 10KOhm

1 2

R1129 0Ohm@

SL1101 @

0402

SL1102 @

0402

SL1103 @

0402

SL1104 @

0402

20K INTERNAL PU

A A

5

4

C18

C17

B17

T61

T62

R63

AC16

AC15

C55

B55

U0501L

SVID0_DATA

SVID0_CLK

SVID0_ALERT_B

SMB_DATA

SMB_CLK

SMB_ALERT_N

USB2_VBUS_SNS

USB2_OTG_ID

USB2_OC1_N

USB2_OC0_N

BGA1296

USB 2.0 USB 3.0

0

Type-C Port 0

1

Type-C Port 1

2

Type-A Port 0

3

Type-A Port 1

4

Camera

5

BT

6

H1 SECURITY KEY

USB3_P0

USB3_P1

PCIE_P5_USB3_P2

PCIE_P4_USB3_P3

PCIE_P3_USB3_P4

SATA_P1_USB3_P5

7

3

USB2_DP7

USB2_DN7

USB2_DP6

USB2_DN6

USB2_DP5

USB2_DN5

USB2_DP4

USB2_DN4

USB2_DP3

USB2_DN3

USB2_DP2

USB2_DN2

USB2_DP1

USB2_DN1

USB2_DP0

USB2_DN0

Type-C Port 0

Type-A Port 1

Type- A Port 0

Type-C Port 1

V5

V6

AC12

AC10

AB6

AB7

Y9

Y10

V9

V7

Y13

V13

V16

V15

V12

V10

2

USB2_7_CAM2_P

USB2_7_CAM2_N

USB2 Ports

USB2_7_CAM2_P 46

USB2_7_CAM2_N 46

USB2_6_HAVEN_P 35

USB2_6_HAVEN_N 35

USB2_5_BT_P 53

USB2_5_BT_N 53

USB2_4_CAM_P 45

USB2_4_CAM_N 45

USB2_3_A1_P 44

USB2_3_A1_N 44

USB2_2_A0_P 44

USB2_2_A0_N 44

USB2_1_C1_P 89

USB2_1_C1_N 89

USB2_0_C0_P 89

USB2_0_C0_N 89

Title :

Title :

Title :

Size

Size

Size

Dept.:

Dept.:

Dept.:

Custom

Custom

Custom

Thursday, May 31, 2018

Thursday, May 31, 2018

Thursday, May 31, 2018

Date: Sheet

Date: Sheet

Date: Sheet

USB2 Ports

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

CPU_SVID/SMBUS/USB2

CPU_SVID/SMBUS/USB2

CPU_SVID/SMBUS/USB2

CCNB/EE2

CCNB/EE2

CCNB/EE2

R1.1

H1 SECURITY KEY

BT

Camera

Type-A Port 1

Type-A Port 0

Type-C Port 1

Type-C Port 0

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

11

11

11

of

of

of

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

U0501M

PCH_SPI_MOSI28

PCH_SPI_MISO28

D D

PCH_SPI_CS0_L28

PCH_SPI_CLK28

T1201TPC26T @

SIO_SPI_2_TXD/GPIO12329

WLAN_PE_RST53

T1209TPC26T @

T1202TPC26T @

T1203TPC26T @

T1204TPC26T @

C C

B B

HP_INT_ODL36

T1210TPC26T @

T1205TPC26T @

T1206TPC26T @

T1211TPC26T @

T1212TPC26T @

SIO_SPI_0_FS1/GPIO10629

TPM_SPI_CS2_L35

T1207TPC26T @

T1208TPC26T @

CONFIG PIN 3 2 1 0

SAMSUNG 8GB K4F6E304HB

SAMSUNG 4GB K4F8E304HB

MICRON 8GB MT53B512M32D2NP-062WT:C

MICRON 4GB MT53B256M32D1NP-062 WT:C

HYNIX 8GB H9HCNNNBPUMLHR

HYNIX 4GB H9HCNNN8KUMLHR 0 1 0 1

MEMORY STRAPPING TABLE

1

1

1

1

1

1

1

1

R1254 2.2KOhm

GND

1

R1203 2.2KOhm@

GND

1

SL1201 @

1

1

PCH_MEM_CONFIG0

PCH_MEM_CONFIG1

GPIO_121

GPIO_120

GPIO_118

GPIO_117

HP_INT_ODL

GPIO_113

GPIO_112

GPIO_111

1 2

PCH_SPI_FP_MOSI

1 2

PCH_SPI_FP_MISO

0402

GPIO_105

GPIO_104

A58

FST_SPI_MOSI_IO0

B58

FST_SPI_MISO_IO1

B60

FST_SPI_IO2

B61

FST_SPI_IO3

C57

FST_SPI_CS1_N

B57

FST_SPI_CS0_N

C56

FST_SPI_CLK

E62

SIO_SPI_2_TXD

C62

SIO_SPI_2_RXD

D59

SIO_SPI_2_FS2

E56

SIO_SPI_2_FS1

D61

SIO_SPI_2_FS0

F62

SIO_SPI_2_CLK

H58

SIO_SPI_1_TXD

H57

SIO_SPI_1_RXD

F61

SIO_SPI_1_FS1

K55

SIO_SPI_1_FS0

F58

SIO_SPI_1_CLK

J52

SIO_SPI_0_TXD

H54

21

SIO_SPI_0_RXD

H52

SIO_SPI_0_FS1

F52

SIO_SPI_0_FS0

F54

SIO_SPI_0_CLK

BGA1296

0 00

0

0 0

0

0 0 1 1

0 1 0 0

0

1

010

12

R1201

2.2KOhm

GND GND

4

PCH_MEM_CONFIG1

PCH_MEM_CONFIG0

12

R1202

2.2KOhm

MEM Config

LPSS_I2C7_SDA

LPSS_I2C7_SCL

LPSS_I2C6_SDA

LPSS_I2C6_SCL

LPSS_I2C5_SDA

LPSS_I2C5_SCL

LPSS_I2C4_SDA

LPSS_I2C4_SCL

LPSS_I2C3_SDA

LPSS_I2C3_SCL

LPSS_I2C2_SDA

LPSS_I2C2_SCL

LPSS_I2C1_SDA

LPSS_I2C1_SCL

LPSS_I2C0_SDA

LPSS_I2C0_SCL

AP62

AP61

AL63

AK61

PCH_I2C_PEN_SDA

AP49

PCH_I2C_PEN_SCL

AP51

PCH_I2C_TRACKPAD_1V8_SDA

AP52

PCH_I2C_TRACKPAD_1V8_SCL

AP54

PCH_I2C_TOUCHSCREEN_1V8_SDA

AM62

PCH_I2C_TOUCHSCREEN_1V8_SCL

AL62

PCH_I2C_HAVEN_TPM_SDA

AP59

PCH_I2C_HAVEN_TPM_SCL

AP58

AN62

AM61

PCH_I2C_AUDIO_SDA

AR62

PCH_I2C_AUDIO_SCL

AR63

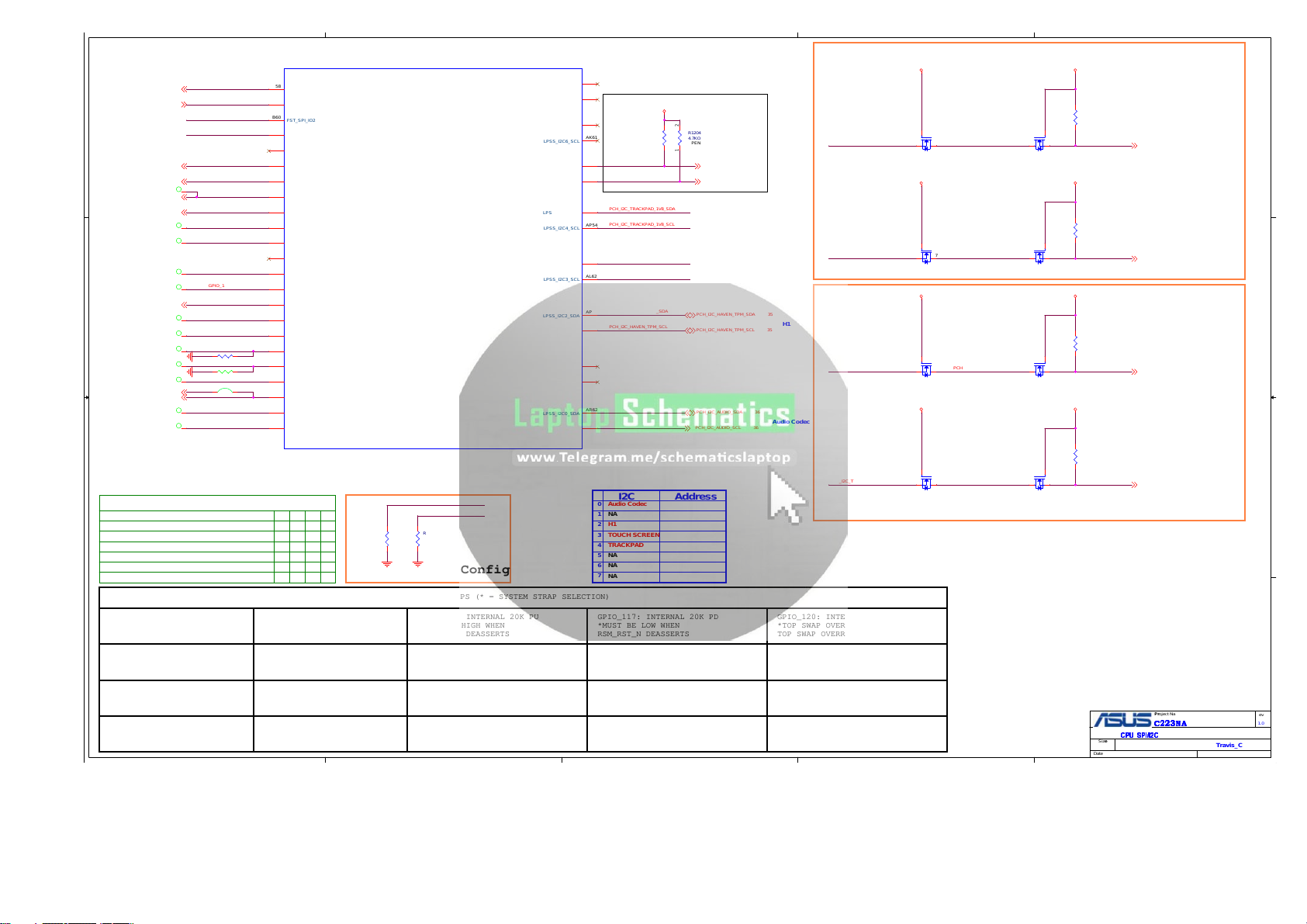

I2C

0

Audio Codec

1

NA

2

H1

3

TOUCH SCREEN

4

TRACKPAD

5

NA

6

NA

7

NA

PP1800_SENSOR_S

R1207

4.7KOhm

/PEN

3

1 2

1 2

Address

R1204

4.7KOhm

/PEN

I2C Ports

R1.1

PCH_I2C_PEN_SDA 46

PCH_I2C_PEN_SCL 46

Track PAD

Touch Screen

PCH_I2C_HAVEN_TPM_SDA 35

PCH_I2C_HAVEN_TPM_SCL 35

PCH_I2C_AUDIO_SDA 36

PCH_I2C_AUDIO_SCL 36

H1

Audio Codec

2

PP1800_SOC_A PP3300_TRACKPAD_DX

12

R1210

2

PCH_I2C_TCP_1V8_SCL_QPCH_I2C_TRACKPAD_1V8_SCL

61 7

Q1205A

PMDXB600UNE

PP1800_SOC_A PP3300_TRACKPAD_DX

2

PCH_I2C_TCP_1V8_SDA_QPCH_I2C_TRACKPAD_1V8_SDA

61 7

Q1206A

PMDXB600UNE

PP1800_SOC_A PP3300_TOUCHSCREEN_DX

2

PCH_I2C_TCS_1V8_SCL_QPCH_I2C_TOUCHSCREEN_1V8_SCL

61 7

Q1203A

PMDXB600UNE

/touch screen

PP1800_SOC_A PP3300_TOUCHSCREEN_DX

2

PCH_I2C_TCS_1V8_SDA_QPCH_I2C_TOUCHSCREEN_1V8_SDA

61 7

Q1204A

PMDXB600UNE

/touch screen

3 48

Q1205B

PMDXB600UNE

3 48

Q1206B

PMDXB600UNE

3 48

Q1203B

PMDXB600UNE

3 48

Q1204B

PMDXB600UNE

/touch screen

/touch screen

2.2KOhm

5

12

R1209

2.2KOhm

5

12

R1205

2.2KOhm

1%

/touch screen

5

12

R1206

2.2KOhm

1%

/touch screen

5

1

Track Pad

Level Shift

PCH_I2C_TRACKPAD_3V3_SCL 31

PCH_I2C_TRACKPAD_3V3_SDA 31

Touch Screen

Level Shift

PCH_I2C_TOUCHSCREEN_3V3_SCL 45

PCH_I2C_TOUCHSCREEN_3V3_SDA 45

HARDWARE STRAPS (* = SYSTEM STRAP SELECTION)

GPIO_39: INTERNAL 20K PD

*DISABLE CSE ROM BYPASS: 0

ENABLE CSE ROM BYPASS: 1

GPIO_40: INTERNAL 20K PD

*MUST BE LOW WHEN

A A

RSM_RST_N DEASSERTS

GPIO_43: INTERNAL 20K PU

ENABLE BOOT FROM EMMC: 1

*DISABLE BOOT FROM EMMC: 0

GPIO_44: INTERNAL 20K PU

*ENABLE BOOT FROM SPI: 1

DISABLE BOOT FROM SPI: 0

5

GPIO_47: INTERNAL 20K PD

*DON'T FORCE DNX FW LOAD: 0

FORCE DNX FW LOAD: 1

GPIO_48: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_104: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_105: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_106: INTERNAL 20K PU

*MUST BE HIGH WHEN

RSM_RST_N DEASSERTS

GPIO_111: INTERNAL 20K PU

DO NOT BOOT FROM SPI: 1

*BOOT FROM SPI: 0

GPIO_118: INTERNAL 20K PD

*NO FLASH DESCRIPTOR OVERRIDE: 0

OVERRIDE FLASH DESCRIPTOR: 1

GPIO_110: INTERNAL 20K PU

LPC BUFFERS AT 1.8V: 1

*LPC BUFFERS AT 3.3V: 0

4

GPIO_117: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_123: INTERNAL 20K PU

*MUST BE HIGH WHEN

RSM_RST_N DEASSERTS

GPIO_112: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

GPIO_113: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

3

GPIO_120: INTERNAL 20K PD

*TOP SWAP OVERRIDE DISABLE: 0

TOP SWAP OVERRIDE ENABLE: 1

GPIO_121: INTERNAL 20K PD

*MUST BE LOW WHEN

RSM_RST_N DEASSERTS

Project Name

Project Name

Project Name

C223NA

C223NA

CPU_SPI/I2C

CPU_SPI/I2C

CPU_SPI/I2C

Dept.:

Dept.:

Dept.:

CCNB/EE2

CCNB/EE2

CCNB/EE2

C223NA

1

Engineer:

Engineer:

Engineer:

Title :

Title :

Title :

Size

Size

Size

Custom

Custom

Custom

Thursday, May 31, 2018

Thursday, May 31, 2018

Thursday, May 31, 2018

Date: Sheet

Date: Sheet

2

Date: Sheet

Travis_Chan

Travis_Chan

Travis_Chan

12

12

12

of

of

of

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

4

3

2

1

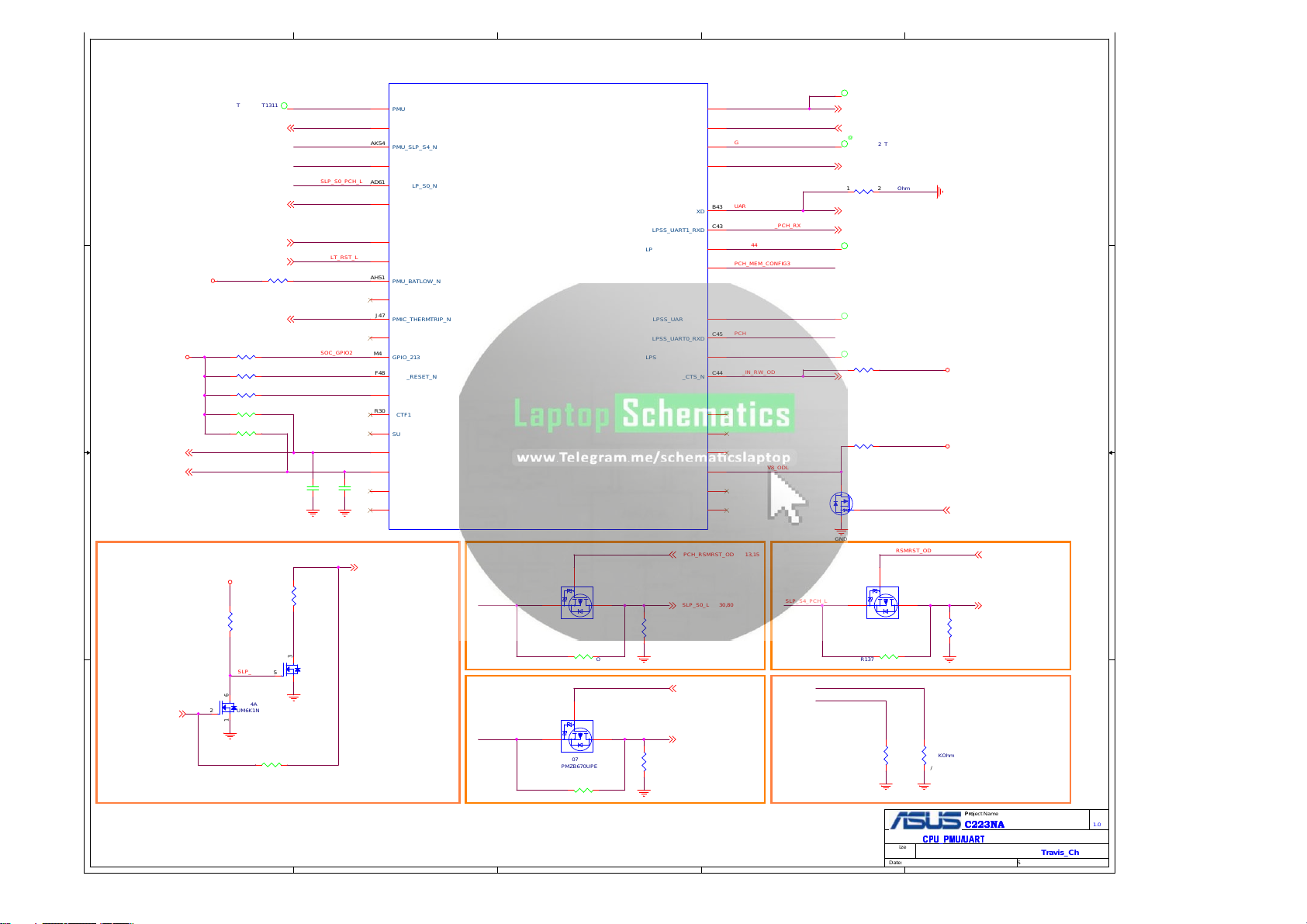

U0501N

@

EN_PP3300_EMMC

1

T1311TPC26T

D D

PP3300_SOC_A

C C

B B

A A

PP1800_SOC_A

PCH_I2C_PMIC_SDA80

PCH_I2C_PMIC_SCL80

SLP_S3_L13,30,80,83

5

PCH_SUSCLK53

SYS_RST_ODL29,30,32,35

EC_PCH_PW R_BTN_ODL29,30

PLT_RST_L13,29,30,35,51,53

1 2

R1302 100KOhm

THERMTRIP_L80

1 2

R1306 10KOhm

1 2

R1307 10KOhm

1 2

R1308 10KOhm

1 2

R1304 1KOhm@

1 2

R1305 1KOhm@

PP3300_A

12

R1309

100KOhm

SLP_S33

5

61

Q1304A

2

UM6K1N

GND

1 2

R1310 0Ohm

@

GND

12

SLP_S33_Q

34

R1364

1KOhm

Q1304B

UM6K1N

SLP_S4_PCH_L

SLP_S3_PCH_L

SLP_S0_PCH_L

SOC_GPIO213

SOC_GPIO223

SOC_NCTF_H48

12

C1302

22PF/50V

@

PLT_RST_L

BATLOW_L

12

GNDGND

C1301

22PF/50V

@

AG55

PMU_WAKE_N

AE62

PMU_SUSCLK

AK54

PMU_SLP_S4_N

AC62

PMU_SLP_S3_N

AD61

PMU_SLP_S0_N

AD62

PMU_RSTBTN_N

AK55

PMU_PWRBTN_N

AG57

PMU_PLTRST_N

AH51

PMU_BATLOW_N

AK49

PMU_AC_PRESENT

J47

PMIC_THERMTRIP_N

J45

PMIC_STDBY

M47

GPIO_213

F48

PMIC_RESET_N

H48

PMIC_PWRGOOD

R30

NCTF1

AG58

SUS_STAT_N

F47

PMIC_I2C_SDA

H45

PMIC_I2C_SCL

L47

GPIO_214

P47

GPIO_215

BGA1296

PLT_RST_L 13,29,30,35,51,53

4

SLP_S0_PCH_L

SLP_S3_PCH_L

PCH_RSMRST_OD

1

G

2 3

D

S

Q1306

PMZB670UPE

1 2

@

R1366 0Ohm

PCH_RSMRST_OD

1

G

2 3

D

S

Q1307

PMZB670UPE

1 2

@

R1368 0Ohm

3

LPSS_UART2_TXD

LPSS_UART2_RXD

LPSS_UART2_RTS_N

LPSS_UART2_CTS_N

LPSS_UART1_TXD

LPSS_UART1_RXD

LPSS_UART1_RTS_N

LPSS_UART1_CTS_N

LPSS_UART0_TXD

LPSS_UART0_RXD

LPSS_UART0_RTS_N

LPSS_UART0_CTS_N

PMC_SPI_TXD

PMC_SPI_RXD

PMC_SPI_FS2

PMC_SPI_FS1

PMC_SPI_FS0

PMC_SPI_CLK

12

R1365

499KOhm

1%

GND

12

R1367

499KOhm

1%

GND

PCH_RSMRST_OD 13,15

SLP_S0_L 30,80

PCH_RSMRST_OD 13,15

SLP_S3_L 13,30,80,83

PCHTX_SERVORX_UART

H41

PCHRX_SERVOTX_UART

J41

GPIO_48

L41

EC_SMI_ODL

M41

UART_PCH_TX_GPS_RX

B43

UART_GPS_TX_PCH_RX

C43

GPIO_44

A42

PCH_MEM_CONFIG3

C42

GPIO_39

B45

PCH_MEM_CONFIG2

C45

GPIO_40

A46

EC_IN_RW_OD

C44

H50

J50

M48

EDP_HPD_1V8_ODL

P48

L48

E52

SLP_S4_PCH_L

@

1

T1307 TPC26T

PCHTX_SERVORX_UART 32,35

PCHRX_SERVOTX_UART 32,35

@

1

T1308 TPC26T

EC_SMI_ODL 30

1 2

R1315 2.2KOhm

UART_PCH_TX_GPS_RX 29

UART_GPS_TX_PCH_RX 29

@

1

T1312 TPC26T

@

1

T1309 TPC26T

@

1

T1310 TPC26T

1 2

R1317 100KOhm

EC_IN_RW_OD 35

1 2

R1303 100KOhm

32

D

1

G

S

GND

2 3

R1370 0Ohm

PCH_MEM_CONFIG3

PCH_MEM_CONFIG2

2

GND

Hardware Strap (B43)

for eMMC boot source

1=enable (default)

0=disable

Use SPI as boot device

PD this strap to disable

PP1800_SOC_A

PP1800_SOC_A

Q1305

2N7002K

PCH_RSMRST_OD

1

G

S

Q1308

PMZB670UPE

1 2

@

D

EDP_HPD_3V3 45

12

R1369

499KOhm

1%

GND

MEM Config

12

12

R1319

R1301

2.2KOhm

2.2KOhm

/DRAM

/DRAM

GND GND

Project Name

Project Name

Project Name

C223NA

C223NA

Title :

Title :

Title :

Size

Size

Size

Dept.:

Dept.:

Dept.:

Custom

Custom

Custom

Thursday, May 31, 2018

Thursday, May 31, 2018

Thursday, May 31, 2018

Date: Sheet

Date: Sheet

Date: Sheet

C223NA

CPU_PMU/UART

CPU_PMU/UART

CPU_PMU/UART

CCNB/EE2

CCNB/EE2

CCNB/EE2

PCH_RSMRST_OD 13,15

SLP_S4_L 30,80

Engineer:

Travis_Chan

Engineer:

Travis_Chan

Engineer:

Travis_Chan

13

13

13

1

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

of

of

of

5

4

3

2

1

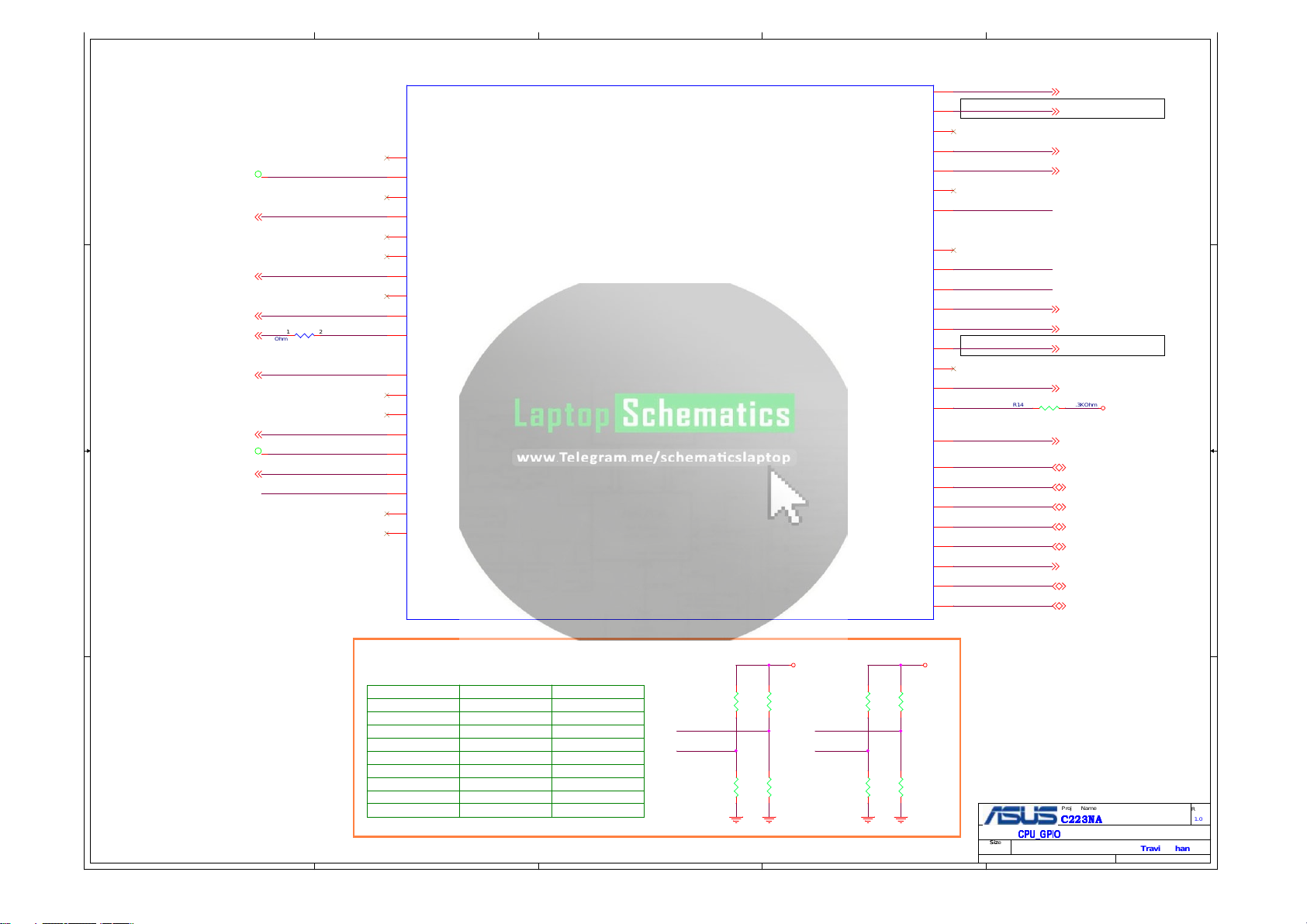

U0501O

D D

T1401@

1

EN_PP3300_TOUCHSCREEN83

I2S_PCH_TX_SPKR_RX36

Speaker AMP

C C

B B

I2S_SFRM_SPKR36

I2S_SCLK_SPKR36

PMIC_PCH_INT_ODL80

EC_PCH_KB_INT_ODL30

HAVEN_PCH_INT_ODL35

R1483

20Ohm

T1405@

1

1 2

ISH_GPIO_8

I2S_SCLK_SPKR_R

FP_RST_ODL

CONFIG_STRAP3

AK57

AM52

AM55

AM57

AM49

AM51

AM54

AK51

AK58

AM48

F34

F35

H34

C37

H35

B37

C29

C31

C27

ISH_GPIO_9

ISH_GPIO_8

ISH_GPIO_7

ISH_GPIO_6

ISH_GPIO_5

ISH_GPIO_4

ISH_GPIO_3

ISH_GPIO_2

ISH_GPIO_1

ISH_GPIO_0

GPIO_33

GPIO_32

GPIO_31

GPIO_30

GPIO_29

GPIO_28

GPIO_27

GPIO_26

GPIO_25

BGA1296

GPIO_18

GPIO_24

GPIO_23

GPIO_22

GPIO_21

GPIO_20

GPIO_19

GPIO_9

GPIO_17

GPIO_16

GPIO_15

GPIO_14

GPIO_13

GPIO_12

GPIO_11

GPIO_10

GPIO_0

GPIO_8

GPIO_7

GPIO_6

GPIO_5

GPIO_4

GPIO_3

GPIO_2

GPIO_1

TRACKPAD_INT_1V8_ODL

J39

PEN_PDCT_ODL

C25

B25

A26

C26

B27

CONFIG_STRAP4

C33

A30

CONFIG_STRAP1

C35

CONFIG_STRAP2

C36

TRACKPAD_INT_1V8_ODL

F39

FP_INT

C38

PEN_INT_ODL

C30

E39

C34

SHIPPING_STRAP

L39

A38

B29

H39

B31

A34

B35

FP_INT

B39

C39

B33

1 2

R1491 3.3KOhm1%

TRACKPAD_INT_1V8_ODL 14,31

PEN_PDCT_ODL 46

EC_PCH_WAKE_ODL 30

TOUCHSCREEN_INT_1V8_ODL 45

TRACKPAD_INT_1V8_ODL 14,31

FP_INT 14,29

PEN_INT_ODL 46

EC_SCI_ODL 30

@

PP1800_A

TRC_CLK0 29

TRC_DATA0[8] 29

TRC_DATA0[7] 29

TRC_DATA0[6] 29

TRC_DATA0[5] 29

TRC_DATA0[4] 29

FP_INT 14,29

TRC_DATA0[2] 29

TRC_DATA0[1] 29

R1.1

R1.1

Config Strap

PP1800_A

CONFIG_STRAP3

CONFIG_STRAP4

12

R1484

10KOhm

1%

@

12

R1486

3.3KOhm

1%

@

GND GND

2

12

CONFIG_STRAP1PUCONFIG_STRAP2 CONFIG

PU

PU

PD

A A

PD

PD

Z

Z

*Z

5

4

PD

Z

PU

PD

Z

PU

PD

*Z

PU

CONFIG_0

CONFIG_1

CONFIG_2

CONFIG_3

CONFIG_4

CONFIG_5

CONFIG_6

CONFIG_7

CONFIG_8

CONFIG_STRAP1

CONFIG_STRAP2

3

R1489

10KOhm

1%

@

12

R1492

3.3KOhm

1%

@

GND GND

12

12

R1490

10KOhm

1%

@

R1493

3.3KOhm

1%

@

12

12

R1485

10KOhm

1%

@

R1487

3.3KOhm

1%

@

PP1800_A

Project Name

Project Name

Project Name

C223NA

C223NA

CPU_GPIO

CPU_GPIO

CPU_GPIO

CCNB/EE2

CCNB/EE2

CCNB/EE2

C223NA

Engineer:

Engineer:

Engineer:

1

Title :

Title :

Title :

Size

Size

Size

Dept.:

Dept.:

Dept.:

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Thursday, May 31, 2018

Thursday, May 31, 2018

Thursday, May 31, 2018

Travis_Chan

Travis_Chan

Travis_Chan

14

14

14

of

of

of

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

PP1800_SOC_A

R1505100Ohm

12

D D

NTRST/EXTD29

TMS/TMSC29

MIPI60 Debug

C C

B B

TDO/EXTA29

TDI/EXTB29

TCK29

EXTE/TRIGIN29

EXTF/TRIGOUT29

PP3300_SOC_A

12

C1522

0.1UF/16V

GND

PP3300_RTC

R150251Ohm

R1504100Ohm

12

12

GND

SUSPWRNACK30

PCH_RSMRST_L29,30

PCH_PROCHOT_ODL30,80,89

1 2

R1508 100KOhm

R150151Ohm

R1503100Ohm

12

12

1 2

R1506 51Ohm

1 2

R1507 51Ohm

@

1 2

R1597 100KOhm

Input

3.3

XTAL 32.768KHZ

4

PCH_RTCRST_ODL

PCH_RTEST_ODL

PCH_RSMRST_L

RTC_EXPAD

BRTCX2

BRTCX1

PCH_INTRUDER

1 2

C1523 18PF/50V

A18

C19

C24

C23

A22

C22

B23

C20

C21

B19

AC63

AC55

AH49

AC57

E47

AG51

AC58

AC59

AC54

U0501P

RSVD1

RSVD7

JTAG_TRST_N

JTAG_TMS

JTAG_TDO

JTAG_TDI

JTAG_TCK

JTAG_PREQ_N

JTAG_PRDY_N

JTAG_PMODE

SUSPWRDNACK

RTC_RST_N

RTC_TEST_N

RSM_RST_N

PROCHOT_N

VCC_RTC_EXTPAD

RTC_X2

RTC_X1

INTRUDER

BGA1296

3

PP3300_A

12

RSVD9

RSVD3

NCTF2

RSVD10

RSVD4

NCTF3

NCTF6

NCTF5

NCTF4

NCTF8

NCTF10

NCTF12

NCTF13

NCTF9

NCTF11

NCTF14

NCTF1

NCTF7

RSVD6

RSVD8

RSVD5

RSVD2

R1593

499KOhm

1%

PCH_RSMRST_OD

H43

AG52

A60

J43

AG54

A61

BJ2

BG1

B15

C15

D8

E8

F8

C9

E10

H10

A14

C14

C1

F1

B4

A4

U0501Q

M16

NCTF15

L16

NCTF12

F16

NCTF7

E16

NCTF3

J16

NCTF11

H16

NCTF10

H12

NCTF8

F12

NCTF5

M12

NCTF14

M10

NCTF13

F14

NCTF6

H14

NCTF9

BGA1296

APL_C1

APL_F1

PCH_RSMRST_OD 13

1

1

T1501 @

T1502 @

2

GPIO_219

GPIO_218

GPIO_217

GPIO_216

NCTF1

PWM3

PWM2

PWM1

PWM0

NCTF2

NCTF4

R1509

PCH_RTEST_ODL PCH_RTCRST_ODL

EC_PCH_RTCRST15,30

0Ohm

1 2

@

EC_PCH_RTCRST

1

G

EMMC_RST_ODL

L30

M30

M29

P30

AP57

E41

F41

PEN_RESET

C41

GPIO_34

B41

C63

E63

PP3300_RTC

PCH_RTCRST_ODL

32

D

Q1501

2N7002K

S

GND GND

PP3300_RTC

PCH_RTEST_ODL

1

@

1

T1503 TPC26T

1

12

R1595

20KOhm

1%

12

C1525

1UF/6.3V

12

R1596

20KOhm

1%

EMMC_RST_ODL 51

TOUCHSCREEN_RST_1V8 45

PEN_RESET 46

@

T1504 TPC26T

CCNB/EE2

CCNB/EE2

CCNB/EE2

12

C1526

1UF/6.3V

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

of

of

of

15

15

15

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

32

D

Q1503

1

2N7002K

G

S

GND GND

Title :

Title :

Title :

CPU_RTC/PWM

CPU_RTC/PWM

CPU_RTC/PWM

Size

Size

Size

Dept.:

Dept.:

Dept.:

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Thursday, May 31, 2018

Thursday, May 31, 2018

Thursday, May 31, 2018

Q1502

2N7002K

12

C1527

1UF/6.3V

@

EC_PCH_RTCRST15,30

2

EC_PCH_RTCRST

R1594

10MOhm

BRTCX1

A A

BRTCX2

1 2

SL1509 @

0402

BRTCX2_R

21

X1501

32.768KHZ

1 2

1 2

C1524 15PF/50V

SEIKO : 07009-00113600

5

4

GND

PCH_RSMRST_L

32

D

1

G

S

GND GND

3

5

4

3

2

1

D D

1%

1%

1%

1%

1%

1%

1%

1%

1%

PCIE_REF_CLK_RCOMP

PMU_RCOMP

USB_SSIC_RCOMP

USB2_RCOMP

MCSI1_RCOMP

GPIO_RCOMP

MCSI2_RCOMP

EMMC_RCOMP

MDSI_RCOMP

1 2

R1696 60.4Ohm

GND

1 2

R1697 200Ohm

GND

1 2

R1698 137OHM

GND

1 2

R1699 113Ohm

GND

1 2

C C

R1601 150Ohm

GND

R1602 200Ohm

GND

R1603 150Ohm

GND

R1604 200Ohm

GND

R1605 150Ohm

GND

1 2

1 2

1 2

1 2

LPDDR3 105 Ohm 20171019

1% @

1%

MEM_CH1_RCOMP

MEM_CH0_RCOMP

1 2

R1606 105Ohm

B B

GND

R1607 105Ohm

GND

1 2

U0501R

E21

PCIE_REF_CLK_RCOMP

AG59

PMU_RCOMP

AB15

USB_SSIC_RCOMP

Y15

USB2_RCOMP

H27

MCSI_DPHY1.1_RCOMP

E34

GPIO_RCOMP

F27

MCSI_DPHY1.2_RCOMP

V59

EMMC_RCOMP

AP7

MDSI_RCOMP

D2

NCTF10

AV30

MEM_CH1_RCOMP

AV34

MEM_CH0_RCOMP

NCTF5

NCTF6

NCTF3

NCTF16

NCTF8

NCTF7

NCTF2

NCTF4

NCTF14

SOC_PWROK

NCTF11

JTAGX

NCTF1

NCTF13

NCTF9

NCTF12

NCTF15

NCTF18

NCTF17

AM58

AM59

AB49

R25

C13

B13

AB13

AC13

P27

AG49

J29

B21

A3

P25

C2

M39

P39

R39

R37

1 2

R1608 0Ohm@

1 2

R1610 1MOHM@

EC_PCH_PWROK 30

PMIC_EC_PWROK_OD 30,80

GND

BGA1296

A A

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

Title :

Title :

Title :

CPU_RCOMP

CPU_RCOMP

CPU_RCOMP

Size

Size

Size

B

B

B

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

Thursday, May 31, 2018

Date: Sheet of

5

4

3

2

Thursday, May 31, 2018

Dept.:

Dept.:

Dept.:

CCNB/EE2

CCNB/EE2

CCNB/EE2

Engineer:

Engineer:

Engineer:

1

Travis_Chan

Travis_Chan

Travis_Chan

16

16

16

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

PPVAR_VCCG I

12

12

12

C1781

1UF/6.3V

PPVAR_VCCG I

D D

PPVAR_VNN

PPVAR_VNN

C C

PP1100_VCCIO

@

GND

12

12

C1712

10UF/6.3V

@

GND

EDGE CAP

12

12

C1725

2.2UF/6.3V

GND

12

12

C1711

22UF/6.3V

GND

EDGE CAP

GND GND

EDGE CAP

AM42,AM25,AM23,AM41

C1782

2.2UF/6.3V

C1713

10UF/6.3V

@

C1726

2.2UF/6.3V

C1720

22UF/6.3V

C1701

2.2UF/6.3V

12

12

C1714

10UF/6.3V

@

2018/02/13 Travis Change C1702,C1703,C1705,C1706,C1708,C1709,C1710,C1712,

C1713,C1714,C1715,C1716,C1717,C1718,C1719,C1781 to DNS

Change C1701,C1782 to 2.2uF (PI

12

C1727

1UF/6.3V

12

12

C1721

10UF/6.3V

@

12

C1702

1UF/6.3V

@

C1715

10UF/6.3V

@

C1722

10UF/6.3V

@

C1728

10UF/6.3V

@

12

12

12

C1723

10UF/6.3V

@

C1703

1UF/6.3V

@

C1716

10UF/6.3V

@

BACKSIDE

C1729

10UF/6.3V

12

12

12

12

12

C1704

1UF/6.3V

C1717

10UF/6.3V

@

C1724

10UF/6.3V

@

TOPSIDE

12

12

4

PPVAR_VCCGI

C1705

1UF/6.3V

@

C1718

10UF/6.3V

@

12

12

⺢嬘

C1706

1UF/6.3V

@

C1719

10UF/6.3V

@

)

12

12

C1707

1UF/6.3V

C1708

1UF/6.3V

@

12

12

C1709

1UF/6.3V

@

C1710

1UF/6.3V

@

PPVAR_VNN

TOPSIDE

2018/02/13 Travis Change C1725,C1726 to 2.2uF

Change C1711,C1720 to 22uF (PI

PP1100_VCCIO

12

C1730

1UF/6.3V

12

C1731

1UF/6.3V

BACKSIDE

)

⺢嬘

PP1100_VCCIO

BACKSIDE

TOPSIDE

3

2

PP1050_VCCRAM_IO_S PP1240_VDD2_IO_A

PP1050_VCCRAM _IO_S

12

12

C1758

1UF/6.3V

GND

EDGE CAP

GND

PLACE NEAR VCCRAM_1P05_IO PINS

PP1240_VDDQ2_SRAM_A

PP1240_VDD2_SR AM_A

12

C1753

1UF/6.3V

GND

GND

PP1240_VDDQ2_SRAM_A

PP1240_VDD2_SR AM_A

12

C1752

1UF/6.3V

GND GND GND

PLACE NEAR AM28

VDD2_1P24_GLM

12

C1759

C1760

1UF/6.3V

1UF/6.3V

PP1050_VCCRAM _IO_S

12

C1757

10UF/6.3V

12

12

C1754

C1755

1UF/6.3V

1UF/6.3V

@

PP1240_VDD2_SR AM_A

12

C1756

EDGE CAP

PLACE NEAR AM20,AK20,AM37

VDD2_1P24_GLM

10UF/6.3V

BACKSIDE

12

C1761

1UF/6.3V

BACKSIDE

TOPSIDE

BACKSIDE

TOPSIDE

12

12

C1762

1UF/6.3V

GND

EDGE CAP

PLACE NEAR AE20,AE18,AE22,AG22

VDD2_1P24_MPHY

PP1240_VDD2_IO_A

BACKSIDE

12

C1766

1UF/6.3V

GND

12

C1767

1UF/6.3V

GND

EDGE CAP

PLACE NEAR AA18,AA20

VDD2_1P24_DSI_CSI

PP3300_RTC

12

12

C1769

1UF/6.3V

@

AA44

VCCRTC_3P3V

C1763

1UF/6.3V

C1770

0.1UF/16V

PP1240_VDD2_IO_A

12

C1764

1UF/6.3V

@

PP1240_VDD2_IO_A

12

C1765

10UF/6.3V

GND

PP1240_VDD2_IO_A

12

C1768

10UF/6.3V

TOPSIDE

1

BACKSIDE

TOPSIDE

PP1240_VDD2_IO_A

TOPSIDE

PP3300_RTC

PP1100_VDDQ

12

12

C1732

C1733

1UF/6.3V

B B

PP1100_VDDQ

GND

12

GND

PP1050_VCCRAM _S

12

GND

PP1050_VCCRAM _S

A A

GND

1UF/6.3V

12

C1735

C1734

22UF/6.3V

10UF/6.3V

EDGE CAP

12

12

C1743

C1742

1UF/6.3V

1UF/6.3V

EDGE CAP

PLACE NEAR VCCRAM_1P05 PINS

5

12

C1744

1UF/6.3V

C1736

10UF/6.3V

@

BACKSIDE

12

12

C1738

22UF/6.3V

BACKSIDE

C1747

10UF/6.3V

12

12

C1739

22UF/6.3V

TOPSIDE

12

C1740

C1741

10UF/6.3V

4

TOPSIDE

10UF/6.3V

@

2018/02/14 Travis Change C1735,C1738,C1739 to 22uF

Change C1736,C1740 to DNS (PI

12

C1737

10UF/6.3V

12

C1745

1UF/6.3V

12

C1746

10UF/6.3V

PP1100_VDDQ

)

⺢嬘

PP1050_VCCRAM_S PP1240_VDD2_IO_A

3

PP1240_VDDQ2_SRAM_A

PP1240_VDD2_SR AM_A

12

12

C1750

1UF/6.3V

BACKSIDE

BACKSIDE

PP1240_VDD2_SR AM_A

12

C1751

10UF/6.3V

C1749

1UF/6.3V

GND

GND

PP1240_VDD2_IO_A

12

C1748

1UF/6.3V

GND

EDGE CAP

PLACE NEAR AJ20,AJ22,AK22

VDD2_1P24_AUD_ISH_PLL

PLACE NEAR AG20

VDD2_1P24_USB2

TOPSIDE

2

PP1800_SOC_A

12

12

C1771

1UF/6.3V

GND

EDGE CAP

PLACE NEAR VDD_1P8V_A

BACKSIDE

12

C1777

1UF/6.3V

TOPSIDE

12

C1778

1UF/6.3V

EDGE CAP

GND

AC41,AA42,Y44,V44,V46 PLACE NEAR VDD_3P3V_A

12

GND

12

12

C1772

C1773

1UF/6.3V

1UF/6.3V

@

PP1800_SOC_A

PP1800_SOC_A

C1774

1UF/6.3V

BACKSIDE

PP3300_SOC_A

C1779

1UF/6.3V

Title :

Title :

Title :

CPU_DECOUPLING

CPU_DECOUPLING

CPU_DECOUPLING

Size

Size

Size

Dept.:

Dept.:

Dept.:

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Thursday, May 31, 2018

Thursday, May 31, 2018

Thursday, May 31, 2018

PP3300_SOC_APP3300_SOC_A

PP1800_SOC_A

BACKSIDE

C1775

4.7UF/6.3V

TOPSIDE

12

PP3300_SOC_A

12

C1780

AK25,AJ25

1UF/6.3V

GNDGND

12

C1776

4.7UF/6.3V

Project Name

Project Name

Project Name

C223NA

C223NA

C223NA

CCNB/EE2

CCNB/EE2

CCNB/EE2

1

Engineer:

Engineer:

Engineer:

Travis_Chan

Travis_Chan

Travis_Chan

of

of

of

17

17

17

Rev

Rev

Rev

1.0

1.0

1.0

99

99

99

5

4

3

2

1

U0501S

AM36

VSS107

AG42

VSS70

AG44

VSS71

AG46

VSS72

AH15

VSS73

AH16

D D

C C

B B

AH48

AH5

AH52

AH54

AH55

AH57

AH58

AH59

AH6

AH7

AJ1

AJ18

AJ2

AJ23

AJ27

AJ34

AJ36

AJ63

AK10

AK12

AK18

AK23

AK27

AK48

AK5

AK52

AK59

AK9

AM18

AM22

AM27

AM34

AM39

AM46

AN1

AN10

AN11

AN13

AN14

AN16

AN17

AN2

AN25

AN27

AN28

AN30

AN34

AN36

AN37

AN39

AN47

AN48

AN5

AN50

AN51

AN53

B63

AC18

A5

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS11

VSS31

BGA1296

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

A12

A16

A20

A24

A28

A32

A36

A40

A44

A48

A52

A56

A62

A9

AA1

AA2

AA27

AA34

AA41

AA63

AB10

AB12

AB16

AB48

AB5

AB52

AB57

AB59

AB9

AC27

AC34

AC39

AE1

AE10

AE11

AE13

AE14

AE16

AE17

AE2

AE23

AE27

AE34

AE39

AE4

AE41

AE47

AE48

AE5

AE50

AE51

AE53

AE54

AE56

AE57

AE59

AE63

AE7

AE8

AG13

AG18

AG23

AG27

AG34

AG37

AG39

AG41

GNDGND GNDGND

AR19

AR32

AR45

AT12

AT16

AT19

AT2

AT25

AT29

AT3

AT35

AT39

AT45

AT48

AT52

AT57

AT61

AT62

AT7

AU32

AV19

AV2

AV21

AV23

AV29

AV3

AV32

AV35

AV41

AV43

AV45

AV55

AV61

AV62

AV9

AW14

AW30

AW34

AW50

AY10

AY32

AY54

AY58

AY6

B62

BA1

BA12

BA16

BA17

BA2

BA21

BA25

BA27

BA29

BA32

BA35

BA37

BA39