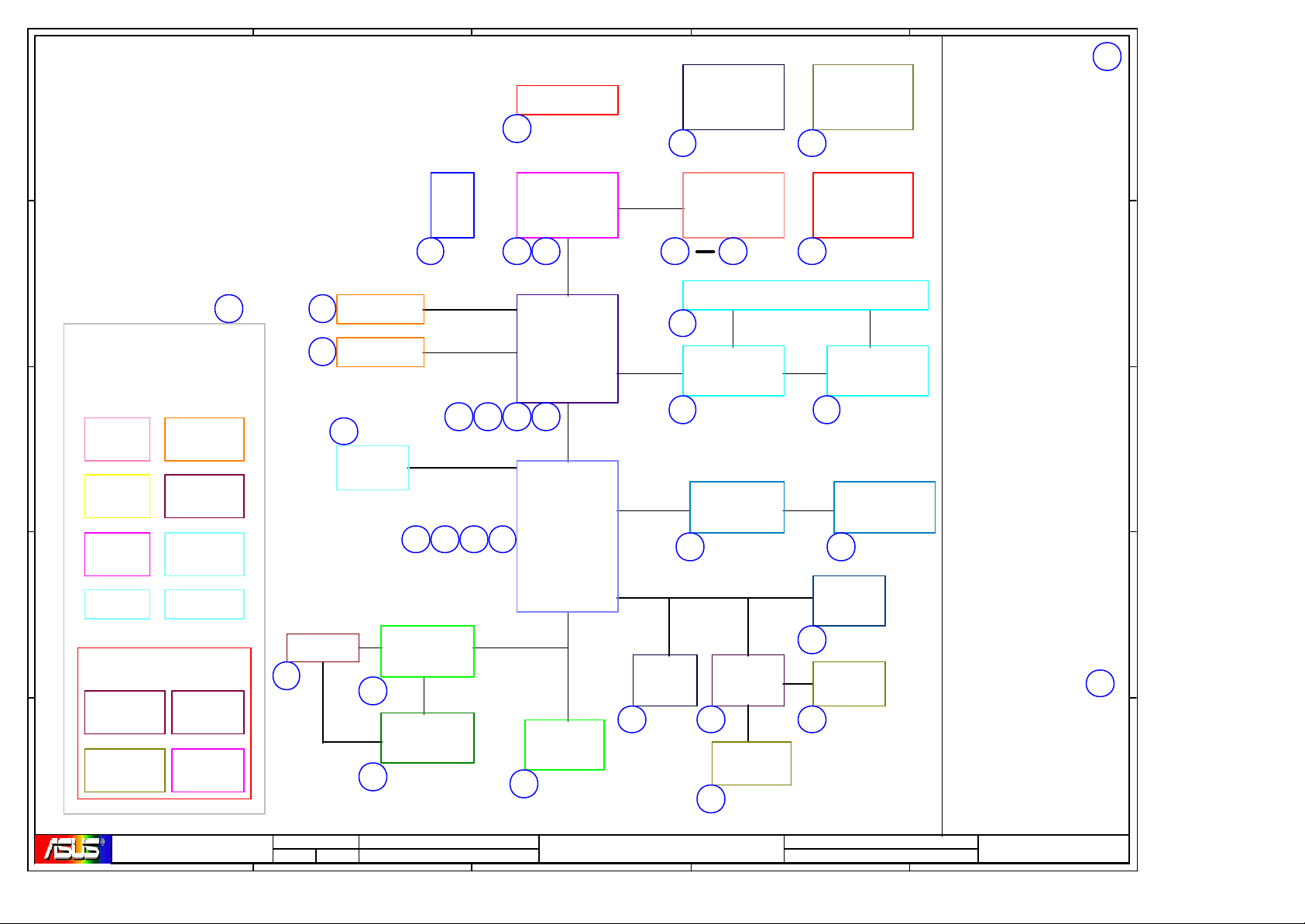

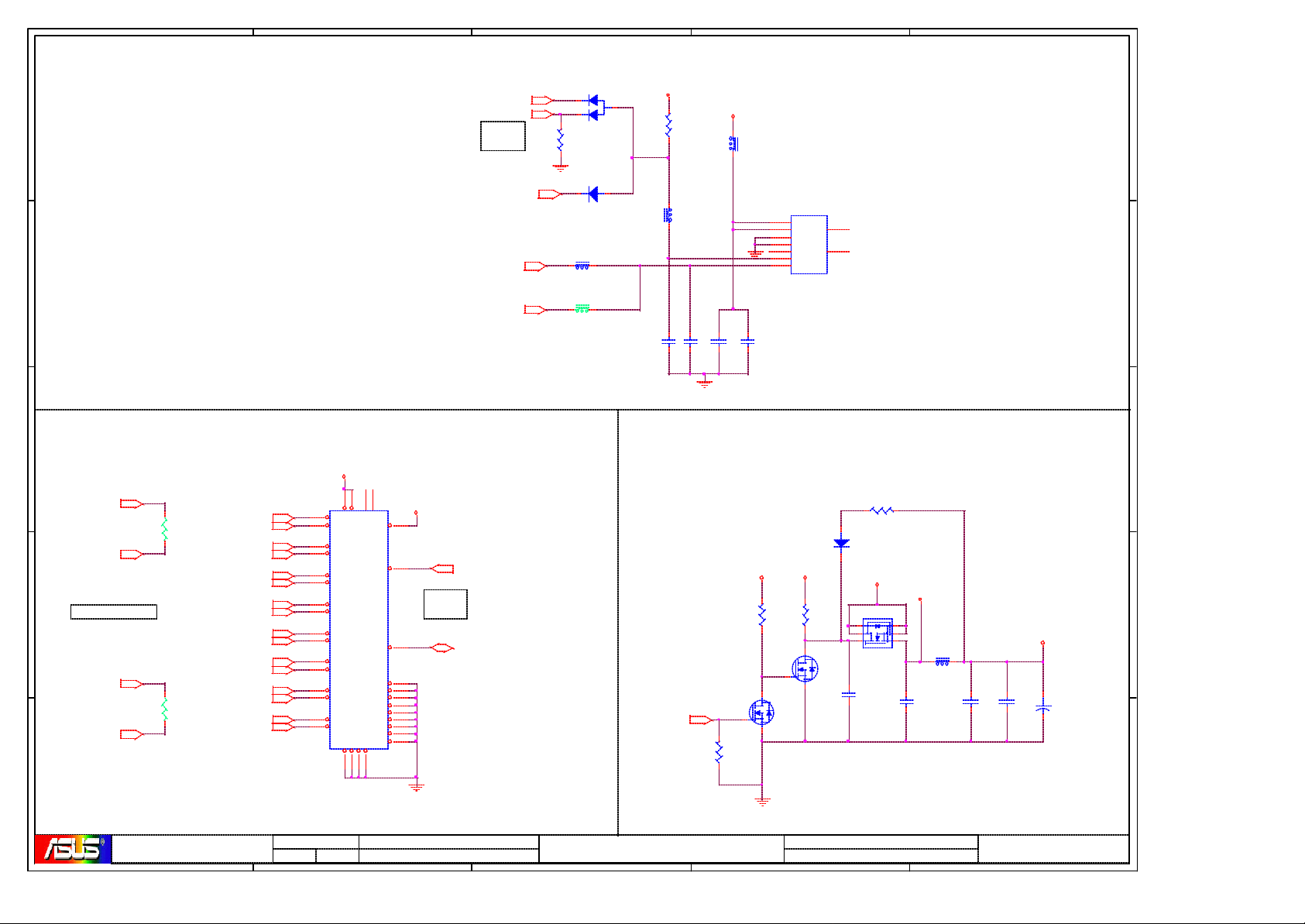

Asus CARMEL Schematics

A

B

C

D

E

FILE LIST

LED

1 1

05

THERMAL

BOARD

34

CLOCK

GEN

31

CARMEL

FAN

BANIAS

Block Diagram

32

2 2

26

13

14

LCD

CRT

LVDS

RGB

IO BOARD

DC-DC

3 3

JACK

MODEM

25

MDC

FWH

USB

PORT

4 4

OP

LAN PHY

MIC

AC97

06 07

AC LINK

03

08

1815 1716

04

PSB

MCHM

MONTARA

-GM

09

HUB

ICH4

DDR

IDE

POWER

(IMVP4)

35 41

12

DDR

DIMM 0

10

PRIMARY

IDE

19

LPC

POWER

ON/OFF

CKTS

33

DDR TERMINATION

DDR

DIMM 1

11

SECONDARY

IDE

20

DEBUG

PORT

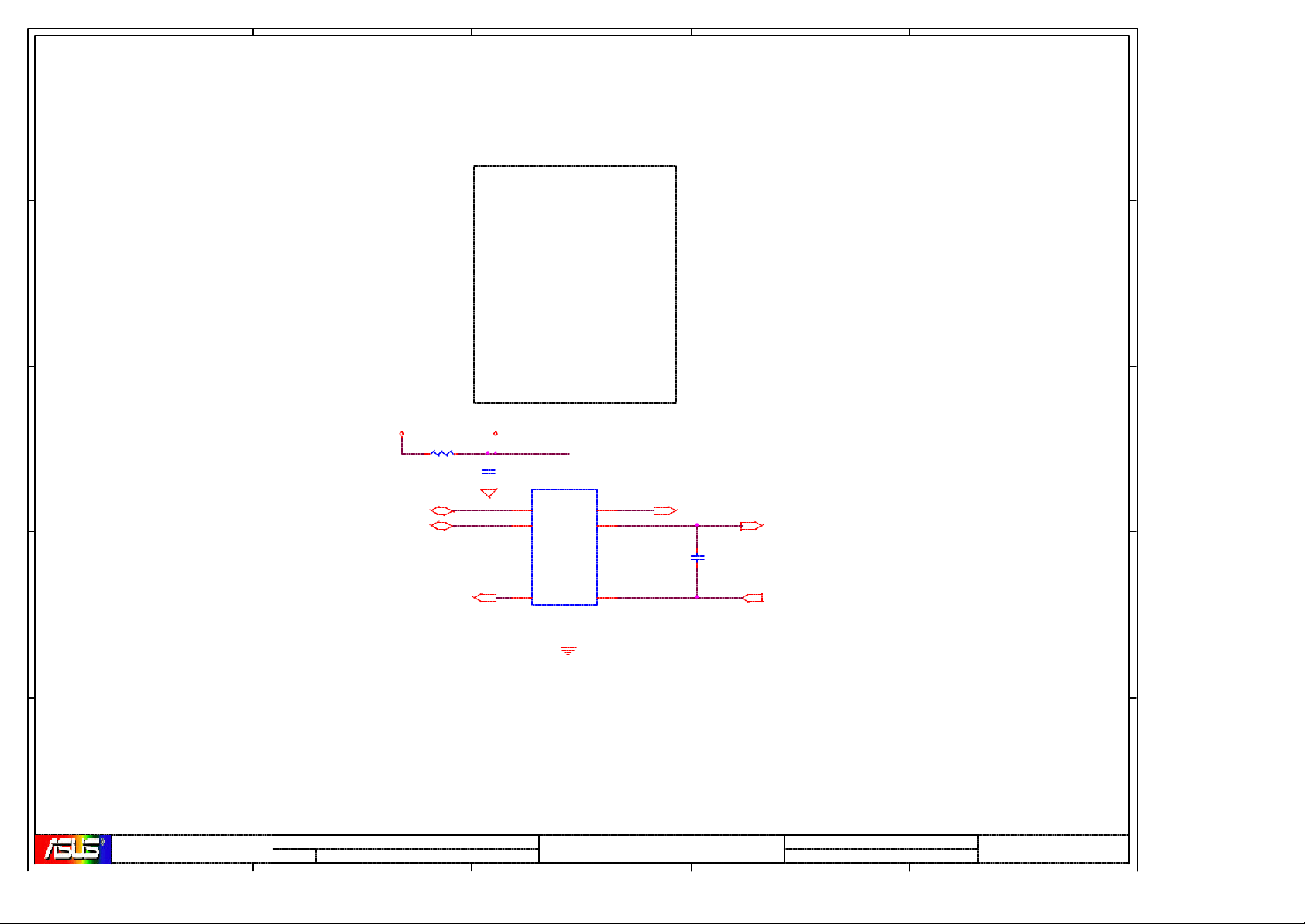

01_BLOCK DIAGRAM

02_REVISION LIST

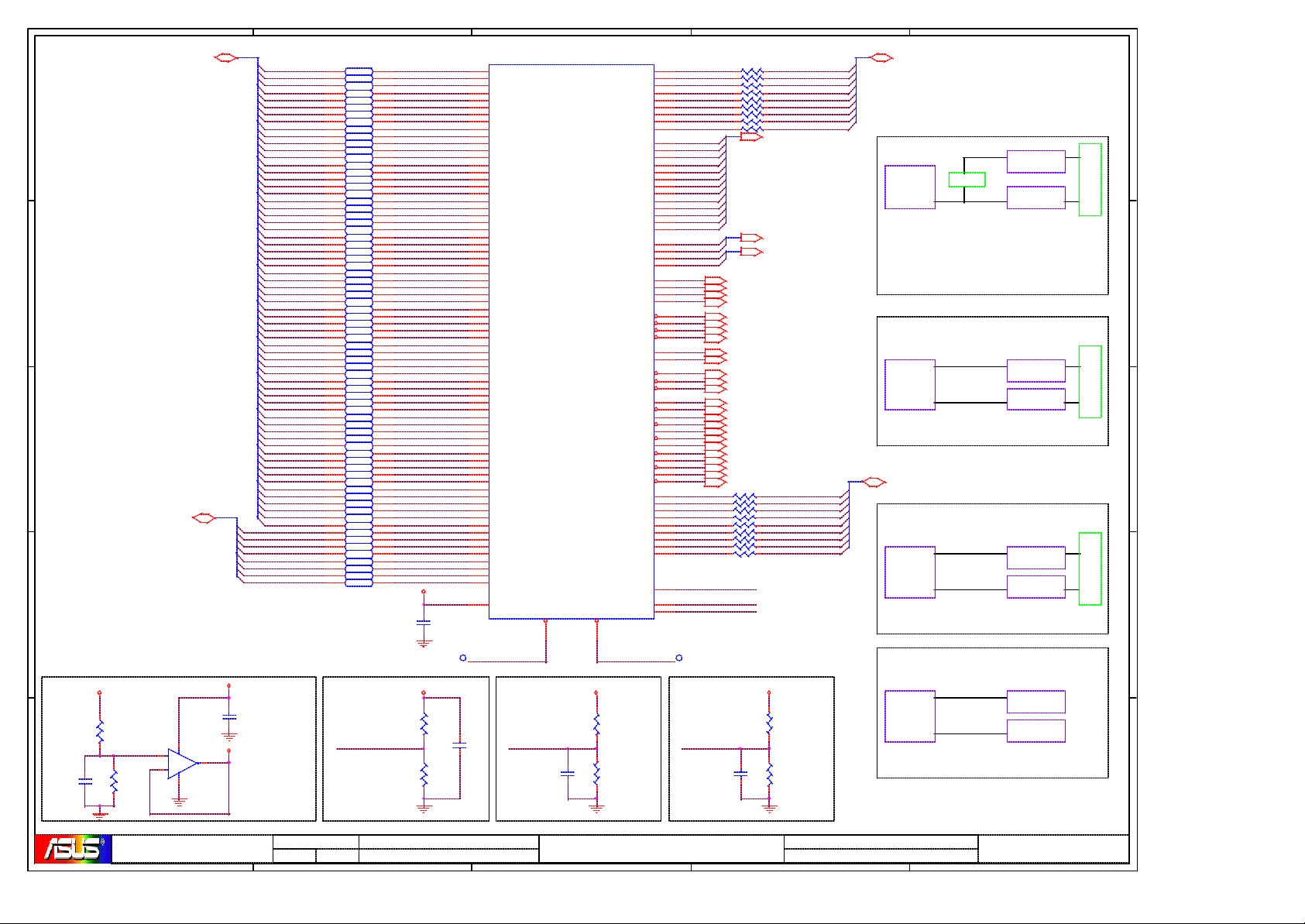

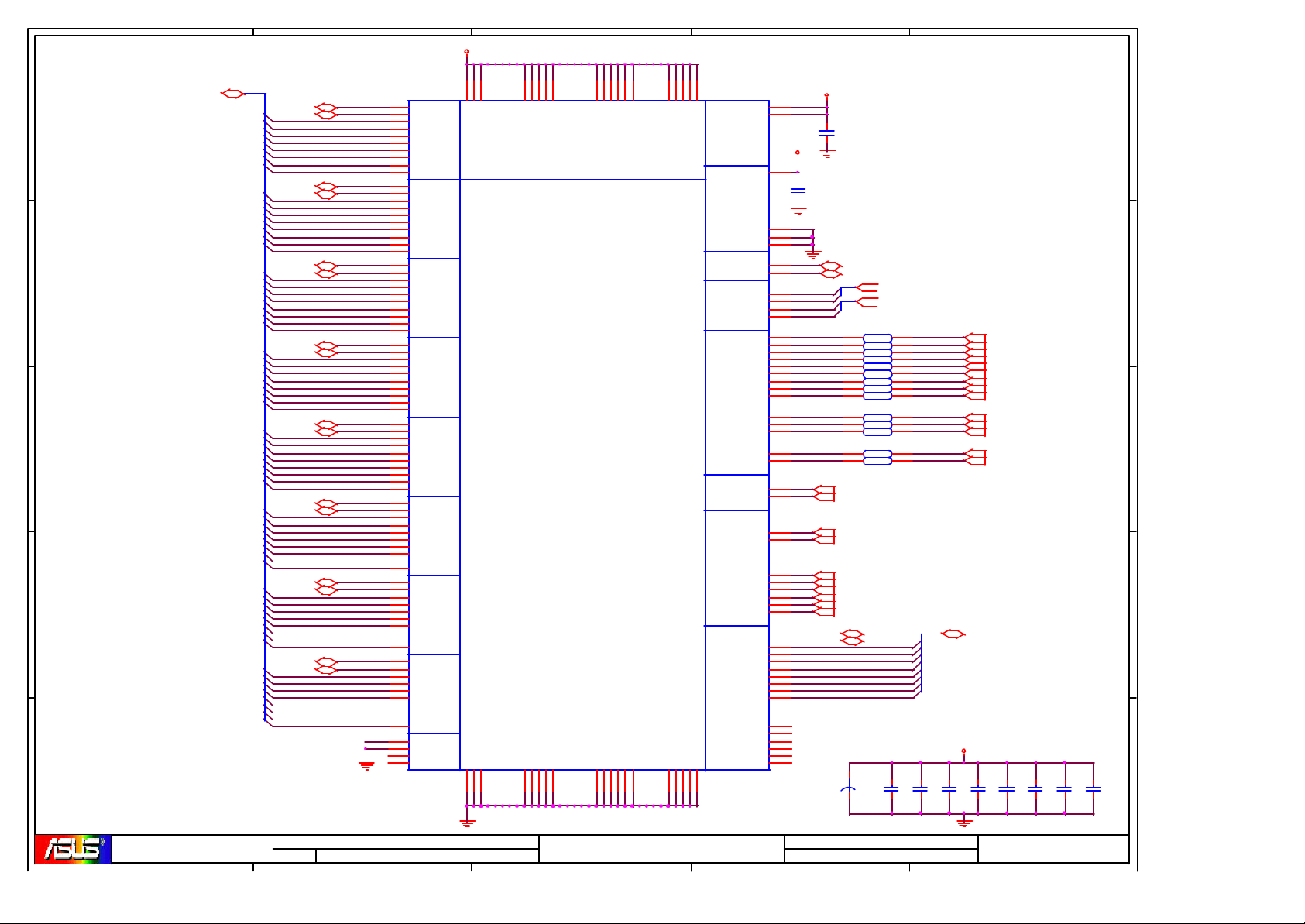

03_CPU_BANIAS(HOST)

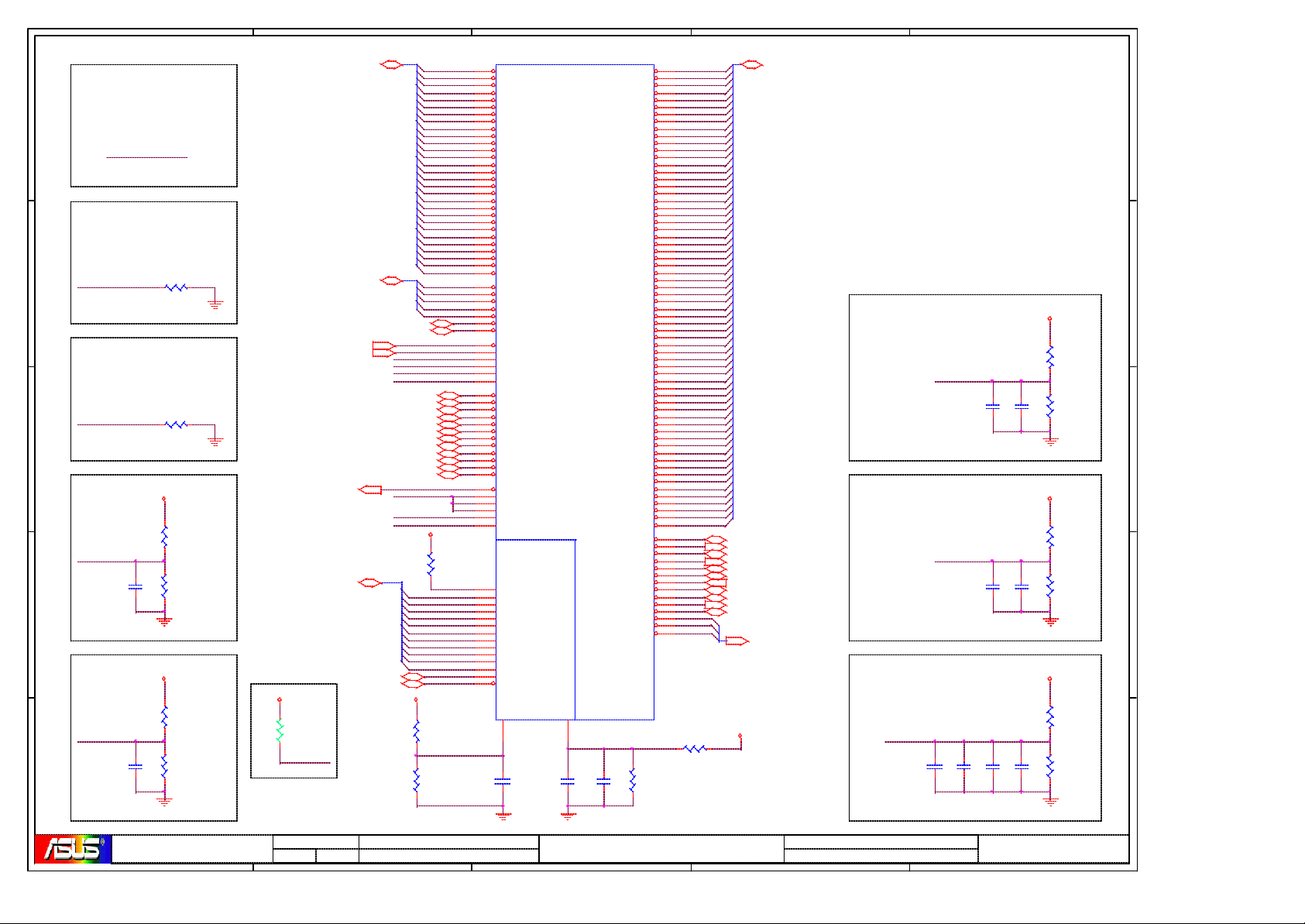

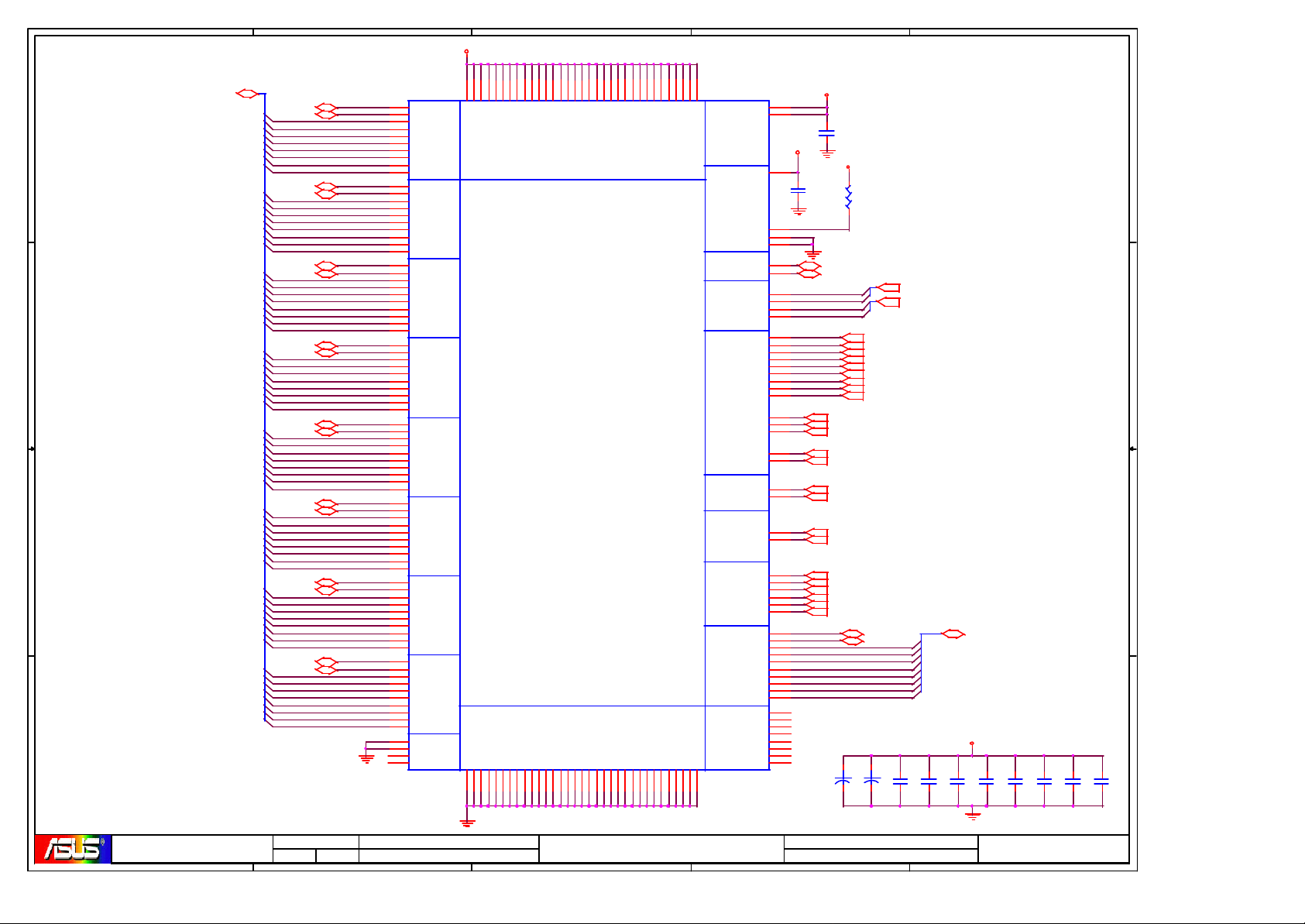

04_CPU_BANIAS(PWR)

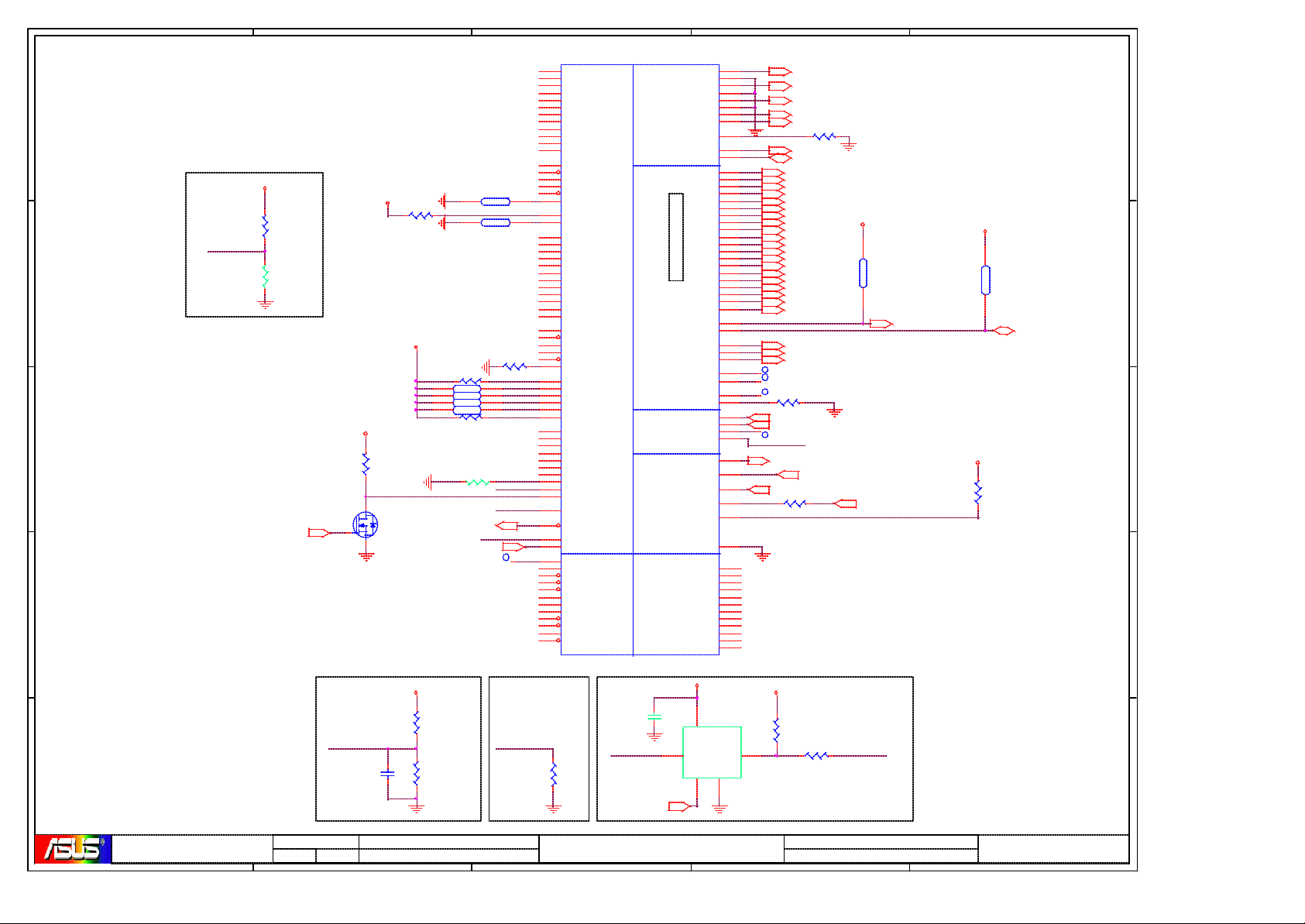

05_THERMAL

06_NB_MCHM(DDR)

07_NB_MCHM(HOST)

08_NB_MCHM(VGA)

09_NB_MCHM(PWR)

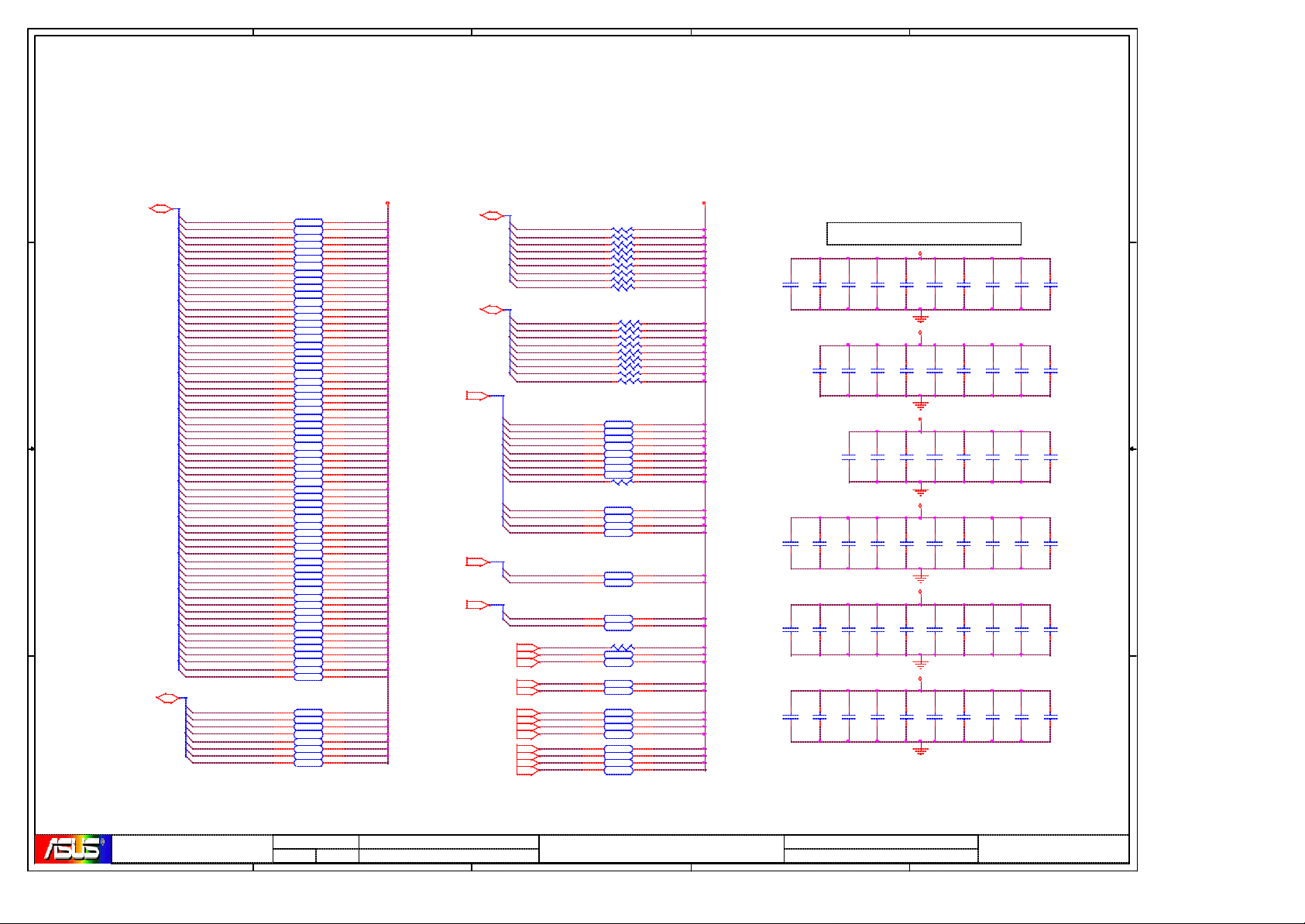

10_DDR SODIMM-0

11_DDR SODIMM-1

12_DDR_TERMINATION

13_LVDS & BACKLIGHT

14_CRT_CONNECTOR

15_ICH4-M(HUB_PCI)

16_ICH4-M(H_U_IDE_PM)

17_ICH4-M(PWR)

18_ICH4-M_PULLUP

19_IDE_HDD

20_IDE_CDROM

21_SUPER_I/O_87393

22_IR & LPT_PORT

23_LPC_KBC & PS2

24_DISCHARGE, DEBUG PORT

25_MDC

26_IOBOARD

27_MINIPCI

28_RICOH551

29_CB_PWR_551

30_PCM_CONN(SIGNAL)

31_CLOCK_ICS950811

32_FAN

33_PWR & RESET_SEQ

34_LED BOARD

01

24

IR

22

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

REV. LIST

60-N4LMB1000-A01P

E

02

SOCKET

PORTBAR CON

PS2

PRINTER

5 5

PORT

PROJECT:

A

LAN

CON

USB

PORT

WB

30

REVISION DESCRIPTION:

SHEET OF

CARDBUS

28

POWER

SWITCH

29

Monday, January 13, 2003

DATE:

B

1394

1

27

PCI

MINIPCI

KBC

23

BLOCK DIAGRAM

C

SIO

21

PRINTER

PORT

22

A

REVISION LIST

R1.0 2002/09/02

R1.1 2002/12/07 1) Pull ACIN_OC(R531) high to +V3.3

1 1

R1.2 2002/12/27

2 2

3 3

4 4

5 5

Initial

2) Pull BAT1_IN#_OC(R532) high to +V3.3

3) Pull BAT2_IN#_OC(R533) high to +V3.3

4) Change Q90 to U57(same P/N:06-004600000)

5) U46 Pin6 connected to +V3.3SUS

PROJECT:

A

WB

REVISION DESCRIPTION:

B

Monday, January 13, 2003

DATE:

SHEET OF

B

2

C

REVISION LIST

C

D

PCB STACK-UP

PCB THICKNESS: 1.2 mm

L1 TOP

L2 GND1

L3 IN1

L4 IN2

L5 VCC

L6 IN3

L7 GND2

L8 BOT

IMPEDENCE

Single-Ended

27.4 OHM WIDTH

TOP/BOT 22 mils

IN1/IN3 16 mils

37.5 OHM WIDTH

TOP/BOT 13.5 mils

IN1/IN3 10 mils

42 OHM WIDTH

TOP/BOT 11 mils

IN1/IN3 8.5 mils

55 OHM WIDTH

TOP/BOT 6 mils

IN1/IN3 5 mils

75 OHM WIDTH

TOP/BOT 2.5 mils

IN1/IN3 2 mils

Differential

70 OHM WIDTH/SPACE

TOP/BOT 8 mils/ 4 mils

IN1/IN3 8 mils/ 3.5 mils

90 OHM WIDTH/SPACE

TOP/BOT 5 mils/ 5 mils

IN1/IN3 5 mils/ 5 mils

100 OHM WIDTH/SPACE

TOP/BOT 4 mils/ 6 mils

IN1/IN3 4.25 mils/ 5.75 mils

PCI INTERFACE

PCI_REQ#

CB&1394

MINIPCI

IDSEL

CB&1394

PCI_REQ#0

PCI_REQ#1

PCI_AD20MINIPCI

PCI_AD21

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

E

POWER INTERFACE

SIGNALS TYPE

CLK_EN# I +V3.3

PM_PSI#

VR_VID[5:0]

1.5V_PWRGD I +V3.3

1.8V_PWRGD +V3.3I

CPU_VRON

VRM_PWRGD

PM_STPCPU# +V3.3O

CHG_LED

RST_BTN#

OTP_RESET#

SHUT_DOWN#

+V5_LCM

PM_SLPDLY_S3#

PM_SLP_S4#

BAT_LEARN

BAT_LLOW#_OC

BAT1_IN#_OC

BAT2_IN#_OC I +V3.3

ACIN_OC

CHG_EN_OC

PM_DPRSLPVR

ACIN_3VA

+5VAO

EN_+3VALWAYS

AC_BAT_SYS

A/D_DOCK_IN PWR

SMC_BAT1

SMD_BAT1

SMC_BAT2

SMD_BAT2

BAT_LOW#

POWER PLANE

VOLTAGEPOWER CURRENT

+VCORE

+VCCP 2.5A

+V1.2S

+V1.25S

+V1.5S

+V1.5

+V1.5SUS

+V2.5

+V3.3S

+V3.3

+V3.3SUS

+V5S

+V5

+V5SUS

+V12

+V12S

1.46V

1.05V

1.2V

1.25V

1.5V

1.5V

1.5V

2.5V

3.3V

3.3V

5V

5V

5V

12V 0.25A

12V

E

POWER

O +VCCP

+VCCP

O

+V3.3O

+V3.3I

I

+V3.3

O

+V3.3

+V3.3

I

I

+V3.3

PWR

+V5

O

+V3.3

O

+V3.3

I

+V3.3

I

+V3.3

+V3.3

I

+V3.3

I

I

+V3.3

O

+V3.3

+V3.3

I

+V3.3

PWR

O +V3.3

PWR

DC

DC

+V3.3

IO

IO

+V3.3

IO

+V3.3

IO

+V3.3

I +V5_LCM

25A

2.5A

0.5A

1.32A

30 mA

64 mA

0.3 A+V1.8S 1.8V

6.68A

1.732A3.3V

1.515A

14 mA

2.5A

3.75A

0.5A

0.25A

A

B

C

D

E

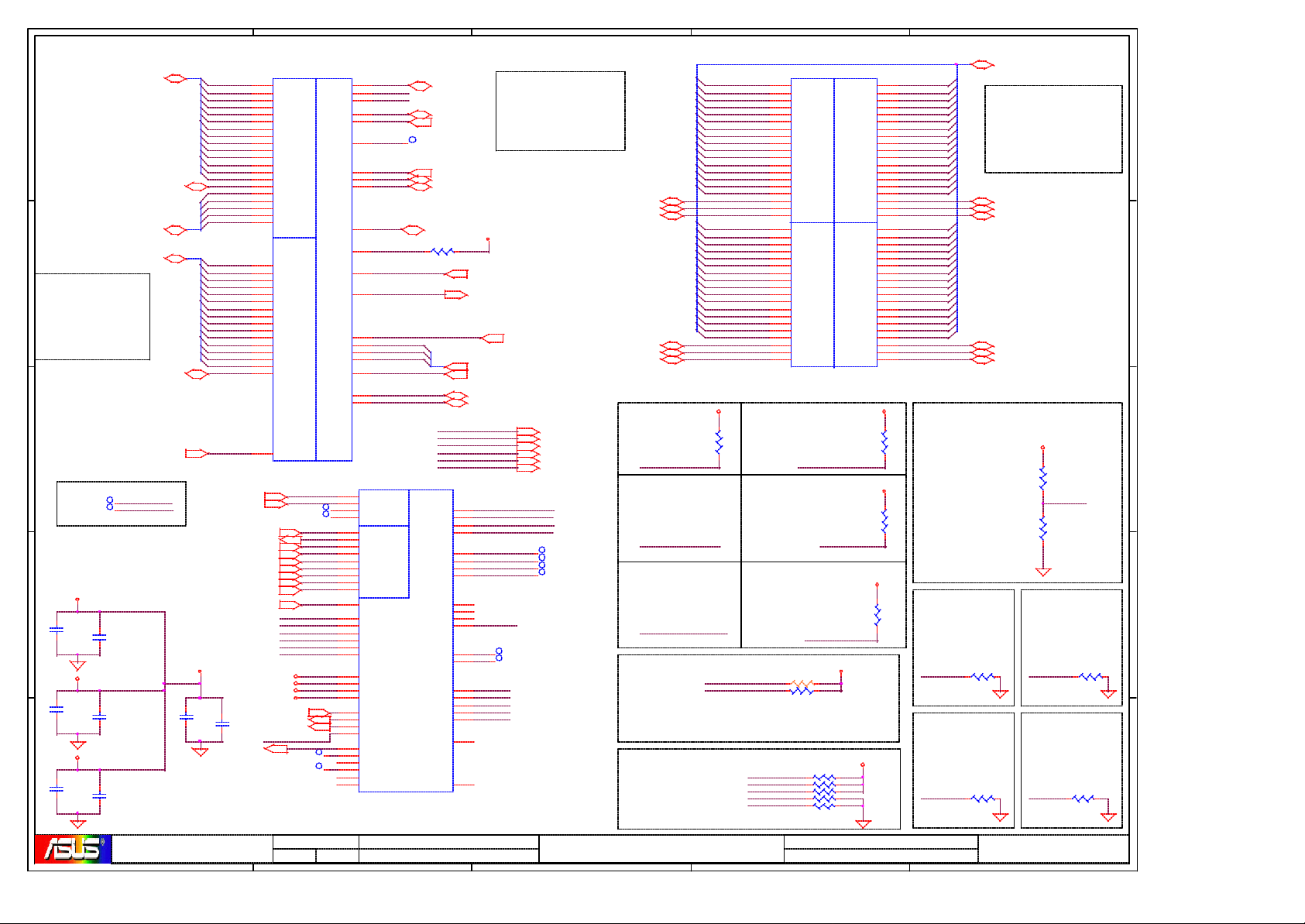

H_A#[16:3]7

1 1

H_ADSTB#07

H_REQ#[4:0]7

H_A#[31:17]7

2 2

ADDR GROUP 0 -> L3

ADDR GROUP 1 -> L6

SPACE >= 1:2

STROBE SPACE >=1:3

GROUP SPACE >=1:5

LENGTH: 0.5" - 6.5"

(#0012)

H_ADSTB#17

3 3

T1 TPC28 1

T2 TPC28 1

V1.1

CPU PLL

CIRCUITS

1.71V - 1.89V(+/- 5%)

S0-S1M: 0.3A

+V1.8S_AC26

4 4

12

C215

0.01U

GND

+V1.8S_N1

12

C42

0.01U

GND

+V1.8S_B1

12

5 5

C62

0.01U

GND

_CLK_CPU_BCLK

_CLK_CPU_BCLK#

12

C21610U

12

C4310U

12

C6410U

H_DPWR#8

PROJECT:

A

CPU Pin A1 need to be enlarged(M)

H_A#16

H_A#15

H_A#14

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

H_A#6

H_A#5

H_A#4

H_A#3

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

1"-6.5"

_CLK_CPU_BCLK31

_CLK_CPU_BCLK#31

H_A20M#16

H_FERR#16

H_IGNNE#16

H_DPSLP#8,16

H_CPUSLP#16

H_INTR16

H_NMI24

H_SMI#16

H_STPCLK#16

H_PWRGD16

+V1.8S

12

12

C248

0.01U

GND

WB

C23610U

PM_PSI#35

U27B

AA2

A[16]#

Y3

A[15]#

AA3

A[14]#

U1

A[13]#

Y1

A[12]#

Y4

A[11]#

W2

A[10]#

T4

A[9]#

W1

A[8]#

V2

A[7]#

R3

A[6]#

V3

A[5]#

U4

ADDRESS GROUP 0ADDRESS GROUP 1

A[4]#

P4

A[3]#

U3

ADSTB[0]#

T1

REQ[4]#

P1

REQ[3]#

T2

REQ[2]#

P3

REQ[1]#

R2

REQ[0]#

AF1

A[31]#

AE1

A[30]#

AF3

A[29]#

AD6

A[28]#

AE2

A[27]#

AD5

A[26]#

AC6

A[25]#

AB4

A[24]#

AD2

A[23]#

AE4

A[22]#

AD3

A[21]#

AC3

A[20]#

AC7

A[19]#

AC4

A[18]#

AF4

A[17]#

AE5

ADSTB[1]#

SOCKET479P

C19

DPWR#

2"-8"

2"-8"

T4 TPC28 1

T6 TPC28 1

<=10"

0.5"-12"

<=10"

<=10"

<=10"

<=10"

<=10"

<=10"

<=10"

<=10"

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

+V1.8S_AC26

+V1.8S_N1

+V1.8S_B1

+V1.8S

H_THERMDA5

H_THERMDC5

H_THRMTRIP_S#16

H_PROCHOT#

TPC28 1

T50

TPC28 1

T20

REVISION DESCRIPTION:

N2

ADS#

H_PRDY#

A10

PRDY#

PREQ#

DEFER#

DRDY#

DBSY#

CONTROL

LOCK#

RESET#

RS[2]#

RS[1]#

RS[0]#

TRDY#

HITM#

BNR#

BPRI#

DBR#

BR0#

IERR#

INIT#

HIT#

B15

B14

A16

A15

AC26

F26

B18

A18

C17

B17

C16

C14

AF7

B10

L1

J3

A7

L4

H2

M2

N4

A4

B5

J2

B11

L2

K1

H1

M3

K3

K4

U27C

BCLK[0]

BCLK[1]

ITP_CLK[0]

ITP_CLK[1]

C2

A20M#

D3

FERR#

A3

IGNNE#

A6

SLP#

D1

LINT0

D4

LINT1

B4

SMI#

C6

STPCLK#

E4

PWRGOOD

H4

VID[5]

G4

VID[4]

G3

VID[3]

F3

VID[2]

F2

VID[1]

E2

VID[0]

VCCA[3]

N1

VCCA[2]

B1

VCCA[1]

VCCA[0]

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

E1

PSI#

TEST3

C3

RSVD3

RSVD2

RSVD1

B2

RSVD0

SOCKET479P

H_PREQ#

H_BR0#

H_IERR#

0.5"-12"

DATE:

SHEET OF

B

H_ADS# 7

H_BNR# 7

H_BPRI# 7

T3 TPC281

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR0# 7

R217 561 2

<=10"

<=10"

H_RS#2

H_RS#1

H_RS#0

COMP[3]

COMP[2]

HOSTCLKLEGACY CPU

COMP[1]

COMP[0]

BPM[3]#DPSLP#

BPM[2]#

BPM[1]#

BPM[0]#

GTLREF[3]

GTLREF[2]

GTLREF[1]

GTLREF[0]

TEST1

TEST2

MISC

TRST#

VCCSENSE

VSSSENSE

Monday, January 13, 2003

3

TCK

TDO

TMS

TDI

<=3"

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

COMMON CLOCK -> L6

WIDTH: 4 mils

SPACE >= 1:2

GROUP SPACE >=1:5

LENGTH: 1" - 6.5"(OPT: 4"+/-0.5")

Breakout Length:<=200 mil

(#0011)

+VCCP

H_INIT# 16,26

H_LOCK# 7

H_CPURST# 7

H_RS#[2:0] 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

CPU_COMP3

AB1

CPU_COMP2

AB2

CPU_COMP1

P26

CPU_COMP0

P25

H_BPM#3

C9B7

H_BPM#2

A9

H_BPM#1

B8

H_BPM#0

C8

AC1

G1

E26

H_GTLREF0

AD26

C5

F23

H_TCK

A13

H_TDI

C12

H_TDO

A12

H_TMS

C11

H_TRST#

B13

AE7

AF6

T48 TPC281

T49 TPC281

VR_VID5 35

VR_VID4 35

VR_VID3 35

VR_VID2 35

VR_VID1 35

VR_VID0 35

T44 TPC281

T45 TPC28

1

T46 TPC281

T47 TPC281

H_DINV#07

H_DSTBN#07

H_DSTBP#07

H_DINV#17

H_DSTBN#17

H_DSTBP#17

TOPOLOGY 2A:

R-CPU-ICH Y-FORK

CPU-ICH: 0.5" - 12"

R - CPU <= 3"

(#0013)

H_PWRGD

TOPOLOGY 2B:

MCH-CPU-ICH4

MCH-CPU:0.5"-6.5"

CPU-ICH4:0.5"-12"

(#0013)

H_DPSLP#

TOPOLOGY 3:

CPU-ICH-R-LSC-FWH

CPU-ICH:0.5" - 12"

R - LSC <= 3"

LSC-FWH:0.5"-6"(#0013)

H_INIT#

Close to Pin A12 of CPU

Width= 5 mils

Length <= 2"

CPU-BANIAS-1(24.5W)

C

H_D#15

H_D#14

H_D#13

H_D#12

H_D#11

H_D#10

H_D#9

H_D#8

H_D#7

H_D#6

H_D#5

H_D#4

H_D#3

H_D#2

H_D#1

H_D#0

H_D#31

H_D#30

H_D#29

H_D#28

H_D#27

H_D#26

H_D#25 H_D#57

H_D#24

H_D#23

H_D#22 H_D#54

H_D#21

H_D#20

H_D#19

H_D#18

H_D#17

H_D#16

R23

332

1 2

CPU DEBUG PORT

H_PREQ#

H_PRDY#

Close to Pin A8 of CPU

H_TMS

H_TDO

H_TDI

H_TCK

H_TRST#

U27A

C25

D[15]#

E23

D[14]#

B23

D[13]#

C26

D[12]#

E24

D[11]#

D24

D[10]#

B24

D[9]#

C20

D[8]#

B20

D[7]#

A21

D[6]#

B26

D[5]#

A24

D[4]#

B21

D[3]#

A22

D[2]#

A25

D[1]#

A19

D[0]#

D25

DINV[0]#

C23

DSTBN[0]#

C22

DSTBP[0]#

K25

D[31]#

N25

D[30]#

H26

D[29]#

M25

D[28]#

N24

D[27]#

L26

D[26]#

J25

D[25]#

M23

D[24]#

J23

D[23]#

G24

D[22]#

F25

D[21]#

H24

D[20]#

M26

D[19]#

L23

D[18]#

G25

D[17]#

H23

D[16]#

J26

DINV[1]#

K24

DSTBN[1]#

L24

DSTBP[1]#

SOCKET479P

TOPOLOGY 1B:

CPU-ICH-R

CPU-ICH: 0.5" - 12"

ICH-R <= 3"

(#0013)

H_FERR#

TOPOLOGY 1C:

CPU-R-LSC-ICH

CPU-R: 0.5" - 12"

R - LSC<= 3"

LSC-ICH:0.5"-12"

TOPOLOGY 1B:

CPU-ICH-R

CPU-ICH: 0.5" - 12"

ICH-R <= 3"

(#0013)

R220 2001 2

R219 5612

CPU JTAG

R37 39

1 2

R224 561 2

R223 1501 2

R225 27.41 2

R226 6801 2

D[47]#

D[46]#

D[45]#

D[44]#

D[43]#

D[42]#

D[41]#

D[40]#

D[39]#

D[38]#

D[37]#

DATA GROUP 0DATA GROUP 1

D[36]#

DATA GROUP 2DATA GROUP 3

D[35]#

D[34]#

D[33]#

D[32]#

DINV[2]#

DSTBN[2]#

DSTBP[2]#

D[63]#

D[62]#

D[61]#

D[60]#

D[59]#

D[58]#

D[57]#

D[56]#

D[55]#

D[54]#

D[53]#

D[52]#

D[51]#

D[50]#

D[49]#

D[48]#

DINV[3]#

DSTBN[3]#

DSTBP[3]#

H_PROCHOT#

H_THRMTRIP_S#

+VCCP

No Stuff

No Stuff

+VCCP

+VCCP

+VCCP

GND

1 2

+VCCP+VCCP

Y25

AA26

Y23

V26

U25

V24

U26

AA23

R23

R26

R24

V23

U23

T25

AA24

Y26

T24

W25

W24

AF26

AF22

AF25

AD21

AE21

AF20

AD24

AF23

AE22

AD23

AC25

AC22

AC20

AB24

AC23

AB25

AD20

AE24

AE25

1 2

1 2

R403

56

R404

56

R38

56

H_D#47

H_D#46

H_D#45

H_D#44

H_D#43

H_D#42

H_D#41

H_D#40

H_D#39

H_D#38

H_D#37

H_D#36

H_D#35

H_D#34

H_D#33

H_D#32

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#56

H_D#55

H_D#53

H_D#52

H_D#51

H_D#50

H_D#49

H_D#48

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

H_GTLREF0

LENGTH <=0.5"

WIDTH = 5 mils

SPACE >= 25 mils

X BPSB(#0004)

CPU_COMP2 :

Length <= 0.5"

Width = 18 mils(L1/L8)

Width = 14 mils(L3/L6)

Space>= 25 mils

X BPSB(#0001)

CPU_COMP2

Pin AD1,AC2 of BANIAS

CPU_COMP3 :

Length <= 0.5"

Width = 5 mils

Space>= 25 mils

X BPSB(#0001)

CPU_COMP3 CPU_COMP1

Pin AD1,AC2 of BANIAS

H_D#[63:0] 7

DATA GROUP 0,2 -> L3

DATA GROUP 1,3 -> L6

SPACE >= 1:3

GROUP SPACE >=1:5

LENGTH: 0.5" - 5.5"

(#0012)

H_DINV#2 7

H_DSTBN#2 7

H_DSTBP#2 7

H_DINV#3 7

H_DSTBN#3 7

H_DSTBP#3 7

+VCCP

1 2

1 2

GND

CPU_COMP0 :

Length <= 0.5"

Width = 18 mils(L1/L8)

Width = 14 mils(L3/L6)

Space>= 25 mils

X BPSB(#0001)

R12

1 2

27.4

R13561 2

CPU_COMP0

CPU_COMP1 :

Length <= 0.5"

Width = 5 mils

Space>= 25 mils

X BPSB(#0001)

GND GND

E

Close to

Pin AD26

R182

of CPU

1K

H_GTLREF0

Same Side w/ CPU

R183

2K

R21

1 2

27.4

R202

1 2

56

GNDGND

A

B

C

D

E

K22

VCC26

VCC25

VCC24

VCC23

VCC

VCCP15

VCCP16

VCCP17

VCCP18

VCC27

VCCP19

0.745V - 1.356V(+/- 1.5%)

C0: 25 A

C3: 7.59A

C4: 0.9A

AA21

AA19

AA17

AA15

AA13

AA11

AA9

AA7

AA5

Y22Y6W21W5V22V6U5

VCC39

VCC38

VCC37

VCC36

VCC35

VCC34

VCC33

VCC32

VCC31

VCC30

VCC29

VCC28

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCP25

U21

+VCCP

AB6

VCC40

AB8

VCC41

AB10

VCC42

AB12

VCC43

AB14

VCC44

AB16

VCC45

AB18

VCC46

AB20

VCC47

AB22

VCC48

AC9

VCC49

AC11

VCC50

AC13

VCC51

AC15

VCC52

AC17

VCC53

AC19

VCC54

AD8

VCC55

AD10

VCC56

AD12

VCC57

AD14

VCC58

AD16

VCC59

AD18

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

U27D

SOCKET479P

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

VSS99

VSS98

VSS100

VSS61

VSS62

VSS63

P21

SOCKET479P

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

G22

U27E

P5

P2

N26

N23

N22

N6

N3

M24

M21

M5

M4

M1

L25

L22

L6

L3

K26

K23

K21

K5

K2

J24

J22

J6

J4

J1

H25

H21

H5

H3

G26

G23

AC24

AC21

AC18

AC16

AC14

AC12

AC10

AC8

AC5

AC2

AB26

AB23

AB21

AB19

AB17

AB15

AB13

AB11

AB9

AB7

AB5

AB3

AA25

AA22

AA20

AA18

AA16

AA14

AA12

AA10

AA8

AA6

AA4

AA1

Y24

Y21Y5Y2

W26

W23

W22W6W3

V25

V21V5V4V1U24

U22U6U2

T26

T23

T21T5T3

R25

R22R6R4R1P24

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

AD1

VSS161

AD4

VSS162

AD7

VSS163

AD9

VSS164

AD11

VSS165

AD13

VSS166

AD15

VSS167

AD17

VSS168

AD19

VSS169

AD22

VSS170

AD25

VSS171

AE3

VSS172

AE6

VSS173

AE8

VSS174

AE10

VSS175

AE12

VSS176

AE14

VSS177

AE16

VSS178

AE18

VSS179

AE20

VSS180

AE23

VSS181

AE26

VSS182

AF2

VSS183

AF5

VSS184

AF9

VSS185

AF11

VSS186

AF13

VSS187

AF15

VSS188

AF17

VSS189

AF19

VSS190

AF21

VSS191

AF24

VSS192

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

A2A5A8

A11

A14

A17

A20

A23

A26B3B6B9B12

B16

B19

B22

B25C1C4C7C10

C13

GND

VSS23

C15

VSS24

C18

C21

VSS25

VSS26

VSS27

C24D2D5D7D9

GND

VSS28

VSS29

VSS30

VSS31

D11

D13

VSS32

VSS33

D15

D17

VSS34

VSS35

D19

VSS36

VSS37

D21

D23

D26E3E6E8E10

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

E12

E14

VSS44

VSS45

E16

E18

VSS46

VSS47

VSS48

VSS49

E20

E22

E25F1F4F5F7F9F11

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

F13

VSS57

F15

VSS58

F17

VSS59

F19

VSS60

F21

F24G2G6

HFM(1.3GHz-1.7GHz): 1.468V

LFM( 600MHz): 0.956V

1 1

+VCORE

F20

F18F8F6

E21

E19

E17E9E7E5D22

D20

D18D8D6

VCC9

VCC8

VCC7

VCC6

VCC5

VCC4

VCC3

VCC2

VCC1

2 2

VCCQ[1]

VCCQ[0]

W4

P23

+VCCP

12

12

C41

C46

0.1U

0.1U

3 3

GND

VCCP1

D10

VCC10

VCCP2

D12

VCC11

VCCP3

D14

VCC12

VCCP4

D16

VCC13

VCCP5

E11

VCC14

VCCP6

E13

E15

J21J5H22H6G21G5F22

VCC22

VCC21

VCC20

VCC19

VCC18

VCC17

VCC16

VCC15

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

F10

F12

F14

F16K6L5

L21M6M22N5N21P6P22R5R21T6T22

1.0V - 1.1V(+/- 5%)

S0-S1M: 2.5 A(CPU,MCH,ICH)

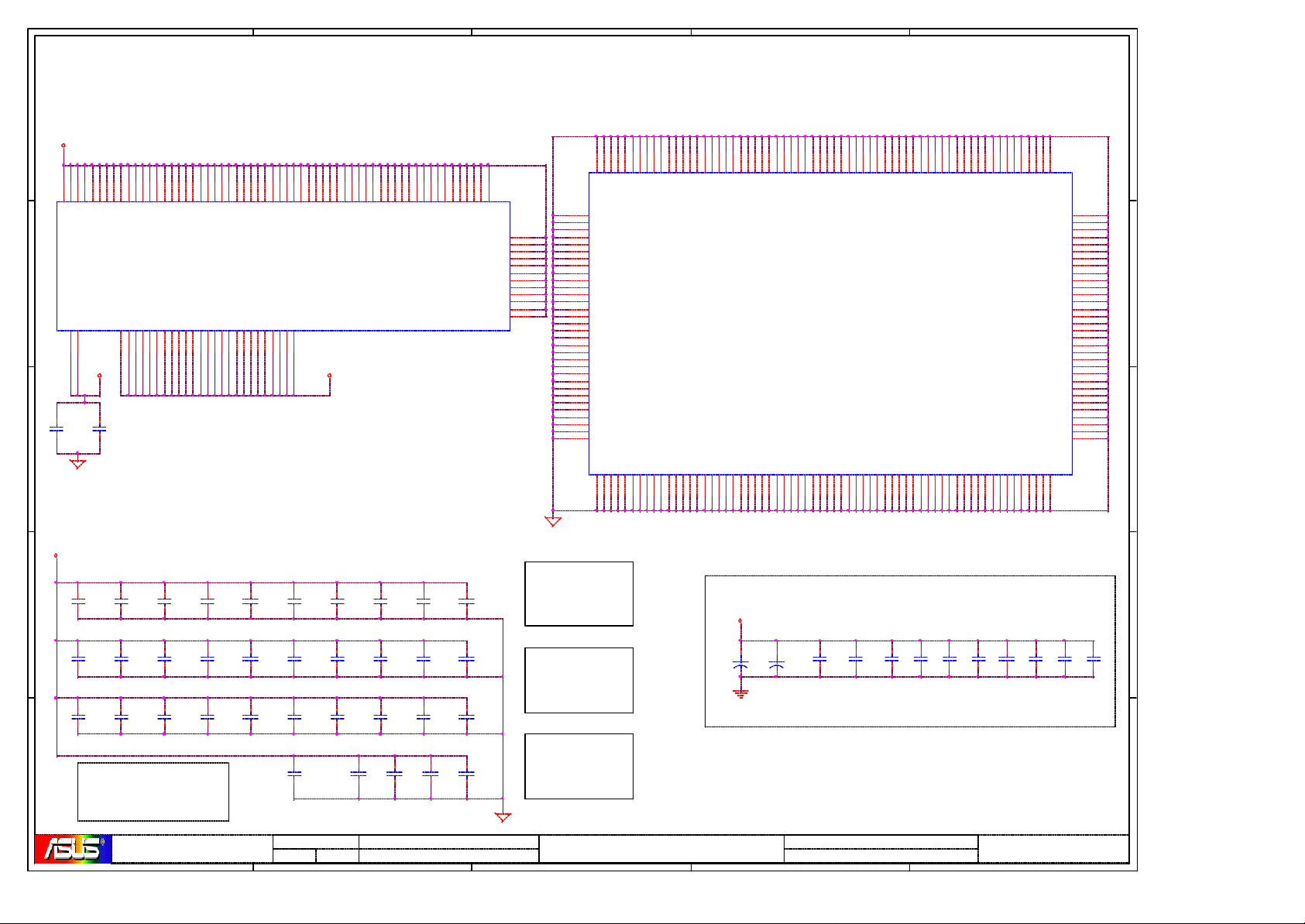

CPU VCORE Decoupling Capacitor

+VCORE

Mid Frequency

GND

Decoupling (Place

around Processor)

High Frequency

Decoupling (Place

underneath

Processor) using

10uF/6.3V X5R

+VCORE

Bulk

Decoupling

C

+VCCP

12

CE2

+

150U

CPU-BANIAS-2(24.5W)

+VCCP (CPU) Decoupling Capacitor

(Place near CPU)

12

CE1

+

150U

12

12

C38

C39

0.1U

0.1U

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

12

12

C230

0.1U

C226

0.1U

12

C225

0.1U

12

12

C227

C40

0.1U

0.1U

E

12

12

C232

0.1U

C229

0.1U

12

C25

0.1U

12

12

12

12

C9

10UF

C30

10UF/6.3V

C50

10UF/6.3V

12

C10

10UF

12

12

C31

10UF/6.3V

C52

10UF/6.3V

C8

4 4

5 5

10UF

12

C29

10UF

12

C49

10UF/6.3V

Four 200 uF are

12

C11

10UF

12

12

C32

10UF/6.3V

C53

10UF/6.3V

12

C20

10UF

12

12

C33

10UF/6.3V

C59

10UF/6.3V

12

C18

10UF

12

12

12

C44

10UF/6.3V

C54

10UF/6.3V

C72

10UF/6.3V

12

12

12

C22

10UF

C45

10UF/6.3V

C57

10UF/6.3V

12

C70

10UF/6.3V

12

C21

10UF

12

12

C51

10UF/6.3V

C60

10UF/6.3V

12

C69

10UF/6.3V

12

C19

10UF

12

12

12

C47

10UF/6.3V

C58

10UF/6.3V

C66

10UF/6.3V

12

C27

10UF

12

12

12

C48

10UF/6.3V

C63

10UF/6.3V

C61

10UF/6.3V

located in IMVP4

PROJECT:

A

WB

REVISION DESCRIPTION:

Monday, January 13, 2003

DATE:

SHEET OF

B

4

A

1 1

2 2

B

Route H_THERMDA and H_THERMDC

on the same layer

------------------OTHER SIGNALS

12 mils

===============GND

10 mils

=========H_THERMDA(10 mils)

10 mils

=========H_THERMDC(10 mils)

10 mils

=========GND

12 mils

---------------------OTHER SIGNALS

C

D

E

Avoid BPSB,Power

+V3.3S

R35 200

3 3

SCL_3S10,11,18,31

SDA_3S10,11,18,31 H_THERMDA 3

1 2

PM_THRM#(Pull-Up 10K in Page 32)

PM_THRM#16,32

4 4

5 5

PROJECT:

A

WB

REVISION DESCRIPTION:

Monday, January 13, 2003

DATE:

SHEET OF

B

5

GND

SCL_3S

+V3.3S_THM

+V3.3S_THM

12

C71

0.1U

Standby Mode: 3uA(Max. 10uA)

Full Active: 0.5 mA(Max. 1mA)

1

U5

8

7

6

VCC

SMBCLK

OVERT

SMBDATA

Close to Pin A18

& B18 of CPU

ALERT#

MAX6657

5

GND

DXP

DXN

4

2

3

THERMAL

C

OS#_OC(Pull-Up 10K in Page 32)

OS#_OC

OS#_OC 32

H_THERMDASDA_3S

H_THERMDC

4"-8"

12

C65

2200P

4"-8"

H_THERMDC 3

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

E

A

_DDR_DATA[63:0]10,11,12

1 1

2 2

3 3

_DDR_CB[7:0]10,11,12

4 4

_DDR_DATA0

_DDR_DATA1

_DDR_DATA2

_DDR_DATA3

_DDR_DATA4

_DDR_DATA5

_DDR_DATA6

_DDR_DATA7

_DDR_DATA8

_DDR_DATA9

_DDR_DATA10

_DDR_DATA11

_DDR_DATA12

_DDR_DATA13

_DDR_DATA14

_DDR_DATA15

_DDR_DATA16

_DDR_DATA17

_DDR_DATA18

_DDR_DATA19

_DDR_DATA20

_DDR_DATA21

_DDR_DATA22

_DDR_DATA23

_DDR_DATA24

_DDR_DATA25

_DDR_DATA26

_DDR_DATA27

_DDR_DATA28

_DDR_DATA29

_DDR_DATA30

_DDR_DATA31

_DDR_DATA32

_DDR_DATA33

_DDR_DATA34

_DDR_DATA35

_DDR_DATA36

_DDR_DATA37

_DDR_DATA38

_DDR_DATA39

_DDR_DATA40

_DDR_DATA41

_DDR_DATA42

_DDR_DATA43

_DDR_DATA44

_DDR_DATA45

_DDR_DATA46

_DDR_DATA47

_DDR_DATA48

_DDR_DATA49

_DDR_DATA50

_DDR_DATA51

_DDR_DATA52

_DDR_DATA53

_DDR_DATA54

_DDR_DATA55

_DDR_DATA56

_DDR_DATA57

_DDR_DATA58

_DDR_DATA59

_DDR_DATA60

_DDR_DATA61

_DDR_DATA62

_DDR_DATA63

_DDR_CB0

_DDR_CB1

_DDR_CB2

_DDR_CB3

_DDR_CB4

_DDR_CB5

_DDR_CB6

_DDR_CB7

Intel suggested that DDR_VREF should

be turned off in S3-S5. But measure the

leakage because there is no +V2.5S.

+V5

12

DDR_VREF

4

C301

0.1uF

1.225V-1.275V

S0-S1M:10 mA(Max.

50 mA)

12

R290

10K

12

12

C297

0.1uF

5 5

R289

10K

1

3

52

V+

+

V-

LMV321M5X

U36

B

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

10Ohm

RN27B

RN27A

RN26B

RN26A

RN79A

RN79B

RN78A

RN78B

RN25B

RN25A

RN24B

RN24A

RN77A

RN77B

RN76A

RN76B

RN23B

RN23A

RN22B

RN22A

RN75A

RN75B

RN74A

RN74B

RN21B

RN21A

RN20B

RN20A

RN73A

RN73B

RN72A

RN72B

RN14B

RN14A

RN13B

RN13A

RN67A

RN67B

RN66A

RN66B

RN12B

RN12A

RN11B

RN11A

RN65A

RN65B

RN64A

RN64B

RN10B

RN10A

RN9B

RN9A

RN63A

RN63B

RN62A

RN62B

RN8B

RN8A

RN7B

RN7A

RN61A

RN61B

RN60A

RN60B

RN19B

RN19A

RN18B

RN18A

RN71A

RN71B

RN70A

RN70B

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

1.23125V-1.26875V

S0-S1M:Max. 80 mA

S3: 0 mA

DDR_SMRCOMP

Thermal Power: ~ 3.8W

DDR_DATA0

DDR_DATA1

DDR_DATA2

DDR_DATA3

DDR_DATA4

DDR_DATA5

DDR_DATA6

DDR_DATA7

DDR_DATA8

DDR_DATA9

DDR_DATA10

DDR_DATA11

DDR_DATA12

DDR_DATA13

DDR_DATA14

DDR_DATA15

DDR_DATA16

DDR_DATA17

DDR_DATA18

DDR_DATA19

DDR_DATA20

DDR_DATA21

DDR_DATA22

DDR_DATA23

DDR_DATA24

DDR_DATA25

DDR_DATA26

DDR_DATA27

DDR_DATA28

DDR_DATA29

DDR_DATA30

DDR_DATA31

DDR_DATA32

DDR_DATA33

DDR_DATA34

DDR_DATA35

DDR_DATA36

DDR_DATA37

DDR_DATA38

DDR_DATA39

DDR_DATA40

DDR_DATA41

DDR_DATA42

DDR_DATA43

DDR_DATA44

DDR_DATA45

DDR_DATA46

DDR_DATA47

DDR_DATA48

DDR_DATA49

DDR_DATA50

DDR_DATA51

DDR_DATA52

DDR_DATA53

DDR_DATA54

DDR_DATA55

DDR_DATA56

DDR_DATA57

DDR_DATA58

DDR_DATA59

DDR_DATA60

DDR_DATA61

DDR_DATA62

DDR_DATA63

DDR_CB0

DDR_CB1

DDR_CB2

DDR_CB3

DDR_CB4

DDR_CB5

DDR_CB6

DDR_CB7

DDR_VREF

12

C298

0.1uF

T24 TPC28 1

12

R324

60.4

12

R311

60.4

AF2

AE3

AF4

AH2

AD3

AE2

AG4

AH3

AD6

AG5

AG7

AE8

AF5

AH4

AF7

AH6

AF8

AG8

AH9

AG10

AH7

AD9

AF10

AE11

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ24

MONTARA_GML

D DR_RCVENIN#

12

C314

0.1uF

U35B

LxWxH=37.5x37.5x2.58

SM_SDQ0

SM_SDQ1

SM_SDQ2

SM_SDQ3

SM_SDQ4

SM_SDQ5

SM_SDQ6

SM_SDQ7

SM_SDQ8

SM_SDQ9

SM_SDQ10

SM_SDQ11

SM_SDQ12

SM_SDQ13

SM_SDQ14

SM_SDQ15

SM_SDQ16

SM_SDQ17

SM_SDQ18

SM_SDQ19

SM_SDQ20

SM_SDQ21

SM_SDQ22

SM_SDQ23

SM_SDQ24

SM_SDQ25

SM_SDQ26

SM_SDQ27

SM_SDQ28

SM_SDQ29

SM_SDQ30

SM_SDQ31

SM_SDQ32

SM_SDQ33

SM_SDQ34

SM_SDQ35

SM_SDQ36

SM_SDQ37

SM_SDQ38

SM_SDQ39

SM_SDQ40

SM_SDQ41

SM_SDQ42

SM_SDQ43

SM_SDQ44

SM_SDQ45

SM_SDQ46

SM_SDQ47

SM_SDQ48

SM_SDQ49

SM_SDQ50

SM_SDQ51

SM_SDQ52

SM_SDQ53

SM_SDQ54

SM_SDQ55

SM_SDQ56

SM_SDQ57

SM_SDQ58

SM_SDQ59

SM_SDQ60

SM_SDQ61

SM_SDQ62

SM_SDQ63

SM_SDQ64

SM_SDQ65

SM_SDQ66

SM_SDQ67

SM_SDQ68

SM_SDQ69

SM_SDQ70

SM_SDQ71

SM_VREF

Close to Pin AJ22

SM_RCVENIN#

AC16

DDR_SMVSWINGL

12

C

DDR_DQS0

AG2

SM_SDQS0

SM_SDQS1

SM_SDQS2

SM_SDQS3

SM_SDQS4

SM_SDQS5

SM_SDQS6

SM_SDQS7

SM_SDQS8

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_B1

SMA_B2

SMA_B4

SMA_B5

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS#0

SM_CS#1

SM_CS#2

SM_CS#3

SM_BA0

SM_BA1

DDR SYSTEM MEMORY

SM_RAS#

SM_CAS#

SM_WE#

SM_CMDCLK0

SM_CMDCLK#0

SM_CMDCLK1

SM_CMDCLK#1

SM_CMDCLK2

SM_CMDCLK#2

SM_CMDCLK3

SM_CMDCLK#3

SM_CMDCLK4

SM_CMDCLK#4

SM_CMDCLK5

SM_CMDCLK#5

SM_DM0

SM_DM1

SM_DM2

SM_DM3

SM_DM4

SM_DM5

SM_DM6

SM_DM7

SM_DM8

SMRCOMP

SMVSWINGL

SM_RCVENOUT#

SMVSWINGH

AC15

DDR_RCVENOUT#

+V2.5_GMCH_SM+V2.5_GMCH_SM

12

R302

604

R301

C302

150

0.1uF

1 2

DDR_DQS1

AH5

DDR_DQS2

AH8

DDR_DQS3

AE12

DDR_DQS4

AH17

DDR_DQS5

AE21

DDR_DQS6

AH24

DDR_DQS7

AH27

DDR_DQS8

AD15

DDR_AA0

AC18

DDR_AA1

AD14

DDR_AA2

AD13

DDR_AA3

AD17

DDR_AA4

AD11

DDR_AA5

AC13

DDR_AA6

AD8

DDR_AA7

AD7

DDR_AA8

AC6

DDR_AA9

AC5

DDR_AA10

AC19

DDR_AA11

AD5

DDR_AA12

AB5

DDR_AB1

AD16

DDR_AB2

AC12

DDR_AB4

AF11

DDR_AB5

AD10

AC7

AB7

AC9

AC10

AD23

AD26

AC22

AC25

AD22

AD20

AC21

AC24

AD25

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

DDR_DM0

AE5

DDR_DM1

AE6

DDR_DM2

AE9

DDR_DM3

AH12

DDR_DM4

AD19

DDR_DM5

AD21

DDR_DM6

AD24

DDR_DM7

AH28

DDR_DM8

AH15

DDR_SMRCOMP

AB1

DDR_SMVSWINGL

AJ22

D DR_SMVSWINGH

AJ19

T25 TPC281

0.8 VCCSM +/- 2%0.2 VCCSM +/- 2%

D DR_SMVSWINGH

Close to Pin AJ19

R97101 2

R100101 2

R102101 2

R10110

1 2

R95101 2

R99101 2

R94101 2

R98101 2

R9610

1 2

DDR_AA[12:0] 10,11,12

DDR_AB[2:1] 11,12

DDR_AB[5:4] 11,12

DDR_CKE0 10,12

DDR_CKE1 10,12

DDR_CKE2 11,12

DDR_CKE3 11,12

DDR_CS0# 10,12

DDR_CS1# 10,12

DDR_CS2# 11,12

DDR_CS3# 11,12

DDR_BS0# 10,11,12

DDR_BS1# 10,11,12

DDR_RAS# 10,11,12

DDR_CAS# 10,11,12

DDR_WE# 10,11,12

CLK_DDR0 10

CLK_DDR0# 10

CLK_DDR1 10

CLK_DDR1# 10

CLK_DDR2 10

CLK_DDR2# 10

CLK_DDR3 11

CLK_DDR3# 11

CLK_DDR4 11

CLK_DDR4# 11

CLK_DDR5 11

CLK_DDR5# 11

R315101 2

R318101 2

R321101 2

R320101 2

R31310

1 2

R317101 2

R312101 2

R316101 2

R314101 2

1.23125V-1.26875V

S0-S1M:Max. 80 mA

S3: 0 mA

+V2.5_GMCH_SM+V2.5

R303

150

1 2

12

12

R304

C303

604

0.1uF

D

_DDR_DQS0

_DDR_DQS1

_DDR_DQS2

_DDR_DQS3

_DDR_DQS4

_DDR_DQS5

_DDR_DQS6

_DDR_DQS7

_DDR_DQS8

_DDR_DM0

_DDR_DM1

_DDR_DM2

_DDR_DM3

_DDR_DM4

_DDR_DM5

_DDR_DM6

_DDR_DM7

_DDR_DM8

_DDR_DQS[8:0] 10,11,12

(MCH-Sighting041)

M-GM system memory interface generates

single pulse CKE events which may cause

Intermittent hangs and display corruptions

when using Micron and Infineon

S0-DIMMs.

MCH-M

10 OHM

Route for COMMAND

1. DDR_AA[12:6],DDR_AA3,DDR_AA0

2. DDR_WE#

3. DDR_RAS#

4. DDR_CAS#

5. DDR_BS0#,DDR_BS1#

Route for CPC

1. DDR_AA[5:4],DDR_AA[2:1]

MCH-M

Route for CPC

1. DDR_AB[5:4],DDR_AB[2:1]

_DDR_DM[8:0] 10,11,12

Route for CONTROL

1. DDR_CKE[1:0],DDR_CS[1:0]#

MCH-M

Route for CONTROL

1. DDR_CKE[3:2],DDR_CS[3:2]#

Route for CLOCK

1. CLK_DDR[2:0],CLK_DDR[2:0 ]#

MCH-M

Route for CLOCK

1. CLK_DDR[5:3],CLK_DDR[5:3 ]#

E

SO-DIMM0

SO-DIMM1

SO-DIMM0

SO-DIMM1

SO-DIMM0

SO-DIMM1

SO-DIMM0

SO-DIMM1

TERMINATION

TERMINATION

TERMINATION

PROJECT:

A

WB

REVISION DESCRIPTION:

Monday, January 13, 2003

DATE:

SHEET OF

B

6

C

MONTARA_GM-1(3.8W)

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

E

A

MCH_HLZCOMP :

Length <= 0.5"

Width = 18 mils(L1/L8)

Width = 14 mils(L3/L6)

1 1

2 2

3 3

4 4

5 5

Space>= 25 mils

X BPSB(#0002)

MCH_HLZCOMP

MCH_HYRCOMP :

Length <= 0.5"

Width = 18 mils(L1/L8)

Width = 14 mils(L3/L6)

Space>= 25 mils

X BPSB(#0002)

MCH_HYRCOMP

MCH_HXRCOMP :

Length <= 0.5"

Width = 18 mils(L1/L8)

Width = 14 mils(L3/L6)

Space>= 25 mils

X BPSB(#0002)

MCH_HXRCOMP

MCH_HYSWING :

Length <= 0.5"

Width = 15 mils

Space>= 25 mils

X BPSB(#0005)

1/3(+VCCP) +/- 2%

MCH_HYSWING

Close to Pin H28

MCH_HXSWING :

Length <= 0.5"

Width = 15 mils

Space>= 25 mils

X BPSB(#0005)

1/3(+VCCP) +/- 2%

MCH_HXSWING MCH_HDVREF

Close to Pin B20

1 2

R254 27.4

_CLK_MCH_BCLK#31

_CLK_MCH_BCLK31

1 2

R257 27.4

V1.1

H_CPURST#3

HUB_PD[10:0]15

R54

56Ohm

1 2

H_CPURST#

+VCCP

12

R253

301

12

C271

R262

0.1uF

150

1 2

+VCCP +VCCP

12

R255

301

12

R263

C272

150

0.1uF

1 2

B

U35A

H_A#[31:3]3

H_REQ#[4:0]3

H_DSTBN#03

H_DSTBN#13

H_DSTBN#23

H_DSTBN#33

H_DSTBP#03

H_DSTBP#13

H_DSTBP#23

H_DSTBP#33

H_DINV#03

H_DINV#13

H_DINV#23

H_DINV#33

HUB_PSTRB15

HUB_PSTRB#15

0.8V +/- 2%

H_ADSTB#03

H_ADSTB#13

MCH_HYRCOMP

MCH_HYSWING

MCH_HXRCOMP

MCH_HXSWING

MCH_HDVREF

MCH_HCCVREF

MCH_HAVREF

+V1.2S_GMCH_HI

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

+V1.2S_GMCH_HI+VCCP

12

1 2

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

R306

27.4

MCH_HLZCOMP

1 2

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

<=8"

<=8"

<=8"

HUB_PSTRB

HUB_PSTRB#

MONTARA_GML

R308

49.9

H UB_VSWING_MCH

R305

100

AA27

AA28

AB27

AB28

AA26

AD29

AE29

LxWxH=37.5x37.5x2.58

P23

HA#3

T25

HA#4

T28

HA#5

R27

HA#6

U23

HA#7

U24

HA#8

R24

HA#9

U28

HA#10

V28

HA#11

U27

HA#12

T27

HA#13

V27

HA#14

U25

HA#15

V26

HA#16

Y24

HA#17

V25

HA#18

V23

HA#19

W25

HA#20

Y25

HA#21

HA#22

W24

HA#23

W23

HA#24

W27

HA#25

Y27

HA#26

HA#27

W28

HA#28

HA#29

Y26

HA#30

HA#31

R28

H_REQ#0

P25

H_REQ#1

R23

H_REQ#2

R25

H_REQ#3

T23

H_REQ#4

T26

H_ADSTB0#

H_ADSTB1#

HCLK#

HCLK

H28

HYRCOMP

K28

HYSWING

B20

HXRCOMP

B18

HXSWING

J28

HDSTBN#0

C27

HDSTBN#1

E22

HDSTBN#2

D18

HDSTBN#3

K27

HDSTBP#0

D26

HDSTBP#1

E21

HDSTBP#2

E18

HDSTBP#3

J25

DINV#0

E25

DINV#1

B25

DINV#2

G19

DINV#3

F15

H_CPURST#

K21

HDVREF0

J21

HDVREF1

J17

HDVREF2

Y28

HCCVREF

Y22

HAVREF

T2

HLZCOMP

U7

HUB_PD0

U4

HUB_PD1

U3

HUB_PD2

V3

HUB_PD3

W2

HUB_PD4

W6

HUB_PD5

V6

HUB_PD6

W7

HUB_PD7

T3

HUB_PD8

V5

HUB_PD9

V4

HUB_PD10

W3

HUB_PSTRB

V2

HUB_PSTRB#

PSWING

U2

12

C304

0.1uF

C

HOST

HUB I/F

HUB_LVREF

0.343V- 0.357V(Typ. 0.35V)

W1

HUB_VREF_MCH

12

12

C309

0.1uF

C307

0.01UF

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BREQ0#

H_BNR#

H_BPRI#

H_DBSY#

H_RS#0

H_RS#1

H_RS#2

R319

100

1 2

K22

H27

K25

L24

J27

G28

L27

L23

L25

J24

H25

K23

G27

K26

J23

H26

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

L28

M25

N24

M28

N28

N27

P27

M23

N25

P28

M26

N23

P26

M27

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_RS#0

H_RS#1

H_RS#2

1 2

R310

240

H_ADS# 3

H_TRDY# 3

H_DRDY# 3

H_DEFER# 3

H_HITM# 3

H_HIT# 3

H_LOCK# 3

H_BR0# 3

H_BNR# 3

H_BPRI# 3

H_DBSY# 3

H_RS#[2:0] 3

+V1.2S_GMCH_HI

H_D#[63:0] 3

D

MCH_HAVREF:

Length <= 0.5"

Width = 5 mils

Space>= 25 mils

X BPSB(#0003)

MCH_HCCVREF:

Length <= 0.5"

Width = 5 mils

Space>= 25 mils

X BPSB(#0003)

MCH_HDVREF:

Length <= 0.5"

Width = 5 mils

Space>= 25 mils

X BPSB(#0003)

C103

0.1uF

2/3(+VCCP) +/- 2%

MCH_HAVREF

C109

0.1uF

2/3(+VCCP) +/- 2%

MCH_HCCVREF

C290

0.1uF

2/3(+VCCP) +/- 2%

12

12

C99

C98

0.1uF

0.1uF

E

+VCCP

12

R78

49.9

12

12

R79

C110

100

1uF

1 2

+VCCP

12

R278

49.9

12

12

12

R275

C289

100

1uF

1 2

12

R68

49.9

12

C102

R72

1uF

100

1 2

PROJECT:

A

WB

REVISION DESCRIPTION:

Monday, January 13, 2003

DATE:

SHEET OF

B

7

C

MONTARA_GM-2(3.8W)

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

E

A

1 1

+V1.5S_GMCH_DVO

R82

1K

ADDDETECT

2 2

3 3

4 4

5 5

V1.1

1 2

R461

1K_*

1 2

PM_SUSCLK16

B

+V1.5S_GMCH_DVO

+V1.5S_GMCH_DVO

+V1.5S_GMCH_DVO

R288

1K

1 2

3

Q72

D

2N7002

1

G

S

2

0.5 VCCDVO +/- 2%

DVO_VREF

Close to Pin F1

1 2

R85

100K

R84 2.2K

R89 2.2K

CLK_DPMS

+V1.5S_GMCH_DVO

R299

1K

1 2

12

R300

C299

1K

0.1U

1 2

1 2

1 2

2.2KOhm

3 4

2.2KOhm

5 6

2.2KOhm

7 8

2.2KOhm

1 2

R80 1K_*12

AGP_BUSY#16,18

_CLK_MCH6631

RN6B

100K

3 4

1 2

100K

RN6A

1 2

RN5A

RN5C

RN5D

MCH_GRCOMP

T26 TPC28

R83

100K

ADDDETECT

DVO_VREF

1

Width= 10 mils

Space>=20

mils

MCH_GRCOMP

C

U35C

LxWxH=37.5x37.5x2.58

R3

DVOBD0

R5

DVOBD1

R6

DVOBD2

R4

DVOBD3

P6

DVOBD4

P5

DVOBD5

N5

DVOBD6

P2

DVOBD7

N2

DVOBD8

N3

DVOBD9

M1

DVOBD10

M5

DVOBD11

P3

DVOBCLK

P4

DVOBCLK#

T6

DVOBHSYNC

T5

DVOBVSYNC

L2

DVOBBLANK#

M2

DVOBFLDSTL

G2

DVOBCINTRB

M3

DVOBCCLKINT

K5

DVOCD0

K1

DVOCD1

K3

DVOCD2

K2

DVOCD3

J6

DVOCD4

J5

DVOCD5

H2

DVOCD6

H1

DVOCD7

H3

DVOCD8

H4

DVOCD9

H6

DVOCD10

G3

DVOCD11

J3

DVOCCLK

J2

DVOCCLK#

K6

DVOCHSYNC

L5

DVOCVSYNC

L3

DVOCBLANK#

H5

DVOCFLDSTL

K7

MI2CCLK

N6

MI2CDATA

N7

MDVICLK

M6

MDVIDATA

P7

MDDCCLK

T7

MDDCDATA

E5

ADDID0

F5

ADDID1

E3

ADDID2

E2

ADDID3

G5

ADDID4

F4

ADDID5

G6

ADDID6

F6

ADDID7

L7

ADDDETECT

D5

DPMS

F1

GVREF

F7

AGPBUSY#

D1

GRCOMP

Y3

66IN

AA5

RVSD0

F2

RVSD1

F3

RVSD2

B2

RVSD3

B3

RVSD4

C2

RVSD5

C3

RVSD6

C4

RVSD7

D2

RVSD8

D3

RVSD9

D7

RVSD10

L4

RVSD11

MONTARA_GML

R296

40.2

M_LCLKCTLB

12

DVO

PCI_RST#15,19,20,24

GREEN#

DACCLKSMISCNC

DDCACLK

DDCADATA

Montania #035

LVDS

DDCPCLK

DDCPDATA

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

MCHDETECTVSS

+V5S

12

C273

0.1U_*

1 2

A B

NC7SZ384_*

BLUE

BLUE#

GREEN

RED

RED#

HSYNC

VSYNC

REFSET

IYAM0

IYAM1

IYAM2

IYAM3

IYAP0

IYAP1

IYAP2

IYAP3

IYBM0

IYBM1

IYBM2

IYBM3

IYBP0

IYBP1

IYBP2

IYBP3

ICLKAM

ICLKAP

ICLKBM

ICLKBP

LVREFH

LVREFL

LVBG

LIBG

DPWR#

DPSLP#

RSTIN#

PWROK

EXTTS0

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

54

U33

VCCBE#

3

C9

D9

C8

D8

A7

A8

H10

J9

E8

B6

G9

G14

E15

C15

C13

F14

E14

C14

B13

H12

E12

C12

G11

G12

E11

C11

G10

D14

E13

E10

F10

B4

C5

G8

F8

A5

D12

F12

B12

A10

B7

B17

H9

C6

AA22

Y23

AD28

J11

D6

AJ1

B1

AH1

A2

AJ2

A28

AJ28

A29

B29

AH29

AJ29

AA9

AJ4

GND

CRT_REFSET

LVDS_YA0M 13

LVDS_YA1M 13

LVDS_YA2M 13

LVDS_YA3M 13

LVDS_YA0P 13

LVDS_YA1P 13

LVDS_YA2P 13

LVDS_YA3P 13

LVDS_YB0M 13

LVDS_YB1M 13

LVDS_YB2M 13

LVDS_YB3M 13

LVDS_YB0P 13

LVDS_YB1P 13

LVDS_YB2P 13

LVDS_YB3P 13

LVDS_CLKAM 13

LVDS_CLKAP 13

LVDS_CLKBM 13

LVDS_CLKBP 13

LVDS_BACK_ADJ 13

LVDS_BACK_EN 13

LVDS_VDD_EN 13

1

1 2

R280 1.5K

_CLK_MCH_DREF 31

_CLK_MCH_DREFSS 31

1

M_LCLKCTLB

H_DPWR# 3

<=6.5"

PCI_RST# 15,19,20,24

R62601 2

+V3.3S

R269

10K

1 2

D

CRT_BLUE 14

CRT_GREEN 14

CRT_RED 14

CRT_HSYNC 14

CRT_VSYNC 14

R76

1 2

137

CRT_DDC2BC 14

CRT_DDC2BD 14

T21TPC281

T22TPC28

T7TPC281RN5B

T23TPC28

H_DPSLP# 3,16

R631

0Ohm

1 2

+V3.3S_GMCH_GPIO

2.2K

1 2

RN59A

LVDS_DDC2BC 13

Supprt EID

IMVP4_PWRGD 31,33,35

M_LCLKCTLB

+V3.3S_GMCH_GPIO

2.2K

3 4

RN59B

+V3.3S_GMCH_GPIO

R287

10K

1 2

E

LVDS_DDC2BD 13

PROJECT:

A

WB

REVISION DESCRIPTION:

Monday, January 13, 2003

DATE:

SHEET OF

B

8

C

MONTARA_GM-3(3.8W)

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

E

A

B

(MCH-Sighting041)

The core supply (1.2V) should be

powered up a minimum of 1ms before

the DVO and GPIO IO (1.5V and 3.3V)

voltage rails.

C

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.3 A

+V1.2S_GMCH_CORE

12

C97

0.1U

D

+V1.2S_GMCH_HI

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.3 A

12

C306

0.1U

E

LxWxH=37.5x37.5x2.58

1 1

2 2

3 3

4 4

5 5

LxWxH=37.5x37.5x2.58

MONTARA_GML

U35D

C1

VSS0

G1

VSS1

L1

VSS2

U1

VSS3

AA1

VSS4

AE1

VSS5

R2

VSS6

AG3

VSS7

AJ3

VSS8

D4

VSS9

G4

VSS10

K4

VSS11

N4

VSS12

T4

VSS13

W4

VSS14

AA4

VSS15

AC4

VSS16

AE4

VSS17

B5

VSS18

U5

VSS19

Y5

VSS20

Y6

VSS21

AG6

VSS22

C7

VSS23

E7

VSS24

G7

VSS25

J7

VSS26

M7

VSS27

R7

VSS28

AA7

VSS29

AE7

VSS30

AJ7

AC8

W9

AB9

AG9

C10

J10

AA10

AE10

D11

F11

H11

AB11

AC11

AJ11

J12

AA12

AG12

A13

D13

F13

H13

N13

R13

U13

AB13

AE13

J14

P14

T14

AA14

AC14

D15

H15

N15

R15

U15

AB15

AG15

F16

J16

P16

VSS31

H8

VSS32

K8

VSS33

P8

VSS34

T8

VSS35

V8

VSS36

Y8

VSS37

VSS38

E9

VSS39

L9

VSS40

N9

VSS41

R9

VSS42

U9

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS181

AJ26

VSS

VSS179

VSS180

E28L6T9

VSS177

VSS178

C22

D28

VSS173

VSS174

VSS176

AJ18

AJ20

VSS172

AJ10

AJ12

VSS170

VSS171

W29

AA29

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

T16

AA16

AE16

A17

D17

H17

N17

R17

U17

AB17

AC17

F18

J18

AA18

AG18

A19

D19

H19

AB19

AE19

F20

J20

AA20

AC20

A21

D21

H21

M21

P21

T21

V21

Y21

AA21

AB21

AG21

B24

F22

J22

L22

N22

R22

U22

W22

AE22

A23

D23

AA23

AC23

AJ23

F24

H24

K24

M24

P24

T24

V24

AA24

AG24

A25

D25

AA25

AE25

G26

J26

L26

N26

R26

U26

W26

AB26

A27

F27

AC27

AG27

AJ27

AC28

AE28

C29

E29

G29

J29

L29

N29

U29

+V1.2S

80 OHM/100MHZ

Caution:

L2 be placed between Pin U9 ans U13

+V1.2S_GMCH_CORE

80 OHM/100MHZ

+V1.5S

80 OHM/100MHZ

1.425V - 1.575V(+/- 5%)

S0-S1M: Max. 90 mA

Caution:

There is no vias between Pin B8 and C99,C100

(It means C99,C100 must be in same layer with MCHM)

1.425V - 1.575V(+/- 5%)

1.425V - 1.575V(+/- 5%)

S0-S1M: Max. 70 mA

1.425V - 1.575V(+/- 5%)

S0-S1M: Max. 70 mA

2.375V - 2.625V(+/- 5%)

S0-S3: Max. 50 mA

3.135V - 3.465V(+/- 5%)

1.14V - 1.26V(+/- 5%)

L29

S0-S1M:Max. 1.4 A

21

12

12

+

+

CE16

10U

CE17

150U

CE18

150U

1.14V - 1.26V(+/- 5%)

L11

S0-S1M:Max. 90 mA

21

12

12

C119

10U

L10

+V1.5S

80 OHM/100MHZ

+V1.5S

80 OHM/100MHZ

+V1.5S

80 OHM/100MHZ

+V2.5

80 OHM/100MHZ

0.1U

C125

21

L24

L23

L20

L21

+V1.2S_GMCH_CORE +V1.2S_GMCH_CORE+V1.2S_GMCH_DPLLB

21

21

21

21

CE10

22U/10V

+V3.3S

12

+

CE15

150U

CE9

22U/10V

12

+

C277

0.1U

80 OHM/100MHZ

80 OHM/100MHZ

12

+

12

0.1U

C104

12

0.1U

C122

12

C111

10U

12

C291

0.1uF

12

C286

0.1uF

12

+

C276

0.1U

12

C283

0.1U

L25

10U/16V_TAN

L22

21

CE11

150U

+V1.2S_GMCH_CORE

12

12

0.1U

0.1U

0.1U

C115

C113

C117

+V1.2S_GMCH_HI

+V1.5S_GMCH_DVO

12

C114

0.1U

21

12

C300

0.1U

+V1.5S_GMCH_ADAC

12

C293

0.01uF

+V1.5S _GMCH_ALVDS

12

C287

+V1.5S_GMCH_DLVDS

0.01uF

12

+V2.5_GMCH_TXLVDS

12

12

C284

0.1U

+V3.3S_GMCH_GPIO

12

+

CE14

C296

0.1U

12

+

C295

0.1U

12

12

+V1.2S_GMCH_DPLLA

1.14V - 1.26V(+/- 5%)

12

S0-S1M: 0.3 A

U35E

J15

VCC0

P13

VCC1

T13

VCC2

N14

VCC3

R14

VCC4

U14

VCC5

P15

VCC6

T15

VCC7

AA15

VCC8

N16

VCC9

R16

VCC10

U16

VCC11

P17

VCC12

T17

VCC13

AA17

VCC14

AA19

VCC15

W21

VCC16

H14

VCC17

V1

VCCHL0

Y1

VCCHL1

W5

VCCHL2

U6

VCCHL3

U8

VCCHL4

W8

VCCHL5

V7

VCCHL6

V9

VCCHL7

E1

VCCDVO_0

J1

VCCDVO_1

N1

VCCDVO_2

E4

VCCDVO_3

J4

VCCDVO_4

M4

VCCDVO_5

E6

VCCDVO_6

H7

VCCDVO_7

J8

VCCDVO_8

L8

VCCDVO_9

M8

VCCDVO_10

N8

VCCDVO_11

R8

VCCDVO_12

K9

VCCDVO_13

M9

VCCDVO_14

P9

VCCDVO_15

A9

VCCADAC0

B9

VCCADAC1

B8

VSSADAC

A11

VCCALVDS

B11

VSSALVDS

G13

VCCDLVDS0

B14

VCCDLVDS1

J13

VCCDLVDS2

B15

VCCDLVDS3

F9

VCCTXLVDS0

B10

VCCTXLVDS1

D10

VCCTXLVDS2

A12

VCCTXLVDS3

MONTARA_GML

A3

VCCGPIO_0

A4

VCCGPIO_1

D29

Y2

VCCAHPLL

VCCAGPLL

POWER

Caution:

There is no vias

between Pin B11

and C106,C107

(It means C106,

C107 must be in

same layer with

MCHM)

VCCADPLLA

A6

B16

VTTLF0

VTTLF1

VTTLF2

VTTLF3

VTTLF4

VTTLF5

VTTLF6

VTTLF7

VTTLF8

VTTLF9

VTTLF10

VTTLF11

VTTLF12

VTTLF13

VTTLF14

VTTLF15

VTTLF16

VTTLF17

VTTLF18

VTTLF19

VTTLF20

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCQSM0

VCCQSM1

VCCASM0

VCCADPLLB

VCCASM1

12

C280

0.1U

1.0V - 1.1V(+/- 5%)

S0-S1M: 2.5 A(CPU,MCH,ICH)

S0-S1M: Max. 0.72A

G15

H16

H18

J19

H20

L21

N21

R21

U21

H22

M22

P22

T22

V22

Y29

K29

F29

AB29

A26

A20

A18

A22

A24

H29

M29

V29

AC1

AG1

AB3

AF3

Y4

AJ5

AA6

AB6

AF6

Y7

AA8

AB8

Y9

AF9

AJ9

AB10

AA11

AB12

AF12

AA13

AJ13

AB14

AF15

AB16

AJ17

AB18

AF18

AB20

AF21

AJ21

AB22

AF24

AJ25

AF27

AC29

AF29

AG29

AJ6

AJ8

AD1

AF1

C101

0.1U

M_PWR_VTTF0

M_PWR_VTTF1

M_PWR_VTTF2

M_PWR_VTTF3

M_PWR_VTTF4

CE12

150U

C126

0.1U

C121

0.1U

12

C315

0.1U

+V1.2S _GMCH_ASM

12

C319

0.1U

12

+

CE8

150U

12

12

C106

C88

0.1U

0.1U

C264 0.1uF1 2

C259 0.1uF

1 2

C265 0.1uF1 2

C274 0.1uF1 2

C279 0.1uF1 2

+V2.5_GMCH_SM

12

+

CE13

150U

12

C116

0.1U

C118

0.1U

12

12

C316

C100

0.1U

0.1U

12

12

C130

C124

0.1U

0.1U

+V2.5_GMCHQSM

12

+

CE19

100U

L19

21

80 OHM/100MHZ

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.3 A

12

CE3

100U

12

80 OHM/100MHZ

+

12

12

C123

0.1U

12

C112

0.1U

12

C324

4.7U

R3341 1 2

L28

80 OHM/100MHZ

+VCCP

12

12

+

+

CE4

150U

2.375V - 2.625V(+/- 5%)

S0-S1M: Max. 2.07A

S3: Max. 25 mA

L26

21

12

12

C321

0.1U

12

12

C120

0.1U

+V2.5_GMCH_SM

L30

21

80 OHM/100MHZ

+V1.2S_GMCH_HI

21

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.4 A

+V2.5

PROJECT:

A

WB

REVISION

Monday, January 13, 2003

SHEET OF

B

9

DESCRIPTION:

C

MONTARA_GM-4(3.8W)

SCHEMATIC FILE NAME : DESIGN ENGINEER :DATE:

LIBRARY DATE :

D

E

A

B

+V2.5

C

D

E

CN13

9

10

21

22

33

343536

45

46

57

58

69

70

81

82

929394

113

114

131

132

143

144

155

156

157

167

168

179

180

191

VDD26

VDD27

VSS7

VSS8

28

383940

VDD28

VDD29

VSS5

VSS6

16

27

VDD30

VDD31

VSS3

VSS4

4

15

192

VDD32

VDD33

VSS1

VSS2

3

SPDI2CCPCCOMMANDCLOCKNC

BYTE 8 VREFCKE CS

DU/RESET#

VREF1

VREF2

VDDSPD

SA0

SA1

SA2

SCL

SDA

A1

A2

A4

A5

A0

A3

A6

A7

A8

A9

A10/AP

A11

A12

WE#

RAS#

CAS#

BA0

BA1

S0#

S1#

CKE0

CKE1

CK0

CK0#

CK1

CK1#

CK2

CK2#

DQS8

DM8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DU1

DU/A13

DU/BA2

DU2

DU3

VDDID

DUHOLD1

_DDR_DATA[63:0]6,11,12

1 1

2 2

3 3

4 4

5 5

_DDR_DQS06,11,12

_DDR_DM06,11,12

_DDR_DQS16,11,12

_DDR_DM16,11,12

_DDR_DQS26,11,12

_DDR_DM26,11,12

_DDR_DQS36,11,12

_DDR_DM36,11,12

_DDR_DQS46,11,12

_DDR_DM46,11,12

_DDR_DQS56,11,12

_DDR_DM56,11,12

_DDR_DQS66,11,12

_DDR_DM66,11,12

_DDR_DQS76,11,12

_DDR_DM76,11,12

_DDR_DQS0

_DDR_DM0

_DDR_DATA0

_DDR_DATA1

_DDR_DATA2

_DDR_DATA3

_DDR_DATA4

_DDR_DATA5

_DDR_DATA6

_DDR_DATA7

_DDR_DQS1

_DDR_DM1

_DDR_DATA8

_DDR_DATA9

_DDR_DATA10

_DDR_DATA11

_DDR_DATA12

_DDR_DATA13

_DDR_DATA14

_DDR_DATA15

_DDR_DQS2

_DDR_DM2

_DDR_DATA16

_DDR_DATA17

_DDR_DATA18

_DDR_DATA19

_DDR_DATA20

_DDR_DATA21

_DDR_DATA22

_DDR_DATA23

_DDR_DQS3

_DDR_DM3

_DDR_DATA24

_DDR_DATA25

_DDR_DATA26

_DDR_DATA27

_DDR_DATA28

_DDR_DATA29

_DDR_DATA30

_DDR_DATA31

_DDR_DQS4

_DDR_DM4

_DDR_DATA32

_DDR_DATA33

_DDR_DATA34

_DDR_DATA35

_DDR_DATA36

_DDR_DATA37

_DDR_DATA38

_DDR_DATA39

_DDR_DQS5

_DDR_DM5

_DDR_DATA40

_DDR_DATA41

_DDR_DATA42

_DDR_DATA43

_DDR_DATA44

_DDR_DATA45

_DDR_DATA46

_DDR_DATA47

_DDR_DQS6

_DDR_DM6

_DDR_DATA48

_DDR_DATA49

_DDR_DATA50

_DDR_DATA51

_DDR_DATA52

_DDR_DATA53

_DDR_DATA54

_DDR_DATA55

_DDR_DQS7

_DDR_DM7

_DDR_DATA56

_DDR_DATA57

_DDR_DATA58

_DDR_DATA59

_DDR_DATA60

_DDR_DATA61

_DDR_DATA62

_DDR_DATA63

11

DQS0

12

DM0

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

25

DQS1

26

DM1

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

47

DQS2

48

DM2

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

61

DQS3

62

DM3

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

133

DQS4

134

DM4

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

147

DQS5

148

DM5

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

169

DQS6

170

DM6

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

183

DQS7

184

DM7

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

202

SIDE_NC2

201

SIDE_NC1

204

HOLD2

DDR_DIMM_200P

VDD1

VDD2

VDD3

BYTE 0BYTE 1BYTE 2BYTE 3BYTE 4BYTE 5BYTE 6BYTE 7

VSS31

VSS32

VSS33

173

174

185

186

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

POWER

DDR-DIMM

GROUND

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

104

125

126

137

138

149

150

159

161

162

VDD14

VDD15

VSS19

VSS20

103

VDD16

VDD17

VSS17

VSS18

87

888990

VDD18

VDD19

VSS15

VSS16

75

76

VDD20

VDD21

VSS13

VSS14

63

64

VDD22

VDD23

VSS11

VSS12

51

52

VDD24

VDD25

VSS9

VSS10

DDR_VREF

1

2

197

194

196

198

195

193

111

110

108

107

112

109

106

105

102

101

115

100

99

119

118

120

117

116

121

122

96

95

37

160

158

91

77

78

71

73

79

83

72

74

80

84

85

86

97

98

123

124

199

200203

12

C147

0.1uF

+V3.3S

12

C143

0.1uF

SCL_3S 5,11,18,31

SDA_3S 5,11,18,31

DDR_AA1

DDR_AA2

DDR_AA4

DDR_AA5

_DDR_AA0

_DDR_AA3

_DDR_AA6

_DDR_AA7

_DDR_AA8

_DDR_AA9

_DDR_AA10

_DDR_AA11

_DDR_WE#

_DDR_RAS#

_DDR_CAS#

_DDR_BS0# DDR_BS0#

_DDR_BS1#

_DDR_DQS8

_DDR_DM8

_DDR_CB0

_DDR_CB1

_DDR_CB2

_DDR_CB3

_DDR_CB4

_DDR_CB5

_DDR_CB6

_DDR_CB7

DDR_AA[2:1] 6,12

DDR_AA[5:4] 6,12

3 4

1 2

3 4

1 2

1 2

3 4

1 2

3 4

1 2

3 4

1 2

3 4

3 4

1 2

DDR_CS0# 6,12

DDR_CS1# 6,12

DDR_CKE0 6,12

DDR_CKE1 6,12

CLK_DDR0 6

CLK_DDR0# 6

CLK_DDR1 6

CLK_DDR1# 6

CLK_DDR2 6

CLK_DDR2# 6

RN80B

10Ohm

RN80A

10Ohm

RN81B

10Ohm

RN81A

10Ohm

RN17A

10Ohm

RN17B

10Ohm

RN16A

10Ohm

RN16B

10Ohm

RN69A

10Ohm

RN69B

10Ohm

RN68A

10Ohm

RN68B

10Ohm

RN15B

10Ohm

RN15A

10Ohm

_DDR_DQS8 6,11,12 _DDR_CB[7:0] 6,11,12

_DDR_DM8 6,11,12

FOR +V2.5 DECOUPLING

12

+

12

C310

CE22

0.1uF

150U

DDR_AA0

DDR_AA3

DDR_AA6

DDR_AA7

DDR_AA8

DDR_AA9

DDR_AA10

DDR_AA11

DDR_AA12_DDR_AA12

DDR_WE#

DDR_RAS#

DDR_CAS#

DDR_BS1#

12

C339

0.1uF

+V2.5

2.375V - 2.625V(+/- 5%)

S0-S3: 8.12 A

12

12

C331

C337

0.1uF

0.1uF

DDR_AA0 6,11,12

DDR_AA3 6,11,12

DDR_AA6 6,11,12

DDR_AA7 6,11,12

DDR_AA8 6,11,12

DDR_AA9 6,11,12

DDR_AA10 6,11,12

DDR_AA11 6,11,12

DDR_AA12 6,11,12

DDR_WE# 6,11,12

DDR_RAS# 6,11,12

DDR_CAS# 6,11,12

DDR_BS0# 6,11,12

DDR_BS1# 6,11,12

12

12

C311

0.1uF

C332

0.1uF

12

12

C313

C312

0.1uF

0.1uF

PROJECT:

A

WB

REVISION DESCRIPTION:

Monday, January 13, 2003

DATE:

SHEET OF

B

10

C

DDR200 SO-DIMM 0

SCHEMATIC FILE NAME : DESIGN ENGINEER :

LIBRARY DATE :

D

E

A

B

+V2.5

C

D

E

1

2

197

194

196

198

195

193

111

110

108

107

112

109

106

105

102

101

115

100

99

119

118

120

117

116

121

122

96

95

37

160

158

91

77

78

71

73

79

83

72

74

80

84

85

86

97

98