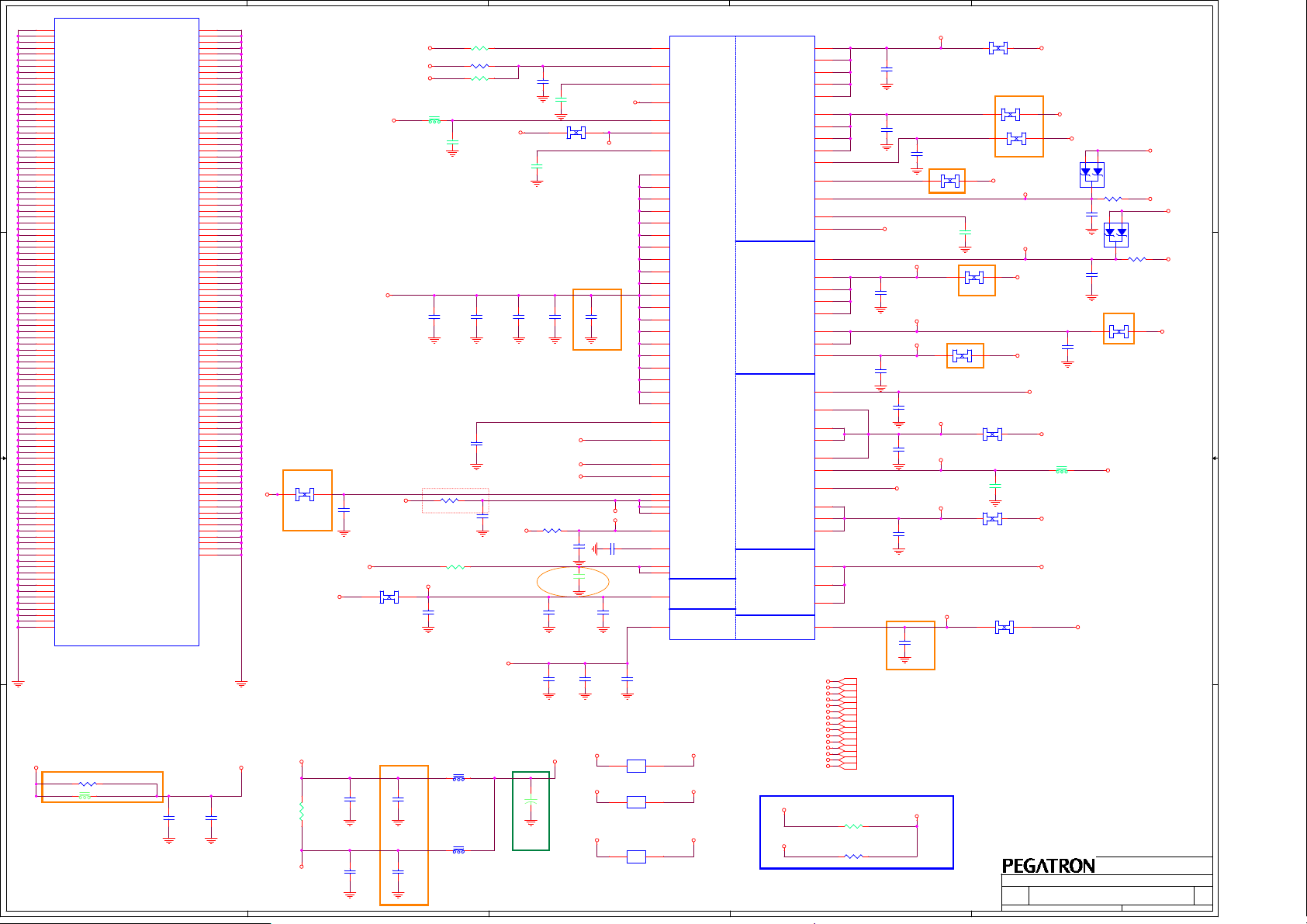

Asus B34Y Schematic

5

4

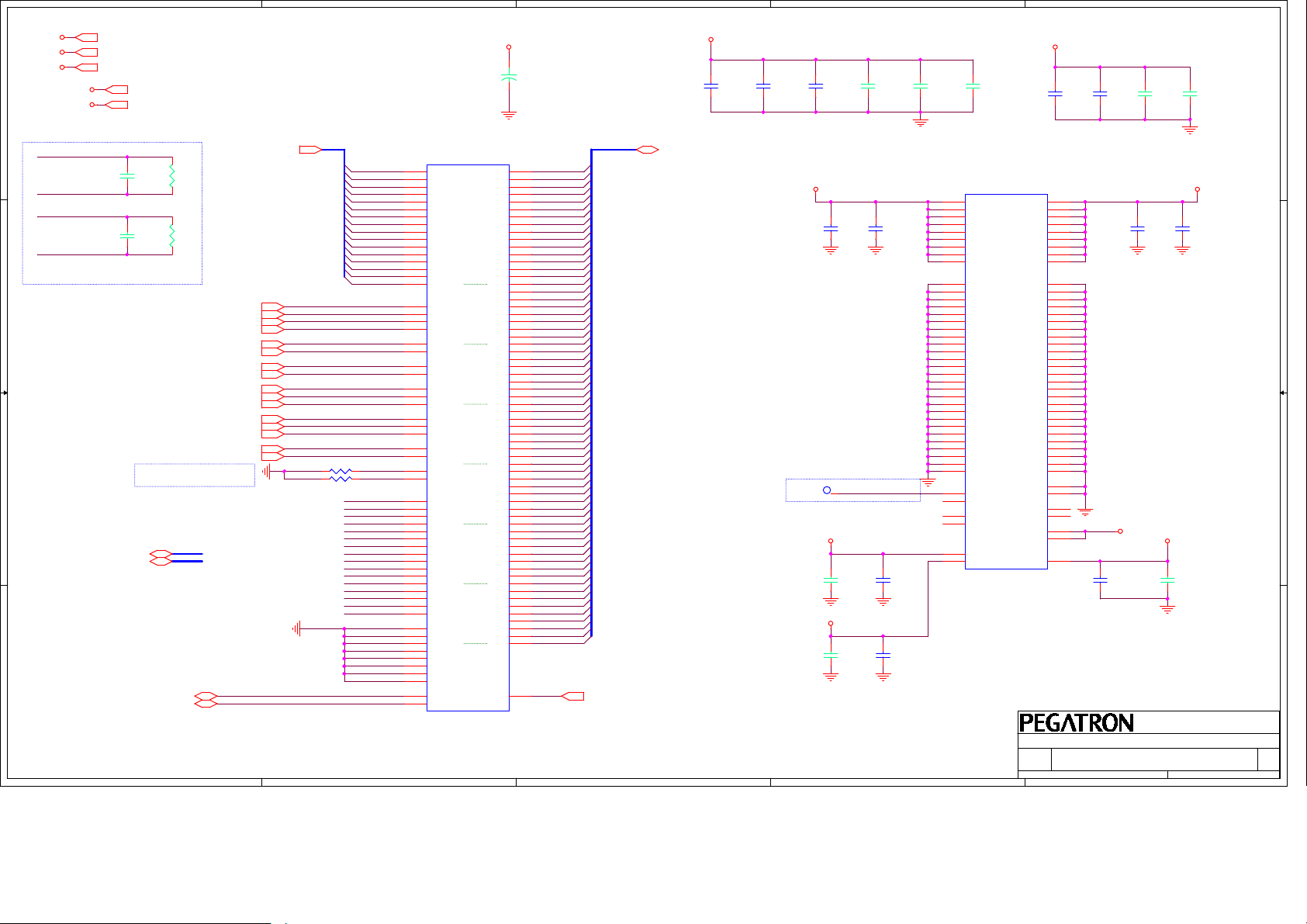

3

2

1

SYSTEM PAGE REF.

01. Block Diagr am

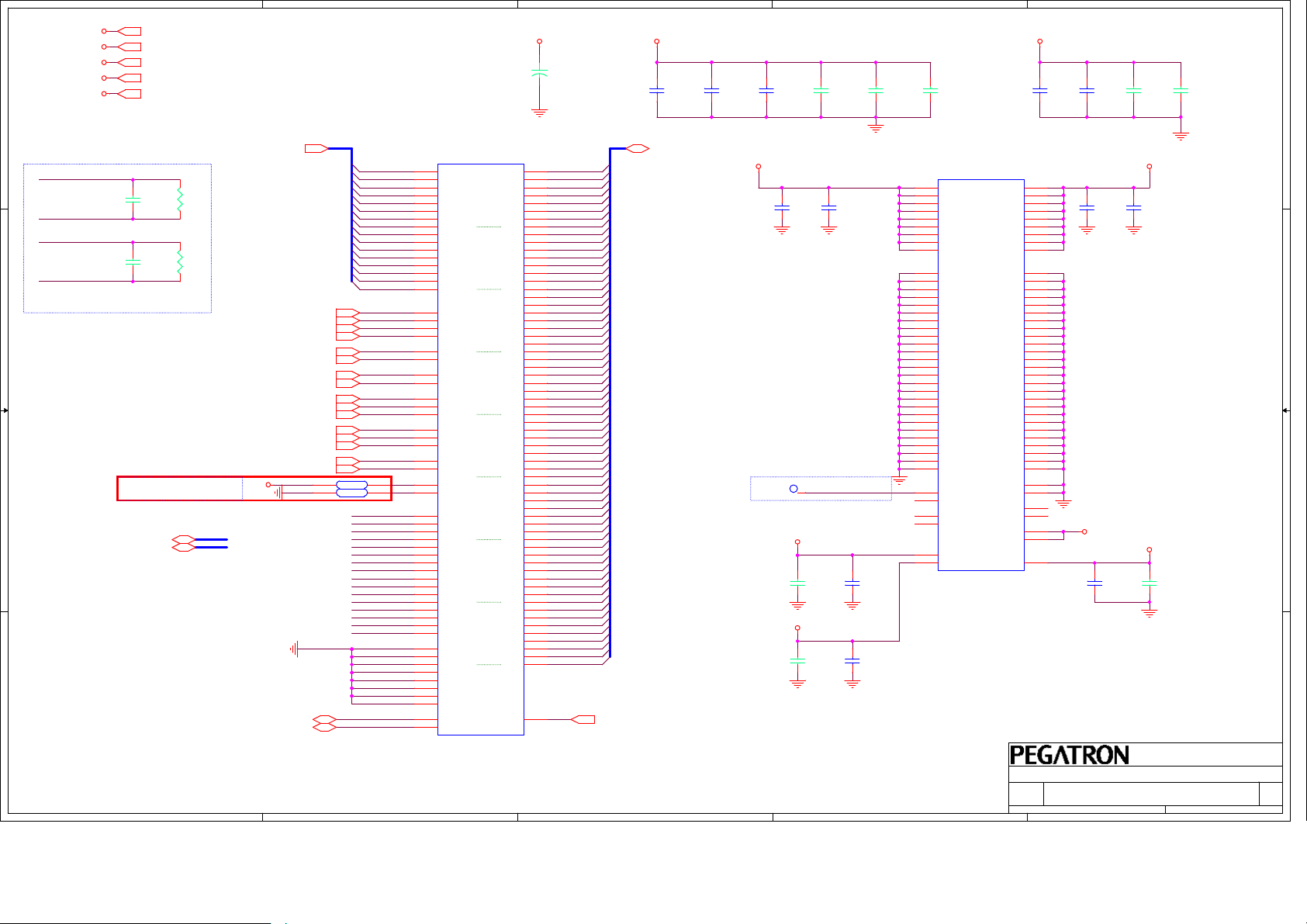

02. System Sett ing

03. CPU(1)_DMI, DP,PEG,FDI

04. CPU(2)_CLK, MSIC,JTAG

05. CPU(3)_DDR3

06. CPU(4)_PROC RSSOE POWER

07. CPU(5)_GRAP HIC POWER

08. CPU(6)_GND

D D

09. CPU(7)_RESE RVED

10. CPU_PCH_XDP

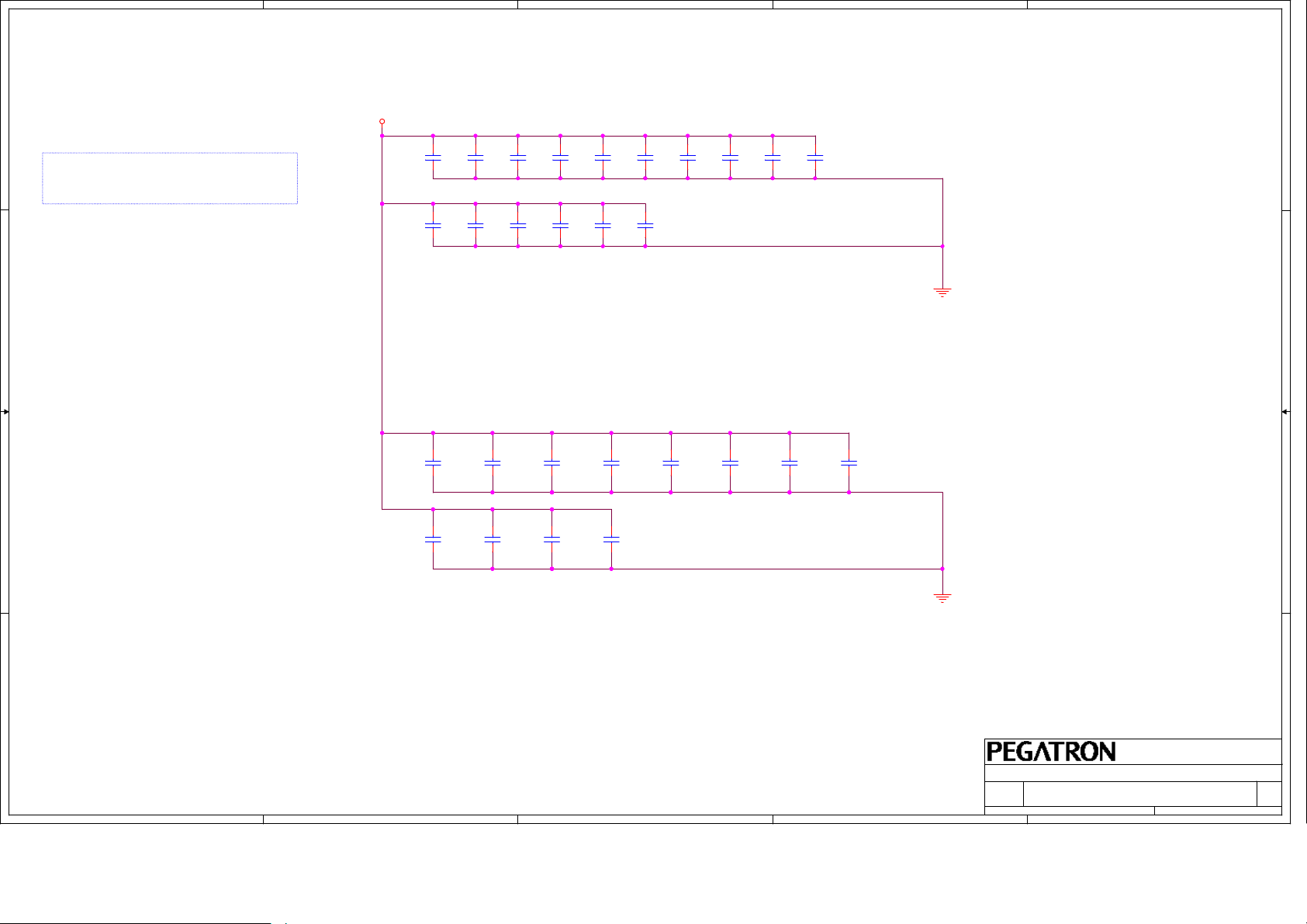

11. CPU DECOUPL ING

16. DDR3(1)_SO- DIMM0

18. DDR3(3)_CA/ DQ Voltage

20. PCH(1)_SATA ,IHDA,RTC,LPC

21. PCH(2)_PCIE ,CLK,SMB,PEG

22. PCH(3)_FDI, DMI,SYS PWR

23. PCH(4)_DP,L VDS,CRT

24. PCH(5)_PCI, NVRAM,USB

25. PCH(6)_CPU, GPIO,MISC

26. PCH(7)_POWE R,GND

27. PCH(8)_POWE R,GND

28. PCH(9)_SPI, SMB

29. CLK_ICS9LRS 3197

30. EC_NPCE795( 1)

31. EC_NPCE795( 2) KB,TP

32. RST_Reset C ircuit

33. LAN_RTL8111 E

C C

34. LAN_RJ45

38. AUD(1)_ALC2 69

40. CB(1)_RTS51 38

44. BUG_Debug

45. CRT(1)_LVDS

46. CRT(1)_CRT

48. TV(1)_HDMI

50. FAN_Fan

51. mSATA, HDD, ODD

52. USB30 Port

53. MINICARD_WL AN

55. Camera

56. LED_Indicat or

57. DSG_Dischar ge

60. DC_DC/BAT C ONN

65. ME_CONN,Ske w Hole

69 G-SENSOR*** **

80_POWER_VCORE& VGFX

81_POWER_SYSTEM

82_POWER_+VCCP

B B

83_POWER_DDR & VTT

84_POWER_+1.8VS

85_POWER_0.85VS

87_POWER_+VGA_C ORE(DSC)

88_POWER_CHARGE R(ISL88731)

90_POWER_DETECT

91_POWER_LOAD S WITCH

92_POWER_PROTEC T

93_POWER_SIGNAL

94_POWER_FLOWCH ART

95. POWER_ HIST ORY

97. SYSTEM_HIST ORY

98. Power On Se quence

99. Power On Ti ming

A A

B34Y Chief River Platform(TACOMA FALL2) Rev 1.2

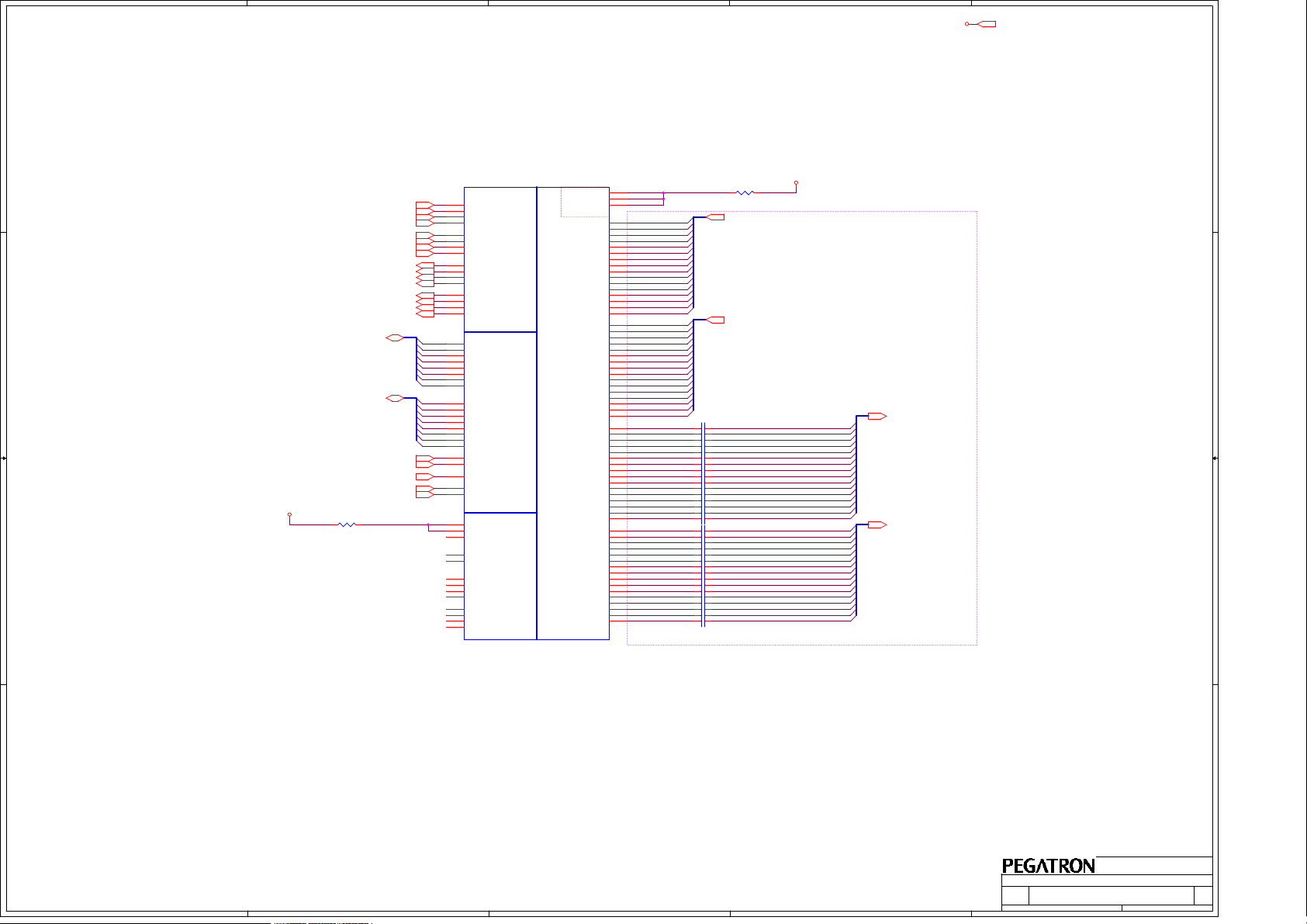

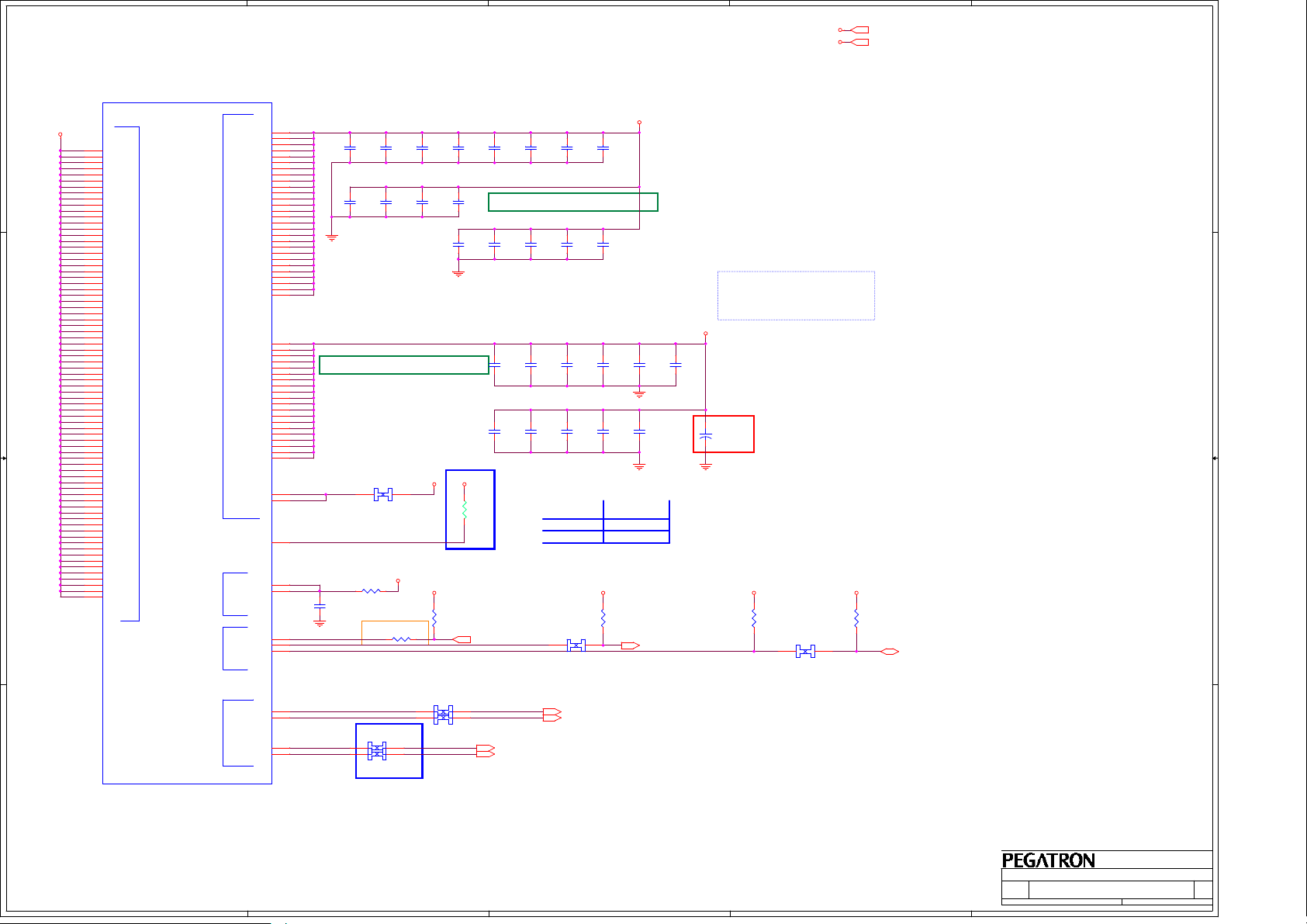

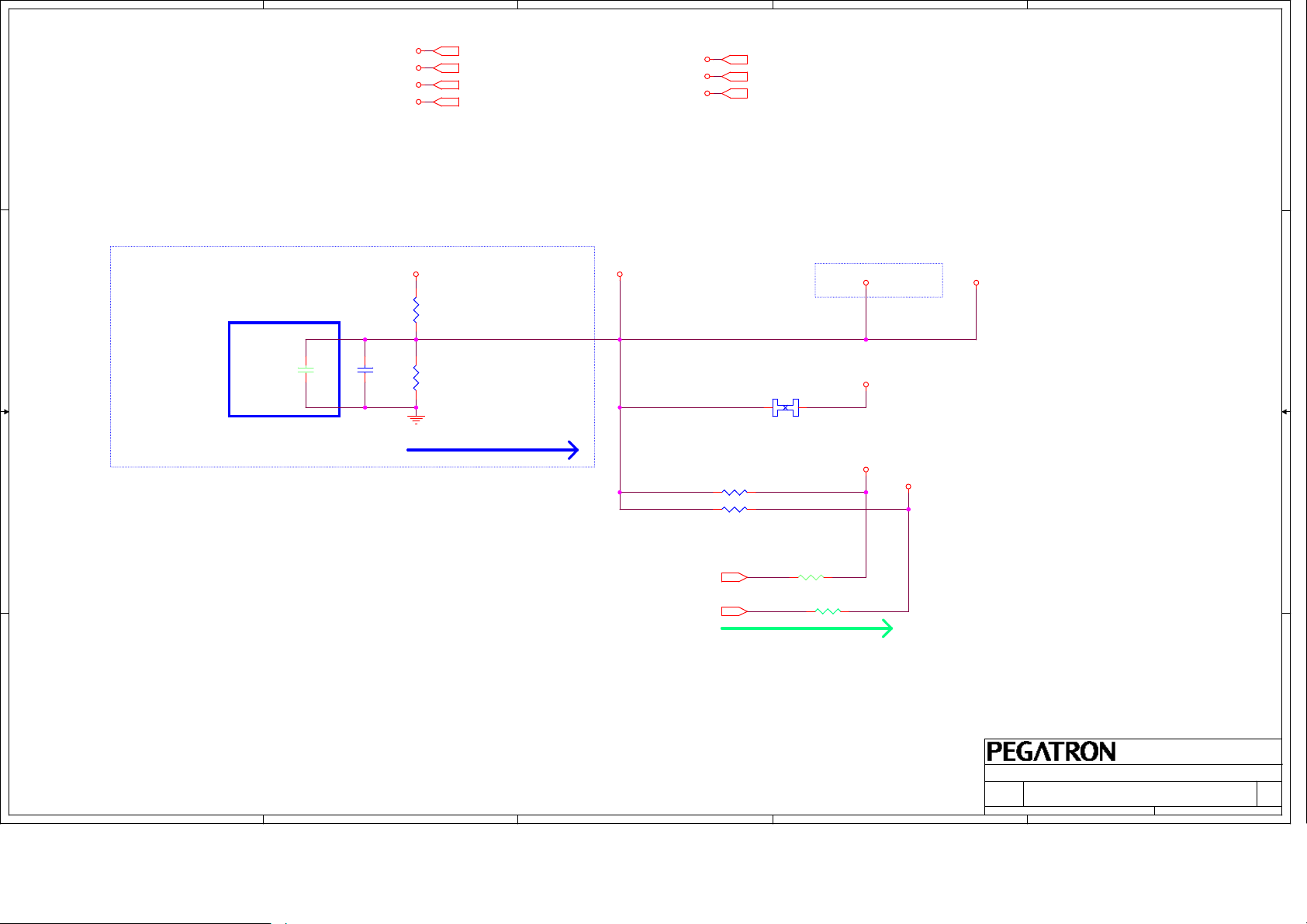

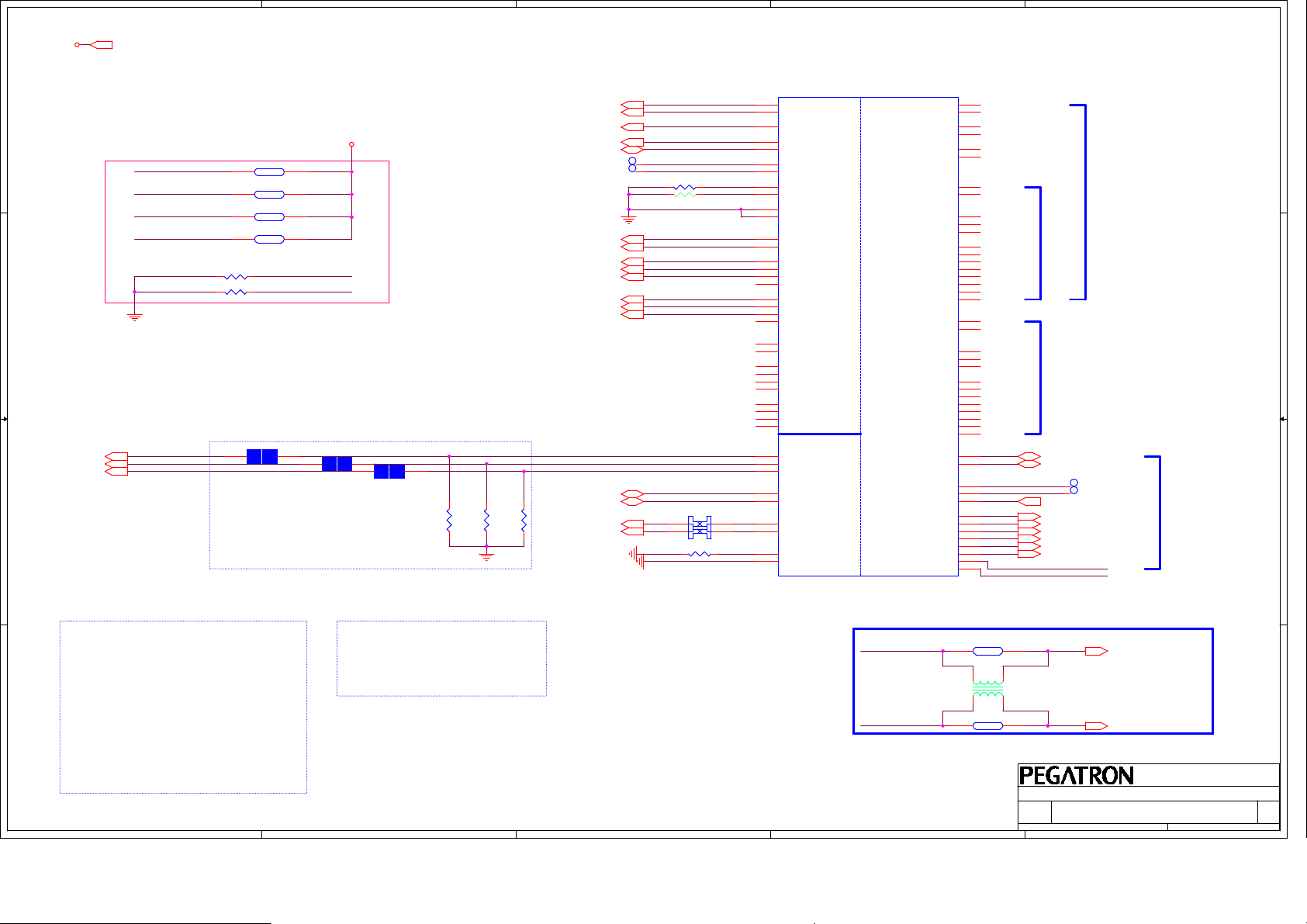

BLOCK DIAGRAM

LCD Panel

Page 45

CRT

Page 46

HDMI

Page 48

Touchpad

Keyboard

Page 31

PWM Fan

Page 50

Speaker

Page 38

Combo Audio Jack

(IO DB)

Page 66

Discharge Circuit

Reset Circuit

LVDS

RGB

HDMI

TPM(Optional)

Debug Conn.

Azalia Codec

Page 62

EC

NPCE795L

Page 30

ALC269

DC & BATT. Conn.

Page 57

Page 32

Page 44

SPI ROM

Page 38

Skew Holes

LPC

Page 28

Azalia

Page 57

Page 65

CPU

Ivy Bridge

FDI x4

DMI x4

PCH

Panther Point

SATA

SATA

mSATA

0

4

2

ODD

(Optional 2nd Batt)

Page 20~28

Page 3~11

SSD

HDD

DDR3 1333MHz

PCIEx1

USB 2.0

USB 3.0

Page 51

Page 51

Page 51

3

DDR3 SO-DIMM

5

2

3

1

9

3

8

2

MiniCard

WLAN + BT3.0

Rainbow Peak

10/100/1000 LAN

RTL8111F-CG

USB 2.0

(IO DB)

USB 2.0

(IO DB)

CardReader

RTS5138-GR

CMOS Camera

internal MIC

USB30 with charging

Charging is optional

Page 16, 18

Page 53

Page 66

Page 66

Page 40

Page 55

Page 52

Power

+VCC_CORE

+VGFX_CORE

RJ45

Page 34Page 33~34

+VGA_CORE

Load Switch

Power Protect

Page 80

System

Page 81

VTT

Page 82

DDR3

Page 83

+1.8VS

Page 84

+VCCSA

Page 85

Page 87

Charger

Page 88

Detect

Page 90

Page 91

Page 92

Title :

Title :

Title :

Block Diagram

Block Diagram

Block Diagram

Engineer:

Engineer:

B34

B34

B34

Engineer:

1

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Trunks Chen

Trunks Chen

Trunks Chen

of

1 59Wednesday, February 01, 2 012

of

1 59Wednesday, February 01, 2 012

of

1 59Wednesday, February 01, 2 012

Rev

Rev

Rev

1.0

1.0

1.0

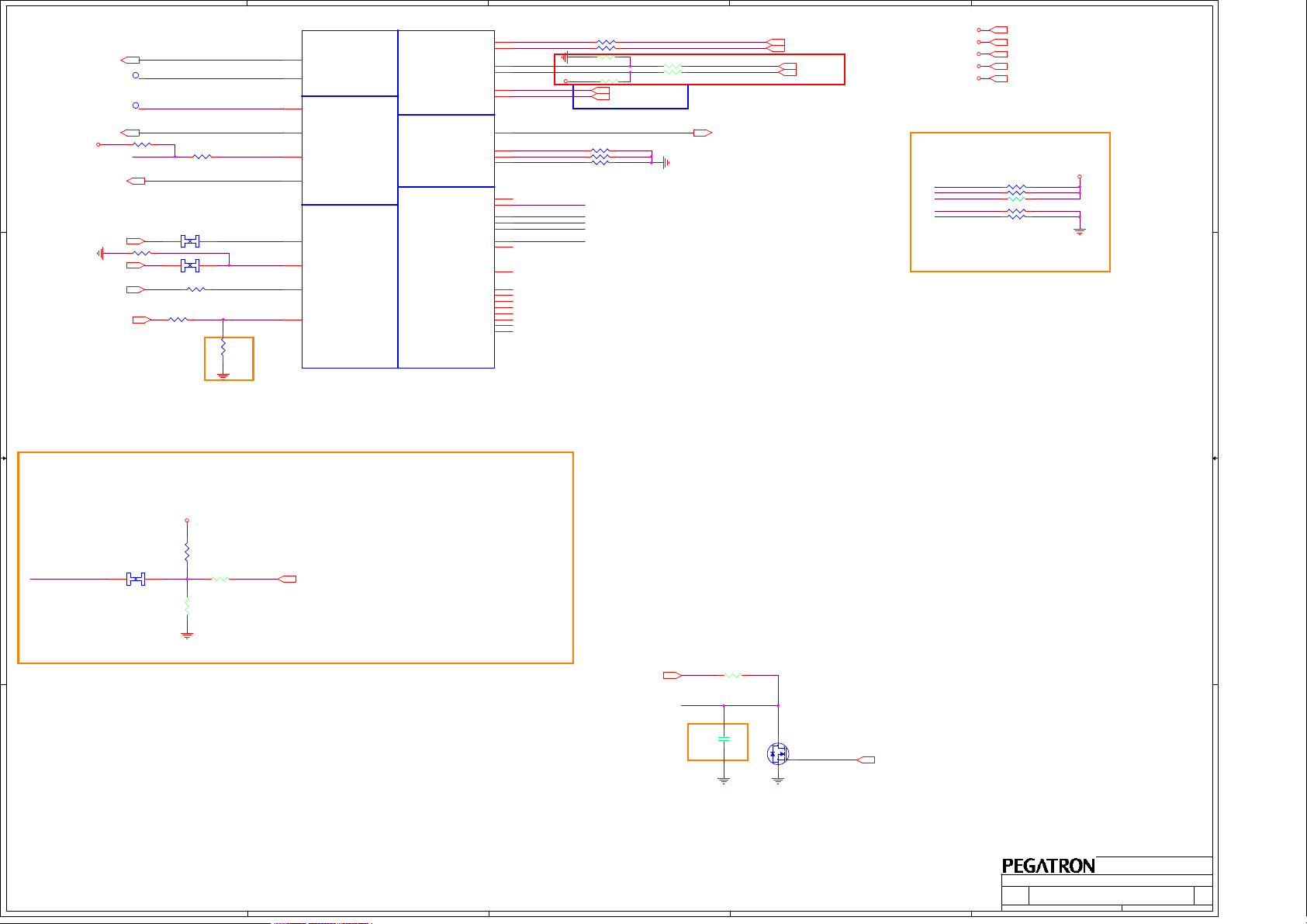

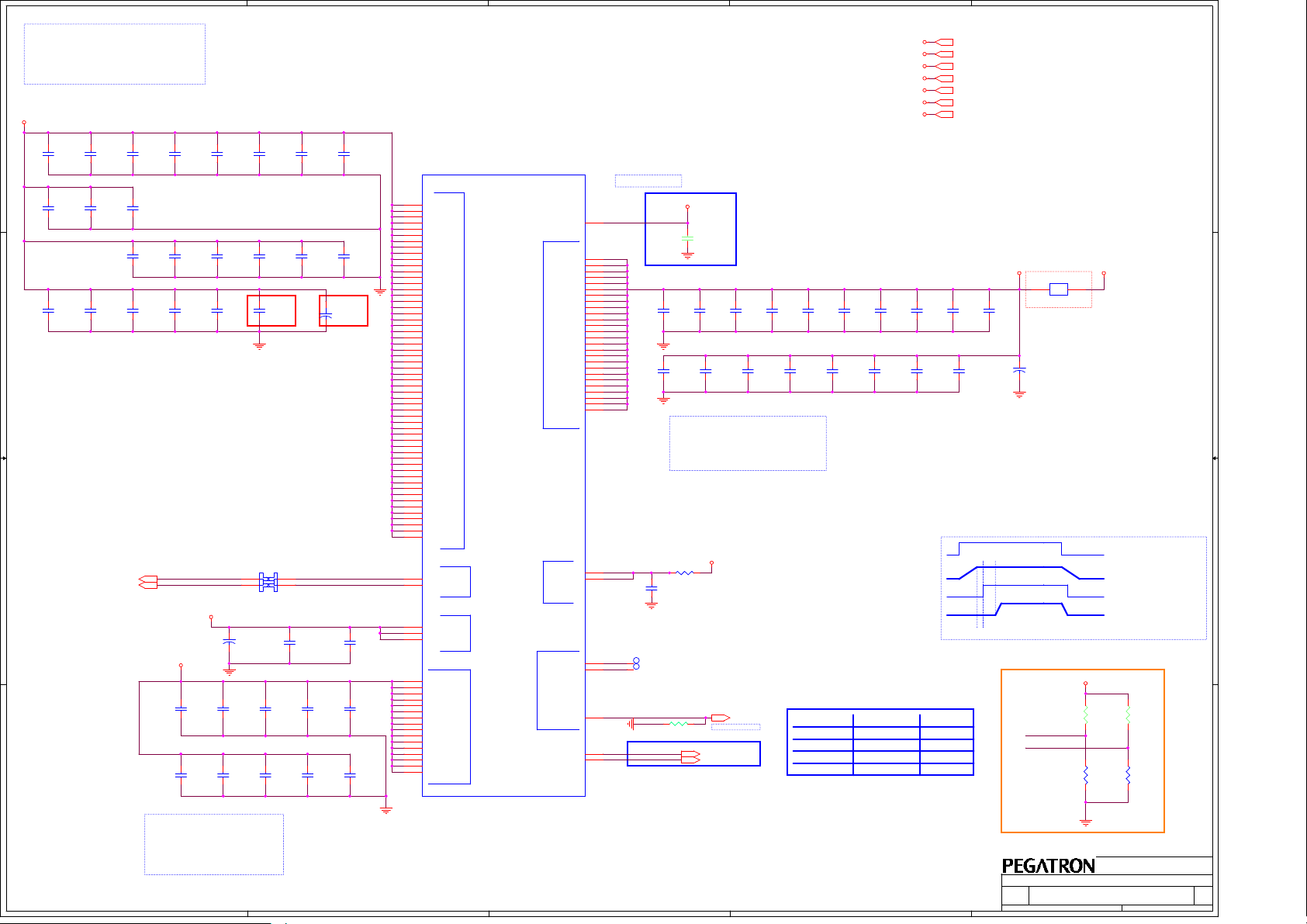

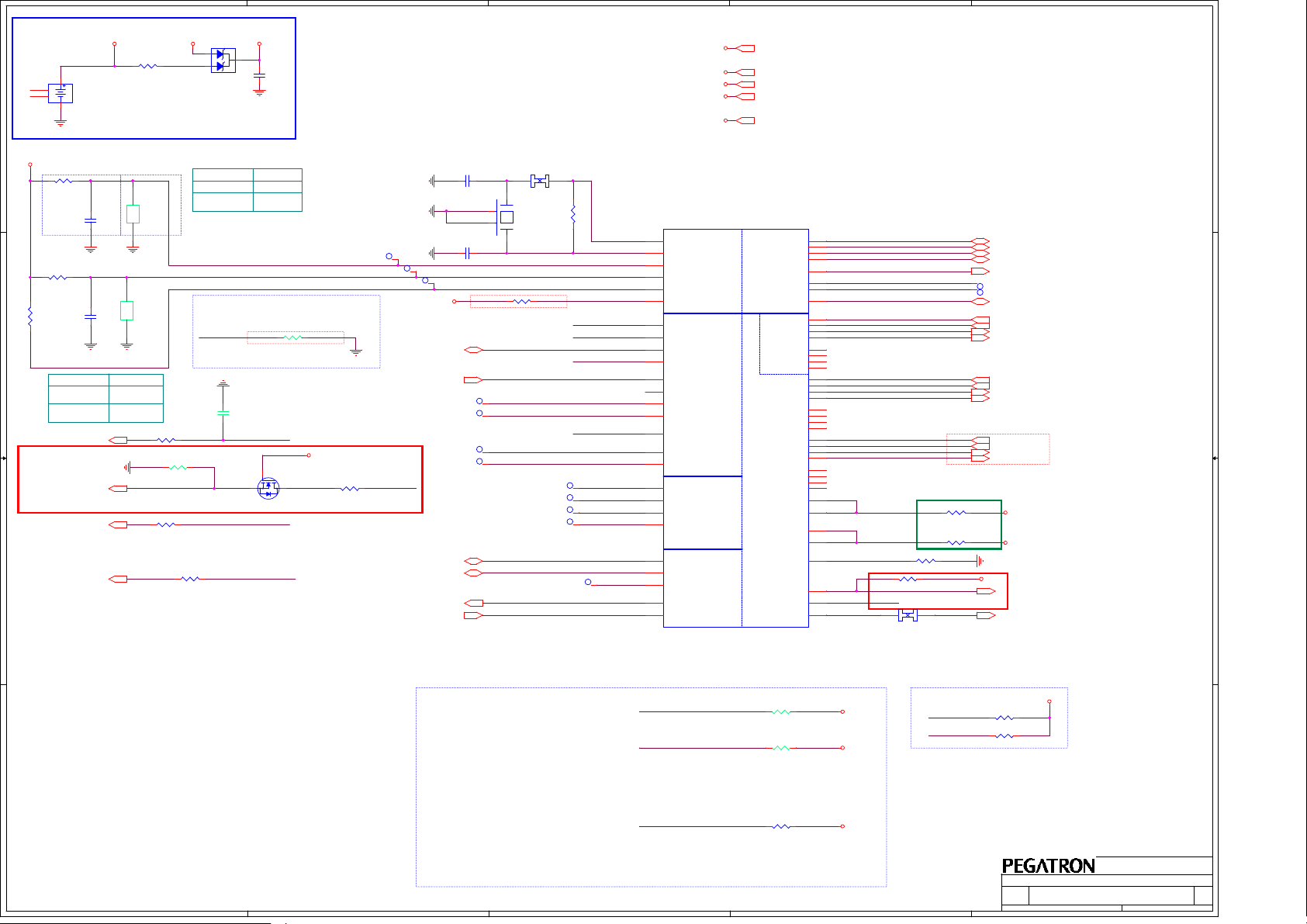

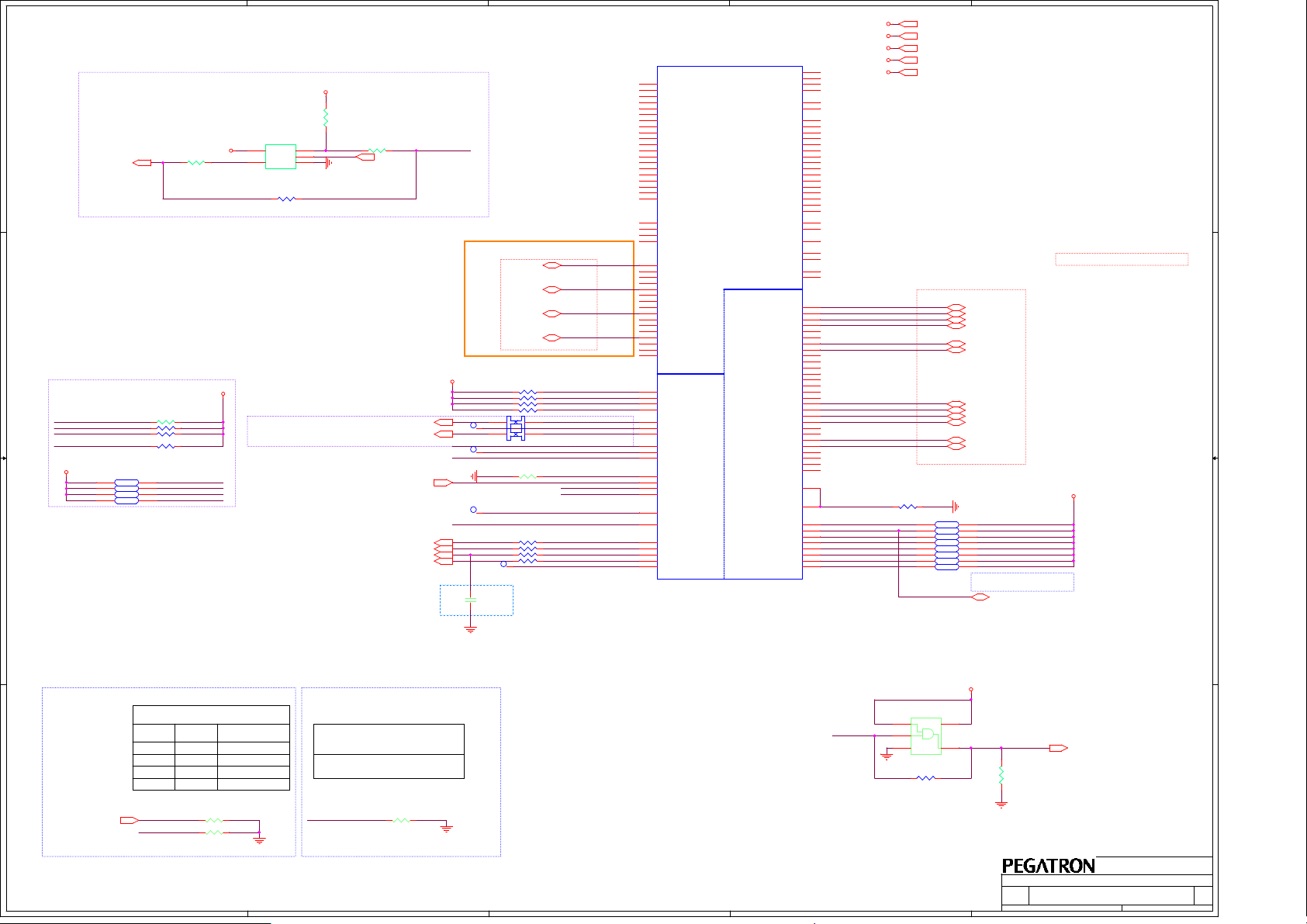

PCH_CPT

GPIO

D D

C C

B B

A A

5

PCH_CPT

GPIO

GPIO 00

GPIO 01

GPIO [2:5]

GPIO 06

GPIO 07

GPIO 08

GPIO 09

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22

GPIO 23

GPIO 24

GPIO 25

GPIO 26

GPIO 27

GPIO 28

GPIO 29

GPIO 30

GPIO 31

GPIO 32

GPIO 33

GPIO 34

GPIO 35

GPIO 36

GPIO 37

GPIO 38

GPIO 39

GPIO 40

GPIO 41

GPIO 42

GPIO 43

GPIO 44

GPIO 45

GPIO 46

GPIO 47

GPIO 48

GPIO 49

GPIO 50

GPIO 51

GPIO 52

GPIO 53

GPIO 54

GPIO 55

GPIO 56

GPIO 57

GPIO 58

GPIO 59

GPIO 60

GPIO 61

GPIO 62

GPIO 63

GPIO 64

GPIO 65

GPIO 66

GPIO 67

GPIO 72

GPIO 73

GPIO 74

GPIO 75

5

Signal NameUse As Power

4

Internal &

External

Pull-up/down

4

EC

NPCE795L

3

EC GPIO

GPA0

GPA1

GPA2

GPA3

GPA4

GPA5

GPA6

GPA7

GPB0

GPB1

GPB2

GPB3

GPB4

GPB5

GPB6

GPB7

GPC0

GPC1

GPC2

GPC3

GPC4

GPC5

GPC6

GPC7

GPD0

GPD1

GPD2

GPD3

GPD4

GPD5

GPD6

GPD7

GPE0

GPE1

GPE2

GPE3

GPE4

GPE5

GPE6

GPE7

GPF0

GPF1

GPF2

GPF3

GPF4

GPF5

GPF6

GPF7

GPG0

GPG1

GPG2

GPG6

GPH0

GPH1

GPH2

GPH3

GPH4

GPH5

GPH6

GPI0

GPI1

GPI2

GPI3

GPI4

GPI5

GPI6

GPI7

GPJ0

GPJ1

GPJ2

GPJ3

GPJ4

GPJ5

3

Use As Signal Name

2

1

SM_BUS ADDRESS :

SM-Bus Device

SO-DIMM 0

SO-DIMM 1

N/A

PCIE 1

PCIE 2

Minicard WLAN

PCIE 3

USB3.0

PCIE 4

N/A

PCIE 5

PCIE 6

GLAN

N/A

PCIE 7

N/A

PCIE 8

SATA0

SATA HDD

SATA1

N/A

SATA2

SATA ODD

SATA3

N/A

N/ASATA4

SATA5

N/A

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

2

Date: Sheet

SM-Bus Address

1010000x ( A0h )

1010001x ( A4h )

USB 0

USB Port (1)

USB 1

USB Port (2)

USB 3.0 Port (3)N/A

USB 2

USB Port (4)

USB 3

N/A

USB 4

N/A

USB 5

USB 6

N/A

N/A

USB 7

CMOS Camera

USB 8

WLAN

USB 9

Card Reader

USB 10

N/A

USB 11

N/A

USB 12

N/A

USB 13

B34

B34

B34

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

System Setting

System Setting

System Setting

Trunks Chen

Trunks Chen

Trunks Chen

of

of

of

2 59Wednesday, February 01, 2012

2 59Wednesday, February 01, 2012

2 59Wednesday, February 01, 2012

Rev

Rev

Rev

1.0

1.0

1.0

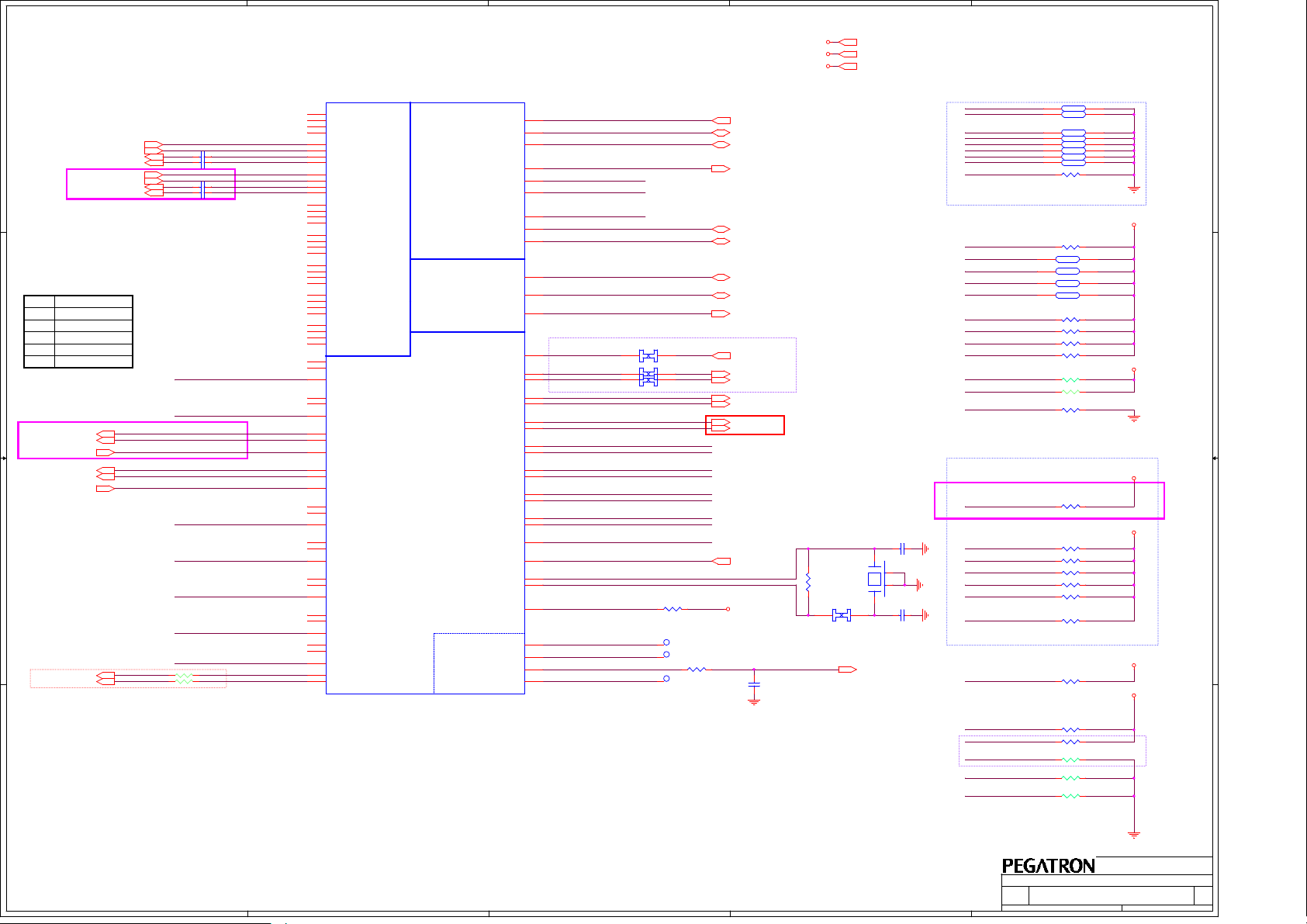

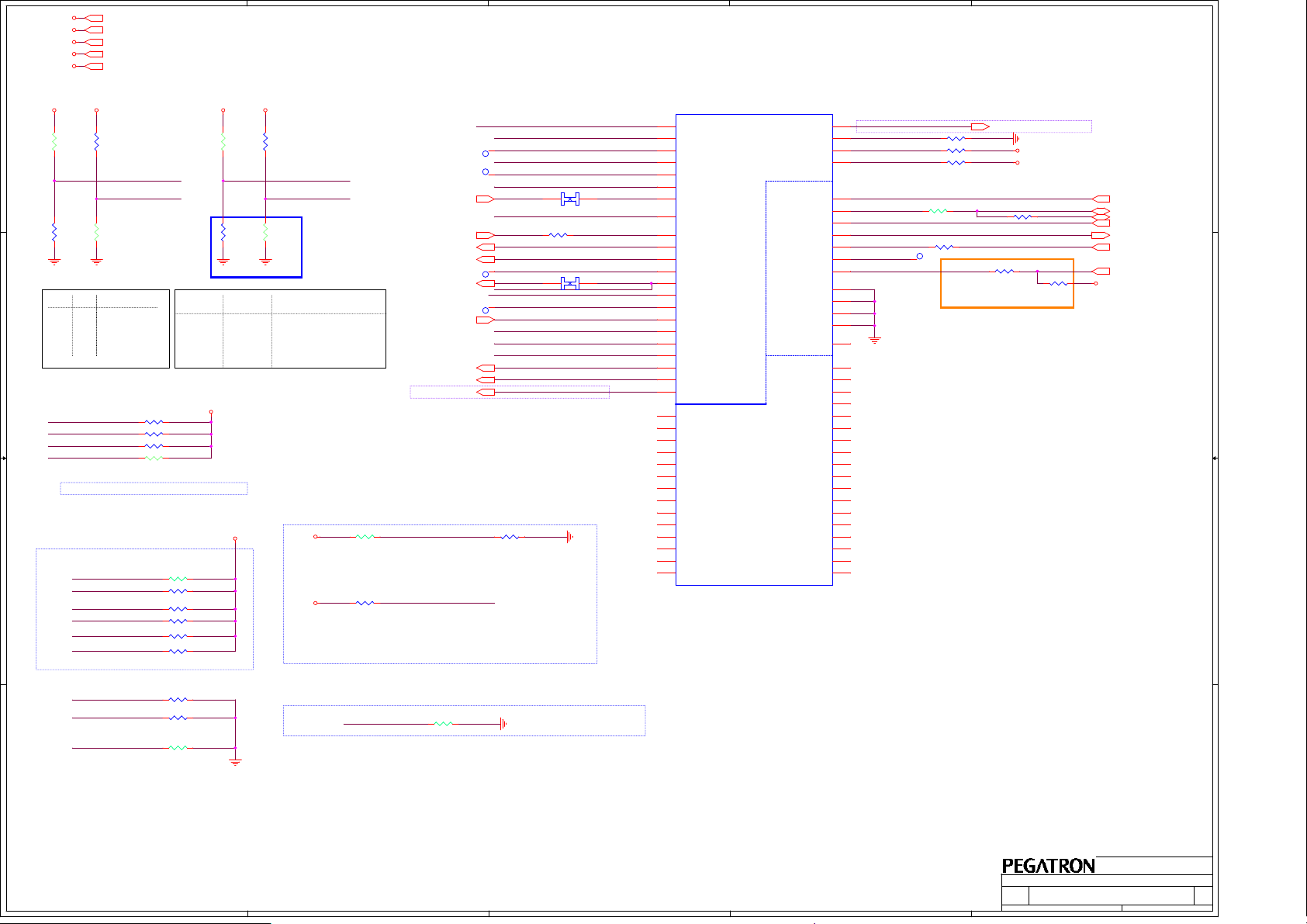

5

D D

4

3

2

+VCCP

+VCCP 4,6,7,26,27,30,32,82

1

U0301A

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

AA11

AC12

AA10

AG11

AE11

AE10

P10

P11

W11

W1

AA6

W6

AC9

W10

W3

AA7

W7

AA3

AC8

U11

AG8

AF3

AD2

AG4

AF4

AC3

AC4

AE7

AC1

AA4

AE6

M2

P6

P1

N3

P7

P3

K1

M8

N4

R2

K3

M7

P4

T3

U7

V4

Y2

U6

T4

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI0_TX#[0]

FDI0_TX#[1]

FDI0_TX#[2]

FDI0_TX#[3]

FDI1_TX#[0]

FDI1_TX#[1]

FDI1_TX#[2]

FDI1_TX#[3]

FDI0_TX[0]

FDI0_TX[1]

FDI0_TX[2]

FDI0_TX[3]

FDI1_TX[0]

FDI1_TX[1]

FDI1_TX[2]

FDI1_TX[3]

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

eDP_COMPIO

eDP_ICOMPO

eDP_HPD

eDP_AUX#

eDP_AUX

eDP_TX#[0]

eDP_TX#[1]

eDP_TX#[2]

eDP_TX#[3]

eDP_TX[0]

eDP_TX[1]

eDP_TX[2]

eDP_TX[3]

ES1

01V010000003

DMI Intel(R) FDI DP

PCI EXPRESS -- GRAPHICS

DMI_TXN022

DMI_TXN122

DMI_TXN222

DMI_TXN322

DMI_TXP022

DMI_TXP122

DMI_TXP222

DMI_TXP322

DMI_RXN022

DMI_RXN122

DMI_RXN222

DMI_RXN322

DMI_RXP022

DMI_RXP122

DMI_RXP222

DMI_RXP322

C C

VCCIO pull high 24.9 ohm

+VCCP

B B

FDI_TXN[7:0]22

FDI_TXP[7:0]22

FDI_FSYNC022

FDI_FSYNC122

FDI_INT22

FDI_LSYNC022

FDI_LSYNC122

12

DP_COMP

R030224.9Ohm 1%

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_COMP

PCIENB_RXN15

PCIENB_RXN14

PCIENB_RXN13

PCIENB_RXN12

PCIENB_RXN11

PCIENB_RXN10

PCIENB_RXN9

PCIENB_RXN8

PCIENB_RXN7

PCIENB_RXN6

PCIENB_RXN5

PCIENB_RXN4

PCIENB_RXN3

PCIENB_RXN2

PCIENB_RXN1

PCIENB_RXN0

PCIENB_RXP15

PCIENB_RXP14

PCIENB_RXP13

PCIENB_RXP12

PCIENB_RXP11

PCIENB_RXP10

PCIENB_RXP9

PCIENB_RXP8

PCIENB_RXP7

PCIENB_RXP6

PCIENB_RXP5

PCIENB_RXP4

PCIENB_RXP3

PCIENB_RXP2

PCIENB_RXP1

PCIENB_RXP0

PCIENB_TXN0

CX0301 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXN1

CX0302 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXN2

CX0303 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXN3

CX0304 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXN4

CX0305 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXN5

CX0306 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXN6

CX0307 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXN7

CX0308 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXN8

CX0309 0.22UF/10V /DIS

PCIENB_TXN9

CX0310 0.22UF/10V /DIS

PCIENB_TXN10

CX0311 0.22UF/10V /DIS

PCIENB_TXN11

CX0312 0.22UF/10V /DIS

PCIENB_TXN12

CX0313 0.22UF/10V /DIS

PCIENB_TXN13

CX0314 0.22UF/10V /DIS

PCIENB_TXN14

CX0315 0.22UF/10V /DIS

PCIENB_TXN15

CX0316 0.22UF/10V /DIS

PCIENB_TXP0

CX0317 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXP1

CX0318 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXP2

CX0319 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXP3

CX0320 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXP4

CX0321 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXP5

CX0322 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXP6

CX0323 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXP7

CX0324 0.22UF/10V /DIS_non-N13M-GS

PCIENB_TXP8

CX0325 0.22UF/10V /DIS

PCIENB_TXP9

CX0326 0.22UF/10V /DIS

PCIENB_TXP10

CX0327 0.22UF/10V /DIS

PCIENB_TXP11

CX0328 0.22UF/10V /DIS

PCIENB_TXP12

CX0329 0.22UF/10V /DIS

PCIENB_TXP13

CX0330 0.22UF/10V /DIS

PCIENB_TXP14

CX0331 0.22UF/10V /DIS

PCIENB_TXP15

CX0332 0.22UF/10V /DIS

R0301 24.9Ohm1%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PCIENB_RXN[15:0] 70

PCIENB_RXP[15:0] 70

If Support PCIE Gen3, change AC Cap to 0.22uF

+VCCP

PEG Compensation(Keep if PEG no used)

Enable PCIE Lane Reversal

Need to PD CFG[2]

PCIEG_RXN15

PCIEG_RXN14

PCIEG_RXN13

PCIEG_RXN12

PCIEG_RXN11

PCIEG_RXN10

PCIEG_RXN9

PCIEG_RXN8

PCIEG_RXN7

PCIEG_RXN6

PCIEG_RXN5

PCIEG_RXN4

PCIEG_RXN3

PCIEG_RXN2

PCIEG_RXN1

PCIEG_RXN0

PCIEG_RXP15

PCIEG_RXP14

PCIEG_RXP13

PCIEG_RXP12

PCIEG_RXP11

PCIEG_RXP10

PCIEG_RXP9

PCIEG_RXP8

PCIEG_RXP7

PCIEG_RXP6

PCIEG_RXP5

PCIEG_RXP4

PCIEG_RXP3

PCIEG_RXP2

PCIEG_RXP1

PCIEG_RXP0

PCIEG_RXN[15:0] 70

PCIEG_RXP[15:0] 70

R1.1

A A

CPU(1)_DMI,DP,PEG,FDI

CPU(1)_DMI,DP,PEG,FDI

CPU(1)_DMI,DP,PEG,FDI

Title :

Title :

Title :

Trunks Chen

Trunks Chen

Engineer:

Engineer:

B34

B34

B34

Engineer:

1

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Trunks Chen

of

of

of

3 59Wednesday, February 01, 2012

3 59Wednesday, February 01, 2012

3 59Wednesday, February 01, 2012

Rev

Rev

Rev

1.0

1.0

1.0

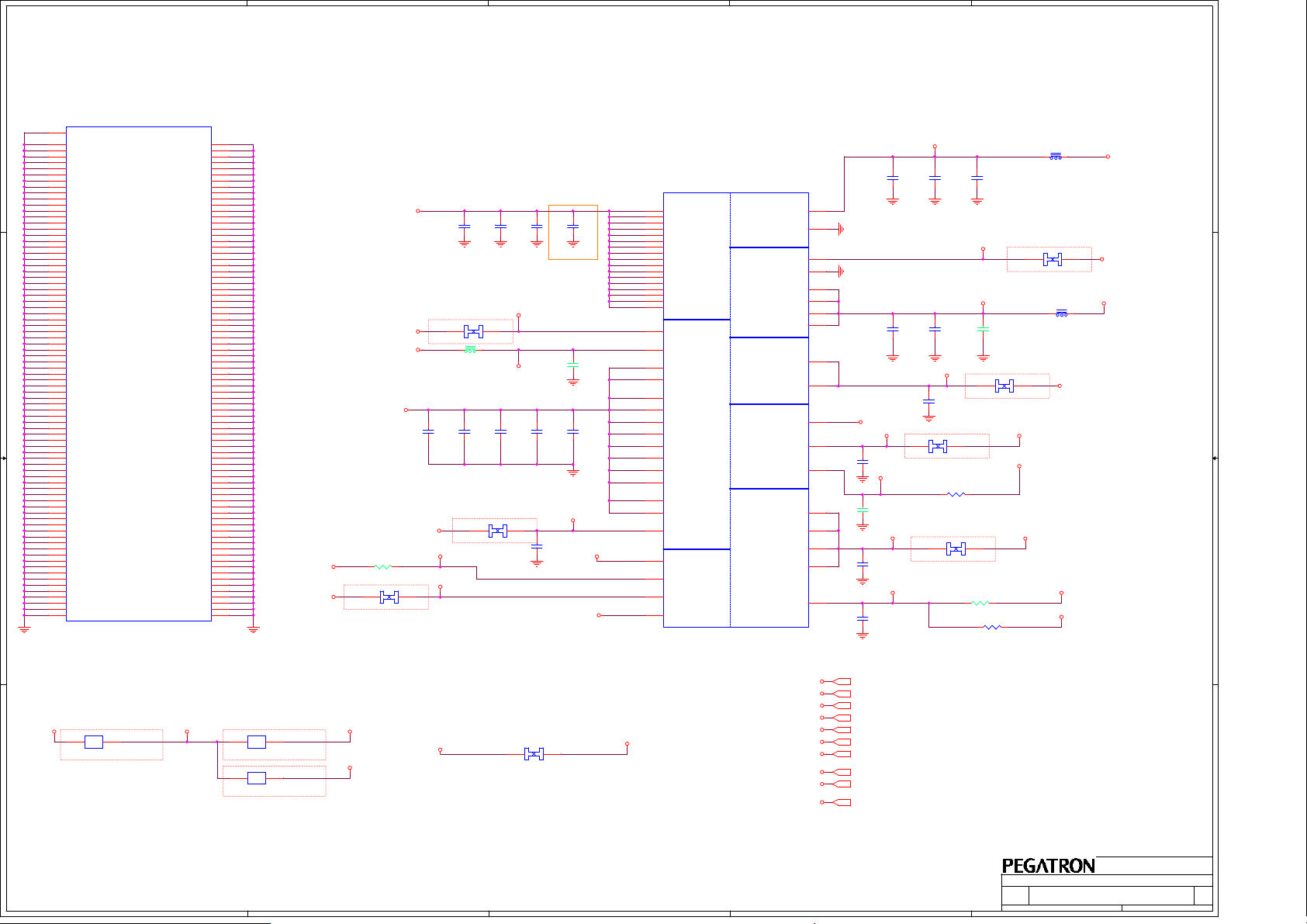

5

U0301B

H_SNB_IVB#25

D D

+VCCP

H_THRMTRIP#25,32

H_PM_SYNC22

H_CPUPWRGD25

PM_DRAM_PWRGD22

BUF_PLT_RST#24,30,32,33,53,62,70

C C

1

T0401

1

T0402

H_PECI25

12

5%

R040462Ohm

H_PROCHOT# H_PROCHOT#_D

R0406

NB_R0402_5MIL_SMALL

12

R040810KOhm

R0407

NB_R0402_5MIL_SMALL

1 2

R0416 1.5KOhm

TP_SKTOCC#_R

TP_CATERR#_R

12

5%

R040356Ohm

10V240000028

12

H_PM_SYNC_R

12

H_CPUPWRGD_R

12

VDDPWRGOOD_R

R0409130Ohm

R2.1

BUF_CPU_RST#

12

R0417

750Ohm

R1.0 0119

Sandy Bridge:R0417 = 750 ohm (10V220000093)

Ivy Bridge:R0417 = 680 ohm (10V240000041)

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

ES1

4

J3

CLK_EXP_P_R

BCLK

H2

MISC THERMAL PWR MANAGEMENT

DPLL_REF_CLK

DPLL_REF_CLK#

BCLK_ITP

CLOCKS

BCLK_ITP#

BCLK#

AG3

AG1

N59

N58

CLK_EXP_N_R

CLK_DP_P_R

CLK_DP_N_R

+VCCP

3

12

R04220Ohm

12

R04230Ohm

R04251KOhm

@

@

R04261KOhm

CLK_XDP_ITP_P 21

CLK_XDP_ITP_N 21

12

R04280Ohm /eDP

12

R04290Ohm /eDP

CLK_EXP_P 21

CLK_EXP_N 21

CLK_DP_P 21

CLK_DP_N 21

for eDP functio n

2

+1.5VS_VCCDDQ

+3VS

+3VSUS

+VCCP

+3V

+1.5VS_VCCDDQ 7

+3VS 16, 17,20,21,22,23,24,25,26,27,28,30,31,32,33,38,44,45,46,48,50,51,53,56,57,62,66,80,85,91,92

+3VSUS 22,24,27,28,30,33,53,56,81,92

+VCCP 3,6,7,26,27,30,32,82

+3V 24,40,53,55,57, 62,91

1

XDP_Debug

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TRST#

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

AT30

BF44

SM_RCOMP_0

BE43

SM_RCOMP_1

BG43

SM_RCOMP_2

N53

N55

L56

TCK

L55

TMS

J58

M60

TDI

L59

TDO

K58

G58

E55

E59

G55

G59

H60

J59

J61

R0418 140Ohm

R0419 25.5Ohm

R0420 200Ohm

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

XDP_TDI

1 2

1%

1 2

1%

1 2

1%

SM_DRAMRST#

DDR3

MISC

JTAG & BPM

CPUDRAMRST# 5

System Memory Impedance Compensation

Huron River platform Design Guide 436735 P.88 Table 37.

Huron River platform Design Guide Update 440484

SM_RCOMP_1 use 26ohm 1%

DDR3 DRAM RESET

R.10 PU/PD for JTAG signals

XDP_TMS

XDP_TDI

XDP_PREQ#

XDP_TCK

XDP_TRST#

1 2

R0438 51Ohm

1 2

R0439 51Ohm

1 2

R0440 51Ohm

@

1 2

R0441 51Ohm

1 2

R0442 51Ohm

+VCCP

PM_SYS_PWRGD is the power good for +1.5V_VCCD DQ

+1.5VS_VCCDDQ

12

R0449

200Ohm

1%

B B

PM_DRAM_PWRGD

A A

R0451

NB_R0402_5MIL_SMALL

5

1.57 Volt

12

12

R0450

1KOhm

1%

R2.1

12

@

R0452

1.1KOhm

1%

@

PM_PWROK 22,30,92

4

Different from EVEREST

If don't support S3 power reduction

1. Unmount U0404, D0404, C0413, C0420, R0450, R0452, R0453, R0460

2. Change R0449 to 200ohm from 1kohm, change R0409 to 130ohm from 0ohm - Design Guide 1.0 page 106

3. Unmount Q0501, C0501, R0506, R0504, R0507

4. Mount R0501, change r0508 to 0ohm from 1kohm

5 Unmount Q0701, R0703, R0705, Q0702

6. Mount R0702 and short JP0701

7. Unmount R2232, R2231, Q2203

C0401

12

R04610Ohm

@

3

D

1 2

@

Q0401

2N7002

1

THRO_CPU

G

S

2

2

THRO_CPU 30

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

VR_HOT#80

R1.0 0224

Intel Comments

3

H_PROCHOT#

47PF/50V

B34

B34

B34

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

CPU(2)_CLK,MISC,JTAG

CPU(2)_CLK,MISC,JTAG

CPU(2)_CLK,MISC,JTAG

Trunks Chen

Trunks Chen

Trunks Chen

of

of

of

4 59Wednesday, February 01, 2012

4 59Wednesday, February 01, 2012

4 59Wednesday, February 01, 2012

Rev

Rev

Rev

1.0

1.0

1.0

5

4

3

2

1

+DDR3

AP11

AR11

AT13

AU13

BA13

BB11

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

U0301C

AG6

SA_DQ[0]

AJ6

SA_DQ[1]

SA_DQ[2]

AL6

SA_DQ[3]

AJ10

SA_DQ[4]

AJ8

SA_DQ[5]

AL8

SA_DQ[6]

AL7

SA_DQ[7]

SA_DQ[8]

AP6

SA_DQ[9]

AU6

SA_DQ[10]

AV9

SA_DQ[11]

AR6

SA_DQ[12]

AP8

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

BC7

SA_DQ[16]

BB7

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

BA7

SA_DQ[20]

BA9

SA_DQ[21]

BB9

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CAS#

SA_RAS#

SA_WE#

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DIM0_CLK_DDR0 16

M_A_DIM0_CLK_DDR#0 16

M_A_DIM0_CKE0 16

M_A_DIM0_CLK_DDR1 16

M_A_DIM0_CLK_DDR#1 16

M_A_DIM0_CKE1 16

M_A_DIM0_CS#0 16

M_A_DIM0_CS#1 16

M_A_DIM0_ODT0 16

M_A_DIM0_ODT1 16

M_A_DQS#[7:0] 16

M_A_DQS[7:0] 16

M_A_A[15:0] 16

M_B_DQ[63:0]17

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS017

M_B_BS117

M_B_BS217

M_B_CAS#17

M_B_RAS#17

M_B_WE#17

D D

C C

B B

M_A_DQ[63:0]16

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS016

M_A_BS116

M_A_BS216

M_A_CAS#16

M_A_RAS#16

M_A_WE#16

BD13

BF12

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

U0301D

AL4

SB_DQ[0]

AL1

SB_DQ[1]

AN3

SB_DQ[2]

AR4

SB_DQ[3]

AK4

SB_DQ[4]

AK3

SB_DQ[5]

AN4

SB_DQ[6]

AR1

SB_DQ[7]

AU4

SB_DQ[8]

AT2

SB_DQ[9]

AV4

SB_DQ[10]

BA4

SB_DQ[11]

AU3

SB_DQ[12]

AR3

SB_DQ[13]

AY2

SB_DQ[14]

BA3

SB_DQ[15]

BE9

SB_DQ[16]

BD9

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

BF8

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

DDR SYSTEM MEMORY B

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DIM0_CLK_DDR0 17

M_B_DIM0_CLK_DDR#0 17

M_B_DIM0_CKE0 17

M_B_DIM0_CLK_DDR1 17

M_B_DIM0_CLK_DDR#1 17

M_B_DIM0_CKE1 17

M_B_DIM0_CS#0 17

M_B_DIM0_CS#1 17

M_B_DIM0_ODT0 17

M_B_DIM0_ODT1 17

+DDR3 7,16,17,18,57,83

M_B_DQS#[7:0] 17

M_B_DQS[7:0] 17

M_B_A[15:0] 17

ES1

01V010000003

ES1

01V010000003

R1.0 S3 circuit : DRAM_RST# to memory should b e high during S3

+DDR3

R0507

@

1KOhm

1 2

A A

DDR3_DRAMRST#16,17 CPUDRAMRST# 4

DRAMRST_CNTRL_PCH9,21

5

1 2

R0508 1KOhm

R0508 use 1k ohm

Design Guide 0.9 p107(436735)

Close to DIMM

R0504

1 2

NB_R0402_5MIL_SMALL

12

R05010Ohm

Q0501

2N7002

S

D

3

2

@

G

1

12

1%

4.99KOhm

12

C0501

@

0.1UF/10V

4

@

R0506

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

Size Project Name

Size Project Name

Size Project Name

C

C

C

B34

B34

Date: Sheet

Date: Sheet

3

2

Date: Sheet

B34

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

CPU(3)_DDR3

CPU(3)_DDR3

CPU(3)_DDR3

Trunks Chen

Trunks Chen

Trunks Chen

of

of

of

5 59Wednesday, February 01, 2012

5 59Wednesday, February 01, 2012

5 59Wednesday, February 01, 2012

Rev

Rev

Rev

1.0

1.0

1.0

5

4

3

2

1

+VCCP

+VCORE

Vcc for process or core

Voltage range: 0.3 - 1.52V

U0301F

D D

+VCORE

A26

VCC74

A29

VCC73

A31

VCC72

A34

VCC71

A35

VCC70

A38

VCC69

A39

VCC68

A42

VCC67

C26

VCC66

C27

VCC65

C32

VCC64

C34

VCC63

C37

VCC62

C39

VCC61

C42

VCC60

D27

VCC59

D32

VCC58

D34

VCC57

D37

VCC56

D39

VCC55

D42

VCC54

E26

VCC53

E28

VCC52

E32

VCC51

E34

VCC50

E37

VCC49

E38

VCC48

F25

VCC47

F26

VCC46

F28

VCC45

F32

VCC44

F34

VCC43

F37

VCC42

C C

B B

F38

VCC41

F42

VCC40

G42

VCC39

H25

VCC38

H26

VCC37

H28

VCC36

H29

VCC35

H32

VCC34

H34

VCC33

H35

VCC32

H37

VCC31

H38

VCC30

H40

VCC29

J25

VCC28

J26

VCC27

J28

VCC26

J29

VCC25

J32

VCC24

J34

VCC23

J35

VCC22

J37

VCC21

J38

VCC20

J40

VCC19

J42

VCC18

K26

VCC17

K27

VCC16

K29

VCC15

K32

VCC14

K34

VCC13

K35

VCC12

K37

VCC11

K39

VCC10

K42

VCC9

L25

VCC8

L28

VCC7

L33

VCC6

L36

VCC5

L40

VCC4

N26

VCC3

N30

VCC2

N34

VCC1

N38

VCC0

CORE SUPPLY

PEG AND DDRSENSE LINES SVID QUIET RAILS

POWER

Voltage for the memory control ler and

shared cache de fined at the

motherboard VCC IO_SENSE and

VSS_SENSE_VCCIO

AF46

VCCIO34

VCCIO28

VCCIO27

VCCIO26

VCCIO23

VCCIO22

VCCIO21

VCCIO20

VCCIO19

VCCIO18

VCCIO17

VCCIO16

VCCIO15

VCCIO14

VCCIO13

VCCIO12

VCCIO11

VCCIO10

VCCIO9

VCCIO8

VCCIO7

VCCIO6

VCCIO5

VCCIO4

VCCIO3

VCCIO2

VCCIO1

VCCIO0

VCCIO47

VCCIO46

VCCIO45

VCCIO44

VCCIO43

VCCIO42

VCCIO41

VCCIO40

VCCIO39

VCCIO38

VCCIO37

VCCIO36

VCCIO35

VCCIO33

VCCIO32

VCCIO31

VCCIO30

VCCIO29

VCCIO25

VCCIO24

VCCIO49

VCCIO48

VCCIO_SEL

VCCPQE1

VCCPQE0

VIDALERT#

VIDSCLK

VIDSOUT

AG48

AG50

AG51

AJ17

AJ21

AJ25

AJ43

AJ47

AK50

AK51

AL14

AL15

AL16

AL20

AL22

AL26

AL45

AL48

AM16

AM17

AM21

AM43

AM47

AN20

AN42

AN45

AN48

AA14

AA15

AB17

AB20

AC13

remove 1UF C0612,C0615,C0608,C0624

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

+VCCIO_CPU_F

W17

BC22

VCCP_SEL

Filitered(BGA only)

AM25

AN22

12

C0622

1UF/6.3V

A44

H_CPU_SVIDALRT#

B43

H_CPU_SVIDCLK

C44

H_CPU_SVIDDAT

12

C0628

1UF/6.3V

12

C0610

1UF/6.3V

R0601

1 2

NB_R0603_32MIL_SMALL

1 2

R0613 0Ohm

Intel Comments

R0602

12

C0631

1UF/6.3V

12

C0609

1UF/6.3V

+VCCP

5%

1 2

43Ohm

+VCCP

12

R2.1

12

C0632

1UF/6.3V

12

C0606

1UF/6.3V

vx_c0603_small

+VCCP +3VA

12

12

12

@

C0635

1UF/6.3V

C0611

1UF/6.3V

C0618

10UF/6.3V

R0615

10KOhm

1 2

vx_c0603_small

vx_c0603_small

12

C0634

C0636

1UF/6.3V

1UF/6.3V

remove 1UF C0614,C0616,C0623,C0607

vx_c0603_small

12

12

C0619

C0621

10UF/6.3V

10UF/6.3V

vx_c0603_small

12

12

C0626

C0625

1UF/6.3V

1UF/6.3V

12

C0603

10UF/6.3V

vx_c0603_small

vx_c0603_small

12

C0602

10UF/6.3V

VCCIO_SEL

12

12

12

12

H

L

C0637

1UF/6.3V

vx_c0603_small

C0620

10UF/6.3V

C0627

1UF/6.3V

C0605

10UF/6.3V

vx_c0603_small

12

12

12

12

C0613

1UF/6.3V

C0617

10UF/6.3V

C0629

1UF/6.3V

vx_c0603_small

C0604

10UF/6.3V

VCCSA

12

12

1.05V

1.00V

C0630

1UF/6.3V

C0601

10UF/6.3V

Chief River

Decoupling guide from Intel (EE)

+VCCP 1uF * 18pcs

10uF * 10pcs

220uF *1pcs

+VCCP

12

C0633

1UF/6.3V

12

+

CE0603

330UF/2.5V

change size 352 8 2mm (08/12)

Cheif River

+VCCP +VCCP +VCCP +VCCP

Close to CPU

12

R0603

75Ohm

1%

VR_SVID_ALERT# 80

Close to VR

SP0601

1 2

1 2

R0605

54.9Ohm

1%

Close to CPU Close to VR

VR_SVID_CLK 80

R0607

130Ohm

1%

1 2

SP0602

1 2

+VCCP 3,4,7,26,27,30,32,82

+VCORE 9,11,80

R0608

130Ohm

1%

1 2

VR_SVID_DATA 80

SP0603

F43

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

ES1

A A

01V010000003

5

VCC_SENSE_R VCCSENSE

G43

VSS_SENSE_R

SP0605

AN16

AN17

VCCP_SENSE_R

VSSP_SENSE_R

NB_R0402_20MIL_SMALL

1 2

1 2

SP0606

NB_R0402_20MIL_SMALL

4

NB_R0402_20MIL_SMALL

1 2

1 2

SP0604

NB_R0402_20MIL_SMALL

+VCCP_SENSE

+VSSP_SENSE

VSSSENSE

+VCCP_SENSE 82

+VSSP_SENSE 82

VCCSENSE 80

VSSSENSE 80

Title :

Title :

Title :

CPU(4)_PWR

CPU(4)_PWR

CPU(4)_PWR

Trunks Chen

Trunks Chen

Engineer:

Engineer:

B34

B34

B34

Engineer:

1

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

3

2

Date: Sheet

Trunks Chen

6 59Wednesday, February 01, 2012

6 59Wednesday, February 01, 2012

6 59Wednesday, February 01, 2012

of

of

of

Rev

Rev

Rev

1.0

1.0

1.0

5

4

3

2

1

Decoupling guide from Intel PDDG R0.8

+VGFX_CORE

1uF * 11pcs

10uF * 6pcs

22uF * 6pcs

+VGFX_CORE

D D

12

12

12

12

C C

B B

A A

C0727

C0725

1UF/6.3V

1UF/6.3V

12

C0719

C0717

1UF/6.3V

1UF/6.3V

vx_c0603_small

12

C0739

C0738

22UF/6.3V

22UF/6.3V

VCCGT_SENSE80

VSSGT_SENSE80

PLL supply volt age

(DC + AC specif ication)

12

12

12

12

12

C0731

1UF/6.3V

C0722

1UF/6.3V

C0790

10UF/6.3V

C0740

22UF/6.3V

12

vx_c0603_small

12

C0726

1UF/6.3V

C0791

10UF/6.3V

C0741

22UF/6.3V

change size fro m 0805 power request

+VCCSA

vx_c0603_small

5

12

12

Decoupling guide for A14 (EE)

+VCCSA

1uF * 5pcs

10uF * 5pcs

Graphics core v oltage

Voltage range: 0 - 1.52V

12

vx_c0603_small

VCCGT_SENSE

VSSGT_SENSE

+1.8VS

C0783

10UF/6.3V

vx_c0603_small

C0735

1UF/6.3V

12

12

12

C0729

C0732

1UF/6.3V

1UF/6.3V

12

C0788

C0789

10UF/6.3V

10UF/6.3V

vx_c0603_small

12

C0742

22UF/6.3V

SP0706

NB_R0402_20MIL_SMALL

SP0707

NB_R0402_20MIL_SMALL

CE0701

330UF/2V

vx_c0603_small

12

12

C0781

10UF/6.3V

12

12

C0736

1UF/6.3V

C0743

22UF/6.3V

12

12

C0792

10UF/6.3V

C0733

1UF/6.3V

12

C0730

1UF/6.3V

vx_c0603_small

12

C0787

10UF/6.3V

VCCGT_SENSE_R

VSSGT_SENSE_R

12

C0761

1UF/6.3V

12

vx_c0603_small

12

vx_c0603_small

12

vx_c0603_small

C0777

10UF/6.3V

C0734

1UF/6.3V

+

12

C0728

1UF/6.3V

12

C0786

10UF/6.3V

CE0703

330UF/2.5V

12

12

12

MAX:1.2A

TDC: 1.2A

C0764

1UF/6.3V

MAX:6A

C0793

10UF/6.3V

C0737

1UF/6.3V

4

AA46

AB47

AB50

AB51

AB52

AB53

AB55

AB56

AB58

AB59

AC61

AD47

AD48

AD50

AD51

AD52

AD53

AD55

AD56

AD58

AD59

AE46

N45

P47

P48

P50

P51

P52

P53

P55

P56

P61

T48

T58

T59

T61

U46

V47

V48

V50

V51

V52

V53

V55

V56

V58

V59

W50

W51

W52

W53

W55

W56

W61

Y48

Y61

F45

G45

BB3

BC1

BC4

L17

L21

N16

N20

N22

P17

P20

R16

R18

R21

U15

V16

V17

V18

V21

W20

U0301G

VAXG21

VAXG20

VAXG19

VAXG18

VAXG17

VAXG16

VAXG15

VAXG14

VAXG13

VAXG12

VAXG11

VAXG10

VAXG9

VAXG8

VAXG7

VAXG6

VAXG5

VAXG4

VAXG3

VAXG2

VAXG1

VAXG0

VAXG55

VAXG54

VAXG53

VAXG52

VAXG51

VAXG50

VAXG49

VAXG48

VAXG47

VAXG46

VAXG45

VAXG44

VAXG43

VAXG42

VAXG41

VAXG40

VAXG39

VAXG38

VAXG37

VAXG36

VAXG35

VAXG34

VAXG33

VAXG32

VAXG31

VAXG30

VAXG29

VAXG28

VAXG27

VAXG26

VAXG25

VAXG24

VAXG23

VAXG22

VAXG_SENSE

VSSAXG_SENSE

VCCPLL2

VCCPLL1

VCCPLL0

VCCSA15

VCCSA14

VCCSA13

VCCSA12

VCCSA11

VCCSA10

VCCSA9

VCCSA8

VCCSA7

VCCSA6

VCCSA5

VCCSA4

VCCSA3

VCCSA2

VCCSA1

VCCSA0

ES1

01V010000003

DDR3 Reference Voltage

+V_SM_REF 10mil

+V_SM_VREF

AY43

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

+V_SM_VREF

vx_c0603_small

vx_c0603_small

SM_VREF

VDDQ25

VDDQ24

VDDQ23

VDDQ22

VDDQ21

VDDQ20

VDDQ19

VDDQ18

VDDQ17

VDDQ16

VDDQ15

VDDQ14

VDDQ13

VDDQ12

VDDQ11

VDDQ10

VDDQ9

VDDQ8

VDDQ7

VDDQ6

VDDQ5

VDDQ4

DDR3 - 1.5V RAILS

POWER

GRAPHICS

VDDQ3

VDDQ2

VDDQ1

VDDQ0

pull high in p.18

12

C0794

0.1UF/16V @

MAX:10A

12

12

C0704

1UF/6.3V

12

C0775

10UF/6.3V

Chief River

Decoupling guide from Intel (EE)

+1.5VS_VCCDDQ

1uF * 10pcs

10uF * 8pcs

330uF * 1pcs

C0709

1UF/6.3V

12

vx_c0603_small

C0774

10UF/6.3V

12

C0705

1UF/6.3V

vx_c0603_small

12

C0772

10UF/6.3V

12

C0706

1UF/6.3V

12

vx_c0603_small

12

C0769

10UF/6.3V

C0707

1UF/6.3V

vx_c0603_small

12

12

C0767

10UF/6.3V

C0708

1UF/6.3V

Filtered(BGA On ly)

+1.5VS_VCCDDQ

1 2

R0707 0Ohm

12

C0714

1UF/6.3V

SENSE

LINES

1.8V RAIL

QUIET RAILS

VSS_SENSE_VDDQ

VCCDQ1

VCCDQ0

VDDQ_SENSE

AM28

AN26

BC43

BA43

1

T0701

1

T0702

SA RAIL

VCCSA_VID[0]

VCCSA_VID[1]

U10

D48

D49

R0704 0Ohm

VCCSA_SEL0

VCCSA_SEL1

1 2

@

VCCSA_SENSE 85

Close to CPU

VCCSA_SEL0 85

VCCSA_SEL1 85

+VCCSA_SEL0 +VCCSA_SEL1

L

L

H

SENSE LINES

VCCSA_SENSE

Chief River

3

2

12

12

vx_c0603_small

+VCCP

+VCCSA

+1.8VS

+VGFX_CORE

+1.5VS

+V_SM_VREF

C0713

1UF/6.3V

vx_c0603_small

C0765

10UF/6.3V

L

H

L

+DDR3

12

12

C0710

1UF/6.3V

C0770

10UF/6.3V

VCCSA

0.9V

0.85V

0.725V

0.675VH H

+VCCP 3,4,6,26,27,30,32,82

+DDR3 5,16,17,18,57,83

+VCCSA 85

+1.8VS 25,26,80,84

+VGFX_CORE 9,80

+1.5VS 26,53,57,91

+V_SM_VREF 18,83

+1.5VS_VCCDDQ +DDR3

12

12

C0712

C0711

1UF/6.3V

12

C0768

10UF/6.3V

vx_c0603_small

>100 ns

change short pin footprint

1UF/6.3V

CE0702

330UF/2V

> 0 SUSB_EC#

R1.0 0209

Intel Comments

VCCSA_SEL0

VCCSA_SEL1

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

Processor I/O supply

voltage for DDR3

(DC + AC specification)

JP0701

2

112

ICCMAX_VDDQ 5A

3MM_OPEN_5MIL

+1.5V_VCCDDQ

+1.5V_VCCDDQ Power Good

(U0404 pin 4)

+0.75VS

+VCCP

R0708

1KOhm

@

1 2

1 2

R0701

1KOhm

1 2

1 2

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

B34

B34

B34

1

R0709

1KOhm

@

R0702

1KOhm

CPU(5)_GFX_PWR

CPU(5)_GFX_PWR

CPU(5)_GFX_PWR

Trunks Chen

Trunks Chen

Trunks Chen

of

of

of

7 59Wednesday, February 01, 2012

7 59Wednesday, February 01, 2012

7 59Wednesday, February 01, 2012

Rev

Rev

Rev

1.0

1.0

1.0

5

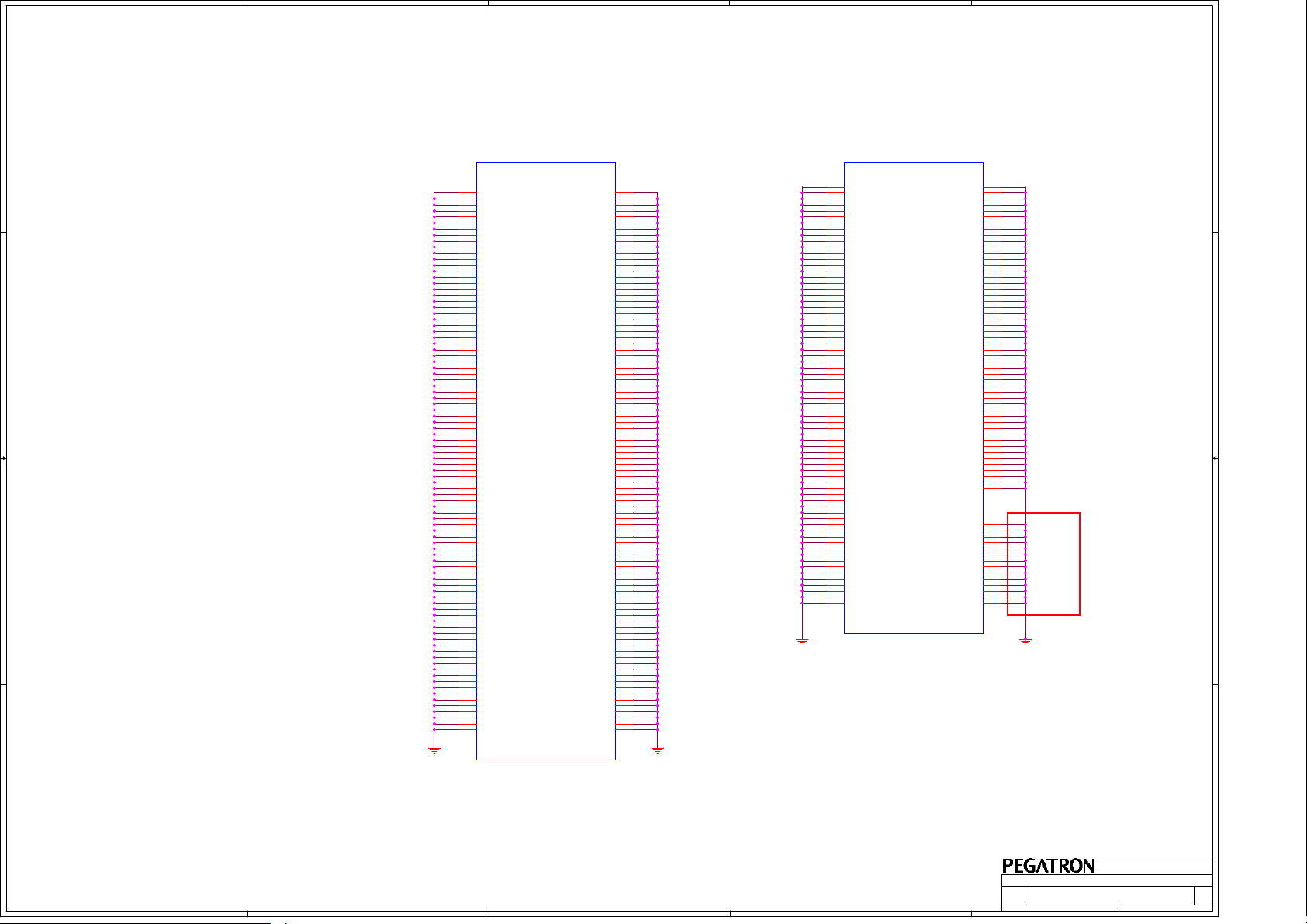

D D

4

3

2

1

BG17

BG21

BG24

BG28

BG37

BG41

BG45

BG49

BG53

BG9

C29

C35

C40

D10

D14

D18

D22

D26

D29

D35

D40

D43

D46

D50

D54

D58

G48

G51

G61

H10

H14

H17

H21

H53

H58

M11

M15

D4

D6

E25

E29

E3

E35

E40

F13

F15

F19

F29

F35

F40

F55

G6

H4

J1

J49

J55

K11

K21

K51

K8

L16

L20

L22

L26

L30

L34

L38

L43

L48

L61

U0301I

VSS8

VSS7

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

VSS0

VSS10

VSS288

VSS287

VSS286

VSS283

VSS282

VSS281

VSS280

VSS279

VSS278

VSS277

VSS285

VSS276

VSS275

VSS274

VSS273

VSS272

VSS271

VSS284

VSS269

VSS268

VSS270

VSS267

VSS266

VSS265

VSS264

VSS263

VSS262

VSS261

VSS260

VSS259

VSS257

VSS256

VSS258

VSS255

VSS253

VSS252

VSS251

VSS250

VSS254

VSS249

VSS248

VSS247

VSS246

VSS245

VSS243

VSS242

VSS241

VSS244

VSS240

VSS239

VSS238

VSS237

VSS236

VSS235

VSS234

VSS233

VSS232

VSS231

VSS228

VSS227

ES1

01V010000003

VSS

NCTF

VSS230

VSS226

VSS229

VSS225

VSS224

VSS223

VSS222

VSS221

VSS220

VSS219

VSS218

VSS217

VSS216

VSS215

VSS214

VSS213

VSS212

VSS211

VSS209

VSS208

VSS207

VSS206

VSS205

VSS204

VSS210

VSS202

VSS201

VSS203

VSS200

VSS199

VSS198

VSS197

VSS196

VSS195

VSS194

VSS193

VSS192

VSS190

VSS191

VSS189

VSS188

VSS186

VSS185

VSS184

VSS183

VSS182

VSS187

VSS181

VSS180

VSS179

VSS178

VSS_NCTF13

VSS_NCTF12

VSS_NCTF6

VSS_NCTF5

VSS_NCTF4

VSS_NCTF3

VSS_NCTF2

VSS_NCTF1

VSS_NCTF0

VSS_NCTF11

VSS_NCTF10

VSS_NCTF9

VSS_NCTF8

VSS_NCTF7

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W13

W15

W18

W21

W46

W8

Y4

Y47

Y58

Y59

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

BGA only

All NCTF pins should be test points

and should be routed as trace.

U0301H

A13

VSS299

A17

VSS298

A21

VSS297

A25

VSS296

A28

VSS295

A33

VSS294

A37

VSS293

A40

VSS292

A45

VSS291

A49

VSS290

A53

VSS289

A9

VSS300

AA1

VSS177

AA13

VSS175

AA50

VSS174

AA51

VSS173

AA52

VSS172

AA53

VSS171

AA55

VSS170

AA56

VSS169

AA8

VSS176

AB16

VSS168

AB18

VSS167

AB21

VSS166

AB48

VSS165

AB61

VSS164

C C

B B

AC10

AC14

AC46

AD17

AD20

AD61

AE13

AF17

AF21

AF47

AF48

AF50

AF51

AF52

AF53

AF55

AF56

AF58

AF59

AG10

AG14

AG18

AG47

AG52

AG61

AH58

AK52

AM13

AM20

AM22

AM26

AM30

AM34

AJ13

AJ16

AJ20

AJ22

AJ26

AJ30

AJ34

AJ38

AJ42

AJ45

AJ48

AL10

AL13

AL17

AL21

AL25

AL28

AL33

AL36

AL40

AL43

AL47

AL61

VSS162

VSS161

VSS160

AC6

VSS163

VSS158

VSS157

AD4

VSS159

VSS156

VSS154

AE8

VSS155

AF1

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

AG7

VSS140

AH4

VSS133

VSS132

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

AJ7

VSS131

AK1

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS

VSS98

VSS105

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS81

VSS80

VSS79

VSS82

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS78

VSS70

VSS69

VSS68

VSS71

VSS67

VSS66

VSS65

VSS64

VSS62

VSS61

VSS60

VSS59

VSS63

VSS58

VSS57

VSS56

VSS55

VSS54

VSS53

VSS52

VSS50

VSS49

VSS48

VSS51

VSS45

VSS44

VSS43

VSS42

VSS47

VSS41

VSS40

VSS39

VSS38

VSS37

VSS46

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS29

VSS28

VSS26

VSS27

VSS25

VSS23

VSS22

VSS21

VSS20

VSS19

VSS18

VSS17

VSS16

VSS15

VSS14

VSS13

VSS12

VSS24

VSS11

VSS9

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

ES1

01V010000003

A A

Title :

Title :

Title :

CPU(6)_GND

CPU(6)_GND

CPU(6)_GND

Trunks Chen

Trunks Chen

Engineer:

Engineer:

B34

B34

B34

Engineer:

1

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

BG1-HW RD Div.2-NB RD Dept .5

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Trunks Chen

of

of

of

8 59Wednesday, February 01, 2012

8 59Wednesday, February 01, 2012

8 59Wednesday, February 01, 2012

Rev

Rev

Rev

1.0

1.0

1.0

5

CFG strapping information:

CFG[2]: PCIE Static Numbering Lane Reversal- CFG[2] is for the 16x

- 1: (Default) Normal Operation, Lane # definition matches sockect pin map definition

- 0: Lane Numbers Reversed

D D

CFG[4]: Embedded DisplayPort Detection

- 1: (Default) Disabled ; No Physical Display Port attached to Embedded DisplayPort

- 0: Enabled ; An external Display Port device is connected to the Embedded Display Port

CFG[6:5]: PCI Express Port Bifurcation Straps

- 11 : (Default) x 1 6

- 10 : x 8 , x 8

- 01 : Reserved

- 00 : x 8 , x 4 , x 4

CFG[7]: PEG DEFER TRAINING

- 1: (Default) PEG Train immediately following xxRESETB de assertion

- 0: PEG Wait for BIOS training

CFG2

C C

CFG4

CFG5

CFG6

CFG7

1 2

1%

R0902 1KOhm

1 2

1%

R0903 1KOhm

@

1 2

1%

R0904 1KOhm

@

1 2

1%

R0905 1KOhm@

1 2

1%

R0906 1KOhm@

4

3

T0913

T0914

T0915

T0916

T0917

1

VCC_VAL_SENSE

1

VSS_VAL_SENSE

1

VAXG_VAL_SENSE

1

VSSAXG_VAL_SENSE

1

VCCAXG_VAL_SENSE

CFG2

CFG4

CFG5

CFG6

CFG7

U0301E

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD39

K48

RSVD37

BA19

RSVD15

AV19

RSVD18

AT21

RSVD22

BB21

RSVD12

BB19

RSVD13

AY21

RSVD17

BA22

RSVD14

AY22

RSVD16

AU19

RSVD20

AU21

RSVD19

BD21

RSVD11

BD22

RSVD10

BD25

RSVD9

BD26

RSVD8

BG22

RSVD1

BE22

RSVD6

BG26

RSVD0

BE26

RSVD4

BF23

RSVD3

BE24

RSVD5

2

1

Chief River

BE7

BG7

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

C4

D3

D1

A58

A59

C59

A61

C61

D61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BG1

BE1

BD1

DDR_WR_VREF01

DDR_WR_VREF02

RESERVED

RSVD7

RSVD2

RSVD31

RSVD36

RSVD35

RSVD34

RSVD33

RSVD32

RSVD28

RSVD27

RSVD29

RSVD21

RSVD38

RSVD25

RSVD26

RSVD24

RSVD23

RSVD30

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

ES1

01V010000003

PROCESSOR DRIVEN Vref PATH WAS STUFFED BY DEFAULT:

1 2

B B

DDR_WR_VREF01

DRAMRST_CNTRL_PCH5,9,21

DDR_WR_VREF02

A A

DRAMRST_CNTRL_PCH5,9,21

5

R0907 0Ohm

Q0901A

@

UM6K1N

1%

12

2

R0909

1KOhm

1 2

R0910 0Ohm

Q0901B

@

UM6K1N

1%

12

5

R0911

1KOhm

4

61

34

DIMM0_VREF_DQ 18

DIMM1_VREF_DQ 18

3

For iFDIM testing

R0912~ R0917 close to pin < 1 inch

+VCORE+VGFX_CORE

12

R0912

@

49.9Ohm

1%

VAXG_VAL_SENSE VCC_VAL_SENSE

R0913

@

100Ohm

1%

1 2

VSSAXG_VAL_SENSE VSS_VAL_SENSE

12

R0914

@

49.9Ohm

1%

2

@

@

@

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

12

1 2

12

R0915

49.9Ohm

1%

R0916

100Ohm

1%

R0917

49.9Ohm

1%

R1.1 0512

B34

B34

B34

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

CPU(7)_RSVD

CPU(7)_RSVD

CPU(7)_RSVD

Trunks Chen

Trunks Chen

Trunks Chen

of

9 59Wednesday, February 01, 2012

of

9 59Wednesday, February 01, 2012

of

9 59Wednesday, February 01, 2012

Rev

Rev

Rev

1.0

1.0

1.0

5

4

3

2

1

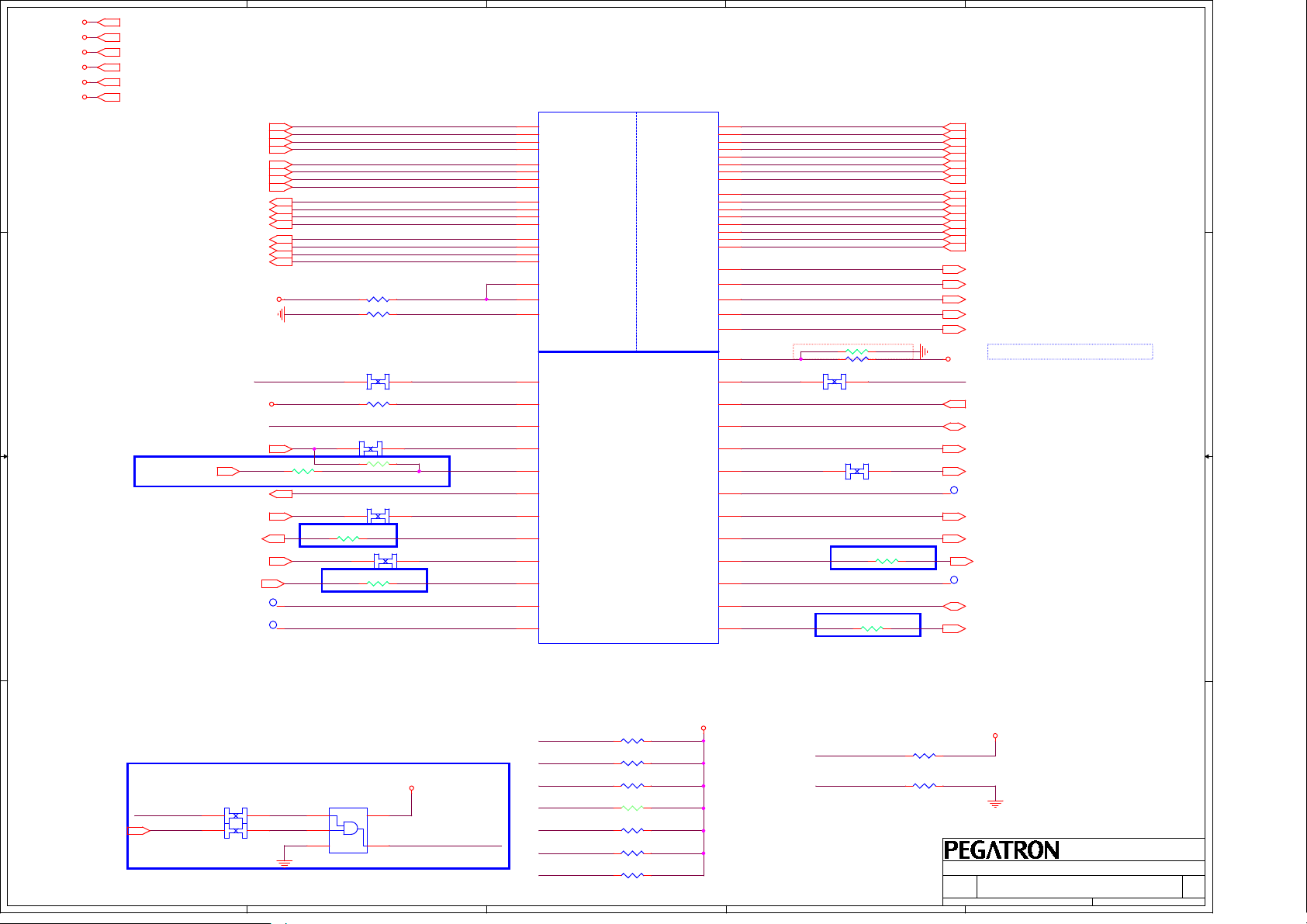

+VTT_PCH_ORG

+3VSUS

+VCCP

+3VS

D D

+VTT_PCH_ORG 22,26,27

+3VSUS 22,24,27,28,30,33,53,56,81,92

+VCCP 3,4,6,7,26,27,30,32,82

+3VS 16,17,20,21,22,23,24,25,26,27,28,30,31,32,33,38,44,45,46 ,48,50,51,53,56,57,62,66,80,85,91,92

remove XDP connector

C C

Check Connector

CPU XDP connector

PCH XDP connector

B B

A A

Title :

Title :

Title :

Engineer:

Engineer:

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

Size Project Name

Size Project Name

Size Project Name

B

B

B

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

B34

B34

B34

Engineer:

CPU_PCH_XDP

CPU_PCH_XDP

CPU_PCH_XDP

Trunks Chen

Trunks Chen

Trunks Chen

1

Rev

Rev

Rev

1.0

1.0

10 59Wednesday, February 01, 2012

10 59Wednesday, February 01, 2012

10 59Wednesday, February 01, 2012

1.0

of

of

of

5

4

3

2

1

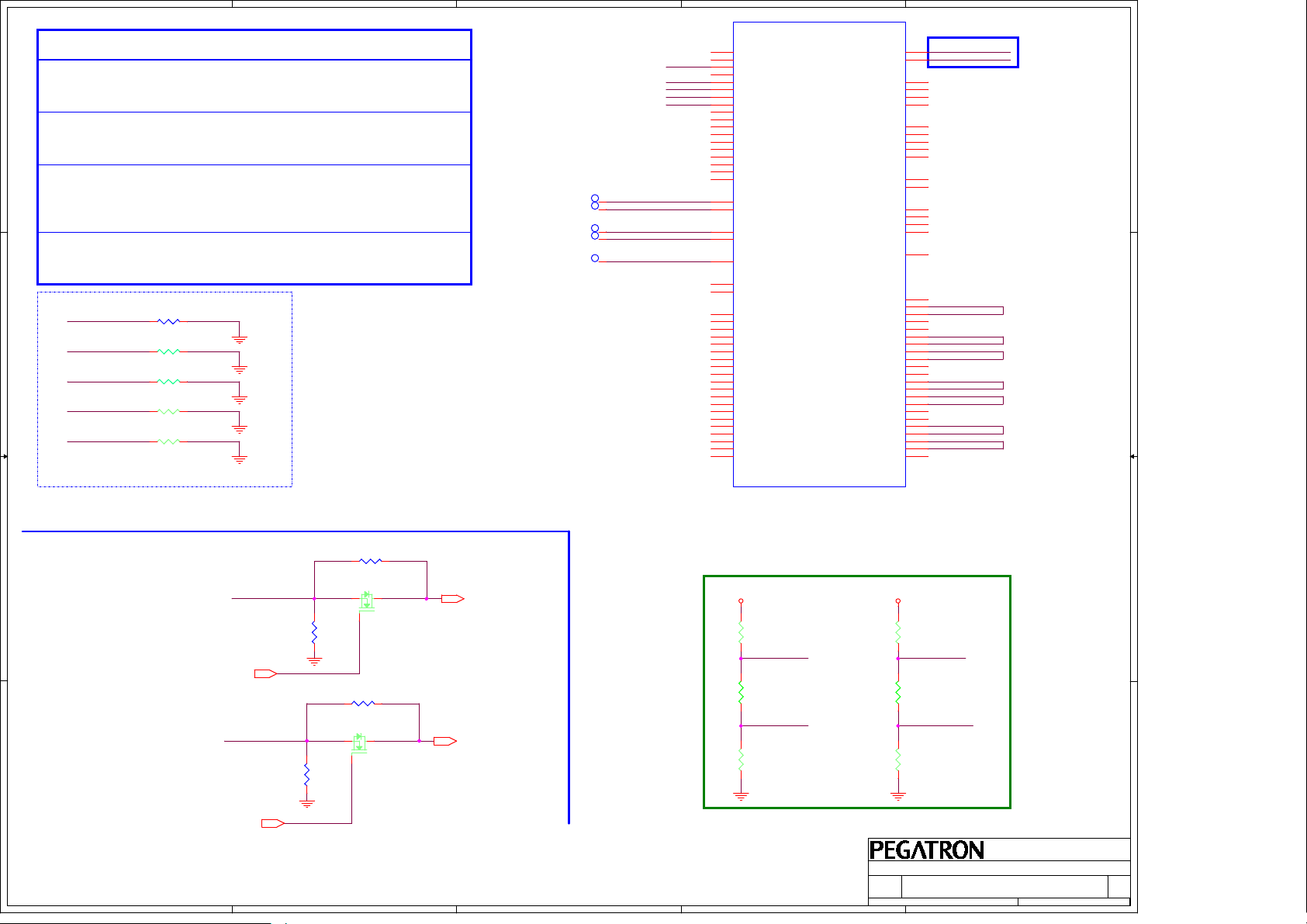

D D

Chief River

Decoupling guide from Intel PDDG R0.8

+VCORE 2.2uF * 16 pcs

22uF * 12 pcs

C C

B B

+VCORE

vx_c0402_small

12

C1101

2.2UF/6.3V

vx_c0402_small

12

C1111

2.2UF/6.3V

12

C1136

22UF/6.3V

12

C1144

22UF/6.3V

12

C1102

2.2UF/6.3V

vx_c0402_small

12

C1112

2.2UF/6.3V

vx_c0402_small

12

12

vx_c0402_small

12

C1103

2.2UF/6.3V

vx_c0402_small

vx_c0402_small

12

C1113

2.2UF/6.3V

vx_c0402_small

C1137

22UF/6.3V

C1145

22UF/6.3V

12

C1104

2.2UF/6.3V

12

C1114

2.2UF/6.3V

12

C1138

22UF/6.3V

12

C1146

22UF/6.3V

vx_c0402_small

12

C1105

2.2UF/6.3V

vx_c0402_small

vx_c0402_small

12

C1115

2.2UF/6.3V

vx_c0402_small

12

C1139

22UF/6.3V

12

C1147

22UF/6.3V

vx_c0402_small

12

C1106

2.2UF/6.3V

12

C1117

2.2UF/6.3V

12

C1140

22UF/6.3V

12

C1107

2.2UF/6.3V

vx_c0402_small

vx_c0402_small

12

C1108

2.2UF/6.3V

12

C1141

22UF/6.3V

12

C1109

2.2UF/6.3V

vx_c0402_small

12

12

C1110

2.2UF/6.3V

C1142

22UF/6.3V

12

C1143

22UF/6.3V

A A

Title :

Title :

Title :

Engineer:

Engineer:

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

Size Project Name

Size Project Name

Size Project Name

B

B

B

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

B34

B34

B34

Engineer:

CPU DECOUPLING

CPU DECOUPLING

CPU DECOUPLING

Trunks Chen

Trunks Chen

Trunks Chen

11 59Wednesday, February 01, 2012

11 59Wednesday, February 01, 2012

11 59Wednesday, February 01, 2012

1

Rev

Rev

Rev

1.0

1.0

1.0

of

of

of

5

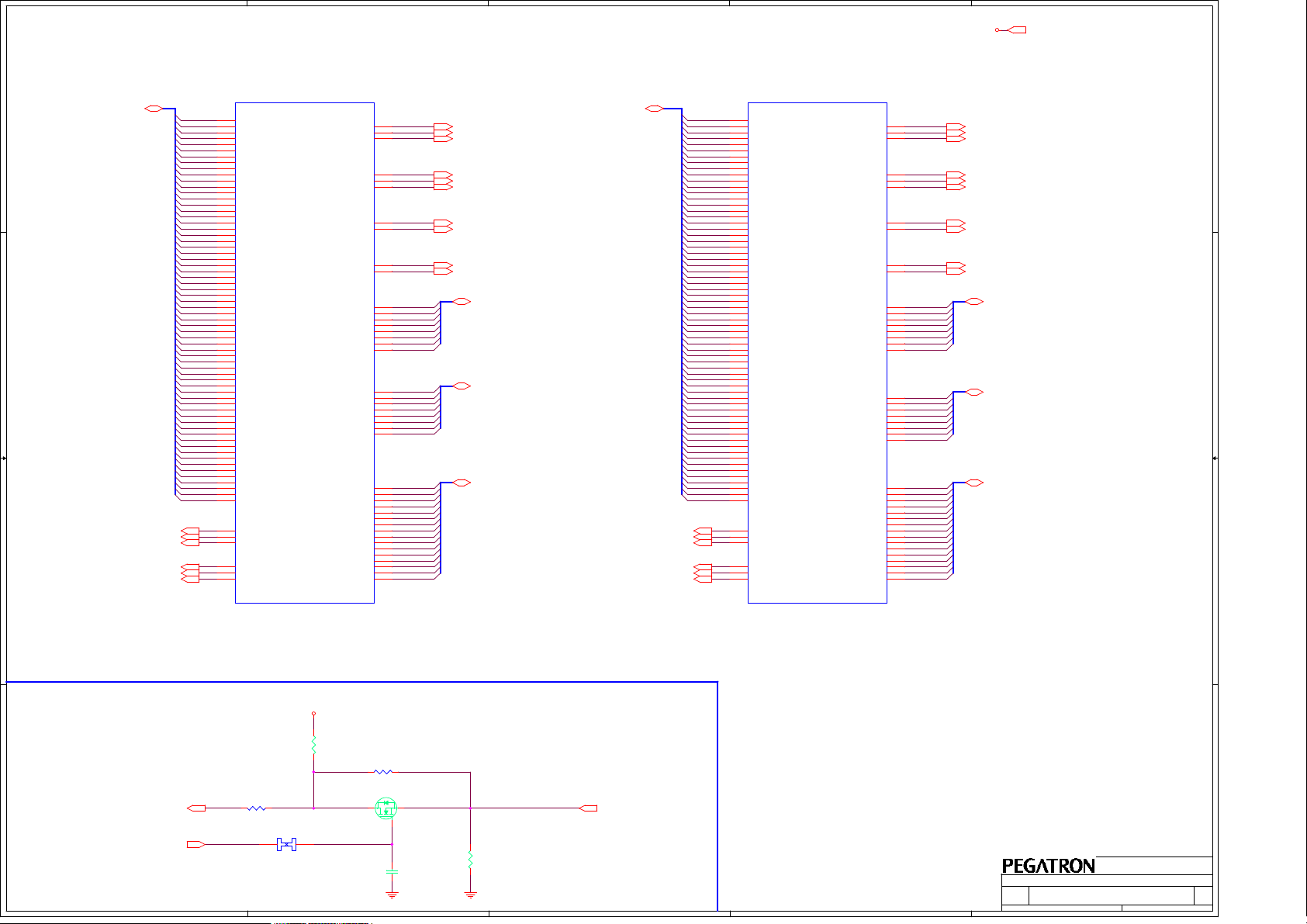

+DDR3

+0.75VS

+3VS

+V_VREF_CA_DIMM0

+V_VREF_DQ_DIMM0

D D

+DDR3 5,7,17,18,57,83

+0.75VS 17,57,83

+3VS 17,20,21,22,23,24,25,26,27,28,30,31,32,33,38,44,45,46,48,50,51,53,56,57,62,66,80,85,91,92

+V_VREF_CA_DIMM0 17,18

+V_VREF_DQ_DIMM0 18

4

+DDR3

12

+

CE1603

220UF/4V

@

3

+DDR3

Layout Note: Place these caps near SO DIMM 0

12

C1610

10UF/6.3V

vx_c0603_small

12

C1611

10UF/6.3V

vx_c0603_small

vx_c0603_small

12

C1609

10UF/6.3V

vx_c0603_small

12

C1612

10UF/6.3V

@

2

vx_c0603_small

12

C1613

10UF/6.3V

@

12

C1620

10UF/6.3V

@

vx_c0603_small

+0.75VS

12

C1616

1UF/6.3V

12

C1617

1UF/6.3V

12

1

C1618

1UF/6.3V

@

12

C1619

1UF/6.3V

@

M_A_DIM0_CLK_DDR0

M_A_DIM0_CLK_DDR#0

M_A_DIM0_CLK_DDR1

M_A_DIM0_CLK_DDR#1

12

12

C1602

10PF/50V

@

C1601

10PF/50V

@

12

12

1%

150Ohm

R1603

@

1%

150Ohm

R1604

@

PLACE CLOSE TO SODIMM

C C

B B

M_A_DQS[7:0]5

M_A_DQS#[7:0]5

A A

M_A_DIM0_CLK_DDR15

M_A_DIM0_CLK_DDR#15

M_A_DIM0_CLK_DDR05

M_A_DIM0_CLK_DDR#05

M_A_DIM0_CS#15

M_A_DIM0_CS#05

M_A_DIM0_ODT15

M_A_DIM0_ODT05

M_A_DIM0_CKE15

M_A_DIM0_CKE05

SMBus Slave Address: A0H

DM should connect to GND directly

Design Guide 0.9 p86 (436735)

SMB_CLK_S17,28,31,53

SMB_DAT_S17,28,31,53

M_A_A[15:0]5

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_WE#5

M_A_RAS#5

M_A_CAS#5

M_A_BS25

M_A_BS15

M_A_BS05

1 2

R1601 10KOhm

1 2

R1602 10KOhm

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

J1601A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

102

CK1

104

CK1#

101

CK0

103

CK0#

121

S1#

114

S0#

120

ODT1

116

ODT0

113

WE#

110

RAS#

115

CAS#

79

BA2

108

BA1

109

BA0

74

CKE1

73

CKE0

201

SA1

197

SA0

188

DQS7

186

DQS#7

171

DQS6

169

DQS#6

154

DQS5

152

DQS#5

137

DQS4

135

DQS#4

64

DQS3

62

DQS#3

47

DQS2

45

DQS#2

29

DQS1

27

DQS#1

12

DQS0

10

DQS#0

187

DM7

170

DM6

153

DM5

136

DM4

63

DM3

46

DM2

28

DM1

11

DM0

202

SCL

200

SDA

DDR3_DIMM_204P

0

1

2

3

4

5

6

7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

RESET#

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

30

M_A_DQ0

M_A_DQ1

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ2

M_A_DQ3

M_A_DQ7

M_A_DQ13

M_A_DQ8

M_A_DQ10

M_A_DQ14

M_A_DQ9

M_A_DQ12

M_A_DQ15

M_A_DQ11

M_A_DQ16

M_A_DQ21

M_A_DQ23

M_A_DQ18

M_A_DQ20

M_A_DQ17

M_A_DQ22

M_A_DQ19

M_A_DQ29

M_A_DQ24

M_A_DQ26

M_A_DQ31

M_A_DQ30

M_A_DQ28

M_A_DQ25

M_A_DQ27

M_A_DQ39

M_A_DQ37

M_A_DQ33

M_A_DQ35

M_A_DQ32

M_A_DQ36

M_A_DQ38

M_A_DQ34

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ42

M_A_DQ40

M_A_DQ44

M_A_DQ41

M_A_DQ43

M_A_DQ53

M_A_DQ49

M_A_DQ55

M_A_DQ50

M_A_DQ52

M_A_DQ48

M_A_DQ51

M_A_DQ54

M_A_DQ58

M_A_DQ62

M_A_DQ57

M_A_DQ61

M_A_DQ63

M_A_DQ56

M_A_DQ60

M_A_DQ59

0~7

8~15

16~23

24~31

32~39

40~47

48~55

56~63

DDR3_DRAMRST# 5,17

12V02GBRM000

M:1202-00EE000

S:1202-00KB000

5

4

M_A_DQ[63:0] 5

3

MAX: 2.68A

+DDR3

TDC: 2.68A

12

12

C1605

0.1UF/10V

C1606

0.1UF/10V

Layout Note: Place these caps near SO DIMM 0

1

PM_EXTTS#0_DIM_A

T1601

Reserve

+V_VREF_CA_DIMM0

vx_c0402_small

+V_VREF_DQ_DIMM0

vx_c0402_small

12

C1624

2.2UF/6.3V

@

12

C1622

2.2UF/6.3V

@

W/S=20/20

12

C1623

0.1UF/10V

W/S=20/20

12

C1625

0.1UF/10V

2

J1601B

75

VDD1

81

VDD3

87

VDD5

93

VDD7

99

VDD9

105

VDD11

111

VDD13

117

VDD15

123

VDD17

2

VSS1

8

VSS3

13

VSS5

19

VSS7

25

VSS9

31

VSS11

37

VSS13

43

VSS15

48

VSS17

54

VSS19

60

VSS21

65

VSS23

71

VSS25

127

VSS27

133

VSS29

138

VSS31

144

VSS33

150

VSS35

155

VSS37

161

VSS39

167

VSS41

172

VSS43

178

VSS45

184

VSS47

189

VSS49

195

VSS51

198

EVENT#

125

TEST

77

NC1

122

NC2

126

VREFCA

1

VREFDQ

DDR3_DIMM_204P

12V02GBRM000

+DDR3

76

VDD2

82

VDD4

88

VDD6

94

VDD8

100

VDD10

106

VDD12

112

VDD14

118

VDD16

124

VDD18

3

VSS2

9

VSS4

14

VSS6

20

VSS8

26

VSS10

32

VSS12

38

VSS14

44

VSS16

49

VSS18

55

VSS20

61

VSS22

66

VSS24

72

VSS26

128

VSS28

134

VSS30

139

VSS32

145

VSS34

151

VSS36

156

VSS38

162

VSS40

168

VSS42

173

VSS44

179

VSS46

185

VSS48

190

VSS50

196

VSS52

207

GND1

208

GND2

205

NP_NC1

206

NP_NC2

203

VTT1

204

VTT2

199

VDDSPD

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

BG1-HW RD Div.2-NB RD Dept.5

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

B34

B34

B34

12

MAX: 0.75A

TDC: 0.75A

+0.75VS

C1615

0.1UF/10V

12

C1607

0.1UF/10V

+3VS

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

12

C1608

0.1UF/10V

12

C1614

vx_c0402_small

2.2UF/6.3V

@

DDR3(1)_SO-DIMM0

DDR3(1)_SO-DIMM0

DDR3(1)_SO-DIMM0

Trunks Chen

Trunks Chen

Trunks Chen

16 59Wednesday, February 01, 2012

16 59Wednesday, February 01, 2012

16 59Wednesday, February 01, 2012

Rev

Rev

Rev

1.0

1.0

1.0

5

4

3

2

1

+DDR3

+0.75VS

+3VS

+V_VREF _CA_DIMM1

+V_VREF _DQ_DIMM1

D D

M_B_DIM0_ CLK_DDR0

M_B_DIM0_ CLK_DDR#0

M_B_DIM0_ CLK_DDR1

M_B_DIM0_ CLK_DDR#1

PLACE CLOSE TO SODIMM

C C

B B

A A

+DDR3 5,7 ,16,18,57,83

+0.75VS 16,57,83

+3VS 16,2 0,21,22,23,24,25,26 ,27,28,30,31,32,33 ,38,44,45,46,48,50 ,51,53,56,57,62,66,8 0,85,91,92

+V_VREF _CA_DIMM1 16 ,18

+V_VREF _DQ_DIMM1 18

M_B_A[15 :0]5

M_B_A0

10KOhm

10KOhm

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

34

12

M_B_DQS 7

M_B_DQS #7

M_B_DQS 6

M_B_DQS #6

M_B_DQS 5

M_B_DQS #5

M_B_DQS 4

M_B_DQS #4

M_B_DQS 3

M_B_DQS #3

M_B_DQS 2