Page 1

B1A Internal BIOS Specification

T

Software Specifications

Get to know more about the B1 Series Notebook

with a detailed look at the software specifications.

he information contained in the chapter can be quite useful when you

are troubleshooting the system’s hardware. Each item has its

7

individual usage for you to understand the software side of the

notebook’s architecture.

Page 2

B1A Internal BIOS Specification

Content

1. Introduction................................................................................................................ 1

2. Hardware Overview...................................................................................................2

2.1 Chipset Strapping............................................................................................. 5

2.2 Multiplex Pin Assignment................................................................................5

2.3 General Purpose Pin Usage..............................................................................8

2.4 Connections of System Management Bus .....................................................11

2.5 Connections of Power Management Control Pins......................................... 11

3. Configuration of PCI Devices..................................................................................12

4. Functions of Embedded Controller..........................................................................13

4.1 Host Interface and Command Set .............................. 錯誤! 尚未定義書籤。

4.1 Fast Button and Function Hot Key Events ............................................................13

4.2 Power Management Events............................................................................15

4.2.1 Thermal Control..................................................................................15

4.3 LED Control...................................................................................................18

5. M-Mode Control Mechanism ..................................................................................19

6. Power Management .................................................................................................19

6.1 APM and Legacy PM.....................................................................................20

6.1.1 Common Settings................................................................................ 20

6.1.2 Full On Sate ........................................................................................21

6.1.3 Standby Sate........................................................................................21

6.1.4 Suspend To RAM Sate........................................................................ 21

6.1.5 Suspend To Disk Sate .........................................................................21

6.2 ACPI...............................................................................................................21

6.2.1 ACPI-Enabling Initialization ..............................................................22

6.2.2 ACPI-Disabling Initialization ............................................................. 22

6.2.3 Thermal Control..................................................................................22

6.2.4 Control Method Battery ......................................................................22

6.2.5 Control Method Sleep Button .............................................................22

6.2.6 Methods for Proprietary On-Screen Display Utility...........................22

7. Callback Services for nVidia’s VGA BIOS ............................................................. 22

8. Clock Generator Setting...........................................................................................23

9. Setup Menu ..............................................................................................................24

10. Reference ...............................................................................................................24

ii

Page 3

B1A Internal BIOS Specification

1. Introduction

B1A is a high-performance/2-spindles/Balanced Mobility notebook PC supporting

1GHz P-III level or above socket uPGA2 CPUs. The major features of B1A system

BIOS support following industry specifications:

Advanced Configuration and Power Interface Specification, Revision 2.0

Advanced Power Management (APM) BIOS Interface Specification, Revision

2.0

Plug and Play BIOS Specification, Version 1.0A

PCI BIOS Specification, Revision 2.0

System Management BIOS Reference Specification, Version 2.3

System Management Bus BIOS Interface Specification, Revision 1.0

PC 2001 System Design Guide, Version 1.0

Additionally, it’s also in compliance with all other standards and specifications of PC

industry if not specifically indicated. Table 1 shows the summary of the B1A BIOS

features.

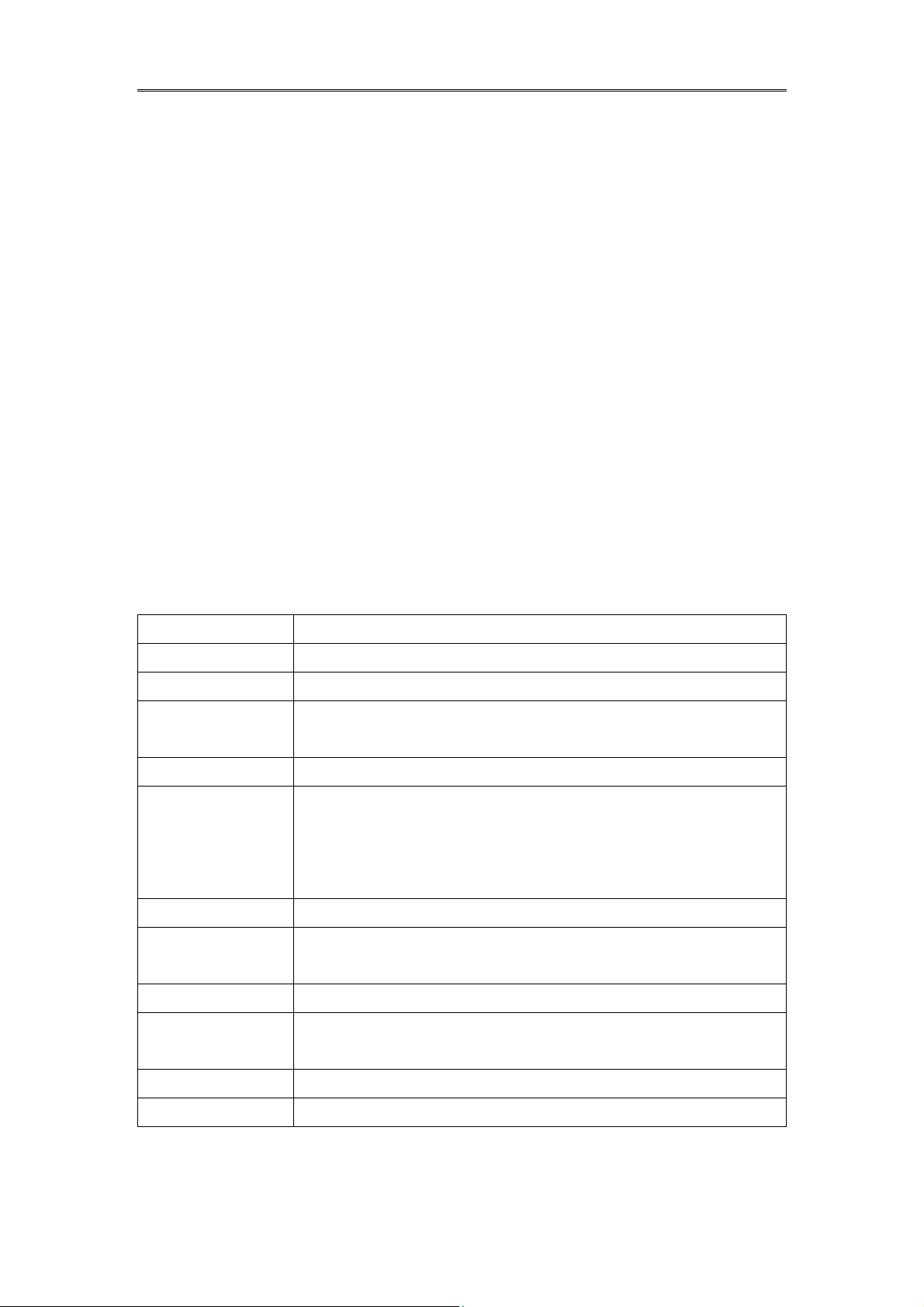

Table 1. The Features of System BIOS

Item Description

BIOS Vendor AWARD

BIOS Size 256 KB

CPU / Cache Automatic frequency and cache size detection; host clock and

VID adjusting.

DRAM Auto-sizing and SPD detection support.

HDD/CDROM 4-drive, FDMA, UDMA, fast PIO, block PIO, 32-bit IO,

SMART disk, and INT 13 extensions support; automatic model

typing, size detection, and parameters setting (drive geometry,

transfer mode, block size, LBA); bootable CDROM.

FDD 3 mode floppy disk support; floppy disk seek disable.

Booting Quiet boot; quick boot; multi-boot from HDD, FDD, CDROM,

USB devices, and 1394 peripheral; boot sequence control.

Display Automatic LCD/CRT presence detection.

Keyboard Numlock power-on state and typematic rate/delay setting;

US/JP/EU keyboards support.

PS/2 mouse Support.

Parallel port Enhanced parallel port (EPP) support for network adapters.

- 1 -

Page 4

B1A Internal BIOS Specification

Security 2-level password control, quick lock FDD access control, HDD

boot sector protection, and virus check reminder message.

Smart card reader and Finger Print authentication as optional for

security at BIOS booting and file encryption and description

PnP Legacy ISA, PnP ISA and PCI devices auto-configuration; PnP

ISA and PCI run-time BIOS services support.

APM Full on, standby, suspend-to-RAM, and suspend-to-disk power

management modes support; run-time BIOS services support.

ACPI C0, C1, C2, C3, S0, S1, S3, S4, S4BIOS, and S5 power

management modes, control method battery, proprietary

on-screen display utility support.

SMBus SMBus run-time BIOS services providing APs and O.S. to

access SPD EPROMs of SO-DIMM modules via 1st SMBus

interface of VT8231 ( south bridge)

SMB System Management BIOS v.2.3 support.

M-Mode Dynamically change host clock of CPU and Memory clock or

even Video clock.

Others Daylight savings time; Fast A20; 32-bit BIOS services; graphic

setup menu (English only).

The audience for this document includes system BIOS, embedded controller firmware,

and platform hardware designers.

2. Hardware Overview

The components of B1A platform and their features are listed in the following table.

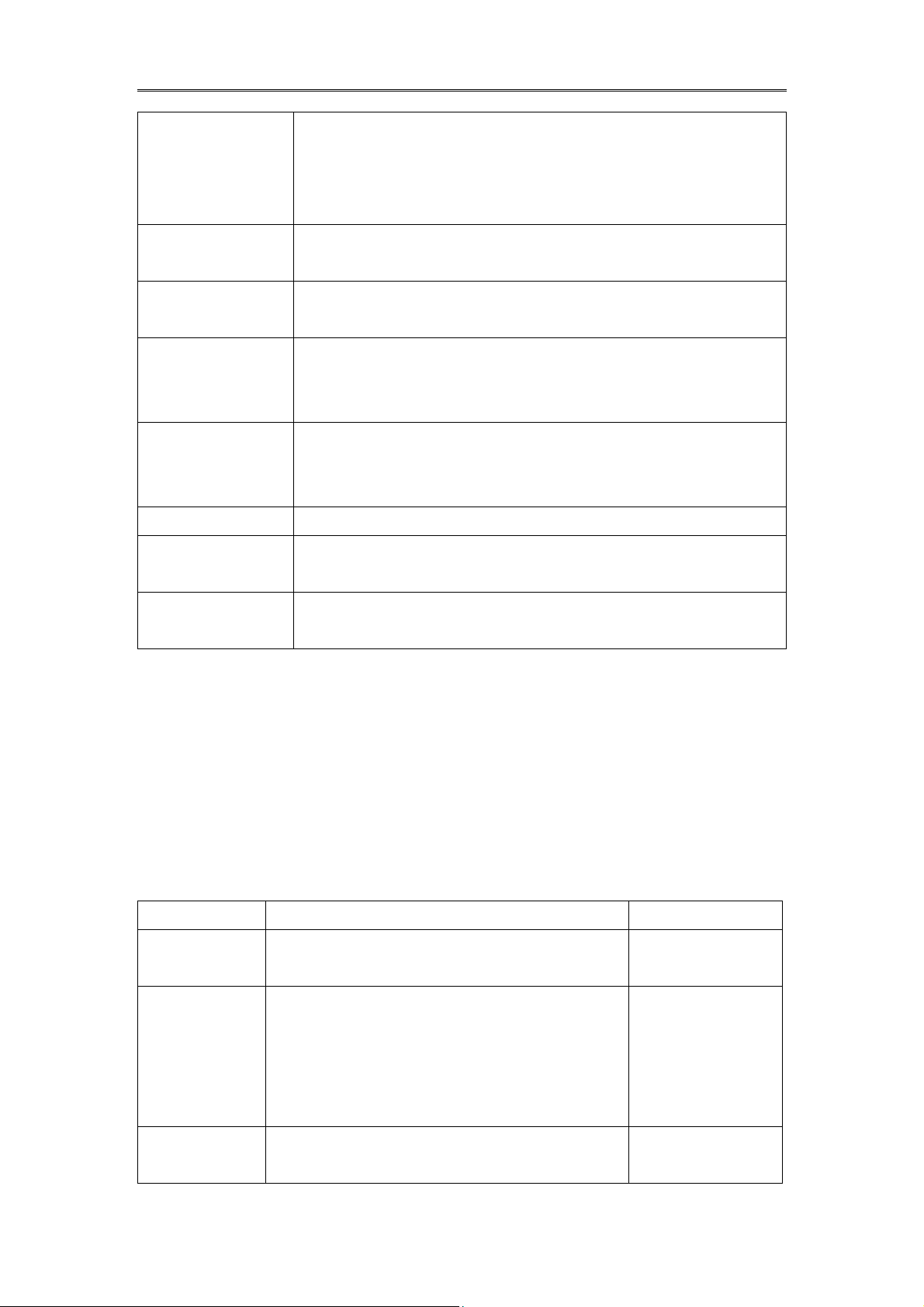

Table 2. Component List

Component Features Remark

CPU - PIII (1) Socket uPGA2

(2) > 1GHz

Core Chip

(NB) – Twister

Core Chip

(SB) – VT8231

(1) 66/100/133 MHz, 64 Bit CPU FSB

(2) 66/100/133 MHz, 64 Bit SDR/VCM

SDRAM: supports 8 banks up to 4GB

(512Mb x8/x16 tech.), mixed 1M / 2M / 4M

/ 8M / 16M / 32M / 64MxN DRAMs

(1) Integrated Peripheral Controllers:

Dual UDMA-33/66/100 EIDE

- 2 -

Supports SDR only

Page 5

B1A Internal BIOS Specification

VGA –

Embedded

VGA

Root Hub & 4 USB Ports

1/10/100 Mb Ethernet

AC ’97 Audio/Modem Interfaces

Digital Audio

LPC Interface

SMB Interface

Hardware Monitor

(2) Integrated Legacy Functions:

KBC w/ PS2 mouse support

RTC w/ 256 byte CMOS RAM

DMA, Timer, & Interrupt Controllers

Serial IRQ

Fast reset and Gate A20

(1) Full internal 4x AGP performance

(2) 128 bit 3D & 2D graphic accelerator

(3) Supports up to 3 display interfaces: LCD,

CRT, and TV out

NOT USED

NOT USED

Audio –

VT8231

AC-Link

interface and

Cirrus CS4299

audio CODEC

CardBus –

(4) Dual CRT/Simultaneous dual display

(5) Supports 8 to 32 MB frame buffer using

system memory

(6) Supports S3 DX7 texture compression

(S3TC)

(7) Support resolution up to 1920x1440

(1) SoundBlaster PRO Hardware and Direct

Sound Ready AC97 Digital Audio

Controller compatible

(2) 32 bytes FIFO of each direct sound channel

(3) Standard V1.0 or V.2.0 AC97 Codec

Interface

(4) Hardware assisted FM synthesis

(5) 1 MPU-401 port and 2 game ports

(6) Built-in HSP modem interface

(7) Support 4.1, 5.1, & 4/6 speaker modes

(1) Built-in Smart Card controller supports ISO

OZ711E1

7816-1, -2, -3 smart cards and PC/SC, open

card, and CT-API (B1) standards

(2) Automatically senses whether a PC card or

smart card is inserted

- 3 -

Page 6

B1A Internal BIOS Specification

1394 –

TSB43LV22

Super I/O –

VT8231

EC – NS87591

(Voyager)

(1) Full P1394a support

(2) Fully Interoperable with FireWire and

i.LINK implementation of IEEE std 1394

(3) 2 P1394a cable ports at 100/200/400 Mb/s

(1) LPC system interface

(2) Built-in functions include FDC, parallel

port, 2 serial ports (one w/ Fast IR),

Watchdog Timer, interrupt serializer, &

wake-up control

(1) LPC system interface, 2MB address space,

128 KB on-chip flash, & 4KB on-chip

RAM

(2) 8042 KBC standard interface (60h/64h) and

ACPI PM interface support (62h/66h)

(3) Provides 4 PS/2 channels for KBC &

mouse, 2 ACCESS.bus interfaces, 2

USARTs, 8 PWM outputs, 14 ADC

Wake-up control is

NOT USED

USART is NOT

USED

Battery

Charger –

Max1772

Clock

Generator –

ICS9248-143

CPU VID

Control –

FM3560

LCD Panel

Inverter –

channels, 4 DAC channels, 8 ACM inputs,

up to 32 wake-up inputs, & 84/117 GPIO

pins in 128/176 package

(4) Supports serial IRQ, & voltage/temperature

hardware monitoring

(5) RTC w/ 256 byte CMOS RAM

(1) Compliant with level 2 smart battery

charger specification revision 1.0

(1) Up to 200 MHz support

(2) Spread spectrum for EMI control

(1) 5 bit 2-to-1 multiplexer, 1-bit latch

(2) Used for changing VID when CPU’s

frequency is dynamically changed

(1) 32-level brightness & 256-level contrast

control via SMBus

NOT USED

OZ968

(2) Typical operating frequency ranges from

50KHz to 100 KHz

(3) Brightness output ranges from 0.9v to 2.5v

(level setting 0xFF to 0x00) and contrast

- 4 -

Page 7

B1A Internal BIOS Specification

output ranges from 0.8v to 2.8v (level

setting 0x00 to 0xFF)

LCD Panel SAMSUNG and LG 15” XGA/SXGA+

2.1 Chipset Strapping

The chipset strapping pin states of VT8231 PCI-to-ISA Bridge and Twister controller

are shown in table 3 and 4.

Table 3. Strapping Pin State of VT8231

Pin Strapping State Function

SUSA# 1 Select Intel PIII CPU

VGA_SUSP# 0 Only enable 8 bits XD bus

SA16 0 Disable LPC ROM

MCCS# 1 Disable Automatically select CPU host

clock

SYSSPK DEFAULT ISA ROM

SA17 1 Disable auto reboot

Table 4. Strapping Pin State of Twister

Pin Strapping State Function

MA13, 14 By wire cable Panel ID select

MA2 0 Enable INTA

MA3 0 Enable IO access

MA4 0 PCI base address map 0

MA5 0 Set PCI clock to 33MHz

MA6 0 Enable internal GTL pull up

MA7 0 Set VGA at normal mode

MA (12,8) [01] Set the CPU clock at 100MHz

MA9 0 Enable internal PLL clock

MA10 1 Enable quick start mode

MA11 0 Set IOQ level = 4

2.2 Multiplex Pin Assignment

Table 5 shows the assignment of VT8231 multiplex pins. For the usage of Nations

PC87591 embedded controller, please refer to the other document file named

PC87591_GPIOS.xls.

- 5 -

Page 8

B1A Internal BIOS Specification

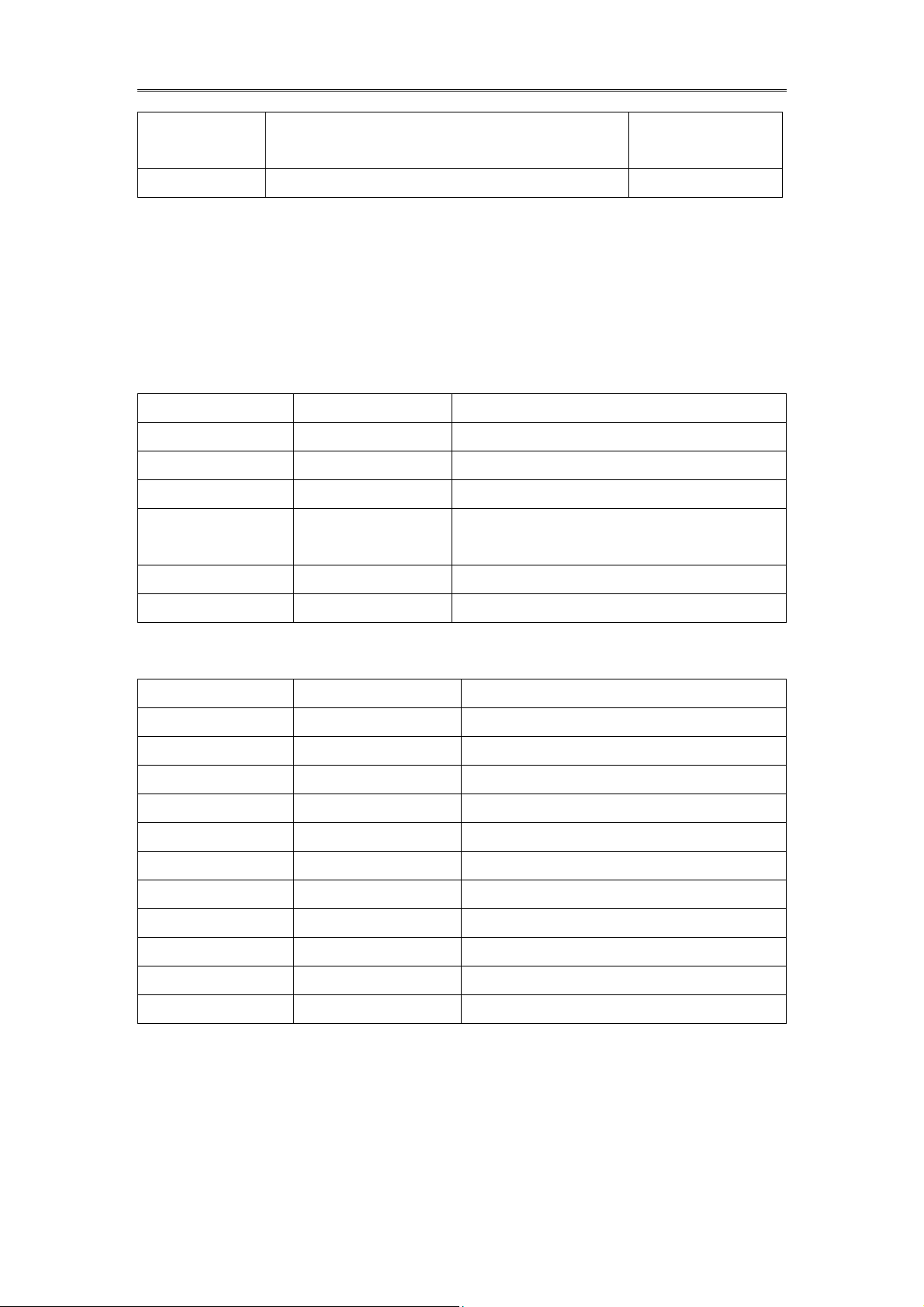

Table 5. Multiplex/Multi-function Pin Assignment of VT8231

Signal Name Pin# I/O Default Used As Register Setting

1

GPI0 F4

GPI1 V3

GPI2 / EXTSMI# W1 I Shared2 EXTSMI#

GPI3 / RING# U3 I Shared SWI#

GPI4 / LID# V2 I Shared NOT USED Pull HIGH

GPI5 / BATLOW# T3 I Shared NOT USED Pull HIGH

GPI6 / PME# U1 I Shared NOT USED Pull HIGH

GPI7 / SMBALRT# T2 I Shared NOT USED Pull HIGH

GPI8 / INTRUDER# F3 I GPI8 ??? NOT USED Pull HIGH

GPI9 / APICCLK Y3 I GPI9 ??? GPI9 ISA_RX58[6]=0

GPI10 / HREQ1# Y11 I GPI10 ??? HREQ1# PM_RXE5[3]=0

GPI11 / HREQ2# V11 I GPI11 ??? HREQ2# PM_RXE5[3]=0

GPI12 / LREQ1# U10 I GPI12 ??? LREQ1# PM_RXE5[2]=0

GPI13 / LREQ2# W10 I GPI13 ??? LREQ2# PM_RXE5[2]=0

GPI14 / WSC# /

V4 I GPI14 ??? WSC# ISA_RX58[7]=1

APICREQ#

GPI15 / LDRQ# /

ACSDIN3

Y8 I GPI15 ??? LDRQ# ISA_RX58[5]=1

PM_RXE5[7]=0

GPI16 / CPUMISS V1 I Shared CPUMISS Pull LOW

GPI17 / AOLGPI /

P3 I Shared THERM# PM_RX40[7]=1

THERM#

GPI18 / GPO18 / FAN2 /

K3 I Shared FAN2 PM_RXE5[0]=0

SLPBTN#

GPI19 / GPO19 /

ACSDIN2

GPO20 / LA20 /

USBOC2#

GPO21 / LA21 /

G5 I GPI19 GPO19 PM_RXE4[5]=1

PM_RXE5[5]=1

W13 I GPI20 USBOC2# PM_RXE4[6]=0

PMIO_RX4E[4]=1

Y13 I GPI21 USBOC3# PM_RXE4[6]=0

USBOC3#

PMIO_RX4E[5]=1

1

NOTE: Dii/Fj/Rxkk means PCI register “kk” of function “j” of device “ii”& PMIOkk means I/O port

offset “kk” relative to the base address of power management I/O base address in which all “ii”, “j”,

and “kk” are hexadecimal values.

2

No register setting is necessary for “shared” pin.

- 6 -

Page 9

B1A Internal BIOS Specification

GPI22 / GPO22 / IOR# U7 O GPI22 IOR# PM_RXE4[7]=1

GPI23 / GPO23 / IOW# T7 O GPI23 IOW# PM_RXE4[7]=1

GPI24 / GPO24 / GPIOA Y2 O GPI24 GPIOA PM_RXE7[0]=0

GPI25 / GPO25 / GPIOC

J5 O GPI25 GPIOC PM_RXE7[1]=0

/ ATEST

GPI26 / GPO26 /

R2 IO SMBDT2 SMBDT2 PM_RX55[2]=0

SMBDT2

GPI27 / GPO27 /

R1 IO SMBCK2 SMBCK2 PM_RX55[2]=0

SMBCK2

GPI28 / JAB1 G3 I JAB1 JAB1 ISA_RX50[7]=0

ISA_RX50[6]=0

GPI29 / JBB1 F1 I JBB1 JBB1 ISA_RX50[7]=0

ISA_RX50[6]=0

GPI30 / GPO30 / GPIOD

Y1 I GPI30 GPIOD PM_RXE7[6]=0

/ DTEST

GPI31 / GPO31 / GPIOE W3 I GPI31 GPIOE PM_RXE7[7]=0

GPO0 / SLOWCLK R4 OD GPO0 SLOWCLK PM_RX54[1,0]=0,1

GPO1 / SUSA# P1 O SUSA# SUSA# PM_RX54[2] = 0

GPO2 / SUSB# P2 O SUSB# SUSB# PM_RX54[3] = 0

GPO3 / SUSSTAT# N5 O SUSSTAT# SUSSTAT# PM_RX54[4] = 0

GPO4 / SUSCLK W2 O SUSCLK SUSCLK PM_RX55[1] = 0

GPO5 / CPUSTP# P4 O CPUSTP# CPUSTP# PM_RXE4[0] = 0

GPO6 / PCISTP# T4 O PCISTP# PCISTP# PM_RXE4[1] = 0

GPO7 / SLP# U6 O SLP# SLP# PM_RXE4[4] = 0

GPO8 / HGNT1# W11 O HGNT1# HGNT1# PM_RXE5[3] = 0

GPO9 / HGNT2# T10 O HGNT2# HGNT2# PM_RXE5[3] = 0

GPO10 / LGNT1# Y10 O LGNT1# LGNT1# PM_RXE5[2] = 0

GPO11 / LGNT2# V10 O LGNT2# LGNT2# PM_RXE5[2] = 0

GPO12 / JAB2 H5 O JAB2 GPO12 PM_RXE5[4] = 1

GPO13 / JBB2 H4 O JBB2 GPO13 PM_RXE5[4] = 1

GPO14 / IRTX R8 O IRTX IRTX PM_RXE5[5] = 0

GPO15 / IRRX U8 O IRRX IRRX PM_RXE5[5] = 0

GPO16 / PCS0# Y6 O PCS0# PCS0# PM_RXE4[2] = 0

GPO17 / MCCS# W6 O MCCS# MCCS# PM_RXE4[3] = 0

GPO28 / APICD0 /

W4 O APICD0 GPO28 ISA_RX58[7] = 0

APICCS#

ISA_RX58[6] = 0

- 7 -

Page 10

B1A Internal BIOS Specification

GPO29 / APICD1 /

APICACK#

Y4 O APICD1 GPO29 ISA_RX58[7] = 0

ISA_RX58[6] = 0

2.3 General Purpose Pin Usage

The used general-purpose pins of VT8231 south bridge and PC87591 embedded

controller (EC) are shown in table 6 and 7, respectively.

Table 6. GPIO Pin Usage of VT8231

Pin I/O Connected to Function

GPI0 I EC_SCI# Accept SCI# from EC

GPI1 I VRCHGNG# Indicate CPU voltage is changing

GPI18 I DOCK_ERROR Indicate DOCK powergood

GPO0 O 1HZ Generates 1 Hz frequency pulse for LEDs

GPO16 O VGA_SUSP Connect to NB(VGA) SUSPEND

GPIOA O GCL_GATE Mask VGATE from CPU VR to GCL

GPIOC O MSK_STAT1# Mask G_SUS_STAT2# from GCL

GPIOD IO AGP_BUSY# Connect to NB(VGA) AGPBUSY#

GPIOE O G_LO/HI# Connect to GCL G_LO/HI#

Table 7. Pin Usage of EC

Pin I/O Connected to Function

IOPA0/PWM0 O PWM output to turn on CPU fan

IOPA1/PWM1 I

IOPA2/PWM2 O Refer to charging flow chart

IOPA3/PWM3 O Refer to charging flow chart

IOPA4/PWM4 I

IOPA5/PWM5 O Used to turn on/off system power

IOPA6/PWM6 I Signal to indicate system is off

IOPA7/PWM7 O BIOS write protect

Signal to indicate system switched

power is OK

Connect to South Bridge RING# for

IOPB0/URXD O

IOPB1/UTXD O

IOPB2/USCLK OD

- 8 -

wake-up

Connect to South Bridge PWRBTN#

input

Connect to South Bridge EXTSMI#

input

Page 11

B1A Internal BIOS Specification

IOPB3/SCL1 I/O

IOPB4/SDA1 I/O

IOPB5/GA20 O

IOPB6/KBRST# O

IOPB7/RING#/PFAIL# I

IOPC0 O

IOPC1/SCL2 I/O SM-Bus Clock ( used on 2nd battery ,

IOPC2/SDA2 I/O SM-Bus Data ( used on 2nd battery ,

IOPC3/TA1 O Connect to South Bridge RSMRST#

SM-Bus Clock ( used on primary

battery )

SM-Bus Data ( used on primary

battery )

Connect to South Bridge Gate A20

input

Connect to South Bridge Keyboard

Reset

591 should assert this signal if both int

& ext power is OK

clock gen , VID…. )

clock gen , VID…. )

input

IOPC4/TB1/EXWINT22 I

IOPC5/TA2 I Count FAN speed

IOPC6/TB2/EXWINT23 I

IOPC7/CLKOUT/SIOCLKIN O

IOPD0/RI1#/EXWINT20 I

IOPD1/RI2#/EXWINT21 I

IOPD2/EXWINT24 I

IOPD3/ECSCI# O Connect to South Bridge SCI# input

IOPE4/SWIN I

Hotkey ( Bootable , direct launch

internet browser )

Hotkey ( Bootable , direct launch E-mail

AP )

Reset 591 itself

Connect to system PME# , wake up

system when low

Connect to COM port RI# , wake up

system when low

Front panel LID switch , low when

panel is closed

Connect to power button , low when

button is pressed

IOPE5/EXWINT40 I

IOPE6/LPCPD#/EXWINT45 I

IOPE7/CLKRUN#/EXWINT46 O

- 9 -

Connect to Hotkey , low when button is

pressed

Connect to Hotkey , low when button is

pressed

Connect to PCI bus CLKRUN# signal

Page 12

B1A Internal BIOS Specification

IOPF0/PSCLK1 I/O

IOPF1/PSDAT1 I/O Connect to PS/2 connector to link

IOPF2/PSCLK2 I/O Connect to PS/2 connector to link

IOPF3/PSDAT2 I/O Connect to PS/2 connector to link

IOPF4/PSCLK3 I/O Connect to touchpad clock pin

IOPF5/PSDAT3 I/O Connect to touchpad data pin

IOPF6/PSCLK4 I To indicate battery voltage is low

IOPF7/PSDAT4 I To indicate adaptor is plugged in

IOPH0/A0/ENV0 O

IOPH1/A1/ENV1 O

IOPH2/A2/BADDR0 O

IOPH3/A3/BADDR1 O

Connect to PS/2 connector to link

external keyboard

external keyboard

external mouse

external mouse

CAPS lock LED indicator

NUM lock LED indicator

SCROLL lock LED indicator

To indicate if M-Mode is turned on

IOPH4/A4/TRIS O To indicate Mute or not

IOPH5/A5/SHBM O

IOPH6/A6 O To system battery status LED

IOPH7/A7 O End of Charge signal

IOPI0/D0 O To reset IDE devices

IOPI1/D1 O Switch AC power to implement battery

IOPI2/D2 I Signal to indicate system enter ACPI

IOPI3/D3 I Signal to indicate system enter ACPI

IOPI4/D4 I Signal to indicate system enter ACPI

IOPI5/D5 O Assert when CPU temperature is high

IOPI6/D6 IO Turn on audio amplifier volume at first

To indicate if user got new e-mail

calibration

S1

S3

S5

power on

IOPI7/D7 I System non-switched power is OK

IOPJ0/RD# O Turn on IDE device's power

IOPJ1/WR0# I Indicate if mute switch is pressed

AD0 I

AD1 I

- 10 -

Sense primary battery temperature

Sense secondary battery temperature

Page 13

B1A Internal BIOS Specification

AD2 I

AD3 I

AD4/IOPE0 I Refer to charging flow chart

AD5/IOPE1 I Refer to charging flow chart

AD6/IOPE2 I Sense adaptor/battery voltage

AD7/IOPE3

AD8/DP I Sense CPU temperature

AD9/DN I Sense CPU temperature

DA0 O

DA1 O

DA2 O

DA3 O

Sense primary battery voltage

Sense secondary battery voltage

Refer to charging flow chart

Refer to charging flow chart

Control panel contrast

Control panel brightness

2.4 Connections of System Management Bus

The connections of all SMBus channels of VT8231 south bridge chipset and PC87591

embedded controller are shown in the table 8.

Table 8. Connections of System Management Bus Channels

SMBus

Interface

VT8231 1

Channel

VT8231

2nd

st

1st

SODIMM

2nd

SODIMM

Device #1 Device #2 Device#3

Name Address Name Address Name Address

1010000x3None None

1010001x Inverter

Connector

Channel

EC 1st

Battery 0001011x None None

Channel

EC 2nd

Channel

ICS9248 -

143 Clock

Generator

1101001x FM3560

CPU VID

selector

0101000x None

0110111x Battery 0001011x

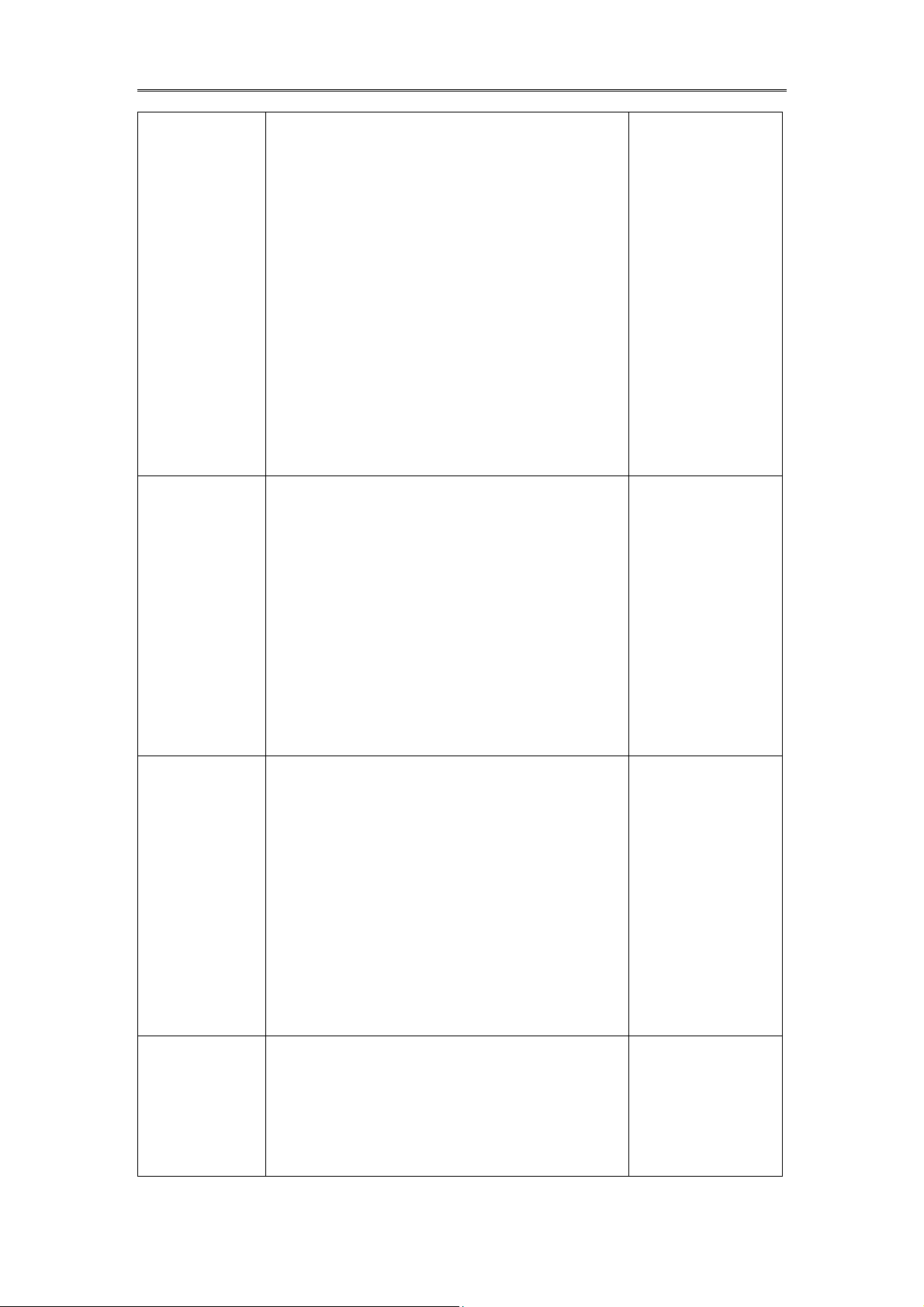

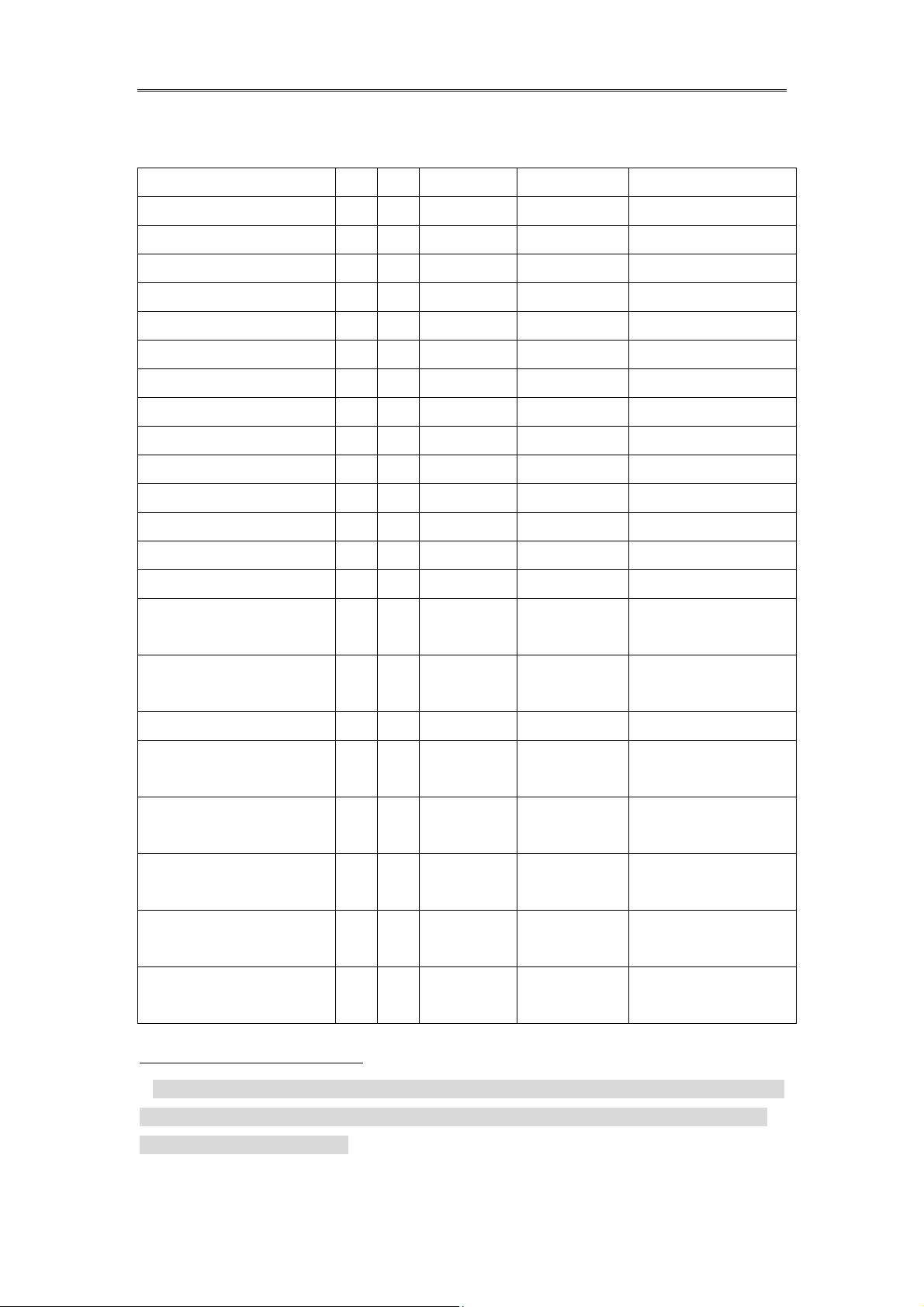

2.5 Connections of Power Management Control Pins

Figure 1 shows the flow diagram of power management control pins. These pins

coming to VT8231 south bridge may trigger SMI, SCI, or resume event.

3

RRAD: x=1; WRITE: x=0

- 11 -

Page 14

B1A Internal BIOS Specification

Figure 1. Flow Diagram of Power Management Control Pins

3. Configuration of PCI Devices

In Twister (VT8603 + VT8231) chipset, the PCI configuration address port is 0x0CF8

~ 0x0CFB and data port is 0x0CFC ~ 0x0CFF. The system BIOS initializes PCI

registers via above address and data ports based on the device selection and interrupt

routing information of all PCI devices or slot on B1A platform listed in following

table.

Table 9. Device Selection & Interrupt Routing of Onboard PCI Devices

Device IDSEL Bus# / Dev# Interrupt Routing

VT8603 Host Bridge AD114 0x00 / 0x00 None

VT8603 P2P Bridge AD12 0x00 / 0x01 None

VT8231 South AD28 0x00 / 0x11 INTA#5 -> INTA#

4

The IDSEL pins of VT8603 and VT8231 are internally assigned by Twister chipset.

5

The interrupt routing of VT8231 south bridge is internally determined.

- 12 -

Page 15

B1A Internal BIOS Specification

Bridge INTB# -> INTB#

INTC# -> INTC# (AC/MC ’97)

INTD# -> INTD# (USB)

OZ711E1 CardBus

Controller

TSB43AB22 1394

Controller

Mini-PCI Slot AD27 0x00 / 0x10 INTB# -> INTB#

The system BIOS assigns 0x8000 and 0x8100 as the I/O base addresses of power

management space registers and SMBus space registers, respectively. It may also

assign IRQ 9 for SCI, IRQ 14 for primary IDE channel, and IRQ 15 for secondary

IDE channel. All other I/O, memory, and IRQ resources for PCI devices are assigned

dynamically as follows:

I/O Base Address: 0x1000 ~ 0xFFFF.

Memory Base Address: 0x10000000 ~ 0xFEE00000.

IRQ (listed in priority): 11, 10, 3, 4, 9, 7, 12, 6, 15, 14

Exclusive IRQ: 5 – reserved for legacy PCMCIA card

AD26 0x00 / 0x0F INTD# -> INTD#

AD30 0x00 / 0x13 INTC# -> INTC#

INTD# -> INTD#

INTC# -> INTC#

Additionally, it sets the cache line size to 4 dwords and the latency timer of PCI bus

master to 64 PCI clock. It also sets PCI sub-system ID to 0x0000 and sub-system

vendor ID to 0x1043 (ASUS) by writing 0x00001043 to following PCI devices:

TSB43LV22 (1394): PCI register 0xF8~0xFB.

OZ711E1 (CardBus): PCI register 0x40~0x43.

4. Functions of Embedded Controller

4.1 Fast Button and Function Hot Key Events

When a fast button or a combination function hot key (Fn + Fxx) is being pressed, the

EC asserts ECSCI# pin to notify VT8231 south bridge if the system is full on. In turn,

it may generate a SMI event in APM and legacy PM mode or a SCI event in ACPI

mode. The system BIOS could setup the EC to report the notification byte via KBC

host interface in APM / legacy PM mode and read the notification byte by using KBC

extend command 0xCD. To support ACPI-enabled O.S., the system BIOS should

setup the EC to report the notification byte via ACPI EC host interface to allow O.S.

to read the notification by using EC query command 0x84. If the system is at suspend

- 13 -

Page 16

B1A Internal BIOS Specification

sate, the EC asserts SMI# to VT8231 for waking up system when a fast button is

pressed. Then it asserts ECSCI# for notifying O.S. or BIOS the fast button event after

the system is back to full on sate. The notification values of fast buttons, function hot

keys and other events are listed in table 12.

Table 12. Event Notification Bytes

Notification Byte Event

0x00 Reserved

0x01 Fast Button (Hot Key) #1: M-Mode

0x02 Fast Button (Hot Key) #2: E-mail

0x03 Fast Button (Hot Key) #3: Internet

0x04 Fast Button (Hot Key) #4: Defined by Users

0x05 Fast Button (Hot Key) #5: Defined by Users

0x06 Reserved

0x07 Reserved

0x08 KBC Wake Up Event

0x09 Reserved

0x0A Fn + F1: Suspend

0x0B Fn _ F2: NOT USED

0x0C Fn + F3: S1 (defined by users)

0x0D Fn + F4: S2 (defined by users)

0x0E Fn + F5: Brightness Up

0x0F Fn + F6: Brightness Down

0x10 Fn + F7: LCD Display Only

0x11 Fn + F8: LCD and CRT Display

0x12 Fn + F9: TV Display Only

0x13 Fn + F10: Mute

0x14 Fn + F11: Volume Up

0x15 Fn + F12: Volume Down

0x16 AC is plugged in or unplugged

0x17 Battery is plugged in or unplugged

0x18 Battery WARNING (Remaining Capacity / Full Charge Capacity

= 10%)

0x19 Battery LOW (Remaining Capacity / Full Charge Capacity =

5%)6

6

If a system is in suspend mode, the EC should trigger resume event first and then notify the system

after it’s full on.

- 14 -

Page 17

B1A Internal BIOS Specification

0x1A Crossing thermal trip point

0x1B Critical shutdown

0x1C ~ 0x1F Reserved

0x20 SMBus Event

4.2 Power Management Events

The power management events triggered by EC are summarized in table 13.

Table 13. Power Management Event of EC

Source Full On S1/S2 S3/S4/S5

Power Button SCI / SMI7 Resume Resume

Modem Ring X Resume Resume

CPU Temperature SCI / SMI X X

Fast Button SCI / SMI Resume Resume

PCI PME# X Resume Resume

Any Key X Resume X

Fn + F1 (Suspend) SCI / SMI X X

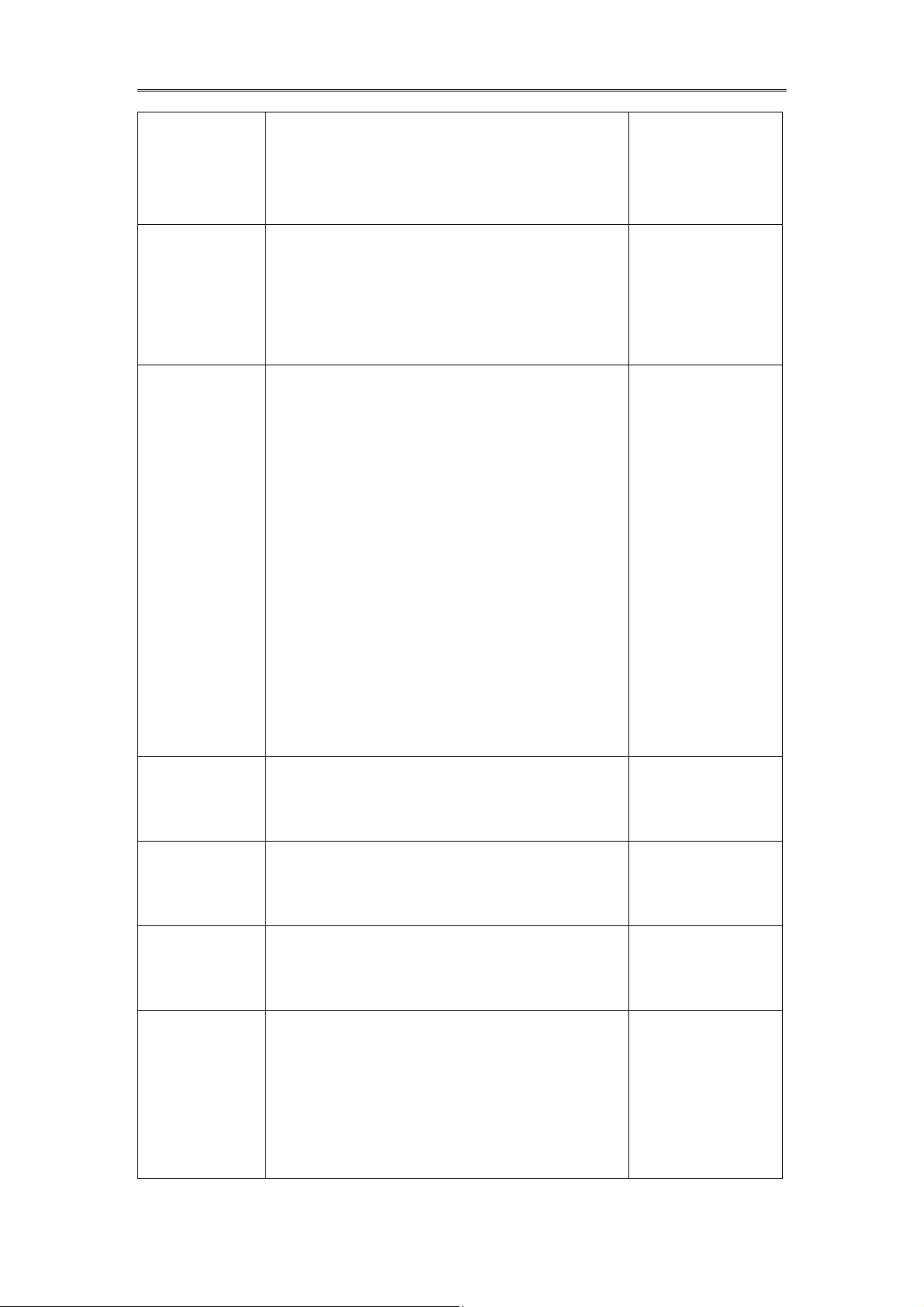

4.2.1 Thermal Control

When the measured CPU temperature is over the setting value of CPU-throttling

temperature, the EC asserts IOPI5 to raise a thermal event for automatically doing

CPU throttling. As well, it asserts ECSCI# pin and reports “crossing trip point” or

“critical shutdown” notification byte to system BIOS or ACPI-enabled O.S. if the

measured CPU temperature is:

Increasing over the CPU-throttling, CPU fan spin-up and critical shutdown

temperature settings.

Decreasing below the CPU-throttling, CPU fan spin-down and critical shutdown

temperature settings.

The EC should continuously measure the CPU temperature at least 5 times in 5

seconds and confirm that the absolute difference value of any two consecutive CPU

temperatures measured is less than or equal to 3 Celsius degrees before proceeding to

do further thermal control. The thermal control algorithm is shown in figure 2. The

cooling policy is PASSIVE (or ACTIVE) if the CPU-throttling temperature setting is

7

SCI in ACPI mode or SMI in APM (legacy PM ) mode.

- 15 -

Page 18

B1A Internal BIOS Specification

less (or greater) than the CPU fan spin-up temperature settings. The default thermal

policy of EC is passive. The figure 3 shows the scale diagram of default temperature

settings.

- 16 -

Page 19

B1A Internal BIOS Specification

Figure 2. Thermal Control Algorithm of EC

- 17 -

Page 20

B1A Internal BIOS Specification

Temperature (℃)

Critical 90

1st fan spin-up (ON) 65

60 1st fan spin-down (OFF)

Throttling 50

Figure 3. Temperature Settings of Default Passive Cooling Policy

4.3 LED Control

The LED control states are shown in table 14.

Table 14. LED Control States

LED Color System State LED State Action

AC /

Battery

Power

State

System

State

Activity

Green /

Orange

Green

Green

AC Battery Green

Plugged No Charging OFF IOPH7=1

Plugged Charging ON IOPH7=0

Unplugged Discharging OFF IOPH7=1

Unplugged Battery Low Flash IOPH7=1

System Off OFF Auto

System On On Auto

STR Flash Auto

Accessed ON Auto HDD

Not Accessed OFF Auto

Get New E-mail(s) ON IOPH5=0 E-mail Green

No New E-mail OFF IOPH5=1

Progressing ON IOPH3=0 M-Mode Orange

Normal OFF IOPH3=1

Green

Mute

NUM Green Locked ON IOPH1=0

Mute ON IOPH4=0 Vo l u m e

Normal OFF IOPH4=1

- 18 -

Page 21

B1A Internal BIOS Specification

Lock Unlocked OFF IOPH1=1

Lock

Lock

Green

Green

Locked ON IOPH0=0 CAPS

Unlocked OFF IOPH0=1

Locked ON IOPH2=0 Scroll

Unlocked OFF IOPH2=1

5. M-Mode Control Mechanism

The implementation algorithm of M-Mode is:

(1) M-mode button is pressed.

(2) EC asserts ECSCI# pin to VT8231 for triggering a SMI event in APM mode or

SCI event in ACPI mode.

(3) The system BIOS or O.S uses SCI query command 0x84 to get SCI

notification byte.

(4) The system BIOS or ASUS’s proprietary application (ACPI mode) put the

system into power-on-suspend (POS) or S1 state.

(5) After seeing SUSA# is asserted, the EC read back the setting value of clock

generator. Then the EC update the host clock setting to 66 MHz (or 133MHz)

if the current CPU host clock is 133 MHz (or 66 MHz) and write it back to

clock generator.

(6) The EC reprogram the PCA9559 I2C EEPROM to set VID based on the new

CPU frequency accordingly.

(7) The EC asserts SMI# pin to wake up system.

6. Power Management

The system BIOS supports legacy PM (power management), APM, and ACP power

management modes. The legacy PM mode implements all power states same as APM

does and is for operating systems that don’t have built-in APM and ACPI functions

such as Windows NT 4.0.

In B1A platform, the EC asserts ECSCI# pin connected to GPI0 of VT8231 for

triggering run time events and SMI# pin connected to EXTSMI# of VT8231 for

triggering resume event. The run time event could be SCI or SMI depending on the

setting of SCI enable bit, SMI enable bit and the general purpose SCI/SMI enable bits

of GPI0 and EXTSMI# pins in power management I/O control registers.

- 19 -

Page 22

B1A Internal BIOS Specification

6.1 APM and Legacy PM

In APM and legacy PM modes, the system BIOS implements full on, standby,

suspend-to-RAM (STR), suspend-to-disk (STD), and soft off power states. The

transitions among these power states described in the table 15 and 16.

Table 15. Suspend Transitions of APM Power States

Current State Next State Trigger Event

Full On Standby General-purpose timer 0 expires.

Full On STR “Suspend” function hot key Fn+F1 is pressed.

Full On STD Battery LOW.

Full On Soft Off Power button is pressed

Standby STR General-purpose timer 0 expires.

Standby STD Battery LOW.

STR STD General-purpose timer 0 expires.

Battery LOW

Table 16. Resume Transitions of APM Power States

Resume Event Standby

-> On

IRQs Y

USB Peripheral Y

AC ’97 Devices

RTC Alarm (IRQ 8) Y Y

Power Button Y Y

RI# Input (CardBus Slot) Y

RI# Input (COM & Mini PCI Slot) Y Y

PME# Y Y

EXTSMI# Y

General-Purpose Timer 0 Y Y

Battery Low Y Y

STR ->

On

STD/Soff

-> On

LID (DISABLED)

Thermal Status (DISABLED)

6.1.1 Common Settings

(Programming information will be described.)

- 20 -

Page 23

B1A Internal BIOS Specification

6.1.2 Full On Sate

(Programming information will be described.)

6.1.3 Standby Sate

(Programming information will be described.)

6.1.4 Suspend To RAM Sate

(Programming information will be described.)

6.1.5 Suspend To Disk Sate

(Programming information will be described.)

6.2 ACPI

The system BIOS declares that the B1A system supports C0, C1, C2, and C3 CPU

device power states and S0, S1, S3, S4BIOS, S4, and S5 system power states in

DSDT and FACP tables. In ACPI-enabled O.S, all suspend and resume conditions are

determined by O.S. The BIOS uses _PRW name objects to report that the RI#, PME#,

and EXTSMI# (control method sleep button) can resume the system from power

suspend states. The possible resume events are listed in table 17.

Table 17. Possible Resume Events in ACPI mode

Resume Event S1 S3 S4 /

S4BIOS

RTC Alarm (IRQ 8) Y Y Y Y

S5

Power Button Y Y Y Y

LID (NO _PRW name object) Y

RI# Y Y Y Y

PME# Y Y Y Y

EXTSMI# (control method sleep

button)

Y Y

- 21 -

Page 24

B1A Internal BIOS Specification

6.2.1 ACPI-Enabling Initialization

(Programming information will be addressed.)

6.2.2 ACPI-Disabling Initialization

(Programming information will be addressed.)

6.2.3 Thermal Control

(Programming information will be addressed.)

6.2.4 Control Method Battery

(Programming information will be addressed.)

6.2.5 Control Method Sleep Button

(Programming information will be addressed.)

6.2.6 Methods for Proprietary On-Screen Display Utility

ASUS has developed a proprietary on-screen display utility for:

Displaying volume- / brightness-changing bars.

Running a web browser or an application program by pressing a fast button.

Turning on E-mal LED when a new E-mail is coming.

Please refer to the specification defined by software team of R&D 3 Notebook

department.

7. Callback Services for nVidia’s VGA BIOS

The system BIOS should support callback services to process INT 15h with AX=5Fxx

- 22 -

Page 25

B1A Internal BIOS Specification

run time BIOS calls for:

Reporting LCD panel ID, TV setting, boot display device, and screen position

information to VGA BIOS at POST.

Bypassing a VGA BIOS run time function call or doing some settings right

before or after the function call.

Please refer to the “S3 VGA BIOS Programmers Guide” for details. The assignment

of LCD panel IDs for B1A is shown in table 18.

Table 18. LCD Panel ID List

LCD Panel Model PANEL_ID[1:0] Panel ID

??? [0:0] 0x0F

??? [0:1] 0x0B

TFT 1024*768 [1:0] 0x07

??? [1:1] 0x00

8. Clock Generator Setting

To reduce system EMI, the unused clocks should be turned off and the spread

spectrum must be enabled. The configuration setting of ICS9248-151 clock generator

for B1A platform at POST is described in table 19.

Table 19. Configuration Setting of Clock Generator

Byte Value Description

0 0x8E (1) Frequency is selected by software.

(2) Enable spread spectrum.

(3) Spread spectrum = 0 ~ –0.5% down spread

1 0xF9 Disable CPUCLK2 & CPUCLK1

2 0x9F Disable PCICLK5 & PCICLK6.

3 0xF0 Disable SDCLK4~7

4 Reserved

5 0xFB Disable 24MHz ( pin25 )

To set new frequency for M-Mode, the possible value of byte 0 is listed in table

below.

- 23 -

Page 26

B1A Internal BIOS Specification

Table 20. Byte 0 Setting Value of Clock Generator for M-Mode

Value CPUCLK

(MHz)

0x8E 100.00 33.33 14.318 0 ~ –0.5%

0x8A 66.67 33.33 14.318 0 ~ –0.5%

PCICLK

(MHz)

IOAPIC

(MHz)

Spread

Percentage

9. Setup Menu

TBD.

10. Reference

TBL.

- 24 -

Loading...

Loading...