Page 1

5

4

3

2

1

D D

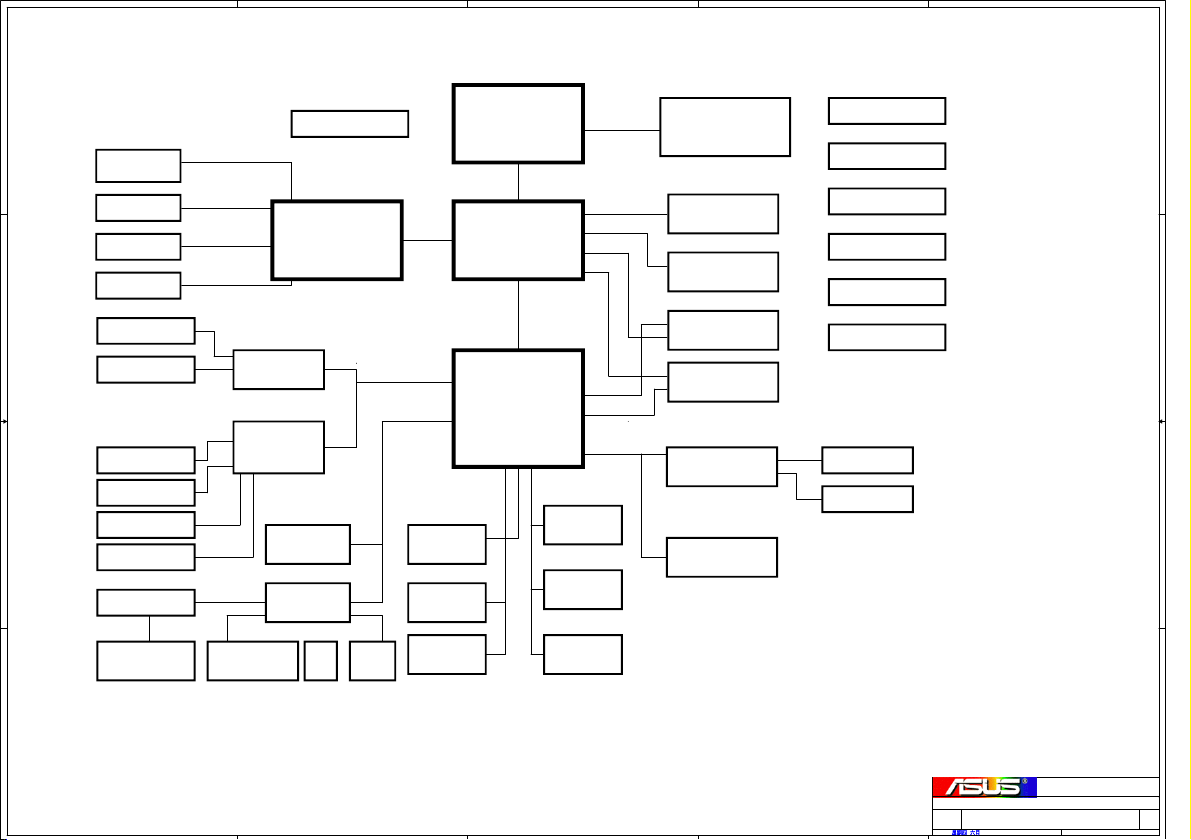

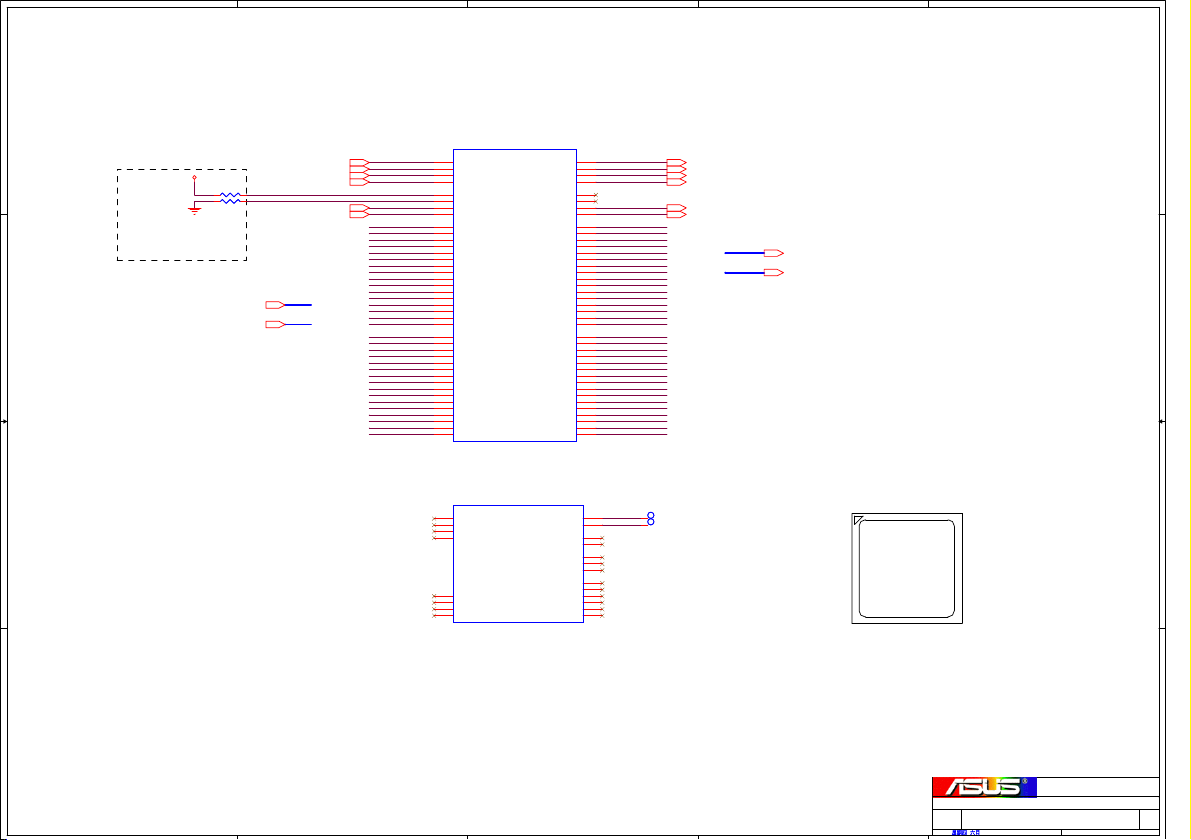

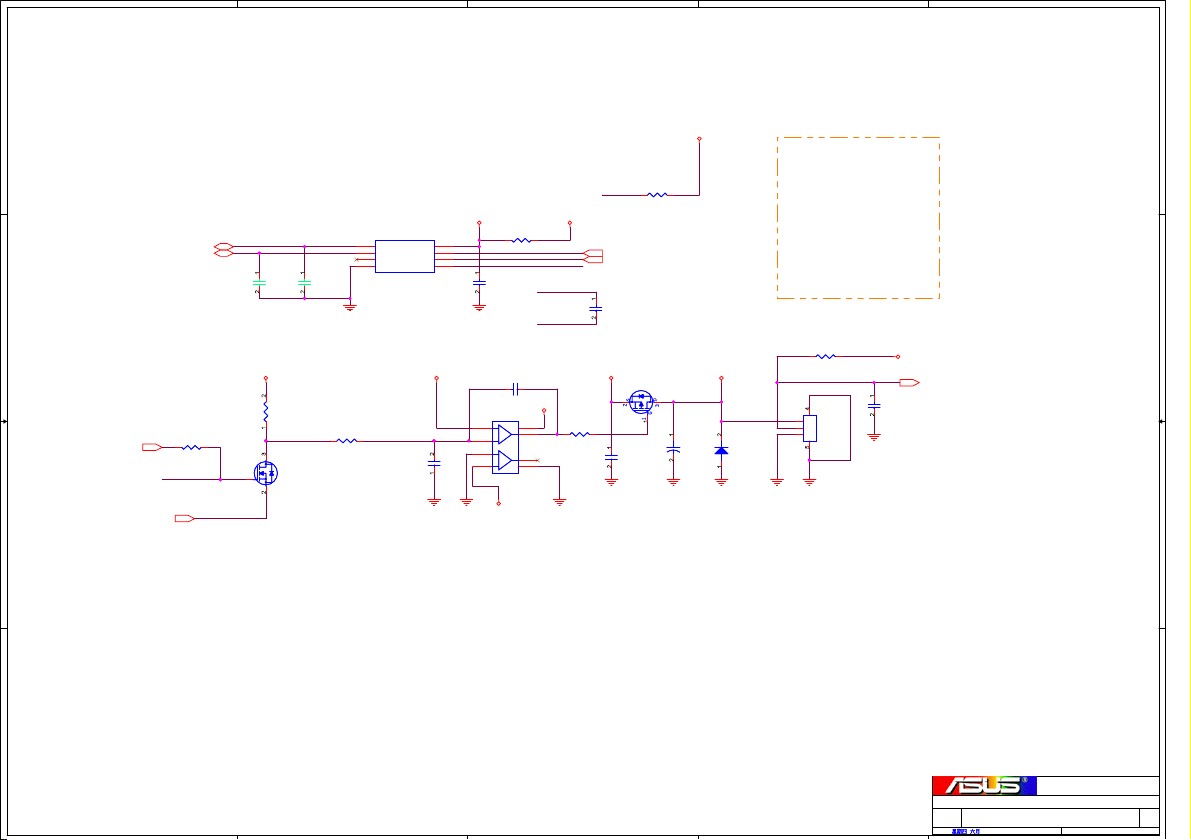

LVDS & INV

PAGE 22

CRT

PAGE 23

TV OUT

PAGE 23

DVI

C C

B B

PAGE 24

CIR

PAGE 37

SIR

PAGE 37

KEYPAD

MATRIX

PAGE 29

INSTANT KEY

PAGE 50

LED

PAGE 50

ISA

ROM (8MB)

PAGE 29

AMPLIFIER

PAGE 31

SPEAKER or

PHONE JACK

PAGE 31

SUPER I/O

ITEIT8712F_IX

PAGE 37

EC IT8511E

MIC AND LINE IN

PAGE 32

CPU VCORE

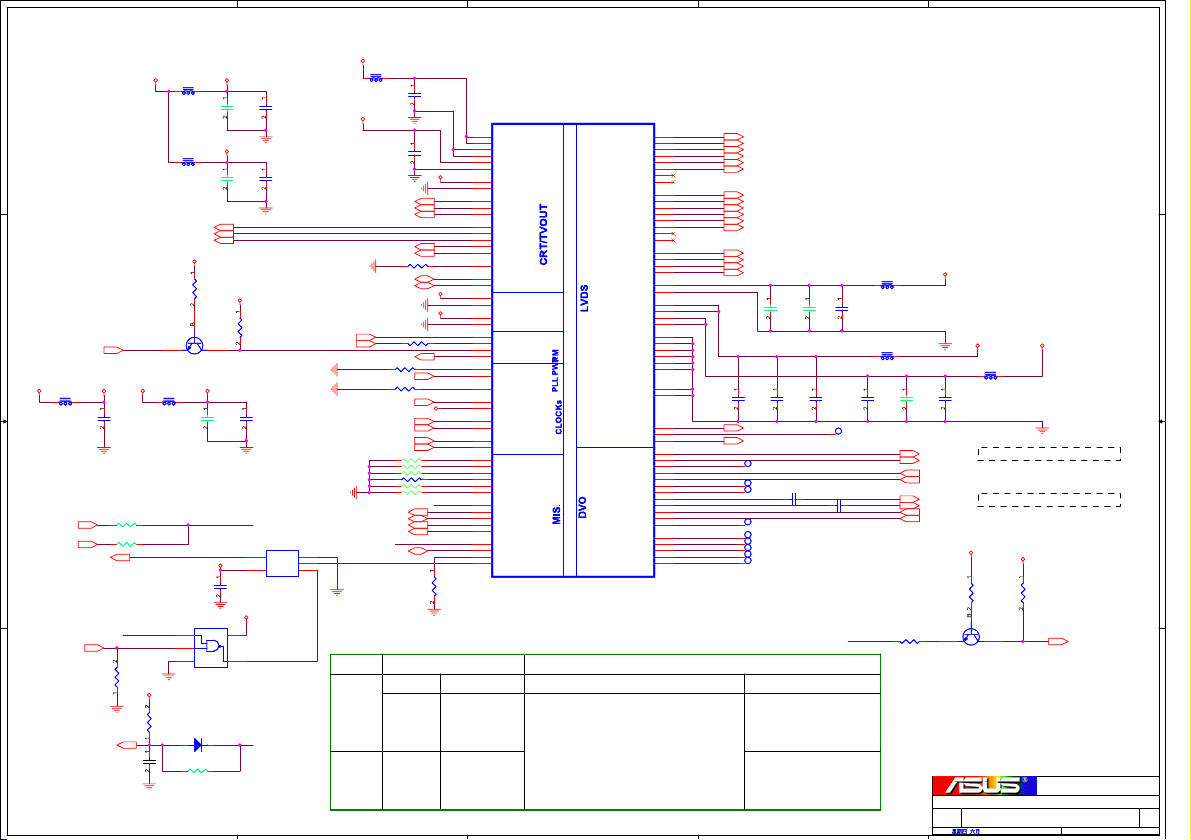

ATI

M76-M

PAGE 28 29

MDC Conn

(RJ11)

PAGE 34

Azalia Codec

ALC 660

PAGE 30

DSP

PAGE 33

SPDIF

PAGE 31

LPC

33MHz

PCIE *16

Azalia

SATA HDD

PAGE 35

PAGE 35

PAGE 35

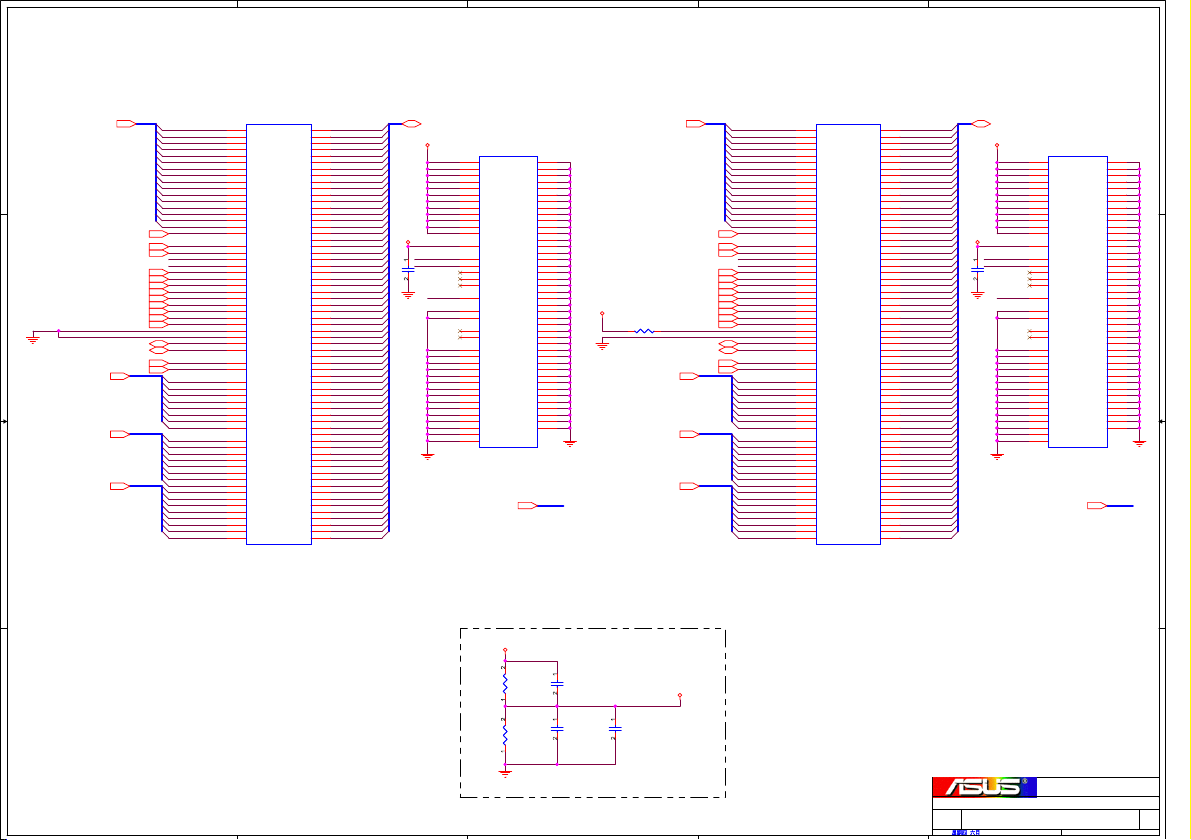

%/&PSGO(MEKVEQ

HDD

ODD

PAGE 56 7 8

PAGE 11 12 1314

PAGE 17 18 1920

AMD

REV.F

H.T 800 MHz

1600MT/s

ATI

RS690M

ALINK

4LANE

ATI

SB600

USB

PAGE 36

PAGE 36

PAGE 22

DDR2-800MHz

PCIE *1

PCIE *1

PCIE *1

PCIE *1

USB 2.0

CON X5

Bluetooth

USB

Camera

USB

USB

USB

PCI 33MHz

Dual Channel DDR2

SO-DIMM X 2

Up to 2GB DD RII

PAGE 91 0

MINI-PCIE

TV Card

PAGE 40

JMB360

e-SATA

PAGE 49

MINI PCIE

WLAN

PAGE 26

NEW CARD

PAGE 27

CardBus

R5C833

PAGE 38

PCI LAN

PAGE 25

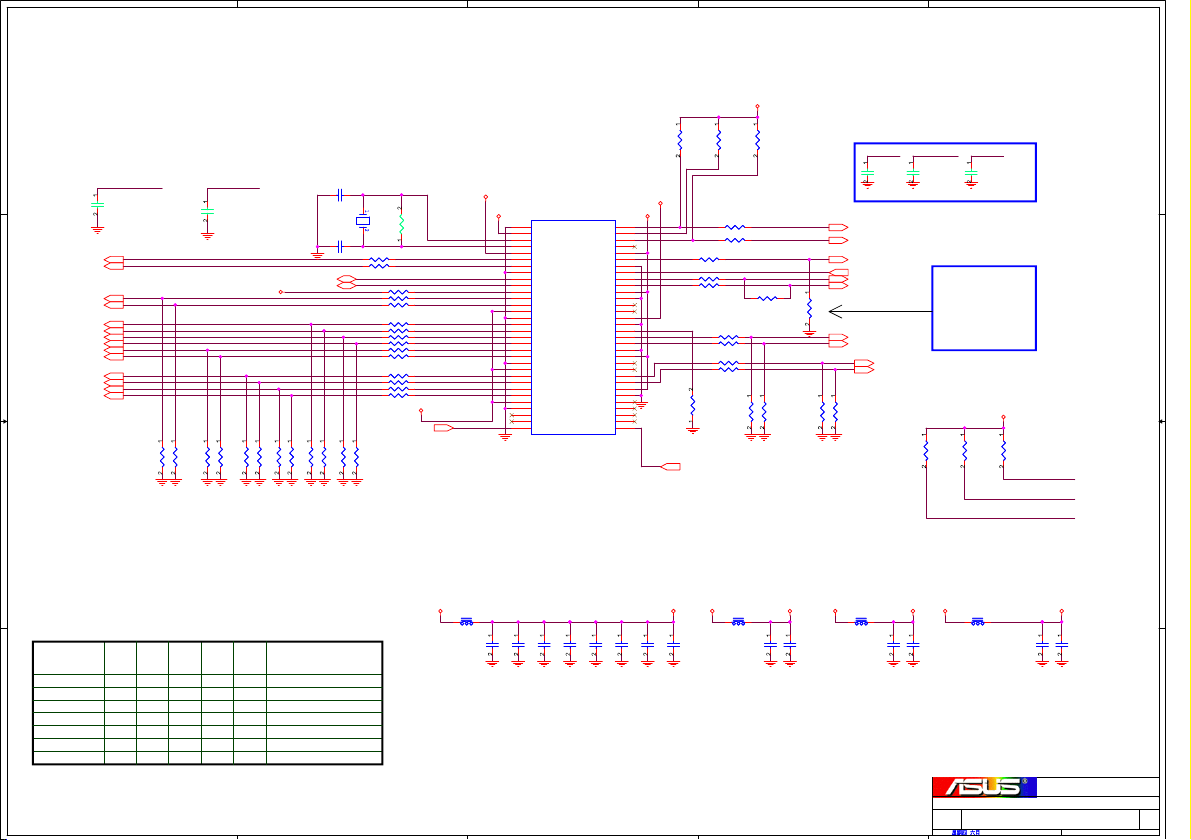

CLOCK GE NERATOR

PAGE 16

LED&SW&T OUCHPAD

PAGE 50

FAN + SENSOR

PAGE 21

DISCHARG E CIRCUIT

PAGE 52

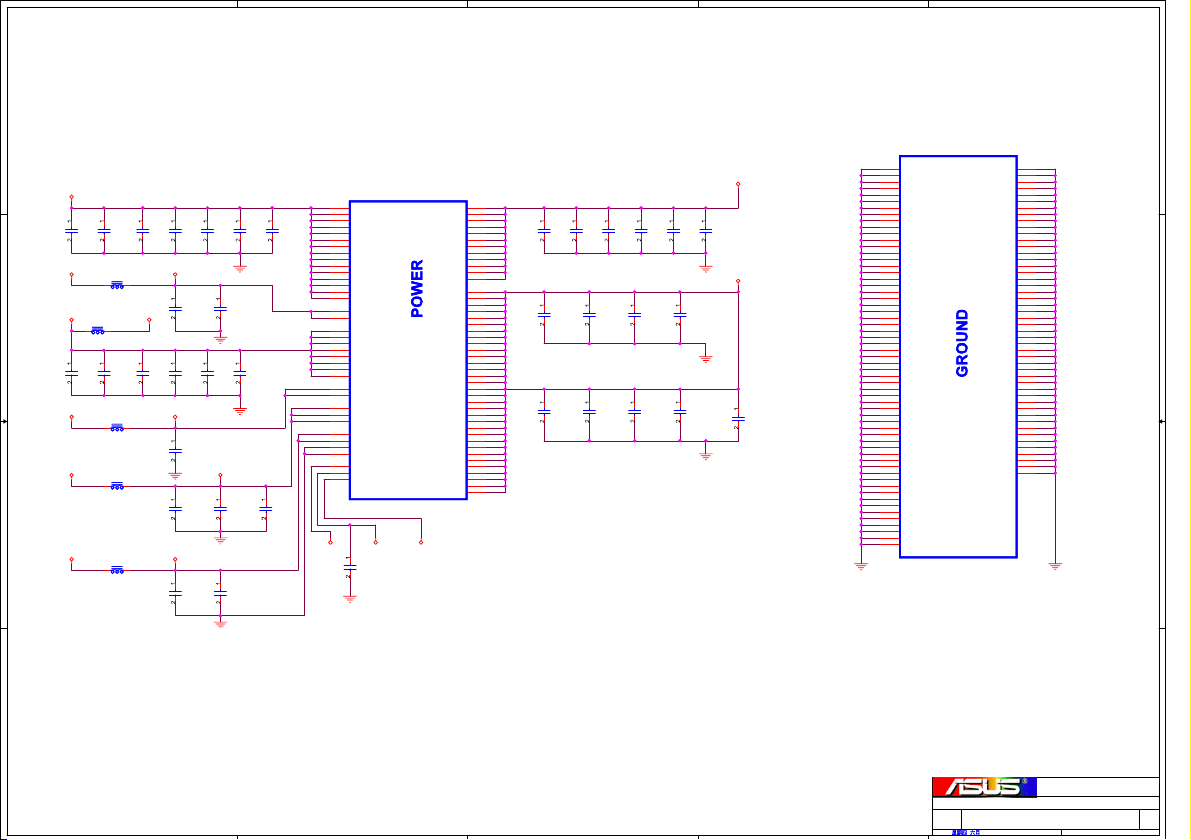

SYSTEM PWR

BAT & CHARGER

1394

PAGE 39

4 in 1

CARD REA DER

PAGE 39

MMC/SD

Memory

Stick/MS PRO

XD

A A

Title :

Title :

Title :

A7K

A7K

A7K

Endy Zhang

Endy Zhang

Endy Zhang

Engineer:

Engineer:

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

Block Diagram

Block Diagram

Block Diagram

Rev

Rev

Rev

2 0

2 0

2 0

1 69 14 2007

1 69 14 2007

1 69 14 2007

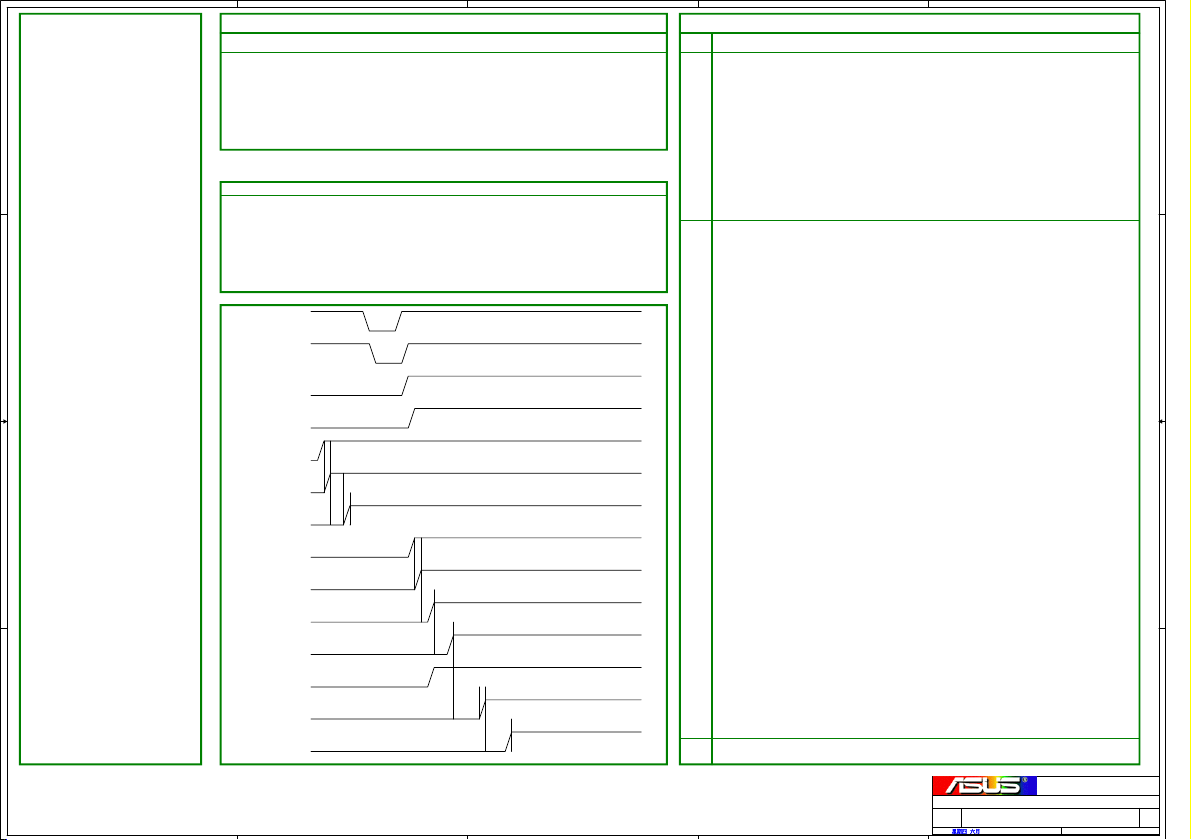

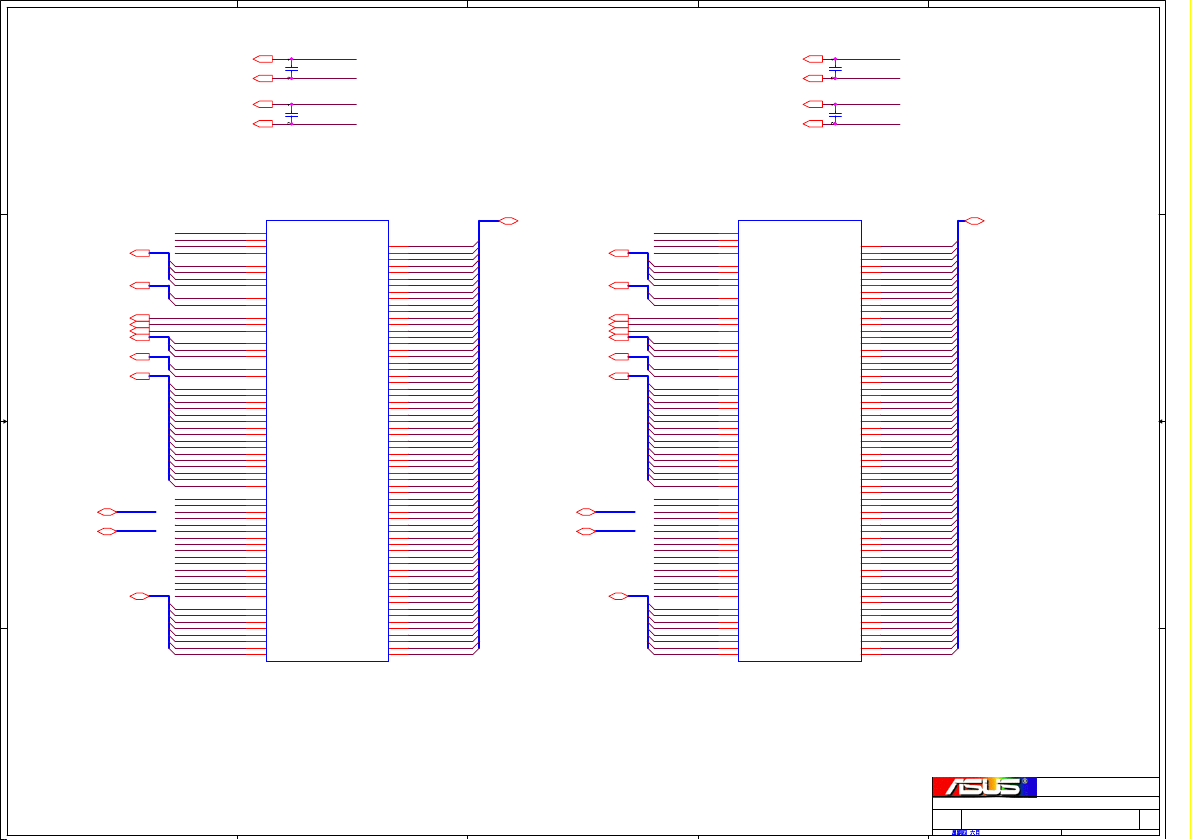

Page 2

5

P01.BALOCK DIAGRAM

P02.TABLE OF CONTENTS

P03.POWER BUDGET

P04.CLOCK DISTRIBUTION

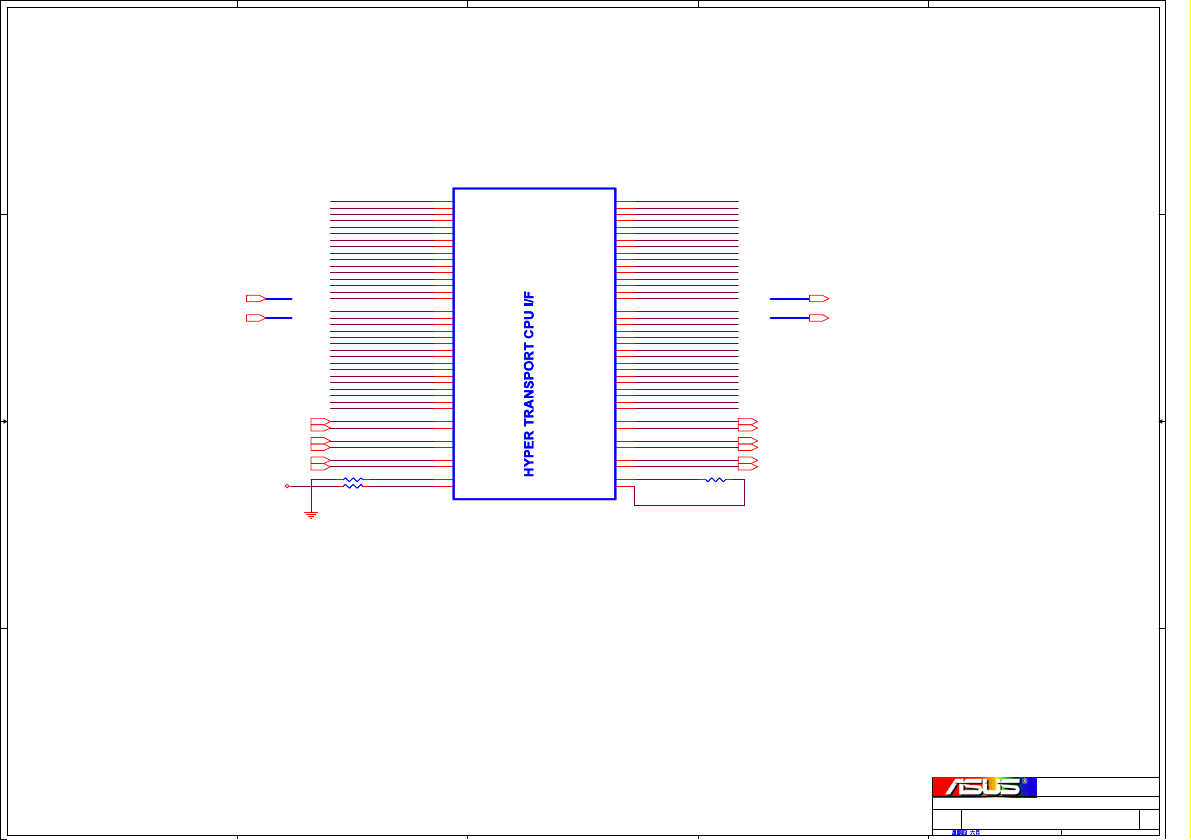

P05.TURION HT I/F

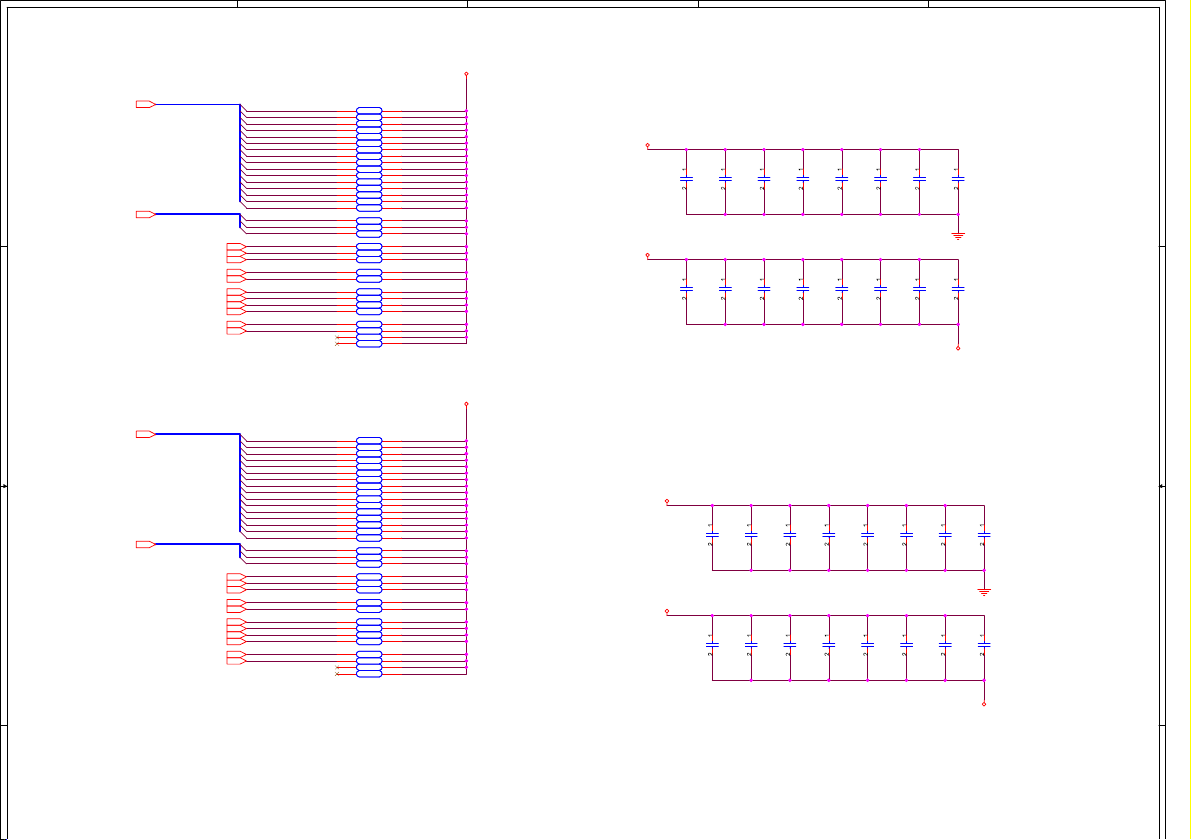

P06.TURION DDR2 MEMORY I/F

P07.TURION CNTL/DEBUG/THERM

P08.TURION POWER

P09.DDR2_SODIMM

P10.DDR2_TERMINATIONS

D D

P11.RS690M-HT LINK0 I/F

P12.RS690M-PCIE LINK I/F

P13.RS690M-SYSTEM I/F&CLKGEN

P14.RS690M-POWER

P15.BLANK

P16.EXTERNAL CLOCK GENERATOR

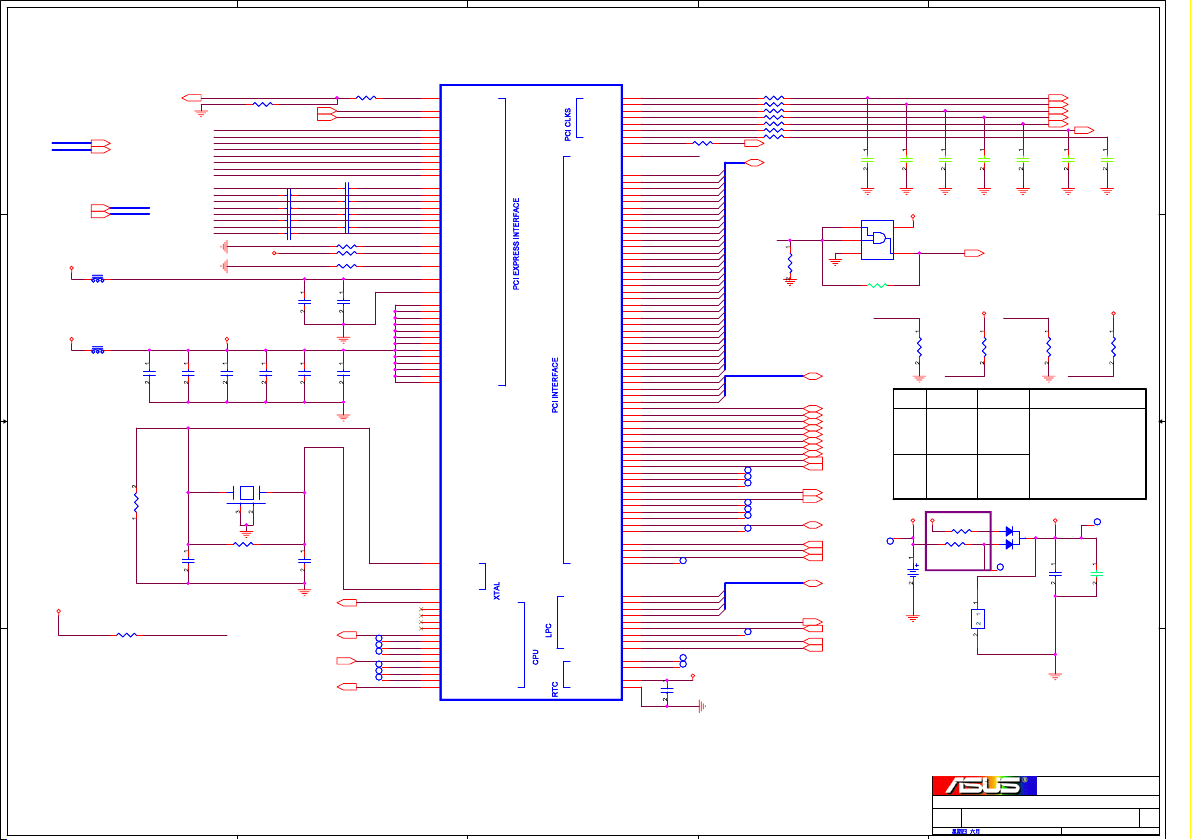

P17.SB600-PCIE/PCI/CPU/LPC

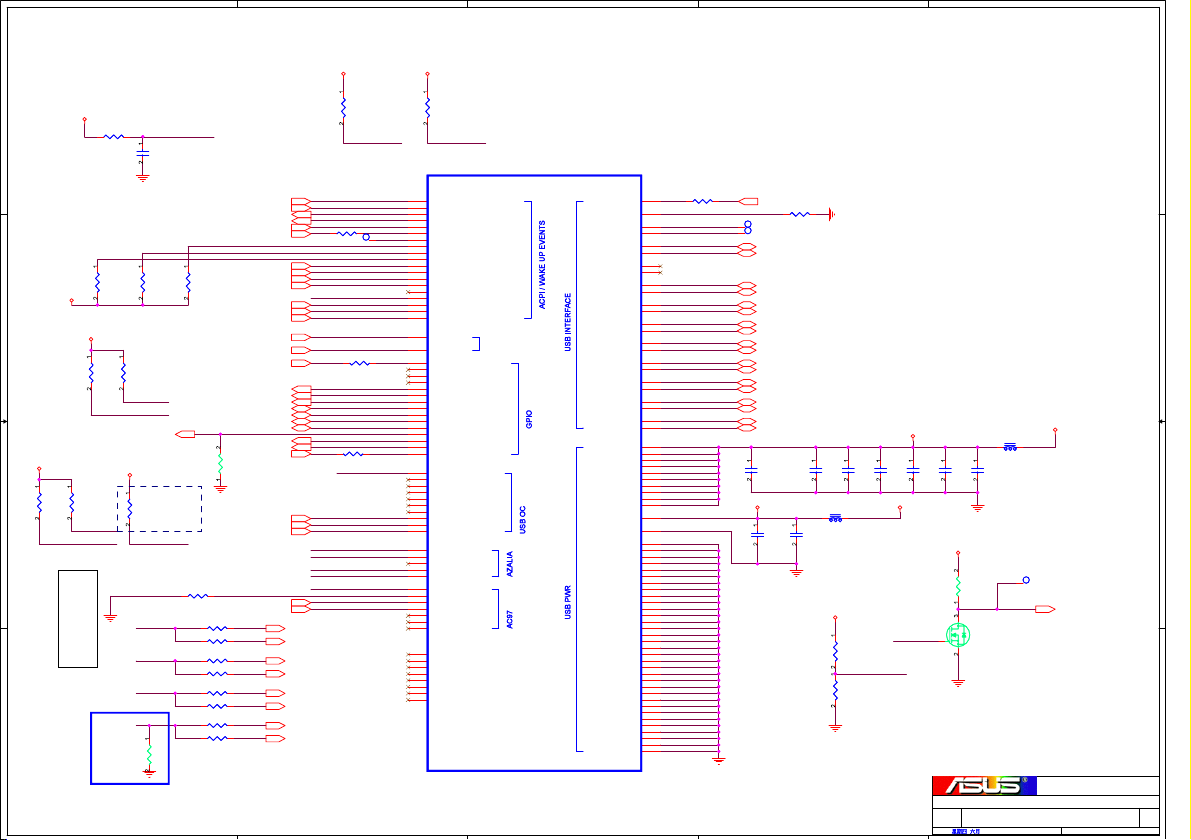

P18.SB600-ACPI/GPIO/USB/AC97/AZA

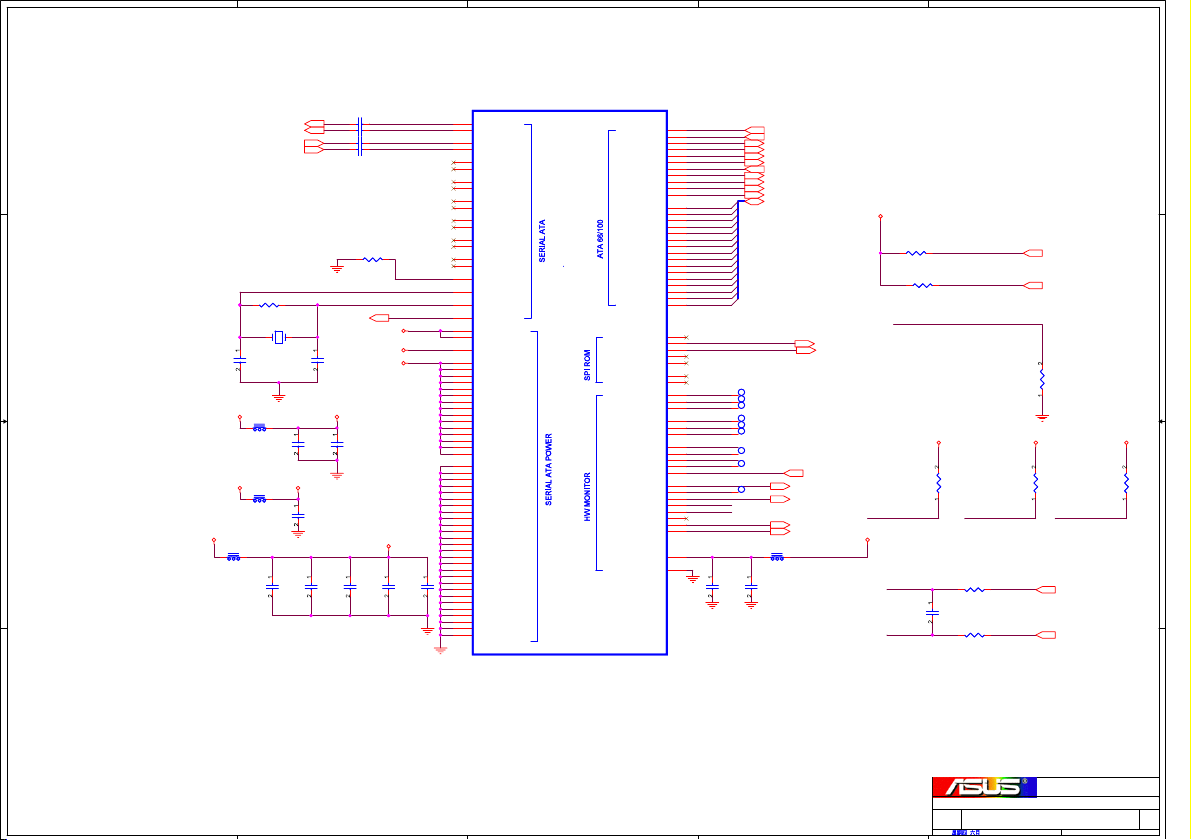

P19.SB600-SATA/IDE/HWM/SPI

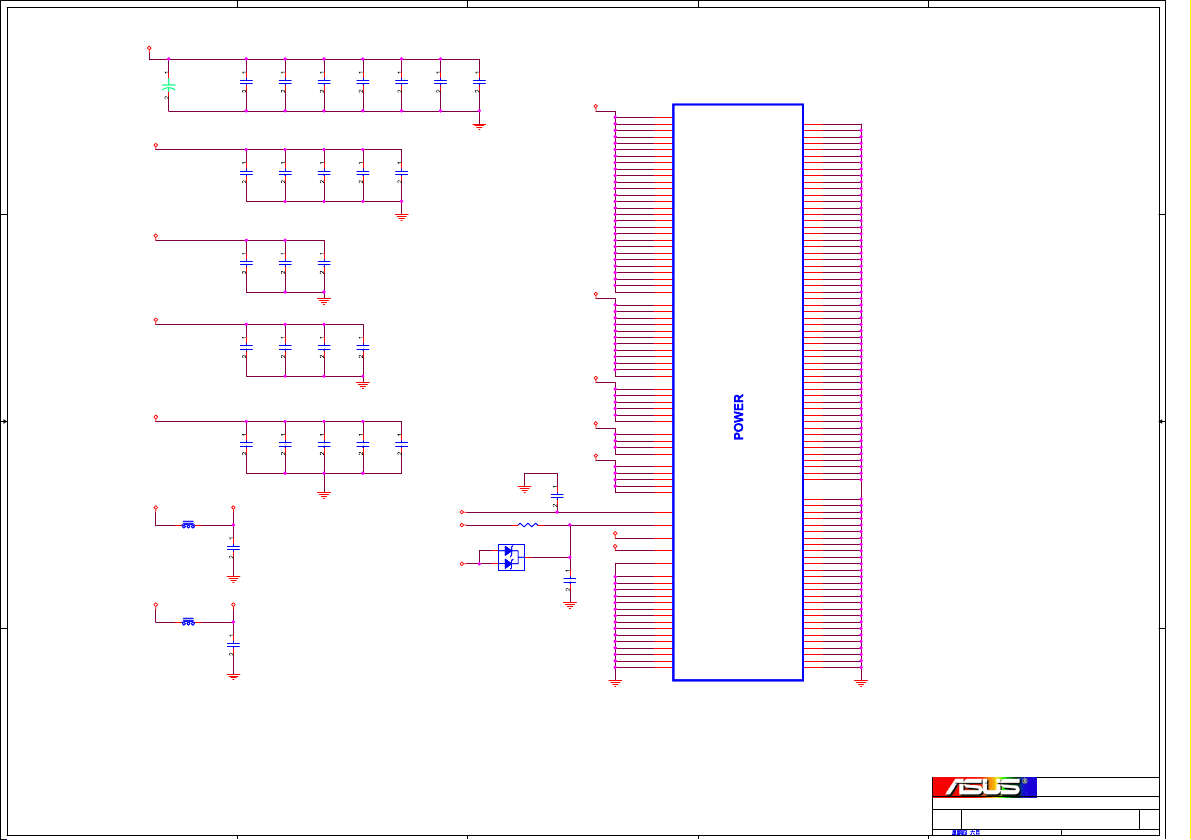

P20.SB600-POWER&DECOUPLING

P21.THERMAL FAN CONTROL

P22.LVDS AND INVERTER

P23.CRT AND TV CONNECTOR

P24.DVI

P25.PCI LAN

P26.MINI PCI-E WLAN

P27.NEW CARD

P28.EC IT8510TE(1/2)

P29.EC IT8510TE(2/2)-ISA ROM

P30.ALC660

P31.AMP AND HEADPHONE

P32.MIC AND LINE IN

C C

P33.DSP

P34.MDC

P35.HDD AND ODD

P36.USB CONNECTOR AND BT

P37.SIO AND SIR

P38.CARD BUS R5C832

P39.1394 AND CARD READER

P40.MINI PCI-E(TV)

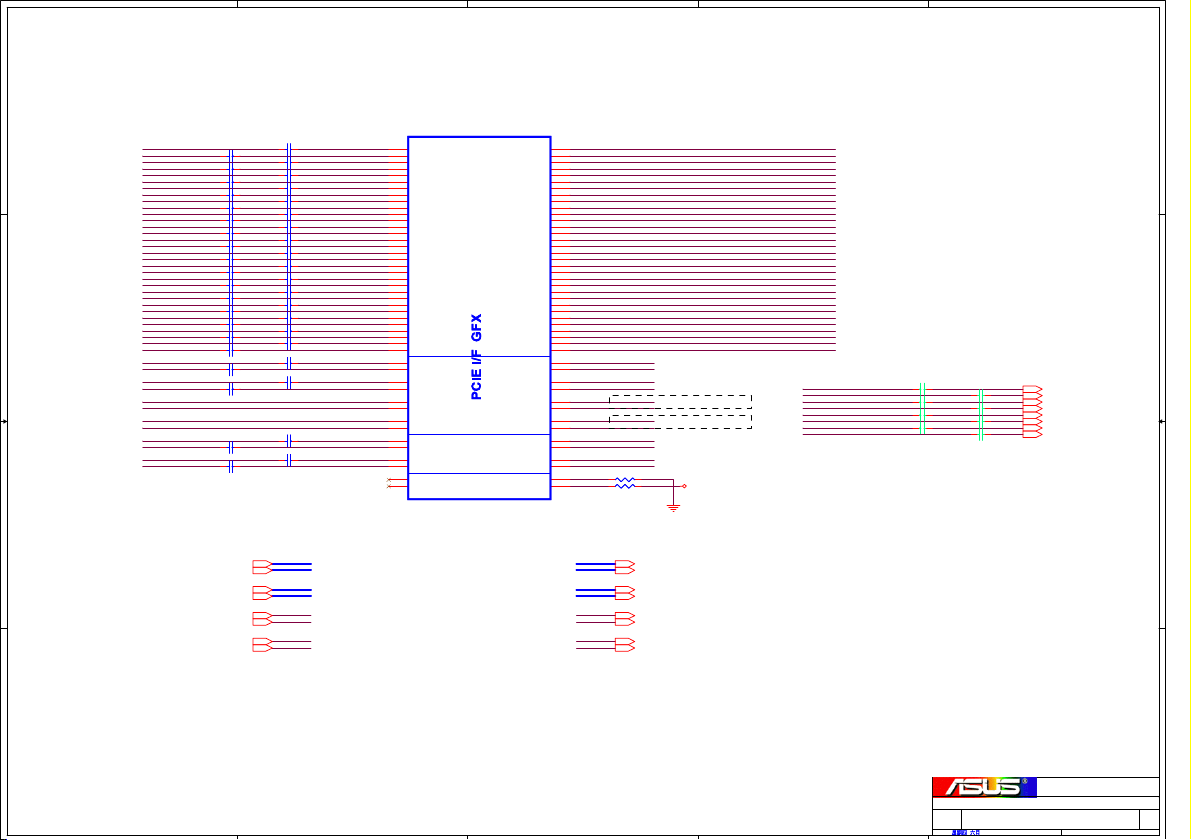

P41.M76(1/5)PCI-E I/F

P42.M76(2/5)DVI&DAC&DDC&PLL&VID

P43.M76(3/5)MEMORY I/F

P44.M76(4/5)BLANK

P45.M76(5/5)POWER

P46.GDDR2 MEMORY(1/2)

P47.GDDR2 MEMORY(2/2)

P48.BLANK

P49.BLANK

P50.FUNCTION KEY

P51.POWER SEQUENCE

P52.DISCHARGE

B B

PCI DEVICES IRQ TABLE

DEVICE

NB VGA

SB

ATA100

AC97/AZALIA

USB

CARD BUS

PCI LAN

SMBUS TABLE

SOURCE SIGNAL NAME LINKED DEVICES

NBSBDAC_SCL/DAC_SDAT CRT/LVDS

EC SMCLK0/SMDAT0 BATTERY

IDSEL# REQ/GNT# PCI INT CLOCK

N/A

AD31(INT)

AD31

AD31

AD30

AD17

AD18

I2C_CLK/I2C_DATA LVDS

I2C_CLK/DDC_DATA DVI

SCLK0/SDATA0

SCLK1/SDATA1

PWR_SW#

PM_PWRBTN#

PM_SUSB#

PM_SUSC#

SUSB_ON

SUSC_ON

+3VSUS

+1.2VSUS

PM_RSMRST#

V5_REF

+3VS

+1.2VS

+VCORE

VDDC_NB

NB_PWRGD

A A

SB_PWRGD

CPU_PWROK

4

N/A

A

N/AN/A

N/A

N/A

N/A

0

1

SO-DIMMs/CLK_GEN/DSP

MINI-PCIE(WLAN)/NEW CARD/MINI-PCIE(TV)

INT

A

B

INT

INT

D

PCI_CLK0

F,G

PCI_CLK1

E

THERMAL(CPU:98H GPU:4CH)SMCLK1/SMDAT1

T1

T2>20ms

T2A<50ms

T3

T4

T5

T6>15ms

T7=0

T7A

3

2

1

GPIO

STRP_DATA SEL_VCC_NB TUNE NB VOLTAGE OUTPUT

NB

RI#EXTEVNT0#

SB

LPC_PME#/GEVENT3#

LPC_SMI#/EXTEVNT1#

WAKE#/GEVENT8#

GPIO10

GPIO6

GPIO4

GPIO5

GPIO8

GPIO0

LLB#/GPIO66

TEMPIN0

TEMPIN1

GPIO11

GPIO12

GPIO64

ECSMI#/GPM0

EC

ECSCI#/GPD3

SM0

SM1

ADC0/GPK0

ADC2/GPK2

GPK4

GPK5

DAC0/GPJ0

DAC2/GPJ2

GPJ3

PWM1/GPA1

GPA4

GPA5

GPA6

GPA7

GPB0

GPB1

GPB7

GPC0

GPC3

GPC4

GPC5

GPC6

GPC7

RI1#/WUI0/GPD0

RI2#/WUI1/GPD1

GPD4

GPD6

GPE0

GPE1

GPE2

GPE3

PWRSE/GPE4

GPE6

GPE7

PS2CLK2/GPF4

PS2DAT2/GPF5

GPF6

GPF7

GPG4

GPG6

GPG7

GPH0

GPH1

GPH2

GPH3

GPH4

GPH5

GPH6

GPH7

GPI1

GPI3

GPI4

GPI5

GPI6

TBD

PME# LCP_PME# PME TO SB OUTPUT

SIO

KB_SCI#

LPC_PME#

LPC_SMI#

SB_WAKE#

BT_DET#

BT_LED_EN#

802_LED_EN#

CB_HWSUSPEND

BT_ON#

WLAN_ON#

BAT_LL#

CPU_THRM

NB_THERM

SB_THRO_CPU

TV_ON#

PM_THERM#

EXSMI#

EXT_SCI#

SM_BAT

SMB1

BATO_AD

AC_AD

KID0

KID1

FAN_DA

BRIGHT_PWM

BATSEL_2P#

FAN_PWM

CHG_LED_UP#

PWR_LED_UP#

BATSEL_3S#

BACK_OFF#

NUM_LED

CAP_LED

THRO_CPU

DJ_LED#

EMAIL_LED#

ACIN_OC#

OP_SD#

BAT_IN_OC#

EC_IDE_RST#

PM_SUSB#

PM_SUSC#

RF_OFF_SW#

FAN0_TACH

EMAIL_SW#

NTERNET#

MARATHON#

DISTP_SW#

PWRSW#_EC

LID_EC#

BT_ON#

TPAD_CLK

TPAD_DAT

PWRLMT#

DJSW#

THRM_CPU

PMTHERM#

AC_APR_UC#

VSUS_ON

VSUS_GD_EC#

MVPOK#

PM_PWRBTN#

SUSC_ON

SUSB_ON

CPU_VRON

PM_RSMRST#

WATCH_DOG#

CHG_EN#

PRECHG

BAT_LL#

BAT_LEARN

KEYBOARD SCI

PME FROM SIO

SMI FROM EC

PCI E WAKE

BLUETOOTH DETECT

BLUETOOTH LED

WIRELESS LAN LED

CARDBUS SUPEND

BLUETOOTH ENABLE(OP TION)

WIRELESS LAN ENABLE

BATTERY LOW(OPTION )

CPU TEMPERATURE(OP TION)

NB TEMPERATURE

CPU OVER TEMP AND S HUT

TV ENABLE

THERM ALERT FROM E C

SMI TO SB

SCI TO SB

SMBUS TO BATTERY

SMBUS TO THERMAL

BATTERY VOLTAGE

AC ADAPTER VOLTAGE

KEYBOARD ID0

KEYBOARD ID1

FAN CONTROL(OPTION)

LCD BRIGHT CONTROL

2P BATTERY

FAN CONTROL

CHARGE LED

POWER LED

3S BATTERY

LCD BACK OFF

NUM LOCK LED

CAP LOCK LED

CPU OVER TEMP AND S HUT

AUDIO DJ LED

EMAIL LED

ADAPTER IN

AUDIO SHUTDOWN

BATTERY IN

EC CONTROL IDE RST

SB SUSB# IN

SB SUSC# IN

RF SWITCH OFF

FAN TACH

EMAIL SWITCH

INTERNET SWITCH

POWER GEAR

DISABLE TOUCHPAD

POWER SWITCH

LID STATUS IN

BLUETOOTH ENABLE

TOUCHPAD CLK

TOUCHPAD DATA

POWER LIMIT

DJ SWITCH

ALERT FROM THERMAL I C

THERM ALERT TO SB

ADAPTER POWER OK

ENABLE VSUS POWER

VSUS OK

CPU POWER OK

PWRBTN TO SB

SUSC ON

SUSB_ON

ENABLE VCORE

SB RSUMRESET

WATCH_DOG CONTROL FAN

ENABLE CHARGE

BATTERY PRECHARGE

BATTERY LOW

BATTERY LEARN

INPUT

INPUT

INPUT

INPUT

INPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

INPUT

OUTPUT

OUTPUT

INPUT

OUTPUT

OUTPUT

INPUT

INPUT

INPUT

INPUT

OUTPUT

OUTPUT

INPUT

OUTPUT

OUTPUT

OUTPUT

INPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

INPUT

OUTPUT

INPUT

OUTPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

INPUT

OUTPUT

OUTPUT

INPUT

INPUT

OUTPUT

INPUT

OUTPUT

INPUT

INPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

Title :

Title :

Title :

A7K

A7K

A7K

Engineer:

Endy Zhang

Engineer:

Endy Zhang

Engineer:

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Table of Contents

Table of Contents

Table of Contents

Date: Sheet of

Date: Sheet of

Date: Sheet of

Endy Zhang

2 69 14 2007

2 69 14 2007

2 69 14 2007

Rev

Rev

Rev

2 0

2 0

2 0

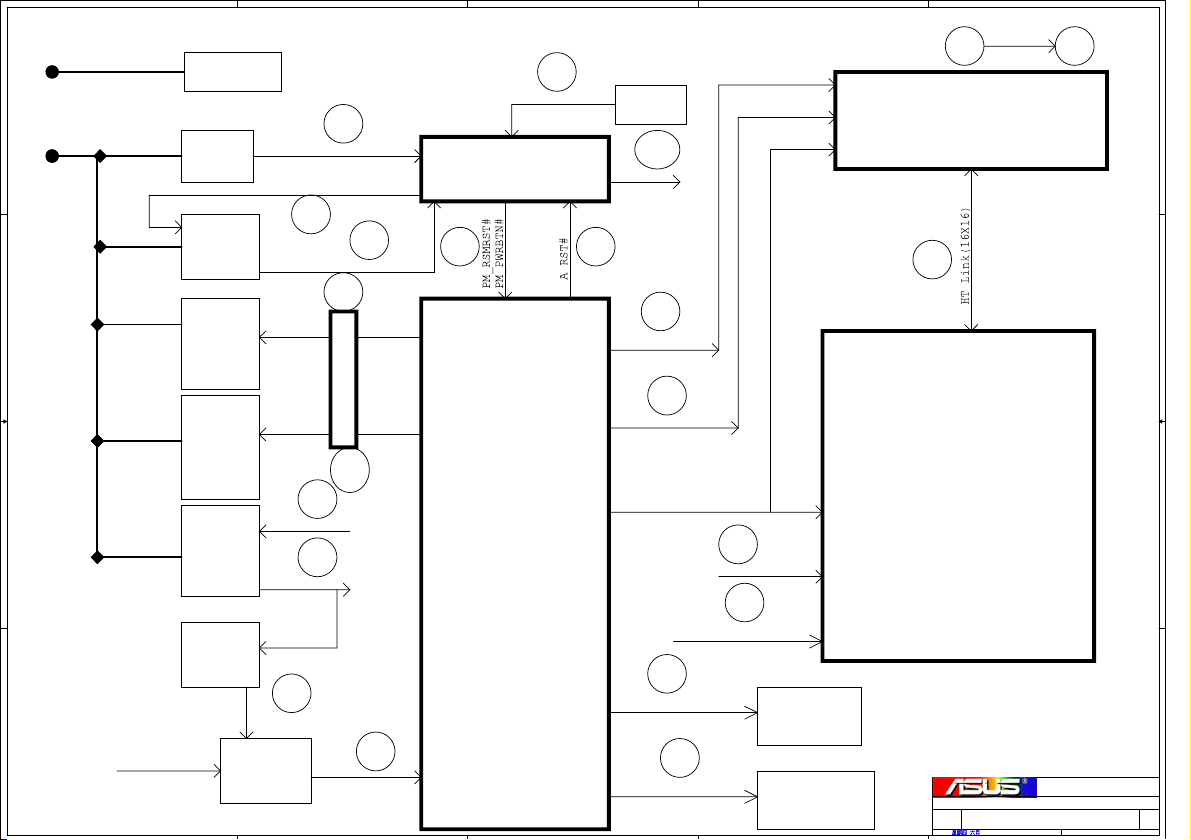

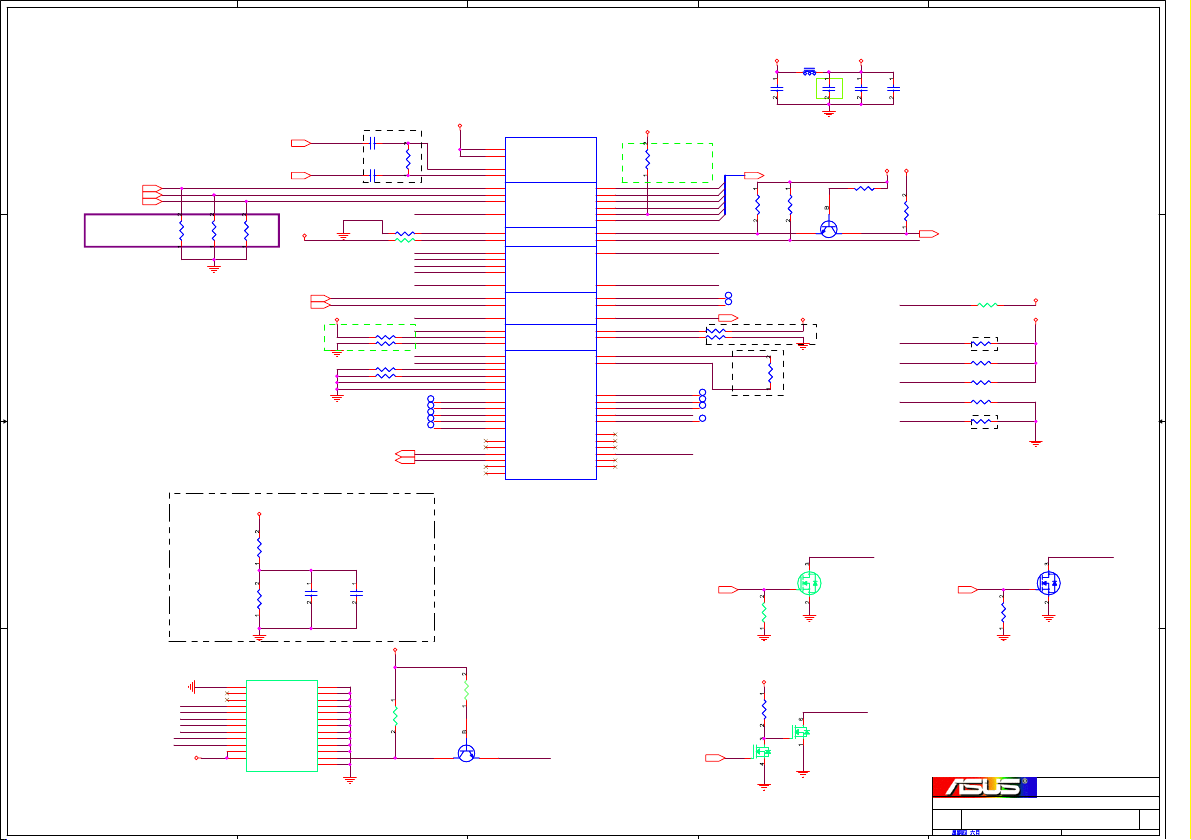

Page 3

5

A7K POWER ON SEQUENCE BLOCK

A/D_DOCK_IN

D D

AC_BAT_SYS

+5VLCM

+2.5VREF

+3VA_EC

+3VA

+5VAO

VSUS_ON

1

+3VA_EC

4

3

2

10

47~66ms

1

11

2

PWRSW#_EC

EC

IT8511TE

Power On

SWITCH

8

CPU_VRON

AMD S1g1 CPU

3

+1.2VSUS

+3VSUS

+5VSUS

4

VSUS_GD_EC#

5

13

16

6

C C

B B

+0.9V

+1.8V

+3V

+5V

+12V

+1.2VS

+1.5VS

+1.8VS

+2.5VS

+3VS

+5VS

+12VS

+VCORE

(MAX8760ETL)

+1.2VS_HT

PM_SUSC#

PM_SUSC#

8

CPU_VRON

9

CPUPWR_GD

HTVDD_EN

EC

7

From

EC

To EC

SUSC_EC#

SUSB_EC1#

SB600

(South Bridge)

12

CPU_PWROK

15

LDT_RESET#

HT_CPU_STOP#

11

PWRGD

13

A_RST#

RS690M

(North Bridge)

14

10

A A

SYS PWRGD

VLDT_PWRGD

PWRGD Logic

11

PWRGD

PCIRST#

13

A_RST#

PCI Device

(RICOH R5C83 3)

PCIE, LPC Device

(Minicard,

Newcard, PCI E LAN,

LPC devices)

Title :

Title :

Title :

A7K

A7K

A7K

Endy Zhang

Endy Zhang

Endy Zhang

Engineer:

Engineer:

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

Power Budget

Power Budget

Power Budget

3 69 14 2007

3 69 14 2007

3 69 14 2007

Rev

Rev

Rev

2 0

2 0

2 0

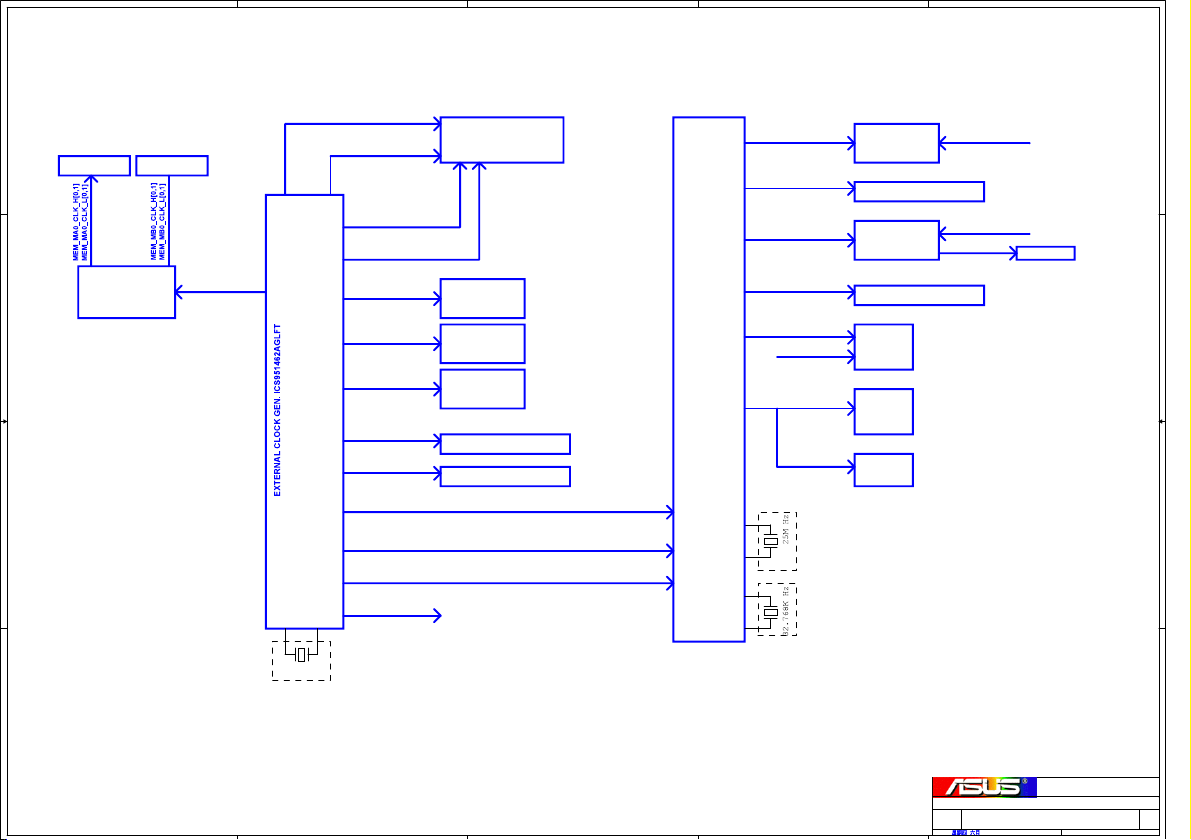

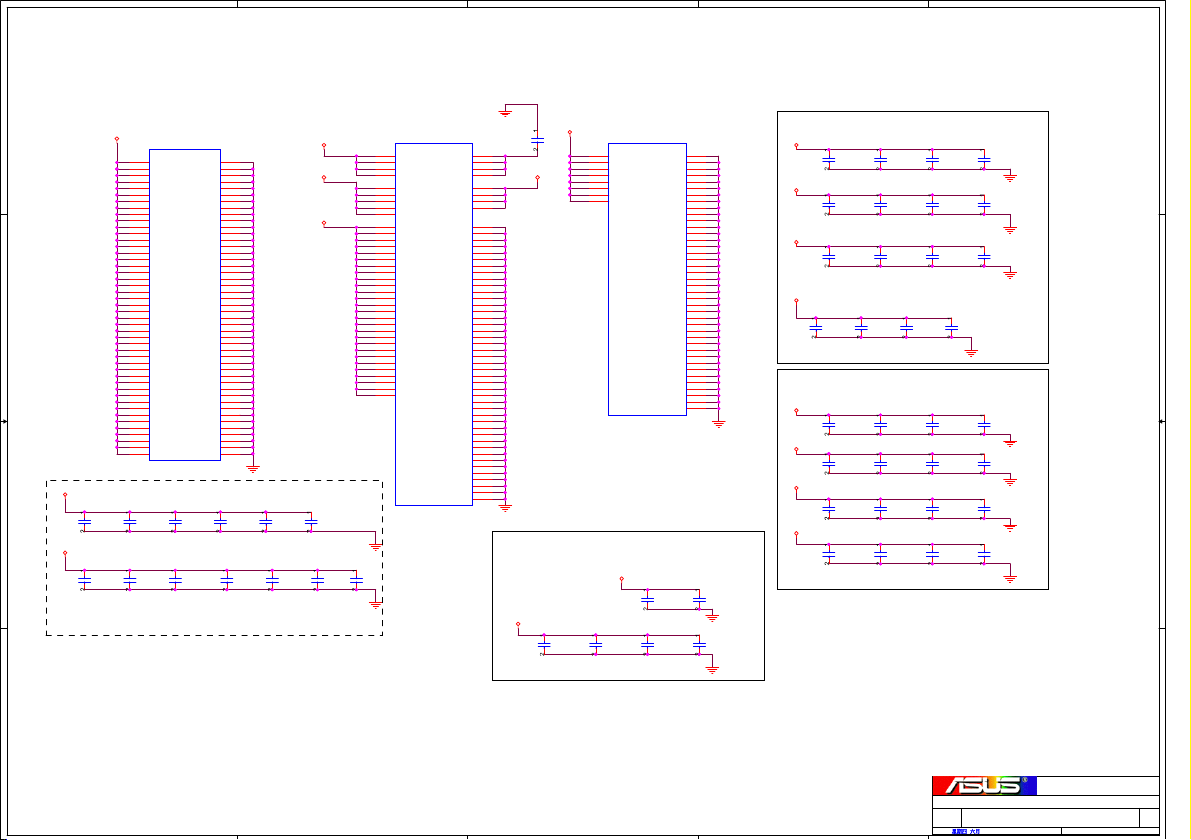

Page 4

5

4

3

2

1

D D

TOP SO-DIMM BOT SO-DIMM

HTTCLK0 FS2

SRCLKT1

TURION S1g1 CPU

C C

B B

LGA638 PACKAGE

CPU_CLK_H

CPU_CLK_L

200MHZ

SRCLKT6

SRCLKT4

(CLKREQ#B)

SRCLKT2

SRCLKT7

SRCLKT3

KREQ#A)

(CL

SRCLKT0

(CLKREQ#C)

SRCLKT5

FS0

48MHZ_0

48MHZ_1

HTREFCLK

66MHZ

NB_OSC

14.318MHZ

NBGFX_CLK_P

NBGFX_CLK_N

100MHZ

NBLINK_CLKP

NBLINK_CLKN

100MHZ

GFX_CLK_P

GFX

_CLK_N

100MHZ

GPP0_CLK_P

GPP0_CLK_N

100MHZ

GPP3_CLK_P

GPP3_CLK_N

100MHZ

GPP1_CLK_P

GPP1_CLK_N

100MHZ

GPP2_CLK_P

GPP2_CLK_N

100MHZ

SBLINK_CLKP

SBLINK_CLKN

100MHZ

CLK_14M_SB

14.318MHZ

CLK_48M_USB

48MHZ

SIO_CLK

48MHZ

ATI NB - RS690M

M76-M

MINI PCIE TV

E-SATA

MINI PCI-E WLAN

NEW CARD

ATI SB

SB600

PCI_CLK_CB

33MHZ

PCI_CLK_LAN

33MHZ

LPC_CLK_EC

33MHZ

LPC_CLK_DEBUG

33MHZ

LPC_CLK_SIO

33MHZ

SIO_CLK

48MHZ

CODEC_BCLK

MDC_BCLK

R5C833

PCI LAN

EC IT8511E

NEWCARD FOR DEBUG

SUPER IO

IT8712F

ALC660

MDC

24.576MHZ XTAL INPUT

32.768KHZ XTAL INPUT

TPAD_CLK

TOUCHPAD

14.31818MHz

A A

Title :

Title :

Title :

A7K

A7K

A7K

Endy Zhang

Endy Zhang

Endy Zhang

Engineer:

Engineer:

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

Clock Distribution

Clock Distribution

Clock Distribution

Rev

Rev

Rev

2 0

2 0

2 0

4 69 14 2007

4 69 14 2007

4 69 14 2007

Page 5

5

D D

HT_CPU_TX_CLK_H111

+1 2VS_HT

R500 49 9OhmR500 49 9Ohm

1 2

R501 49 9OhmR501 49 9Ohm

1 2

LAYOUT: PLAC E NEAR CPU

STUFF WHEN C ONFIGURED AS

16-BIT LINK

C C

HT_CPU_TX_CAD_L[0 15]11

HT_CPU_TX_CAD_H[0 15]11

HT_CPU_TX_CLK_L111

HT_CPU_TX_CLK_H011

HT_CPU_TX_CLK_L011

HT_CPU_TX_CTL_H011

HT_CPU_TX_CTL_L011

4

HT_CPU_TX_CLK_H1

HT_CPU_TX_CLK_L1

HT_CPU_TX_CLK_H0

HT_CPU_TX_CLK_L0

HT_CPU_TX_CTL_H1

HT_CPU_TX_CTL_L1

HT_CPU_TX_CTL_H0

HT_CPU_TX_CTL_L0

HT_CPU_TX_CAD_H15

HT_CPU_TX_CAD_L15

HT_CPU_TX_CAD_H14

HT_CPU_TX_CAD_L14

HT_CPU_TX_CAD_H13

HT_CPU_TX_CAD_L13

HT_CPU_TX_CAD_H12

HT_CPU_TX_CAD_L12

HT_CPU_TX_CAD_H11

HT_CPU_TX_CAD_L11

HT_CPU_TX_CAD_H10

HT_CPU_TX_CAD_L10

HT_CPU_TX_CAD_H9

HT_CPU_TX_CAD_L9

HT_CPU_TX_CAD_H8

HT_CPU_TX_CAD_L8

HT_CPU_TX_CAD_H7

HT_CPU_TX_CAD_L7

HT_CPU_TX_CAD_H6

HT_CPU_TX_CAD_L6

HT_CPU_TX_CAD_H5

HT_CPU_TX_CAD_L5

HT_CPU_TX_CAD_H4

HT_CPU_TX_CAD_L4

HT_CPU_TX_CAD_H3

HT_CPU_TX_CAD_L3

HT_CPU_TX_CAD_H2

HT_CPU_TX_CAD_L2

HT_CPU_TX_CAD_H1

HT_CPU_TX_CAD_L1

HT_CPU_TX_CAD_H0

HT_CPU_TX_CAD_L0

J5

K5

J3

J2

P3

P4

N1

P1

N5

P5

M3

M4

L5

M5

K3

K4

H3

H4

G5

H5

F3

F4

E5

F5

N3

N2

L1

M1

L3

L2

J1

K1

G1

H1

G3

G2

E1

F1

E3

E2

U500A

U500A

L0_CLKIN_H 1

L0_CLKIN_L1

L0_CLKIN_H 0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CAD N_H 15

L0_CAD N_L 15

L0_CAD N_H 14

L0_CAD N_L 14

L0_CAD N_H 13

L0_CAD N_L 13

L0_CAD N_H 12

L0_CAD N_L 12

L0_CAD N_H 11

L0_CAD N_L 11

L0_CAD N_H 10

L0_CAD N_L 10

L0_CAD N_H 9

L0_CAD N_L 9

L0_CAD N_H 8

L0_CAD N_L 8

L0_CAD N_H 7

L0_CAD N_L 7

L0_CAD N_H 6

L0_CAD N_L 6

L0_CAD N_H 5

L0_CAD N_L 5

L0_CAD N_H 4

L0_CAD N_L 4

L0_CAD N_H 3

L0_CAD N_L 3

L0_CAD N_H 2

L0_CAD N_L 2

L0_CAD N_H 1

L0_CAD N_L 1

L0_CAD N_H 0

L0_CAD N_L 0

SOCKET638

SOCKET638

L0_CADOUT _H15

L0_CADOUT _L15

L0_CADOUT _H14

L0_CADOUT _L14

L0_CADOUT _H13

L0_CADOUT _L13

L0_CADOUT _H12

L0_CADOUT _L12

L0_CADOUT _H11

L0_CADOUT _L11

L0_CADOUT _H10

L0_CADOUT _L10

HYPERTRAN SPORT

HYPERTRAN SPORT

L0_CLKOUT_H 1

L0_CLKOUT_L 1

L0_CLKOUT_H 0

L0_CLKOUT_L 0

L0_CTLOUT_ H1

L0_CTLOUT_ L1

L0_CTLOUT_ H0

L0_CTLOUT_ L0

L0_CADOUT _H9

L0_CADOUT _L9

L0_CADOUT _H8

L0_CADOUT _L8

L0_CADOUT _H7

L0_CADOUT _L7

L0_CADOUT _H6

L0_CADOUT _L6

L0_CADOUT _H5

L0_CADOUT _L5

L0_CADOUT _H4

L0_CADOUT _L4

L0_CADOUT _H3

L0_CADOUT _L3

L0_CADOUT _H2

L0_CADOUT _L2

L0_CADOUT _H1

L0_CADOUT _L1

L0_CADOUT _H0

L0_CADOUT _L0

3

HT_CPU_RX_CLK_H1

Y4

HT_CPU_RX_CLK_L1

Y3

HT_CPU_RX_CLK_H0

Y1

HT_CPU_RX_CLK_L0

W1

T5

R5

HT_CPU_RX_CTL_H0

R2

HT_CPU_RX_CTL_L0

R3

HT_CPU_RX_CAD_H15

T4

HT_CPU_RX_CAD_L15

T3

HT_CPU_RX_CAD_H14

V5

HT_CPU_RX_CAD_L14

U5

HT_CPU_RX_CAD_H13

V4

HT_CPU_RX_CAD_L13

V3

HT_CPU_RX_CAD_H12

Y5

HT_CPU_RX_CAD_L12

W5

HT_CPU_RX_CAD_H11

AB5

HT_CPU_RX_CAD_L11

AA5

HT_CPU_RX_CAD_H10

AB4

HT_CPU_RX_CAD_L10

AB3

HT_CPU_RX_CAD_H9

AD5

HT_CPU_RX_CAD_L9

AC5

HT_CPU_RX_CAD_H8

AD4

HT_CPU_RX_CAD_L8

AD3

HT_CPU_RX_CAD_H7

T1

HT_CPU_RX_CAD_L7

R1

HT_CPU_RX_CAD_H6

U2

HT_CPU_RX_CAD_L6

U3

HT_CPU_RX_CAD_H5

V1

HT_CPU_RX_CAD_L5

U1

HT_CPU_RX_CAD_H4

W2

HT_CPU_RX_CAD_L4

W3

HT_CPU_RX_CAD_H3

AA2

HT_CPU_RX_CAD_L3

AA3

HT_CPU_RX_CAD_H2

AB1

HT_CPU_RX_CAD_L2

AA1

HT_CPU_RX_CAD_H1

AC2

HT_CPU_RX_CAD_L1

AC3

HT_CPU_RX_CAD_H0

AD1

HT_CPU_RX_CAD_L0

AC1

HT_CPU_RX_CLK_H1 11

HT_CPU_RX_CLK_L1 11

HT_CPU_RX_CLK_H0 11

HT_CPU_RX_CLK_L0 11

HT_CPU_RX_CTL_H0 11

HT_CPU_RX_CTL_L0 11

2

HT_CPU_RX_CAD_L[0 15] 11

HT_CPU_RX_CAD_H[0 15] 11

1

Do not cross plane.

U500E

U500E

P20

RSVD_MA0_C LK_H3

P19

B B

RSVD_MA0_C LK_L3

N20

RSVD_MA0_C LK_H0

N19

RSVD_MA0_C LK_L0

R26

RSVD_MB0_C LK_H3

R25

RSVD_MB0_C LK_L3

P22

RSVD_MB0_C LK_H0

R22

RSVD_MB0_C LK_L0

SOCKET638

SOCKET638

RSVD_MA_RE SET_L

RSVD_MB_RE SET_L

RSVD_V DSTR B1

RSVD_V DSTR B0

RSVD_VDDNB _FB_H

RSVD_VDDNB _FB_L

RSVD_CORE _TYPE

MISC

MISC

NTERNAL

NTERNAL

FREE5

FREE6

FREE4

FREE1

FREE2

FREE3

T502 TPC28TN/AT502 TPC28TN/A

H16

1

T503 TPC28TN/AT503 TPC28TN/A

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

AF1

A1

TURION S1g1

uPGA638

Top View

A26

A A

Title :

Title :

Title :

A7K

A7K

A7K

Endy Zhang

Endy Zhang

Endy Zhang

Engineer:

Engineer:

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

Turion HT I/F

Turion HT I/F

Turion HT I/F

Rev

Rev

Rev

2 0

2 0

2 0

5 69 14 2007

5 69 14 2007

5 69 14 2007

Page 6

5

4

3

2

1

MEM_MA0_CLK_H2

C600

C600

MEM_MA0_CLK_L2

1 5PF/50V

1 5PF/50V

D D

MEM_MA0_CS_L[0 3]9 10 MEM_MB0_CS_L[0 3]9 10

MEM_MA0_ODT[0 1]9 10

C C

B B

MEM_MA_CAS_L9 10

MEM_MA_WE_L9 10

MEM_MA_RAS_L9 10

MEM_MA_BANK[0 2]910

MEM_MA_CKE[0 1]9 10

MEM_MA_ADD[0 15]9 10

MEM_MA_DQS_H[0 7]9

MEM_MA_DQS_L[0 7]9

MEM_MA_DM[0 7]9

MEM_MA0_CLK_L19

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CS_L3

MEM_MA0_CS_L2

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT1

MEM_MA0_ODT0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7 MEM_MB_DATA23

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA0_CLK_H1

C602

C602

MEM_MA0_CLK_L1

1 5PF/50V

1 5PF/50V

U500B

U500B

Y16

MA0_CLK_H2

AA16

MA0_CLK_L2

E16

MA0_CLK_H1

F16

MA0_CLK_L1

V19

MA0_CS_L3

J22

MA0_CS_L2

V22

MA0_CS_L1

T19

MA0_CS_L0

V20

MA0_ODT1

U19

MA0_ODT0

U20

MA_CAS_L

U21

MA_WE_L

T20

MA_RAS_L

K22

MA_BANK2

R20

MA_BANK1

T22

MA_BANK0

J20

MA_CKE1

J21

MA_CKE0

K19

MA_ADD15

K20

MA_ADD14

V24

MA_ADD13

K24

MA_ADD12

L20

MA_ADD11

R19

MA_ADD10

L19

MA_ADD9

L22

MA_ADD8

L21

MA_ADD7

M19

MA_ADD6

M20

MA_ADD5

M24

MA_ADD4

M22

MA_ADD3

N22

MA_ADD2

N21

MA_ADD1

R21

MA_ADD0

W12

MA_DQS_H7

W13

MA_DQS_L7

Y15

MA_DQS_H6

W15

MA_DQS_L6

AB19

MA_DQS_H5

AB20

MA_DQS_L5

AD23

MA_DQS_H4

AC23

MA_DQS_L4

G22

MA_DQS_H3

G21

MA_DQS_L3

C22

MA_DQS_H2

C21

MA_DQS_L2

G16

MA_DQS_H1

G15

MA_DQS_L1

G13

MA_DQS_H0

H13

MA_DQS_L0

Y13

MA_DM7

AB16

MA_DM6

Y19

MA_DM5

AC24

MA_DM4

F24

MA_DM3

E19

MA_DM2

C15

MA_DM1

E12

MA_DM0

SOCKET638

SOCKET638

MEMORY

MEMORY

INTERFACE

INTERFACE

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

the cap clos e to cpu less than 1200mil

max neckdown to & from ca ps is 500mil

MEM_MA_DATA[0 63] 9

MEM_MA_DATA63

AA12

MEM_MA_DATA62

AB12

MEM_MA_DATA61

AA14

MEM_MA_DATA60

AB14

MEM_MA_DATA59

W11

MEM_MA_DATA58

Y12

MEM_MA_DATA57

AD13

MEM_MA_DATA56

AB13

MEM_MA_DATA55

AD15

MEM_MA_DATA54

AB15

MEM_MA_DATA53

AB17

MEM_MA_DATA52

Y17

MEM_MA_DATA51

Y14

MEM_MA_DATA50 MEM_MB_RAS_L

W14

MEM_MA_DATA49

W16

MEM_MA_DATA48

AD17

MEM_MA_DATA47

Y18

MEM_MA_DATA46

AD19

MEM_MA_DATA45

AD21

MEM_MA_DATA44

AB21

MEM_MA_DATA43

AB18

MEM_MA_DATA42

AA18

MEM_MA_DATA41

AA20

MEM_MA_DATA40

Y20

MEM_MA_DATA39

AA22

MEM_MA_DATA38

Y22

MEM_MA_DATA37

W21

MEM_MA_DATA36

W22

MEM_MA_DATA35

AA21

MEM_MA_DATA34

AB22

MEM_MA_DATA33

AB24

MEM_MA_DATA32

Y24

MEM_MA_DATA31

H22

MEM_MA_DATA30

H20

MEM_MA_DATA29

E22

MEM_MA_DATA28

E21

MEM_MA_DATA27

J19

MEM_MA_DATA26

H24

MEM_MA_DATA25

F22

MEM_MA_DATA24

F20

MEM_MA_DATA23

C23

MEM_MA_DATA22

B22

MEM_MA_DATA21

F18

MEM_MA_DATA20

E18

MEM_MA_DATA19

E20

MEM_MA_DATA18

D22

MEM_MA_DATA17

C19

MEM_MA_DATA16

G18

MEM_MA_DATA15

G17

MEM_MA_DATA14

C17

MEM_MA_DATA13

F14

MEM_MA_DATA12

E14

MEM_MA_DATA11

H17

MEM_MA_DATA10

E17

MEM_MA_DATA9

E15

MEM_MA_DATA8

H15

MEM_MA_DATA7

E13

MEM_MA_DATA6

C13

MEM_MA_DATA5

H12

MEM_MA_DATA4

H11

MEM_MA_DATA3

G14

MEM_MA_DATA2

H14

MEM_MA_DATA1

F12

MEM_MA_DATA0

G12

MEM_MB0_ODT[0 1]9 10

MEM_MB_CAS_L9 10

MEM_MB_WE_L9 10

MEM_MB_RAS_L9 10

MEM_MB_BANK[0 2]910

MEM_MB_CKE[0 1]9 10

MEM_MB_ADD[0 15]9 10

MEM_MB_DQS_H[0 7]9

MEM_MB_DQS_L[0 7]9

MEM_MB_DM[0 7]9

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CS_L3

MEM_MB0_CS_L2

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT1

MEM_MB0_ODT0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE1

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13MEM_MA_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB0_CLK_H29MEM_MA0_CLK_H29

MEM_MB0_CLK_L29MEM_MA0_CLK_L29

MEM_MB0_CLK_H19MEM_MA0_CLK_H19

MEM_MB0_CLK_L19

U500C

U500C

AF18

MB0_CLK_H2

AF17

MB0_CLK_L2

A17

MB0_CLK_H1

A18

MB0_CLK_L1

Y26

MB0_CS_L3

J24

MB0_CS_L2

W24

MB0_CS_L1

U23

MB0_CS_L0

W23

MB0_ODT1

W26

MB0_ODT0

V26

MB_CAS_L

U22

MB_WE_L

U24

MB_RAS_L

K26

MB_BANK2

T26

MB_BANK1

U26

MB_BANK0

H26

MB_CKE1

J23

MB_CKE0

J25

MB_ADD15

MEMORY

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

SOCKET638

SOCKET638

MEMORY

INTERFACE

INTERFACE

J26

W25

L23

L25

U25

L24

M26

L26

N23

N24

N25

N26

P24

P26

T24

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

F26

E26

A24

A23

D16

C16

C12

B12

AD12

AC16

AE22

AB26

E25

A22

B16

A12

C601

C601

1 5PF/50V

1 5PF/50V

C603

C603

1 5PF/50V

1 5PF/50V

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

AD11

AF11

AF14

AE14

Y11

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DATA[0 63] 9

A A

Title :

Title :

Title :

A7K

A7K

A7K

Endy Zhang

Endy Zhang

Endy Zhang

Engineer:

Engineer:

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

Turion DDR2 Memory I/F

Turion DDR2 Memory I/F

Turion DDR2 Memory I/F

6 69 14 2007

6 69 14 2007

6 69 14 2007

Rev

Rev

Rev

2 0

2 0

2 0

Page 7

5

D D

CPU_CLK_H16

R703

R703

680OHM

680OHM

CPU_CLK_L16

R704

R704

680OHM

680OHM

CPU_VDD_FB55

CPU_VDD_FB#55

+1 8V

P700

P700

1

NC

3

DBREQ_L1

5

DBRDY1

7

DBREQ_L2

9

DBRDY2

11

DBREQ_L3

13

DBRDY3

15

DBREQ_L4

17

DBRDY4

19

DBREQ_L5

21

DBRDY5

23

DBREQ_L6

ASP_68200_07_K25

ASP_68200_07_K25

/X

/X

Keep trace t o

resistors le ss

than 1 5" fr om

CPU pin

R724

R724

1KOhm

1KOhm

1%

1%

R725

R725

1KOhm

1KOhm

1%

1%

DBRDY7

DBREQ_L7

DBRDY6

CPU_PWROK17

LDT_STOP#13 17

LDT_RESET#17

R702

Reversion 1.1

C C

B B

A A

R702

680OHM

680OHM

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

+1 8V

4

Keep trace t o resistors

less than 60 0mils from

CPU pin and trace to AC

caps less th an 1250mils

CPU_CLK_H

CPU_CLK_L

+1 8V

CPU_M_VREF

15mil trace. 20mil space

shorter than 6 inches

CPU_M_VREF

C706

C706

1000PF/16V

1000PF/16V

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

3900PF/50V

3900PF/50V

3900PF/50V

3900PF/50V

route as dif f

pair

5/5/5,10mil

+1 8V

R712 39 2OhmR712 39 2Ohm

R714 39 2OhmR714 39 2Ohm

R717 300OhmR717 300Ohm

R719 300OhmR719 300Ohm

CPU_THERMADC21

CPU_THERMADA21

2

4

6

8

10

12

14

16

18

20

22

24

26

1 2

1 2

1 2

1 2

C707

C707

0 1UF/16V

0 1UF/16V

10KOhm

10KOhm

12

12

R728

R728

C704

C704

R701

R701

169Ohm

169Ohm

C705

C705

R705

R705

1 2

1 2

R710

R710

T703 TPC28TT703 TPC28T

T705 TPC28TT705 TPC28T

T707 TPC28TT707 TPC28T

T708 TPC28TT708 TPC28T

T710 TPC28TT710 TPC28T

+3VS

/DEBUG

/DEBUG

3

100UF 6 3V

Need decoupl ing

+2 5V_VDDA

capacitors

U500D

U500D

F8

VDDA1

F9

CPU_CLK_H_C

CPU_CLK_L_C

CPU_PWROK

LDT_STOP#

LDT_RESET#

CPU_PRESENT#

300Ohm

300Ohm

300Ohm

300Ohm

x

x

CPU_TDI

CPU_TRST#

CPU_TCK

CPU_TMS

CPU_DBREQ#

CPU_VCORE_FB_H

CPU_VCORE_FB_L

CPU_VTT_SENSE

CPU_M_VREF

CPU_TEST25_H

CPU_TEST25_L

1

1

1

1

1

CPU_THERMADC

CPU_THERMADA

C E

VDDA2

A9

CLKIN_H

A8

CLKIN_L

A7

PWROK

F10

LDTSTOP_L

B7

RESET_L

AC6

CPU_PRESE NT_L

AF4

SIC

CPU_SID CPU_PROCHOT#

AF5

SID

AF9

TDI

AD9

TRST_L

AC9

TCK

AA9

TMS

E10

DBREQ_L

F6

VDD_FB_H

E6

VDD_FB_L

Y10

VTT_SENSE

W17

M_VREF

AE10

M_ZN

AF10

M_ZP

E9

TEST25_H

E8

TEST25_L

G9

TEST19

H10

TEST18

AA7

TEST13

C2

TEST9

D7

TEST17

E7

TEST16

F7

TEST15

C7

TEST14

AC8

TEST12

C3

TEST7

AA6

TEST6

W7

THERMDC

W8

THERMDA

Y6

TEST3

AB6

TEST2

SOCKET638

SOCKET638

R730

R730

4 7KOhm

4 7KOhm

/DEBUG

/DEBUG

Q703

Q703

LDT_RESET#

PMBS3904

PMBS3904

/DEBUG

/DEBUG

THERMTR P_ L

PROCHOT_L

MISC

MISC

DBRDY

VDDIO_FB_H

VDD O_FB_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

PSI_L

VID5

VID4

VID3

VID2

VID1

VID0

TDO

A5

C6

A6

A4

C5

B5

AF6

AC7

AE9

G10

W9

Y9

A3

P6

R6

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

+1 8V

R700

R700

300Ohm

300Ohm

+1 8V_DRAM_FB

+1 8V_DRAM_FB#

CPU_TEST29_H

CPU_TEST29_L

CPU_TEST21

CPU_TEST26

Required for

compatibilit y

with future

processors

CPU_VID5

CPU_VID4

CPU_VID3

CPU_VID2

CPU_VID1

CPU_VID0

CPU_TDO

CPU_DBRDY

CPU_PSI#

T702 TPC28TT702 TPC28T

T704 TPC28TT704 TPC28T

T706 TPC28TT706 TPC28T

T709 TPC28TT709 TPC28T

PWRLMT#28 63

100UF 6 3V

CPU_THERMTRIP#_R

T700 TPC28TT700 TPC28T

1

T701 TPC28TT701 TPC28T

1

CPU_PSI# 55

R713 44 2OhmR713 44 2Ohm

1 2

R715 44 2OhmR715 44 2Ohm

1 2

R720

R720

80 6Ohm

80 6Ohm

1

1

1

1

From SB From EC

5

2

30Ohm 100Mhz

30Ohm 100Mhz

L700

L700

C700

C700

C701

C701

4 7UF/6 3V

4 7UF/6 3V

close to the ferrite bead

CPU_VID[0 5] 55

R707

R707

R706

R706

300Ohm

300Ohm

300Ohm

300Ohm

Keep trace t o

resistors le ss

than 1 5" fr om

CPU pin

+1 2VS_HT

Route as 80O hm

differential

impedance

Keep trace t o

resistors le ss

than 1" from

CPU pin

3

3

D

D

1

1

1

G

G

S

S

2

2

R726

R726

10KOhm

10KOhm

N/A

N/A

GND

GND

+3VS

R729

R729

CPU_PROCHOT#

10KOhm

10KOhm

/x

/x

2

Q704B

Q704B

UM6K1N

UM6K1N

/x

/x

GND

GND

21

Q700

Q700

PMBS3904

PMBS3904

Q701

Q701

2N7002

2N7002

N/A

N/A

Q704A

Q704A

UM6K1N

UM6K1N

/x

/x

0 22UF/63 V

0 22UF/63 V

10KOhm

10KOhm

CE

1

+2 5V_VDDA+2 5VS

C702

C702

C703

C703

3300PF/50V

3300PF/50V

+1 8V +3VSUS

R708

R708

12

R709

R709

4 7KOhm

4 7KOhm

CPU_THERMTRP# 18 28

+0 9V

R711

CPU_VTT_SENSE

CPU_TEST26

CPU_PRESENT#

CPU_TEST25_H

CPU_TEST25_L

CPU_TEST21

THRO_CPU28SB_THRO_CPU19

R711

1 2

+1 8V

0Ohm /x

0Ohm /x

R716 300OhmR716 300Ohm

1 2

R718 1KOhmR718 1KOhm

1 2

R721 510OhmR721 510Ohm

1 2

R722 510OhmR722 510Ohm

1 2

R723 300OhmR723 300Ohm

1 2

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Turion CNRL/DEBUG/THERM

Turion CNRL/DEBUG/THERM

Turion CNRL/DEBUG/THERM

Date: Sheet of

Date: Sheet of

Date: Sheet of

Erratum 133,

Revision Guide

for AMD NPT

0Fh Processors

CPU_PROCHOT#CPU_PROCHOT#

3

3

D

D

Q702

Q702

1

1

THRO CPUSB_THRO_CPU

1

2N7002

2N7002

G

G

S

S

2

2

R727

R727

10KOhm

10KOhm

GND

GND

Title :

Title :

Title :

A7K

A7K

A7K

Endy Zhang

Endy Zhang

Endy Zhang

Engineer:

Engineer:

Engineer:

7 69 14 2007

7 69 14 2007

7 69 14 2007

Rev

Rev

Rev

2 0

2 0

2 0

Page 8

5

4

3

2

1

D D

+VCORE

U500F

U500F

AC4

VDD1

AD2

VDD2

G4

VDD3

H2

VDD4

J9

VDD5

J11

VDD6

J13

VDD7

K6

VDD8

K10

VDD9

K12

VDD10

K14

VDD11

L4

VDD12

L7

VDD13

L9

VDD14

L11

VDD15

L13

VDD16

M2

VDD17

M6

VDD18

M8

VDD19

M10

VDD20

N7

VDD21

N9

VDD22

N11

VDD23

P8

VDD24

P10

22UF/6 3V

22UF/6 3V

22UF/6 3V

22UF/6 3V

VDD25

R4

VDD26

R7

VDD27

R9

VDD28

R11

VDD29

T2

VDD30

T6

VDD31

T8

VDD32

T10

VDD33

T12

VDD34

T14

VDD35

U7

VDD36

U9

VDD37

U11

VDD38

U13

VDD39

V6

VDD40

V8

VDD41

V10

VDD42

V12

VDD43

V14

VDD44

W4

VDD45

Y2

VDD46

SOCKET638

SOCKET638

C826

C826

C827

C827

22UF/6 3V

22UF/6 3V

C840

C840

C841

C841

22UF/6 3V

22UF/6 3V

C C

+VCORE

C825

C825

22UF/6 3V

22UF/6 3V

B B

+VCORE

C839

C839

22UF/6 3V

22UF/6 3V

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

VDD

VDD

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

place under socket on bot tom side

C829

C829

C828

C828

22UF/6 3V

22UF/6 3V

22UF/6 3V

22UF/6 3V

C842

C842

C843

0 22UF/63 V

0 22UF/63 V

C843

0 22UF/63 V

0 22UF/63 V

+1 2VS_HT

+0 9V +0 9V

+1 8V

C830

C830

22UF/6 3V

22UF/6 3V

C844

C844

0 01UF/16V

0 01UF/16V

180PF/50V

180PF/50V

U500H

U500H

D4

VLDT_A4

VLDT_A3

VLDT_A2

VLDT_A1

VTT8

VTT7

VTT6

VTT5

VTT9

VDD O23

VDD O1

VDD O2

VDD O3

VDD O4

VDD O5

VDD O6

VDD O7

VDD O8

VDD O9

VDD O10

VDD O11

VDD O12

VDD O13

VDD O14

VDD O15

VDD O16

VDD O17

VDD O18

VDD O19

VDD O20

VDD O21

VDD O22

VDD O24

VDD O25

VDD O26

VDD O27

SOCKET638

SOCKET638

POWER

POWER

VLDT_B4

VLDT_B3

VLDT_B2

VLDT_B1

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

I O

I O

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

D3

D2

D1

D10

C10

B10

AD10

W10

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

C845

C845

AE5

AE4

AE3

AE2

AC10

VTT4

AB10

VTT3

AA10

VTT2

A10

VTT1

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

+VCORE

C800

C800

4 7UF 10V

4 7UF 10V

K16

L15

M16

P16

T16

U15

V16

J15

U500G

U500G

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

SOCKET638

SOCKET638

M17

VSS91

N4

VSS92

N8

VSS93

N10

VSS94

N16

VSS95

N18

VSS96

P2

VSS97

P7

VSS98

P9

VSS99

P11

VSS100

P17

VSS101

R8

VSS102

R10

VSS103

R16

VSS104

R18

VSS105

VDD

VDD

T7

VSS106

T9

VSS107

T11

VSS108

T13

VSS109

T15

VSS110

T17

VSS111

U4

VSS112

U6

VSS113

U8

VSS114

U10

VSS115

U12

VSS116

U14

VSS117

U16

VSS118

U18

VSS119

V2

VSS120

V7

VSS121

V9

VSS122

V11

VSS123

V13

VSS124

V15

VSS125

V17

VSS126

W6

VSS130

Y21

VSS131

Y23

VSS132

N6

VSS133

Near the socket on the +1.2V_HT pour

+1 2VS_HT

C847

C847

C846

C846

4 7UF/6 3V

4 7UF/6 3V

4 7UF/6 3V

0 22UF/63 V

0 22UF/63 V

4 7UF/6 3V

C850

C850

C849

C849

180PF/50V

180PF/50V

180PF/50V

180PF/50V

C851

C851

+1 2VS_HT

0 22UF/63 V

0 22UF/63 V

C848

C848

Between the socket and DIMMs, as close as

possible to the socket

+1 8V

0 22UF/63 V

0 22UF/63 V

+1 8V

4 7UF/6 3V

4 7UF/6 3V

+1 8V

0 01UF/16V

0 01UF/16V

+1 8V

C813

C813

22UF/6 3V

22UF/6 3V

Capacitors are placed between the socket and

DIMMs, as close as possible to the socket

+0 9V

4 7UF/6 3V

4 7UF/6 3V

+0 9V

0 22UF/63 V

0 22UF/63 V

+0 9V

1000PF/16V

1000PF/16V

+0 9V

180PF/50V

180PF/50V

C802

C802

C801

C801

0 22UF/63 V

0 22UF/63 V

0 22UF/63 V

0 22UF/63 V

C806

C806

C805

C805

4 7UF 6 3V

4 7UF 6 3V

4 7UF 6 3V

4 7UF 6 3V

C809

C809

C810

C810

180PF/50V

180PF/50V

0 01UF/16V

0 01UF/16V

place under socket on bottom side

C814

C814

C815

C815

22UF/6 3V

22UF/6 3V

0 22UF/63 V

0 22UF/63 V

C817

C817

C818

C818

4 7UF 6 3V

4 7UF 6 3V

4 7UF 6 3V

4 7UF 6 3V

C821

C821

C822

C822

0 22UF/63 V

0 22UF/63 V

0 22UF/63 V

0 22UF/63 V

C832

C832

C831

C831

1000PF/16V

1000PF/16V

1000PF/16V

1000PF/16V

C835

C835

C836

C836

180PF/50V

180PF/50V

180PF/50V

180PF/50V

C803

C803

C807

C807

C811

C811

0 22UF/63 V

0 22UF/63 V

C819

C819

C823

C823

C833

C833

C837

C837

C816

C816

0 22UF/63 V

0 22UF/63 V

C808

C808

4 7UF/6 3V

4 7UF/6 3V

180PF/50V

180PF/50V

C820

C820

4 7UF/6 3V

4 7UF/6 3V

0 22UF/63 V

0 22UF/63 V

1000PF 16V

1000PF 16V

180PF/50V

180PF/50V

C804

C804

C812

C812

C824

C824

C834

C834

C838

C838

DRAM_VTT 0.9 V

A A

Title :

Title :

Title :

A7K

A7K

A7K

Engineer:

Endy Zhang

Engineer:

Endy Zhang

Engineer:

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Turion Power

Turion Power

Turion Power

Date: Sheet of

Date: Sheet of

Date: Sheet of

Endy Zhang

8 69 14 2007

8 69 14 2007

8 69 14 2007

Rev

Rev

Rev

2 0

2 0

2 0

Page 9

5

4

3

2

1

D D

MEM_MA_ADD[0 15]6 10

MEM_MA_BANK2610

MEM_MA_BANK0610

MEM_MA_BANK1610

MEM_MA0_CLK_H16

MEM_MA0_CLK_L16

MEM_MA0_CLK_H26

MEM_MA0_CLK_L26

MEM_MA_CKE06 10

MEM_MA_CKE16 10

MEM_MA_CAS_L6 10

C C

B B

A A

MEM_MA_RAS_L6 10

MEM_MA_WE_L6 10

GND

MEM_MA_DM[0 7]6

MEM_MA_DQS_H[0 7]6

MEM_MA_DQS_L[0 7]6

SMBCLK16 18 33

SMBDATA16 18 33

MEM_MA0_ODT06 10

MEM_MA0 ODT16 10

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA0_CS_L0

MEM_MA0_CS_L1

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM6

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM7

MEM_MA_DQS_H0

MEM_MA_DQS_H1

MEM_MA_DQS_H2

MEM_MA_DQS_H3

MEM_MA_DQS_H6

MEM_MA_DQS_H4

MEM_MA_DQS_H5

MEM_MA_DQS_H7

MEM_MA_DQS_L0

MEM_MA_DQS_L1

MEM_MA_DQS_L2

MEM_MA_DQS_L3

MEM_MA_DQS_L6

MEM_MA_DQS_L4

MEM_MA_DQS_L5

MEM_MA_DQS_L7

U900A

U900A

TOP BOTTOM

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

110

115

30

32

164

166

79

80

113

108

109

198

200

197

195

114

119

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DDR_DMM_200P

DDR_DMM_200P

MEM_MA_DATA5

5

DQ0

MEM_MA_DATA4

7

DQ1

MEM_MA_DATA1

17

DQ2

MEM_MA_DATA6

19

DQ3

MEM_MA_DATA2

4

DQ4

MEM_MA_DATA0

6

DQ5

MEM_MA_DATA3

14

DQ6

MEM_MA_DATA7

16

DQ7

MEM_MA_DATA8

23

DQ8

MEM_MA_DATA9

25

DQ9

MEM_MA_DATA10

35

DQ10

MEM_MA_DATA11

37

DQ11

MEM_MA_DATA12

20

DQ12

MEM_MA_DATA13

22

DQ13

MEM_MA_DATA14

36

DQ14

MEM_MA_DATA15

38

DQ15

MEM_MA_DATA17

43

DQ16

MEM_MA_DATA20

45

DQ17

MEM_MA_DATA19

55

DQ18

MEM_MA_DATA23

57

DQ19

MEM_MA_DATA22

44

DQ20

MEM_MA_DATA21 MEM_MB0_CS_L1

46

DQ21

MEM_MA_DATA18

56

DQ22

MEM_MA_DATA16

58

DQ23

MEM_MA_DATA29

61

DQ24

MEM_MA_DATA28

63

DQ25

MEM_MA_DATA30

73

DQ26

MEM_MA_DATA31

75

DQ27

MEM_MA_DATA25

62

DQ28

MEM_MA_DATA24

64

DQ29

MEM_MA_DATA27

74

DQ30

MEM_MA_DATA26

76

DQ31

MEM_MA_DATA49

123

DQ32

MEM_MA_DATA54

125

DQ33

MEM_MA_DATA55

135

DQ34

MEM_MA_DATA48

137

DQ35

MEM_MA_DATA50

124

DQ36

MEM_MA_DATA52

126

DQ37

MEM_MA_DATA51

134

DQ38

MEM_MA_DATA53

136

DQ39

MEM_MA_DATA32

141

DQ40

MEM_MA_DATA35

143

DQ41

MEM_MA_DATA38

151

DQ42

MEM_MA_DATA34

153

DQ43

MEM_MA_DATA36

140

DQ44

MEM_MA_DATA37

142

DQ45

MEM_MA_DATA33

152

DQ46

MEM_MA_DATA39

154

DQ47

MEM_MA_DATA44

157

DQ48

MEM_MA_DATA45

159

DQ49

MEM_MA_DATA47

173

DQ50

MEM_MA_DATA46

175

DQ51

MEM_MA_DATA40

158

DQ52

MEM_MA_DATA41

160

DQ53

MEM_MA_DATA43

174

DQ54

MEM_MA_DATA42

176

DQ55

MEM_MA_DATA63

179

DQ56

MEM_MA_DATA62

181

DQ57

MEM_MA_DATA58

189

DQ58

MEM_MA_DATA59

191

DQ59

MEM_MA_DATA61

180

DQ60

MEM_MA_DATA60

182

DQ61

MEM_MA_DATA56

192

DQ62

MEM_MA_DATA57

194

DQ63

MEM_MA_DATA[0 63] 6

+1 8V

+3VS

MEM_MA0_CS_L2 MEM_MB0_CS_L2

MEM_MA0_CS_L3

C900

C900

0 1UF/16V

0 1UF/16V

GND GND

GND

MEM_M_VREF

U900B

U900B

112

111

117

96

95

118

81

82

87

103

88

104

199

83

120

50

69

163

1

201

202

203

204

47

133

183

77

12

48

184

78

71

72

121

122

196

193

8

MEM_MA0_CS_L[0 3]6 10

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDDSPD

NC1

NC2

NC3

NC4

NCTEST

VREF

GND0

GND1

NP_NC1

NP_NC2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

DDR_DIMM_200P

DDR_DIMM_200P

+1 8V

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

R901

R901

R902

R902

1KOhm

1KOhm

1%

1%

1KOhm

1KOhm

1%

1%

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

MEM_MB_ADD[0 15]6 10

+3VS

R900

R900

GND

MEM_MB_DM[0 7]6

MEM_MB_DQS_H[0 7]6

GND

MEM_MB_DQS_L[0 7]6

MEM_M_VREF

15mil trace. 20mil space

shorter than 6 inches

C902

C902

0 1UF 16V

0 1UF 16V

MEM_M_VREF

C903

C903

C904

C904

0 1UF 16V

0 1UF 16V

1000PF/16V

1000PF/16V

MEM_MB_BANK2610

MEM_MB_BANK0610

MEM_MB_BANK1610

MEM_MB0_CLK_H16

MEM_MB0_CLK_L16

MEM_MB0_CLK_H26

MEM_MB0_CLK_L26

MEM_MB_CKE06 10

MEM_MB_CKE16 10

MEM_MB_CAS_L6 10

MEM_MB_RAS_L6 10

MEM_MB_WE_L6 10

12

MEM_MB0_ODT06 10

MEM_MB0 ODT16 10

1KOhm

1KOhm

SMBCLK16 18 33

SMBDATA16 18 33

MEM_M_VREF

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB0_CS_L0

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DQS_H0

MEM_MB_DQS_H1

MEM_MB_DQS_H2

MEM_MB_DQS_H3

MEM_MB_DQS_H6

MEM_MB_DQS_H7

MEM_MB_DQS_H5

MEM_MB_DQS_H4

MEM_MB_DQS_L0

MEM_MB_DQS_L1

MEM_MB_DQS_L2

MEM_MB_DQS_L3

MEM_MB_DQS_L6

MEM_MB_DQS_L7

MEM_MB_DQS_L5

MEM_MB_DQS_L4

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

110

115

30

32

164

166

79

80

113

108

109

198

200

197

195

114

119

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

U901A

U901A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DDR_DIMM_200P

DDR_DIMM_200P

MEM_MB_DATA0

5

DQ0

MEM_MB_DATA1

7

DQ1

MEM_MB_DATA7

17

DQ2

MEM_MB_DATA3

19

DQ3

MEM_MB_DATA4

4

DQ4

MEM_MB_DATA5

6

DQ5

MEM_MB_DATA6

14

DQ6

MEM_MB_DATA2

16

DQ7

MEM_MB_DATA13

23

DQ8

MEM_MB_DATA12

25

DQ9

MEM_MB_DATA15

35

DQ10

MEM_MB_DATA11

37

DQ11

MEM_MB_DATA8

20

DQ12

MEM_MB_DATA9

22

DQ13

MEM_MB_DATA14

36

DQ14

MEM_MB_DATA10

38

DQ15

MEM_MB_DATA20

43

DQ16

MEM_MB_DATA17

45

DQ17

MEM_MB_DATA23

55

DQ18

MEM_MB_DATA19

57

DQ19

MEM_MB_DATA16

44

DQ20

MEM_MB_DATA21

46

DQ21

MEM_MB_DATA18

56

DQ22

MEM_MB_DATA22

58

DQ23

MEM_MB_DATA25

61

DQ24

MEM_MB_DATA29

63

DQ25

MEM_MB_DATA31

73

DQ26

MEM_MB_DATA27

75

DQ27

MEM_MB_DATA28

62

DQ28

MEM_MB_DATA24

64

DQ29

MEM_MB_DATA30

74

DQ30

MEM_MB_DATA26

76

DQ31

MEM_MB_DATA49

123

DQ32

MEM_MB_DATA53

125

DQ33

MEM_MB_DATA48

135

DQ34

MEM_MB_DATA52

137

DQ35

MEM_MB_DATA54

124

DQ36

MEM_MB_DATA50

126

DQ37

MEM_MB_DATA55

134

DQ38

MEM_MB_DATA51

136

DQ39

MEM_MB_DATA56

141

DQ40

MEM_MB_DATA57

143

DQ41

MEM_MB_DATA62

151

DQ42

MEM_MB_DATA63

153

DQ43

MEM_MB_DATA60

140

DQ44

MEM_MB_DATA61

142

DQ45

MEM_MB_DATA59

152

DQ46

MEM_MB_DATA58

154

DQ47

MEM_MB_DATA47

157

DQ48

MEM_MB_DATA46

159

DQ49

MEM_MB_DATA44

173

DQ50

MEM_MB_DATA45

175

DQ51

MEM_MB_DATA40

158

DQ52

MEM_MB_DATA42

160

DQ53

MEM_MB_DATA41

174

DQ54

MEM_MB_DATA43

176

DQ55

MEM_MB_DATA37

179

DQ56

MEM_MB_DATA36

181

DQ57

MEM_MB_DATA32

189

DQ58

MEM_MB_DATA33

191

DQ59

MEM_MB_DATA34

180

DQ60

MEM_MB_DATA38

182

DQ61

MEM_MB_DATA39

192

DQ62

MEM_MB_DATA35

194

DQ63

MEM_MB_DATA[0 63] 6

+1 8V

+3VS

MEM_MB0_CS_L3

C901

C901

0 1UF/16V

0 1UF/16V

MEM_M_VREF

GND

MEM_MB0_CS_L[0 3]6 10

112

111

117

96

95

118

81

82

87

103

88

104

199

83

120

50

69

163

1

201

202

203

204

47

133

183

77

12

48

184

78

71

72

121

122

196

193

8

U901B

U901B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDDSPD

NC1

NC2

NC3

NC4

NCTEST

VREF

GND0

GND1

NP_NC1

NP_NC2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

DDR_DIMM_200P

DDR_DIMM_200P

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

GND

Title :

Title :

Title :

A7K

A7K

A7K

Endy Zhang

Endy Zhang

Endy Zhang

Engineer:

Engineer:

ASUSTECH CO LTD

ASUSTECH CO LTD

ASUSTECH CO LTD

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

DDR2 SODIMM

DDR2 SODIMM

DDR2 SODIMM

9 69 14 2007

9 69 14 2007

9 69 14 2007

Rev

Rev

Rev

2 0

2 0

2 0

Page 10

5 4 3 2 1

+0 9V

MEM_MA_ADD[0 15]6 9

D D

MEM_MA_BANK[0 2]6 9

MEM_MA_CAS_L6 9

MEM_MA_RAS_L6 9

MEM_MA_WE_L69

MEM_MA_CKE06 9

MEM_MA_CKE16 9

MEM_MA0_CS_L06 9

MEM_MA0_CS_L16 9

MEM_MA0_CS_L26 9

MEM_MA0_CS_L36 9

MEM_MA0_ODT06 9

MEM_MA0_ODT16 9

C C

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

5 6

47Ohm

47Ohm

7 8

47Ohm

47Ohm

3 4

47Ohm

47Ohm

1 2

47Ohm

47Ohm

7 8

47Ohm

47Ohm

3 4

47Ohm

47Ohm

5 6

47Ohm

47Ohm

5 6

47Ohm

47Ohm

5 6

47Ohm

47Ohm

7 8

47Ohm

47Ohm

5 6

47Ohm

47Ohm

7 8

47Ohm

47Ohm

1 2

47Ohm

47Ohm

1 2

47Ohm

47Ohm

1 2

47Ohm

47Ohm

3 4

47Ohm

47Ohm

3 4

47Ohm

47Ohm

3 4

47Ohm

47Ohm

3 4

47Ohm

47Ohm

7 8

47Ohm

47Ohm

1 2

47Ohm

47Ohm

1 2

47Ohm

47Ohm

7 8

47Ohm

47Ohm

1 2

47Ohm

47Ohm

3 4

47Ohm

47Ohm

5 6

47Ohm

47Ohm

5 6

47Ohm

47Ohm

5 6

47Ohm

47Ohm

7 8

47Ohm

47Ohm

3 4

47Ohm

47Ohm

7 8

47Ohm

47Ohm

1 2

47Ohm

47Ohm

RN1001C

RN1001C

RN1002D

RN1002D

RN1000B

RN1000B

RN1011A

RN1011A

RN1000D

RN1000D

RN1011B

RN1011B

RN1000C

RN1000C

RN1003C

RN1003C

RN1011C

RN1011C

RN1011D

RN1011D

RN1002C

RN1002C

RN1003D

RN1003D

RN1005A

RN1005A

RN1004A

RN1004A

RN1000A

RN1000A

RN1003B

RN1003B

RN1005B

RN1005B

RN1001B

RN1001B

RN1002B

RN1002B

RN1007D

RN1007D

RN1001A

RN1001A

RN1002A

RN1002A

RN1005D

RN1005D

RN1003A

RN1003A

RN1004B

RN1004B

RN1007C

RN1007C

RN1005C

RN1005C

RN1004C

RN1004C

RN1001D

RN1001D

RN1007B

RN1007B

RN1004D

RN1004D

RN1007A

RN1007A

+0 9V

C1000

C1000

0 1UF/16V

0 1UF/16V

C1001

C1001

0 1UF 16V

0 1UF 16V

C1002

0 1UF/16V

0 1UF/16V

C1003

C1003

0 1UF 16V

0 1UF 16V

C1004

C1004

0 1UF/16V

0 1UF/16V

C1005

C1005

0 1UF/16V

0 1UF/16V

C1006

C1006

0 1UF 16V

0 1UF 16V

C1007

C1007

0 1UF/16V

0 1UF/16V

C1002

+0 9V

C1013

C1008

C1008

0 1UF/16V

0 1UF/16V

C1009

C1009

0 1UF 16V

0 1UF 16V

C1011

C1011

C1010

C1010

0 1UF 16V

0 1UF 16V

0 1UF/16V

0 1UF/16V

place behind DIMMs

C1012

C1012

0 1UF/16V

0 1UF/16V

C1013

0 1UF/16V

0 1UF/16V

C1014

C1014

0 1UF 16V

0 1UF 16V

C1015

C1015

0 1UF/16V

0 1UF/16V

+1 8V

+0 9V

MEM_MB_ADD[0 15]6 9

MEM_MB_BANK[0 2]6 9

MEM_MB_CAS_L6 9

MEM_MB_RAS_L6 9

MEM_MB_WE_L69

B B

MEM_MB_CKE06 9

MEM_MB_CKE16 9

MEM_MB0_CS_L06 9

MEM_MB0_CS_L16 9

MEM_MB0_CS_L26 9

MEM_MB0_CS_L36 9

MEM_MB0_ODT06 9

MEM_MB0_ODT16 9

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

3 4

47Ohm

47Ohm

5 6

47Ohm

47Ohm

1 2

47Ohm

47Ohm

7 8

47Ohm

47Ohm

7 8

47Ohm

47Ohm

1 2

47Ohm

47Ohm

5 6

47Ohm

47Ohm

3 4

47Ohm

47Ohm

3 4

47Ohm

47Ohm

5 6

47Ohm

47Ohm

3 4

47Ohm

47Ohm

1 2

47Ohm

47Ohm

7 8

47Ohm

47Ohm

5 6

47Ohm

47Ohm

5 6

47Ohm

47Ohm

7 8

47Ohm

47Ohm

1 2

47Ohm

47Ohm

5 6

47Ohm

47Ohm

1 2

47Ohm

47Ohm

5 6

47Ohm

47Ohm

7 8

47Ohm

47Ohm

7 8

47Ohm

47Ohm

5 6

47Ohm

47Ohm

3 4

47Ohm

47Ohm

7 8

47Ohm

47Ohm

3 4

47Ohm

47Ohm

3 4

47Ohm

47Ohm

1 2

47Ohm

47Ohm

3 4

47Ohm

47Ohm

1 2

47Ohm

47Ohm

1 2

47Ohm

47Ohm

7 8

47Ohm

47Ohm

RN1008B

RN1008B

RN1010C

RN1010C

RN1008A

RN1008A

RN1010D

RN1010D

RN1009D

RN1009D

RN1014A

RN1014A

RN1009C

RN1009C

RN1009B

RN1009B

RN1014B

RN1014B

RN1014C

RN1014C

RN1010B

RN1010B

RN1009A

RN1009A

RN1014D

RN1014D

RN1015C

RN1015C

RN1006C

RN1006C

RN1006D

RN1006D

RN1012A

RN1012A

RN1008C

RN1008C

RN1010A

RN1010A

RN1013C

RN1013C

RN1015D

RN1015D

RN1013D

RN1013D

RN1012C

RN1012C

RN1006B

RN1006B

RN1008D

RN1008D

RN1013B

RN1013B

RN1012B

RN1012B

RN1015A

RN1015A

RN1015B

RN1015B

RN1013A

RN1013A

RN1006A

RN1006A

RN1012D

RN1012D

+0 9V

C1016

C1016

0 1UF/16V

0 1UF/16V

C1017

C1017

0 1UF 16V

0 1UF 16V

C1018

C1018

0 1UF/16V

0 1UF/16V

C1019

0 1UF 16V

0 1UF 16V

0 1UF/16V

0 1UF/16V

C1021

C1021

0 1UF/16V

0 1UF/16V

C1022

C1022

0 1UF 16V

0 1UF 16V

C1023

C1023

0 1UF/16V

0 1UF/16V

C1020

C1020

C1019

+0 9V

C1031

C1024

C1024

0 1UF/16V

0 1UF/16V

C1025

C1025

0 1UF 16V

0 1UF 16V

C1026

C1026

0 1UF/16V

0 1UF/16V

C1027

C1027

0 1UF 16V

0 1UF 16V

C1028

C1028

0 1UF/16V

0 1UF/16V

C1029

C1029

0 1UF/16V

0 1UF/16V

C1030

C1030

0 1UF 16V

0 1UF 16V

C1031

0 1UF/16V

0 1UF/16V

place behind DIMMs

+1 8V

Page 11

5

D D

HT_CPU_RX_CAD_L[0 15]5

C C

HT_CPU_RX_CLK_H15

HT_CPU_RX_CLK_L15

HT_CPU_RX_CLK_H05

HT_CPU_RX_CLK_L05

HT_CPU_RX_CTL_H05

HT_CPU_RX_CTL_L05

VDDHT_PKG

B B

4

HT_CPU_RX_CAD_H15

HT_CPU_RX_CAD_L15

HT_CPU_RX_CAD_H14

HT_CPU_RX_CAD_L14

HT_CPU_RX_CAD_H13

HT_CPU_RX_CAD_L13

HT_CPU_RX_CAD_H12

HT_CPU_RX_CAD_L12

HT_CPU_RX_CAD_H11

HT_CPU_RX_CAD_L11

HT_CPU_RX_CAD_H10

HT_CPU_RX_CAD_L10

HT_CPU_RX_CAD_H9

HT_CPU_RX_CAD_L9

HT_CPU_RX_CAD_H8

HT_CPU_RX_CAD_L8

HT_CPU_RX_CAD_H7

HT_CPU_RX_CAD_L7

HT_CPU_RX_CAD_H6

HT_CPU_RX_CAD_L6

HT_CPU_RX_CAD_H5

HT_CPU_RX_CAD_L5

HT_CPU_RX_CAD_H4

HT_CPU_RX_CAD_L4

HT_CPU_RX_CAD_H3

HT_CPU_RX_CAD_L3

HT_CPU_RX_CAD_H2

HT_CPU_RX_CAD_L2

HT_CPU_RX_CAD_H1

HT_CPU_RX_CAD_L1

HT_CPU_RX_CAD_H0

HT_CPU_RX_CAD_L0

HT_CPU_RX_CLK_H1

HT_CPU_RX_CLK_L1

HT_CPU_RX_CLK_H0

HT_CPU_RX_CLK_L0

HT_CPU_RX_CTL_H0

HT_CPU_RX_CTL_L0

R1100 499OhmR1100 49 9Ohm

1 2

R1101 49 9OhmR1101 49 9Ohm

1 2

HT_RXCALP

HT_RXCALN

R19

R18

R21

R22

U22

U21

U18

U19

W19

W20

AC21

AB22

AB20

AA20

AA19

Y19

T24

R25

U25

U24

V23

U23

V24

V25

AA25

AA24

AB23

AA23

AB24

AB25

AC24

AC25

W21

W22

Y24

W25

P24

P25

A24

C24

U1100A

U1100A

HT_RXCAD15 P