Page 1

5

4

3

2

1

FILE LIST

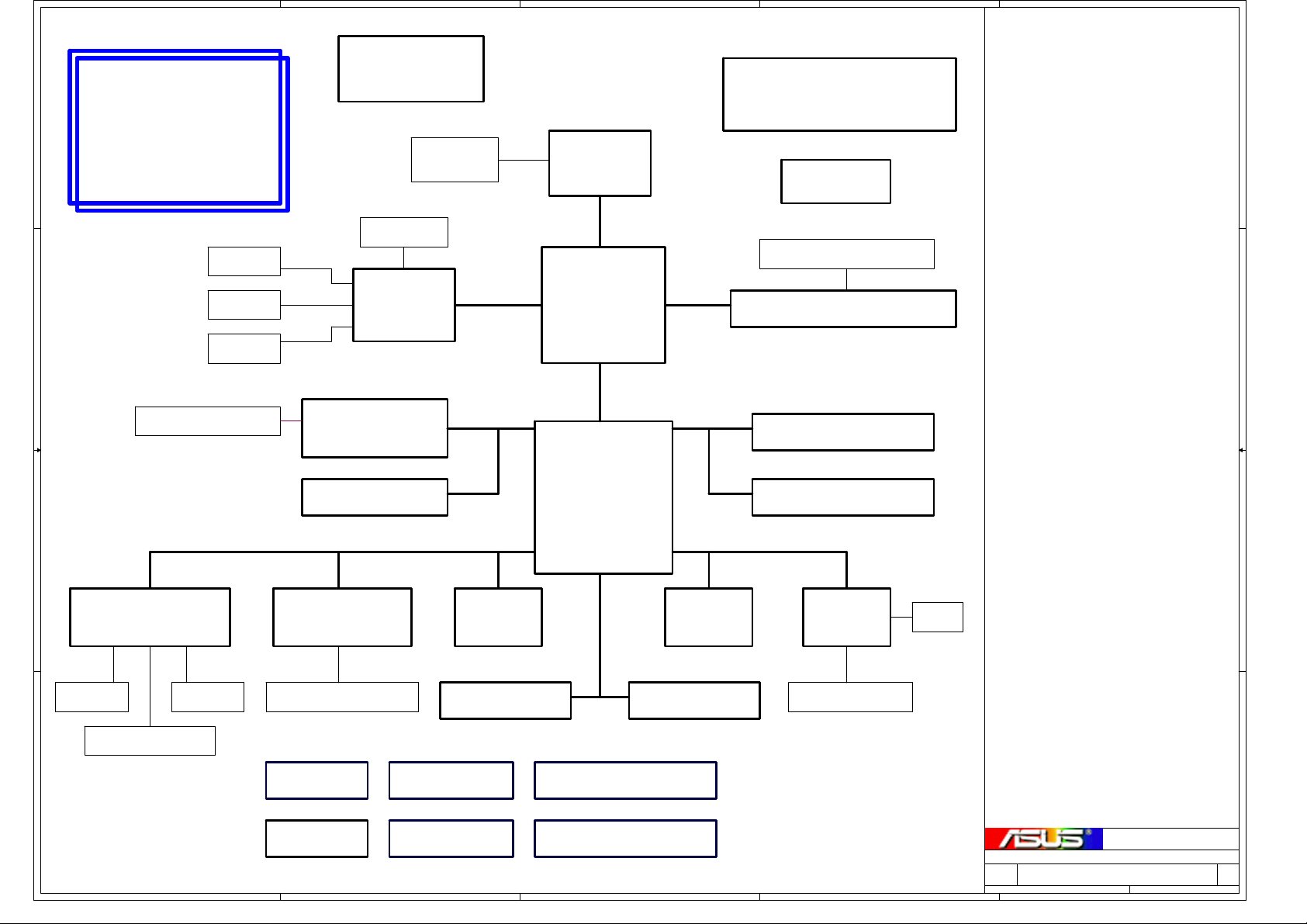

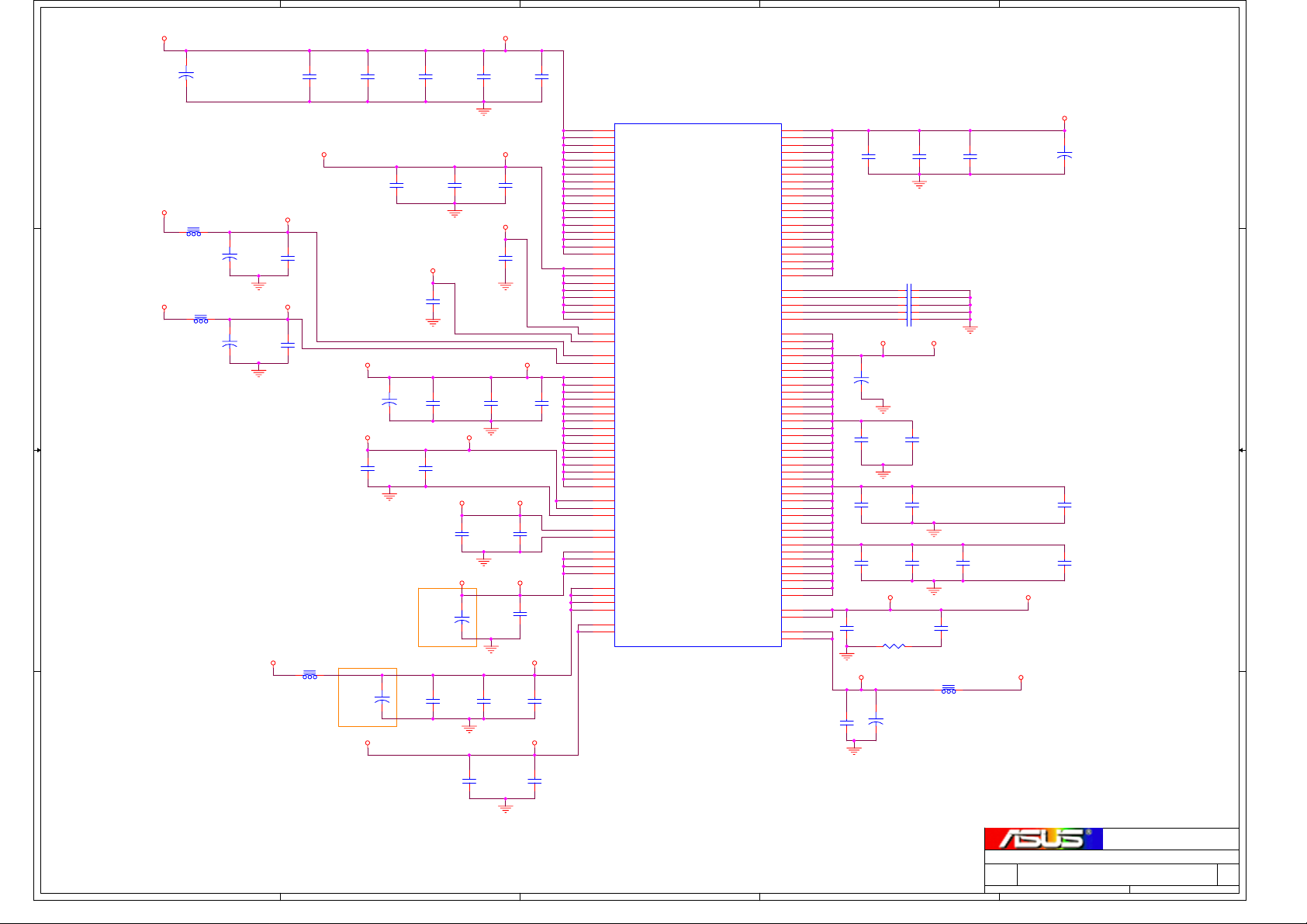

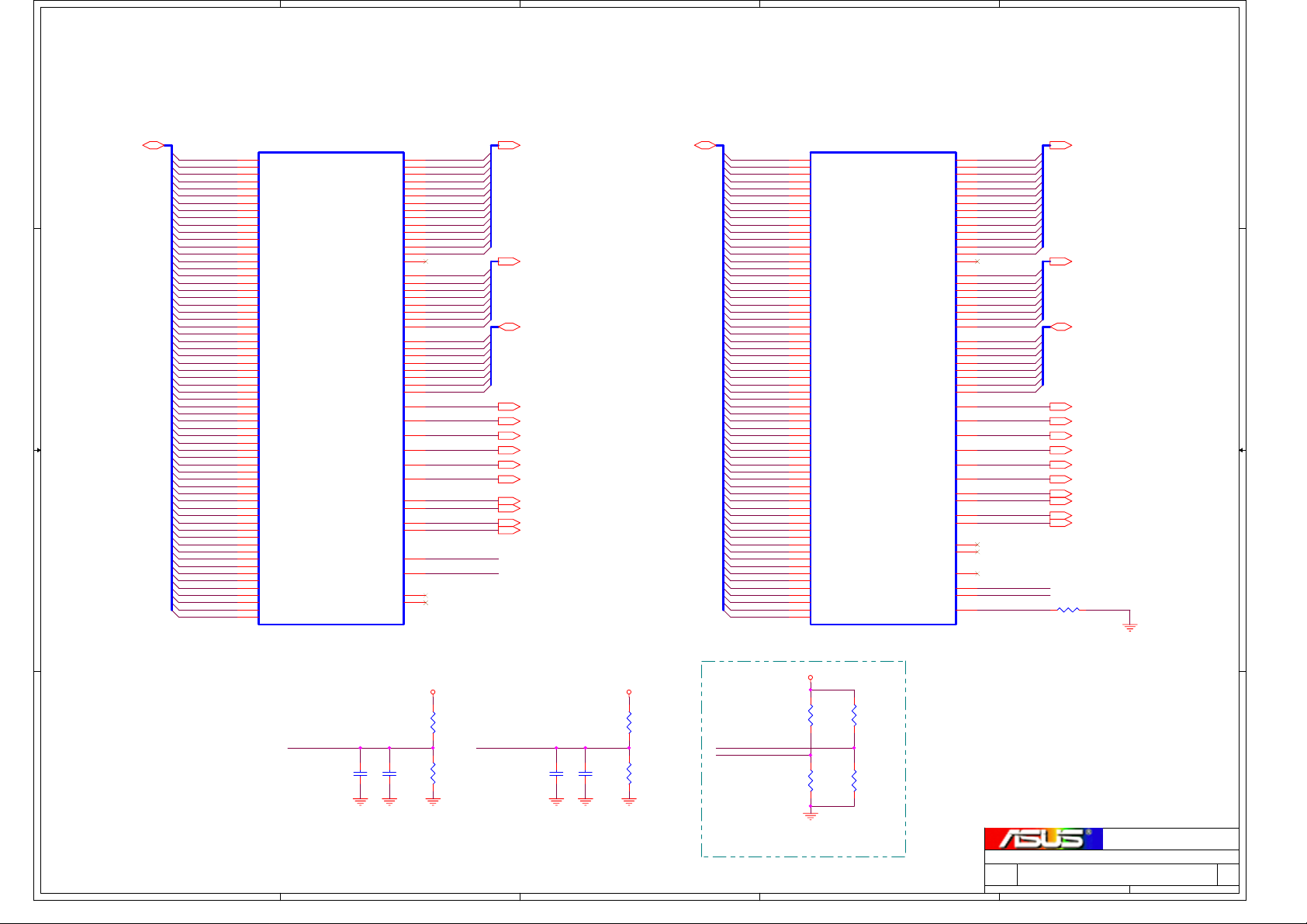

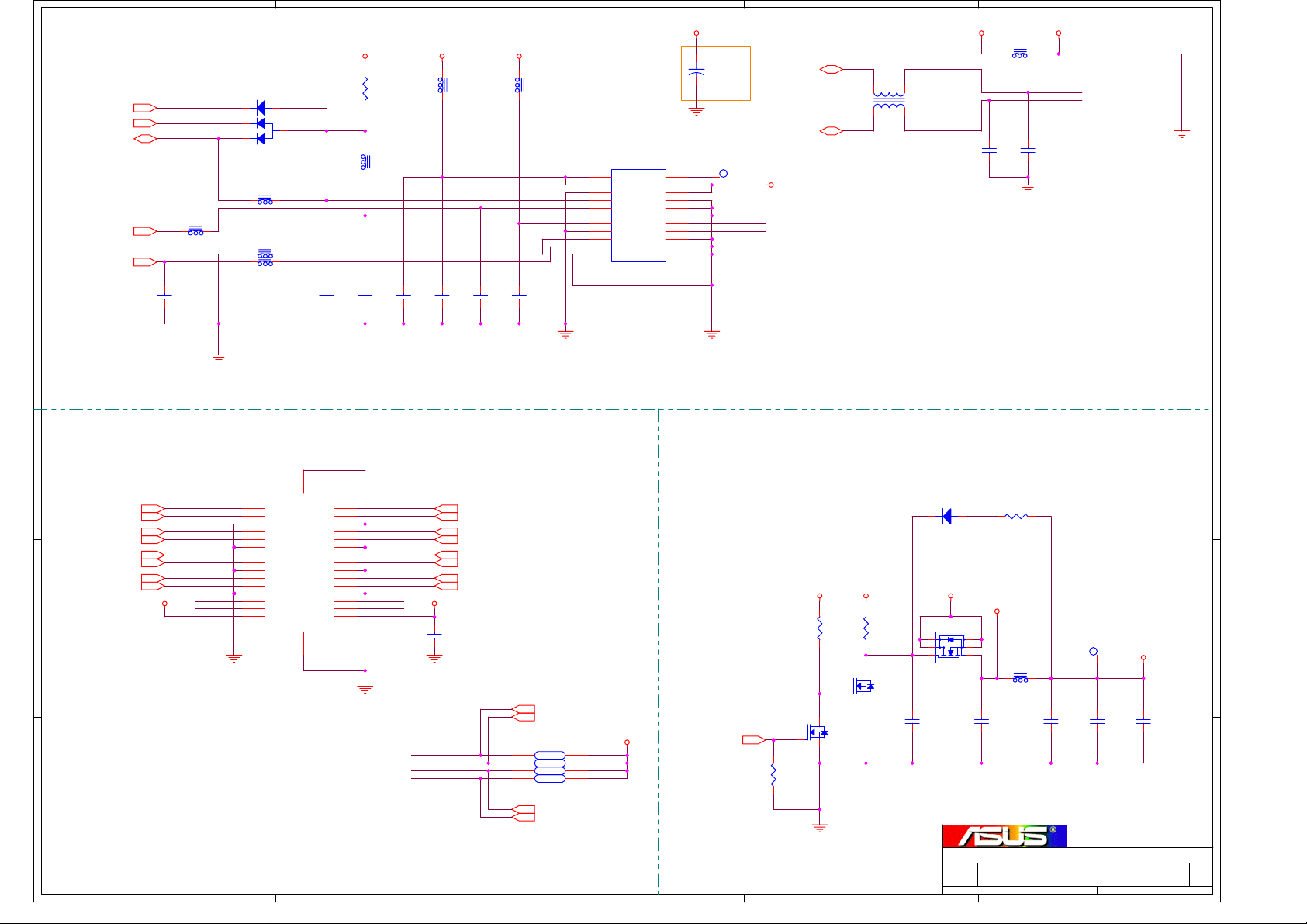

01_BLOCK DIAGRAM

CLOCK GEN

A6G

D D

ICS 950815

Page 23

BLOCK

THERMAL

DIAGRAM

SENSOR

Page 5

VRAM *4

LCD

Page 17

CRT

Page 18

C C

TV-OUT

Page 18

AUDIO AMP & MIC

Page 36,37

LVDS

RGB

AC'97 CODEC

Realtek ALC650

Page 15,16

VGA

ATI M11-P

Page 12,13,14

Page 35

AGP 4X

AC97

MDC

Page 36

PCI

B B

CARDBUS/1394

RICOH R5C593

Page 26,27

1394

Page 26

PCMCIA

Page 28

LAN KBC

Realtek RTL8100CL

Page 24

LAN & Modem Jack

Page 38

Card Reader

Page 27

A A

Audio DJ

Page 40

DC FAN

Page 40

5

Screw Hole

EMI Cap.

4

MINIPCI

Page 25

USB CCD

Page 52

Page 52

CPU

BANIAS

24.5W

Page 3,4

PSB

NORTH

BRIDGE

Intel 855GME

3.8W

Page 6,7,8,9

HUB

SOUTH

BRIDGE

Intel ICH4-M

2.9W

Page 19,20,21,22

USB 2.0

USB CON *4

Page 17

Discharge Circuit

Function Key

3

DDR

DUAL DDR SO-DIMM

IDE

SECONDARY IDE

LPC

M38857

Page 31

Page 39

Page 34

Page 41

POWER

(IMVP4)

Page 43,44,45,46,47,48,49,50

VGA POWER

Page 51

DDR TERMINATION

Page 11

PRIMARY IDE

Page 29

Page 30

SIO

ITE8705

Page 32

PRINTER PORT

Page 33

2

Page 10

SIR

Page 33

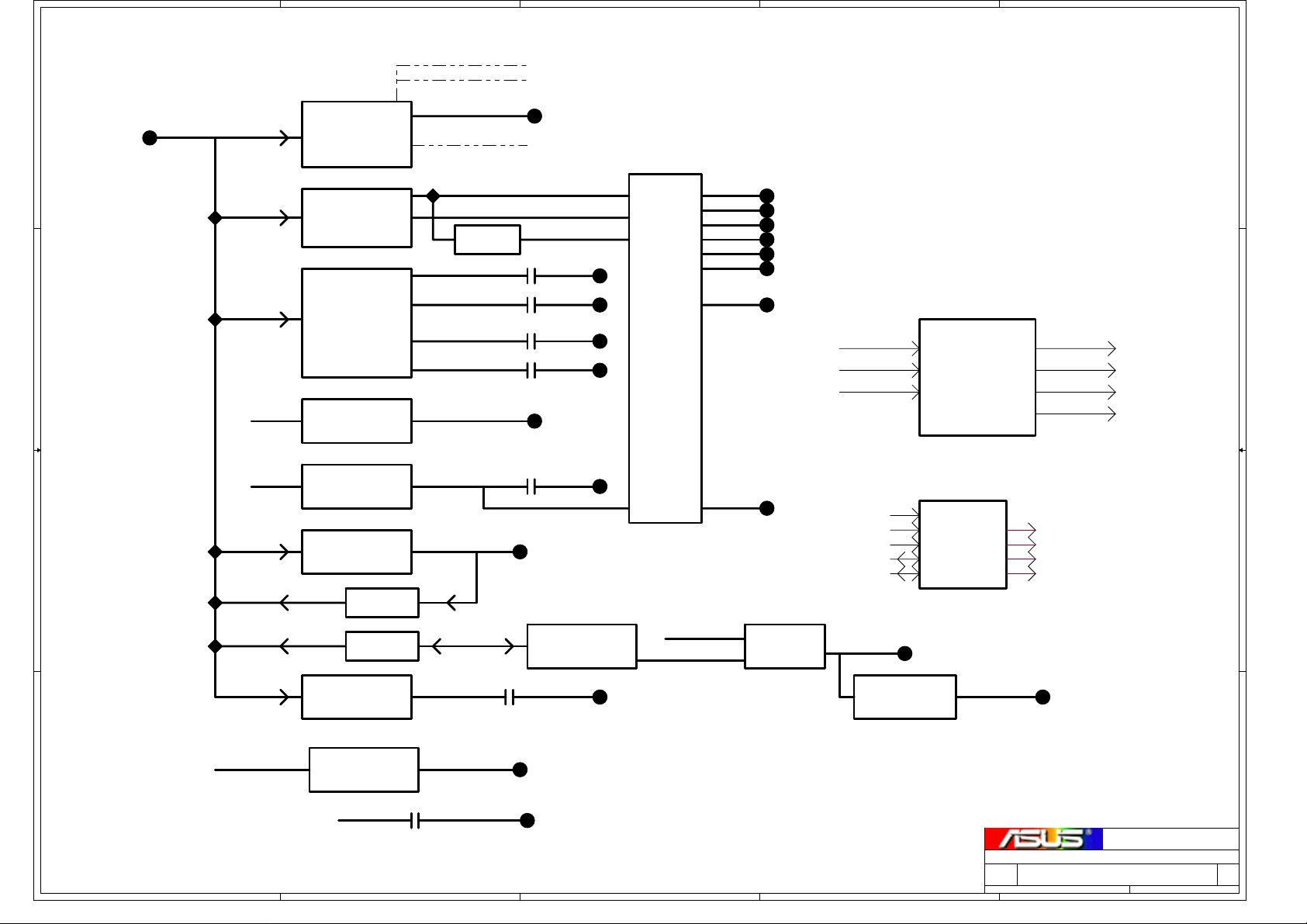

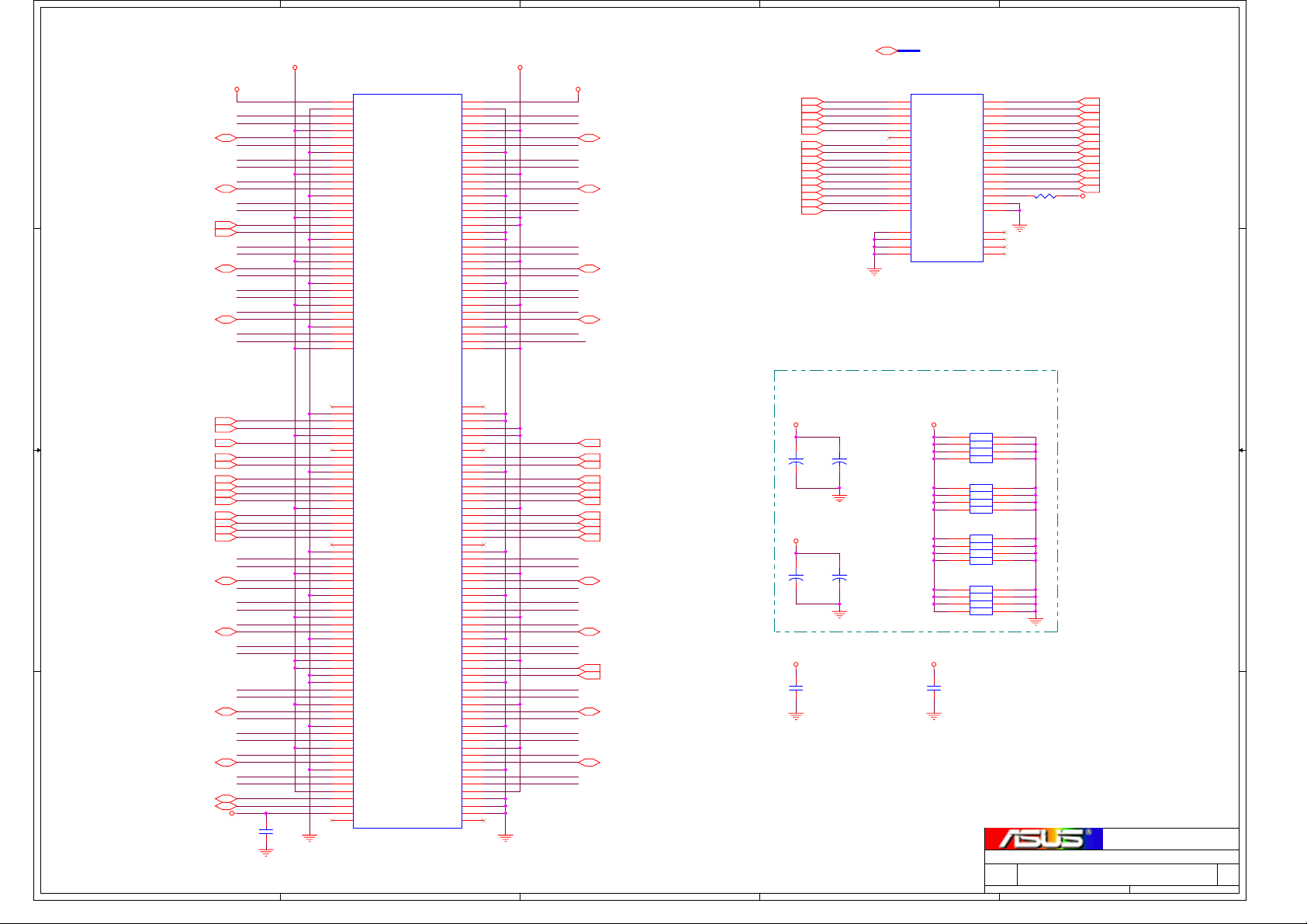

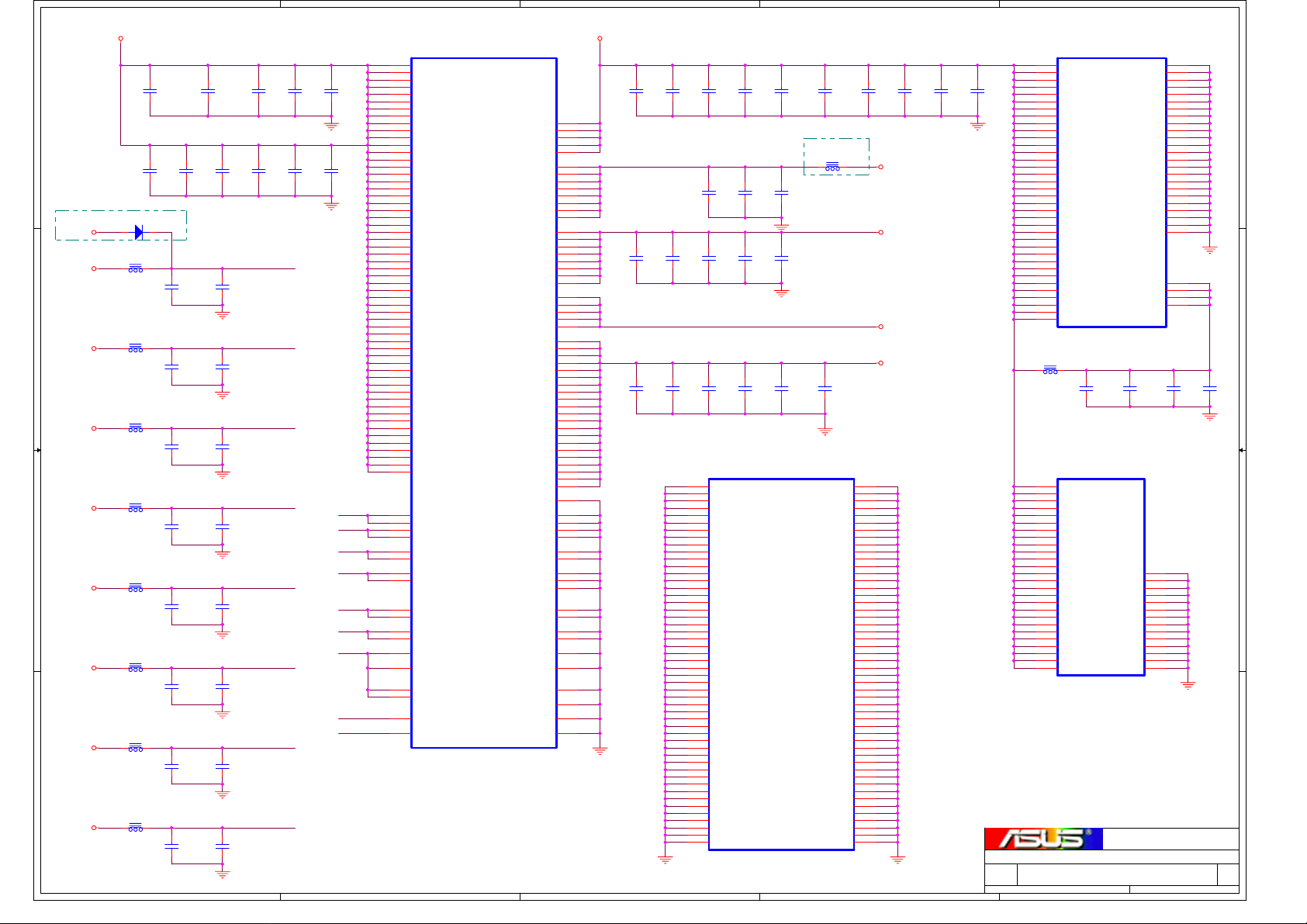

02_POWER DIAGRAM

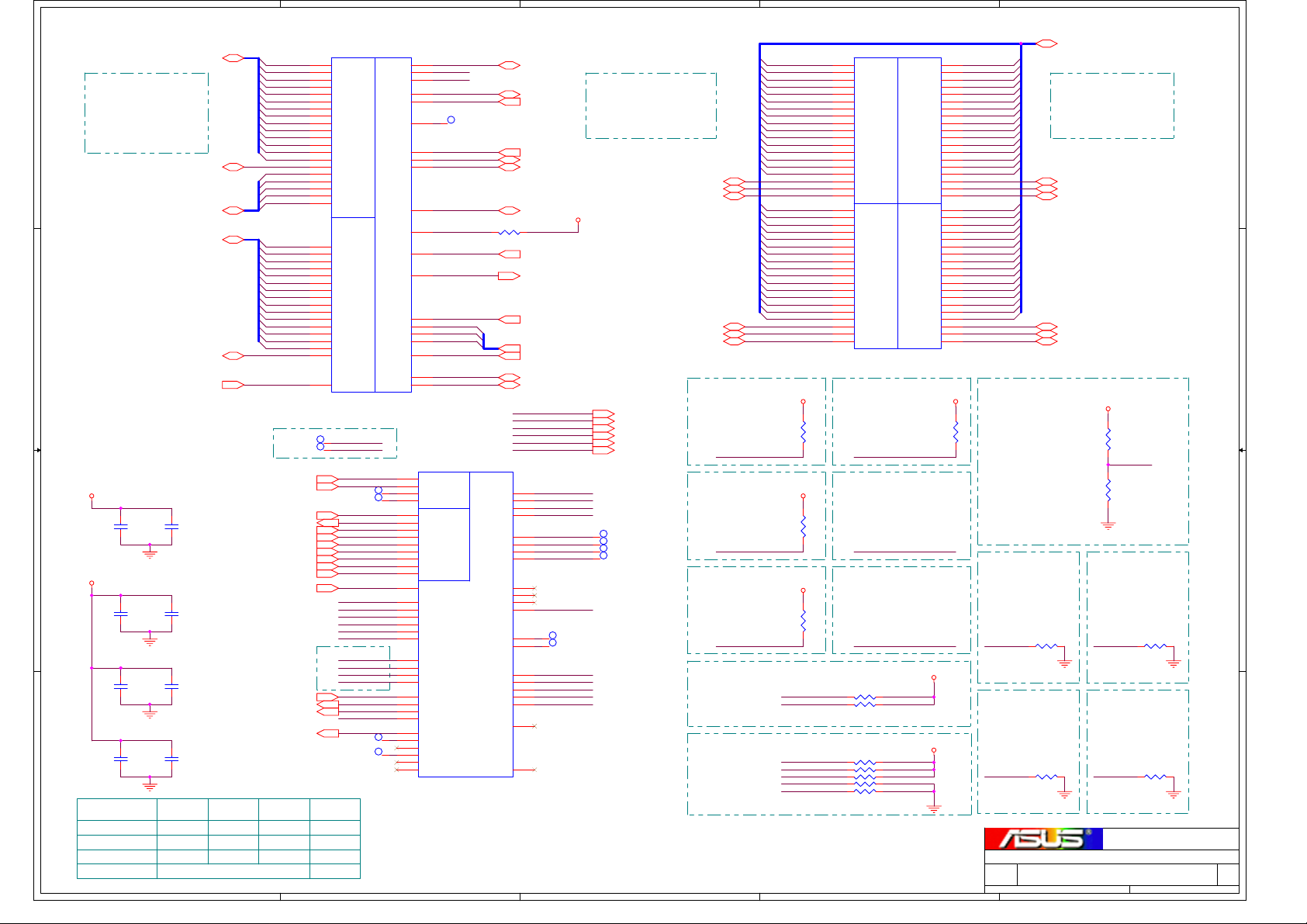

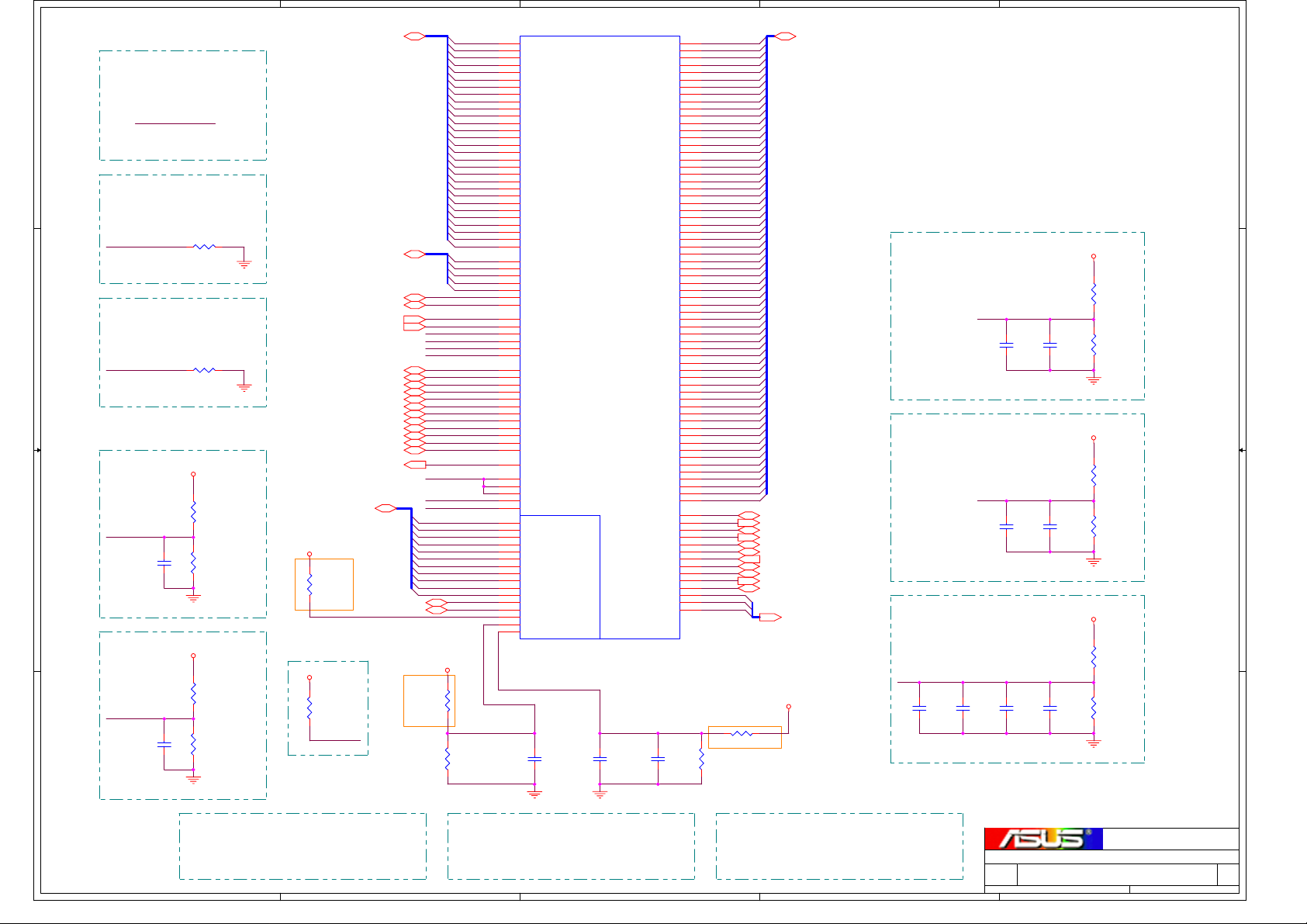

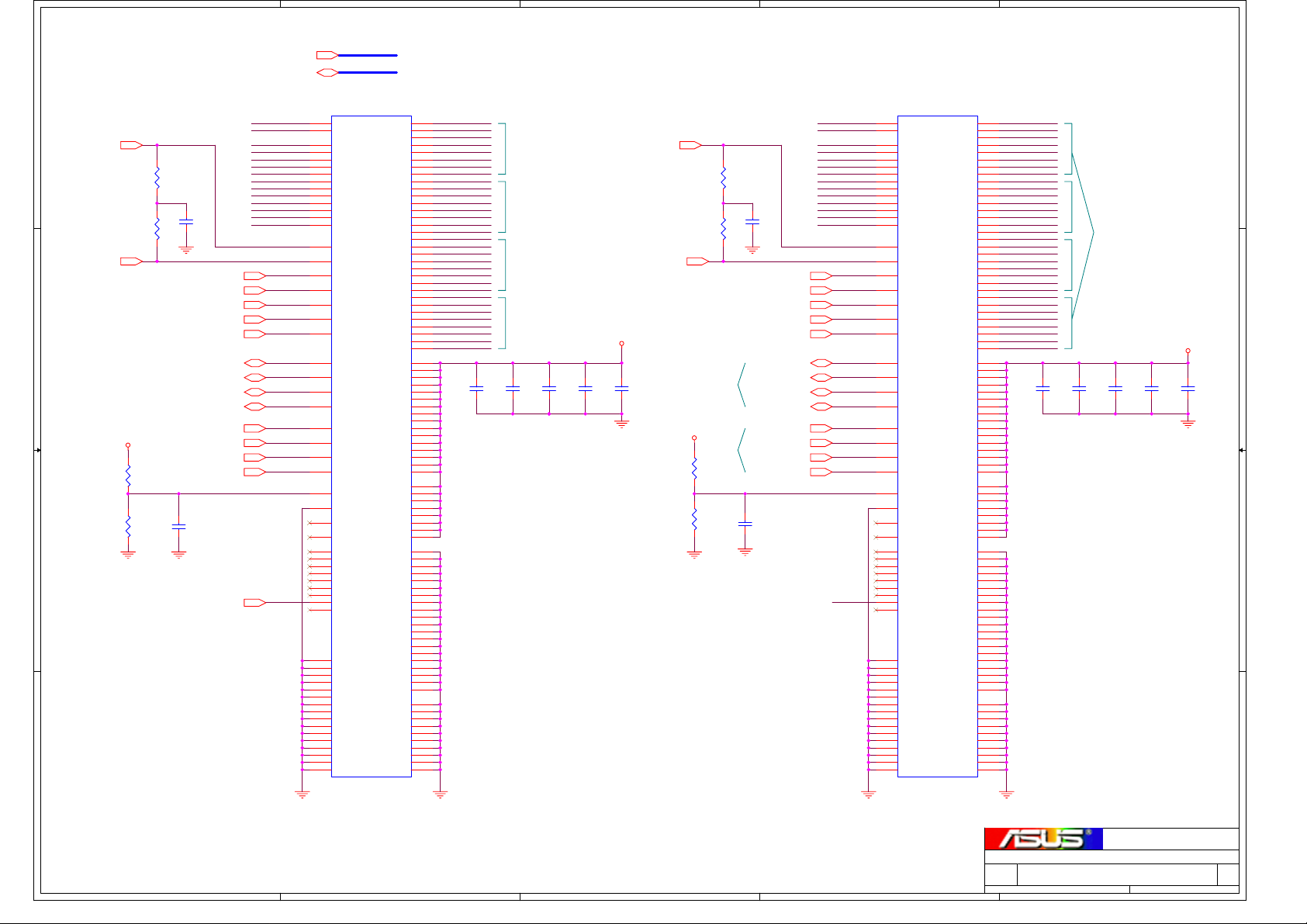

03_CPU-BANIAS(HOST)

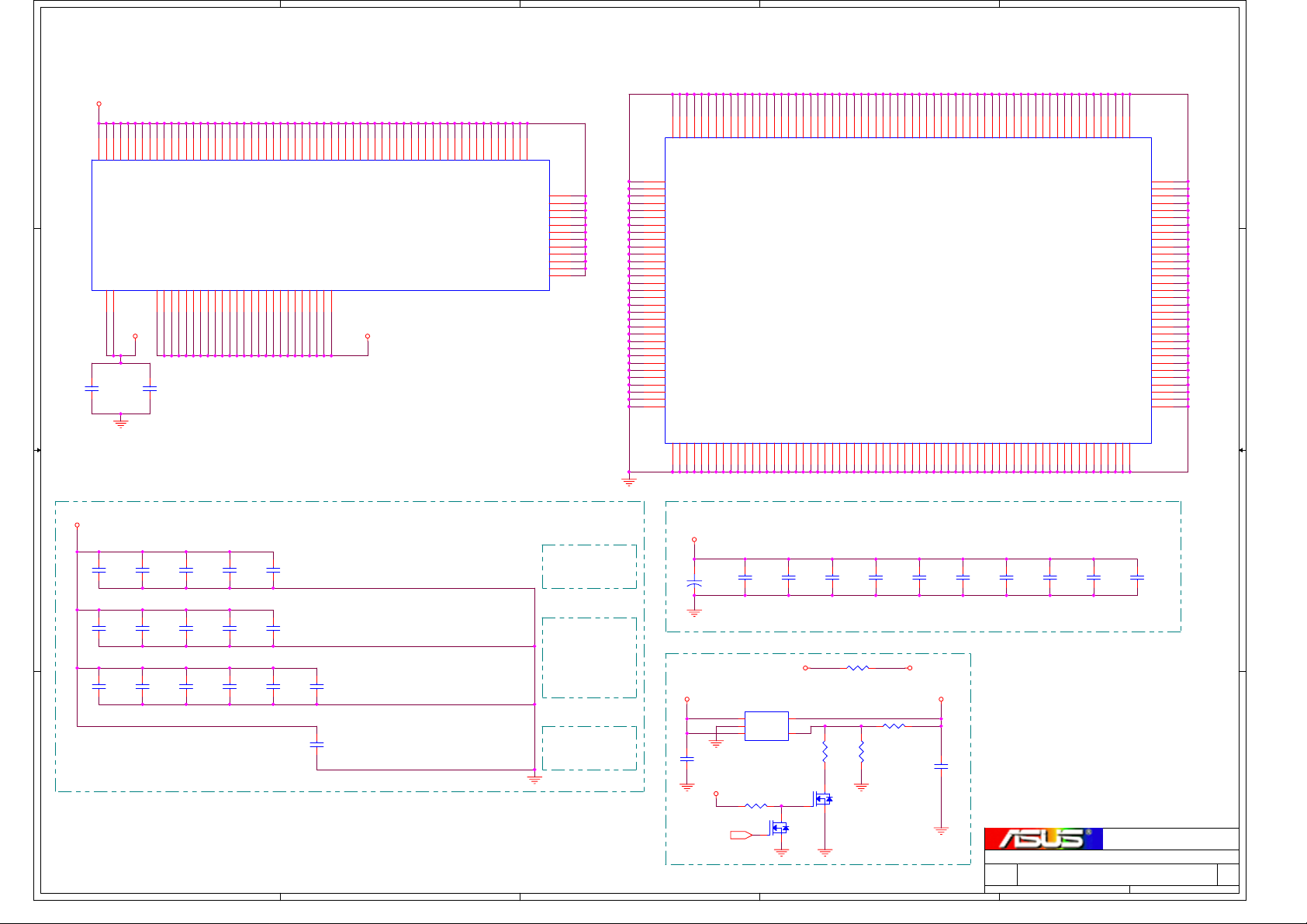

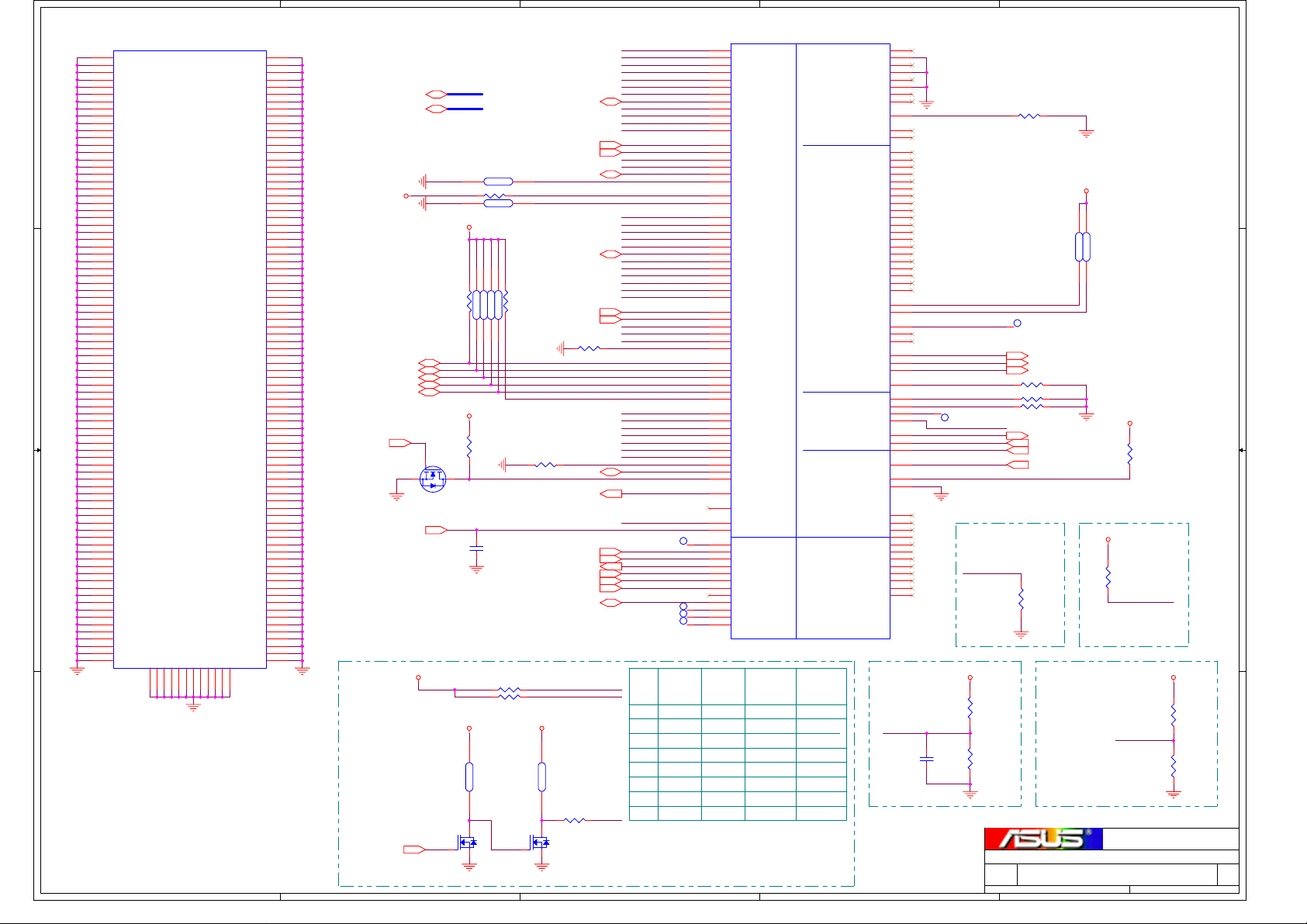

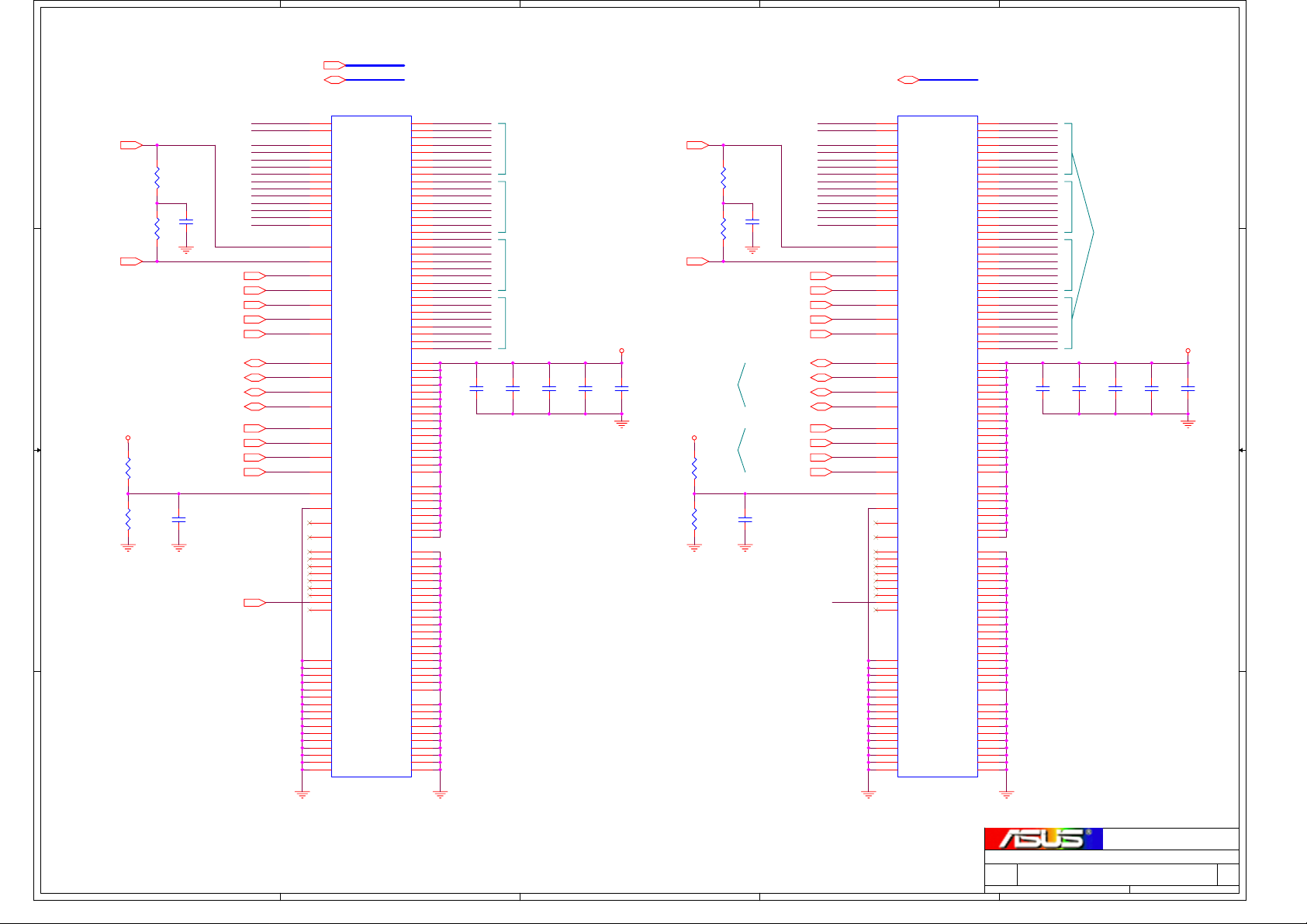

04_CPU-BANIAS(PWR)

05_THERMAL SENSOR

06_NB-MCHM(DDR)

07_NB-MCHM(HOST)

08_NB-MCHM(VGA)

09_NB-MCHM(PWR)

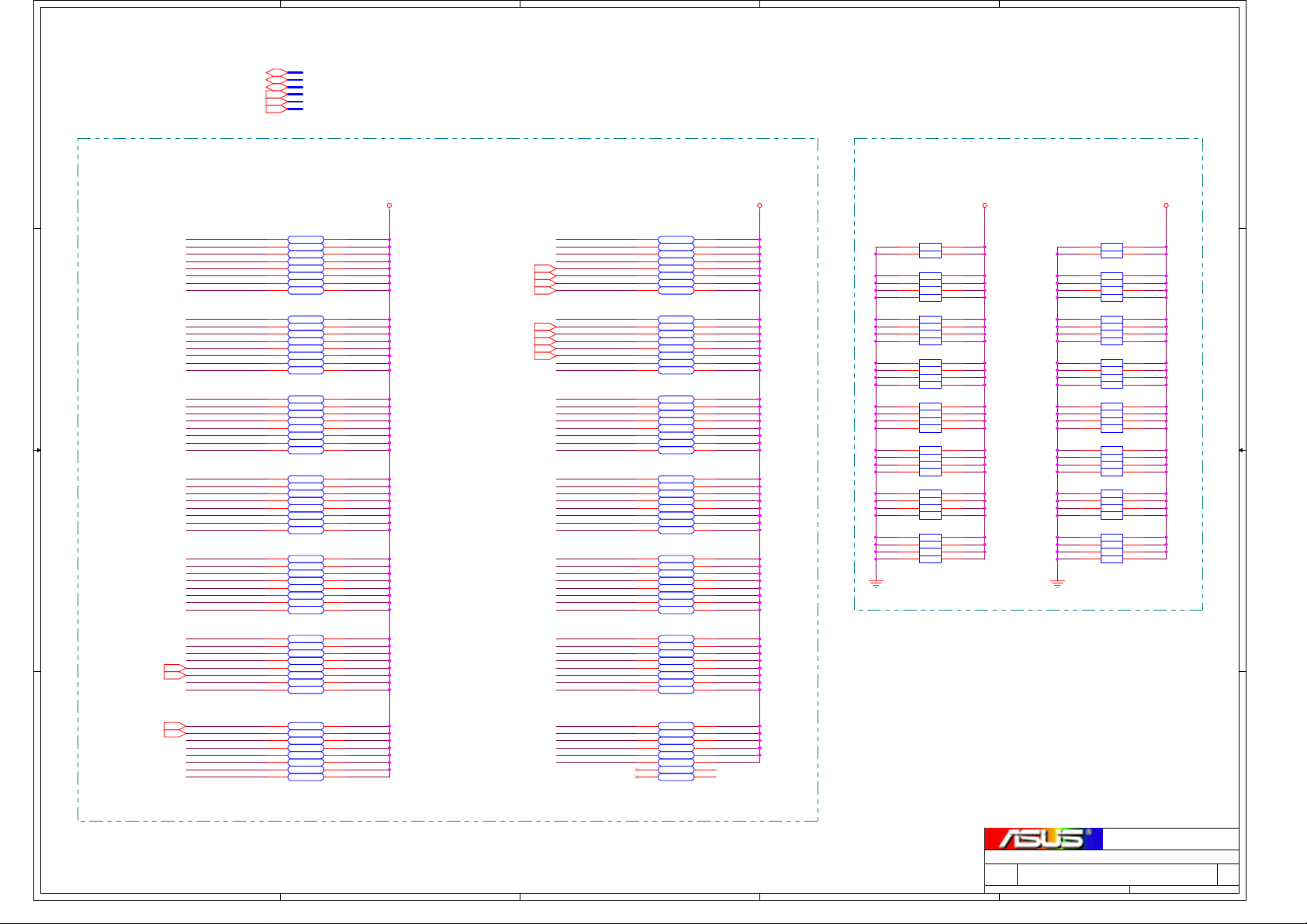

10_DUAL DDR SODIMM

11_DDR TREMINATION

12_ATI M11-P(AGP,LVDS)

13_ATI M11-P(MEMORY IF)

14_ATI M11-P(PWR)

15_VRAM(A CHANNEL)

16_VRAM(B CHANNEL)

17_LVDS & BACKLIGHT

18_CRT & TV-OUT

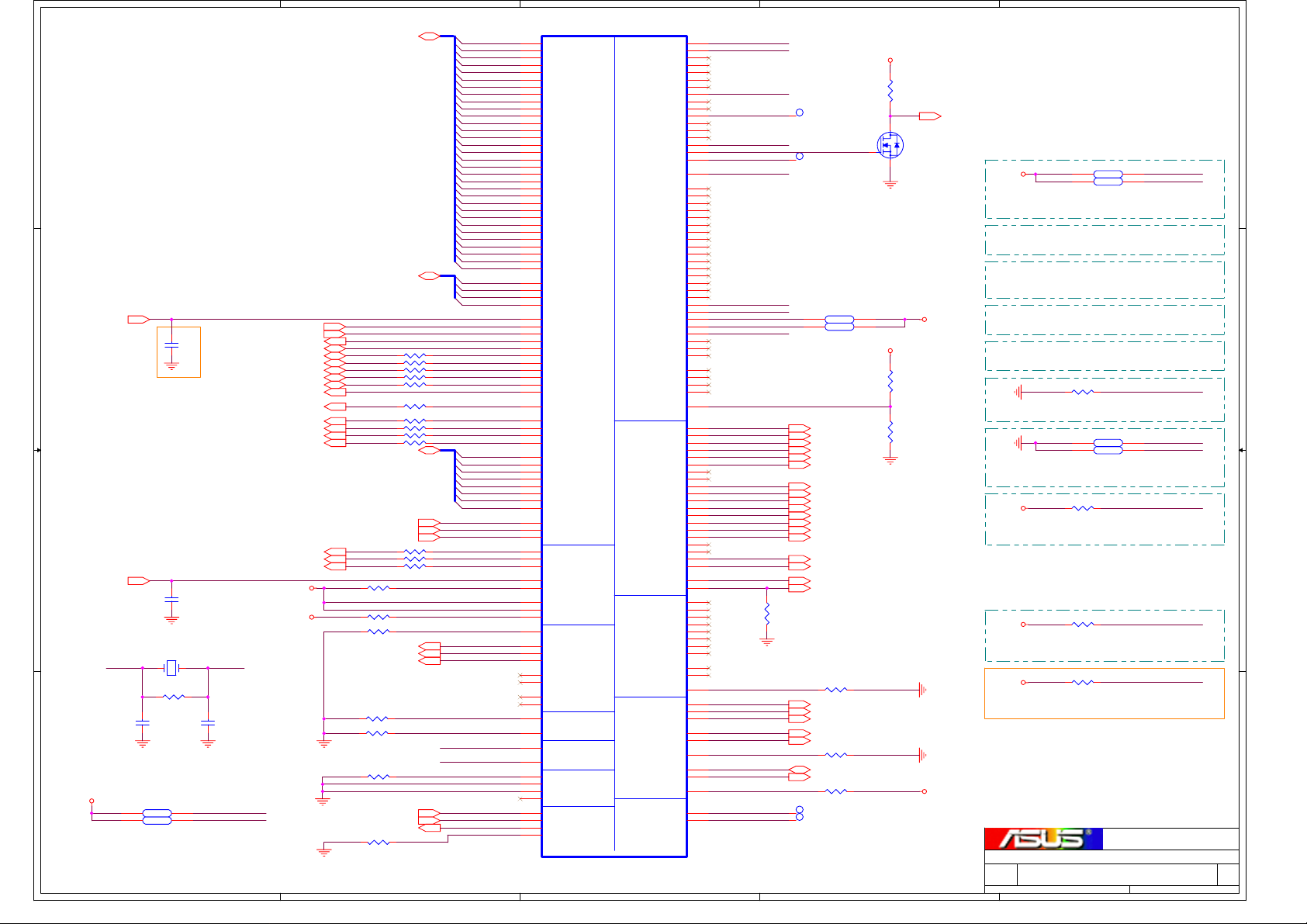

19_ICH4-M(HUB_PCI)

20_ICH4-M(H_U_IDE_PM)

21_ICH4-M(PWR)

22_ICH4-M(PULLUP)

23_CLOCK-ICS950815

24_LAN-RTL8100CL

25_MINIPCI

26_CB1394-R5C593 (1)

27_CB1394-R5C593 (2)

28_PCMCIA SOCKET

29_IDE-HDD

30_IDE-ODD

31_KBC-M38857

32_SIO-ITE8705 & FWH

33_LPT PORT & IR

34_DISCHARGE CIRCUIT

35_CODEC-ALC650

36_AUDIO AMP

37_MIC

38_MDC & RJ45 & RJ11

39_USB

40_FAN & AUDIO DJ

41_FUNCTION KEY

42_PWR & RESET SEQ

43_VCORE

44_1.25V&1.8V

45_2.5V&1.5V&1.2V& 1. 05 V

46_SYSTEM

47_LOAD SWITCH

48_CHARGER

49_PIC16C54

50_BATLOW/SD#

51_VGACORE

52_SCREW HOLE & EMI CAP

53_M/B SETTING

54_REVISION HISTORY

Title :

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

Date: Sheet

Engineer:

A6G

1

BLOCK DIAGRAM

John Hung

154Friday, October 15, 2004

of

Rev

1.1

Page 2

5

System work voltage

Adapter in : 19.5 ~18.5 V

Battery in : 16.8 ~ 11.6V

CPU_VRON

D D

AC_BAT_SYS

MAX1987

4

3

2

1

+V1.25S : JP4,5 page 39

+V2.5 : JP6 page 40

+V1.2S : JP7 page 40

VR_VID0-VR_VID5

PM_STPCPU#.,PM_DPRSLPVR.,PCI#.,MCH_OK.,CLK_EN#

+VCCP : JP9 page 40

+V5S : JP13 page 42

+V5 : JP14 page 42

+VCORE

(25A)

+V1.5SUS : JP15 page 39

+V1.8 : JP16,19 page 39

VRM_PWRGD

+V1.8S : JP17 page42

+V12 : JP18 page 42

+V1.5S : JP22 page 40

SUSC#.

(3V_ON)

LTC3728

(Regulator)

SUSB#

SUSC#

+1.5VO

+2.5VO

78L12

(2A)

+5VO

+V3.3SUS

+12VO

(0.15A)

+V1.5S

+V2.5

(5A)

(5A)

SUSB#

SUSB#

SUSC#

SUSB#

SUSB#

+V5S

+V3S

+V5

+V3

+V12S

+V12

+V1.5S(5A)

+V5A : JP24 page 40

+V3.3A : JP26 or 27 page 39

+V3.3S : JP28 page 42

+V3.3 : JP29 page 42

TPS5130

C C

+5VAO

SUSB#

SUSB#

+1.2VO

+1.05VO

SUSB#

+V2.5

CM8562

+V1.25S

(2A)

(1A)

(2A)

+V1.2S

+VCCP

SWITCH

A/D_VIN

BAT_S

TS#

Power

Signal

Circuit

SHUT_DOWN#

BAT_IN#_OC

ACIN_OC

AC_APR_UC

(Regulator)

SUSC#

BAT

(1A)

+V1.8

SUSB#

+V1.8S

TS#

SUSB#

AC_APR_UC

SMC_BAT

SMD_BAT

PIC16C54C

CHG EN#

CHG LED_UP

PWR LED_UP

BAT_LLOW

+2.5VO

MIC37101-1.8

+1.8VO

LDO

PIC + TL494

B B

(Charge)

FDS6679

(20mA)

FD6JK3TP

MIC5223MB

A/D_VIN

+3VALWAYS_M

78L05

(Regulator)

+V3.3A

(Regulator)

+V3.3SUS

A A

CM2855

(LDO)

+5VAO

5

4

+V1.5SUS

+5VALWAYS

+5VO

+5VCHG

3

(100mA)

SWITCH

(F02JK2E)

+5VLCM

LM4040BIM

(Regulator)

2

+2.5VREF

(500uA)

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

Date: Sheet

A6G

Title :

Engineer:

1

POWER DIAGRAM

Adams Lin

254Friday, October 15, 2004

of

Rev

1.1

Page 3

5

4

3

2

1

H_A#[16:3]7

ADDR GROUP 0 -> L1

ADDR GROUP 1 -> L4

SPACE >= 1:2

D D

C C

B B

A A

STROBE SPACE >= 1:2

GROUP SPACE >= 20 mils

LENGTH: 0.5" - 6.5"

H_ADSTB#07

H_REQ#[4:0]7

H_A#[31:17]7

H_ADSTB#17

H_DPWR#8

CPU PLL CIRCUITS

1.71V - 1.89V(+/- 5%)

S0-S1M: 0.3A

+V1.8S_PROC

+V1.8S_VCCA

+V1.8S_F26

12

C26

0.01UF/10V

+V1.8S_AC26

12

C325

0.01UF/10V

+V1.8S_N1

12

C104

0.01UF/10V

+V1.8S_B1

12

C98

0.01UF/10V

12

C24

10UF/6.3V

12

C322

10UF/6.3V

12

C100

10UF/6.3V

12

C103

10UF/6.3V

Celeron

Banias

Frequency 133

VCCA[1:3]

VCCA[0]

1.8V

1.8V

1.8V

1.8V

H_A#16

H_A#15

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

H_A#6

H_A#5

H_A#4 H_D#3

H_A#3

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

1"-6.5"

T92 TPC28t

T95 TPC28t

_CLK_CPU_BCLK23

_CLK_CPU_BCLK#23

H_A20M#20

H_FERR#20

H_IGNNE#20

H_DPSLP#8,20

H_CPUSLP#20

H_INTR20

H_NMI20

H_SMI#20

H_STPCLK#20

H_PWRGD20

H_THERMDA5

H_THERMDC5

H_THRMTRIP_S#20

PM_PSI#43

Dothan

(400)

100100100

1.8V

1.8V 1.5V

Pin 3,4U54 switch to

5

U31B

AA2

A[16]#

Y3

A[15]#

AA3

A[14]#

U1

A[13]#

Y1

A[12]#

Y4

A[11]#

W2

A[10]#

T4

A[9]#

W1

A[8]#

V2

A[7]#

R3

A[6]#

V3

A[5]#

U4

A[4]#

P4

A[3]#

U3

ADSTB[0]#

T1

REQ[4]#

P1

REQ[3]#

T2

REQ[2]#

P3

REQ[1]#

R2

REQ[0]#

AF1

A[31]#

AE1

A[30]#

AF3

A[29]#

AD6

A[28]#

AE2

A[27]#

AD5

A[26]#

AC6

A[25]#

AB4

A[24]#

AD2

A[23]#

AE4

A[22]#

AD3

A[21]#

AC3

A[20]#

AC7

A[19]#

AC4

A[18]#

AF4

A[17]#

AE5

ADSTB[1]#

C19

DPWR#

SOCKET479P

_CLK_CPU_BCLK

1

_CLK_CPU_BCLK#

1

T94 TPC28t

T96 TPC28t

T93 TPC28t

T98 TPC28t

Dothan

(533)

NC

Pin 1,2

ADDRESS GROUP 0ADDRESS GROUP 1

2"-8"

2"-8"

<=10"

0.5"-12"

<=10"

<=10"

<=10"

<=10"

<=10"

<=10"

<=10"

<=10"

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

+V1.8S_AC26

+V1.8S_N1

+V1.8S_B1

+V1.8S_F26

H_PROCHOT#

ADS#

PRDY#

PREQ#

BNR#

BPRI#

DBR#

DEFER#

DRDY#

DBSY#

BR0#

CONTROL

IERR#

INIT#

LOCK#

RESET#

RS[2]#

RS[1]#

RS[0]#

TRDY#

HIT#

HITM#

1

1

1

1

AC26

C17

C16

C14

AF7

4

B15

B14

A16

A15

C2

D3

D1

D4

C6

H4

G4

G3

N1

F26

B18

A18

B17

C3

N2

A10

B10

L1

J3

A7

L4

H2

M2

N4

A4

B5

J2

B11

L2

K1

H1

M3

K3

K4

U31C

A3

A6

B4

E4

F3

F2

E2

B1

E1

B2

SOCKET479P

H_PRDY#

H_PREQ#H_A#14

1

H_BR0#

H_IERR#

0.5"-12"

<=10"

<=10"

<=3"

H_RS#2

H_RS#1

H_RS#0

BCLK[0]

BCLK[1]

ITP_CLK[0]

ITP_CLK[1]

A20M#

FERR#

IGNNE#

SLP#

LINT0

LINT1

SMI#

STPCLK#

PWRGOOD

VID[5]

VID[4]

VID[3]

VID[2]

VID[1]

VID[0]

VCCA[3]

VCCA[2]

VCCA[1]

VCCA[0]

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

RSVD5

RSVD4

RSVD3

RSVD2

RSVD1

RSVD0

T107 TPC28t

R271 56Ohm

COMP[3]

COMP[2]

HOSTCLKLEGACY CPU

COMP[1]

COMP[0]

BPM[3]#DPSLP#

BPM[2]#

BPM[1]#

BPM[0]#

GTLREF[3]

GTLREF[2]

GTLREF[1]

GTLREF[0]

MISC

VCCSENSE

VSSSENSE

TEST1

TEST2

TCK

TDO

TMS

TRST#

TDI

H_ADS# 7

H_BNR# 7

H_BPRI# 7

H_DEFER# 7

H_DRDY# 7

H_DBSY# 7

H_BR0# 7

12

H_INIT# 20,32

H_LOCK# 7

H_CPURST# 7

H_RS#[2:0] 7

H_TRDY# 7

H_HIT# 7

H_HITM# 7

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

CPU_COMP3

AB1

CPU_COMP2

AB2

CPU_COMP1

P26

CPU_COMP0

P25

H_BPM#3

C9B7

H_BPM#2

A9

H_BPM#1

B8

H_BPM#0

C8

AC1

G1

E26

H_GTLREF0

AD26

1

C5

1

F23

H_TCK

A13

H_TDI

C12

H_TDO

A12

H_TMS

C11

H_TRST#

B13

AE7

AF6

COMMON CLOCK -> L4

WIDTH: 4.5 mils

SPACE >= 1:2

GROUP SPACE >= 20 mils

LENGTH: 2.2" - 6.5"

+VCCP

VR_VID5 43

VR_VID4 43

VR_VID3 43

VR_VID2 43

VR_VID1 43

VR_VID0 43

T103TPC28t

1

T20 TPC28t

1

T106TPC28t

1

T105TPC28t

1

T21 TPC28t

T88 TPC28t

H_D#15

H_D#14

H_D#13

H_D#12

H_D#11

H_D#10

H_D#9

H_D#8

H_D#7

H_D#6

H_D#4

H_D#2

H_D#1

H_DINV#07

H_DSTBN#07

H_DSTBP#07

H_DINV#17

H_DSTBN#17

H_DSTBP#17

TOPOLOGY 1B:

CPU-ICH-R

CPU-ICH: 0.5" - 12"

ICH-R <= 3"

TOPOLOGY 1B:

CPU-ICH-R

CPU-ICH: 0.5" - 12"

ICH-R <= 3"

TOPOLOGY 1C:

CPU-R-LSC-ICH

CPU-R: 0.5" - 12"

R - LSC<= 3"

LSC-ICH:0.5"-12"

H_THRMTRIP_S#

H_FERR#

H_PROCHOT#

H_D#0

H_D#31

H_D#30

H_D#29

H_D#28

H_D#27

H_D#26

H_D#25

H_D#24 H_D#56

H_D#23

H_D#22

H_D#21

H_D#20

H_D#19

H_D#18

H_D#17

H_D#16

+VCCP

12

R239

56Ohm

+VCCP

12

R71

56Ohm

+VCCP

12

R244

56Ohm

CPU DEBUG PORT

Close to Pin

A8 of CPU

Close to Pin A12 of CPU

Width= 5 mils

Length <= 2"

3

H_PREQ#

H_PRDY#

H_TMS

H_TDO

H_TDI

H_TCK

H_TRST#

U31A

C25

D[15]#

E23

D[14]#

B23

D[13]#

C26

D[12]#

E24

D[11]#

D24

D[10]#

B24

D[9]#

C20

D[8]#

B20

D[7]#

A21

D[6]#

B26

D[5]#

A24

B21

A22

A25

A19

D25

C23

C22

K25

N25

H26

M25

N24

L26

J25

M23

J23

G24

F25

H24

M26

L23

G25

H23

J26

K24

L24

TOPOLOGY 2A:

R-CPU-ICH Y-FORK

CPU-ICH: 0.5" - 12"

R - CPU <= 3"

TOPOLOGY 2B:

MCH-CPU-ICH4

MCH-CPU:0.5"-6.5"

CPU-ICH4:0.5"-12"

TOPOLOGY 3:

CPU-ICH-R-LSC-FWH

CPU-ICH:0.5" - 12"

R - LSC <= 3"

LSC-FWH:0.5"-6"

R261 200Ohm /

R260 56Ohm

CPU JTAG

R250 39Ohm

R247 56Ohm

R248 150Ohm

R246 27.4Ohm

R245 680Ohm

D[4]#

D[3]#

D[2]#

D[1]#

D[0]#

DINV[0]#

DSTBN[0]#

DSTBP[0]#

D[31]#

D[30]#

D[29]#

D[28]#

D[27]#

D[26]#

D[25]#

D[24]#

D[23]#

D[22]#

D[21]#

D[20]#

D[19]#

D[18]#

D[17]#

D[16]#

DINV[1]#

DSTBN[1]#

DSTBP[1]#

SOCKET479P

H_PWRGD

H_DPSLP#

H_INIT#

1 2

1 2

DATA GROUP 0DATA GROUP 1

DSTBN[2]#

DSTBP[2]#

DSTBN[3]#

DSTBP[3]#

12

12

12

12

12

2

D[47]#

D[46]#

D[45]#

D[44]#

D[43]#

D[42]#

D[41]#

D[40]#

D[39]#

D[38]#

D[37]#

D[36]#

DATA GROUP 2DATA GROUP 3

D[35]#

D[34]#

D[33]#

D[32]#

DINV[2]#

D[63]#

D[62]#

D[61]#

D[60]#

D[59]#

D[58]#

D[57]#

D[56]#

D[55]#

D[54]#

D[53]#

D[52]#

D[51]#

D[50]#

D[49]#

D[48]#

DINV[3]#

+VCCP

R73

332Ohm

+VCCP

H_D#47

Y25

H_D#46

AA26

H_D#45

Y23

H_D#44

V26

H_D#43

U25

H_D#42

V24

H_D#41

U26

H_D#40

AA23

H_D#39

R23

H_D#38

R26

H_D#37H_D#5

R24

H_D#36

V23

H_D#35

U23

H_D#34

T25

H_D#33

AA24

H_D#32

Y26

T24

W25

W24

H_D#63

AF26

H_D#62

AF22

H_D#61

AF25

H_D#60

AD21

H_D#59

AE21

H_D#58

AF20

H_D#57

AD24

AF23

H_D#55

AE22

H_D#54

AD23

H_D#53

AC25

H_D#52

AC22

H_D#51

AC20

H_D#50

AB24

H_D#49

AC23

H_D#48

AB25

AD20

AE24

AE25

+VCCP

H_GTLREF0:

12

LENGTH <=0.5"

WIDTH = 5.5 mils

SPACE >= 25 mils

CPU_COMP2 :

Length <= 0.5"

Width = 18 mils(L1/L6)

Space>= 20 mils

CPU_COMP2

CPU_COMP3 :

Length <= 0.5"

Width = 5.5 mils(L1/L6)

Space>= 20 mils

CPU_COMP3

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

Date: Sheet

H_D#[63:0] 7

DATA GROUP 0,2 -> L1

DATA GROUP 1,3 -> L4

SPACE >= 1:2

GROUP SPACE >=20 mils

LENGTH: 0.5" - 5.5"

H_DINV#2 7

H_DSTBN#2 7

H_DSTBP#2 7

H_DINV#3 7

H_DSTBN#3 7

H_DSTBP#3 7

R75

27.4Ohm

1 2

R76

56Ohm

1 2

A6G

+VCCP

Close to

12

Pin AD26

of CPU

R224

1KOhm

H_GTLREF0

12

Same Side

w/ CPU

R223

2KOhm

CPU_COMP0 :

Length <= 0.5"

Width = 18 mils(L1/L6)

Space>= 20 mils

R221

Title :

Engineer:

1

27.4Ohm

1 2

R222

56Ohm

1 2

CPU-BANIAS(HOST)

John Hung

354Friday, October 15, 2004

CPU_COMP0

CPU_COMP1 :

Length <= 0.5"

Width = 5.5 mils(L1/L6)

Space>= 20 mils

CPU_COMP1

Rev

1.1

of

Page 4

5

HFM(1.3GHz-1.7GHz): 1.468V

LFM( 600MHz): 0.956V

0.745V - 1.356V(+/- 1.5%)

C0: 25 A

+VCORE

C3: 7.59A

VCC1

D18D8D6

VCC2

D20

VCC3

VCC4

C4: 0.9A

VCC7

VCC6

VCC5

E17E9E7E5D22

VCC8

E19

VCC9

E21

VCC11

VCC10

VCC13

VCC12

F18F8F6

VCC14

F20

VCC15

VCC17

VCC16

VCC19

VCC18

VCC21

VCC20

J21J5H22H6G21G5F22

VCC22

K22

VCC23

VCC25

VCC24

VCC27

VCC26

VCC29

VCC28

Y22Y6W21W5V22V6U5

VCC30

AA5

VCC31

AA7

VCC32

AA9

VCC33

AA11

VCC34

AA13

VCC35

AA15

D D

VCC

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCQ[1]

VCCQ[0]

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16K6L5

W4

P23

C C

12

C35

0.1uF/10V

12

C89

0.1uF/10V

L21M6M22N5N21P6P22R5R21T6T22

VCCP25

U21

4

AB18

AB16

AB14

AB12

AB10

AB8

AB6

AA21

AA19

AA17

VCC46

VCC45

VCC44

VCC43

VCC42

VCC41

VCC40

VCC39

VCC38

VCC37

VCC36

+VCCP+VCCP

1.0V - 1.1V(+/- 5%)

S0-S1M: 2.5 A(CPU,MCH,ICH)

AB20

VCC47

AB22

VCC48

AC9

VCC49

AC11

VCC50

AC13

VCC51

AC15

VCC52

AC17

VCC53

AC19

VCC54

AD8

VCC55

AD10

VCC56

AD12

VCC57

AD14

VCC58

AD16

VCC59

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

AD18

SOCKET479P

VCC60

U31D

AE9

AE11

AE13

AE15

AE17

AE19

AF8

AF10

AF12

AF14

AF16

AF18

3

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF11

AF13

AF15

AF17

AF19

AF21

AF24

AD1

AD4

AD7

AD9

AE3

AE6

AE8

AF2

AF5

AF9

AC24

AC21

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS1

A2A5A8

AC18

AC16

VSS159

VSS158

VSS2

VSS3

A11

AC14

AC12

VSS157

VSS156

VSS4

VSS5

A14

A17

AC10

AC8

VSS155

VSS154

VSS6

VSS7

A20

A23

AC5

AC2

AB26

VSS153

VSS152

VSS151

VSS150

VSS8

VSS9

VSS10

VSS11

A26B3B6B9B12

AB23

AB21

VSS149

VSS12

AB19

AB17

VSS148

VSS147

VSS13

VSS14

B16

B19

AB15

AB13

VSS146

VSS145

VSS144

VSS15

VSS16

VSS17

B22

B25C1C4C7C10

AB11

AB9

VSS143

VSS18

AB7

AB5

VSS142

VSS141

VSS19

VSS20

AB3

AA25

VSS140

VSS139

VSS21

VSS22

C13

C15

AA22

AA20

VSS138

VSS137

VSS23

VSS24

C18

C21

AA18

AA16

AA14

VSS136

VSS135

VSS134

VSS25

VSS26

VSS27

C24D2D5D7D9

2

AA12

AA10

AA8

AA6

VSS133

VSS132

VSS131

VSS130

VSS129

GND

VSS28

VSS29

VSS30

VSS31

VSS32

D11

D13

AA4

AA1

VSS128

VSS33

D15

D17

Y24

Y21Y5Y2

VSS127

VSS126

VSS34

VSS35

D19

D21

VSS125

VSS124

VSS123

VSS36

VSS37

VSS38

D23

D26E3E6E8E10

W26

W23

VSS122

VSS39

W22W6W3

VSS121

VSS120

VSS40

VSS41

V25

VSS119

VSS118

VSS42

VSS43

E12

E14

V21V5V4V1U24

VSS117

VSS116

VSS115

VSS114

VSS44

VSS45

VSS46

VSS47

E16

E18

E20

U22U6U2

VSS113

VSS112

VSS111

VSS110

VSS109

VSS48

VSS49

VSS50

VSS51

VSS52

E22

E25F1F4F5F7F9F11

T26

T23

VSS108

VSS53

T21T5T3

VSS107

VSS106

VSS54

VSS55

F13

R25

VSS105

VSS104

VSS56

VSS57

F15

F17

R22R6R4R1P24

VSS103

VSS102

VSS101

VSS100

VSS58

VSS59

VSS60

VSS61

F19

F21

F24G2G6

1

VSS99

VSS98

VSS62

VSS63

P21

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

G22

U31E

SOCKET479P

P5

P2

N26

N23

N22

N6

N3

M24

M21

M5

M4

M1

L25

L22

L6

L3

K26

K23

K21

K5

K2

J24

J22

J6

J4

J1

H25

H21

H5

H3

G26

G23

+VCORE

B B

A A

12

C359

10UF/6.3V

12

C70

10UF/6.3V

12

C357

10UF/6.3V

M3N : Four 200 uF are located in IMVP4

A3N : Delete 10uF/6.3V from 35pcs to 17pcs

CPU VCORE Decoupling Capacitor

12

C338

10UF/6.3V

12

C358

10UF/6.3V

12

C346

10UF/6.3V

5

12

C368

10UF/6.3V

12

C57

10UF/6.3V

12

C69

10UF/6.3V

12

C369

10UF/6.3V

12

C351

10UF/6.3V

12

C39

10UF/6.3V

12

C51

10UF/6.3V

12

C352

10UF/6.3V

12

C355

10UF/6.3V

12

C343

10UF/6.3V

12

C353

10UF/6.3V

+VCCP

Mid Frequency

Decoupling (Place

around Processor)

High Frequency

Decoupling (Place

underneath

Processor)

using 10uF/6.3V X5R

+VCORE Bulk

Decoupling

4

3

+V3.3S

12

FREQ_SEL8,23

12

+

C538

4.7U

/

CE1

150U/4.0V

+V3.3S

+VCCP (CPU) Decoupling Capacitor

(Place near CPU)

12

12

C34

0.1uF/10V

Vref=1.215V

U53

/

1

IN

OUT

2

GND

3 4

EN ADJ

SI9183DT

R404

/

10KOhm

1 2

34

5

12

C42

0.1uF/10V

5

R400

18.7KOhm

2

Q93B

UM6K1N

/

12

/

61

12

C336

0.1uF/10V

1 2

R397 0Ohm

R399

/

20KOhm

Q93A

UM6K1N

/

1 2

12

12

C344

0.1uF/10V

R398

4.7KOhm

2

+V1.8S_PROC+V1.8S

+V1.8S_PROC

/

C337

0.1uF/10V

12

C537

4.7U

/

12

C340

0.1uF/10V

12

For 855GM /855GME /852GM /852GME:

Load R397

For 852GMV:

Load C537, C538, Q93, R398, R399,

R400, R404, U53

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

Date: Sheet

C360

0.1uF/10V

C335

0.1uF/10V

A6G

C41

0.1uF/10V

Title :

Engineer:

1

C59

0.1uF/10V

CPU-BANIAS(PWR)

John Hung

12

12

12

Rev

454Friday, October 15, 2004

1.1

of

Page 5

5

D D

4

3

2

1

C C

Route H_THERMDA and H_THERMDC

on the same layer

------------------OTHER SIG NAL S

12 mils

===============GND

10 mils

=========H_THERMDA(10 mils)

10 mils

=========H_THERMDC(10 mils)

10 mils

=========GND

12 mils

---------------------OTHER SIGN AL S

Avoid BPSB,Power

B B

+V3.3S_THM+V3.3S

1 2

R243

200Ohm

SCL_3S10,22,23

SDA_3S10,22,23

PM_THRM#20,40

PM_THRM#

(Pull-Up 10K

in Page 35)

A A

SCL_3S

12

Close to Pin A18

& B18 of CPU

Standby Mode: 3uA(Max. 10uA )

Full Active: 0.5mA(Max. 1mA)

+V3.3S_THM

C349

0.1uF/10V

8

7

6

U33

SMBCLK

SMBDATA

ALERT#

1

5

VCC

OVERT

DXP

DXN

GND

MAX6657

4

2

3

OS#_OC

H_THERMDASDA_3S

H_THERMDC

OS#_OC

(Pull-Up 10K

in Page 35)

OS#_OC 40

4"-8"

12

C354

2200P

4"-8"

H_THERMDA 3

H_THERMDC 3

THERMAL SENSOR

Title :

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

5

4

3

2

Date: Sheet

Engineer:

A6G

John Hung

Rev

1

554Friday, October 15, 2004

1.1

of

Page 6

5

D D

DDR Serial Termination

52

U8

V+

V-

LMV321

_DDR_DATA34

_DDR_DATA38

_DDR_DM4

_DDR_DQS4

_DDR_DATA33

_DDR_DATA32

_DDR_DATA37

_DDR_DATA36

_DDR_DATA46

_DDR_DQS5

_DDR_DATA35

_DDR_DATA39

_DDR_DATA40

_DDR_DATA44

_DDR_DATA41

_DDR_DATA45

_DDR_DQS6

_DDR_DATA53

_DDR_DATA52

_DDR_DATA49

_DDR_DATA42

_DDR_DATA47

_DDR_DATA43

_DDR_DM5

_DDR_DATA56

_DDR_DATA60

_DDR_DATA48

_DDR_DATA54

_DDR_DATA50

_DDR_DATA55

_DDR_DATA51

_DDR_DM6

_DDR_DATA63

_DDR_DATA59

_DDR_DATA58

_DDR_DM7

_DDR_DATA62

_DDR_DQS7

_DDR_DATA57

_DDR_DATA61

+V5

DDR_VREF

4

12

C116

0.1uF/10V

1

1.225V-1.275V

S0-S1M:10 mA

(Max. 50 mA)

_DDR_DM0 DDR_DM0

_DDR_DATA7

_DDR_DATA1

_DDR_DATA3

_DDR_DQS0

_DDR_DATA4

_DDR_DATA0

_DDR_DATA5

_DDR_DATA9

_DDR_DATA14

_DDR_DATA12

_DDR_DM1

_DDR_DATA11

_DDR_DATA8

_DDR_DATA2

_DDR_DATA6

_DDR_DATA17

_DDR_DATA16

_DDR_DATA20

C C

_DDR_DATA21

_DDR_DATA10

_DDR_DATA15

_DDR_DQS1

_DDR_DATA13

_DDR_DATA29

_DDR_DATA24

_DDR_DATA19

_DDR_DATA23

_DDR_DATA18

_DDR_DATA22

_DDR_DM2

_DDR_DQS2

_DDR_DATA31

_DDR_DATA27

_DDR_DATA26

_DDR_DATA30

_DDR_DQS3

_DDR_DM3

_DDR_DATA28

_DDR_DATA25

B B

A A

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

Intel suggested that DDR_VREF should be turned

off in S3-S5. But measure the leakage because

there is no +V2.5S.

+V2.5

12

12

5

R89

10KOhm

R90

10KOhm

RN48A10Ohm

RN48B10Ohm

RN48C10Ohm

RN48D10Ohm

RN48E10Ohm

RN48F10Ohm

RN48G10Ohm

RN48H10Ohm

RN47A10Ohm

RN47B10Ohm

RN47C10Ohm

RN47D10Ohm

RN47E10Ohm

RN47F10Ohm

RN47G10Ohm

RN47H10Ohm

RN46A10Ohm

RN46B10Ohm

RN46C10Ohm

RN46D10Ohm

RN46E10Ohm

RN46F10Ohm

RN46G10Ohm

RN46H10Ohm

RN45A10Ohm

RN45B10Ohm

RN45C10Ohm

RN45D10Ohm

RN45E10Ohm

RN45F10Ohm

RN45G10Ohm

RN45H10Ohm

RN44A10Ohm

RN44B10Ohm

RN44C10Ohm

RN44D10Ohm

RN44E10Ohm

RN44F10Ohm

RN44G10Ohm

RN44H10Ohm

12

C118

0.1uF/10V

DDR_DATA7

DDR_DATA1

DDR_DATA3

DDR_DQS0

DDR_DATA4

DDR_DATA0

DDR_DATA5

DDR_DATA9

DDR_DATA14

DDR_DATA12

DDR_DM1

DDR_DATA11

DDR_DATA8

DDR_DATA2

DDR_DATA6

DDR_DATA17

DDR_DATA16

DDR_DATA20

DDR_DATA21

DDR_DATA10

DDR_DATA15

DDR_DQS1

DDR_DATA13

DDR_DATA29

DDR_DATA24

DDR_DATA19

DDR_DATA23

DDR_DATA18

DDR_DATA22

DDR_DM2

DDR_DQS2

DDR_DATA31

DDR_DATA27

DDR_DATA26

DDR_DATA30

DDR_DQS3

DDR_DM3

DDR_DATA28

DDR_DATA25

1

+

3

-

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 16

2 15

7 10

8 9

4 13

3 14

5 12

6 11

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

TP12

TPC28t

4

RN43A10Ohm

RN43B10Ohm

RN43C10Ohm

RN43D10Ohm

RN43E10Ohm

RN43F10Ohm

RN43G10Ohm

RN43H10Ohm

RN42A10Ohm

RN42B10Ohm

RN42G10Ohm

RN42H10Ohm

RN42D10Ohm

RN42C10Ohm

RN42E10Ohm

RN42F10Ohm

RN41A10Ohm

RN41B10Ohm

RN41C10Ohm

RN41D10Ohm

RN41E10Ohm

RN41F10Ohm

RN41G10Ohm

RN41H10Ohm

RN40A10Ohm

RN40B10Ohm

RN40C10Ohm

RN40D10Ohm

RN40E10Ohm

RN40F10Ohm

RN40G10Ohm

RN40H10Ohm

RN39A10Ohm

RN39B10Ohm

RN39C10Ohm

RN39D10Ohm

RN39E10Ohm

RN39F10Ohm

RN39G10Ohm

RN39H10Ohm

1.23125V-1.26875V

S0-S1M:Max. 80 mA

S3: 0 mA

DDR_SMRCOMP

4

3

Thermal Power: ~ 3.8W

LxWxH=37.5x37.5x2.58

DDR_DATA34

DDR_DATA38

DDR_DM4

DDR_DQS4

DDR_DATA33

DDR_DATA32

DDR_DATA37

DDR_DATA36

DDR_DATA46

DDR_DQS5

DDR_DATA35

DDR_DATA39

DDR_DATA40

DDR_DATA44

DDR_DATA41

DDR_DATA45

DDR_DQS6

DDR_DATA53

DDR_DATA52

DDR_DATA49

DDR_DATA42

DDR_DATA47

DDR_DATA43

DDR_DM5

DDR_DATA56

DDR_DATA60

DDR_DATA48

DDR_DATA54

DDR_DATA50

DDR_DATA55

DDR_DATA51

DDR_DM6

DDR_DATA63

DDR_DATA59

DDR_DATA58

DDR_DM7

DDR_DATA62

DDR_DQS7

DDR_DATA57

DDR_DATA61

DDR_DATA0

DDR_DATA1

DDR_DATA2

DDR_DATA3

DDR_DATA4

DDR_DATA6

DDR_DATA7

DDR_DATA8

DDR_DATA9

DDR_DATA10

DDR_DATA11

DDR_DATA12

DDR_DATA13

DDR_DATA14

DDR_DATA15

DDR_DATA16

DDR_DATA17

DDR_DATA18

DDR_DATA19

DDR_DATA20

DDR_DATA21

DDR_DATA22

DDR_DATA23

DDR_DATA24

DDR_DATA25

DDR_DATA26

DDR_DATA27

DDR_DATA28

DDR_DATA29

DDR_DATA30

DDR_DATA31

DDR_DATA32

DDR_DATA33

DDR_DATA34

DDR_DATA35

DDR_DATA36

DDR_DATA37

DDR_DATA38

DDR_DATA39

DDR_DATA40

DDR_DATA41

DDR_DATA42

DDR_DATA43

DDR_DATA44

DDR_DATA45

DDR_DATA46

DDR_DATA47

DDR_DATA48

DDR_DATA49

DDR_DATA50

DDR_DATA51

DDR_DATA52

DDR_DATA53

DDR_DATA54

DDR_DATA55

DDR_DATA56

DDR_DATA57

DDR_DATA58

DDR_DATA59

DDR_DATA60

DDR_DATA61

DDR_DATA62

DDR_DATA63

DDR_VREF

12

C114

0.1uF/10V

AG10

AF10

AE11

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ24

AF2

AE3

AF4

AH2

AD3

AE2

AG4

AH3

AD6

AG5

AG7

AE8

AF5

AH4

AF7

AH6

AF8

AG8

AH9

AH7

AD9

U32B

SDQ[0]

SDQ[1]

SDQ[2]

SDQ[3]

SDQ[4]

SDQ[5]

SDQ[6]

SDQ[7]

SDQ[8]

SDQ[9]

SDQ[10]

SDQ[11]

SDQ[12]

SDQ[13]

SDQ[14]

SDQ[15]

SDQ[16]

SDQ[17]

SDQ[18]

SDQ[19]

SDQ[20]

SDQ[21]

SDQ[22]

SDQ[23]

SDQ[24]

SDQ[25]

SDQ[26]

SDQ[27]

SDQ[28]

SDQ[29]

SDQ[30]

SDQ[31]

SDQ[32]

SDQ[33]

SDQ[34]

SDQ[35]

SDQ[36]

SDQ[37]

SDQ[38]

SDQ[39]

SDQ[40]

SDQ[41]

SDQ[42]

SDQ[43]

SDQ[44]

SDQ[45]

SDQ[46]

SDQ[47]

SDQ[48]

SDQ[49]

SDQ[50]

SDQ[51]

SDQ[52]

SDQ[53]

SDQ[54]

SDQ[55]

SDQ[56]

SDQ[57]

SDQ[58]

SDQ[59]

SDQ[60]

SDQ[61]

SDQ[62]

SDQ[63]

SDQ[64]

SDQ[65]

SDQ[66]

SDQ[67]

SDQ[68]

SDQ[69]

SDQ[70]

SDQ[71]

SMVREF_0

RG82855GME

DDR SYSTEM MEMORY

SDQS[0]

SDQS[1]

SDQS[2]

SDQS[3]

SDQS[4]

SDQS[5]

SDQS[6]

SDQS[7]

SDQS[8]

SMA[0]

SMA[1]

SMA[2]

SMA[3]

SMA[4]

SMA[5]

SMA[6]

SMA[7]

SMA[8]

SMA[9]

SMA[10]

SMA[11]

SMA[12]

SMAB[1]

SMAB[2]

SMAB[4]

SMAB[5]

SCKE[0]

SCKE[1]

SCKE[2]

SCKE[3]

SCS[0]#

SCS[1]#

SCS[2]#

SCS[3]#

SBA[0]

SBA[1]

SRAS#

SCAS#

SWE#

SCK[0]

SCK[0]#

SCK[1]

SCK[1]#

SCK[2]

SCK[2]#

SCK[3]

SCK[3]#

SCK[4]

SCK[4]#

SCK[5]

SCK[5]#

SDM[0]

SDM[1]

SDM[2]

SDM[3]

SDM[4]

SDM[5]

SDM[6]

SDM[7]

SDM[8]

RCVENOUT#

RCVENIN#

SMRCOMP

SMVSWINGL

SMVSWINGH

AG2

AH5

AH8

AE12

AH17

AE21

AH24

AH27

AD15

AC18

AD14

AD13

AD17

AD11

AC13

AD8

AD7

AC6

AC5

AC19

AD5

AB5

AD16

AC12

AF11

AD10

AC7

AB7

AC9

AC10

AD23

AD26

AC22

AC25

AD22

AD20

AC21

AC24

AD25

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

AE5

AE6

AE9

AH12

AD19

AD21

AD24

AH28

AH15

AC15

AC16

AB1

AJ22

AJ19

DDR_DQS0

DDR_DQS1

DDR_DQS2

DDR_DQS3

DDR_DQS4

DDR_DQS5DDR_DATA5

DDR_DQS6

DDR_DQS7

T111 TPC28t

1

DDR_AA0

DDR_AA1

DDR_AA2

DDR_AA3

DDR_AA4

DDR_AA5

DDR_AA6

DDR_AA7

DDR_AA8

DDR_AA9

DDR_AA10

DDR_AA11

DDR_AA12

DDR_AB1

DDR_AB2

DDR_AB4

DDR_AB5

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

DDR_RCVENOUT#

DDR_RCVENIN#

DDR_SMRCOMP

DDR_SMVSWINGL

DDR_SMVSWINGH

11-01

+V2.5_GMCH_SM +V2.5_GMCH_SM +V2.5_GMCH_SM

12

R273

60.4Ohm

12

R272

60.4Ohm

12

C380

0.1uF/10V

0.2 VCCSM +/- 2%

DDR_SMVSWINGL

C401

0.1uF/10V

Close to

Pin AJ22

3

12

R279

604Ohm

12

12

R277

150Ohm

0.8 VCCSM +/- 2%

DDR_SMVSWINGH

C400

0.1uF/10V

Close to

Pin AJ19

2

1

1

1

12

2

_DDR_DATA[63:0] 10,11

_DDR_DM[7:0] 10,11

_DDR_DQS[7:0] 10,11

DDR_AA[12:0] 10,11

DDR_AB[2:1] 10,11

DDR_AB[5:4] 10,11

DDR_CKE0 10,11

DDR_CKE1 10,11

DDR_CKE2 10,11

DDR_CKE3 10,11

DDR_CS0# 10,11

DDR_CS1# 10,11

DDR_CS2# 10,11

DDR_CS3# 10,11

DDR_BS0# 10,11

DDR_BS1# 10,11

DDR_RAS# 10,11

DDR_CAS# 10,11

DDR_WE# 10,11

CLK_DDR0 10

CLK_DDR0# 10

CLK_DDR1 10

CLK_DDR1# 10

CLK_DDR2 10

CLK_DDR2# 10

CLK_DDR3 10

CLK_DDR3# 10

CLK_DDR4 10

CLK_DDR4# 10

CLK_DDR5 10

CLK_DDR5# 10

T112 TPC28t

T110 TPC28t

T109 TPC28t

12

R278

150Ohm

12

R280

604Ohm

1

(MCH-Sighting041)

M-GM system memory interface generates

single pulse CKE events which may cause

Intermittent hangs and display corruptions

when using Micron and Infineon

S0-DIMMs.

MCH-M

Route for COMMAND

1. DDR_AA[12:6],DDR_AA3,DDR_AA0

2. DDR_WE#

3. DDR_RAS#

4. DDR_CAS#

5. DDR_BS0#,DDR_BS1#

Route for CPC

1. DDR_AA[5:4],DDR_AA[2:1]

MCH-M

Route for CPC

1. DDR_AB[5:4],DDR_AB[2:1]

Route for CONTROL

1. DDR_CKE[1:0],DDR_CS[1:0]#

MCH-M

Route for CONTROL

1. DDR_CKE[3:2],DDR_CS[3:2]#

Route for CLOCK

1. CLK_DDR[2:0],CLK_DDR[2:0]#

MCH-M

Route for CLOCK

1. CLK_DDR[5:3],CLK_DDR[5:3]#

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

Date: Sheet

A6G

Dual DDR

SO-DIMM

Dual DDR

SO-DIMM

Dual DDR

SO-DIMM

Dual DDR

SO-DIMM

Title :

Engineer:

1

NB-MCHM(DDR)

John Hung

654Friday, October 15, 2004

TERMINATION

TERMINATION

TERMINATION

of

Rev

1.1

Page 7

5

4

3

2

1

HUB_PD[10:0]19

12

R249

37.4Ohm

R49

56Ohm

/

1 2

H_CPURST#

H_A#[31:3]3

H_REQ#[4:0]3

H_ADSTB#03

H_ADSTB#13

_CLK_MCH_BCLK#23

_CLK_MCH_BCLK23

H_DSTBN#03

H_DSTBN#13

H_DSTBN#23

H_DSTBN#33

H_DSTBP#03

H_DSTBP#13

H_DSTBP#23

H_DSTBP#33

H_DINV#03

H_DINV#13

H_DINV#23

H_DINV#33

H_CPURST#3

HUB_PSTRB19

HUB_PSTRB#19

68.1Ohm

11-07

100Ohm

MCH_COMP Signals

MCH_HLZCOMP :

Length <= 0.5"

Width = 18 mils(L1/L6)

Space>= 20 mils

D D

C C

MCH_HLZCOMP

MCH_HYRCOMP :

Length <= 0.5"

Width = 18 mils(L1/L6)

Space>= 20 mils

MCH_HYRCOMP

MCH_HXRCOMP :

Length <= 0.5"

Width =18 mils(L1/L6 )

Space>= 20 mils

MCH_HXRCOMP

1 2

1 2

R235

27.4Ohm

R226

27.4Ohm

MCH_SWING Signals

MCH_HYSWING :

Length <= 0.5"

Width = 18 mils

Space>= 20 mils

1/3(+VCCP) +/- 2%

MCH_HYSWING

C345

B B

A A

0.1uF/10V

Close to

Pin H28

MCH_HXSWING :

Length <= 0.5"

Width = 18 mils

Space>= 20 mils

1/3(+VCCP) +/- 2%

MCH_HXSWING

C328

0.1uF/10V

Close to

Pin B20

+VCCP

12

R240

301Ohm

12

R241

150Ohm

1 2

+V1.2S_GMCH_HI

11-07

+VCCP

12

R225

301Ohm

12

R228

150Ohm

1 2

+VCCP

MCH_HYRCOMP

MCH_HYSWING

MCH_HXRCOMP

MCH_HXSWING

MCH_HDVREF

MCH_HCCVREF

MCH_HAVREF

HUB_PD0

HUB_PD1

HUB_PD2

HUB_PD3

HUB_PD4

HUB_PD5

HUB_PD6

HUB_PD7

HUB_PD8

HUB_PD9

HUB_PD10

HUB_PSTRB

HUB_PSTRB#

MCH_HLZCOMP

+V1.2S_GMCH_HI

12

R251

R253

1 2

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

0.8V +/- 2%

HUB_VSWING_MCH

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

<=6"

W25

AA27

W24

W23

W27

AA28

W28

AB27

AB28

AA26

AD29

AE29

P23

T25

T28

R27

U23

U24

R24

U28

V28

U27

T27

V27

U25

V26

Y24

V25

V23

Y25

Y27

Y26

R28

P25

R23

R25

T23

T26

H28

K28

B20

B18

J28

C27

E22

D18

K27

D26

E21

E18

J25

E25

B25

G19

F15

K21

J21

J17

Y28

Y22

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

T2

U2

W1

U32A

HA[3]#

HA[4]#

HA[5]#

HA[6]#

HA[7]#

HA[8]#

HA[9]#

HA[10]#

HA[11]#

HA[12]#

HA[13]#

HA[14]#

HA[15]#

HA[16]#

HA[17]#

HA[18]#

HA[19]#

HA[20]#

HA[21]#

HA[22]#

HA[23]#

HA[24]#

HA[25]#

HA[26]#

HA[27]#

HA[28]#

HA[29]#

HA[30]#

HA[31]#

HREQ[0]#

HREQ[1]#

HREQ[2]#

HREQ[3]#

HREQ[4]#

HADSTB[0]#

HADSTB[1]#

BCLK#

BCLK

HYRCOMP

HYSWING

HXRCOMP

HXSWING

HDSTBN[0]#

HDSTBN[1]#

HDSTBN[2]#

HDSTBN[3]#

HDSTBP[0]#

HDSTBP[1]#

HDSTBP[2]#

HDSTBP[3]#

DINV[0]#

DINV[1]#

DINV[2]#

DINV[3]#

CPURST#

HDVREF[0]

HDVREF[1]

HDVREF[2]

HCCVREF

HAVREF

HL[0]

HL[1]

HL[2]

HL[3]

HL[4]

HL[5]

HL[6]

HL[7]

HL[8]

HL[9]

HL[10]

HLSTB

HLSTB#

HLRCOMP

PSWING

HLVREF

RG82855GME

11-07

12

C356

0.1uF/10V

HOST

HUB I/F

0.343V- 0.357V(Typ. 0.35V)

HUB_VREF_MCH

12

C362

0.01UF/10V

HD[0]#

HD[1]#

HD[2]#

HD[3]#

HD[4]#

HD[5]#

HD[6]#

HD[7]#

HD[8]#

HD[9]#

HD[10]#

HD[11]#

HD[12]#

HD[13]#

HD[14]#

HD[15]#

HD[16]#

HD[17]#

HD[18]#

HD[19]#

HD[20]#

HD[21]#

HD[22]#

HD[23]#

HD[24]#

HD[25]#

HD[26]#

HD[27]#

HD[28]#

HD[29]#

HD[30]#

HD[31]#

HD[32]#

HD[33]#

HD[34]#

HD[35]#

HD[36]#

HD[37]#

HD[38]#

HD[39]#

HD[40]#

HD[41]#

HD[42]#

HD[43]#

HD[44]#

HD[45]#

HD[46]#

HD[47]#

HD[48]#

HD[49]#

HD[50]#

HD[51]#

HD[52]#

HD[53]#

HD[54]#

HD[55]#

HD[56]#

HD[57]#

HD[58]#

HD[59]#

HD[60]#

HD[61]#

HD[62]#

HD[63]#

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HIT#

HLOCK#

BREQ0#

BNR#

BPRI#

DBSY#

RS#0

RS#1

RS#2

12

C363

0.1uF/10V

K22

H27

K25

L24

J27

G28

L27

L23

L25

J24

H25

K23

G27

K26

J23

H26

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

L28

M25

N24

M28

N28

N27

P27

M23

N25

P28

M26

N23

P26

M27

1 2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_RS#0

H_RS#1

H_RS#2

R252 287Ohm

R262

11-07

100Ohm

H_D#[63:0] 3

H_ADS# 3

H_TRDY# 3

H_DRDY# 3

H_DEFER# 3

H_HITM# 3

H_HIT# 3

H_LOCK# 3

H_BR0# 3

H_BNR# 3

H_BPRI# 3

H_DBSY# 3

H_RS#[2:0] 3

+V1.2S_GMCH_HI

12

MCH_VREF Signals

MCH_HAVREF:

Length <= 0.5"

Width = 11 mils

Space>= 20 mils

2/3(+VCCP) +/- 2%

MCH_HAVREF

12

C81

0.1uF/10V

MCH_HCCVREF:

Length <= 0.5"

Width = 10 mils

Space>= 20 mils

2/3(+VCCP) +/- 2%

MCH_HCCVREF

12

C376

0.1uF/10V

MCH_HDVREF:

Length <= 0.5"

Width = 11 mils

Space>= 20 mils

2/3(+VCCP) +/- 2%

MCH_HDVREF

12

12

C44

0.1uF/10V

12

C46

0.1uF/10V

C48

0.1uF/10V

12

12

12

C79

1uF/6.3V

C377

1uF/6.3V

C52

1uF/6.3V

+VCCP

12

12

+VCCP

12

12

+VCCP

12

1 2

R67

49.9Ohm

R66

100Ohm

R270

49.9Ohm

R269

100Ohm

R44

49.9Ohm

R46

100Ohm

27.4 ohm (10-003412704) for 855GM/852GM

37.4 ohm (10-003413704) for 855GME

48.7 ohm (10-003414807) for 852GME/852GMV

5

R251:R249:

49.9 ohm (10-003414909) for 855GM/852GM

68.1 ohm (10-003416801) for 855GME

86.6 ohm (10-003418606) for 852GME/852GMV

4

3

R252:

240 ohm (10-003412410) for 855GM/852GM

287 ohm (10-003412817) for 855GME

324 ohm (10-003413214) for 852GME/852GMV

2

Title :

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

Date: Sheet

Engineer:

A6G

1

NB-MCHM(HOST)

John Hung

754Friday, October 15, 2004

of

Rev

1.1

Page 8

5

4

3

2

1

U32D

C1

VSS0

G1

VSS1

L1

VSS2

U1

VSS3

AA1

VSS4

AE1

VSS5

R2

VSS6

AG3

VSS7

AJ3

D D

C C

B B

A A

VSS8

D4

VSS9

G4

VSS10

K4

VSS11

N4

VSS12

T4

VSS13

W4

VSS14

AA4

VSS15

AC4

VSS16

AE4

VSS17

B5

VSS18

U5

VSS19

Y5

VSS20

Y6

VSS21

AG6

VSS22

C7

VSS23

E7

VSS24

G7

VSS25

J7

VSS26

M7

VSS27

R7

VSS28

AA7

VSS29

AE7

VSS30

AJ7

VSS31

H8

VSS32

K8

VSS33

P8

VSS34

T8

VSS35

V8

VSS36

Y8

VSS37

AC8

VSS38

E9

VSS39

L9

VSS40

N9

VSS41

R9

VSS42

U9

VSS43

W9

VSS44

AB9

VSS45

AG9

VSS46

C10

VSS47

J10

VSS48

AA10

VSS49

AE10

VSS50

D11

VSS51

F11

VSS52

H11

VSS53

AB11

VSS54

AC11

VSS55

AJ11

VSS56

J12

VSS57

AA12

VSS58

AG12

VSS59

A13

VSS60

D13

VSS61

F13

VSS62

H13

VSS63

N13

VSS64

R13

VSS65

U13

VSS66

AB13

VSS67

AE13

VSS68

J14

VSS69

P14

VSS70

T14

VSS71

AA14

VSS72

AC14

VSS73

D15

VSS74

H15

VSS75

N15

VSS76

R15

VSS77

U15

VSS78

AB15

VSS79

AG15

VSS80

F16

VSS81

J16

VSS82

P16

VSS83

RG82855GME

11-07

VSS181

AJ26

VSS

VSS179

VSS180

E28L6T9

5

VSS177

VSS178

C22

D28

VSS174

VSS176

AJ18

AJ20

VSS172

VSS173

AJ10

AJ12

VSS171

AA29

VSS169

VSS170

W29

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

T16

AA16

AE16

A17

D17

H17

N17

R17

U17

AB17

AC17

F18

J18

AA18

AG18

A19

D19

H19

AB19

AE19

F20

J20

AA20

AC20

A21

D21

H21

M21

P21

T21

V21

Y21

AA21

AB21

AG21

B24

F22

J22

L22

N22

R22

U22

W22

AE22

A23

D23

AA23

AC23

AJ23

F24

H24

K24

M24

P24

T24

V24

AA24

AG24

A25

D25

AA25

AE25

G26

J26

L26

N26

R26

U26

W26

AB26

A27

F27

AC27

AG27

AJ27

AC28

AE28

C29

E29

G29

J29

L29

N29

U29

Only 855GME & 852GME can

support AGP function!

AGP_AD[31:0]12

AGP_SBA[7:0]12

3 4

RN34B 100KOHM /

+V1.5S_GMCH_DVO

AGP_IRDY#12

AGP_DEVSEL#12

AGP_TRDY#12

AGP_FRAME#12

AGP_STOP#12

PM_SUSCLK20

_CLK_MCH6623

FREQ_SEL4,23

1

1

G

2

S

+V1.5S_GMCH_DVO

Q94A

UM6K1N

/

4

1 2

R41 100KOhm /

1 2

RN34A 100KOHM /

+V1.5S_GMCH_DVO

/

34

56

12

12

12

78

R50 2.2KOhm /

R45 2.2KOhm /

RN11B 2.2KOhm /

RN11A 2.2KOhm /

RN11C 2.2KOhm /

RN11D 2.2KOhm

+V1.5S_GMCH_DVO

R234

1KOhm

/

1 2

3

32

D

Q54

2N7002

/

12

C374

5P

/

R407 1KOhm /

1 2

R408 1KOhm /

1 2

12

61

RN91A

1KOhm

/

+V1.5S_GMCH_DVO

Q94B

UM6K1N

/

5

+V3.3S

2

R35

1KOhm

AGP_C/BE#012

AGP_ADSTB012

AGP_ADSTB0#12

AGP_C/BE#112

AGP_C/BE#312

AGP_ADSTB112

AGP_ADSTB1#12

AGP_PAR12

AGP_VREF12

AGP_SBSTB12

AGP_SBSTB#12

AGP_GNT#12

AGP_REQ#12

AGP_WBF#12

AGP_RBF#12

AGP_C/BE#212

34

RN91B

1KOhm

/

1 2

34

1 2

/

12

R409

1KOhm

/

R43

100KOhm

AGP_AD3

AGP_AD2

AGP_AD5

AGP_AD4

AGP_AD7

AGP_AD6

AGP_AD8

AGP_C/BE#0

AGP_AD10

AGP_AD9

AGP_AD12

AGP_AD11

AGP_ADSTB0

AGP_ADSTB0#

AGP_AD0

AGP_AD1

AGP_C/BE#1

AGP_AD14

AGP_AD30

AGP_AD13

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_C/BE#3

AGP_AD25

AGP_AD24

AGP_AD27

AGP_AD26

AGP_AD29

AGP_AD28

AGP_ADSTB1

AGP_ADSTB1#

AGP_AD17

AGP_AD16

/

AGP_AD18

AGP_AD31

AGP_IRDY#

AGP_DEVSEL#

AGP_TRDY#

AGP_FRAME#

AGP_STOP#

AGP_AD15

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

ADDDETECT

AGP_PIPE

MCH_GRCOMP

T108 TPC28t

AGP_SBSTB

AGP_SBSTB#

AGP_GNT#

AGP_REQ#

T86TPC28t

T90TPC28t

T87TPC28t

GST

GST1

GST0

GST2

FSB

[2:0]

Freq.

000

400 MHz

001

400 MHz

010

400 MHz

011

400 MHz

100

533 MHz

101

533 MHz

110

533 MHz 333 MHz

111

400 MHz

*GST[2:0] are internal pulled-low.

*Current: 852GME/852GMV may still

use the GST configurations.

*Future: 852GME/852GMV only need

GST2 to strap FSB frequency.

3

U32C

R3

DVOBD[0]

R5

DVOBD[1]

R6

DVOBD[2]

R4

DVOBD[3]

P6

DVOBD[4]

P5

DVOBD[5]

N5

DVOBD[6]

P2

DVOBD[7]

N2

DVOBD[8]

N3

DVOBD[9]

M1

DVOBD[10]

M5

DVOBD[11]

P3

DVOBCLK

P4

DVOBCLK#

T6

DVOBHSYNC

T5

DVOBVSYNC

L2

DVOBBLANK#

M2

DVOBFLDSTL

G2

DVOBCINTR#

M3

DVOBCCLKINT

K5

DVOCD[0]

K1

DVOCD[1]

K3

DVOCD[2]

K2

DVOCD[3]

J6

DVOCD[4]

J5

DVOCD[5]

H2

DVOCD[6]

H1

DVOCD[7]

H3

DVOCD[8]

H4

DVOCD[9]

H6

DVOCD[10]

G3

DVOCD[11]

J3

DVOCCLK

J2

DVOCCLK#

K6

DVOCHSYNC

L5

DVOCVSYNC

L3

DVOCBLANK#

H5

DVOCFLDSTL

K7

MI2CCLK

N6

MI2CDATA

N7

MDVICLK

M6

MDVIDATA

P7

MDDCCLK

T7

MDDCDATA

E5

ADDID[0]

F5

ADDID[1]

E3

ADDID[2]

E2

ADDID[3]

G5

ADDID[4]

F4

ADDID[5]

G6

ADDID[6]

F6

ADDID[7]

L7

DVODETECT

D5

DPMS

F1

GVREF

F7

AGPBUSY#

D1

DVORCOMP

Y3

GCLKIN

1

AA5

RSVD0

F2

RSVD1

F3

RSVD2

B2

RSVD3

B3

RSVD4

D2

RSVD5

D3

RSVD6

D7

RSVD7

L4

RSVD8

1

B12

RSVD9

1

F12

RSVD10

1

D12

RSVD11

RG82855GME

11-07

System

Memory

Freq.

266 MHz

200 MHz 100 MHz

200 MHz

266 MHz

266 MHz

266 MHz

333 MHz

GFX core

Clock

-Low

133 MHz

100 MHz

133 MHz

133 MHz

133 MHz

166 MHz

166 MHz

DVO

GFX core

Clock

-High

200 MHz

200 MHz

133 MHz

266 MHz

200 MHz

266 MHz

266 MHz

250 MHz

GREEN#

DACCLKSMISCNC

REFSET

DDCACLK

DDCADATA

LVDS

DDCPCLK

DDCPDATA

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

DPSLP#

PWROK

EXTTS_0

C9

BLUE

D9

BLUE#

C8

GREEN

D8

A7

RED

A8

RED#

H10

HSYNC

J9

VSYNC

E8

B6

G9

G14

IYAM[0]

E15

IYAM[1]

C15

IYAM[2]

C13

IYAM[3]

F14

IYAP[0]

E14

IYAP[1]

C14

IYAP[2]

B13

IYAP[3]

H12

IYBM[0]

E12

IYBM[1]

C12

IYBM[2]

G11

IYBM[3]

G12

IYBP[0]

E11

IYBP[1]

C11

IYBP[2]

G10

IYBP[3]

D14

ICLKAM

E13

ICLKAP

E10

ICLKBM

F10

ICLKBP

B4

C5

G8

F8

A5

C4

GST[0]

C3

GST[1]

C2

GST[2]

A10

LIBG

B7

B17

H9

C6

AA22

DPWR#

Y23

AD28

RSTIN#

J11

D6

AJ1

VSS

B1

NC0

AH1

NC1

A2

NC2

AJ2

NC3

A28

NC4

AJ28

NC5

A29

NC6

B29

NC7

AH29

NC8

AJ29

NC9

AA9

NC10

AJ4

NC11

0.5 VCCDVO +/- 2%

AGP_VREF

Close to

Pin F1

2

CRT_REFSET

LVDS_DDC2BC

LVDS_DDC2BD

LVDS_BACK_ADJ

GST0

GST1

GST2

1

M_LCLKCTLB

+V1.5S_GMCH_DVO

12

C333

0.1uF/10V

R40 137Ohm 1%

1 2

+V3.3S_GMCH_GPIO

3 4

1 2

RN33B 2.2KOhm

RN33A 2.2KOhm

T198TPC28t

1

AGP_ST0 12

AGP_ST1 12

AGP_ST2 12

R227 1.5KOhm

1 2

R492 10KOhm

1 2

R493 10KOhm

1 2

T91TPC28t

H_DPWR# 3

H_DPSLP# 3,20

PCI_RST# 19,29,34

IMVP4_PWRGD 42,43

Width= 10 mils

Space>=20 mils

MCH_GRCOMP

1 2

1 2

12

R233

40.2Ohm

1%

R237

1KOhm

R236

1KOhm

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

Date: Sheet

A6G

+V3.3S_GMCH_GPIO

R34

10KOhm

1 2

+V3.3S

R33

10KOhm

/

M_LCLKCTLB

1 2

+V1.5S_GMCH_DVO

ADDDETECT

Title :

Engineer:

1

R48

1KOhm

1 2

R47

1KOhm

/

1 2

NB-MCHM(VGA)

John Hung

854Friday, October 15, 2004

of

Rev

1.1

Page 9

5

4

3

2

1

C74

0.1uF/10V

12

0.1uF/10V

+V1.5S

+V1.5S

CE18

11-08

C38

0.1uF/10V

C30

0.1uF/10V

0.1uF/10V

C47

12

12

+V1.2S_GMCH_CORE

12

C77

0.1uF/10V

+V1.2S_GMCH_HI

12

C73

+V1.2S_GMCH_CORE

12

C36

+V1.5S_GMCH_DVO

12

C60

0.1uF/10V

+V1.5S_GMCH_ALVDS

C329

0.01UF/10V

+V1.5S_GMCH_DLVDS

C56

+

0.1uF/10V

+V2.5_GMCH_TXLVDS

12

C321

0.1uF/10V

+V3.3S_GMCH_GPIO

12

C29

0.1uF/10V

(MCH-Sighting041)

12

12

12

12

12

12

The core supply (1.2V) should be

powered up a minimum of 1ms

before the DVO and GPIO IO

(1.5V and 3.3V) voltage rails.

U32E

J15

AA15

AA17

AA19

W21

G13

B14

B15

B10

D10

A12

P13

T13

N14

R14

U14

P15

T15

N16

R16

U16

P17

T17

H14

V1

Y1

W5

U6

U8

W8

V7

V9

D29

Y2

A6

B16

E1

J1

N1

E4

J4

M4

E6

H7

J8

L8

M8

N8

R8

K9

M9

P9

A9

B9

B8

A11

B11

J13

F9

A3

A4

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCCHL0

VCCHL1

VCCHL2

VCCHL3

VCCHL4

VCCHL5

VCCHL6

VCCHL7

VCCAHPLL

VCCAGPLL

VCCADPLLA

VCCADPLLB

VCCDVO_0

VCCDVO_1

VCCDVO_2

VCCDVO_3

VCCDVO_4

VCCDVO_5

VCCDVO_6

VCCDVO_7

VCCDVO_8

VCCDVO_9

VCCDVO_10

VCCDVO_11

VCCDVO_12

VCCDVO_13

VCCDVO_14

VCCDVO_15

VCCADAC0

VCCADAC1

VSSADAC

VCCALVDS

VSSALVDS

VCCDLVDS0

VCCDLVDS1

VCCDLVDS2

VCCDLVDS3

VCCTXLVDS0

VCCTXLVDS1

VCCTXLVDS2

VCCTXLVDS3

VCCGPIO_0

VCCGPIO_1

RG82855GME

POWER

VTTLF0

VTTLF1

VTTLF2

VTTLF3

VTTLF4

VTTLF5

VTTLF6

VTTLF7

VTTLF8

VTTLF9

VTTLF10

VTTLF11

VTTLF12

VTTLF13

VTTLF14

VTTLF15

VTTLF16

VTTLF17

VTTLF18

VTTLF19

VTTLF20

VTTHF0

VTTHF1

VTTHF2

VTTHF3

VTTHF4

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCQSM0

VCCQSM1

VCCASM0

VCCASM1

11-07

NB

VCC, VCCASM, VCCHL, VCCAGPLL,

VCCADPLLA, VCCADPLLB:

855GM/852GM: 1.2V

855GME: 1.35V

852GME/852GMV: 1.5V

3

G15

H16

H18

J19

H20

L21

N21

R21

U21

H22

M22

P22

T22

V22

Y29

K29

F29

AB29

A26

A20

A18

A22

A24

H29

M29

V29

AC1

AG1

AB3

AF3

Y4

AJ5

AA6

AB6

AF6

Y7

AA8

AB8

Y9

AF9

AJ9

AB10

AA11

AB12

AF12

AA13

AJ13

AB14

AF15

AB16

AJ17

AB18

AF18

AB20

AF21

AJ21

AB22

AF24

AJ25

AF27

AC29

AF29

AG29

AJ6

AJ8

AD1

AF1

M_PWR_VTTF0

M_PWR_VTTF1

M_PWR_VTTF2

M_PWR_VTTF3

M_PWR_VTTF4

C95

0.1uF/10V

12

C58

0.1uF/10V

C27 0.1uF/10V

C25 0.1uF/10V

C334 0.1uF/10V

C350 0.1uF/10V

C364 0.1uF/10V

+V2.5_GMCH_SM

12

+

CE23

150U/4.0V

12

C405

0.1uF/10V

12

C86

0.1uF/10V

12

C99

0.1uF/10V

+V2.5_GMCHQSM

12

C407

0.1uF/10V

R98

1 2

1Ohm

+V1.2S_GMCH_ASM

12

+

12

CE22

100UF

2

1 2

1 2

1 2

1 2

1 2

12

C67

0.1uF/10V

+V2.5

12

C406

0.1uF/10V

12

C408

0.1uF/10V

12

C102

0.1uF/10V

80Ohm/100MHz

12

C71

0.1uF/10V

2.375V - 2.625V(+/- 5%)

S0-S1M: Max. 2.07A

S3: Max. 25 mA

12

C85

0.1uF/10V

+V2.5_GMCH_SM

12

C117

4.7U

L42

+V1.2S_GMCH_HI

21

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.4 A

ASUSTek COMPUTER INC. NB1

Size Project Name

Custom

Date: Sheet

+VCCP

1.0V - 1.1V(+/- 5%)

S0-S1M: 2.5 A(CPU,MCH,ICH)

12

S0-S1M: Max. 0.72A

+

CE20

150U/4.0V

12

C90

0.1uF/10V

12

C87

0.1uF/10V

Title :

Engineer:

A6G

1

NB-MCHM(PWR)

John Hung

954Friday, October 15, 2004

of

Rev

1.1

+V1.2S

1.14V - 1.26V(+/- 5%)

S0-S1M:Max. 1.4 A

D D

+V1.2S_GMCH_CORE

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.3 A

+V1.2S_GMCH_CORE

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.3 A

C C

B B

12

+

CE21

150U/4.0V

L16

80Ohm/100MHz

CE16

150U/4.0V

L38

80Ohm/100MHz

CE14

150U/4.0V

2.375V - 2.625V(+/- 5%)

S0-S3: Max. 50 mA

1.14V - 1.26V(+/- 5%)

S0-S1M:Max. 90 mA

+V1.2S_GMCH_DPLLA

21

12

+

0.1uF/10V

+V1.2S_GMCH_DPLLB

21

12

+

0.1uF/10V

12

C375

10uF/10V

C327

C326

1.425V - 1.575V(+/- 5%)

S0-S1M: Max. 90 mA

0.1uF/10V

+V1.2S_GMCH_CORE

12

12

1.425V - 1.575V(+/- 5%)

0.1uF/10V

+V2.5

L37

21

80Ohm/100MHz

12

C63

10uF/10V

+V1.5S

CE17

+V1.5S

12

0.1uF/10V

0.1uF/10V

12

0.01UF/10V

C75

12

0.1uF/10V

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.3 A

+V1.2S_GMCH_HI

C83

+

C347

10uF/10V

+V1.5S_GMCH_ADAC

C324

C49

1.14V - 1.26V(+/- 5%)

S0-S1M: 0.3 A

150U/4.0V

C330

1.425V - 1.575V(+/- 5%)

S0-S1M: Max. 70 mA

1.425V - 1.575V(+/- 5%)

S0-S1M: Max. 70 mA

11-08

12

+

CE15

22uF/6.3V

+V3.3S

C320

0.1uF/10V

12

C50

12

12

12

C323

0.1uF/10V

22uF/6.3V

12

3.135V - 3.465V(+/- 5%)

A A

5

10uF/10V

4

Page 10

5

4

3

2

1

+V2.5 +V2.5

DDR_VREF

_DDR_DATA5

D D

_DDR_DQS06,11 _DDR_DM0 6,11

_DDR_DQS16,11

CLK_DDR06

CLK_DDR0#6

_DDR_DQS26,11

_DDR_DQS36,11

C C

_DDR_DATA0 _DDR_DATA1

_DDR_DATA3

_DDR_DATA8

_DDR_DATA13

_DDR_DATA15

_DDR_DATA10

_DDR_DATA20

_DDR_DATA19

_DDR_DATA23

_DDR_DATA25

_DDR_DATA28

_DDR_DATA27

_DDR_DATA31

CON14A

1 2

VREF0 VREF1

3 4

VSS0 VSS1

5 6

DQ0 DQ4

7 8

DQ1 DQ5

9 10

VDD0 VDD1

11 12

DQS0 DM0

13 14

DQ2 DQ6

15 16

VSS2 VSS3

17 18

DQ3 DQ7

19 20

DQ8 DQ12

21 22

VDD2 VDD3

23 24

DQ9 DQ13

25 26

DQS1 DM1

27 28

VSS4 VSS5

29 30

DQ10 DQ14

31 32

DQ11 DQ15

33 34

VDD4 VDD5

35A

A:CK0

37A

A:CK0#

39 40

VSS7 VSS8

41 42

DQ16 DQ20

43 44

DQ17 DQ21

45 46

VDD7 VDD8

47 48

DQS2 DM2

49 50

DQ18 DQ22

51 52

VSS9 VSS10

53 54

DQ19 DQ23

55 56

DQ24 DQ28

57 58

VDD9 VDD10

59 60

DQ25 DQ29

61 62

DQS3 DM3

63 64

VSS11 VSS12

65 66

DQ26 DQ30

67 68

DQ27 DQ31

69 70

VDD11 VDD12

VDD6

VSS6

36

38

DDR_VREF

_DDR_DATA4

_DDR_DATA6

_DDR_DATA2_DDR_DATA7

_DDR_DATA12

_DDR_DATA11

_DDR_DATA14

_DDR_DATA9

_DDR_DATA17

_DDR_DATA16_DDR_DATA21

_DDR_DATA18

_DDR_DATA22

_DDR_DATA24

_DDR_DATA29

_DDR_DATA26

_DDR_DATA30

_DDR_DM1 6,11

_DDR_DM2 6,11

_DDR_DM3 6,11

CLK_DDR36

CLK_DDR3#6

CLK_DDR56

CLK_DDR5#6

DDR_CKE36,11

DDR_CS2#6,11

_DDR_DATA[63:0]6,11

CON14B

37

B:CK0#

89

B:CK2

91

B:CK2#

95

B:CKE1

97

DDR_AA126,11

DDR_AA96,11

DDR_AA76,11

DDR_AB56,11

DDR_AA36,11

DDR_AB16,11

DDR_AA106,11

DDR_BS0#6,11

DDR_WE#6,11

DDR_AA12

DDR_AA9

DDR_AA7

DDR_AB5

DDR_AA3

DDR_AB1

DDR_AA10

DDR_BS0#

DDR_WE#

B:DU/A13

99

B:A12

101

B:A9

105

B:A7

107

B:A5

109

B:A3

111

B:A1

115

B:A10/AP

117

B:BA0

119

B:WE#

121

B:S0#

201

NC0

202

NC1

203

NC2

204

NC3

Dual_DDR_SODIMM_218P

B:CKE0B:CK0

B:A11

B:A8

B:A6

B:A4

B:A2

B:A0

B:BA1

B:RAS#

B:CAS#

B:S1#

B:CK1#

B:CK1

B:SA0

B:SA1

B:SA2

NP_NC7

NP_NC6

NP_NC5

NP_NC4

96B35

100B

102B

106B

108B

110B

112B

116B

118B

120B

122B

158B

160B

194B

196B

198B

208

207

206

205

DDR_AA11

DDR_AA8

DDR_AA6

DDR_AB4

DDR_AB2

DDR_AA0

DDR_BS1#

DDR_RAS#

DDR_CAS#

12

R122 10KOhm

DDR_CKE2 6,11

DDR_AA11 6,11

DDR_AA8 6,11

DDR_AA6 6,11

DDR_AB4 6,11

DDR_AB2 6,11

DDR_AA0 6,11

DDR_BS1# 6,11

DDR_RAS# 6,11

DDR_CAS# 6,11

DDR_CS3# 6,11

CLK_DDR4# 6

CLK_DDR4 6

+V3.3S

FOR +V2.5 DECOUPLING

85 86

DU_0 DU/RESET#

87 88

VSS13 VSS14

CLK_DDR26

CLK_DDR2#6

DDR_CKE16,11 DDR_CKE0 6,11

DDR_AA126,11

DDR_AA96,11

DDR_AA76,11

DDR_AA56,11

DDR_AA36,11

DDR_AA16,11

DDR_AA106,11

DDR_BS0#6,11

DDR_WE#6,11

DDR_CS0#6,11 DDR_CS1# 6,11

B B

_DDR_DQS46,11

_DDR_DQS56,11

_DDR_DQS66,11

_DDR_DQS76,11

A A

SDA_3S5,22,23

SCL_3S5,22,23

5

DDR_AA12

DDR_AA9 DDR_AA8

DDR_AA3

DDR_BS0#

DDR_WE#

_DDR_DATA34

_DDR_DATA38

_DDR_DATA45

_DDR_DATA41

_DDR_DATA43

_DDR_DATA53

_DDR_DATA52

_DDR_DATA48

_DDR_DATA60

_DDR_DATA57

_DDR_DATA62 _DDR_DATA63

_DDR_DATA58 _DDR_DATA59

+V3.3S

12

C168

0.1uF/10V

89A

A:CK2

91A

A:CK2#

93 94

VDD14 VDD15

95A

A:CKE1

97A

A:DU/A13

99A

A:A12

101A

A:A9

103 104

VSS16 VSS17

105A

A:A7

107A

A:A5

109A

A:A3

111A

A:A1

113 114

VDD16 VDD17

115A

A:A10/AP

117A

A:BA0

119A

A:WE#

121A

A:S0#

123 124

DU_1 DU_3

125 126

VSS18 VSS19

127 128

DQ32 DQ36

129 130

DQ33 DQ37

131 132

VDD18 VDD19

133 134

DQS4 DM4

135 136

DQ34 DQ38

137 138

VSS20 VSS21

139 140

DQ35 DQ39

141 142

DQ40 DQ44

143 144

VDD20 VDD21

145 146

DQ41 DQ45

147 148

DQS5 DM5

149 150

VSS22 VSS23

151 152

DQ42 DQ46

153 154

DQ43 DQ47

155 156

VDD22 VDD23

157

VDD24

159

VSS24

161 162

VSS25 VSS26

163 164

DQ48 DQ52

165 166

DQ49 DQ53

167 168

VDD25 VDD26

169 170

DQS6 DM6

171 172

DQ50 DQ54

173 174

VSS27 VSS28

175 176

DQ51 DQ55

177 178

DQ56 DQ60

179 180

VDD27 VDD28

181 182

DQ57 DQ61

183 184

DQS7 DM7

185 186

VSS29 VSS30

187 188

DQ58 DQ62

189 190

DQ59 DQ63

191 192

VDD29 VDD30

193

SDA

195

SCL

197

VDDSPD

199 200

VDDID DU_2

Dual_DDR_SODIMM_218P

4

VSS15

VDD13

A:CKE0

DU/BA2

A:A11

A:A8

A:A6

A:A4

A:A2

A:A0

A:BA1

A:RAS#

A:CAS#

A:S1#

A:CK1#

A:CK1

A:SA0

A:SA1

A:SA2

90

92

96

98

100

102

106

108