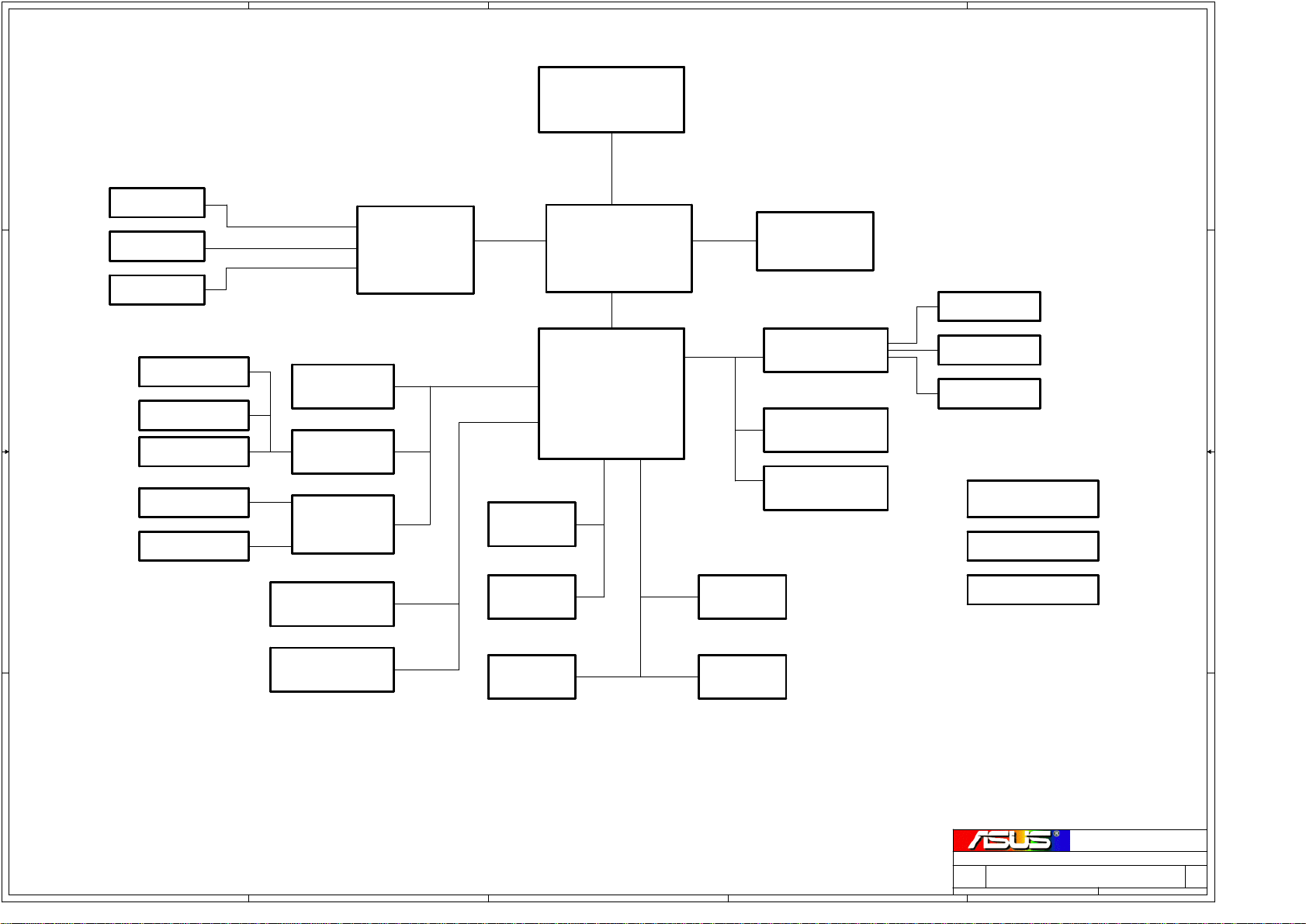

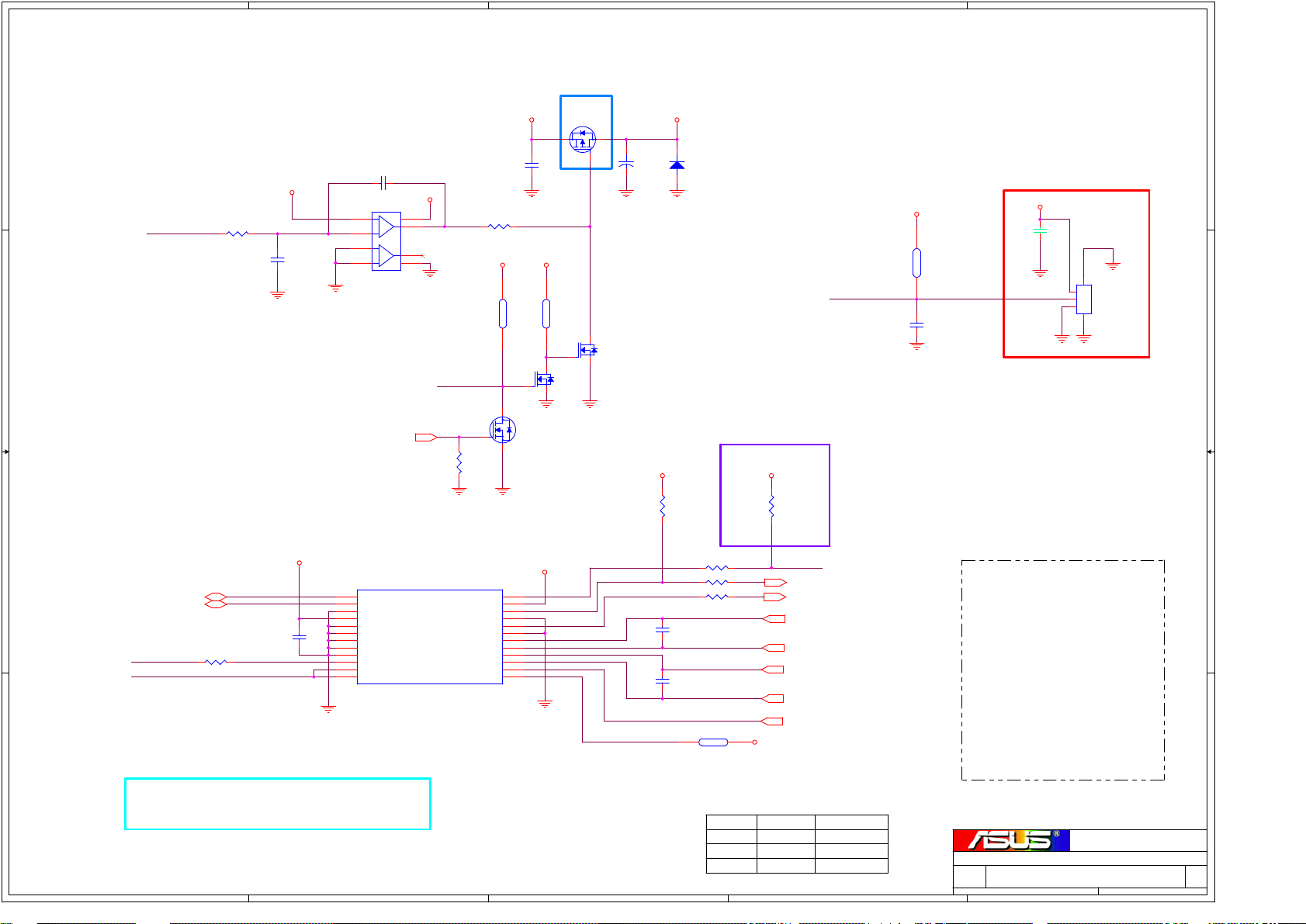

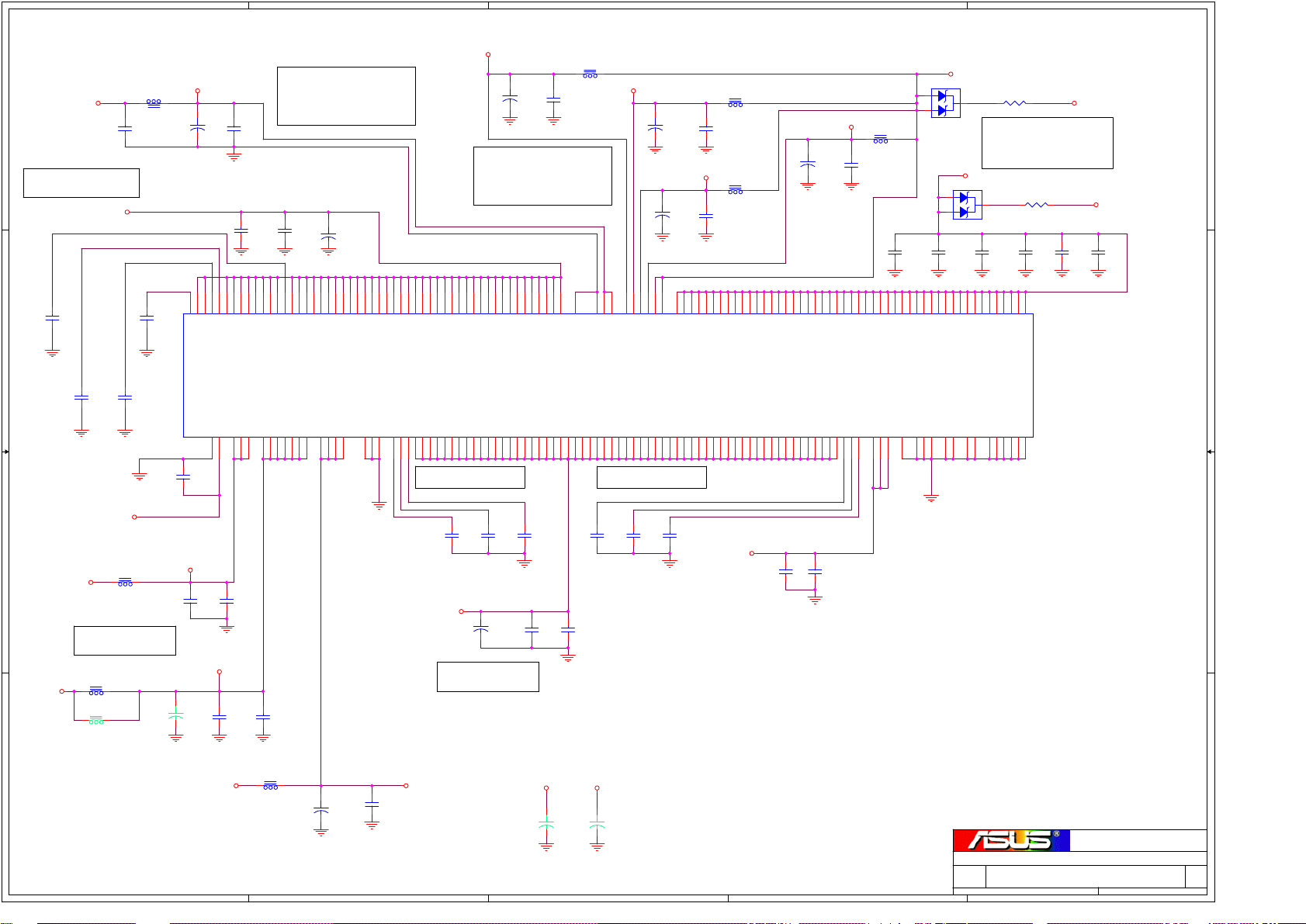

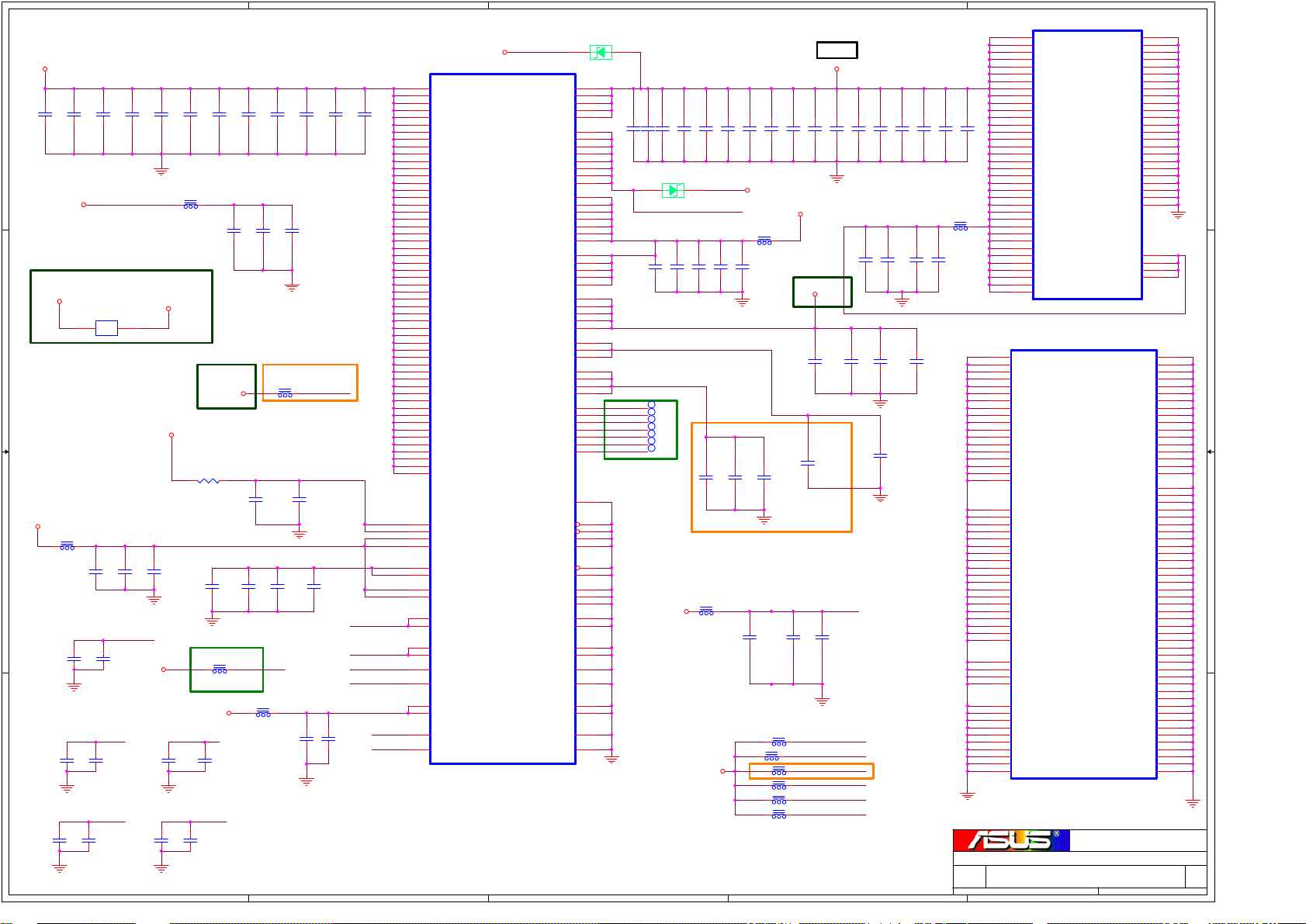

Asus A3V,A3VP Schematics

5

4

3

CP

U

2

1

DOTHAN

D D

LVD

S

PAGE 25

CR

T

PAGE 26

TV

OUT

PAGE 26

C C

CO

PO

AUDI

IN

STANT KEY

B B

M PORT

RTBAR

SI

R

O DJ KEY

PAGE 34

PAGE 28

PAGE 17

PAGE 40

PAGE 40

SUP

LPC47N2

KBC

ATI

M24/26P

PAGE 12,13,14,15,16

FWH

PAGE 28

ER I/O

17

PAGE 17

38857

PAGE 27

AZALIA CODEC

PAGE 29,30,31

LPC

33MHz

Azali

PCI-E

a

CD

HDD

ROM

PAGE 3,4

PAGE 6,7,8,9,10

PAGE 18,19,20

PAGE 38

PAGE 38

53

3MHZ

FSB

533MHz

MCH-M

Alviso

DMI inte

ICH6-M

IDE

rface

DDR2

PCI

33MHz

BT M

PAGE 22,23,24

PAGE 34

odule

DDR2

SO-DIMM

R5C841

PAGE 35,36,37

MINI-PCI 1

WIRE LESS

10/100 LAN

RTL8100CL

PAGE 32

PAGE 33,34

PCMCIA

1394

CARD REA

PAGE 21

DER

CLOC

GENERATO

FAN + SENSOR

PAGE 5

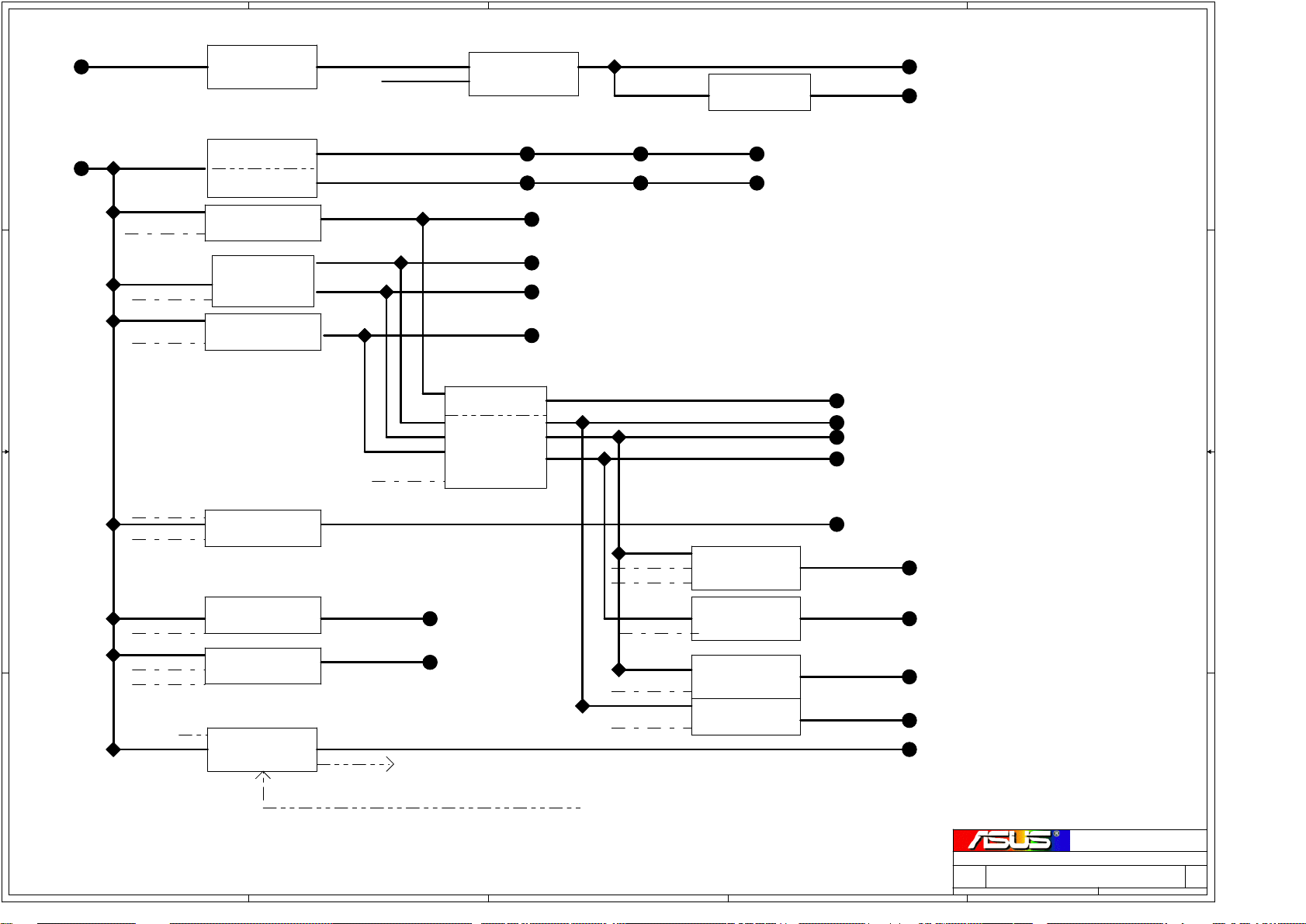

Power On Sequenc

PAGE 42,43

PAGE 36

PAGE 37

PAGE 35

K

R

e

0

PAGE 39

USB

USB CCD

PAGE 25

Title :

BLOCK DIAGRAM

Size

Project Name

Custom

3

2

Date:

A3V

Tuesday, August 02, 2005

Engineer:

Miller Liu

1

Sheet

1

Rev

1.1

55

of

MDC Header

PAGE 34

A A

5

4

USB 2.

X

4

5

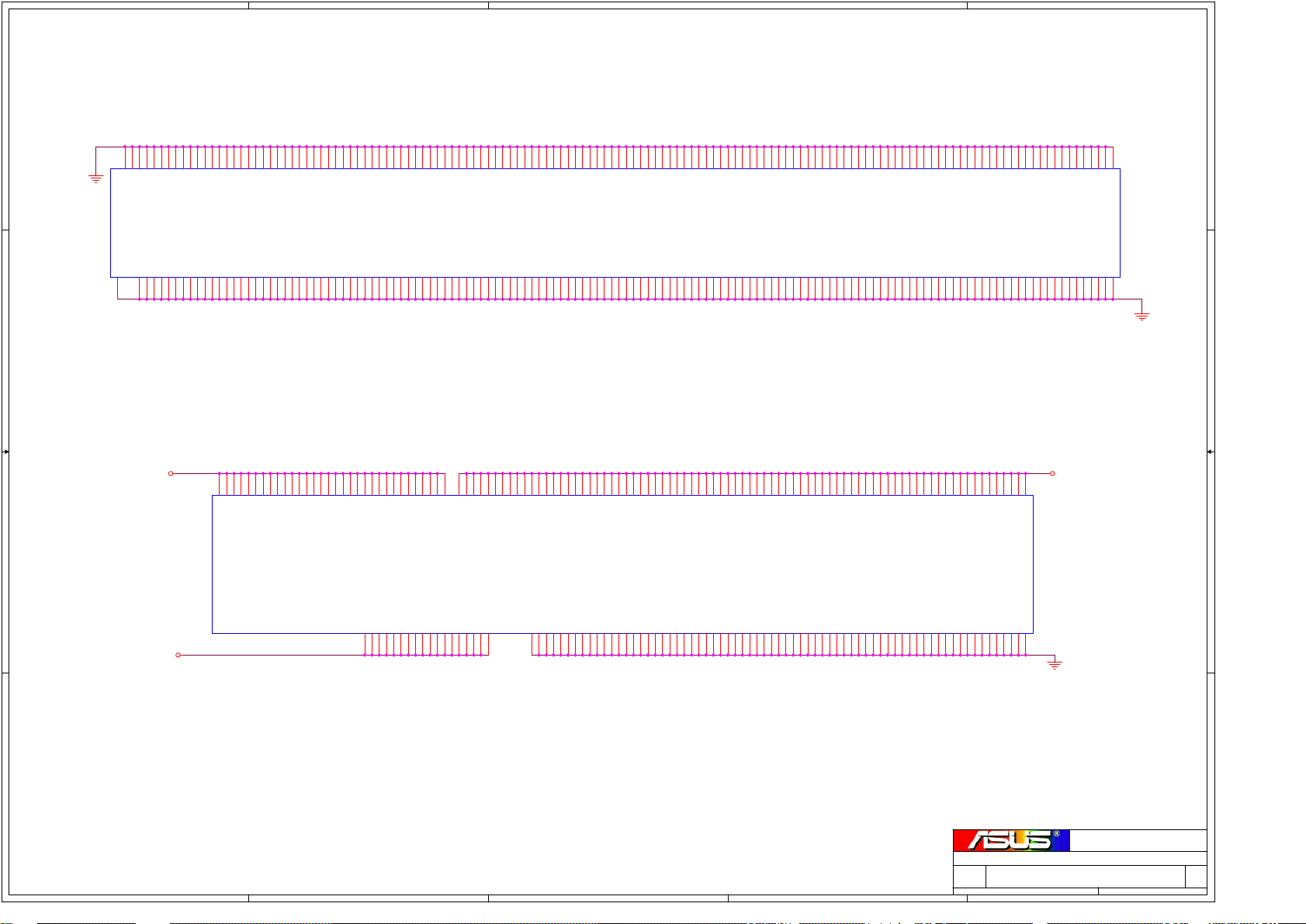

P.5

1

A/D_DOCK_I

D D

AC_BAT_SY

SUSC#_PW

N

(Regulator

S

R

L78L05

P.4

5

MIC5233BM

TPS5102

P.5

2

(UMC4N

)

5

0

)

4

+5VCHG

+5VO

(20mA)

+3VA

+5VA

P.5

1

SWITCH

(F02JK2E

+12V

)

+3VALWAY

+5VALWAY

3

2

1

+5VLCM

LM4040BI

(Regulator

S

S

+3VSUS

+5VSUS

P.5

M

1

)

+2.5VRE

F

+5V

P.4

5

SUSC#_PW

C C

SUSC#_PW

R

R

MAX8743EE

TPS5102

P.4

0

6

I

+3V

+1.8V

P.5

2

UMC4N

+12VS

+5VS

+3VS

SI4800D

SUSB#_PW

+5VO

SUSB#_PW

B B

CPU_VRO

SUSC#_PW

SUSB#_PW

+5MCH_O

A A

5

R

N

R

R

K

P.4

7

MAX8578EU

P.4

6

MAX8743EE

P.4

7

MAX1844EE

CPU_VRO

MAX198

N

7

(Controllor

B

+VCCP

I

+1.05V

+ATI_VCOR

P

P.4

4

)

VR_VID0 - VR_VID5, STP_CPU#, PM_DPRSLPVR

4

R

O

E

DELAY_VR_PWRG

CLK_PWR_GD

Y

+1.8VS

+1.5VS

P.4

+3VS

CPU_F_SE

SUSB#_PW

SUSB#_PW

SUSB#_PW

L

R

R

MIC49150BM

R

8

SI9183D

P.4

8

CM8562

P.5

3

LM358ADR

SI4800BD

P.5

3

T

&

Y

M

+1.8VS_PRO

+0.9VS

+2.5VS

+2.5VO

+1.2VS

+VCORE

C

P

(27A)

D,

#

, PM_PSI#

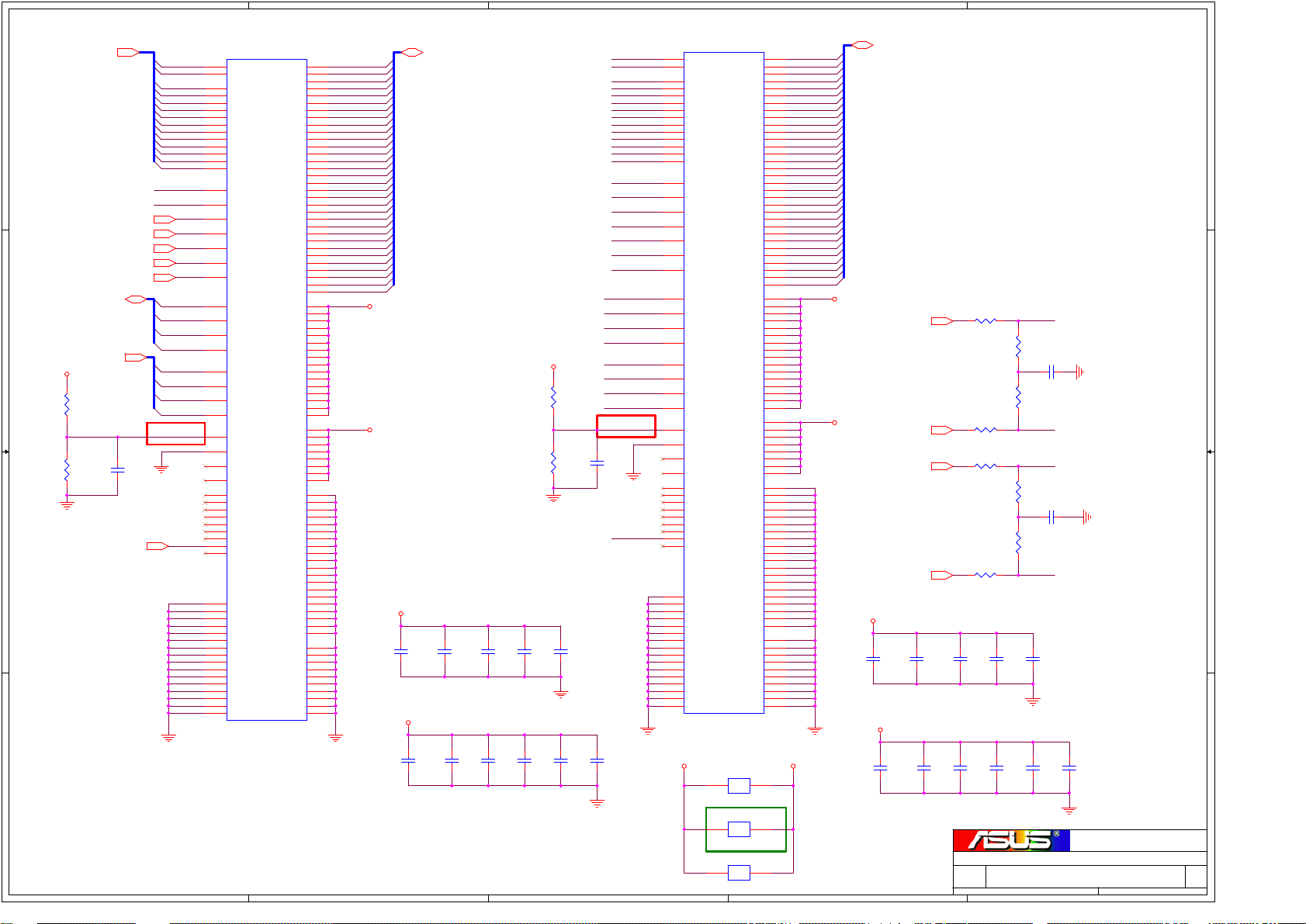

Power Block Diagram

Title :

Size

Project Name

Custom

3

2

Date:

A3V

Tuesday, August 02, 2005

Engineer:

Miller Liu

2

Sheet

1

Rev

1.1

55

of

5

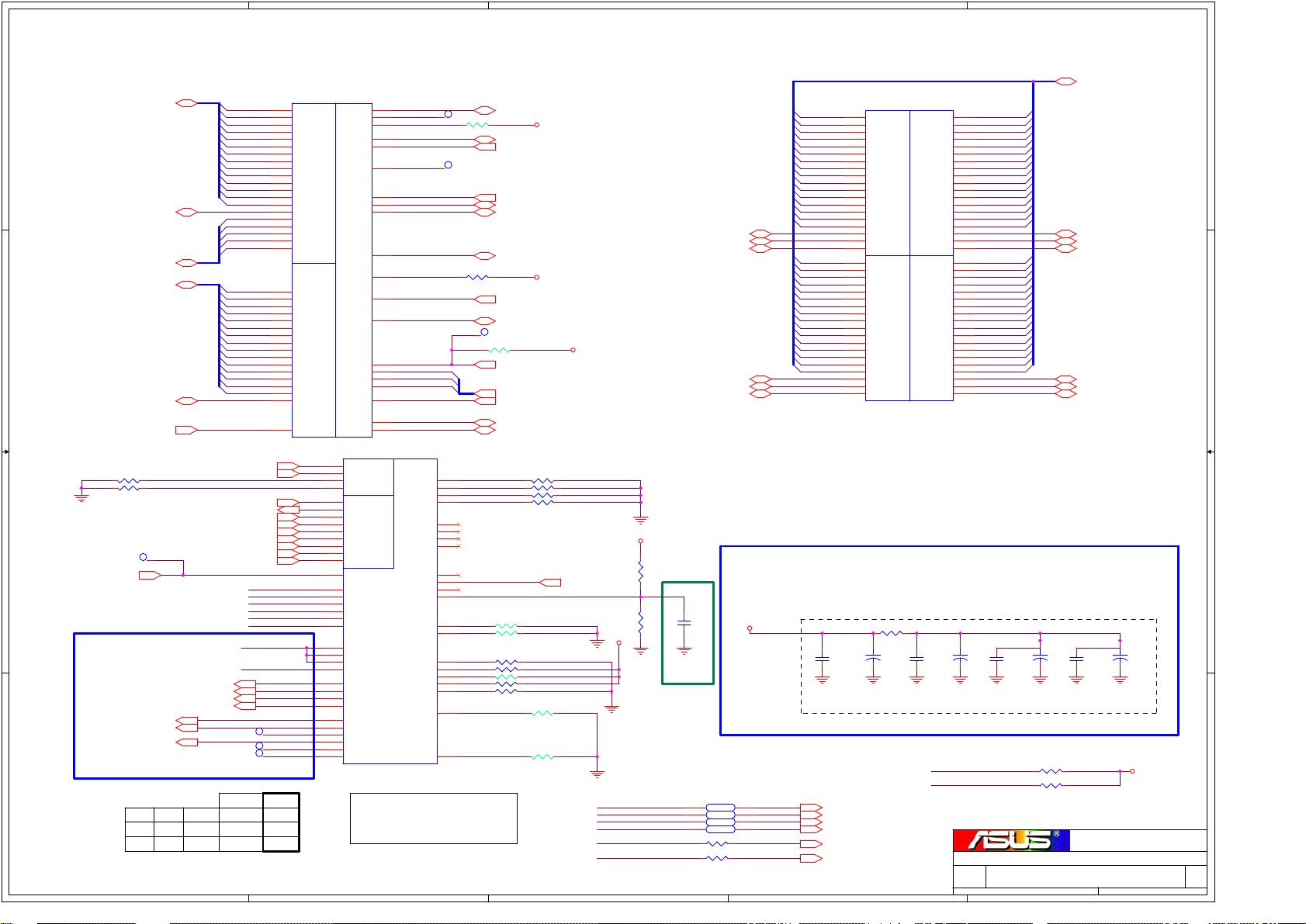

H_A20M#

H_INTR

H_NMI

H_SMI#

H_VID5

H_VID4

H_VID3

H_VID2

H_VID1

H_VID0

1

1

1

-STEP

AA2

Y3

AA3

U1

Y1

Y4

W2

T4

W1

V2

R3

V3

U4

P4

U3

T1

P1

T2

P3

R2

AF1

AE1

AF3

AD6

AE2

AD5

AC6

AB4

AD2

AE4

AD3

AC3

AC7

AC4

AF4

AE5

C19

TPC28t

TPC28t

L0

U48B

A[16]#

A[15]#

A[14]#

A[13]#

A[12]#

A[11]#

A[10]#

A[9]#

A[8]#

A[7]#

A[6]#

A[5]#

A[4]#

A[3]#

ADSTB[0]#

REQ[4]#

REQ[3]#

REQ[2]#

REQ[1]#

REQ[0]#

A[31]#

A[30]#

A[29]#

A[28]#

A[27]#

A[26]#

A[25]#

A[24]#

A[23]#

A[22]#

A[21]#

A[20]#

A[19]#

A[18]#

A[17]#

ADSTB[1]#

DPWR#

SOCKET479P

AC26

M0417

H_A#[16..3]

6

D D

H_ADSTB#0

6

H_REQ#[4..0]

6

H_A#[31..17]

6

C C

H_ADSTB#1

6

H_DPWR#

6

R20

R21

GND

B B

A A

18

H_PWRGD

r0402

12

r0402

12

T28TPC28t

1

PM_PSI#

44

CPU_BSEL0

21,43

CPU_BSEL1

21

49.9Ohm

49.9Ohm

7,18

1%

1%

CPU_THRM_DA

5

CPU_THRM_DC

5

PM_THRMTRIP#

H_PROCHOT_S#

5

H_A#16

H_A#15

H_A#14

H_A#13

H_A#12

H_A#11

H_A#10

H_A#9

H_A#8

H_A#7

H_A#6

H_A#5

H_A#4

H_A#3

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_A#31

H_A#30

H_A#29

H_A#28

H_A#27

H_A#26

H_A#25

H_A#24

H_A#23

H_A#22

H_A#21

H_A#20

H_A#19

H_A#18

H_A#17

CLK_CPU_BCLK

21

CLK_CPU_BCLK#

21

18

18

18

18

H_CPUSLP#

6,18

18

H_FERR#

H_IGNNE#

H_DPSLP#

18

18

18

H_STPCLK#

+VCCA_RSVD

+VCCA_PROC

T27TPC28t

T217

T211

A-STEP B

FSB BSEL1 BSEL0 BSE

Bclk

100

400

533

0 0 1

0 1 0

133

5

4

ADS#

PRDY#

PREQ#

BNR#

BPRI#

DBR#

ADDRESS GROUP 0ADDRESS GROUP 1

DEFER#

DRDY#

DBSY#

BR0#

CONTROL

IERR#

INIT#

LOCK#

RESET#

RS[2]#

RS[1]#

RS[0]#

TRDY#

HIT#

HITM#

U48C

B15

BCLK[0]

B14

BCLK[1]

A16

ITP_CLK[0]

A15

ITP_CLK[1]

C2

A20M#

D3

FERR#

A3

IGNNE#

B7

DPSLP#

A6

SLP#

D1

LINT0

D4

LINT1

B4

SMI#

C6

STPCLK#

E4

PWRGOOD

H4

VID[5]

G4

VID[4]

G3

VID[3]

F3

VID[2]

F2

VID[1]

E2

VID[0]

VCCA[3]

N1

VCCA[2]

B1

VCCA[1]

F26

VCCA[0]

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

B17

PROCHOT#

E1

RSVD5

C16

RSVD4

C3

RSVD3

C14

RSVD2

AF7

RSVD1

B2

RSVD0

SOCKET479P

Dothan FS

Min Ty

VCCA 1.425V 1.5

Min Ty

ICCA

4

N2

A10

B10

L1

J3

A7

L4

H2

M2

N4

A4

B5

J2

B11

L2

K1

H1

M3

K3

K4

TPC28t

TPC28t

H_IERR#

COMP[3]

COMP[2]

HOSTCLKLEGACY CPU

COMP[1]

COMP[0]

BPM[3]#

BPM[2]#

BPM[1]#

BPM[0]#

GTLREF[3]

GTLREF[2]

GTLREF[1]

GTLREF[0]

MISC

VCCSENSE

VSSSENSE

B533

H_RS#2

H_RS#1

H_RS#0

TEST1

TEST2

TCK

TDO

TMS

TRST#

1

1

TDI

T222

R19

r0402

/

T214

R44

r0402

TPC28t

1

R25

H_COMP3

AB1

H_COMP2

AB2

H_COMP1

P26

H_COMP0

P25

C9

A9

B8

C8

AC1

G1

E26

GTL_REF0

AD26

R45

C5

R108

F23

R32

A13

R18

C12

R24

A12

R23

C11

R30

B13

VCCSENSE

AE7

VSSSENSE

AF6

p Max

V 1.575V

p Max

120mA

H_ADS#

56Ohm

H_BNR#

H_BPRI#

H_DEFER#

H_DRDY#

H_DBSY#

H_BR0#

56Ohm

H_INIT#

H_LOCK#

T3

8

/

H_CPURST#

H_RS#[0..2]

H_TRDY#

H_HIT#

H_HITM#

R39

R40

R523

R524

/

1 2

/

1 2

1 2

1 2

1 2

1 2

R487

R484

6

6

6

6

6

6

18

6

54.9Ohm

12

6

6

6

1 2

1 2

r0402

1KOhm

1KOhm

r0402

27.4Ohm

150Ohm

54.9Ohm

/

12

39Ohm

8.2KOhm

+VCCP

6

+VCCP

6

6

1%

54.9Ohm

12

27.4Ohm

54.9Ohm

12

27.4Ohm

H_DPRSTP#

1%

54.9Ohm

/

12

54.9Ohm

/

12

+VCCP

1%

1%

GND

GND

1%

1%

3

18

+VCCP

GND

H_VID1

H_VID0

3

GND

+VCCP

R522

1KOhm

1%

r0402

1 2

R521

2KOhm

1%

r0402

1 2

GND

GND

CAP 0.1UF/16V (0603) X7R (104)

H_VID4

H_VID3

H_VID2

H_VID5

R41

R43

6

6

6

6

12

C901

0.1U

4/13

1 2

3 4

5 6

7 8

1 2

1 2

H_DINV#0

6

H_DSTBN#0

H_DSTBP#0

H_DINV#1

6

H_DSTBN#1

H_DSTBP#1

120mA / 2

0Ohm

0Ohm

0Ohm

0Ohm

r0402

r0402

2

H_D#15

C25

H_D#14

H_D#13

H_D#12

H_D#11

H_D#9

H_D#8

H_D#7

H_D#6

H_D#5

H_D#4

H_D#3

H_D#2

H_D#1

H_D#0

H_D#31

H_D#30

H_D#29

H_D#28

H_D#27

H_D#26

H_D#25

H_D#24

H_D#23

H_D#22

H_D#21

H_D#20

H_D#19

H_D#18

H_D#17

H_D#16

Layout n

ote:

COMP0 and COMP2 need to be Z

Best estimate is 18mil wide trace

14mil if on internal layer. S

Traces should be shorter than 0.5". R

COMP1, COMP3 should be ro

traces shorter

D[15]#

E23

D[14]#

B23

D[13]#

C26

D[12]#

E24

D[11]#

D24

D[10]#

B24

D[9]#

C20

D[8]#

B20

D[7]#

A21

D[6]#

B26

D[5]#

A24

D[4]#

B21

D[3]#

A22

D[2]#

A25

D[1]#

A19

D[0]#

D25

DINV[0]#

C23

DSTBN[0]#

C22

DSTBP[0]#

K25

D[31]#

N25

D[30]#

H26

D[29]#

M25

D[28]#

N24

D[27]#

L26

D[26]#

J25

D[25]#

M23

D[24]#

J23

D[23]#

G24

D[22]#

F25

D[21]#

H24

D[20]#

M26

D[19]#

L23

D[18]#

G25

D[17]#

H23

D[16]#

J26

DINV[1]#

K24

DSTBN[1]#

L24

DSTBP[1]#

SOCKET479P

than 0.5"

0mil

+VCCA_PROC

RN2A

RN2B

RN2C

RN2D

0Ohm

0Ohm

+VCCA_PROC

12

C656

10uF/10V

c0805

VR_VID4

VR_VID3

VR_VID2

VR_VID5

VR_VID1

VR_VID0

2

44

44

44

44

44

44

U48A

DATA GROUP 0DATA GROUP 1

o=27.4ohm traces.

uted as Zo=55ohm

FSB 400MHz FSB 533MHz -

R733

0Ohm

1 2

R0603

12

+

C652

0.01UF

c0402

GNDGND GND

D[47]#

D[46]#

D[45]#

D[44]#

D[43]#

D[42]#

D[41]#

D[40]#

D[39]#

D[38]#

D[37]#

D[36]#

DATA GROUP 2DATA GROUP 3

D[35]#

D[34]#

D[33]#

D[32]#

DINV[2]#

DSTBN[2]#

DSTBP[2]#

D[63]#

D[62]#

D[61]#

D[60]#

D[59]#

D[58]#

D[57]#

D[56]#

D[55]#

D[54]#

D[53]#

D[52]#

D[51]#

D[50]#

D[49]#

D[48]#

DINV[3]#

DSTBN[3]#

DSTBP[3]#

for outer layers and

ee RDDP of Banias.

12

C61

10uF/10V

c0805

H_D#46

AA26

H_D#45

Y23

H_D#44

V26

H_D#43

U25

H_D#42H_D#10

V24

H_D#41

U26

H_D#40

AA23

H_D#39

R23

H_D#38

R26

H_D#37

R24

H_D#36

V23

H_D#35

U23

H_D#34

T25

H_D#33

AA24

H_D#32

Y26

T24

W25

W24

H_D#63

AF26

H_D#62

AF22

H_D#61

AF25

H_D#60

AD21

H_D#59

AE21

H_D#58

AF20

H_D#57

AD24

H_D#56

AF23

H_D#55

AE22

H_D#54

AD23

H_D#53

AC25

H_D#52

AC22

H_D#51

AC20

H_D#50

AB24

H_D#49

AC23

H_D#48

AB25

AD20

AE24

AE25

efer to latest CS layout

> 1.8V

> 1.5V

+VCCA_RSVD

12

+

12

C653

C662

0.01UF

10uF/10V

c0402

c0805

H_D#47

Y25

Place near CPU pin

H_PWRGD

H_PROCHOT_S#

Size

Project Name

Custom

Tuesday, August 02, 2005

Date:

R42

R22

A3V

12

+

C68

0.01UF

c0402

GND GNDGNDGND GND

r0402

1 2

r0402

1

H_D#[0..63]

H_DINV#2

H_DSTBN#2

H_DSTBP#2

H_DINV#3

H_DSTBN#3

H_DSTBP#3

12

C56

10uF/10V

c0805

200Ohm

56Ohm

Title :

Engineer:

Sheet

1

6

6

6

6

6

6

6

12

+

C66

0.01UF

c0402

1%

+VCCP

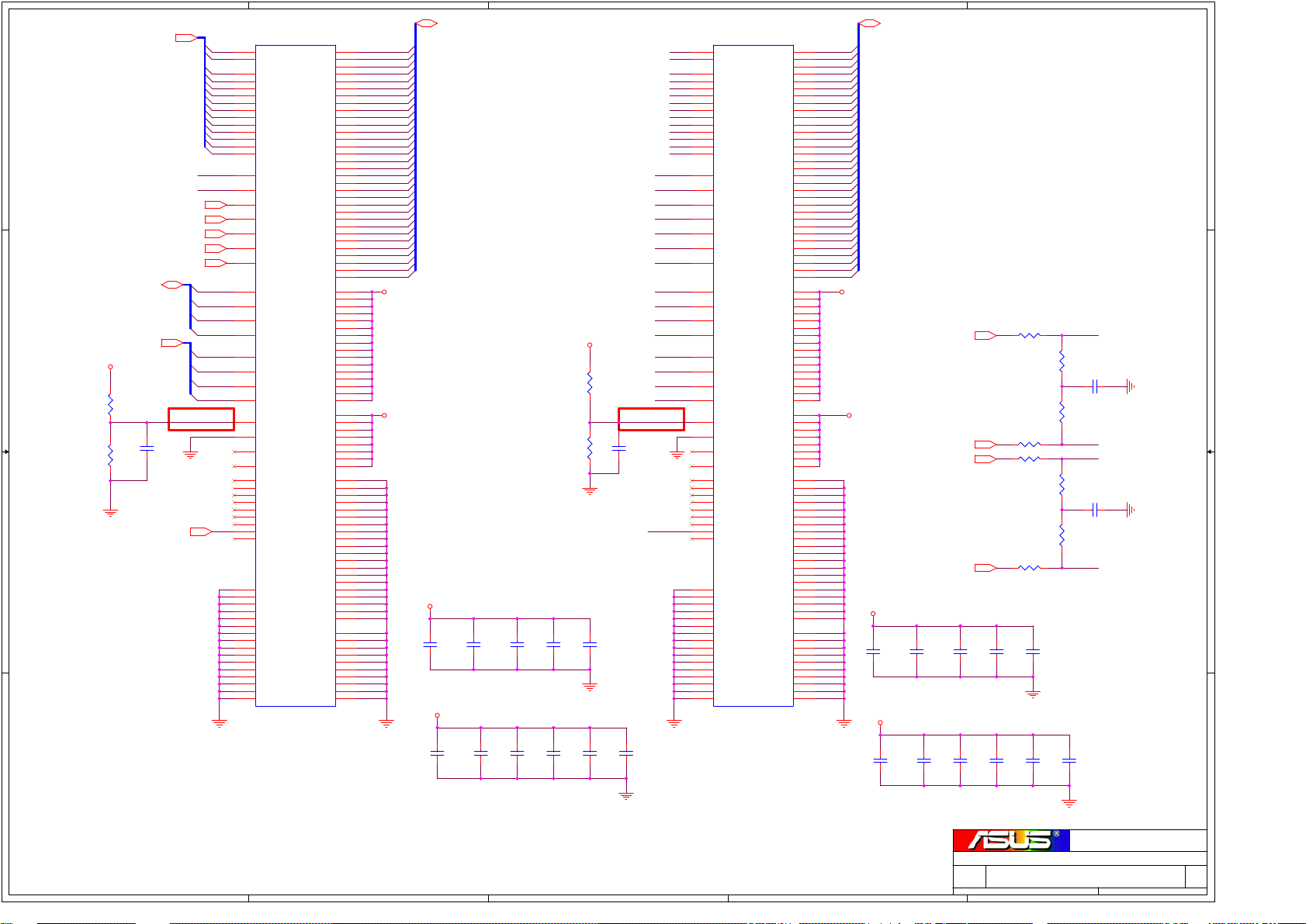

DOTHAN CPU(1)

Miller_Liu

3

M0417

of

Rev

1.1

55

5

Dothan FS

B533

LFM TYP

+VCCP

D D

C C

B B

VCC 1.14V 1.2V

C4 C

ICC 0.9A 7.59

U48D

W4

VCCQ[1]

P23

VCCQ[0]

D10

VCCP1

D12

VCCP2

D14

VCCP3

D16

VCCP4

E11

VCCP5

E13

VCCP6

E15

VCCP7

F10

VCCP8

F12

VCCP9

F14

VCCP10

F16

VCCP11

K6

VCCP12

L5

VCCP13

L21

VCCP14

M6

VCCP15

M22

VCCP16

N5

VCCP17

N21

VCCP18

P6

VCCP19

P22

VCCP20

R5

VCCP21

R21

VCCP22

T6

VCCP23

T22

VCCP24

U21

VCCP25

VCC70

VCC71

VCC72

AF14

AF16

AF18

VCC69

AF12

VCC67

VCC68

AF8

AF10

HFM

3 C0

VCC

VCC63

VCC64

VCC65

VCC66

AE13

AE15

AE17

AE19

1.356V

A 27A

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC62

VCC61

SOCKET479P

AE11

AE9

D6

D8

D18

D20

D22

E5

E7

E9

E17

E19

E21

F6

F8

F18

F20

F22

G5

G21

H6

H22

J5

J21

K22

U5

V6

V22

W5

W21

Y6

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

AC19

AD8

AD10

AD12

AD14

AD16

AD18

+VCORE

4

AF24

AF21

AF19

AF17

AF15

AF13

U48E

A2

VSS1

A5

VSS2

A8

VSS3

A11

VSS4

A14

VSS5

A17

VSS6

A20

VSS7

A23

VSS8

A26

VSS9

B3

VSS10

B6

VSS11

B9

VSS12

B12

VSS13

B16

VSS14

B19

VSS15

B22

VSS16

B25

VSS17

C1

VSS18

C4

VSS19

C7

VSS20

C10

VSS21

C13

VSS22

C15

VSS23

C18

VSS24

C21

VSS25

C24

VSS26

D2

VSS27

D5

VSS28

D7

VSS29

D9

VSS30

D11

VSS31

D13

VSS32

D15

VSS33

D17

VSS34

D19

VSS35

D21

VSS36

D23

VSS37

D26

VSS38

E3

VSS39

E6

VSS40

E8

VSS41

E10

VSS42

E12

VSS43

E14

VSS44

E16

VSS45

E18

VSS46

E20

VSS47

E22

VSS48

E25

VSS49

F1

VSS50

F4

VSS51

F5

VSS52

F7

VSS53

F9

VSS54

F11

VSS55

F13

VSS56

F15

VSS57

F17

VSS58

F19

VSS59

F21

VSS60

F24

VSS61

G2

VSS62

G6

VSS63

G22

VSS64

AF11

VSS192

VSS191

VSS190

VSS189

VSS188

VSS187

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

G23

G26H3H5

H21

H25J1J4J6J22

3

AF9

AF5

AF2

AE26

AE23

AE20

AE18

AE16

AE14

AE12

AE10

AE8

AE6

AE3

AD25

AD22

AD19

AD17

AD15

AD13

AD11

AD9

AD7

AD4

AD1

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS163

VSS162

GND

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS71

VSS78

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

P2

N26

N23

N22N6N3

M24

M21M5M4M1L25

L22L6L3

K26

K23

K21

J24K2K5

P5

VSS160

VSS159

VSS158

VSS161

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS147

VSS146

VSS145

VSS144

VSS143

VSS142

VSS141

VSS140

VSS139

VSS138

VSS137

VSS136

VSS135

VSS134

VSS133

VSS132

VSS131

VSS130

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS99

VSS98

VSS97

VSS96

SOCKET479P

AC24

AC21

AC18

AC16

AC14

AC12

AC10

AC8

AC5

AC2

AB26

AB23

AB21

AB19

AB17

AB15

AB13

AB11

AB9

AB7

AB5

AB3

AA25

AA22

AA20

AA18

AA16

AA14

AA12

AA10

AA8

AA6

AA4

AA1

Y24

Y21

Y5

Y2

W26

W23

W22

W6

W3

V25

V21

V5

V4

V1

U24

U22

U6

U2

T26

T23

T21

T5

T3

R25

R22

R6

R4

R1

P24

P21

2

MOBILE DOTHAN VID TAB

Volta

ge

VID[5.

.0]

0 0 0 0 0 0 1.7

0 0 0 0 0 1 1.6

0 0 0 0 1 0 1.6

0 0 0 0 1 1 1.6

0 0 0 1 0 0 1.6

0 0 0 1 0 1 1.6

0 0 0 1 1 0 1.6

0 0 0 1 1 1 1.5

0 0 1 0 0 0 1.5

0 0 1 0 0 1 1.5

0 0 1 0 1 0 1.5

0 0 1 0 1 1 1.5

0 0 1 1 0 0 1.5

0 0 1 1 0 1 1.5

0 0 1 1 1 0 1.4

0 0 1 1 1 1 1.4

0 1 0 0 0 0 1.4

0 1 0 0 0 1 1.4

0 1 0 0 1 0 1.4

0 1 0 0 1 1 1.4

0 1 0 1 0 0 1.3

0 1 0 1 0 1 1.3

0 1 0 1 1 0 1.3

0 1 0 1 1 1 1.3

0 1 1 0 0 0 1.3

0 1 1 0 0 1 1.3

0 1 1 0 1 0 1.2

0 1 1 0 1 1 1.2

0 1 1 1 0 0 1.2

0 1 1 1 0 1 1.2

0 1 1 1 1 0 1.2

0 1 1 1 1 1 1.2

08V

92V

76V

60V

44V

28V

12V

96V

80V

64V

48V

32V

16V

00V

84V

68V

52V

36V

20V

04V

88V

72V

56V

40V

24V

08V

92V

76V

60V

44V

28V

12V

VID[5.

1 0 0 0 0 0 1.1

1 0 0 0 0 1 1.1

1 0 0 0 1 0 1.1

1 0 0 0 1 1 1.1

1 0 0 1 0 0 1.1

1 0 0 1 0 1 1.1

1 0 0 1 1 0 1.1

1 0 0 1 1 1 1.0

1 0 1 0 0 0 1.0

1 0 1 0 0 1 1.0

1 0 1 0 1 0 1.0

1 0 1 0 1 1 1.0

1 0 1 1 0 0 1.0

1 0 1 1 0 1 0.9

1 0 1 1 1 0 0.9

1 0 1 1 1 1 0.9

1 1 0 0 0 0 0.9

1 1 0 0 0 1 0.9

1 1 0 0 1 0 0.9

1 1 0 0 1 1 0.8

1 1 0 1 0 0 0.8

1 1 0 1 0 1 0.8

1 1 0 1 1 0 0.8

1 1 0 1 1 1 0.8

1 1 1 0 0 0 0.8

1 1 1 0 0 1 0.7

1 1 1 0 1 0 0.7

1 1 1 0 1 1 0.7

1 1 1 1 0 0 0.7

1 1 1 1 0 1 0.7

1 1 1 1 1 0 0.7

1 1 1 1 1 1 0.7

1

LE

.0]

Volta

ge

96V

80V

64V

48V

32V

16V

00V

84V

68V

52V

36V

20V

04V

88V

72V

56V

40V

24V

08V

92V

76V

60V

44V

28V

12V

96V

80V

64V

48V

32V

16V

00V

GND

B533

p Max

V 1.102V

p Max

2.5A

12

12

+VCC

(Pl

ace near CPU)

C567

C621

0.1UF

0.1UF

c0402

c0402

P (CPU) Decoupling Capacitor

2

12

C569

0.1UF

c0402

C619

0.1UF

c0402

GNDGND

Size

Custom

Tuesday, August 02, 2005

Date:

C622

0.1UF

c0402

Project Name

GNDGND GND

A3V

12

12

12

12

C566

0.1UF

c0402

GNDGND

C155

10uF/10V

c0805

Title :

12

DOTHAN CPU(2)

Engineer:

Sheet

1

C615

10uF/10V

c0805

Miller Liu

4

12

C161

0.1UF

c0402

Rev

1.1

55

of

12

10uF/10V

12

10uF/10V

12

10uF/10V

12

10uF/10V

c0805

C574

C594

C576

C181

GND

12

10uF/10V

12

10uF/10V

12

10uF/10V

12

10uF/10V

c0805

C133

C191

C629

C102

GND

Mid Frequency

Decoupling (Place

around

Processor)

High Frequency

Decoupling (Place

underneath

Processor) using

10uF/6.3V X5R

+VCORE

Bulk

Decoupling

1.0V - 1.

2V(+/- 5%)

S0-S1M: 2.

5

A(CPU,MCH,ICH)

+VCCP

12

+

12

C568

0.1UF

CE26

c0402

150U/4.0V

GND

Four 200 uF are

located i

IM

3

n

VP4

Dothan FS

Min Ty

VCCP 0.997V 1.05

Min Ty

ICCP

12

C570

0.1UF

c0402

GND

GND GND GNDGND

12

C620

0.1UF

c0402

+VCORE

12

C587

10uF/10V

c0805

12

C166

10uF/10V

12

C182

12

10uF/10V

10uF/10V

C183

A A

CPU VCORE Decoupling Capacitor

12

12

12

12

12

12

10uF/10V

c0805

C578

10uF/10V

c0805

C184

10uF/10V

C608

10uF/10V

C586

12

12

12

+

5

C596

10uF/10V

c0805

C178

10uF/10V

C606

10uF/10V

C624

0.01UF

12

12

12

C628

10uF/10V

c0805

C157

10uF/10V

C123

10uF/10V

C98

10uF/10V

c0805

12

C561

10uF/10V

c0805

12

C158

10uF/10V

12

C126

10uF/10V

12

C573

10uF/10V

c0805

12

10uF/10V

c0805

12

10uF/10V

12

10uF/10V

12

+

0.01UF

C176

C180

C124

C623

12

10uF/10V

c0805

12

10uF/10V

12

10uF/10V

12

10uF/10V

c0805

C105

C159

C125

C101

12

10uF/10V

12

10uF/10V

12

10uF/10V

12

10uF/10V

c0805

C179

C572

C110

C160

4

5

4

3

2

1

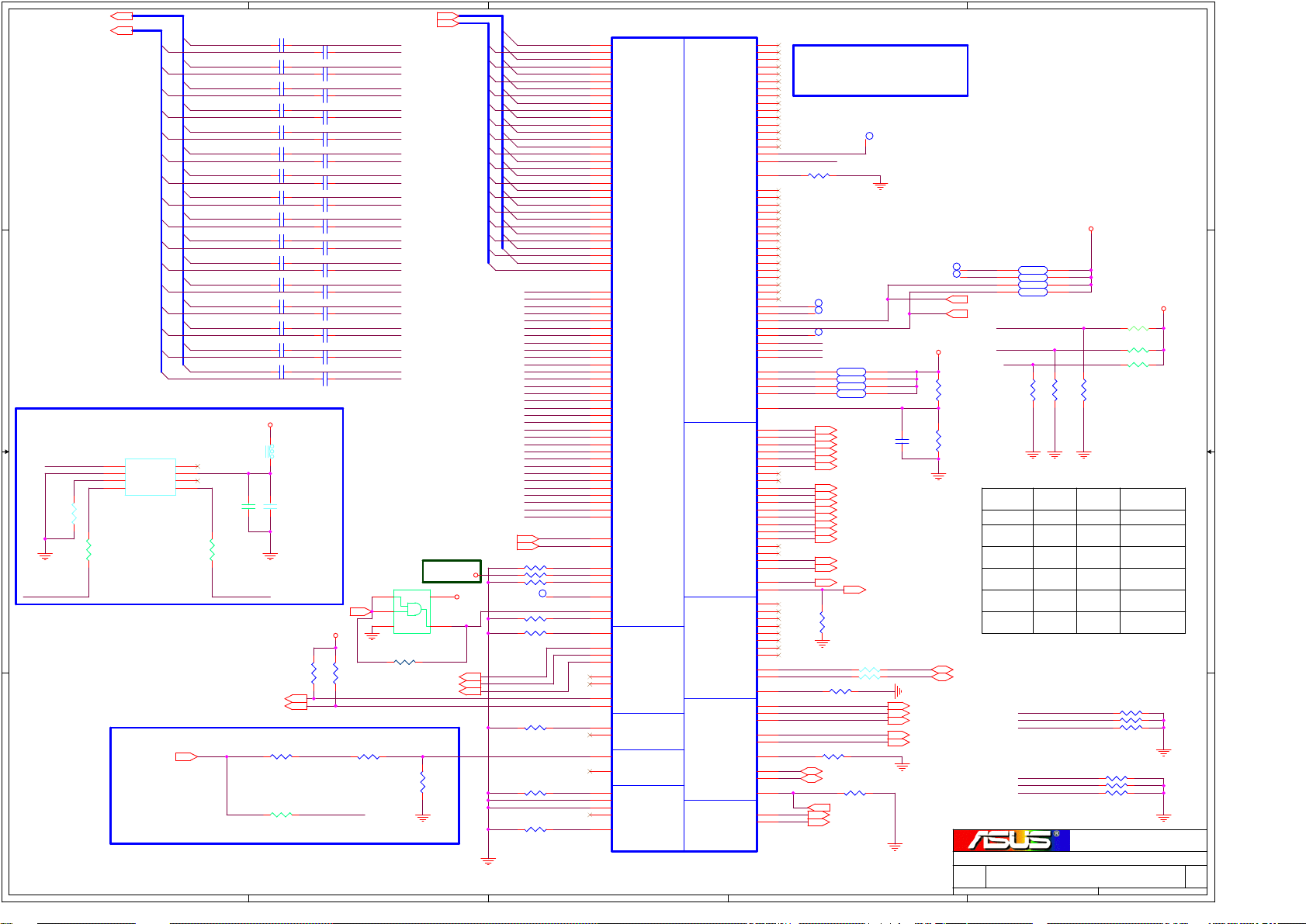

Fan Speed Control

Using a OP AMP and

fine-tuning the level,

D D

SW: FAN_PWM mus

be low dur

C C

ing S3

CPU FAN will be forced on:

1) Thermal Sensor

Over-temperture

2) PROCHOT asserted(CPU)

3) WATCHDOG asserted(KBC)

t

FAN_PWM

R734

300KOhm

1 2

C878

10UF/6.3V

+5VS_FAN

12

GND

we can improve the fan

speed accuracy.

c0402

C246

GND

1 2

A+

3

A-

2

B+

5

B-

6

LM3

WATCHDOG

27

+

-

+

-

U12

58MX

1000PF

+12

V

8

VCC

1

AO

BO

7

4

GND

R134

GND

OS#_OC

12

GND

R155

10KOhm

r0402

1 2

+3V

56

32

3

D

1

1

G

S

2

GND

S

RN21C

10KOhm

+5V

GND

330Ohm

5

Q14

2N7002

S

12

C265

0.1UF

c0402

+3V

M0602

GND

12

+

CE29

47UF/6.3V

+5VS_FAN

GND

+3V

S

12

R735

10KOhm

r0402

D56

1N4148W-A2

1 2

CPU

+5V

S

12

R813

10KOhm

r0402

M0601

FAN

FANSP1

+3V

GND

S

78

12

RN21D

10KOhm

C686

100PF

c0402

Q22

AP3310H

D

S

2

3

G

1

S

34

RN21B

10KOhm

61

Q95A

UM6K1N

2

34

Q95B

UM6K1N

GNDGND

When fan speed is

very slow, after RC

integrator the level

of FANSP1 will be

very low that may

make south bridge do

the wrong detection.

+5VS_FAN

12

C842

0.1UF

/

GND

GND

1

2

3

HOLD1

HOLD2

GND

45

CON14

WTOB_CON_3P

GND

+3V

T_S

C880

0.1UF

c0402

ADT_VGA_P

S

U63

1

SDA

2

SCL

3

GND

4

VCC

12

WM

5

VID0

6

VID1

7

VID2

8

VID3

9

TACH3

10

PWM2/SMBALERT#

11

TACH1

TACH4/ADDRESS_SELECT/THERM#

12 13

TACH2

NTD. 20.64

SMBus Address: 0x2E

GND

PWM1/XTO

Vccp

2.5V/SMBALERT#

12V/VID5

5V/THERM#

VID4

D1+

D2+

PWM3/ADDRESS_ENABLE#

0418

ADT7463

+VCORE

24

23

22

21

20

19

18

17

D1-

16

15

D2-

14

GND

B B

T_S

1 2

R0603

SMB_DA

SMB_CLK_S

0Ohm

tput

SMB_DA

18,21,22,23

SMB_CLK_S

18,21,22,23

FAN_PWM

R739

FANSP1

Pin

10 & Pin 24 set inverting PWM Mode

Set INV=1 to invert PWM ou

A A

Modified Fan Control Circuit

Change MAX6657*2 -> ADT7463

5

4

ADT_D1+

ADT_D2+

ADT_CPU_PWM#

ADT_SMBALE

ADT_THERM#

ADT_D1-

ADT_D2-

ADD_SEL_EN#

3

C879

1000P

C0603

C881

1000P

C0603

R736

RT#

R737

R738

12

12

1 2

R0603

1 2

R0603

1 2

R0603

RN21A

10KOhm

0Ohm

0Ohm

0Ohm

12

Pin 13

1

X 5C **

0 1 5A

0

0 58

FAN_PWM

PM_THERM#13,18

OS#_OC

42

+3

VS

CPU_THRM_DA

CPU_THRM_DC

VGA_THRM_DA

VGA_THRM_DC 12

H_PROCHOT_S#

3

3

12

3

Pin 14 SMB Addr

2

Route H_THERMDA and H_THERMDC

on the same layer

----------------- 12 mils

===============GND

10 mils

=========H_THERMDA(10 mils)

10 mils

=========H_THERMDC(10 mils)

10 mils

=========GND

12 mils

----------------

OTHER SIGNALS

-----OTHER SIGNALS

Avoid BPSB,Power

Title :

Size

Project Name

Custom

Tuesday, August 02, 2005

Date:

A3V

Engineer:

TH

Sheet

1

ERMAL SERSOR,FAN

Miller Liu

Rev

5

1.1

55

of

5

H_XRCOMP

R57

24.9Ohm

1%

D D

C C

B B

A A

1 2

GND

+VCCP

R51

54.9Ohm

1%

1 2

+VCCP

R52

221Ohm

1%

r0402

1 2

R59

100Ohm

1%

r0402

1 2

GND

R86

24.9Ohm

1%

1 2

GND

+VCCP

R68

54.9Ohm

1%

1 2

+VCCP

R77

221Ohm

1%

r0402

1 2

R76

100Ohm

1%

r0402

1 2

GND GND GND

12

GND

12

H_XSCOMP

H_XSWING

C94

0.1UF

c0402

H_YRCOMP

H_YSCOMP

H_YSWING

C163

0.1UF

c0402

GND

12

10uF/10V

12

C152

10uF/10V

c0805

C93

c0805

/

/

4

H_D#[0..63]

3

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

3

U6D

E4

HD0#

E1

HD1#

F4

HD2#

H7

HD3#

E2

HD4#

F1

HD5#

E3

HD6#

D3

HD7#

K7

HD8#

F2

HD9#

J7

HD10#

J8

HD11#

H6

HD12#

F3

HD13#

K8

HD14#

H5

HD15#

H1

HD16#

H2

HD17#

K5

HD18#

K6

HD19#

J4

HD20#

G3

HD21#

H3

HD22#

J1

HD23#

L5

HD24#

K4

HD25#

J5

HD26#

P7

HD27#

L7

HD28#

J3

HD29#

P5

HD30#

L3

HD31#

U7

HD32#

V6

HD33#

R6

HD34#

R5

HD35#

P3

HD36#

T8

HD37#

R7

HD38#

R8

HD39#

U8

HD40#

R4

HD41#

T4

HD42#

T5

HD43#

R1

HD44#

T3

HD45#

V8

HD46#

U6

HD47#

W6

HD48#

U3

HD49#

V5

HD50#

W8

HD51#

W7

HD52#

U2

HD53#

U1

HD54#

Y5

HD55#

Y2

HD56#

V4

HD57#

Y7

HD58#

W1

HD59#

W3

HD60#

Y3

HD61#

Y6

HD62#

W2

HD63#

C1

HXRCOMP

C2

HXSCOMP

D1

HXSWING

T1

HYRCOMP

L1

HYSCOMP

P1

HYSWING

ALVISO_BGA1257

HADSTB0#

HADSTB1#

HBREQ0#

HCPURST#

HCLKINN

HOST

HCLKINP

HDEFER#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDPWR#

HDRDY#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HEDRDY#

HPCREQ#

HCPUSLP#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HVREF

HBNR#

HBPR#

HDBSY#

HHIT#

HHITM#

HLOCK#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HTRDY#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BREQ#0

H_CPURST#

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

TP_H_EDRDY#

TP_H_PCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

R490

r0402

1 2

2

TPC28t

0Ohm

H_ADS#

3

H_ADSTB#0

3

H_ADSTB#1

3

H_BNR#

3

H_BPRI#

3

H_BR0#

3

H_CPURST#

CLK_MCH_BCLK#

CLK_MCH_BCLK

H_DBSY#

3

H_DEFER#

3

H_DINV#0

3

H_DINV#1

3

H_DINV#2

3

H_DINV#3

3

H_DPWR#

3

H_DRDY#

3

H_DSTBN#0

3

H_DSTBN#1

3

H_DSTBN#2

3

H_DSTBN#3

3

H_DSTBP#0

3

H_DSTBP#1

3

H_DSTBP#2

3

H_DSTBP#3

3

H_HIT#

3

H_HITM#

3

T2

4

1

3

TPC28t

H_A#[31..3]

21

21

1

H_LOCK#

H_REQ#[4..0]

H_RS#[0..2]

H_CPUSLP#

H_TRDY#

T223

1

3

+VCCP

R498

100Ohm

1%

r0402

H_VREF

3

3

3

3,18

3

1 2

1 2

R497

200Ohm

r0402

1%

12

C585

0.1UF

c0402

GNDGND

Alviso MCH(1

Title :

Size

Project Name

Custom

5

4

3

2

Date:

A3V

Tuesday, August 02, 2005

Engineer:

Sheet

1

Miller Liu

6

)

Rev

1.1

55

of

5

DMI_TXN[0..3]

19

DMI_TXP[0..3]

19

D D

DMI_RXN[0..3]

19

DMI_RXP[0..3]

19

M_CLK_DDR0

23

M_CLK_DDR1

23

M_CLK_DDR3

22

M_CLK_DDR4

22

M_CLK_DDR#0

23

M_CLK_DDR#1

23

M_CLK_DDR#3

22

M_CLK_DDR#4

22

M_CKE[0..3]

22,23,24

C C

M_CS#[0..3]

22,23,24

M_ODT[0..3]

22,23,24

M_VREF_MCH

B B

12

C201

1UF/10V

GND GND

A A

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_

DMI_

DMI_

DMI_

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

TP_SM

TP_SM

TP_SMCK

TP_SMCK

M_CKE0

M_CKE1

M_CKE2

M_CKE3

M_CS#0

M_CS#1

M_CS#2

M_CS#3

M_OCDCOMP0

M_OCDCOMP1

M_ODT

M_ODT

M_ODT

M_ODT

M_RCOMPN

M_RCOMPP

SMXSL

SMYSLEW

M_VREF_MCH

12

C203

0.1UF

c0402

EW

TXP0

TXP1

TXP2

TXP3

CK2

CK5

0

1

2

3

AA31

AB35

AC31

AD35

Y31

AA35

AB31

AC35

AA33

AB37

AC33

AD37

Y33

AA37

AB33

AC37

AM33

AL1

AE11

AJ34

AF6

AC10

AN33

AK1

#2

AE10

AJ33

AF5

#5

AD10

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

AF22

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

U6A

DMIRXN0

DMIRXN1

DMIRXN2

DMIRXN3

DMIRXP0

DMIRXP1

DMIRXP2

DMIRXP3

DMITXN0

DMITXN1

DMITXN2

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK2

SM_CK3

SM_CK4

SM_CK5

SM_CK0#

SM_CK1#

SM_CK2#

SM_CK3#

SM_CK4#

SM_CK5#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

ALVISO_BGA1257

+2.5VS

R472

R473

+1.8V

GND

DMIDDR MUXING

PM

DREF_CLKN

CLK

DREF_SSCLKN

DREF_SSCLKP

NC

r0402

1 2

r0402

1 2

R520

1 2

R517

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

DREF_CLKP

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

10KOhm

10KOhm

12

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

80.6Ohm

80.6Ohm

PM_

PM_

R471

TPC28t

TPC28t

CFG5

CFG6

CFG7

CFG8

CFG9

TPC28t

TPC28t

TPC28t

TPC28t

TPC28t

TPC28t

CFG16

TPC28t

CFG18

CFG19

TPC28t

TPC28t

TPC28t

TPC28t

TPC28t

TPC28t

TPC28t

PM_

PM_

1 2

GND

EXTTS#0

EXTTS#1

M_RCOMPN

M_RCOMPP

4

r0402

1 2

T221

1

T225

1

T215

1

T216

1

T220

1

T224

1

T212

1

T229

1

T227

1

T218

1

T226

1

T228

1

T2

1

T2

1

T219

1

T213

1

EXTTS#0

EXTTS#1

r0603

R741

R742

33KOhm

R0603

1KOhm

+2.5VS

MCH_SEL1

21

MCH_SEL0

21

CFG5

11

CFG6

11

CFG7

11

CFG8

11

CFG9

11

CFG16

11

CFG18

11

CFG19

11

6

5

12

C581

0.1UF

c0402

12

10KOhm

GND

PM_BMBUSY#

PM_THRMTRIP#

PLT_

DREFCLK#

DREFCLK

R512

40.2Ohm

1%

1 2

/

GND

+2.5VS

18

3,18

RST#

12,17,18,19,27,28,38,40

21

21

M_OCDCOMP0

M_OCDCOMP1

R511

40.2Ohm

1%

1 2

/

GND

D78

1 2

1 2

1N4148W-A2

Before the C1 step, R53,R54 unmount

CLK_MCH_3GPLL#

21

CLK_MCH_3GPLL

21

R740

10KOhm

r0402

Layout Note:

Route as short

as possible.

+VCCP

MCH_PWROK

GND

43,44

M0417

3

U6F

GND

AB29

AC29

H24

H25

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

SDVOCTRL_DATA

SDVOCTRL_CLK

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

ALVISO_BGA1257

T232

1

T230

1

T236

1

T231

1

TPC28t

TPC28t

TPC28t

TPC28t

EXP_ICOMPO

MISCTVVGALVDS

PCI-EXPRESS GRAPHICS

TP_SM

TP_SM

TP_SMCK

TP_SMCK

EXP_COMPI

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

CK2

CK5

#2

#5

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

2

R477

PCIENB_RXN0

PCIENB_RXN1

PCIENB_RXN2

PCIENB_RXN3

PCIENB_RXN4

PCIENB_RXN5

PCIENB_RXN6

PCIENB_RXN7

PCIENB_RXN8

PCIENB_RXN9

PCIENB_RXN10

PCIENB_RXN11

PCIENB_RXN12

PCIENB_RXN13

PCIENB_RXN14

PCIENB_RXN15

PCIENB_RXP0

PCIENB_RXP1

PCIENB_RXP2

PCIENB_RXP3

PCIENB_RXP4

PCIENB_RXP5

PCIENB_RXP6

PCIENB_RXP7

PCIENB_RXP8

PCIENB_RXP9

PCIENB_RXP10

PCIENB_RXP11

PCIENB_RXP12

PCIENB_RXP13

PCIENB_RXP14

PCIENB_RXP15

PCIENB_TXN0

PCIENB_TXN1

PCIENB_TXN2

PCIENB_TXN3

PCIENB_TXN4

PCIENB_TXN5

PCIENB_TXN6

PCIENB_TXN7

PCIENB_TXN8

PCIENB_TXN9

PCIENB_TXN10

PCIENB_TXN11

PCIENB_TXN12

PCIENB_TXN13

PCIENB_TXN14

PCIENB_TXN15

PCIENB_TXP0

PCIENB_TXP1

PCIENB_TXP2

PCIENB_TXP3

PCIENB_TXP4

PCIENB_TXP5

PCIENB_TXP6

PCIENB_TXP7

PCIENB_TXP8

PCIENB_TXP9

PCIENB_TXP10

PCIENB_TXP11

PCIENB_TXP12

PCIENB_TXP13

PCIENB_TXP14

PCIENB_TXP15

1 2

+1.5VS_PCIE

24.9Ohm

PCIENB_RXN[0..15]

PCIENB_RXP[0..15]

PCIENB_TXN0

PCIENB_TXP0

PCIENB_TXN1

PCIENB_TXP1

PCIENB_TXN2

PCIENB_TXP2

PCIENB_TXN3

PCIENB_TXP3

PCIENB_TXN4

PCIENB_TXP4

PCIENB_TXN5

PCIENB_TXP5

PCIENB_TXN6

PCIENB_TXP6

PCIENB_TXN7

PCIENB_TXP7

PCIENB_TXN8

PCIENB_TXP8

PCIENB_TXN9

PCIENB_TXP9

PCIENB_TXN10

PCIENB_TXP10

PCIENB_TXN11

PCIENB_TXP11

PCIENB_TXN12

PCIENB_TXP12

PCIENB_TXN13

PCIENB_TXP13

PCIENB_TXN14

PCIENB_TXP14

PCIENB_TXN15

PCIENB_TXP15

C559

C107

C563

C118

C571

C138

C580

C153

C590

C167

C600

C173

C611

C186

C625

C196

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

0.1UF

1

12

12

C558

C99

C560

C113

C565

C130

C575

C144

C588

C156

C595

C169

C607

C175

C618

C192

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PCIEG_RXN0

PCIEG_RXP0

0.1UF

PCIEG_RXN1

PCIEG_RXP1

0.1UF

PCIEG_RXN2

PCIEG_RXP2

0.1UF

PCIEG_RXN3

PCIEG_RXP3

0.1UF

PCIEG_RXN4

PCIEG_RXP4

0.1UF

PCIEG_RXN5

PCIEG_RXP5

0.1UF

PCIEG_RXN6

PCIEG_RXP6

0.1UF

PCIEG_RXN7

PCIEG_RXP7

0.1UF

PCIEG_RXN8

PCIEG_RXP8

0.1UF

PCIEG_RXN9

PCIEG_RXP9

0.1UF

PCIEG_RXN10

PCIEG_RXP10

0.1UF

PCIEG_RXN11

PCIEG_RXP11

0.1UF

PCIEG_RXN12

PCIEG_RXP12

0.1UF

PCIEG_RXN13

PCIEG_RXP13

0.1UF

PCIEG_RXN14

PCIEG_RXP14

0.1UF

PCIEG_RXN15

PCIEG_RXP15

0.1UF

PCIEG_RXN[0..15]

PCIEG_RXP[0..15]

12

12

Alviso

Sheet

PCIE(2)

Miller Liu

7

Rev

1.1

55

of

Title :

Size

Project Name

Custom

5

4

3

2

Date:

A3V

Tuesday, August 02, 2005

Engineer:

1

5

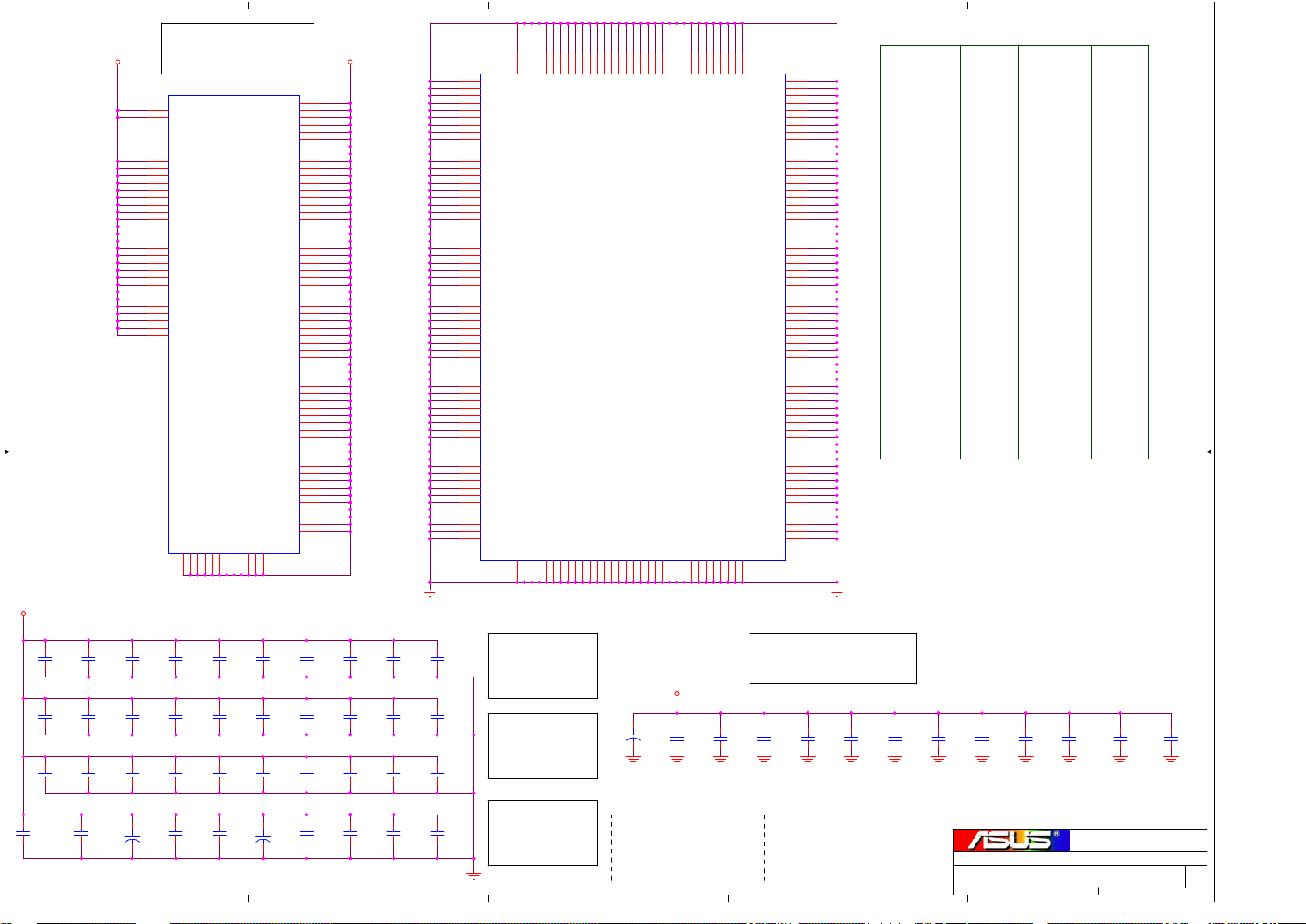

M_A_DQ[0..63]

23

D D

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AP11

AP10

AM7

AN5

AN6

AN3

AM6

AM3

AG2

AG1

AM2

AH3

AG3

AD6

AC4

AD4

AD5

AL9

AL6

AP7

AL7

AP3

AP6

AL4

AK2

AK3

AL3

AF3

AE3

AF2

AF1

U6B

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO_BGA1257

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

DDR SYSTEM MEMORY A

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

4

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_

M_A_

M_A_

M_A_

M_A_

M_A_

M_A_

M_A_

M_A_

M_A_

M_A_A

M_A_A

M_A_A

M_A_A

TPC28t

TPC28t

3

M_B_DQ[0..63]

M_A_B

S#0

23,24

M_A_B

S#1

23,24

M_A_B

S#2

23,24

M_A_DM[0..7]

M_A_DQS[0..7]

M_A_DQS#[0..7]

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

10

11

12

13

T234

1

T237

1

M_A_A[0..13]

M_A_CAS#

M_A_RAS#

M_A_WE#23,24

23,24

23,24

23

23

23

23,24

22

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37M_A_DQ38

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AH11

AH10

AG9

AG8

AH8

AK9

AK6

AH5

AK8

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

AJ9

AJ7

AJ4

AJ8

AJ5

U6C

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO_BGA1257

2

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

DDR SYSTEM MEMORY B

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_

A0

M_B_

A1

M_B_

A2

M_B_

A3

M_B_

A4

M_B_

A5

M_B_

A6

M_B_

A7

M_B_

A8

M_B_

A9

M_B_A

10

M_B_A

11

M_B_A

12

M_B_A

13

TPC28t

TPC28t

1

M_B_B

S#0

22,24

M_B_B

S#1

22,24

M_B_B

S#2

22,24

M_B_DM[0..7]

M_B_DQS[0..7]

M_B_DQS#[0..7]

M_B_A[0..13]

M_B_CAS#

T233

1

T235

1

M_B_RAS#

M_B_WE#22,24

22,24

22,24

22

22

22

22,24

A A

Alviso DDR2 SLOT (

Title :

Size

Project Name

Custom

5

4

3

2

Date:

A3V

Tuesday, August 02, 2005

Engineer:

Miller Liu

8

Sheet

1

3)

Rev

1.1

55

of

2.5V/2

mA

+2.5VS

D D

VTT

0.9475V/1.05V

/

12

C70

0.1UF

c0402

C C

GND

12

2.5V/0.

B B

+1.5VS

PCIE-1

1.425V/1.5V/

/ /

L29

80Ohm/100Mhz

+1.5VS

L30

80Ohm/100Mhz

A A

5

12

/1.1025V

/640mA

+VCCP

VCCP_GMCH_CAP1

VCCP_GMCH_CAP2

VCCP_GMCH_CAP3

VCCP_GMCH_CAP4

12

C69

0.1UF

c0402

GNDGND

15mA

+2.5VS

L28

120Ohm/100Mhz

.5V

21

21

/

5

L8

2 1

150Ohm/100Mhz

C71

0.1UF

c0402

12

C109

0.1UF

c0402

GND

C174

0.1UF

c0402

GND

21

1.575V

1500mA

+2.5VS_CRTDAC

12

+

VTT50

VTT51

C72

0.1UF

c0402

1 2

+1.5VS_3GPLL

12

C617

0.1UF

c0402

+1.5VS_PCIE

12

+

CE12

150U/4.0V

/

GND

C74

0.01UF

c0402

VTT49

G37

GND

+1.5VS

VTT48

VSSA_3GBG

GND

GND

VTT47

VCCA_3GBG

F37

12

12

C616

10uF/10V

c0805

12

GND

VTT45

VTT46

VCCA_3GPLL2

Y27

C200

10uF/10V

c0805

C562

0.1UF

c0402

12

C591

0.1UF

c0402

VTT42

VTT43

VTT44

VCCA_3GPLL0

VCCA_3GPLL1

J37

Y29

Y28

12

GND

L94

120Ohm/100Mhz

VTT41

VCC3G6

VTT40

VCC3G5

L37

C579

0.1UF

c0402

Layout N

Route caps withi

Alviso. Route FB withi

Al

viso.

12

C593

10uF/10V

c0805

GND

GND

A6

VTT34

VTT35

VTT36

VTT37

VTT39

VTT38

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

AF18

AE37

W37

U37

R37

N37

21

12

GND

4

ote: VssA_CRTDAC

n 250mil of

n 3" of

12

+

CE25

150U/4.0V

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VCCSM64

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

AE1

B28

A28

A27

AF20

AP19

AF19

GND

12

GND

C665

0.1UF

c0402

4

+

CE27

150U/4.0V

2.5V/6

2.5V/2

R10

P10

N10

M10

K10

J10Y9W9U9R9P9N9M9L9J9N8M8N7M7N6M6N5M5N4M4N3M3N2M2B2V1N1M1G1

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

AC11

AB11

AB10

AB9

AP8

AM1

No

te: All VCCSM pins

shorted internally.

V1.8_DDR_CAP6

V1.8_DDR_CAP4

V1.8_DDR_CAP3

+1.8V

1.5V/25

+1.5VS_DDRDLL

1.5V/4

+1.5VS_MPLL

8mA

mA

L11

K11

W10

V10

U10

T10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

AJ12

AH12

AG12

AF12

AE12

AD11

12

C205

0.1UF

c0402

12

+

DDR2-1.8V(2

1.7V/1.8V

/ /

0mA

5mA

12

+

GND

Route VssA_

from GMCH to decoupl

cap

ground lead and than

connect to the gnd pl

R11

P11

N11

M11

VTT7

VTT8

VTT9

VTT10

VCCSM48

VCCSM49

VCCSM50

VCCSM51

AN12

AM12

AL12

AK12

12

C217

0.1UF

c0402

CE28

150U/4.0V

Slot)

/1.9V

2.4A

CE10

100UF/4V

CRTDAC GND

W11

V11

U11

T11

VTT3

VTT4

VTT5

VTT6

VCCSM44

VCCSM45

VCCSM46

VCCSM47

AG13

AF13

AE13

AP12

12

C233

0.1UF

c0402

GND

12

C632

0.1UF

c0402

+1.8V

GND

120Ohm/100Mhz

12

C187

0.1UF

c0402

GND

K13

J13

K12

VTT0

VTT1

VTT2

VCCSM41

VCCSM42

VCCSM43

AL13

AK13

AJ13

AH13

12

GND

12

+

CE14

150U/4.0V

/

VCCSM40

3

L21

21

ing

ane

E19

G19

H20

VCC_SYNC

VSSA_CRTDAC

VCCA_CRTDAC1

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

AE15

AE14

AP13

AN13

AM13

No

shorted internally.

12

C234

0.1UF

c0402

C627

10uF/10V

c0805

+1.8V

12

+

CE13

150U/4.0V

/

GND

3

+1.5VS_HPLL

1.5V/4

5mA

12

+

CE11

100UF/4V

GND

1.5V/4

12

+

100UF/4V

GND

AC2

AC1

B23

C35

AA1

AA2

F19

VCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCH_MPLL1

VCCH_MPLL0

VCCA_CRTDAC0

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

te: All VCCSM pins

12

12

C211

0.1UF

c0402

GND

GND

+1.5VS_DPLLB

0mA

CE23

GND

V18

T18

K18

K17

VCC45

VCC46

VCC47

VCC48

POWE

VCCSM22

VCCSM23

VCCSM24

VCCSM25

AH25

AG25

AF25

AE25

C220

0.1UF

c0402

12

C195

0.1UF

c0402

12

C556

0.1UF

c0402

U19

K19

W18

VCC42

VCC43

VCC44

VCCSM19

VCCSM20

VCCSM21

AL25

AK25

AJ25

L26

21

120Ohm/100Mhz

L89

21

120Ohm/100Mhz

1.5V/4

0mA

1.5V/15

W20

U20

T20

K20

V19

VCC37

VCC38

VCC39

VCC40

VCC41

R

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

AF26

AE26

AP25

AN25

AM25

V1.8_DDR_CAP5

V1.8_DDR_CAP2

V1.8_DDR_CAP1

+2.5VS

C62

10uF/10V

c0805

0mA

K21

AG26

2

+1.5VS

D53

1

+1.5VS_DPLLA

12

+

CE3

100UF/4V

GND

H27

K26

H26

K25

J25

K24

K23

K22

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

12

12

C554

0.1UF

c0402

GND

120Ohm/100Mhz

12

C63

0.1UF

c0402

GND

R27

P27

N27

M27

L27

K27

J27

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

A21

AM37

AH37

AP29

AD28

AD27

2

2

21

12

V27

VCC18

C599

10uF/10V

c0805

J28

H28

G28

VCC16

VCC17

VCCA_LVDS

A25

A35

BAT54C

D54

1

2

BAT54C

12

C577

10uF/10V

c0805

GND GND

P28

N28

M28

L28

K28

VCC11

VCC12

VCC13

VCC14

VCC15

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

D19

H17

B26

B25

GND

Date:

VCC10

VCCD_TVDAC

L7

GND GND

U27

T27

VCC19

VCC20

VCCHV0

VCCHV1

B22

B21

R476

1KOhm

r0402

1 2

3

Alviso C

Min Typ

VCC 1V 1.05

Min Typ

ICC

+VCCP

3

12

C564

10uF/10V

c0805

M29

K29

J29

V28

U28

T28

R28

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

C18

F18

E18

H18

G18

Size

Project Name

Custom

Tuesday, August 02, 2005

ore

R478

1KOhm

r0402

1 2

12

C604

0.1UF

c0402

T29

R29

N29

VCC0

VCC1

VCC2

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

F17

E17

D18

A3V

U6G

ALVISO_BGA1257

Max

V 1.1V

Max

3.7A

12

C582

0.1UF

c0402

GND

Engineer:

1

+3

VS

12

GND

Title :

Sheet

1

+2.5VS

C592

0.1UF

c0402

Alvis

o POWER (4)

Miller Liu

9

Rev

1.1

55

of

5

D D

AL24

AN24

A26

E26

G26

J26

B27

E27

G27

W27

AA27

AB27

AF27

AG27

AJ27

AL27

AN27

E28

W28

AA28

AB28

AC28

A29

D29

E29

F29

G29

H29

GND

VSS267

VSS266

VSS265

VSS264

VSS263

VSS262

VSS261

VSS129

VSS128

VSS127

VSS126

VSS125

VSS124

VSS123

VSS122

VSS121

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

4

L29

P29

U29

V29

W29

AA29

AD29

AG29

AJ29

AM29

C30

Y30

AA30

AB30

AC30

AE30

AP30

D31

E31

F31

G31

H31

J31

K31

L31

M31

N31

P31

R31

T31

U31

V31

W31

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS84

VSS83

VSS82

VSS81

VSS80

VSS79

VSS78

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS101

VSS100

VSS77

3

AD31

AG31

AL31

A32

C32

Y32

AA32

AB32

AC32

AD32

AJ32

AN32

D33

E33

F33

G33

H33

J33

K33

L33

M33

N33

P33

R33

T33

U33

V33

W33

AD33

AF33

AL33

C34

AA34

VSS76

VSS75

VSS74

VSS73

VSS72

VSS71

VSS70

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

VSS61

VSS60

VSS59

VSS58

VSS57

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

2

AB34

AC34

AD34

AH34

AN34

B35

D35

E35

F35

G35

H35

J35

K35

L35

M35

N35

P35

R35

T35

U35

V35

W35

Y35

AE35

C36

AA36

AB36

AC36

AD36

AE36

AF36

AJ36

AL36

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS29

VSS28

VSS27

VSS26

VSS25

VSS24

VSS23

VSS22

VSS21

VSS20

VSS19

VSS18

VSS17

VSS16

VSS15

VSS14

VSS13

VSS12

VSS11

1

AN36

E37

H37

K37

M37

P37

T37

V37

Y37

AG37

U6H

VSS4

VSS3

VSS2

ALVISO_BGA1257

VSS1

VSS0

VSS9

VSS8

VSS7

VSS6

VSS5

VSS10

VSS

VSSALVDS

VSS271

VSS270

VSS269

VSS268

VSS260

VSS259

VSS258

VSS257

VSS256

VSS255

VSS254

VSS253

VSS252

VSS251

VSS250

VSS249

VSS248

VSS247

VSS246

VSS245

VSS244

VSS243

VSS242

VSS241

VSS240

VSS239

VSS238

VSS237

VSS236

VSS235

VSS234

VSS233

VSS232

VSS231

VSS230

VSS229

VSS228

VSS227

VSS226

VSS225

VSS224

VSS223

VSS222

VSS221

VSS220

VSS219

VSS218

VSS217

VSS216

VSS215

VSS214

VSS213

VSS212

VSS211

VSS210

VSS209

VSS208

VSS207

VSS206

VSS205

VSS204

VSS203

VSS202

VSS201

VSS200

VSS199

VSS198

VSS197

VSS196

VSS195

VSS194

VSS193

VSS192

VSS191

VSS190

VSS189

VSS188

VSS187

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153