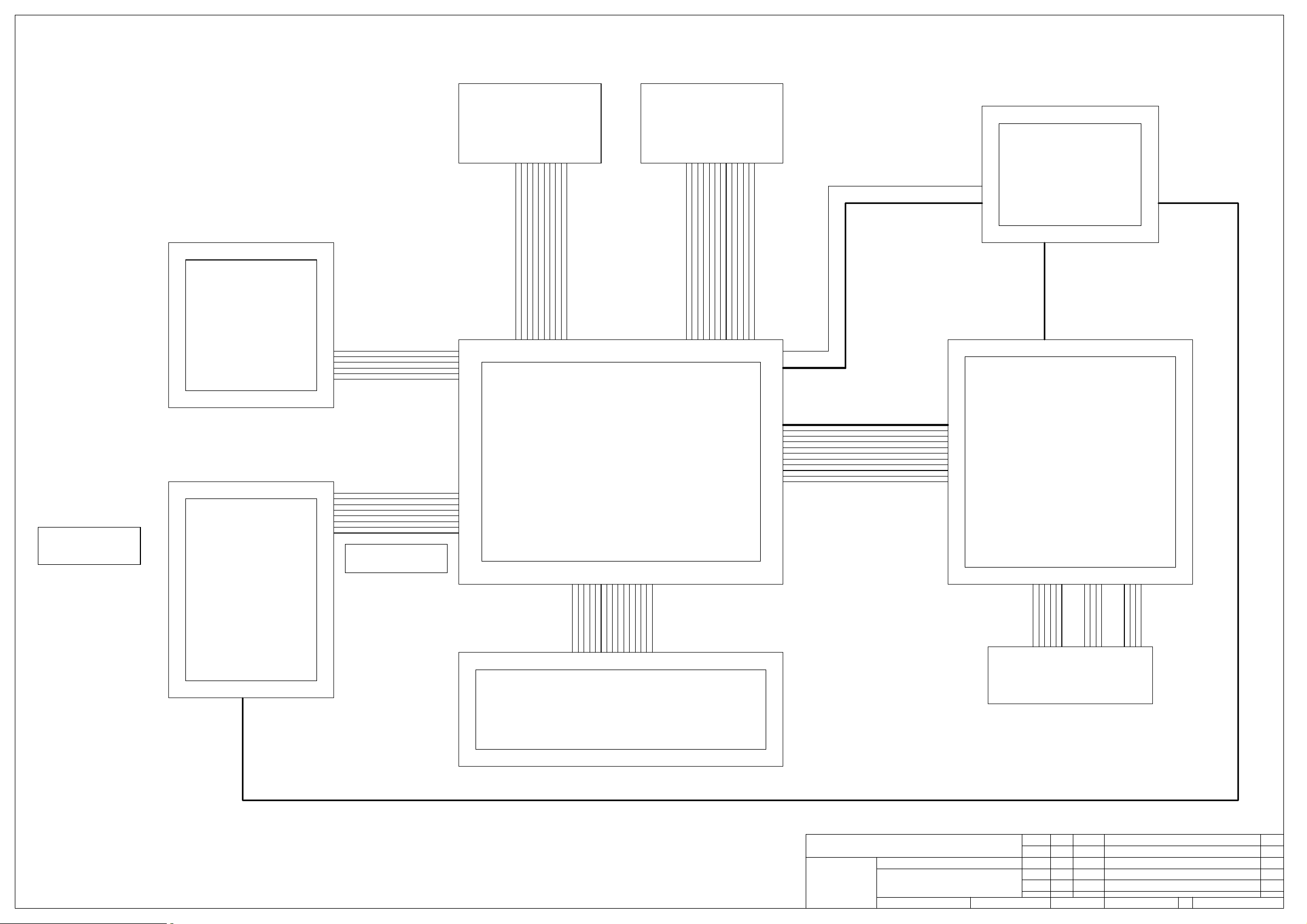

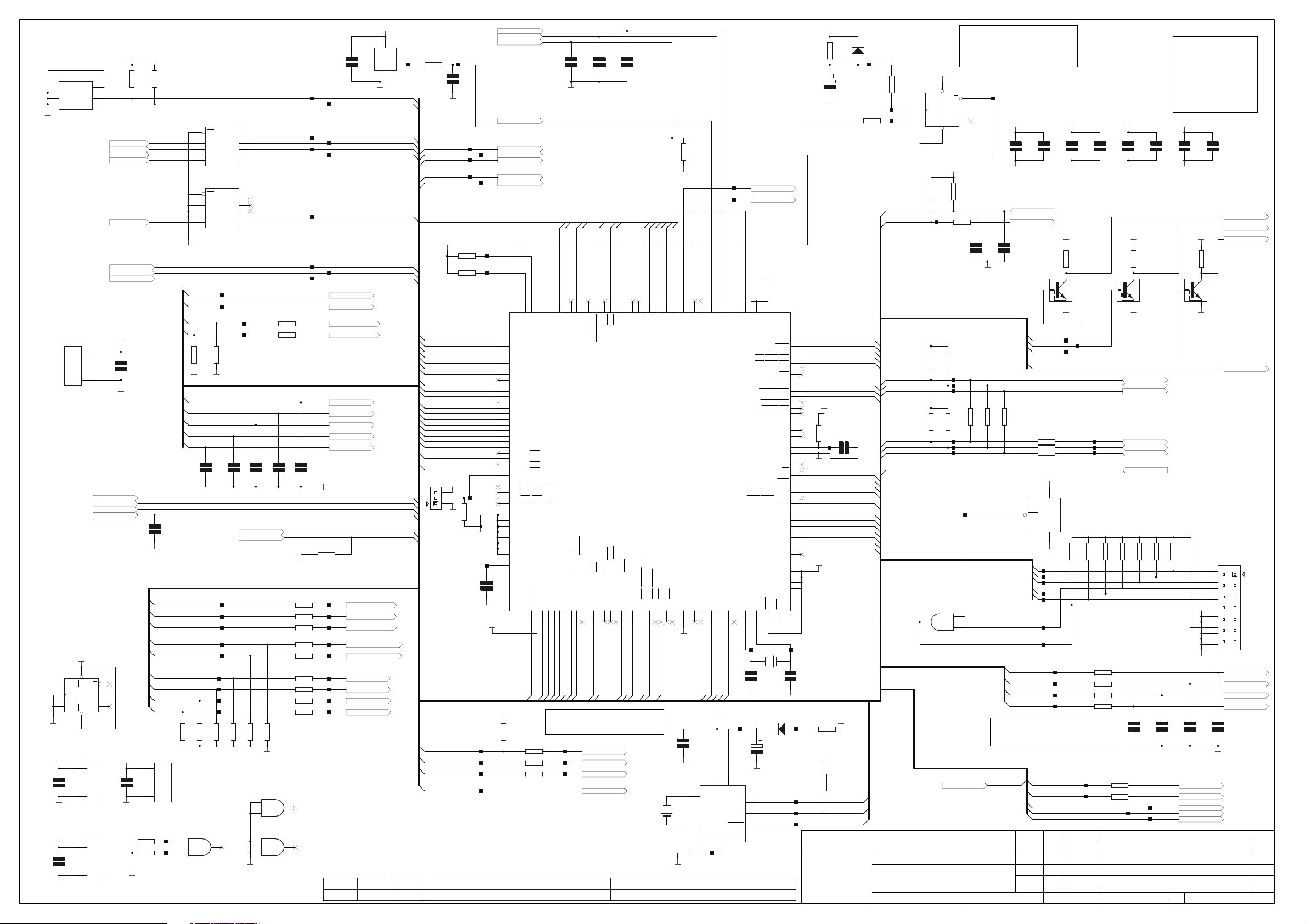

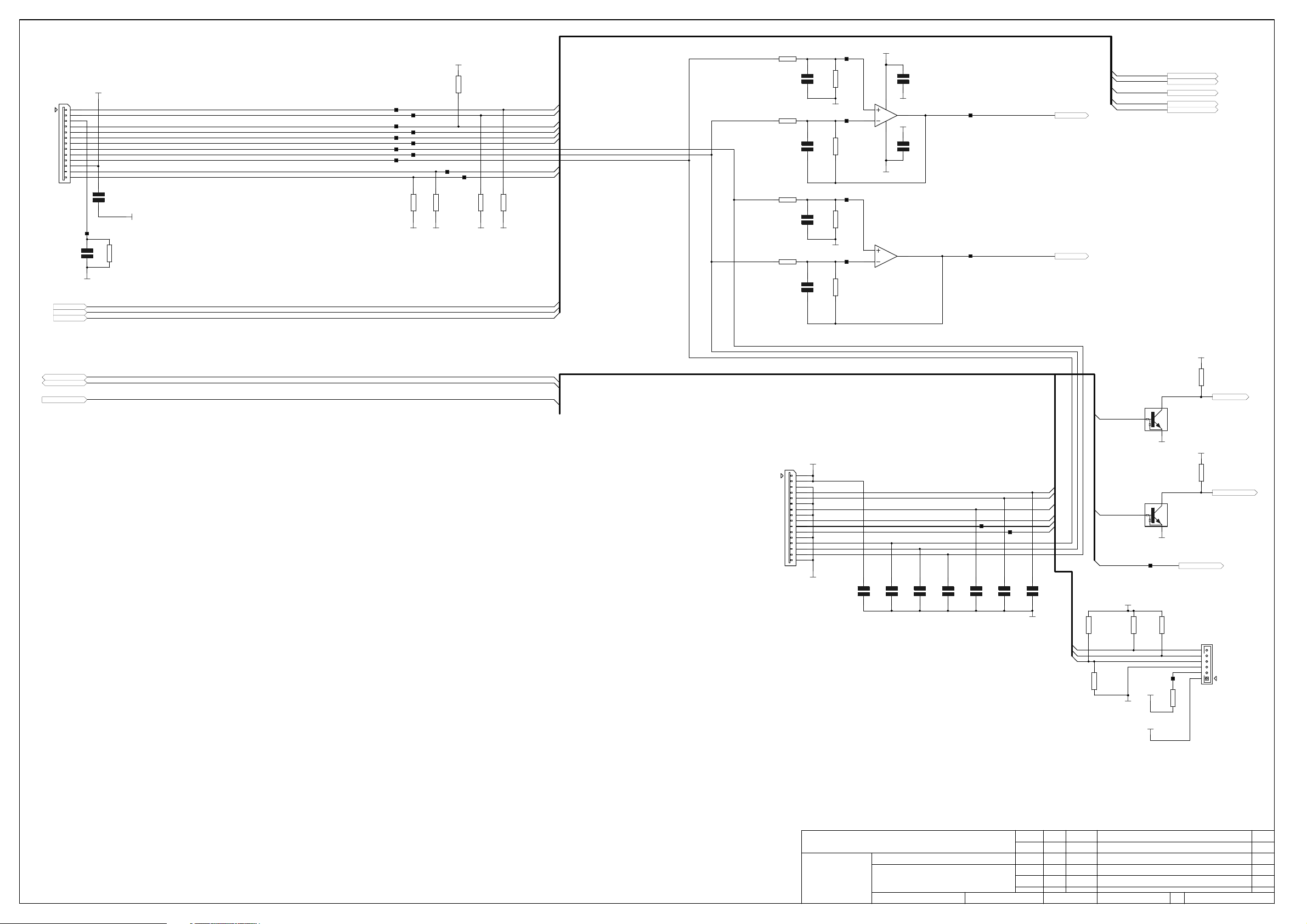

Arcam Solo Movie 5.1 Schematic

Only one module inserted at a time

There is a possiblity that power amp

outputs may have to be connected to the

speaker terminals with flying leads.

Depends on board space available for

heavy tracks.

Front Panel Connections

File Name

# Front input (3.5mm stereo jack)

# Headphone socket (3.5mm

stereo jack)

# Headphone detect switching

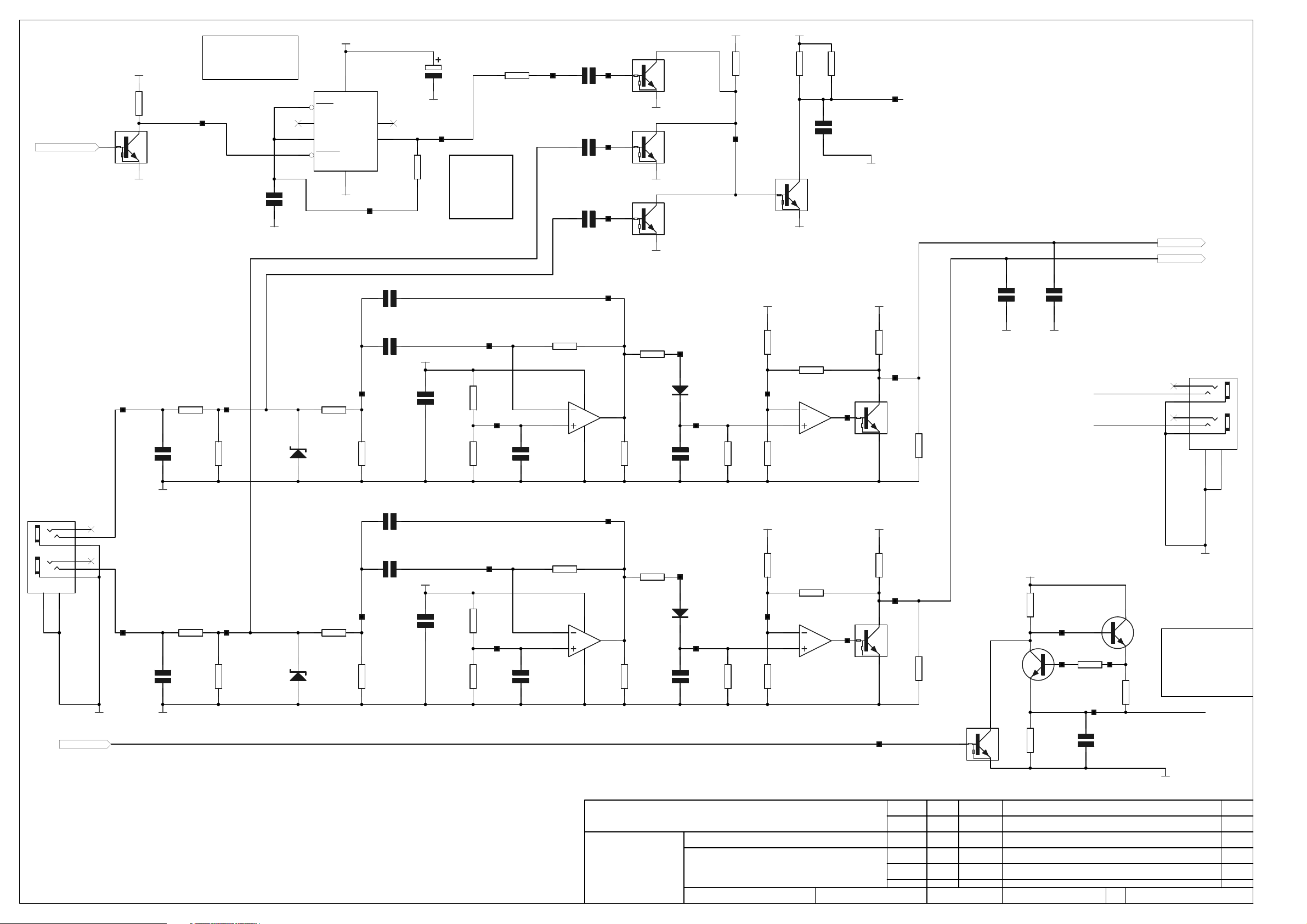

Power Amp Board

File Name

# Power amps

# Power connections from PSU

board

# Power amp muting and status

# Temperature?

FLEXI

LEFT_INPUT

RIGHT_INPUT

GROUND

LEFT_HP

RIGHT_HP

JACK_INSERTED

LEFT

CENTRE

RIGHT

SURROUND_LEFT

SURROUND_RIGHT

TEMPERATURE

MUTE

STATUS

Power amp board and Audio board may

actually be joined together on the same

L-shaped board. To be decided.

DAB/FM Tuner Module

File Name

AM/FM Tuner Module

File Name

FLEXI FLEXI

POWER

0V_D

LEFT_AUDIO

RIGHT_AUDIO

CLOCK

DATA

SPDIF

#RESET

AUDIO_GROUND

MODULE_PRESENT

Audio Board

File Name

# Display and system control uC (H8)

# Analogue inputs (phonos/front/TV scart)

# DACs (5.1 channel) + filtering/diff-single ended

# DACs (2-ch D.mix) + filtering/diff-single ended

# ADC

# Pre-amp chip

# Analogue bass management?

# Analogue outputs (line level - 5.1)

# Analogue record outputs (line level - 2-ch D.mix) for SCART to TV /

record out

# Power connections from PSU board

# Audio connections from: DAB-FM module/AM-FM module/Control uC

(alarm clock)

# Audio connections to: headphone board

# Control lines to/from: Vaddis8/Control uC

# SPDIF TX/RX and clock recovery

# RS232 connection

# IR input and output (back panel)

Mains and Power Board

File Name

# IEC mains inlet

# Voltage selector switch (internal)

# Power on/off rocker switch

# Standby power relay

# Connectors to and from

MAINS_RELAY_CONTROL

POWER_LINES

POWER

0V_D

LEFT_AUDIO

RIGHT_AUDIO

PLL_DO

PLL_CLK

PLL_DI

PLL_CE

AUDIO_GROUND

RDS_DATA

RDS_CLK

STEREO

TUNED

AMP CT

Vaddis8 and Video Board

File Name

transformers

# Secondary regulation circuit (John)

AMP CT

POWER_LINES

MOLEX POWER

POWER_LINES

# Video and Audio DSP

# Drive/servo control

# Video amplifiers and switching

# HDMI I/O

# Video format conversion

# Power connections from PSU board

DIGITAL_AUDIO_CLOCKS

SPDIF_TO_V8

SPDIF_FROM_V8

ADC_DATA

DAC_DATA_0

DAC_DATA_1

DAC_DATA_2

DAC_DATA_3

CHIP_SELECT

COMS_CLK

COMS_DATA

FLEXI

# Header for network connection

EU variant

----------------SCART in (SAT) including stereo audio feed

SCART out (TV) including stereo audio feed to AND

from TV

Phono composite in (GAME)

USA variant

------------------Phono YUV in (SAT)

Phono YUV out (TV)

Phono composite in (SAT and GAME)

Phono composite out (TV)

POWER_LINES

Display Board

File Name

# Dot matrx VFD

# Switch matrix decode

# LED drive

+5V(STBY)

+36V_VAR(D)

VFD_F1

VFD_F2

+3V3(STBY)

IR_EYE

#LED_RED

FLEXI

#LED_BLUE

KEYB0

KEYB1

CPU_AGND

DISPDAT

DISPCLK

DISPLAT

DISPBLK

DVD Drive

File Name

POWER

GROUND

LASER_RF

FOCUS

RF_GROUND

TRACKING

GROUND

EJECT MOTOR

TRAY OPEN

TRAY CLOSED

GROUND

SPINDLE MOTOR

ENDSTOP

SLED MOTOR

FLEXI AMP CT AMP CT

DRAWING TITLE

23425

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

Solo5.1 Architecture

Filename:

_Solo5.1_audio_architecture.sch

Notes:

Contact Engineer:

10/03/05MJT Rough outline of Solo5.1 system

INITIALS

Printed:

DATE

28-Apr-2005

11Sheet of

A2

DRAWING NO.

Contact Tel: (01223) 203210Mark Tweedale

ECO No. DESCRIPTION OF CHANG E

ISSUE

LXXX_X_X

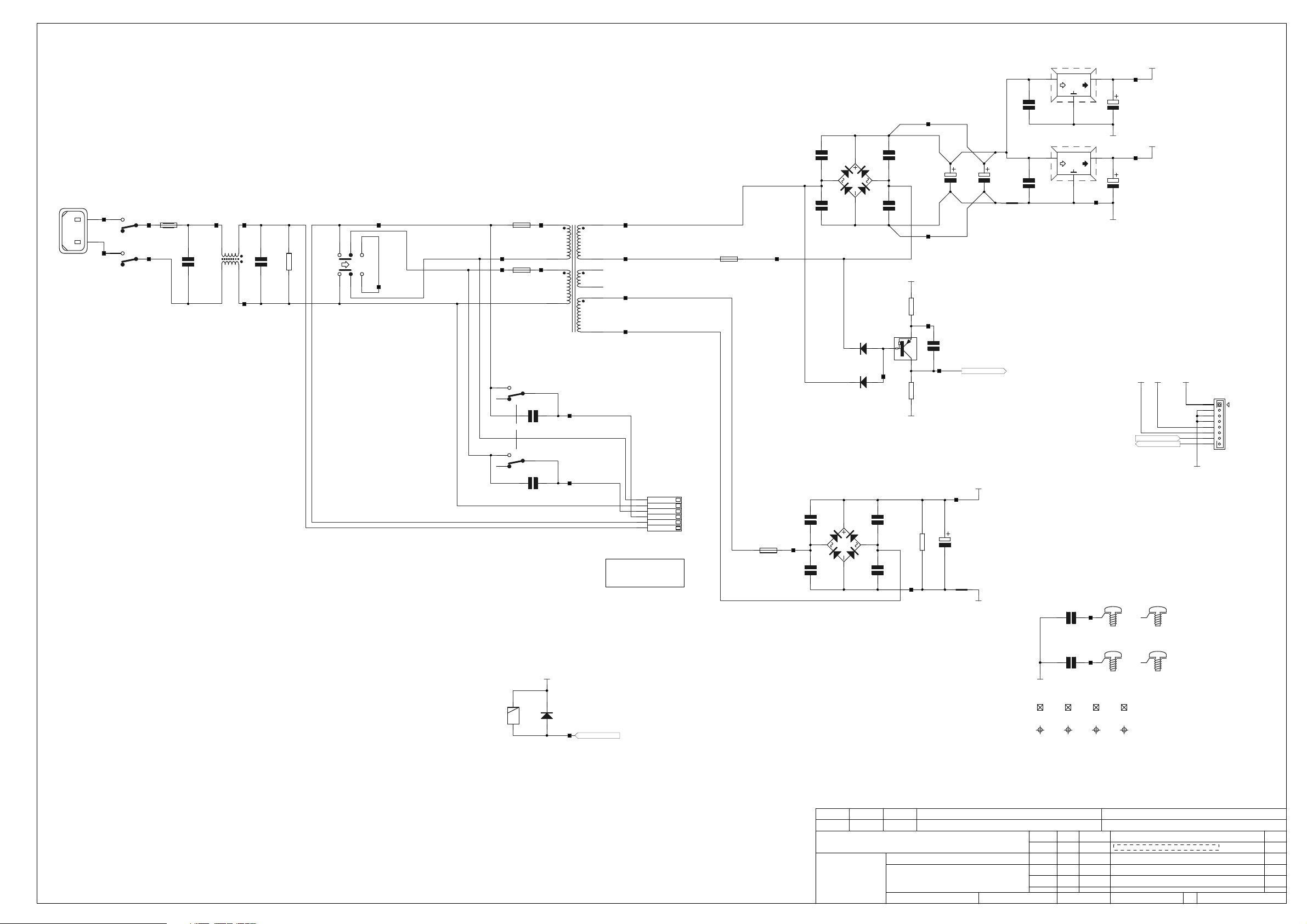

SKT1

Emuden

M1907

Fuse ratings (see parent level in BoM)

230V - T3.15A Fuse (S506 Bussmann)

115V - T6.3A Fuse (S506 Bussmann)

SW1B

SDDJE32100

P1

L

L

SW1A

N

N

SDDJE32100

P11

FS5

T3.15A

S506

P2 P3 P4

FHLD1

20mm HLDR

P12

L_PRE

C1

220N

275V

PP X2

N_PRE

3

4

1

2

L1

1mH

P14

C2

220N

275V

PP X2

R1

1M5

0W5

VR37

L_POST

2A22B

115V 230V

1A11B

N_POST

P30

SW2

18-000-0022

P15

N_115V

L_115V

P16

P17

FS3

T100mA

ETF

FS4

T100mA

ETF

RLY1C

Omron

G2R-24-5VDC

P33

TX1

6

115V

115V

0V

5

P34

4

115V

115V

3

0V

PCB Mount Encapsulated Toroid

RLY1B

G2R-24-5VDC

Omron

C3

P18

3N3

250V

CER

RLY1A

Omron

G2R-24-5VDC

C4

P26

3N3

250V

CER

+5V

D1

1N4148

DO-35

P29

RELAY_SW

P5

13

DIGITAL

P19

15

9

VFD FIL

No longer needed to drive the filament

10

P20

11

VFD HT

P21

12

L_TX2

L_115V_TX2

ferrite clamp around large

transformer primary and

secondary cables

TX2 MAIN TX PRIMARY

CON3

1

DK GREY

2

RED

3

LT GREY

4

GREY

5

BLUE

6

BLUE

WAGO

256 Straight Lever

FS1

1A FF

0.256

R251

FS2

125mA FF

0.00174

R251

P22

P27

C5

100N

100V

X7R

C6

100N

100V

X7R

C13

100N

100V

X7R

C14

100N

100V

X7R

D2

1N4148

DO-35

D3

1N4148

DO-35

DBR1

W02G

DBR2

W02G

TR1

DTA114ESA

SC-72

P23

C7

100N

100V

X7R

C8

100N

100V

X7R

C18

100N

100V

X7R

C15

100N

100V

X7R

+3V3

DGND

P32

R2

0R0

0W25

MF

R3

150K

0W25

MF

P6

P31

P24

R4

100K

0W25

MF

C11

1000UF

35V

YXF

C21

100N

100V

X7R

To Schmitt triggerinput on uC

P25

AC_PRESENT

+40V_UNREG

P28

C9

100UF

100V

YK

SP2

DGND

C12

470UF

25V

YXF

REG1

LM1117T-5.0/NOPB

HS1A

TO-220

6043PB

23C/W

C19

100N

100V

X7R

REG2

LM1117T-3.3

HS2A

TO-220

6043PB

23C/W

C20

100N

100V

X7R

SP1

C22

10N

100V

NPO

C10

10N

DGND

100V

NPO

FD1 FD2 FD3 FD4

TOOL1 TOOL2 TOOL3 TOOL4

+3V3

+5V

DGND

DGND

FIX1

Dia 3.2mm

FIX3

Dia 3.5mm

P9

C16

470UF

25V

YXF

+3V3

P10

C17

1000UF

10V

YXF

+5V +3V3 +40V_UNREG

AC_PRESENT

RELAY_SW

FIX2

1

Dia 3.2mm

FIX4

1

Dia 3.5mm

DGND

CON2

JST

PH

1

2

3

4

5

6

7

8

+5

P7

P8

1

P13

1

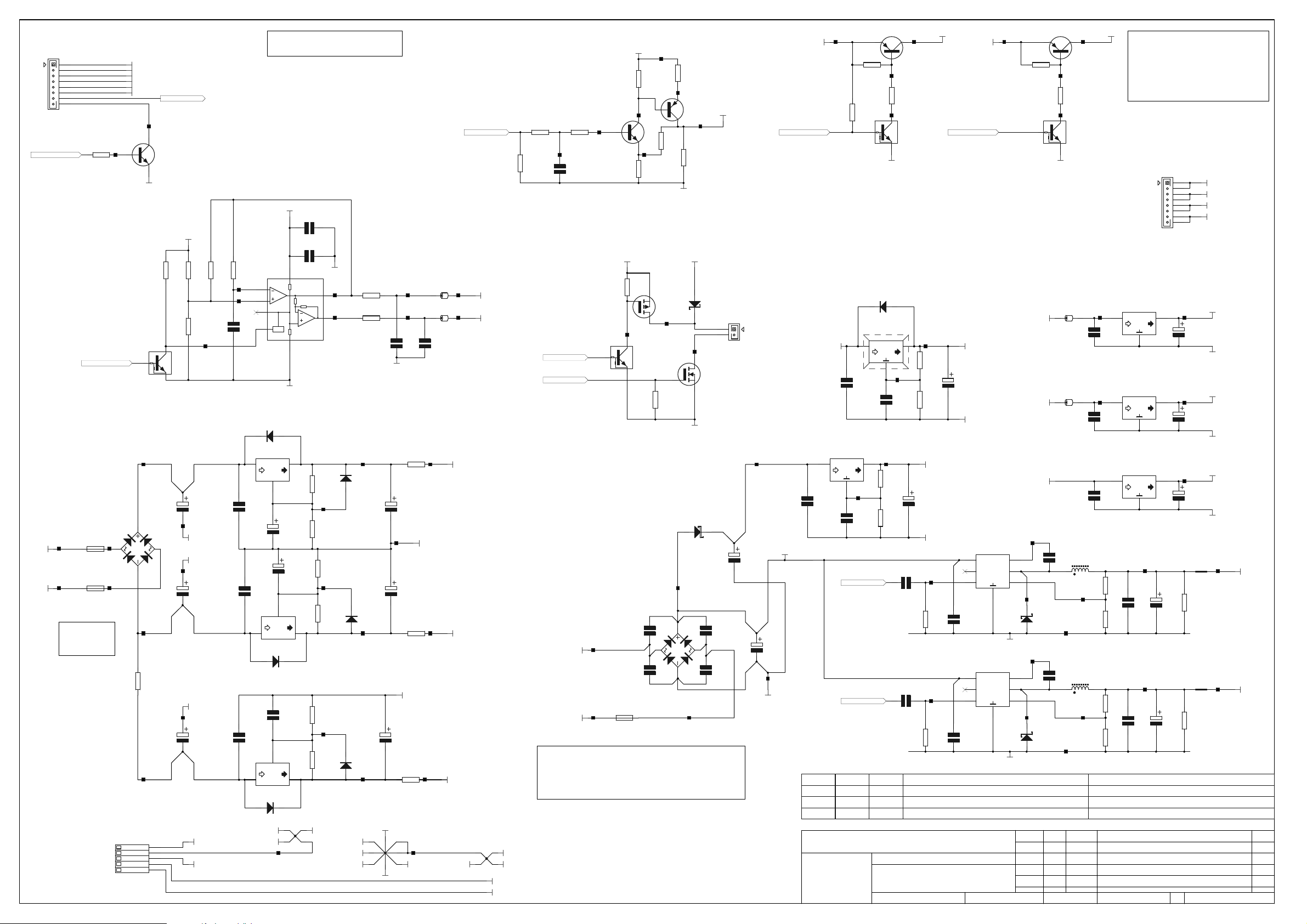

ITEM1 1 Blank PCB Solo5.1 MainsL107PB

ITEM2 1 Pad Damping 15x6x3MM RubberE827AP Fit to top of Relay RLY1

DRAWING TITLE

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB5 9QR

Solo 5.1 Mains PSU

Filename:

L107CT_1.0.sch

Notes:

Contact Engineer:

07_E019 9/02/07 1.0AJD CAPs changed to 105 deg. Safety silk updates for fuses.

06_E177 22/11/06 FS1 & FS2 corrected, C12 changed, added FS5 B.1PK

06_E033

NM

SWB

ECO No. DESCRIPTION OF CHANGE

Contact Tel: (01223) 203200Scott Burr

INITIALS

Printed:

Second prototype, added R4, re-tracked relay,

09/05/06

selector overlay. wago order

First prototype

DATE

13-Feb-2007

1 1Sheet of

A2

DRAWING NO.

B.0

ISSUE

L107CT

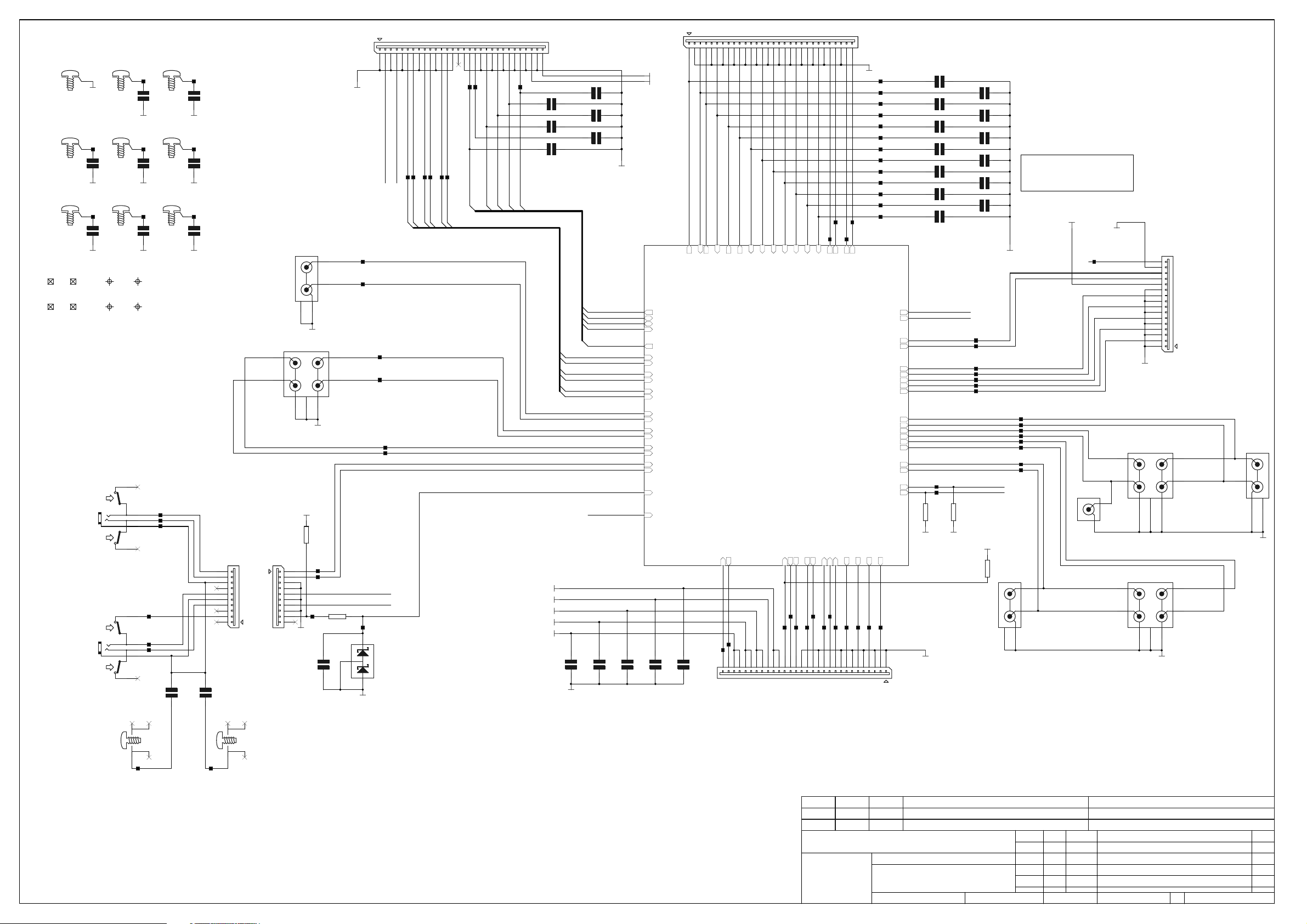

FIX1

Dia 3.5mm

1

FIX2

Dia 3.5mm

1

FIX7

Dia 3.2mm

1

FD1 FD2

FD3 FD4

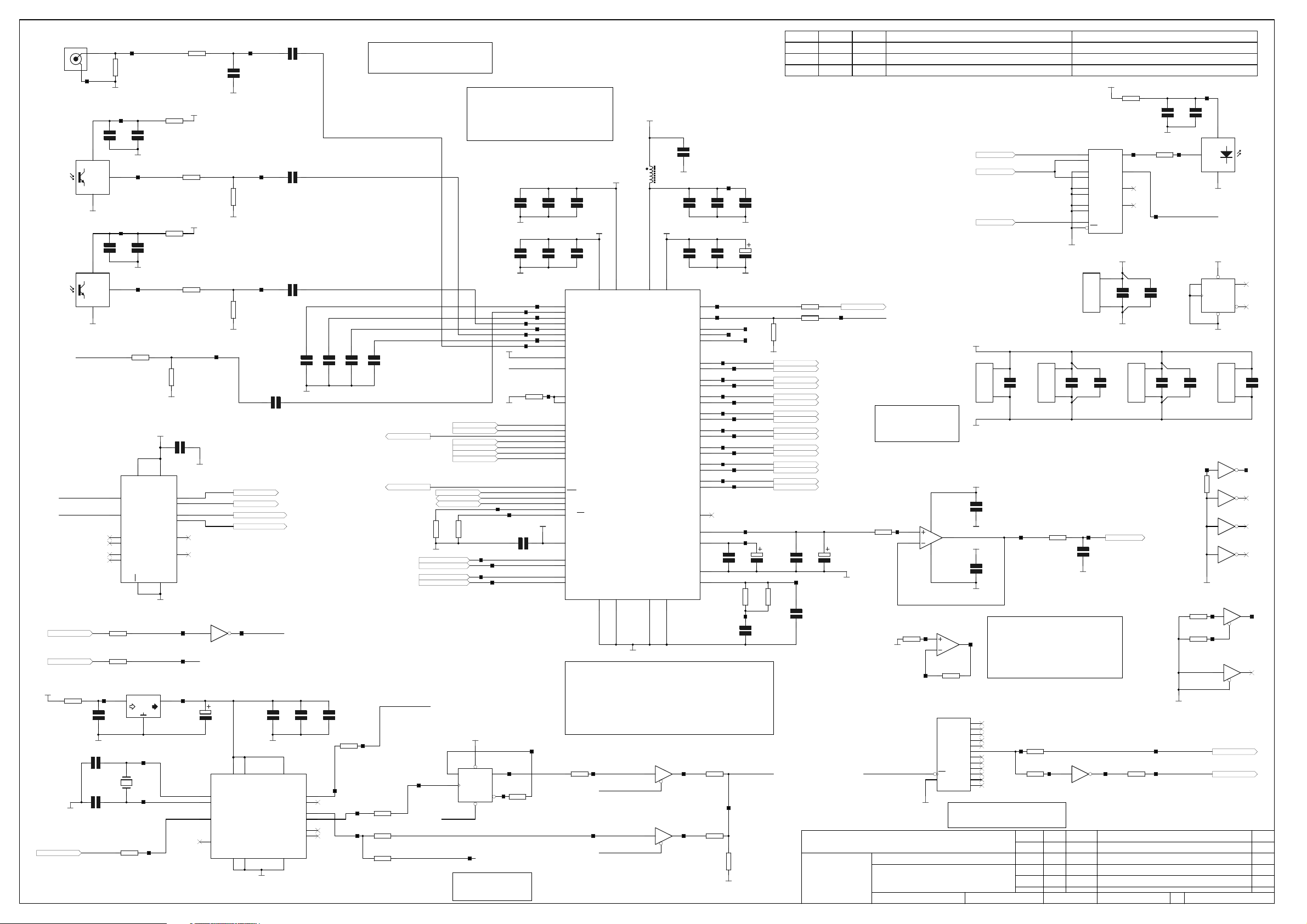

FRONT PANEL

AUX INPUT

FRONT PANEL

HEADPHONE SKT

FIX3

Dia 3.5mm

GND

FIX4

Dia 3.5mm

P2 P3 P14

C33

10N

50V

0603

GND GND GND

FIX8

Dia 3.2mm

P4 P5 P16

C35

10N

50V

0603

GND GND

TOOL1

3mm

TOOL3

3mm

NCL

SKT5

2

L

3

R

1

NCR

CLIFF ELECTRONICS

JY

NCL

SKT6

2

L

3

R

1

NCR

CLIFF ELECTRONICS

JY

NC NC

FIX5

Dia 3.5mm

1

P1 P13

C31

10N

50V

0603

GND GND

FIX6

Dia 3.5mm

1

C34

10N

50V

0603

FIX9

Dia 3.5mm

1

C36

10N

50V

0603

TOOL2

3mm

TOOL4

3mm

NC

P6

P7

P8

NC

P9

P10

P11

NC

4

ITEM1

1

1

2 3

NC

P20

1

1

1

GND

HP_GND

C29

10N

50V

0603

C32

10N

50V

0603

C38

10N

50V

0603

C39

10N

50V

0603

C30

10N

50V

0603

P15

CON5

10

9

8

7

6

5

4

3

2

1

MOLEX

52044

NC NC

4

1

NC

NC

NC

ITEM2

1

2 3

NC

TV_IN_L

TV_IN_R

NC

SKT2

KYOYAKU GOLD

+3V3(STBY)

CON6

1

2

3

4

5

6

7

8

9

10

MOLEX

52045

GND

SKT1

KUNMING

GOLD

SCRN

GND

SCRN

C23

100N

16V

0603

CON1

MOLEX

52806

123456789

GND

P32

SAT_IN_L

P33

SAT_IN_R

AUX_IN_L

Now labelled AV on the back panel

AUX_IN_R

GND

P34

P35

FRONT_IN_L

FRONT_IN_R

Now labelled AUX input

R1

100K

0603

P17

P18

HP_OUT_L

HP_OUT_R

P38

D1

BAT54S

SOT-23

GND

P19

R2

220K

0603

1mm FFC - Molex / 52806-3010 or JST / 30FMN-BTRK

101112131415161718192021222324252627282930

NC

P21

P22

TVSCART_IN_R

SATSCART_IN_R

SATSCART_IN_L

TVSCART_IN_L

AUXSCART_IN_R

AUXSCART_IN_L

FIXED_VOL_L_MU

FIXED_VOL_R_MU

P26

P28

P29

P30

P31

VADDIS_PROG

P36

P37

P27

Fo (-3dB) = 7.23Hz

CON2

MOLEX

C26

1N0

50V

0603

52806

+12V(D)

-5V(VID)

CODEC_INT

I2C_SDA

I2C_SCLK

I2C_RES*

VADDIS_PROG

AUXSCART_IN_L

AUXSCART_IN_R

TVSCART_IN_L

TVSCART_IN_R

SATSCART_IN_L

SATSCART_IN_R

SAT_IN_L

SAT_IN_R

AUX_IN_L

AUX_IN_R

TV_IN_L

TV_IN_R

FRONT_IN_L

FRONT_IN_R

HD_PHONE

HS_TEMP

C27

1N0

50V

0603

To L104AY (Video Board)

P42

47P

C1

50V 0603

47P

C2

50V 0603

47P

C3

50V 0603

I2C_SCLK

I2C_RES*

I2C_SDA

CODEC_INT

+5V(STBY)

+36V_VAR(D)

VFD_F2

VFD_F1

+3V3(H8)

GND

47P

C37

50V 0603

47P

C4

50V 0603

NF

47P

C5

50V 0603

CODEC_INT

I2C_SDA

I2C_SCLK

I2C_RES*

VADDIS_PROG

AUXSCART_IN_L

AUXSCART_IN_R

TVSCART_IN_L

TVSCART_IN_R

SATSCART_IN_L

SATSCART_IN_R

HS_TEMP

C25

C24

1N0

1N0

50V

50V

0603

0603

GND

1mm FFC - Molex / 52806-3010 or JST / 30FMN-BTRK

123456789

VAD_RX0

H8_VAD_COM

VAD_H8_COM

Vaddis port 1

VAD_H8_COM

H8_VAD_COM

101112131415161718192021222324252627282930

VAD_TX0

ADC_PCM

SPDIF_SW

VAD_DIGOP

DAC_PCM3

DAC_PCM2

Vaddis port 0 - To prog V addis

VAD_TX0

VAD_RX0

ADC_PCM

SPDIF_SW

DAC_PCM2

DAC_PCM3

VAD_DIGOP

Main PCB.sch

KEYB_STBY

LED_SPARE3*

P46

P47

C28

30

1N0

50V

0603

1mm FFC - Molex / 52806-3010 or JST / 30FMN-BTRK

To L104AY (Video Board)

GND

P48

P49

P50

P51

P52

P53

P54

P55

P56

DAC_PCM1

DAC_PCM0

RX_LRCLK

RX_SCLK

RMCK+

RMCK-

CLK27M_VADDIS+

P61

P62

P12

RMCK-

RMCK+

RX_SCLK

RX_LRCLK

DAC_PCM0

DAC_PCM1

LED_SPARE1*

LED_RED*

LED_BLUE*

LED_SPARE2*

IR_FRONT

P43

P44

P45

KEYB0

KEYB1

KEYB_GND

P65

P67

DISP_DAT

P66

P68

P69

P70

CLK27M_VADDIS-

P23

CLK27M_VADDIS-

CLK27M_VADDIS+

FIXED_VOL_L_MU

FIXED_VOL_R_MU

AMP_MUTE_LCR*

AMP_MUTE_SUR*

PWR_AMP_SR

PWR_AMP_R

PWR_AMP_C

PWR_AMP_L

PWR_AMP_SL

PRE_OUT_L

PRE_OUT_R

PRE_OUT_C

PRE_OUT_SUB

PRE_OUT_SL

PRE_OUT_SR

Z2_OUT_L

Z2_OUT_R

HP_OUT_L

HP_OUT_R

DISP_CLK

DISP_DAT

DISP_LAT

DISP_LAT

DISP_CLK

P71

P72

CON3

MOLEX

52806

P57

P58

P59

P60

DISP_BLK

DISP_BLK

P73

1234567891011121314151617181920212223242526272829

47P

C8

50V 0603

47P

C9

50V 0603

47P

C10

50V 0603

47P

C11

50V 0603

47P

C12

50V 0603

47P

C13

50V 0603

C14

47P

50V 0603

FIXED_VOL_L_MU

FIXED_VOL_R_MU

P63

P64

R3

47K

0603

GNDGND

GND

C15

50V 0603

C16

50V 0603

C17

50V 0603

NF

C18

50V 0603

NF

C19

50V 0603

NF

C20

50V 0603

NF

P74

P75

P76

P77

P78

P79

P80

HP_OUT_L

HP_OUT_R

R4

47K

0603

+3V3(STBY)

KUNMING

GOLD

Solo 2.1 only

NF Solo 5.1

47P

47P

47P

47P

47P

47P

R5

10K

0603

NF

These caps on audio clock and data lines from

the Vaddis are not fitted to help improve the

video noise floor problems on CVBS. (In

conjunction with high value source resistance

NF

termination on the video board.)

NF

+3V3(STBY)

GND

P81

P82

P83

P84

P85

P86

P87

P88

SKT9

Zone2 / Record

SCRN

GND

P89

HS_TEMP

AMP_MUTE_LCR*

AMP_MUTE_SUR*

PWR_AMP_SR

PWR_AMP_R

PWR_AMP_C

PWR_AMP_L

PWR_AMP_SL

SKT3

SKT8

KYOYAKU GOLD

SKT4

KYOYAKU GOLD

PRE_OUT_C PRE_OUT_L

PRE_OUT_SUB

KYOYAKU

GOLD

Solo 2.1 only

NF Solo 5.1

Z2_OUT_L

Z2_OUT_R

CON4

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

MOLEX

52806

GND

1mm FFC - Molex / 52806-1610

Solo 5.1 only

NF Solo 2.1

SCRN

SCRN

GND

To L103AY (Power Amp Board)

PRE_OUT_R

PRE_OUT_SL

PRE_OUT_SR

Solo 2.1 only

NF Solo 5.1

GOLD

KUNMING

SKT7

GND

SCRN

To L108AY (Display Board)

L998CT - Solo Movie 5.1

Main/Audio PCB

QTY DESCRIPTIONPART No. NOTESITEM

ITEM3 1 Blank PCB Solo5.1 Main BoardL998PB

DRAWING TITLE

Solo Movie Main PCB - Top level

Filename:

Top level Solo Movie 3.0.prj

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB25 9QR

Notes:

Contact Engineer:

markt@arcam.co.uk

Contact Tel:

AJD 25/06/07 3.0Added connectors for Solo 2.1 options07_E129

07_E084 MJT 11/06/07

07_E045 MJT 07/03/07

07_E014 MJT 01/02/07 No schematic changes. Layout change only (R620, R621 moved) 2.0

06_E194 MJT 23/01/07 1.0

ECO No. DESCRIPTION OF CHANGE

01223 203210 (direct)Mark Tweedale

01223 203200 (reception)

INITIALS

Printed:

2-Aug-2007

None to this sheet.

Changed R442 - R445 for compatibility with revised VFD.

None to this sheet.

Changed C810, C851 to longer life parts due to heat.

SKT500 changed to common GND/EMC type, R338, R339,

R217, R647 added to PCB. Some caps on CON2 removed

DATE

1 11Sheet of

A2

DRAWING NO.

2.2

2.1

ISSUE

L998CT

KEYB_STBY

KEYB0

KEYB1

KEYB_GND

HD_PHONE

HS_TEMP

IR_FRONT

RDS_CLK

RDS_DATA

PLL_DO

STEREO

TUNED

FM_PRES

CLIENT_PRES*

IR_FRONT

Z1_RM_IN

Z2_RM_IN

AC_PRESENT

RX_CMOS

RLEAD*

SATSCART_IN_L

SATSCART_IN_R

SAT_IN_L

SAT_IN_R

TVSCART_IN_L

TVSCART_IN_R

TV_IN_L

TV_IN_R

AUXSCART_IN_L

AUXSCART_IN_R

AUX_IN_L

AUX_IN_R

FRONT_IN_L

FRONT_IN_R

SATSCART_IN_L

SATSCART_IN_R

SAT_IN_L

SAT_IN_R

TVSCART_IN_L

TVSCART_IN_R

TV_IN_L

TV_IN_R

AUXSCART_IN_L

AUXSCART_IN_R

AUX_IN_L

AUX_IN_R

FRONT_IN_L

FRONT_IN_R

VAD_DIGOP

MicroController.sch

KEYB_STBY

KEYB0

KEYB1

KEYB_GND

HD_PHONE

HS_TEMP

RDS_CLK

RDS_DATA

PLL_DO

STEREO

TUNED

FM_PRES

CLIENT_PRES*

IR_FRONT

Z1_RM_IN

Z2_RM_IN

AC_PRESENT

RX_CMOS

RLEAD*

VAD_H8_SW H8_VAD_SW

24M_CLK_EN*

12M_CLK_EN*

CODEC_INT

ALARM_RAW

PREAMP_CLK

PREAMP_DA

PREAMP_MUTE

SAT_SCART_SW

TV_SCART_SW

AUX_SCART_SW

PREOUT_MUTE*

PREOUT_MUTE_Z2*

SURR_SEL_0

SURR_SEL_1

Z2_SEL_PRE

Z2_SEL_2D

I2CDAB_SCLK

I2CDAB_SDA

I2CDAB_RES*

VADDIS_PROG

TRIG_OUT*

VFD_HT_ADJ

POWER_ON

HARD_STBY*

FAST_SLOW*

PATH_AD*

AMP_MUTE_LCR*

AMP_MUTE_SUR*

LED_RED*

LED_BLUE*

LED_SPARE1*

LED_SPARE2*

LED_SPARE3*

DAB/VAD*

24M/22M*

I2C_SCLK

I2C_SDA

I2C_RES*

PLL_CLK

PLL_DI

PLL_CE

FAN_ON

TX_CMOS

PATH_B*

PATH_C*

DISP_CLK

DISP_DAT

DISP_LAT

DISP_BLK

DAC_PCM0

DAC_PCM1

DAC_PCM2

DAC_PCM3

RX_SCLK

RX_LRCLK

ALARM_RAW

PREAMP_CLK

PREAMP_DA

PREAMP_MUTE

SAT_SCART_SW

TV_SCART_SW

AUX_SCART_SW

PREOUT_MUTE*

PREOUT_MUTE_Z2*

SURR_SEL_0

SURR_SEL_1

Z2_SEL_PRE

Z2_SEL_2D

PLL_CLK

PLL_DI

PLL_CE

ADC_BUF_L+

ADC_BUF_L-

ADC_BUF_R+

ADC_BUF_R-

I2C_SCLK

I2C_SDA

I2C_RES*

VADDIS_PROG

AMP_MUTE_LCR*

AMP_MUTE_SUR*

LED_RED*

LED_BLUE*

LED_SPARE1*

LED_SPARE2*

LED_SPARE3*

DISP_CLK

DISP_DAT

DISP_LAT

DISP_BLK

DAB_DIGOP

Codec.sch

ADC_BUF_L+

ADC_BUF_L-

ADC_BUF_R+

ADC_BUF_R-

DAC_PCM0

DAC_PCM1

DAC_PCM2

DAC_PCM3

RX_SCLK

RX_LRCLK

VAD_DIGOP

DAB_DIGOP

DAB/VAD*

24M/22M*

24M_CLK_EN*

12M_CLK_EN*

I2C_SCLK

I2C_SDA

I2C_RES*

VQ_BUF

DAC_L+

DAC_L-

DAC_R+

DAC_R-

DAC_C+

DAC_C-

DAC_SUB+

DAC_SUB-

DAC_LS+

DAC_LS-

DAC_RS+

DAC_RS-

DAC_2CH_L+

DAC_2CH_L-

DAC_2CH_R+

DAC_2CH_R-

SPDIF_SW

ADC_PCM

RMCK+

RMCK-

CLK27M_VADDIS+

CLK27M_VADDIS-

SMPS_SYNC

SMPS_SYNC*

CODEC_INT

ADC_UNBUF_L+

ADC_UNBUF_L-

ADC_UNBUF_R+

ADC_UNBUF_R-

SMPS_SYNC

SMPS_SYNC*

CODEC_INT

Filters.sch

ADC_UNBUF_L+

ADC_UNBUF_L-

ADC_UNBUF_R+

ADC_UNBUF_R-

VQ_BUF

DAC_L+

DAC_L-

DAC_R+

DAC_R-

DAC_C+

DAC_C-

DAC_SUB+

DAC_SUB-

DAC_LS+

DAC_LS-

DAC_RS+

DAC_RS-

DAC_2CH_L+

DAC_2CH_L-

DAC_2CH_R+

DAC_2CH_R-

SPDIF_SW

ADC_PCM

RMCK+

RMCKCLK27M_VADDIS+

CLK27M_VADDIS-

CODEC_INT

ADC_BUF_L+

ADC_BUF_L-

ADC_BUF_R+

ADC_BUF_R-

DAC_OUT_L

DAC_OUT_R

DAC_OUT_C

DAC_OUT_SUB

DAC_OUT_SL

DAC_OUT_SR

DAC_2DMIX_L

DAC_2DMIX_R

ADC_BUF_L+

ADC_BUF_L-

ADC_BUF_R+

ADC_BUF_R-

DAC_2DMIX_L

DAC_2DMIX_R

Tuner interface.sch

TUNER_L

PLL_CLK

PLL_DI

PLL_CE

PLL_CLK

PLL_DI

PLL_CE RDS_DATA

I2CDAB_SCLK

I2CDAB_RES*

IR remote.sch

IR_FRONT

TRIG_OUT*

IR_FRONT Z2_RM_IN

PSU.sch

VFD_HT_ADJ AC_PRESENT

SMPS_SYNC

SMPS_SYNC*

POWER_ON

SMPS_SYNC

SMPS_SYNC*

HARD_STBY*

FAN_ON

FAST_SLOW*

RS232.sch

TX_CMOS RX_CMOS

PATH_AD*

PATH_B*

PATH_C*

VAD_TX0 VAD_RX0

VAD_H8_COM H8_VAD_COM

VAD_TX0 VAD_RX0

VAD_H8_COM H8_VAD_COM

H8_VAD_SW VAD_H8_SW

TUNER_R

RDS_CLK

PLL_DO

STEREO

TUNEDI2CDAB_SDA

DAB_DIGOP

FM_PRES

CLIENT_PRES*

Z1_RM_IN

RLEAD*

RDS_CLK

RDS_DATA

PLL_DO

STEREO

TUNED

DAB_DIGOP

FM_PRES

CLIENT_PRES*

Z1_RM_IN

Z2_RM_IN

AC_PRESENT

RX_CMOS

RLEAD*

VAD_H8_SWH8_VAD_SWVAD_H8_SW

SATSCART_IN_L

SATSCART_IN_R

SAT_IN_L

SAT_IN_R

TVSCART_IN_L

TVSCART_IN_R

TV_IN_L

TV_IN_R

AUXSCART_IN_L

AUXSCART_IN_R

AUX_IN_L

AUX_IN_R

FRONT_IN_L

FRONT_IN_R

DAC_2DMIX_L

DAC_2DMIX_R

TUNER_IN_L

TUNER_IN_R

ALARM_RAW

PREAMP_CLK

PREAMP_DA

PREAMP_MUTE

SAT_SCART_SW

TV_SCART_SW

AUX_SCART_SW

PREOUT_MUTE*

Preamp.sch

SATSCART_IN_L

SATSCART_IN_R

SAT_IN_L

SAT_IN_R

TVSCART_IN_L

TVSCART_IN_R

TV_IN_L

TV_IN_R

AUXSCART_IN_L

AUXSCART_IN_R

AUX_IN_L

AUX_IN_R

FRONT_IN_L

FRONT_IN_R

DAC_2DMIX_L

DAC_2DMIX_R

TUNER_IN_L

TUNER_IN_R

ALARM_RAW

DAC_OUT_L

DAC_OUT_R

DAC_OUT_C

DAC_OUT_SUB

DAC_OUT_SL

DAC_OUT_SR

PREAMP_CLK

PREAMP_DA

PREAMP_MUTE

SAT_SCART_SW

TV_SCART_SW

AUX_SCART_SW

PREOUT_MUTE*

FIXED_VOL_L

FIXED_VOL_R

DRAWING TITLE

ADC_UNBUF_L+

ADC_UNBUF_L-

ADC_UNBUF_R+

ADC_UNBUF_R-

PRE_SUB

PRE_SL

PRE_SR

PRE_REC_L

PRE_REC_R

FIXED_VOL_L_MU

FIXED_VOL_R_MU

PRE_L

PRE_R

PRE_C

ADC_UNBUF_L+

ADC_UNBUF_L-

ADC_UNBUF_R+

ADC_UNBUF_R-

Solo Movie Main PCB - Structure

Filename:

Main PCB.sch

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB25 9QR

Notes:

Contact Engineer:

markt@arcam.co.uk

DAC_2DMIX_L

DAC_2DMIX_R

SURR_SEL_0

SURR_SEL_1

Z2_SEL_PRE

Z2_SEL_2D

PREOUT_MUTE*

PREOUT_MUTE_Z2*

PREAMP_CLK

PREAMP_DA

PREAMP_MUTE

01223 203210 (direct)Mark Tweedale

Contact Tel:

01223 203200 (reception)

Audio switch and mute.sch

PRE_L

PRE_R

PRE_C

PRE_SUB

PRE_SL

PRE_SR

PRE_REC_L

PRE_REC_R

DAC_2DMIX_L

DAC_2DMIX_R

SURR_SEL_0

SURR_SEL_1

Z2_SEL_PRE

Z2_SEL_2D

PREOUT_MUTE*

PREOUT_MUTE_Z2*

PREAMP_CLK

PREAMP_DA

PREAMP_MUTE

AJD 25/06/07 3.007_E129 None to this sheet.

07_E084 MJT 11/06/07 None to this sheet. 2.2

07_E045 MJT 07/03/07 None to this sheet. 2.1

07_E014 MJT 01/02/07 No schematic changes. Layout change only (R620, R621 moved) 2.0

06_E194 MJT 23/01/07 1.0Full production. No changes to this sheet

ECO No. DESCRIPTION OF CHANGE

INITIALS

Printed:

DATE

2-Aug-2007

PWR_AMP_L

PWR_AMP_R

PWR_AMP_C

PWR_AMP_SL

PWR_AMP_SR

PRE_OUT_L

PRE_OUT_R

PRE_OUT_C

PRE_OUT_SUB

PRE_OUT_SL

PRE_OUT_SR

Z2_OUT_L

Z2_OUT_R

HP_OUT_L

HP_OUT_R

FIXED_VOL_L

FIXED_VOL_R

2 11Sheet of

PWR_AMP_L

PWR_AMP_R

PWR_AMP_C

PWR_AMP_SL

PWR_AMP_SR

PRE_OUT_L

PRE_OUT_R

PRE_OUT_C

PRE_OUT_SUB

PRE_OUT_SL

PRE_OUT_SR

Z2_OUT_L

Z2_OUT_R

HP_OUT_L

HP_OUT_R

FIXED_VOL_L_MU

FIXED_VOL_R_MU

DRAWING NO.

A2

ISSUE

L998CT

IR_FRONT

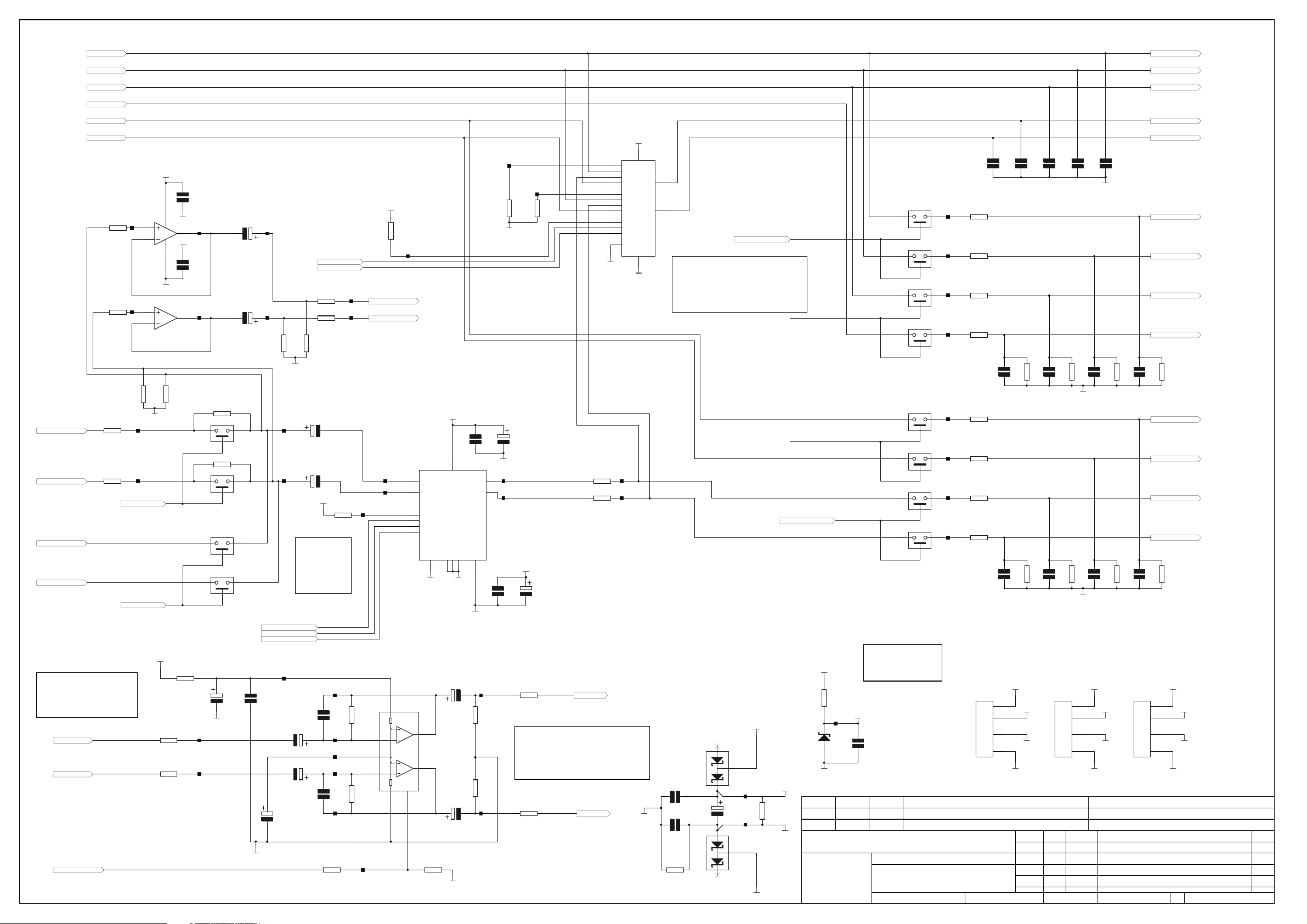

Pd=2.5mW

+5V(STBY)

R300

10K

0W063

0603

TR300

MMUN2211LT1

SOT-23

GND

Do NOT use NE555 /

LM555 etc for IC300. Must

be CMOS type otherwise

frequency will be wrong.

P303

GND

C300

1N0

50V

0603

X7R

2

TRIG

5

Vcont

6

THR HLD

4

RESET

+5V(STBY)

8

VCC

D CHG

GND

1

GND

IC300

7

3

OP

LMC555CM

SO-8

P307

+5V(STBY)

C301

100UF

25V

YK

GND

NCNC

P306

R308

20K

0W063

0603

Re-modulation

frequency =

36.8kHz approx.

IR eye we use is

36.7kHz.

R337

1K0

0603

C302

P310 P311

10uF

10V

1206

C303

P302

10uF

10V

1206

C304

P333

10uF

10V

1206

TR301

MMUN2211LT1

SOT-23

GND

TR302

MMUN2211LT1

SOT-23

GND

TR303

MMUN2211LT1

SOT-23

GND

R309

4K7

0W063

0603

Pd=5.3mW

P318

+12V(D)

GND

R312

2K2

0W125

0805

R313

2K2

0W125

0805

C305

100P

50V

0603

TR304

MMUN2211LT1

SOT-23

Pd=66mW each

RC5_OUT

GND

REMOTE OUT

P325

Z1_RM_IN

Z2_RM_IN

Z1_RM_IN

Z2_RM_IN

SKT300

SCRN1

R

R

L

SCRN2

TRIG_OUT*

C319

47P

50V

0603

GND

R314

2K2

0W125

0805

P331

P332 P334

TR308

BC849B

SOT-23

R307

10K

0W063

0603

R335

100R

0W125

0805

RC5_OUT

TRIG_OUT

P335

C322

100P

50V

0603

TR309

BD179

TO-126

R336

22R

0W125

0805

NC

NC

GND

SKT301

R

4

56L

R

1

L

2

3

SCRN1

SCRN2

GND

Load vs current

O/C --> 11.2V

470R --> 10.4V (22mA)

330R --> 8.7V (26mA)

220R --> 6.3V (28mA)

100R --> 3.1V (31mA)

S/C --> 34mA

TRIG_OUT

12V TRIG OUT

GND

C318

47P

50V

0603

+12V(D)

C308

C309

ZONE1 REMOTE

P300

4

NC

56L

1

NC

2

3

P301

GND

R315

2K2 0W063

0603

C306

1N0

100V

0805

GND

ZONE2 REMOTE

R316

2K2 0W063

0603

C307

1N0

100V

0805

GND

P304

R301

10K

0W063

0603

P305

R304

10K

0W063

0603

R317

47K 0W063

0603

DZ300

BZX84C

4V7

SOT-23

R318

47K 0W063

0603

DZ301

BZX84C

4V7

SOT-23

P308

R319

680R

0W063

0603

C310

C311

P309

R320

680R

0W063

0603

50V

0603

50V

0603

50V

0603

50V

0603

330P

330P

+5V(STBY)

330P

330P

+5V(STBY)

C312

100N

16V

0603

C314

100N

16V

0603

P312

P313

R321

3K3

0W063

0603

P314

R325

1K8

0W063

0603

P316

R323

3K3

0W063

0603

P317

R326

1K8

0W063

0603

Centre frequency of bandpass = 37kHz (measured)

R327 130K

0W063 0603

C313

100N

16V

0603

R328 130K

0W063 0603

C315

100N

16V

0603

84

2

3

2

3

IC301A

LM358D

SO-8

84

IC302A

LM358D

SO-8

1

P315

1

R302

10K

0W063

0603

R338

4K7

0W063

0603

R305

10K

0W063

0603

R339

4K7

0W063

0603

+5V(STBY) +5V(STBY)

Pd(max)=8mW Pd(max)=5.3mW

P319

D300

BAS16

SOT-323

P321

C316

680P

50V

0603

P322

D301

BAS16

SOT-323

C317

680P

50V

0603

R329

470K

0W063

0603

Pd(max)=8mW Pd(max)=5.3mW

P324

R330

470K

0W063

0603

R322

3K3

0W063

0603

R333 22K

0W063 0603

P320

6

5

R331

1K5

0W063

0603

+5V(STBY) +5V(STBY)

R324

3K3

0W063

0603

R334 22K

0W063 0603

P323

6

5

R332

1K5

0W063

0603

IC301B

LM358D

SO-8

IC302B

LM358D

SO-8

P327P329

7

TR305

MMUN2211LT1

SOT-23

7

TR306

MMUN2211LT1

SOT-23

R310

4K7

0W063

0603

R311

4K7

0W063

0603

P330

P326

P328

R303

10K

0W063

0603

R306

10K

0W063

0603

MMUN2211LT1

TRIG_OUT*

TR307

SOT-23

DRAWING TITLE

Solo Movie Main PCB - IR Remote

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB25 9QR

Filename:

Notes:

Contact Engineer:

IR remote.sch

markt@arcam.co.uk

Contact Tel:

AJD 25/06/07 3.007_E129 None to this sheet.

07_E084 MJT 11/06/07 None to this sheet. 2.2

07_E045 MJT 07/03/07 None to this sheet. 2.1

07_E014 MJT 01/02/07 No schematic changes. Layout change only (R620, R621 moved) 2.0

06_E194 MJT 23/01/07 1.0Full production. R338, R339 added to PCB

01223 203210 (direct)Mark Tweedale

01223 203200 (reception)

ECO No. DESCRIPTION OF CHANGE

INITIALS

Printed:

DATE

2-Aug-2007

3 11Sheet of

A3

DRAWING NO.

ISSUE

L998CT

GND

GND

+3V3(H8)

+3V3(H8)

IC401A

1

A0

2

A1

A23SDA

24LC08BT/SN

SO-8

IC400C

VCC

GND

74LVC244APW

TSSOP-20

+3V3(H8)

3

CLK

2

D

C419

100N

16V

0603

GND

C420

100N

16V

0603

GND

WP

SCL

20

10

1

IC402A

Q

RD

Q

SD

74HC74D

4

SO-14

14

VCC

7

GND

IC402C

74HC74D

SO-14

IC401B

8

VCC

4

GND

24LC08BT/SN

SO-8

7

6

5

+3V3(STBY)

Z2_RM_IN

RLEAD*

Z1_RM_IN

IR_FRONT

6

5

+3V3(H8)

R467

10K

0603

RDS_DATA

STEREO

TUNED

PLL_DO

RDS_CLK

CLIENT_PRES*

FM_PRES

AC_PRESENT

C414

100N

16V

0603

GND

NC

NC

+3V3(H8)

C432

100N

16V

0603

GND

R413

4K7 0603

R415

4K7 0603

GND

R468

10K

0603

I2CEEPROM_SCLK

I2CEEPROM_SDA

RDS_DATA

STEREO

TUNED

PLL_DO

RDS_CLK

CLIENT_PRES*

FM_PRES

AC_PRESENT

C405

47P

50V

0603

GND

SAT_SCART_SW_U

TV_SCART_SW_U

AUX_SCART_SW_U

PREOUT_MUTE_U*

PREOUT_MUTE_Z2_U*

SURR_SEL_0_U

SURR_SEL_1_U

Z2_SEL_PRE_U

Z2_SEL_2D_U

IC406E

14

VCC

7

GND

74VHC08M

SO-14

P400

P401

5V to 3V3 translation

IC400A

1

OE

2

A0

4

A1

6

A2

8

A3

74LVC244APW

TSSOP-20

IC400B

19

OE

17

A0

15

A1

13

A2

11

A3

74LVC244APW

TSSOP-20

GND

AMP_MUTE_LCR_U*

AMP_MUTE_SUR_U*

R404

47K

0603

GND

GND

LED_SPARE1*

LED_SPARE2*

LED_SPARE3*

LED_BLUE*

LED_RED*

C422

1N0

50V

0603

Z2_RM_IN

RLEAD*

Z1_RM_IN

IR_FRONT

R447

R446

47K

47K

0603

0603

IC406B

74VHC08M

SO-14

4

6

5

R405

47K

0603

P412

P413

P414

P415

R448

47K

0603

P466

P467

P407

P408

P409

P410

P411

NC

Y0

Y1

Y2

Y3

Y0

Y1

Y2

Y3

C423

R449

47K

0603

18

16

14

12

3

5

7

9

P468

P470

1N0

50V

0603

HD_PHONE

KEYB_STBY

R450

47K

0603

12

13

GND

RDS_DATA_3V3

STEREO_3V3

TUNED_3V3

PLL_DO_3V3

NC

NC

NC

RDS_CLK_3V3

POWER_ON

HARD_STBY*

R425

1K0 0603

R426

1K0 0603

C424

C430

1N0

1N0

50V

50V

0603

0603

R417 10K

R418 10K

R419 10K

R420 10K

R421 10K

R422 10K

R428 10K

R429 10K

R430 10K

R451

47K

0603

GND

IC406A

74VHC08M

SO-14

1

2

IC406D

74VHC08M

SO-14

3

11

C425

GND

0603

0603

0603

0603

0603

0603

0603

0603

0603

NC

NC

+3V3(STBY)

IC407

LM19

1

GND

NF

TO-92

+Vs

Vout

GND

3

R456

P488 P489

2

470R

0W063

0603

24M/22M*

24M_CLK_EN*

12M_CLK_EN*

FAN_ON

FAST_SLOW*

+3V3(H8)

DISP_BLK_U

DISP_LAT_U

LED_SPARE3*

LED_SPARE2*

LED_SPARE1*

LED_BLUE*

LED_RED*

PATH_B*

PATH_AD*

PATH_C*

I2CEEPROM_SCLK

I2CEEPROM_SDA

I2CDAB_RES*

I2CH8_RES*

I2CDAB_SCLK

I2CDAB_SDA

I2CH8_SCLK

I2CH8_SDA

RDS_CLK_3V3

RLEAD*

NF

+3V3(H8)

CON400

3

2

1

HARWIN

M20-973

Hi: Emulate

Low: Normal operation

PREAMP_MUTE_U

PREAMP_DA_U

PREAMP_CLK_U

DAB/VAD*

C438

100N

16V

0603

GND

R402 4K7

0603

R403 4K7

0603

GND

R457

4K7

0603

C437

100N

16V

0603

P429

P469

P402

P403

P404

P405

P406

P478

P479

P436

POWER_ON

HARD_STBY*

AMP_MUTE_LCR*

AMP_MUTE_SUR*

LED_SPARE1*

LED_SPARE2*

LED_SPARE3*

LED_BLUE*

LED_RED*

1N0

50V

0603

HD_PHONE

KEYB_STBY

Despite the labels above:

HI = LED on

LO = LED off

GND

R423

10K

0603

P454

SAT_SCART_SW

P455

TV_SCART_SW

P456

AUX_SCART_SW

P457

PREOUT_MUTE*

P458

PREOUT_MUTE_Z2*

P459

SURR_SEL_0

P460

SURR_SEL_1

P461

Z2_SEL_PRE

P462

Z2_SEL_2D

ITEM401 1 Ferrite Plate - This part is RoHS compliant.F242 Place on top of IC403

ITEM400 1 Con Jumper Socket 0.1IN Gold Blue8K004

P475

P477

P480

P490

GND

P437

GND

+3V3(H8)

P476

P481

P420

P421

P422

P423

NC

NC

NC

NC

NC

NC

NC

NC

P418

P419

102

C433

100N

16V

0603

+3V3(H8)

KEYB0

KEYB1

KEYB_GND

HS_TEMP

24M/22M*

24M_CLK_EN*

12M_CLK_EN*

FAN_ON

FAST_SLOW*

5

6

7

8

9

11

12

13

14

15

16

17

19

20

21

22

23

24

26

27

28

29

30

31

32

35

36

37

38

2

10

18

25

50

70

95

41

NF

R406

10K

0603

DISP_DAT_U

MD0

MD1

MD2

1

144

MD2

PC0/A0

PC1/A1

PC2/A2

PC3/A3

PC4/A4

PC5/A5

PC6/A6

PC7/A7

PB0/A8

PB1/A9

PB2/A10

PB3/A11

PB4/A12

PB5/A13

PB6/A14

PB7/A15

PA0/A16

PA1/A17

PA2/A18

PA3/A19

PA4/A20/IRQ4

PA5/A21/IRQ5

PA6/A22/IRQ6

PA7/A23/IRQ7

EMLE

PH0/CS4/RAS4/WE

PH1/CS5/RAS5/SDRAMphi

PH2/CS6/(IRQ6)

PH3/CS7/(IRQ7)/OE/CKE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCL

R431 10K

R432 220R

R433 220R

142

143

MD0

MD1

P30/TXD0/IrTXD

Set as interrupt?

Set as interrupt

Set as interrupt?

Set as interrupt

WDTOVF39NMI

P10/PO8/TIOCA042P11/PO9/TIOCB043P12/PO10/TIOCC0/TCLKA44P13/PO11/TIOCD0/TCLKB45P14/PO12/TIOCA146P15/PO13/TIOCB1/TCLKC47P16/PO14/TIOCA2/EDRAK248P17/PO15/TIOCB2/TCLKD/EDRAK3

40

FAST_SLOW*

FAN_ON

HARD_STBY*

IR_FRONT

WDTOVF*

No ERC on IC403 pin 59 (CODEC_INT) to

prevent warning of Output and I/O on the same

net

0603

0603

0603

GND

TX_CMOS_U

141

P31/TXD1

POWER_ON

P463

P464

P465

C400

47P

50V

0603

RX_CMOS

NC

139

140

P33/RXD1/SCL1

P32/RXD0/IrRXD/SDA1

Z1_RM_IN

Z2_RM_IN

DISP_CLK_U

P53

NC

136

137

138

P53/ADTRG/IRQ3

P34/SCK0/SCK4/SDA0

P35/SCK1/SCL0/(OE)/(CKE)

Set as interrupt?

P20/PO0/TIOCA3/(IRQ8)51P21/PO1/TIOCB3/(IRQ9)52P22/PO2/TIOCC3/(IRQ10)53P23/PO3/TIOCD3/TXD4/(IRQ11)54P24/PO4/TIOCA4/RXD4/(IRQ12)55P25/PO5/TIOCB4/(IRQ13)56P26/PO6/TIOCA5/(IRQ14)57P27/PO7/TIOCB5/(IRQ15)

49

NC

TRIG_OUT*

AC_PRESENT

PREAMP_MUTE

PREAMP_DA

PREAMP_CLK

DAB/VAD*

C401

47P

50V

0603

NC

135

P52/SCK2/IRQ2

NCNCNC

VAD_H8_SW

134

C402

47P

50V

0603

R410

10R

0603

GND

KEYB1

KEYB0

BOX_TEMP

HS_TEMP

VFD_HT_ADJ

ALARM_RAW

FM_PRES

CLIENT_PRES*

STEREO_3V3

RDS_DATA_3V3

PLL_DO_3V3

H8_VAD_SW_U

133

P51/RXD2/IRQ1

TUNED_3V3

NC

NC

122

123

124

125

126

127

128

P91/AN9

P92/AN10

P93/AN11

P94/AN12/DA2

P95/AN13/DA3

P96/AN14/DA4

P97/AN15/DA5

P50/TXD2/IRQ0

Set as interrupt

Set as interrupt

Set as interrupt?

Set as interrupt

P80/(IRQ0)/EDREQ2

P81/(IRQ1)/TXD3/EDREQ333P82/(IRQ2)/ETEND2

P83/(IRQ3)/RXD3/ETEND359P84/(IRQ4)/EDACK260P85/(IRQ5)/SCK3/EDACK361DCTL62PE0/D063PE1/D164PE2/D265PE3/D366PE4/D467PE5/D568PE6/D6

3

34

58

NCNCNC

RTC_RES*

RTC_DA

RTC_SCLK

KEYB_STBY

HD_PHONE

CODEC_INT

32.768KHz

XTAL CYLINDRICAL

Place on CON400 between pins 1 & 2 [for normal (Non-emulation) operation]

121

P90/AN8

X401

GND

GND

GND

NC

NC

113

114

115

116

117

118

119

120

P40/AN0

P41/AN1

P42/AN2

P43/AN3

P44/AN4

P45/AN5

P46/AN6/DA0

P47/AN7/DA1

NC

NC

PREAMP_DA_U

PREAMP_CLK_U

Z2_SEL_2D_U

Z2_SEL_PRE_U

+3V3(H8)

C421

100N

16V

0603

1

2

X1

VCC2

3

X2

GND

4

R466

P426

0R0

0603

New reset circuit

P452

VFD_HT_ADJ

P453

ALARM_RAW

+3V3(H8)

KEYB_GND

111

112

129

VREF

AVSS

AVCC

PG6/BREQ

PG5/BACK

PG4/BREQO

PG3/CS3/RAS3/CAS

PG2/CS2/RAS2/RAS

PG1/CS1

PG0/CS0

P65/TMO1/IDACK1/IRQ13

P64/TMO0/DACK0/IRQ12

P63/TMCI1/TEND1/IRQ11

P62/TMCI0/TEND0/IRQ10

P61/TMRI1/DREQ1/IRQ9

P60/TMRI0/(DREQ0)/IRQ8

PF4/HWR

PF3/LWR

PF2/IRQ15/LCAS/DQML

PF1/IRQ14/UCAS/DQMU

69

C426

12P

50V

PREAMP_MUTE_U

0603

8

VCC1

SCLK

RESET

PE7/D7

XTAL96EXTAL

71

NC

P435 P443

GND

7

6

I/O

5

IC405

DS1302Z

SO-8

PF0/WAIT

PD7/D15

PD6/D14

PD5/D13

PD4/D12

PD3/D11

PD2/D10

97

103

X400

25MHz

HC49-4H

C428

0.1F

5.5V

NF Gold

RTC_SCLK

RTC_DA

RTC_RES*

PLLVCC

PLLVSS

PF7/Phi

PF6/AS

PF5/RD

PD1/D9

PD0/D8

VCC

VCC

VCC

VCC

STBY

92

NF

D401

BAS16

SOT-323

NC

NC

RES

GNDGND

+3V3(H8)

D400

R411

BAS16

20K

SOT-323

0603

GND

KEYB_STBY

1=Prog, 0=Run

IC403

HD64F2378RVFQ34V

QFP-144

132

PG6

131

PG5

130

PG4

110

AMP_MUTE_SUR_U*

109

AMP_MUTE_LCR_U*

108

NC

107

NC

106

PLL_CLK*

105

PLL_CE*

104

PLL_DI*

83

NC

82

+3V3(H8)

NC

81

NC

R455

200R

101

NC

0603

100

NC

P439

91

93

94

GND

NC

90

NC

89

DAB/VAD*

88

24M_CLK_EN*

87

12M_CLK_EN*

86

24M/22M*

85

NC

84

VADDIS_PROG_U

80

PREOUT_MUTE_Z2_U*

79

TV_SCART_SW_U

78

AUX_SCART_SW_U

77

SAT_SCART_SW_U

PREOUT_MUTE_U*

76

75

SURR_SEL_1_U

74

SURR_SEL_0_U

73

NC

+3V3(H8)

4

72

98

99

RES*

C427

12P

50V

0603

+3V3(H8)

NF

P425P424

R452

2K2

0603

+3V3(H8)

R409

4K7

0603

P427

P428

P430

DRAWING TITLE

C412

10UF

50V

YK

C434

100N

16V

0603

R412

0R0

0603

P431

R414

10K

0603

P432

P433

+3V3(H8)

VAD_H8_SW

H8_VAD_SW_U

I2CDAB_SCLK

I2CDAB_SDA

I2CDAB_RES*

I2CH8_SCLK

I2CH8_SDA

I2CH8_RES*

CODEC_INT

Solo Movie Main PCB - H8 Micro

Filename:

MicroController.sch

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB25 9QR

Notes:

Contact Engineer:

+3V3(H8)

13

11

CLK

12

D

10

+3V3(STBY)

R407

4K7

P434

+3V3(STBY)

R400

10K

0603

NF NF

+3V3(STBY)

R458

10K

0603

IC406C

74VHC08M

SO-14

8

markt@arcam.co.uk

MD2:

High = Running (Single chip mode and User

Program mode if Vaddis programs H8 flash)

Low = Boot mode (Cold boot programming using

RS232 cable)

IC402B

74HC74D

SO-14

8

MD2

Q

RD

Q

SD

R438 220R

R401

10K

0603

R459

10K

0603

R408

4K7

P416

P417

P491

P492

P493

P494

10

9

9

0603

P438

NC

+3V3(H8)

C431

10uF

10V

1206

GND

RS232 coms to Vaddis

VAD_H8_SW

H8_VAD_SW

C403

C404

47P

47P

50V

50V

0603

0603

GND

R460

R461

0R0

0603

NF NF NF

P444

Contact Tel:

R462

0R0

0R0

0603

0603

R463 0R0 0603

R464 0R0 0603

R465 0R0 0603

IC404

SOT-23

LM809M3-3.08

RESET*

DISP_BLK_U

DISP_LAT_U

DISP_CLK_U

DISP_DAT_U

R442 - R445 were 680R but had to be changed as

Noritake Itron changed the design of the VFD.

330R now required to fix the corruption.

RX_CMOS TX_CMOS_U

07_E084 MJT 11/06/07 2.2Changed R442 - R445 for compatibility with revised VFD.

07_E045 MJT 07/03/07 None to this sheet. 2.1

07_E014 MJT 01/02/07 No schematic changes. Layout change only (R620, R621 moved) 2. 0

06_E194 MJT 23/01/07 1.0Full production. No changes to this sheet

ECO No. DESCRIPTION OF CHANGE

01223 203210 (direct)Mark Tweedale

01223 203200 (reception)

+3V3(H8)

C411

C415

10uF

10N

10V

50V

1206

0603

GND

+5V(D) +5V(D) +5V(D)

R439

1K0

0603

TR403

MMUN2211LT1

SOT-23

GND GND GND

PLL_CLK*

P440

PLL_CE*

PLL_DI*

TRIG_OUT*

+3V3(H8)

RST

GND

P451

P482

P483

P485

P486

P484

P487

VADDIS_PROG_U VADDIS_PROG

PATH_AD*

PATH_B*

PATH_C*

P441

P442

Choose a lower reset voltage?

VCC

GND

R416

4K7

0603

R442 330R

P445

R443 330R

P446

R444 330R

P447

R445 330R

P448

AJD 25/06/07 3.007_E129 None to this sheet.

DATE

INITIALS

2-Aug-2007

Printed:

C416

10N

50V

0603

P495

P496

P497

R427

R434

4K7

4K7

0603

0603

P449

P450

R437 1K0 0603

+3V3(H8)

GND

0603

0603

0603

0603

R424

1K0

0603

4 11Sheet of

C410

10uF

10V

1206

R440

1K0

0603

TR404

MMUN2211LT1

SOT-23

I2CDAB_SCLK

I2CDAB_SDA

I2CDAB_RES*

I2C_SCLK

I2C_SDA

I2C_RES*

CODEC_INT

R435

R436

4K7

4K7

0603

0603

C406

47P

50V

0603

TX_CMOS

P473

Notes for H8 uC

----------------------- ----RXD2/TXD2 (pins 98/97) are the

RS232 coms to the Vaddis

Set Real-time clock to use internal

trickle charge (single diode and 2k

resistor)

XTAL is now 25MHz. Is this a

problem for timing?

+3V3(H8)

C413

C436

10N

10uF

50V

10V

0603

1206

GND

These sigs should be high in standby

for minimum current draw

+3V3(H8)

R453

R454

4K7

4K7

0603

0603

PG4

P53

WDTOVF*

RES(in)*

PG5

PG6

RES*

GND

C407

C408

47P

47P

50V

50V

0603

0603

TX_CMOSRX_CMOS

VADDIS_PROG

P472

PATH_AD*

PATH_B*

P474

PATH_C*

DRAWING NO.

A2

C435

10N

50V

0603

R441

1K0

0603

TR405

MMUN2211LT1

SOT-23

NF

CON499

1

2

3

4

5

6

7

8

9

10

11

12

13

14

3M

2500 series

C409

47P

50V

0603

GND

L998CT

PLL_CLK

PLL_CE

PLL_DI

TRIG_OUT*

Bodged for JTAG socket

DISP_BLK

DISP_LAT

DISP_CLK

DISP_DAT

ISSUE

SKT500

SAT

AV

KYOYAKU

GOLD

P549

1

VCC

O/P

GND

2

GND

1

VCC

O/P

GND

2

GND

DAB_DIGOP_SW

R500

75R

0W125

0805

GND

C501

100N

16V

0603

3

RX500

OC-0805R*007

C502

100N

16V

0603

3

RX501

OC-0805R*007

-3dB point at: 1/(2*Pi*[100+75]*47p) = 19.4MHz

P515 P523

P516

C521

10uF

10V

1206

GND

P517 P524

P518

C522

10uF

10V

1206

GND

P519 P525

R506

1K8

0603

R505

100R

0603

+5V(D)

R501

10R

0W125

0805

R504

1K8

0603

+5V(D)

R502

10R

0W125

0805

R507

1K8

0603

Output approx 0.5V

R533

220R

0603

GND

GND

Output approx 0.5V

GND

Output approx 0.5V

GND

P526

Switched Input from DAB and possible streaming client card

+3V3(D)

C529

470N

16V

GND

0805

12

16

EN

CLK27M_VADDIS

OK to have

unconnected inputs

(produces HIGH output)

12M_CLK_EN*

24M_CLK_EN*

+5V(D)

R521

0R0

0603

GND

24M/22M*

RMCK

C550

27P

50V

0603

C551

27P

50V

0603

24M/22M*

DIN110DOUT1+

11

DIN2

2

RIN1+

NC

1

NC

RIN1-

3

NC

RIN2+

4

RIN2-

NC

R542

4K7

0603

R543

4K7

0603

REG500

LM1117MPX-3.3

SOT-223

P536

C517

100N

16V

0603

GND GND

R527

10K

0603

DOUT1-

DOUT2+

DOUT2-

ROUT1

ROUT2

EN

9

13

GND

24M_CLK_EN_R*

+3V3

P520

X500

27MHz

HC49

P521

P522

VCC

GND

7

8

6

5

15

NC

14

NC

IC508

SN65LVDS049

TSSOP-16

P590

P527

NC

No output termination resistors:

Built-in 50 Ohm source impedance.

IC507C

5 6

74HC04D SO-14

+3V3(PLL)

C543

100UF

10V

YXF

1

7

XTI

8

XTO

14

FSEL

16

NC

2

C546

47P

50V

0603

R534

220R

0603

R535

220R

0603

RMCK+

RMCK-

CLK27M_VADDIS+

CLK27M_VADDIS-

DIV_2_EN12M_CLK_EN_R*

P589P588

VDD312VDD1

IC506

SM8707E

VSOP-16

VSS311VSS1

GND

C531

10N

50V

0603

C530

10N

50V

0603

C535

10N

50V

0603

C536

10N

50V

0603

C534

10N

50V

0603

C518

100N

16V

0603

5

6

To Vaddis 8

To Vaddis 8

To Vaddis 8

To Vaddis 8

VDD2

MO1

MO2

AO1

AO2

SO1

SO2

VSS2

GND

C519

100N

16V

0603

3

4

9

10

13

15

NC

NC

CLOCK GENERATOR

C537

10N

50V

0603

C520

100N

16V

0603

R529

56R 0603

P504

SPDIF data rate @ 96kHz 2-ch PCM:

96k x 32 bits x 2 channels = 6.144MHz

Bi-phase encoding has up to 2 symbols per bit.....

Therefore minimum bandwith is 12.288MHz

SPDIF_SAT_ELEC

SPDIF_SAT

SPDIF_AUX

C539

C538

10N

10N

50V

50V

0603

0603

ADC_PCM

CODEC_INT

CLK27M_VADDIS

P597

R509

P503

100R 0603

R510

P505

100R 0603

R511

100R 0603

SMPS_CLK_FAST

I2C_RES*

I2C_SCLK

I2C_SDA

R520

2K0

0603

GND

ADC_BUF_L+

ADC_BUF_L-

ADC_BUF_R+

ADC_BUF_R-

P507

Note about ground pins on CS42528:

The two DGND pins (5 & 52) have about 3.5 Ohms between

them in the device.

The two AGND pins (25 & 40) have several MegOhms

between them and DGND

Conclusion: AGND and DGND appear to be separate within

the chip

C523

10uF

10V

1206

GND

C526

10uF

10V

1206

GND

P528

P529

P530

P531

P532

P533

P534

P535

+3V3(D)

OMCK

R522

47K

GND

0603

RX_LRCLK

RX_SCLK

DAC_PCM0

DAC_PCM1

DAC_PCM2

DAC_PCM3

P537

P506

P568

P567

P569

IC503B

9

Q

P508

8

!Q

74LVC74AD

S0-14

P538

100N

C552

16V 0603

P509

R512

100R 0603

+3V3(D)

P510

R539

2K0

0603

+3V3(D)

10

12

D

SD*

11

CLK

RD*

13

DIV_2_EN

P591

Divide by 2:

RD* = 1 : Running

RD* = 0 : Stop (output Low)

+5V(A)

C504

100N

16V

0603

L500

GND

GND

SO-14

2U2

24

41

VARX

AGND25AGND

40

2 3

1

5 6

4

VA

RMCK

SAI_SDOUT

SAI_LRCK

SAI_SCLK

AOUTA1+

AOUTA1-

AOUTB1+

AOUTB1-

AOUTA2+

AOUTA2-

AOUTB2+

AOUTB2-

AOUTA3+

AOUTA3-

AOUTB3+

AOUTB3-

AOUTA4+

AOUTA4-

AOUTB4+

AOUTB4-

MUTEC

FILT+

REFGND

LPFLT

P512

IC502A

74LVC125AD

SO-14

P513

IC502B

74LVC125AD

C533

10N

50V

0603

C541

100N

16V

0603

TXP

VQ

IC501

CS42528-CQZ

LQFP-64

110R 0603

110R 0603

50

55

54

60

61

36

37

35

34

32

33

31

30

28

29

27

26

22

23

21

20

38

17

18

19

39

NC

R530

R531

+3V3(D)

C532

C503

10N

100N

50V

16V

0603

0603

+3V3(D) +5V(A)

C540

C507

10N

100N

50V

16V

0603

0603

51

49

48

47

46

45

44

43

42

53

59

P550

58

57

56

64

63

62

11

12

10

15

16

14

13

3

2

1

7

8

9

6

180R 0603

VD4VD

RXP0

RXP1/GPO1

RXP2/GPO2

RXP3/GPO3

RXP4/GPO4

RXP5/GPO5

RXP6/GPO6

RXP7/GPO7

VLS

OMCK

ADCIN1

ADCIN2

CX_LRCK

CX_SCLK

CX_SDOUT

CX_SDIN1

CX_SDIN2

CX_SDIN3

CX_SDIN4

INT

RST

SCL/CCLK

SDA/CDOUT

AD1/CDIN

AD0/CS

VLC

AINL+

AINL-

AINR+

AINR-

DGND5DGND

52

Audio master clock frequency for different sample rates

Fs Master clock frequency 24M/22M* 24M_CLK_EN* 12M_CLK_EN*

32kHz 12.288MHz (384 x Fs) 1 1 0

44.1kHz 11.2896MHz (256 x Fs) 0 1 0

48kHz 12.288MHz (256 x Fs) 1 1 0

88.2kHz 22.5792MHz (256 x Fs) 0 0 1

96kHz 24.576MHz (256 x Fs) 1 0 1

176.4kHz 22.5792MHz (128 x Fs) 0 0 1

192kHz 24.576MHz (128 x Fs) 1 0 1

R513

P511

12M_CLK_EN_R*

For sample rates 32-48kHz

32k = 384Fs

44k - 48kHz = 256Fs

P592

24M_CLK_EN_R*

For sample rates above 48kHz

88k - 96kHz = 256Fs

176k - 192kHz = 128Fs

Designator Qty Arcam p/n Description Position / Notes

ITEM500 1 Ferrite Disk - This part is RoHS compliant.F243 Place on top of IC501

ITEM501 2 Pad Damping 7.5x6x3MM RubberE828AP Place one each side of X500

ITEM502 1 Ferrite Disk - This part is RoHS compliant.F243 Place on top of both IC502/IC503 (See assembly drawing)

ITEM503 1 Pad Damping 7.5x6x3MM RubberE828AP Place on top of C527

P539

C505

C524

100N

10uF

16V

10V

0603

1206

GND

C508

C527

470N

220UF

The footprint for this cap is kept at the original small one.

16V

Cap will overhang some SM components.

YXF

GND

R516 110R

0603

R517 33R

0603

R544

P501

47K

0603

P502

NF

GND

DAC_L+

DAC_L-

DAC_R+

DAC_R-

DAC_LS+

DAC_LS-

DAC_RS+

DAC_RS-

DAC_C+

DAC_C-

DAC_SUB+

DAC_SUB-

DAC_2CH_L+

DAC_2CH_L-

DAC_2CH_R+

DAC_2CH_R-

P542 P546

P543

R523

1K5

0603

P545

C544

22N

16V

0603

OMCK

C545

100UF

25V

YK

R524

16K

0603

C514

100N

16V

0603

P544

C547

1N0

100V

0805

NP0

DRAWING TITLE

C548

4U7

50V

YK

P551

GND

Solo Movie Main PCB - CODEC

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB25 9QR

P540

P541

16V

0805

GND

P570

P572

P574

P576

P578

P580

P582

P584

P500

P514

R528

10K

0603

P571

P573

P575

P577

P579

P581

P583

P585

C513

100N

16V

0603

SPDIF_SW To Vaddis 8

RMCK

CODEC DAC output :

0.94 x VA = 4.7V pp differential

= 1.66Vrms differential

150 Ohm output impedance

R525

1K0

0603

TL072CD

SO-8

R540

0R0

0603

GND

SMPS_CLK_FAST

Filename:

Codec.sch

Notes:

Contact Engineer:

84

3

2

IC505B

P547

5

6

TL072CD

SO-8

P548

IC504A

74HC4040D

SO-16

10

CP

11

MR

GND

markt@arcam.co.uk

VAD_DIGOP

DAB_DIGOP

DAB/VAD*

+3V3(D)

IC502E

VCC

GND

74LVC125AD

SO-14

GND

+7V(A)

IC505A

GND

1

GND

-7V(A)

7

P554

R541

1K0

0603

9

Q0

7

Q1

6

Q2

5

Q3

3

Q4

2

Q5

4

Q6

13

Q7

12

Q8

14

Q9

15

Q10

1

Q11

Sync frequency:

32/48/96/192kHz sample rate - 375kHz

44.1/88.2/176.4kHz sample rate - 352.8kHz

Contact Tel:

Ditch the parallel caps and just have the largest value?

14

C509

100N

16V

0603

7

C515

100N

16V

0603

C516

100N

16V

0603

VQ used to bias ADC input signals

VQ (nominal) = 2.7V

Max allowed VQ current = 10uA

Therefore smallest load = 270k Ohms!!!

Use FET input opamp, eg TL072 (cheap)

Low-pass filter output to reduce noise

(Spec is 50nV/RtHz with gain=10 : quite noisey!)

NC

NC

NC

NC

NC

DIV_2^6

NC

NC

R536 100R

NC

NC

NC

NC

07_E084 MJT 11/06/07 None to this sheet. 2.2

07_E045 MJT 07/03/07 None to this sheet. 2.1

07_E014 MJT 01/02/07 No schematic changes. Layout change only (R620, R621 moved) 2. 0

06_E194 MJT 23/01/07 1.0Full production. No changes to this sheet

01223 203210 (direct)Mark Tweedale

01223 203200 (reception)

+5V(D)

R503

10R

0W125

0805

14

7

11

10

14

13

15

GND

C511

100N

16V

0603

-3dB = 159Hz

GND

IC507F

74HC04D

SO-14

DATE

2-Aug-2007

IC500A

1I021Y

3

1I1

5

2I0

6

2I1

3I0

3I1

4I0

4I1

1

S

EN

74HCT157D

SO-16

IC500B

VCC

GND

74HCT157D

SO-16

C549

100N

16V

0603

1213

VAD_DIGOP

DAB_DIGOP

DAB/VAD*

IC503C

VCC

GND

74LVC74AD

S0-14

R526

P552 P553

10K

0603

R515 330R

P555

0603

P557

0603

AJD 25/06/07 3.007_E129 None to this sheet.

ECO No. DESCRIPTION OF CHANGE

INITIALS

Printed:

16

8

C554

10uF

10V

1206

VQ_BUF

2Y

3Y

4Y

+5V(D)

GND

5 11Sheet of

4

P559 P560

7

9

NC

12

NC

C510

100N

16V

0603

IC504B

VCC

GND

74HC4040D

SO-16

R514 330R

0603

C525

10uF

10V

1206

GND

R508

100R

0603

P586

C553

10uF

10V

1206

16

C512

100N

16V

0603

8

GND

SMPS_SYNC

P565

SMPS_SYNC*

P566P556

A2

P558

C506

100N

16V

0603

1

I/P

GND

DAB_DIGOP_SW

+3V3(D)

2

D

3

CLK

GND

C528

10uF

10V

1206

P561

R538

0R0

0603

1 2

3 4

GND

R518

P563

12 11

47K 0603

R519

P564

47K 0603

DRAWING NO.

TX500

2

OC-0805T*001

VCC

GND

3

IC503A

74LVC74AD

4

S0-14

5

Q

SD*

6

!Q

RD*

1

IC507G

14

VCC

7

GND

74HC04D

SO-14

IC507D

89

P562

74HC04D SO-14

IC507A

74HC04D SO-14

IC507B

74HC04D SO-14

IC507E

1011

74HC04D SO-14

IC502D

13

74LVC125AD

SO-14

9 8

IC502C

10

74LVC125AD

SO-14

SMPS_SYNC

SMPS_SYNC*

L998CT

NC

NC

NC

NC

NC

P587

C542

100N

16V

0603

NC

ISSUE

PRE_L

PRE_R

PRE_C

PRE_SUB

PRE_SL

PRE_SR

+7V(A)

C600

100N

16V

0603

84

3

2

-7V(A)

5

6

NF NF

R606

47K

0603

GND

R607

47K

0603

GND

GND

1

C601

100N

16V

0603

7

PRE_REC_L

PRE_REC_R

DAC_2DMIX_L

DAC_2DMIX_R

R604

47R

0603

R608

47R

0603

R600

1K0

0603

R605

1K0

0603

P600

IC604A

NJM2114M

DMP-8

P601

IC604B

NJM2114M

DMP-8

P621

P624

Z2_SEL_PRE

Z2_SEL_2D

Select preamp record out or 2-ch D.Mix

+5V(D)

R620

100K

0603

R621

100K

0603

R627

2R2

0W125

0805

Note:

When headphones are inserted while a

DD5.1 or similar soundtrack is playing,

the 5.1 outputs mute and the preamp

routes the 2chDmix to L/R.

PRE_L

PRE_R

PREAMP_MUTE

P642

P643

R615

0R0 0603

9

R639

0R0 0603

8

1

16

C624

470UF

25V

YK

GND

P607

P608

C636

100UF

10V

YXF

C637

100UF

10V

YXF

1011

NF

IC602C

DG412DY

SO-16

67

NF

IC602B

DG412DY

SO-16

23

NF

IC602A

DG412DY

SO-16

1415

NF

IC602D

DG412DY

SO-16

GND

C602

100N

50V

0805

P640

P641

R640

47K

0603

GND

P604

P605

PREAMP_CLK

PREAMP_DA

PREAMP_MUTE

P606

C628

1UF 50V YK

C629

1UF 50V YK

C627

10UF

50V

YK

SURR_SEL_0

SURR_SEL_1

R641

47R 0603

R642

47R 0603

SCART audio output

R646

47K

goes via mutes on Preamp.sch page

0603

10V

C603

100UF

YXF

10V

C604

100UF

YXF

+7V(A)

R613

10K

0603

Pull-up on SEL to

+7V(A) sets address

for Z2 volume:

D2 = 1

D1 = 1

to use same control

lines as main vol

chip.

P613

C622

33P

50V

NF

0603

P615

P616

P617

C623

33P

50V

NF

0603

P619

R622

1K0

0603

P602

P603

R623

75K

0603

R624

75K

0603

P612

P620

+7V(A)

R601

47K

0603

P609

FIXED_VOL_L

FIXED_VOL_R

Zone 2 volume

May not need in and out coupling caps

Don't think we need these output coupling caps

P610

P611

12

10

HEADPHONE AMP

100mW 20-30 ohms

8

2

3

6

4

5

1

IN1

3

IN2

SEL

8

CL

9

DA

MUTE

DGND

11

GND GND

IC607

1

7

LM4880M

SO-8

NF

R614

1K0

0603

+7V(A)

7

AGND12AGND24AGND3

C625

470UF

25V

YK

C626

470UF

25V

YK

GND

C607

100N

16V

0603

VCC

OUT1

OUT2

VEE

6

5

-7V(A)

P614

R625

2K2

0603

R626

2K2

0603

P618

P622

P623

R603

R602

1K0

1K0

0603

0603

GND

C612

100UF

10V

WL

GND

14

P625

13

P627

IC606

BD3812F

SO-14

GND

C613

C608

100UF

100N

10V

16V

WL

0603

R629

4R7

1W

CF

Note re: Update PCB process and HP_OUT_L and

HP_OUT_R

For some reason, the update PCB process has always

wanted to disconnect and then re-connect these two

nets. I cannot find the cause for this oddity, however

ignoring it seems to be the right thing to do!

(Mark T 08/12/06)

R630

4R7

1W

CF

R643

47R 0603

R644

47R 0603

HP_OUT_L

HP_OUT_R

GND

To Power Amps --------------------- To Pre-out Phonos ---------------------

PWR_AMP_L

PWR_AMP_R

PWR_AMP_C

PWR_AMP_SL

+7V(A)

14

4

X0

V+

5

X1

6

X2

7

X3

13

Y1

12

Y2

11

Y3

10

Y4

2

EN

1

A0

16

A1

15

GND

P644

P645

-7V(A)

COMX

COMY

V-

3

GND

8

9

IC605

DG409DY

SO-16

IN0: Default - mute on power up

IN1: Biamp mode - LS amp = L, RS amp = R

IN2: Zone2 amps - LS amp = Z2 L, RS amp = Z2 R

IN3: Normal 5.1 - LS amp = LS, RS amp = RS

Note: want Normal 5.1 on IN3 as this has the worst

non-selected X-talk to the output as this input pin is

closest to the output pin.

C609

100N

16V

0603

C610

100N

16V

0603

R647

1M0

0W063

0603

NC

NC

D600

BAT54S

SOT-23

C630

100UF

25V

YK

D601

BAT54S

SOT-23

PREOUT_MUTE*

P629

P630

+7V(A)

-7V(A)

+7V_MUTES

R645

1M0

0603

-7V_MUTES

67

IC600B

DG412DY

PREOUT_MUTE*

PREOUT_MUTE*

PREOUT_MUTE*

PREOUT_MUTE_Z2*

+5V(SW) currents:

Zenner = (7-5.1) / 620 = 3mA

P631

+5V(SW)

QTY DESCRIPTIONPART No. NOTESITEM

DG412 = 5 x 5uA max

Resistor Pd @ 3mA= 5.6mW

C611

100N

16V

0603

+7V(A)

R628

620R

0W125

0805

DZ600

BZX84C

5V1

SOT-23

GND

ITEM600 1 4.1m m I/D, 7.3mm O/D O-RingF275 Place over C630, halfway down.

DRAWING TITLE

8

SO-16

23

IC600A

DG412DY

1

SO-16

1415

IC600D

DG412DY

16

SO-16

1011

IC600C

DG412DY

9

SO-16

67

IC601B

DG412DY

8

SO-16

23

IC601A

DG412DY

1

SO-16

1415

IC601D

DG412DY

16

SO-16

1011

IC601C

DG412DY

9

SO-16

P633

P634

P635

P636

P637

P638

P639

47R

0603

R632

47R

0603

R633

47R

0603

R634

47R

0603

R635

47R

0603

R636

47R

0603

R637

47R

0603

R638

47R

0603

IC600E

DG412DY

SO-16

V+

VL

GND

V-

R631

P632

Solo Movie Main PCB - Audio Switch & Mute

Filename:

Audio switch and mute.sch

A & R Cambridge Ltd.

Pembroke Avenue

Waterbeach

Cambridge CB25 9QR

Notes:

Contact Engineer:

markt@arcam.co.uk

Contact Tel:

C632

C633

C634

C631

100P

100P

50V

0603

NP0

C614

470P

50V

0603

C618

470P

50V

0603

+7V_MUTES

13

+5V(SW)

12

5

GND

4

-7V_MUTES

07_E084 MJT 11/06/07 None to this sheet. 2.2

07_E045 MJT 07/03/07 None to this sheet. 2.1

07_E014 MJT 01/02/07 No schematic changes. Layout change only (R620, R621 moved) 2. 0

06_E194 MJT 23/01/07 1.0Full production. R647 added to PCB

ECO No. DESCRIPTION OF CHANGE

01223 203210 (direct)Mark Tweedale

01223 203200 (reception)

100P

50V

50V

0603

0603

NP0

NP0

R609

47K

0603

R616

47K

0603

R610

C615

47K

470P

0603

50V

0603

GND

R617

C619

47K

470P

0603

50V

0603

GND

IC601E

13

V+

12

VL

5

GND

4

V-

DG412DY

SO-16

AJD 25/06/07 3.007_E129 None to this sheet.

DATE

INITIALS

2-Aug-2007

Printed:

100P

50V

0603

NP0

GND

C616

470P

50V

0603

C620

470P

50V

0603

+7V_MUTES

+5V(SW)

GND

-7V_MUTES

C635

100P

50V

0603

NP0

R611

47K

0603

R618

47K

0603

6 11Sheet of

PWR_AMP_SR

PRE_OUT_L

PRE_OUT_R

PRE_OUT_C

PRE_OUT_SUB

R612

C617

47K

470P

0603

50V

0603

PRE_OUT_SL

PRE_OUT_SR

Z2_OUT_L

Zone2 / Record

Z2_OUT_R

R619

C621

47K

470P

0603

50V

0603

+7V_MUTES

NF

IC602E

13

V+

+5V(SW)

12

VL

5

GND

4

V-

DG412DY

SO-16

-7V_MUTES

A2

GND

DRAWING NO.

via FFC

NOTE: No clamp diodes to rail.

ISSUE

L998CT

FM/AM MODULE INTERFACE (Kwang Sung Module)

+12V(D)

RDS_DATA

RDS_CLK

DGND

PLL_DO

PLL_CLK

PLL_DI

PLL_CE

R_OUT

GND

L_OUT

VCC

STEREO

TUNED

CON700

MOLEX

52045

PLL_CLK

PLL_DI

PLL_CE

I2CDAB_SDA

I2CDAB_SCLK

I2CDAB_RES*

1

2

3

4

5

6

7

8

9

10

11

12

13

GND

P721

C701

100N

16V

0603

RDS_DATA

RDS_CLK

PLL_DO

PLL_CLK

PLL_DI

PLL_CE

TUN_R

TUN_GND

TUN_L

STEREO

TUNED

C700

100N

16V

0603

R716

10R

0603

GND

P700

P702

P704

P706

P708

P701

P703

P705

P707

R700

68K

0603

+3V3(STBY)

P709

R701

68K

0603

R702

47K

0603

P710

R703

47K

0603

GNDGNDGNDGND

R704

47K

0603