Page 1

APPLE INC.

6

DESIGNER

DESCRIPTION OF CHANGE

REV.

A

D

C

B

A

D

C

B

8 7

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

TITLE

DRAWING NUMBER

SHT

OF

METRIC

DRAFTER

ENG APPD

QA APPD

RELEASE

DESIGN CK

MFG APPD

SCALE

NONE

MATERIAL/FINISH

NOTED AS

APPLICABLE

SIZE

D

THIRD ANGLE PROJECTION

DIMENSIONS ARE IN MILLIMETERS

XX

X.XX

X.XXX

DO NOT SCALE DRAWING

REV

ZONE

ECN

CK

APPD

DATE

ENG

APPD

DATE

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

ANGLES

TABLE_TABLEOFCONTENTS_HEAD

TABLE_TABLEOFCONTENTS_ITEM TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEAD

DRAWING

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEAD

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

SCHEM,MLB,MBP17

12/18/2007

PVT

521911

Schematic / PCB #’s

ALIASES RESOLVED

SMC

45

49

M87_MLB

08/28/2007

Left Clutch Barrel Interconnect

44

47

M87_MLB

08/28/2007

External USB Connector

43

46

MASTER

MASTER

PATA Connector

42

44

MASTER

MASTER

FireWire Ports

41

43

M87_MLB

08/28/2007

FireWire Port Power

40

42

M87_MLB

08/28/2007

FireWire PHY (TSB83AA22)

39

41

M87_MLB

08/28/2007

FireWire Link (TSB83AA22)

38

40

M87_MLB

08/28/2007

Ethernet Connector

37

39

M87_MLB

08/28/2007

Yukon Power Control

36

38

T9_NOME

03/19/2007

Ethernet (Yukon)

35

37

T9_NOME

01/25/2007

Left I/O Board Connector

34

34

(MASTER)

(MASTER)

Memory Active Termination

33

33

(MASTER)

(MASTER)

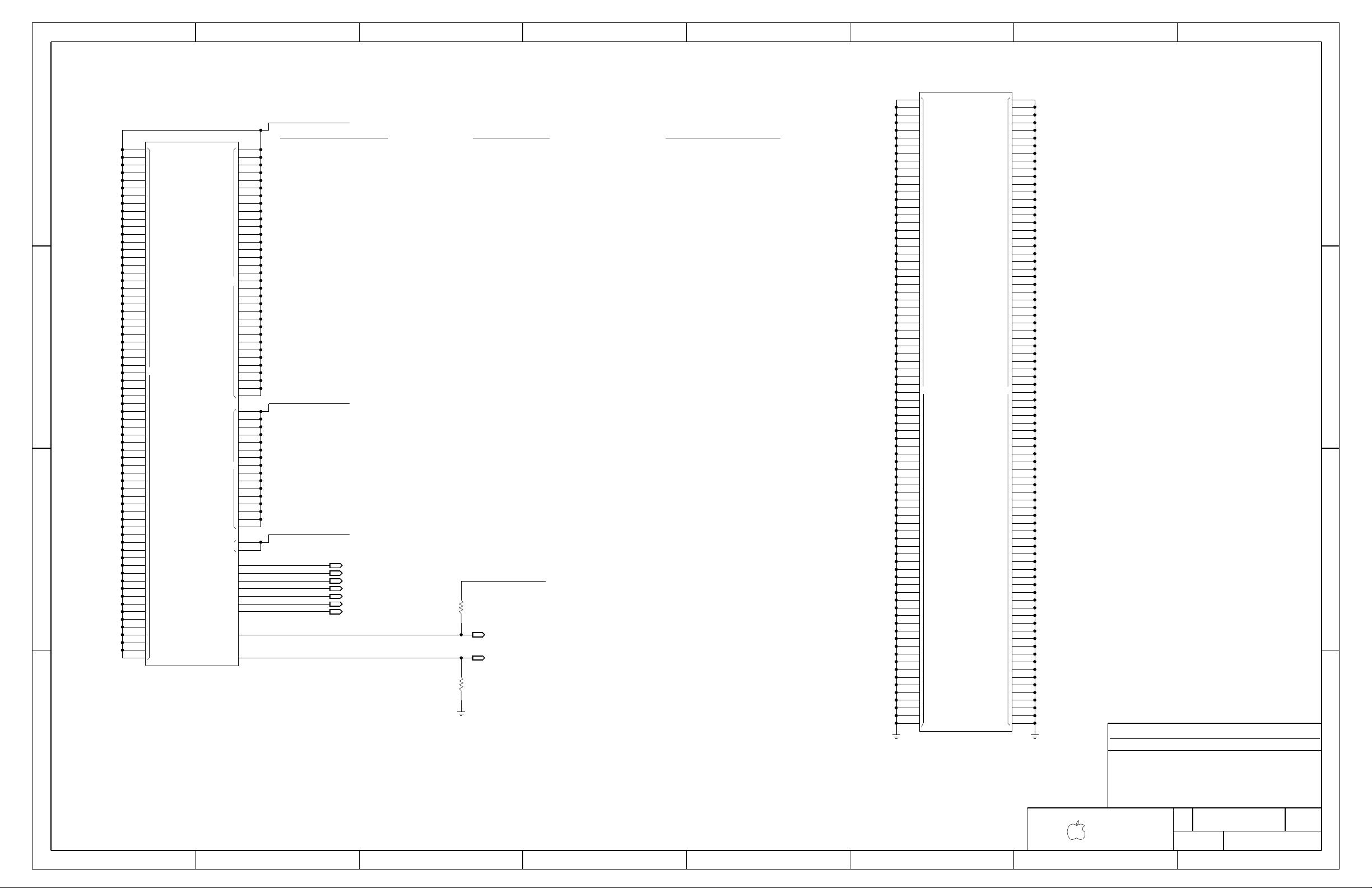

DDR2 SO-DIMM Connector B

32

32

M87_MLB

08/28/2007

DDR2 SO-DIMM Connector A

31

31

M87_MLB

08/28/2007

Clock Termination

30

30

M87_MLB

08/28/2007

Clock (CK505)

29

29

T9_NOME

01/25/2007

SB Misc

28

28

M87_MLB

08/28/2007

SB Decoupling

27

27

MASTER

MASTER

SB Power & Ground

26

26

T9_NOME

01/25/2007

SB Pwr Mgt, GPIO, Clink

25

25

M87_MLB

08/28/2007

SB PCI, PCIe, DMI, USB

24

24

M87_MLB

08/28/2007

SB Enet, Disk, FSB, LPC

23

23

T9_NOME

01/25/2007

NB Graphics Decoupling

22

22

M87_MLB

08/28/2007

NB Standard Decoupling

21

21

MASTER

MASTER

NB Grounds

20

20

T9_NOME

01/25/2007

NB Power 2

19

19

T9_NOME

01/25/2007

NB Power 1

18

18

T9_NOME

01/25/2007

NB DDR2 Interfaces

17

17

T9_NOME

01/25/2007

NB Misc Interfaces

16

16

T9_NOME

01/25/2007

NB PEG / Video Interfaces

15

15

T9_NOME

03/19/2007

NB CPU Interface

14

14

T9_NOME

01/25/2007

eXtended Debug Port (XDP)

13

13

T9_NOME

01/22/2007

CPU Decoupling & VID

12

12

M87_MLB

08/28/2007

CPU Power & Ground

11

11

M87_MLB

08/28/2007

CPU FSB

10

10

M87_MLB

08/28/2007

Signal Aliases

9

9

MASTER

MASTER

Power Aliases

8

8

(MASTER)

(MASTER)

Functional / ICT Test

7

7

MASTER

MASTER

Revision History

6

6

N/A

N/A

BOM Configuration

5

5

N/A

N/A

Power Block Diagram

4

4

N/A

N/A

Power Block Diagram

3

3

(MASTER)

(MASTER)

System Block Diagram

2

2

(MASTER)

(MASTER)

106

01/25/2007

T9_NOME

FireWire Constraints

89

105

08/28/2007

M87_MLB

Clock & SMC Constraints

88

104

01/25/2007

T9_NOME

SB Constraints (2 of 2)

87

103

01/25/2007

T9_NOME

SB Constraints (1 of 2)

86

102

01/25/2007

T9_NOME

Memory Constraints

85

101

01/25/2007

T9_NOME

NB Constraints

84

100

01/25/2007

T9_NOME

CPU/FSB Constraints

83

98

12/06/2007

M87_LIO

LCD Backlight Support

82

96

(MASTER)

(MASTER)

Project Specific Connectors

81

94

MASTER

MASTER

DVI Display Connector

80

93

MASTER

MASTER

1.8V FB Power Supply

79

92

08/28/2007

M87_MLB

GDDR3 Frame Buffer B (Bot)

78

91

08/28/2007

M87_MLB

GDDR3 Frame Buffer A (Bot)

77

90

MASTER

MASTER

LVDS Display Connector

76

89

09/26/2007

M87_MLB

GPU (G84M) Core Supply

75

88

08/28/2007

M87_MLB

NV G84M Video Interfaces

74

87

08/28/2007

M87_MLB

GPU Straps

73

86

08/28/2007

M87_MLB

NV G84M GPIO/MIO/Misc

72

85

08/28/2007

M87_MLB

GDDR3 Frame Buffer B (Top)

71

84

08/28/2007

M87_MLB

GDDR3 Frame Buffer A (Top)

70

82

08/28/2007

M87_MLB

NV G84M Frame Buffer I/F

69

81

08/28/2007

M87_MLB

NV G84M Core/FB Power

68

80

08/28/2007

M87_MLB

NV G84M PCI-E

67

79

MASTER

MASTER

PBus Supply & Batt. Charger

66

78

09/26/2007

M87_MLB

3.425V G3Hot Supply & Power Control

65

77

08/28/2007

M87_MLB

FW PHY Power Supplies

64

76

MASTER

MASTER

1.5V Power Supply

63

75

08/28/2007

M87_MLB

1.8V DDR2 Supply

62

74

08/28/2007

M87_MLB

1.25V / 1.05V Power Supply

61

73

MASTER

MASTER

5V / 3.3V Power Supply

60

71

MASTER

MASTER

IMVP6 CPU VCore Regulator

59

70

08/28/2007

M87_MLB

Power FETs

58

69

(MASTER)

(MASTER)

DC-In & Battery Connectors

57

61

01/25/2007

T9_NOME

SPI BootROM

56

59

08/28/2007

M87_MLB

Sudden Motion Sensor (SMS)

55

58

08/28/2007

M87_MLB

ALS Support

54

57

11/06/2007

M87_LIO

Current & Thermal Sensors

53

56

08/28/2007

M87_MLB

Fan Connectors

52

55

08/28/2007

M87_MLB

Thermal Sensors

51

54

MASTER

MASTER

Current Sensing

50

53

08/28/2007

M87_MLB

Current & Voltage Sensing

49

52

(MASTER)

(MASTER)

SMBus Connections

48

51

08/28/2007

M87_MLB

LPC+ Debug Connector

47

92

PCB Rule Definitions

M87_MLB

10/03/2007

109

91

Project Specific Constraints

M87_MLB

08/28/2007

108

Contents

(.csa)

Sync

Date

Page

Table of Contents

1

1

N/A

N/A

1

PCB

CRITICAL820-2262

PCBF,MLB,MBP17

TITLE=MLB

ABBREV=DRAWING

LAST_MODIFIED=Tue Dec 18 15:43:01 2007

Date

Page Contents Sync

(.csa)

90

GPU (G84M) Constraints

M87_MLB

10/02/2007

107

CRITICAL051-7431

SCH

1

SCHEM,MLB,MBP17

50

10/15/2007

M87_MLB

SMC Support

46

(.csa)

Sync

Date

Page Contents

92

1

0.1

? ?

Proto Release

051-7431

A.0.0

SCHEM,MLB,MBP17

Page 2

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

DRAWING NUMBER

SHT

OF

SIZE

D

PG 66

PG 81PG 81

PG 81

J9610

CLK CHIP

DIMM’s

100 MHz

PG 81

PG 80

PG 67

PG 74

PG 74

PG 69

1.26V - 1.05V

GDDR3 FRAME BUFFER A/B (BOT)

U9100,U9150,U9200,U9250

PG 77,78

GDDR3 FRAME BUFFER A/B (TOP)

PG 71,72

U8400,U8450,U8500,U8550

Core 1.05V

J4300

Conn

FireWire

TSB83AA22

LVDS DISP

DVI-INTERFACE

VIDEO INTERFACES

DVI DISPLAY CONN

NV G84M FRAME BUFFER I/F

NV G84M

Core

PCI-EBUS INTERFACE

PG 23

CAMERA

PG 44

LEFT CLUTCH BARREL INTERCONN

Supply

Power

U5570

Pg 51

Pg 51

U5500

Temp Sense

PG 54

ALS SENS

J6990/50

DC/Batt

U5805

CPU

GPU

Conn

PG 57

PG 30

TERMSClocks

PG 29

CK 505

U2900

J3200

J3100

DIMM

PG31,32

DDR2 - Dual Channel

1.8V - 64 Bits

533/667/800? MHz

U1000

CPU

PG 13

J1300

PG 16/17

Main Memory

2.? GHz

PG 10

Core ~1.2V

PG 11,12

FSB

64-Bit

Core

1.05 - 1.25V

NB-GMCH

PG 14

TV

PCI-E

U1400

U5550 Pg 51

Right Side

LPC Conn

PG 47

J5100

PG 44

WWAN

J4731

Geyser

Trackpad/Keyboard

J9600

U5900

PG 55

PG 52

FAN CONN

POWER SENSE PG 49-50

J5650/60

SUDDEN MOTION SENSOR

Ser

Prt

FanADC

Pg 46

SMC

BSBB,0 BSA

U4900

A

Bluetooth

J9660

IR

LEFT I/O

J3400

U2900

SPI

PG 56

Boot ROM

USB

J4600

PG 43

EXT-A

CONN

PG 25

GPIOs

LPC

0

2 14 3

USB

5

PG 24

7 69 8

U6100

Misc

CLnk 0

PG 16

PG 16PG 16

DMI

PG 18~22

x4 DMI

2.5 GHz

DMI SPI

CLnk 0

PG 25

PG 24

SB-ICH8

U2300

SATA

PG 23

IDE

PG 23

PCI-E

PG 24

J3200

J3100

PG 25

AZALIA

PG 23

TSB83BA22

FW-Link

U4000

32-Bit

33 MHz

Pg 38

Pg 39

FW-PHY

J4310

Pg 41

PCI

PG 24PG 25

CLnk 1

PG 23

Pg 25

Core

E-NET

ETHERNET

Pg 35

(YUKON ULTRA)

J3900

U3700

E-NET

Pg 37

Conn

Pg 59

Audio

Codec

U6200

PG 15

RGB LVDS

800/1066? MHz

PG 15

LIO BOARD

Mini PCI-E

AirPort

Out

x16 PCI-E

SDVO

U8000

J9400

SATA-2SATA-1 Ln1 Ln3Ln2

1.2 V / 1.5 GHz

3.3 V

PG 77

J9000/10

Conn

PATA

Pg 42

Conn

Conn

J4400

J9660

SATA

Ln4 Ln5 Ln6

3 - X1

2.5 GHz

PG 34

EXT-B

CONNS

USB

EXT-C

PG 34

EXPRESS CARD

PG 34

PG 24

SATA-0

ITP/XDP CONN

8-Bit

U4000

100 MHz

SMB

SYNC_DATE=(MASTER)

SYNC_MASTER=(MASTER)

System Block Diagram

051-7431

2

92

A.0.0

Page 3

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

DRAWING NUMBER

SHT

OF

SIZE

D

M88 POWER SYSTEM ARCHITECTURE

PM_SLP_S3_DELAY_L

P3V3S3_SS

(12A MAX CURRENT)

VOUT2

CURRENT)

PP0V9_S0

(10mA MAX CURRENT)

PP1V8_S3_ISNS

(10A MAX CURRENT)

PP1V8_S0GPU

P1V25S0_SS

Q7095

PP1V25_ENET

PP1V8_S3

(5.5A MAX)

PP3V3_S5

(8A MAX CURRENT)

PP5V_S5

CHGR_EN

LIO_DCIN_ISENSE

A

U5705

INRUSH LIMITER

(PAGE 57)

Q7970

VIN

U5495

SMC_GPU_VSENSE

(PAGE 61)

U7450

U5420

NBCORE_IOUT

PWRBTN*

PLT_RST_L

CPU_PWRGD

CPUPWRGD(GPIO49)

CLPWROK

P1V8P1V5P1V05S0_PGOOD

SIGNAL DELAY TIME

99ms

200ms

STEP 06 (S5 POWER STATUS)TRUTH TABLE

L(S5 OFF)

ACIN WITH/WITHOUT BATTERY

BATTERY ONLY,PRESS PWR BUTTON

(UNUSED)

TP1V25ENET_PGOOD

(PAGE 61)

U7400

TPS51117

VIN

1V8S3_PGOOD

(PAGE 62)

U7500

1.8V

0.9V

VOUT1

RSMRST_PWRGD

GPUVCORE_IOUT

VOUT

PPVBAT_G3H_CHGR_OUT

BATTERY CHARGE

SMC_ADAPTER_EN

SMC_BC_ACOK

PP18V5_G3H_CHGR

U7859

U7858

P3V3GPU_SS

PP3V3_S0

PP1V9_ENET

V4(1.25V)

V2(3.3V)

V1(5V)

S0PGOOD_PWROK

V3(1.8V)

LTC2900

(PAGE 66)

U7870

RST*

Q7020

VIN

VOUT

TP_P1V8_S0GPU_PGOOD

(UNUSED)

Q4260

FWPWR_EN_L_DIV

PPBUS_FW_FWPWRSW_F

ISL6269

U9300

(PAGE 79)

PGOOD

EN

VOUT

PGOOD

EN_PSV

PM_ENET_EN

P1V8_S3_IOUT

VOUT2

VOUT

EN

PP1V25_S0

Q7010

PP3V3_GPU

PP5V_S5

Q3810

Q7030

IN

(PAGE 36)

TPS79501

U3850

01,05-09

ALL_SYS_PWRGD

MCH

POWER ON SEQUENCE LIST

PPVIN_FW_3V3FW

1.5A FUSE

(PAGE 64)

TPS799195

(PAGE 64)

VIN

Q4261

Q3801

Q7850

Q3801

U5440

P1V8S3_EN

PM_S4_STATE_L

C=0.47UF

A

R=10K

DELAY

P3V3S3_SS

PP5V_S0

(PAGE 60)

TPS51120

EN2

PGOOD

PP3V42_G3H

SMC_PM_G2_EN

EN2

P5VS3_SS

C=68NF

R=47K

DELAY

EN1

3.3V

EN2

5V

VIN

VOUT1

PM_SLP_S3_L

PGOOD

Q7012

SLP_S3*

Q7851

U2300

S4_STATE*

ICH8M

VR_PWRGD_CLKEN_L

P5VS3_SS

P5VS0_SS

V

EN_PSV

PM_GPUVCORE_EN

A

PPBUS_G3H

ISL9504

CPUVCORE

U7100

VOUT

VIN

VR_ON

A

(PAGE 66)

FET

PBUS SUPPLY /

BATTERY CHARGER

U7900

(PAGE 66)

PGOOD

(44A MAX CURRENT)

PPVCORE_SO_CPU

V

SMC_CPU_VSENSE

CPUVCORE_IOUT

U5400

CLKEN#

(PAGE 59)

BATTERY ONLY:

ADAPTER IN :

PM_S4_STATE_L

PM_SLP_S4_L(P94)

PM_SLP_S5_L(P95)

P17(BTN_OUT)

PLT_RST*

IMVP_VR_ON(P16)

99ms DLY

RSMRST_OUT(P15)

U1400

(PAGE 63)

PPVCORE_S0_NB_R

U7880

P1V8S3_PGOOD

PP1V5_S0

TPS51117

PM_SLP_S3_DELAY_L

PGOOD

1.5V

EN_PSV

(PAGE 65)

Q6950

PPVBATT_G3H_FET_F

BATT_POS

518S0457

J6950

87438-1043

CRITICAL

PPVBATT_G3H_FET

8A FUSE

A

VR_PWRGOOD_DELAY

PM_SB_PWROK

U2840

SHDN*

VIN

PBUS_LDO_EN

Energy Star LDO

(PAGE 66)

U7950

MAX8719

VOUT

ISL6257

VOUT

VIN

ENABLES

VIN

VOUT

PP5V_S3

Q7000

IMVP_VR_ON

87438-0832

CRITICAL

PP18V5_DCIN

J6990

27.11UF

H(S5 ON)

518S0456

Q7096

Q7096

C=1UF

R=100K

DELAY

P1V25S0_SS

Q7002

S3_VTT_EN

VIN

EN

SHDN*

U7700

VOUT

U7720

VOUT

PP3V3_FW

PP1V95_FW

4.2UF

(0.2A MAX CURRENT)

PLATFORM,CPU RESET

BATTERY ONLY

NO AC/BATTERY

S0 CPU POWER ON

VR_PWRGOOD_DELAY

S0PWRGD_OK

S0 SYSTEM POWER ON

S3 POWER ON

S5 POWER ON

G3H POWER ON

PWR/RST STATUS

7ms

STEP

H(S5 ON)

14-18

17,19-24

25-27

L(S5 OFF)

01-04

10-13

PM_SLP_S5_L

PM_SLP_S3_L

08-1

05

PM_SLP_S3_L(P93)

U4900

(PAGE 45)

RST*

PWR_BUTTON(P90)

U2830

VR_PWRGD_CLKEN

RSMRST_PWRGD

SMC_ONOFF_L

RSMRST_IN(P13)

PWRGD(P12)

PWROK

SMC

RESET*

HCPURST*

U1000

PWROK

VRMPWRGD

CPU

PWRGOOD

RSMRST*

PLTRST*

SMC_PBUS_VSENSE

VIN

U7600

VOUT

V

Q5315

EN_PSV

VIN

TPS51117

1.05V

VOUT

PGOOD

SHDN*

VIN

3.425V"G3HOT"

LT3470

U7800

VOUT

SMC RESET "BUTTON"

(PAGE 46)

(0.2A MAX CURRENT)

RN5VD30A-F

PP3V42_G3H

PP1V05_S0

U5000

VOUT

SMC_RESET_L

(10A MAX CURRENT)

FSB_CPURST_L

IMVP_VR_ON

PM_RSMRST_L

PM_PWRBTN_L

10

28

26

27

PPDCIN_G3H

P3V3S0_SS

Q7070

(4.5A MAX CURRENT)

GPUVCORE_PGOOD

GPUVCORE_PGOOD

U2300

ICH8M

A

IMVP_VR_ON

U7300

(18A MAX CURRENT)

PGOOD

Q7850

SMC_ADAPTER_EN

P1V8S3_EN

PM_GPUVCORE_EN

DELAY

Q7002

P5VS0_SS

P3V3S0_SS

R=47K

C=68NF

R=100K

DELAY

C=33NF

Q7012

PM_P1V8_S0GPU_EN

PM_SLP_S3_LS5V

Q7851

C=33NF

R=100K

DELAY

DELAY

PP3V3_S5

PPVCORE_GPU

U7850

PP3V3_S5

PP3V3_ENET

P3V3ENET_SS

PM_P1V8_S0GPU_EN

WOL_EN

P3V3ENET_SS

PM_SLP_S3_L

S5_EN

TPS511160

(6A MAX CURRENT)

LT3470

P1V8_S0GPU_IOUT

A

PPVP_FW

P3V3GPU_SS

R=100K

DELAY

C=1UF

Q7072

PM_P3V3GPU_EN

RST*

(PAGE 65)

U7860

MAX6838

VCC

RSTIN

PP3V3_S3

A

P1V25_S0_IOUT

PP1V25_S0_ISNS

VIN

PM_SLP_S3_DELAY_L

C=33NF

R=100K

Q3800

FWPWR_EN_L_DIV

PM_ENET_EN

U5410

PP1V8_S0GPU_ISNS

U5430

(PAGE 75)

U8900

ISL6263B

LIO_BATT_ISENSE

U5715

SYNC_DATE=(MASTER)

Power Block Diagram

051-7431

A.0.0

92

3

SYNC_MASTER=(MASTER)

Page 4

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

DRAWING NUMBER

SHT

OF

SIZE

D

Power Block Diagram

051-7431

A.0.0

92

4

SYNC_MASTER=N/A

SYNC_DATE=N/A

Page 5

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

BOM OPTIONS

BOM NAME

BOM NUMBER

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

TABLE_ALT_ITEM

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

DESCRIPTION

REFERENCE DES

BOM OPTION

QTY

PART NUMBER

CRITICAL

TABLE_BOMGROUP_ITEM

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

DRAWING NUMBER

SHT

OF

SIZE

D

Alternate Parts

BOM Variants

BOM Groups

Module Parts

Bar Code Labels / EEE #’s

SYNC_DATE=N/A

92

A.0.0

051-7431

5

BOM Configuration

SYNC_MASTER=N/A

VRAM8,VRAM_16M,VRAM_SAMSUNG,VRAM_512_SAMSUNG

FB_512_SAMSUNG

CRITICAL826-4393

1

[EEE:Z3K]

EEE_Z3K

LBL,P/N LABEL,PCB,28MM X 6 MM

EEE_ZVX

[EEE:ZVX]

826-4393

1

CRITICAL

LBL,P/N LABEL,PCB,28MM X 6 MM

CRITICAL338S0509

1

U8000

IC,GPU,NV,G84M,BGA

338S0434

1

CRITICAL

U2300

IC,SB,ICH8M,B1,PRQ,BGA

353S1651

1

ISL9504BCRITICAL

U7100

IC,ISL9504B,2PH IMVP6 REG,PMON,QFN48

1

359S0130

U2900

CRITICAL

IC,SLG2AP101,LW PWR CLK GEN,CK505,QFN68

CRITICAL

SMC_BLANK

338S0274

1

U4900

IC,SMC,HS8/2116

CRITICAL341S2194

U4900

1

SMC_PROG

IC,SMC,DEVELOPMENT,M88

U6100

341S2192

BOOTROM_PROG

1

CRITICAL

IC,EFI ROM,DEVELOPMENT,M87

IC,SGRAM,GDDR3,16MX32,800MHZ,136 FBGA

U8400,U8450,U8500,U8550,U9100,U9150,U9200,U9250

333S0423

8

CRITICAL

VRAM_512_SAMSUNG

333S0424

U8400,U8450,U8500,U8550

4

IC,SGRAM,GDDR3,16MX32,900MHZ,136 FBGA

VRAM_256_HYNIX

CRITICAL

IC,SGRAM,GDDR3,16MX32,900MHZ,136 FBGA

333S0424

U8400,U8450,U8500,U8550,U9100,U9150,U9200,U9250

CRITICAL

8

VRAM_512_HYNIX

ALL

376S0445376S0448

Si7806ADN for FSM6296

CRITICAL

1

338S0432

U1400

IC,NB,CRESTLINE,GM,C0,PRQ,ROHS-SPECIAL,965PM

337S3559

IC,PDC,SR,PRQ,2.6G,35W,800FSB,6M,BGA

1

CRITICAL

CPU_2_6GHZ

U1000

337S3560

IC,PDC,SR,PRQ,2.5G,35W,800FSB,6M,BGA

U1000

CRITICAL

1

CPU_2_5GHZ

P1V8S3_1V8,SMS_MOT_DIS,YUKON_ULTRA,VGA_TERM_CONN

M88_COMMON2

U8400,U8450,U8500,U8550

4

333S0423

VRAM_256_SAMSUNG

IC,SGRAM,GDDR3,16MX32,800MHZ,136 FBGA

CRITICAL

U6100

335S0384 CRITICAL

BOOTROM_BLANK

1

IC,16MBIT 8-PIN SPI SERIAL FLASH,SOIC8

[EEE:ZVW]

1

826-4393 CRITICAL

EEE_ZVW

LBL,P/N LABEL,PCB,28MM X 6 MM

1

826-4393

[EEE:Z3L]

EEE_Z3L

CRITICAL

LBL,P/N LABEL,PCB,28MM X 6 MM

FB_256_SAMSUNG

VRAM4,VRAM_16M,VRAM_SAMSUNG,VRAM_256_SAMSUNG

PCBA,2.6GHZ,512VRAM-HY,M88

630-9092

M88_COMMON,CPU_2_6GHZ,FB_512_HYNIX,EEE_Z3K

PCBA,2.5GHZ,512VRAM-HY,M88

630-9225

M88_COMMON,CPU_2_5GHZ,FB_512_HYNIX,EEE_ZVW

1

338S0386

U3700

CRITICAL

IC,88E8058,GIGABIT ENET XCVR,64P QFN

VRAM8,VRAM_16M,VRAM_HYNIX,VRAM_512_HYNIX

FB_512_HYNIX

VRAM4,VRAM_16M,VRAM_HYNIX,VRAM_256_HYNIX

FB_256_HYNIX

M88_PROGPARTS

BOOTROM_PROG,SMC_PROG

SMC_DEBUG_NO,XDP,LPCPLUS

M88_DEBUG

M88_COMMON1

BKLT_5V_PWR,ISL9504B,ONEWIRE_PU,GPUVID_1P23V

M88_COMMON

COMMON,ALTERNATE,M88_COMMON1,M88_COMMON2,M88_DEBUG,M88_PROGPARTS

PCBA,2.5GHZ,512VRAM-SAM,M88

630-9228

M88_COMMON,CPU_2_5GHZ,FB_512_SAMSUNG,EEE_ZVX

PCBA,2.6GHZ,512VRAM-SAM,M88

630-9093

M88_COMMON,CPU_2_6GHZ,FB_512_SAMSUNG,EEE_Z3L

157S0030157S0011

E&E alt to TDK/BiTech magnetics

ALL

138S0602138S0603

Murata alt to Samsung 22uF acoustic caps

ALL

TI alternate to National

353S1294353S1681

ALL

ALL

376S0466

AOS alternate to Siliconix Si4413

376S0543

152S0276152S0683

ALL

Mag Layers alternate to Dale/Vishay

104S0017104S0024

ALL

Panasonic alternate to Cyntec

128S0175

alternate to Halogen free Sanyo 330uf D3 tant

ALL

128S0056

128S0147

alternate to Halogen free Sanyo 100uF tant

ALL

128S0057

128S0157

alternate to Halogen free Sanyo 220uF 15 mohm tant

128S0122

ALL

alternate to halogen free Sanyo 150uF tant

128S0150128S0115

ALL

alternate to halogen free Sanyo 220uF 35 mohm tant

128S0160128S0113

ALL

alternate to halogen free Sanyo 330uF C2 tant

ALL

128S0083 128S0165

Page 6

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

DRAWING NUMBER

SHT

OF

SIZE

D

11/06/07 --

Page 25: Removed NO STUFF BOM option from R2552, pull up on SB GPIO38.

12/12/07 --

12/12/07 --

18.0.0:

pg. 82 Changed C9805 to 2.2uF for LED power sequencing.

08/10/07 -- Page 65: Changed L7810 3.425V G3 Hot inductor to 152S0301. R7070 changed from 100K to 10K.

08/17/07 -- Page 48: Changed SMBus SMC "A" pull ups R5270 and R5271 to 3.3K to improve rise time on SCL..

08/03/07 -- Page 5: Removed Q4690 BOM table entry. BOM table is on CSA pg. 46

08/10/07 -- Synced to M87 MLB label 4.3.0

08/10/07 -- Page 3: Revised power block diagram.

08/10/07 -- Page 37: T3900,T3901 magnetics changed to 157S0053.

Removed R3410 and R3411.

Added GPIOs to support iPhone headset.

08/14/07 -- Synced to M87 MLB label 5.1.0

08/16/07 -- Removed Rev B Silego clock chip as alternate.

08/16/07 -- Page 51: Temp Sensors: Changed U5500 and U5570 to EMC1043-1 APN 353S1947.

Page. 9,34:

Page. 9,34:

7.1.0:

08/22/07 --

5.0.0:

6.2.0:

6.0.0 & 5.1.0:

6.1.0:

7.0.0:

08/22/07 --

Changed R5413 and R5443 to 0.005 ohm resistors.

Changed L7100 and L7101 to 152S0624.

Page 50: Adding C5411,C5412,C5441,C5442 feedback caps for current sense op amps

Page 66: Changed R7920 to halogen free 107S0110.

Changed R5491 and R5493 to 6.81K to allow full resolution of GPUVCORE current sense

Page 61: R7455 changed to 7.5K to change max load current margin on PP1V05.

Page 9: IPHS_SW_BIAS_EN_L now connected to SB_SLOAD (GPIO 38).

Page 91: Added diff pair properties to new current sensor pairs.

Page 59: CPU Vcore supply changes per characterization.

Page 5,75: Changed BOM option to GPUVID_1P23V

Page 51: Temp sensors: Added R5501,R5502,R5571,R5572 pull ups on U5500 and U5570.

Page 82: Changed L9891,L9893,L9894 to 155S0220

Page 50: Current Sensors: Changed U5410 and U5440 to MAX4245

Page 66: Changed U7901 to MAX4245. Changed F7902 to 740S0055.

Page 25: Added NO STUFF to R2552 (was pull up on SB GPIO38 which is now used on IPHS).

Page 90: Changed frame buffer net physical type to GDDR3_50SE.

Page 66: U7901 voltage follower changed from OPA333 to OPA705.

Page 5: Changed CPU parts to ES2, B1 for EVT

label 6.2.0

label 1.5.0

label 6.5.0

label 1.7.0

label 8.2.0

Page 82: Add BOMOPTION OMIT to RX9892.

Synced M87 LIO

Synced M87 MLB

Synced M87 LIO

Synced M87 MLB

Page 73:

Synced M87 MLB

08/22/07 -08/22/07 -08/22/07 -08/22/07 -08/22/07 --

08/24/07 --

8.1.0:

08/24/07 --

8.0.0:

08/24/07 --

08/23/07 --

08/23/07 -08/23/07 --

08/23/07 --

08/22/07 -08/22/07 --

08/23/07 --

08/23/07 --

08/23/07 --

08/23/07 --

7.2.0:

pg. 76 L9010,L9011pg. 43 L4600

pg. 44 FL4735

pg. 43 L4600

NB_CLK100M_DPLSS_P/N

Changed the orientation on these filters to match layout:

EVT Release of Schematic BOM and PCBF

152S0683 is the Mag layers alternate for Dale/Vishay inductors.

Page 5: Added alternate sources for these parts:

128S0164 is the Kemet alternate to Sanyo caps

104S0023 is the Panasonic alternate to Cyntec resistors

pg. 80 L9460,L9464,L9468,L9476,L9480,L9484

Changed the following filters to 155S0371 for supply issues:

Changed net physical and net spacing to CRT_50S on these signals

Major release label name : m87_mlb_051-7413_8.2.0

BOM Changes only

RFA 529050

Synced m87_mlb CSA pgs.

09/04/07 -09/04/07 --

08/30/07 --

8.2.0:

09/04/07 --

09/04/07 --

9.1.0:

08/30/07 --

9.0.0:

8.4.0:

08/29/07 --

08/29/07 --

8.3.0:

08/29/07 --

08/29/07 --

ICH8 GPIO 22 IPHS_SW_BIAS_EN_L routes to JJ3400.63

pg. 76 L9010,L9011

NB_CLK96M_DOT_P/N

Changed C7134 to 0.01uF 132S0042.

09/11/07 --

09/11/07 --

09/11/07 --

09/11/07 --

09/11/07 --

09/11/07 --

11.0.0:

09/11/07 --

09/06/07 --

09/04/07 --

10.0.0:

Page 50:

Page 82: LCD Backlight

630-9228: ZVX PCBA,2.5GHZ,512VRAM-SAM,M88

Changed R5425 and R5435 to 104S0023.

630-9225: ZVW PCBA,2.5GHZ,512VRAM-HY,M88

Added BOM variants and EEE codes for 2.5GHz:

HF capacitor substitution, with halogen parts as alternates.

Page 62: Removed OMIT property and BOM option table to make C7540 and C7541 only 128S0073.

Page 5: Removed alternate to 128S0164 Kemet 220uF tantalum cap at C7540 and C7541.

Page 57: Removed NO STUFF from DZ6960 (377S0044), ESD diode on BATT_POS per Chris.

pg. 5 Alternates BOM table updates.

Added OMIT properties and BOM option table to change these beads to 155S0220:

L9891,L9893,L9894

removed R8992,C8992

Page 75: GPU Vcore supply: Changed L8920 from 152S0525 to 152S0697.Dale 0.9uH 27A inductor has smaller pad size than Vishay IHLP4040.

<rdar://problem/5493576> M87/M88 MLB/LED: LED driver current mirror can not be disabled + power sequencing issue

Removed BOM tables and OMIT BOM options from HF capacitor substitution, with halogen parts as alternates.

Added R9810

label 7.0.0

label 9.0.0

label 10.3.0

label 10.2.0

Page 5: Added 376S0448 as alternate for 376S0445.

GPUVCORE: Current sense to use IMVP6 IMON + Non-inverting Opamp

<rdar://problem/5510696> TASK: M87 LIO changes to support LED board

Page 5: Removed HDCP ROM. Removed U8770, R8770,R871, C8770.

Page 50: updating GPUVcore current sense resistor values for gain of 4.83

Page 65: Changed C7860 to 0.0047uF (radar://5468257

Page 66: Swapped U7901 pins 1 and 3 signals (positive and negative inputs).

10/01/07 --

10/01/07 --

10/01/07 --

10/01/07 --

Synced M87 LIO

Synced M87 LIO

09/12/07 --

Synced M87 MLB

Page 50 & 75:

Synced M*& MLB

12.0.0:

13.0.0:

10/05/07 --

10/05/07 --

09/26/07 -09/26/07 --

12.0.0:

09/28/07 -09/28/07 -09/28/07 --

09/26/07 --

11.1.0:

11.2.0:

Page 93: <rdar://problem/5525486> M87/88 1V8 FB DC converter transient response improve/BOM change

C9307 change to 68pF, 0402, 10V, 10%

Page 5: Changed Module parts for new Penryn APNs.

C9308 change to 680pF, 0402, 10V, 10%

R9308 change to 40.2k, 0402, 1%;

Change 72968

Synced m87_MLB label

10/09/07 --

10/09/07 --

10/09/07 --

13.1.0:

DVT:

08/10/07 -- Page 10-12: Updated U1000 CPU part number to reflect latest Penryn pin-out.

08/14/07 -- Page 49: Changed Q5322 to SOT23 part same as M87.

08/14/07 -- Page 75: Changed GPU VID pull up/downs to 2.2K ohms.

DVT (cont):

Changed Q5030 to new LED Driver IC

Changed all GDDR3_46SE constraints back to GDDR3_50SE.

Deleted, Q5032,R5032,R5030

Changed R9809 to 200k

Added, C5030

Page 50: Named unnamed net on Q5030.

as alternate.

change C7134 to 0.022uF 132S0102 per Dayu

Page 90: Graphics constraints

10.0.0

12.2.0

12.1.0

Changed C9807 to 0.1uF

Page 57: Changed DZ6960-DZ6963 to 377S0068. These are NO STUFFs.

Page 81: Added FL9600 155S0372 to multi-touch trackpad power and GND.

Page 53: Changed U5750 TMP102 to RevE part 353S2039 with old part 353S1807

Page 69: NO STUFF battery positive terminal varistor DZ6960

Page 46: Changed to new Sleep LED circuit

Page 43: Changed L4605 ferrite bead to 155S0329 for lower DCR.

Page 59: CPU Vcore power supply

Changed R9807 to 5.1k

Synced M87_MLB label:

Synced M87_MLB label:

Synced M*&_LIO label:

10/24/07 --

10/24/07 --

14.5.0:

10/24/07 --

10/19/07 --

10/19/07 --

10/12/07 --

14.0.0:

10/12/07 -10/12/07 --

10/12/07 --

14.1.0:

10/12/07 --

11/01/07 --

17.0.0:

16.0.0:

11/01/07 --

14.0.0

ICH8 GPIO 2 IPHS_SW_INT routes to JJ3400.65

11/06/07 --

Synced M87_LIO label

Page 50: Removed ST SIL driver and returned to EVT’s BJT-driven current source

Page 5: Updated CPUs to PRQ parts, removed XDP_CONN and GPU_TMP401 bom options and changed to SMC_DEBUG_NO for PVT

Page 98: Changed R9808 to 200K, R9809 to 100K, C9802 to 0.033uF, C9807 to 0.33uF to improve Q9806 Vgs and sequencing

12/10/07 --

PVT:

12/12/07 --

Page 98: Changed C9805 to actual 2.2uF part (removed table entry)

18.1.0:

18.2.0:

12/13/07 --

Page 13: NO STUFFed R1330/R1331 since the LVDS_CTRL_DATA/CLK lines are grounded

EVT:

See earlier schematics for info about releases 0.0.1 - 4.0.0

Proto:

18.3.0:

12/16/07 --

Page 54: Added C8992/R8992 to provide differential sense option

A.0.0:

12/18/07 --

Release as Rev A

6

92

A.0.0

051-7431

Revision History

SYNC_MASTER=N/A

SYNC_DATE=N/A

Page 7

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

DRAWING NUMBER

SHT

OF

SIZE

D

Backlight Connector

6 TPs, 2 with each of above TP pairs

Left Clutch Barrel Connector

Other Func Test Points

IR & Sleep LED Connector

(HOST_DETECT_L)

Left I/O Power Connector

Request for at least 10 GND test points

NOTE: 10 additional GND test points are

called out separately in these notes.

RTC Battery Connector

FUNC_TEST

Thermal Diode Connectors

LPC+ Debug Connector

FUNC_TEST

2 TPs

per

FUNC_TEST

Battery Digital Connector

FUNC_TEST

FUNC_TEST

FUNC_TEST

FUNC_TEST

FUNC_TEST

Request for 3 test points

Request for 2 test points

Fan Connectors

System Validation TPs

FUNC_TEST

FUNC_TESTFUNC_TEST

Left ALS

FUNC_TEST

FUNC_TEST

Functional Test Points

NO_TEST

MAKE_

BASE

NB NO_TESTs

FUNC_TEST

ICT Test Points

Current Sense Calibration

MAKE_

BASE

NO_TEST

CPU FSB NO_TESTs

I404

I405

I406

I407

I408

I409

I410

I411

I412

I413

I414

I415

I416

I417

I418

I419

I420

I421

I422

I423

I424

I426

I427

I430

I431

I432

I433

I436

I442

I443

I447

I448

I490

I491

I492

I493

I494

I495

I496

I497

I498

I506

I507

I509

I515

I516

I517

I519

I520

I521

I529

I530

I531

I533

I534

I535

I536

I539

I540

I541

I542

I544

I545

I546

I547

I548

I549

I550

I551

I552

I553

I554

I555

I556

I557

I558 I559

I561

I567

I568

I569

I570

I571

Functional / ICT Test

051-7431

A.0.0

92

7

SYNC_MASTER=MASTER

SYNC_DATE=MASTER

TRUE

FSB_BNR_L

FSB_ADSTB_L<1..0>

TRUE

NC_CPU_RSVD5

TRUE

FSB_DBSY_L

TRUE

FSB_REQ_L<4..0>

FSB_HIT_L

TRUE

FSB_DSTB_L_N<3..0>

TRUE

TRUE

FSB_DINV_L<3..0>

NC_CPU_RSVD5

TRUE TRUE

TRUE

FSB_BREQ0_L

TRUE

FSB_ADS_L

TRUE

FSB_HITM_L

FSB_LOCK_L

TRUE

TRUE

FSB_D_L<63..0>

FSB_DSTB_L_P<3..0>

TRUE

FSB_DRDY_L

TRUE

TRUE

FSB_A_L<31..3>

TRUE

NC_NB_RSVD<24>

TRUE

NC_NB_RSVD<26..27>

TRUETRUE

TP_NB_NC<1..16>

LPC_FRAME_L

TRUE

TRUE

FWH_INIT_L

SMC_TX_L

TRUE

NC_NB_NC<1..16>

TRUE

TP_NB_RSVD<26..27>

TP_NB_RSVD<24>

PPVCORE_S0_CPU

TRUE

PP5V_S3

TRUE

USB_IR_N

TRUE

NB_CLK100M_PCIE_P

TRUE

NB_RESET_L

TRUE

PP5V_S3_CAMERA_F

TRUE

P1V8P1V5P1V05S0_PGOOD

TRUE

PM_ENET_EN

TRUE

PM_S4_STATE_L

TRUE

FSB_DPWR_L

TRUE

TRUE

SYS_LED_ANODE

CPU_STPCLK_L

TRUE

FSB_CLK_NB_P

TRUE

PLT_RST_L

TRUE

FSB_CLK_CPU_N

TRUE

TRUE

USB_IR_P

IMVP_VR_ON

TRUE

IMVP_DPRSLPVR

TRUE

IMVP6_VID<6..0>

TRUE

TRUE

PPVBATT_G3_RTC

SMBUS_SMC_BSA_SCL

TRUE

SMC_BS_ALRT_L

TRUE

BKLT_PWM

TRUE

FSB_CLK_NB_N

TRUE

NB_CLK100M_PCIE_N

TRUE

PP5V_S0

TRUE

TRUE

FAN_LT_PWM

FAN_LT_TACH

TRUE

FAN_RT_PWM

TRUE

FAN_RT_TACH

TRUE

PP3V42_G3H

TRUE

PP5V_S0

TRUE

TRUE

LPC_AD<0>

TRUE

LPC_AD<1>

PM_CLKRUN_L

TRUE

TRUE

PCI_FW_GNT_L

TRUE

SMC_TMS

TRUE

DEBUG_RESET_L

SMC_TRST_L

TRUE

TRUE

SMC_TDO

SMC_MD1

TRUE

TRUE

PCI_CLK33M_LPCPLUS

LPC_AD<2>

TRUE

LPC_AD<3>

TRUE

INT_SERIRQ

TRUE

TRUE

PM_SUS_STAT_L

TRUE

SMC_TDI

TRUE

SMC_TCK

TRUE

SMC_RESET_L

TRUE

SMC_NMI

TRUE

SMC_RX_L

LINDACARD_GPIO

TRUE

TRUE

ALS_GAIN

TRUE

LTALS_OUT

HSTHMSNS_D_P

TRUE

HSTHMSNS_D_N

TRUE

TRUE

RSFSTHMSNS_D_P

TRUE

RSFSTHMSNS_D_N

CPUTHMSNS_D2_P

TRUE

TRUE

CPUTHMSNS_D2_N

TRUE

CPU_PWRGD

TRUE

CPU_DPSLP_L

TRUE

PM_DPRSLPVR

CPU_DPSLP_L

TRUE

TRUE

PM_LAN_ENABLE

PCI_RST_L

TRUE

PM_RSMRST_L

TRUE

PM_SB_PWROK

TRUE

SB_RTC_RST_L

TRUE

PM_STPCPU_L

TRUE

PM_STPPCI_L

TRUE

VR_PWRGD_CLKEN

TRUE

TRUE

VR_PWRGOOD_DELAY

FSB_CPURST_L

TRUE

FSB_CPUSLP_L

TRUE

NB_SB_SYNC_L

TRUE

PM_BMBUSY_L

TRUE

CPU_THERMTRIP_R

TRUE

NB_CLKREQ_L

TRUE

SMC_LRESET_L

TRUE

GPU_RESET_L

TRUE

FSB_CLK_CPU_P

TRUE

CPU_DPRSTP_L

TRUE

PM_SLP_S5_L

TRUE

PM_SLP_S3_L

TRUE

TRUE

SMC_ONOFF_L

TRUE

PM_SYSRST_L

USB_CAMERA_F_P

TRUE

USB_CAMERA_F_N

TRUE

PPVCORE_GPU

TRUE

PP5V_S0

TRUE

ISENSE_CAL_EN

TRUE

PPBUS_G3H

TRUE

PP18V5_DCIN

TRUE

GND

TRUE

BATT_POS

TRUE

SMBUS_SMC_BSA_SDA

TRUE

BKLT_P5V_EN

TRUE

BKLT_GND

TRUE

BKLT_PWR

TRUE

TRUE

GND

TRUE

GND

TRUE

GND

TRUE

GND

GND

TRUE

TRUE

GND

GND

TRUE

82

82

82

82

81

81

81

79

80

80

80

75

65

81

65

65

66

59

66

59

59

63

58

65

58

65

58

62

54

57

54

62

54

61

52

48

52

58

52

60

65

49

47

49

49

49

59

59

81

58

47

46

47

83

45

47

58

47

49

58

88

65

45

88

82

88

88

88

88

42

45

42

87

47

47

83

83

83

83

59

83

88

59

40

75

42

57

88

83

83

83

83

83

83

83

83

83

83

83

83

83

83

83

47

46

12

46

86

30

63

65

43

83

83

30

28

30

86

83

57

57

30

30

27

43

27

47

47

47

47

47

47

88

47

47

47

46

47

47

47

46

54

23

23

59

23

28

30

30

28

14

83

30

23

46

36

81

45

68

27

49

57

14

14

10

14

14

14

14

14

14

14

14

14

14

14

14

14

16

45

45

11

44

81

29

28

62

61

34

14

81

23

29

24

29

81

59

83

59

48

46

82

29

29

8

28

8

45

45

45

38

46

47

47

46

47

47

45

45

45

45

46

46

46

47

45

47

45

54

91

91

91

91

91

91

13

10

25

10

45

28

45

25

28

29

29

28

16

13

14

25

25

29

45

67

29

16

45

35

46

28

91

91

49

8

49

40

66

48

82

82

82

10

10

7

10

10

10

10

10

10

10

10

10

10

10

10

10 16

23

47

43

16

8

8

24

16

16

44

61

36

25

10

46

10

14

9

10

24

45

59

12

28

45

45

81

14

16

7

52

52

52

52

8

7

23

23

25

24

45

28

45

45

45

30

23

23

25

25

45

45

45

45

43

25

34

34

51

51

51

51

51

51

10

7

16

7

25

24

25

9

23

25

25

25

9

10

10

16

16

23

16

28

28

10

10

25

25

45

25

44

44

8

7

45

8

57

57

45

81

81

81

Page 8

APPLE INC.

NONE

SCALE

REV.

A

D

C

B

A

D

C

B

8 7

6

5

4

3

2 1

8

7 6

5

4

3

2

1

THE INFORMATION CONTAINED HEREIN IS THE PROPRIETARY

PROPERTY OF APPLE COMPUTER, INC. THE POSSESSOR

AGREES TO THE FOLLOWING

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IN WHOLE OR PART

I TO MAINTAIN THE DOCUMENT IN CONFIDENCE

NOTICE OF PROPRIETARY PROPERTY

DRAWING NUMBER

SHT

OF

SIZE

D

Yukon EC will not be supported

1.8V-0.9V Rails

5V Rails

"FW" (FireWire) Rails

"ENET" Rails

3.3V-2.5V Rails

"G3Hot" (Always-Present) Rails

Chipset "VCore" Rails

MAX I = ?.??A

"GPU" Rails

SYNC_DATE=(MASTER)

SYNC_MASTER=(MASTER)

8

92

A.0.0

051-7431

Power Aliases

PP3V3_S0GPU

PP3V3_S0GPU

PP3V3_S0GPU

PP3V3_S0GPU

PP3V3_S0GPU

MAKE_BASE=TRUE

VOLTAGE=3.3V

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.6 mm

PP1V25_S0_ISNS

VOLTAGE=3.3V

MIN_NECK_WIDTH=0.2 mm

PP3V3_FW

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.4 mm

PPVP_FW_PORTB_UF

MAKE_BASE=TRUE

PPVP_FW_PORTA_UF

MAKE_BASE=TRUE

PP1V8_S3

PP1V8_S3

MIN_LINE_WIDTH=0.6 mm

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=1.8V

MAKE_BASE=TRUE

VOLTAGE=1.25V

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.6 mm

PP1V25_S0_ISNS

PP1V05_S0

PPVCORE_S0_NB_R

PP0V9_S3_MEM_VREF

PP0V9_S0

PP3V3_ENET

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

MIN_LINE_WIDTH=0.6 mm

PP3V3_S0

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=3.3V

MAKE_BASE=TRUE

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S3

PP3V3_S3

PP3V3_S3

VOLTAGE=3.3V

PP3V3_S3

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

MAKE_BASE=TRUE

PP5V_S0

PP5V_S0

VOLTAGE=5V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.6 mm

PP5V_S0

PP5V_S0

PP5V_S0

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

PPBUS_G3H

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6 mm

VOLTAGE=12.6V

MIN_NECK_WIDTH=0.25 mm

PP3V3_S0GPU_TMDS

PP3V3_S0GPU_TMDS

PP3V42_G3H

VOLTAGE=3.42V

MIN_LINE_WIDTH=0.3 mm

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2 mm

PP3V42_G3H

PP5V_S5

PP5V_S3

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=5V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6 mm

PP5V_S0

PP5V_S0

PP5V_S5

PP5V_S5

VOLTAGE=5V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

PP5V_S5

PP3V42_G3H

PPDCIN_G3H

PP3V3_S3

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP1V25_S0

PP5V_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S3

PP3V3_S3

PP3V3_S3

PP3V3_S3

PP3V3_S3

PP3V3_S3

PP3V3_S3

PP3V3_S5

PP3V3_S5

PP3V3_S5

PP3V3_S5

PP3V3_S5

PP3V3_S5

PP3V3_S5

PP3V3_S5

PP3V3_S5

PP5V_S3

PP5V_S5

PP3V42_G3H

PP5V_S0

PP5V_S0

PP5V_S0

PP3V3_S0

PP3V42_G3H

PPDCIN_G3H

PP3V42_G3H

PP3V42_G3H

PP3V42_G3H

PPDCIN_G3H

PP5V_S3

PP3V3_S0

PP3V3_S5

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP3V3_S0

PP5V_S5

PPVCORE_S0_CPU

PP3V3_S0GPU

PP3V3_S0GPU

PP3V3_S0GPU

PP3V3_S0GPU

PP3V3_S0GPU

PP3V3_S0GPU

PP1V9_ENET

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PP1V5_S0

PP1V5_S0

PP1V5_S0

PP1V5_S0

PP1V5_S0

PP1V5_S0

PP1V5_S0

PP1V5_S0

PP1V5_S0

PP1V5_S0

PP1V8_S3_ISNS

PP1V8_S3_ISNS

PP1V8_S3_ISNS

PP3V3_S5

PP3V3_S5

PP3V3_S3

PP3V3_S3

PP5V_S3

PPBUS_G3H

PP1V8_S3

PP1V8_S3

PP1V8_S3

PP0V9_S3_MEM_VREF

PP3V3_ENET

PPVCORE_S0_NB_R

PP1V05_S0

PP1V05_S0

PP1V05_S0

PP1V05_S0

PP1V95_FW

PP3V3_S0GPU_TMDS

PP1V05_S0

PP0V9_S3_MEM_VREF

PP1V05_S0

PP0V9_S3_MEM_VREF

PP0V9_S0

PP3V3_ENET

PP1V9_ENET

PP1V25_ENET

PP3V3_S5

PP3V3_S5

PP3V3_S5

PP5V_S0

PP3V3_S5

PP3V3_S5

PPVCORE_S0_CPU

PP1V8_S3

PP1V25_ENET

PP0V9_S3_MEM_VREF

PP1V05_S0

GND

PPVP_FW

PPVP_FW

PPVP_FW_PORTB_UF

PP3V3_FW

PPBUS_FW_FWPWRSW_F

PPVP_FW

PPVP_FW_PORTA_UF

PP1V25_S0

PP3V3_FW

PP3V3_FW

PP3V3_FW

PP3V3_FW

PP1V95_FW

PP1V95_FW

PP3V3_S5

PP1V05_S0

PPVP_FW

PP3V42_G3H

PP3V42_G3H

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PPBUS_G3H

PP5V_S3

PP5V_S3

PP5V_S5

PP5V_S5

PP5V_S5

PP5V_S5

PP3V42_G3H

PP5V_S5

PP5V_S5

PP5V_S5

PP5V_S5

PP3V3_S0

PP3V3_S0

PP1V25_ENET

GND

PPVCORE_GPU

PPVCORE_GPU

PP1V8_S0GPU

PP1V8_S0GPU

PP1V05_S0

PP1V05_S0

PP1V05_S0

PP1V8_S0GPU_ISNS

PP1V8_S0GPU_ISNS

PP1V8_S0GPU_ISNS

PP1V8_S0GPU_ISNS

PP1V8_S0GPU_ISNS

PP1V8_S0GPU_ISNS

PP1V05_S0

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=1.05V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=3.3V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.4 mm

PP3V3_S0GPU_TMDS

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.4 mm

VOLTAGE=18.5V

MIN_NECK_WIDTH=0.2 mm

PPDCIN_G3H

MAKE_BASE=TRUE

PP3V3_S5

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.6 mm

VOLTAGE=3.3V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.25mm

MIN_LINE_WIDTH=0.6mm

VOLTAGE=1.5V

PP1V5_S0

PP1V8_S3_ISNS

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=1.8V

MAKE_BASE=TRUE

MAKE_BASE=TRUE

VOLTAGE=0.9V

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.4 mm

PP0V9_S3_MEM_VREF

PPVCORE_S0_NB_R

MIN_LINE_WIDTH=0.4 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=0.9V

MAKE_BASE=TRUE

VOLTAGE=1.9V

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.4 mm

PP1V9_ENET

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.3 mm

MIN_LINE_WIDTH=0.6 mm

VOLTAGE=1.25V

PPVCORE_S0_CPU

PPBUS_FW_FWPWRSW_F

MAKE_BASE=TRUE

PPVP_FW

VOLTAGE=33V

MIN_NECK_WIDTH=0.3 mm

MIN_LINE_WIDTH=0.6 mm

MAKE_BASE=TRUE

VOLTAGE=3.3V

MIN_LINE_WIDTH=0.4 mm

MIN_NECK_WIDTH=0.2 mm

MAKE_BASE=TRUE

PP3V3_ENET

MAKE_BASE=TRUE

VOLTAGE=1.95V

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.4 mm

PP1V95_FW

MIN_LINE_WIDTH=0.6 mm

VOLTAGE=1.25V

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2 mm

PP1V25_S0

VOLTAGE=0.9V

PP0V9_S0

MAKE_BASE=TRUE

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.6 mm

PP1V25_ENET

VOLTAGE=1.25V

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

PPVCORE_GPU

VOLTAGE=1.2V

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=1.8V

PP1V8_S0GPU

MAKE_BASE=TRUE

MIN_LINE_WIDTH=0.6 mm

MIN_NECK_WIDTH=0.2 mm

VOLTAGE=1.8V

PP1V8_S0GPU_ISNS

PP5V_S0

PP5V_S0

PP5V_S5

PP3V3_S0

PP1V25_S0_ISNS

PP3V3_S0GPU

PP3V3_S0GPU

PP3V3_S0GPU

PP1V25_S0_ISNS

PP1V25_S0_ISNS

PP1V25_S0_ISNS

42 58 43

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

91

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

65

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

53

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

52

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

51

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

50

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

48

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

47

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

46

61

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

42

61

61

61

61

61

61

61

61

61

61

61

61 50

32

32

32

32

32

32

32

32

32

32

32

82

82

82

82

82

82

82

82

82

82

82

82

82

82

82

32

32

32

32

32

32

32

32

32

32

32

32

32

32

32

32

32

32

32

32

82

50

50

50

50

50

50

50

50

82

50

50

50

50 46

31

31

31

31

31

31

31

31

31

31

31

82

82

82

82

82

79

79

79

79

79

79

79

79

79

79

79

79

79

79

79

82

82

31

31

82

31

31

31

31

31

31

91

91

91

91

91

91

91

91

91

82

82

82

31

31

31

31

31

31

31

31

31

31

31

31

91

91

79

46

46

46

46

46

46

91

91

82

91

91

46

91

46

79

46

46

46

46

82

82

30

30

30

30

30

30

30

30

30

30

30

30

81

81

81

81

81

75

75

75

75

75

75

75

75

75

75

75

75

75

75

75

81

81

30

30

81

30

30

30

30

30

30

76

76

76

76

76

76

76

76

76

81

81

81

30

30

30

30

30

30

30

30

30

30

30

30

76

76

75

30

30

30

30

30

30

76

76

81

76

76

30

76

30

75

30

30

30

30

81

81

27

29

29

29

29

29

29

29

29

29

29

29

80

80

80

80

80

66

66

66

66

66

66

66

66

66

66

66

66

66

66

66

81

81

79

80

80

79

79

81

29

29

80

29

29

29

29

29

29

65

65

65

65

65

65

65

65

65

79

81

80

80

80

29

81

81

81

81

29

29

29

29

29

29

29

29

29

29

29

79

65

65

66

27

27

27

27

27

27

65

65

80

65

65

27

65

27

81

81

66

79

79

79

79

81

79

79

79

79

27

27

27

27

80

80

79

79

26

28

28

28

28

28

28

28

28

28

28

28

81

81

81

81

65

65

65

65

65

63

63

63

63

63

63

63

63

63

63

63

63

63

63

63

66

66

75

65

65

75

75

66

81

28

28

65

28

28

28

28

28

28

81

81

81

81

81

81

81

60

60

60

60

60

60

60

60

60

75

66

65

65

65

28

66

66

66

66

28

28

28

28

28

28

28

28

28

28

28

75

60

60

81

81

63

26

26

26

26

26

26

60

60

65

60

60

26

60

26

66

66

63

75

75

75

75

66

75

75

75

75

26

26

26

26

65

65

75

75

80

80

80

80

80

72

72

23

27

27

27

27

27

27

27

27

27

27

27

65

65

65

65

59

59

59

59

59

62

62

62

62

62

62

62

62

62

62

62

62

62

62

62

65

65

65

59

59

65

65

65

65

27

27

59

27

27

27

27

27

27

65

65

65

65

65

65

65

58

58

58

58

58

58

58

58

58

65

65

59

59

59

27

65

65

65

65

27

27

27

27

27

27

27

27

27

27

27

65

80

80

80

80

80

80

72

72

72

72

72

72

58

58

65

65

62

23

23

23

23

23

23

58

58

59

58

58

23

58

23

65

65

72

72

72

62

65

65

65

65

65

65

65

65

65

23

23

23

78

78

78

78

78

23

78

59

59

65

72

80

80

80

72

72

72

65

76

76

76

76

76

69

69

21

26

26

26

26

26

26

26

26

26

26

26

58

58

58

58

58

58

58

58

58

61

61

61

61

61

61

61

61

61

61

61

61

61

61

61

57

57

63

58

58

63

63

57

58

26

26

58

26

26

26

26

26

26

58

58

58

58

58

58

58

56

56

56

56

56

56

56

56

56

63

57

58

58

58

26

57

57

57

57

26

26

26

26

26

26

26

26

26

26

26

63

76

76

76

76

76

76

69

69

69

69

69

69

91

91

91

91

91

91

91

91

91

91

56

56

58

58

61

21

21

21

21

21

21

56

56

58

56

56

21

56

21

57

57

69

69

69

61

63

63

63

63

57

63

63

63

63

21

21

21

77

77

77

77

77

21

91

77

58

58

63

69

76

76

76

69

69

69

63

75

75

75

75

75

67

67

19

25

25

25

25

25

25

25

25

25

25

25

55

55

55

55

54

54

54

54

54

60

60

60

60

60

60

60

60

60

60

60

60

60

60

60

48

48

62

54

54

62

62

48

55

25

25

54

25

25

25

25

25

25

55

55

55

55

55

55

55

48

48

48

48

48

48

48

48

48

62

48

54

54

54

25

48

48

48

48

25

25

25

25

25

25

25

25

25

25

25

62

75

75

75

75

75

75

67

67

67

67

67

67

63

63

63

63

63

63

63

63

63

63

48

48

55

55

60

19

19

19

19

19

19

48

48

54

48

48

19

48

19

48

48

67

67

67

60

62

62

62

62

48

62

62

62

62

19

19

19

74

74

74

74

74

19

63

74

54

54

62

67

75

75

75

67

67

67

62

74

74

74

74

74

65

91

91

65

18

24

24

24

24

24

24

24

24

24

24

24

54

54

54

54

52

52

52

52

52

59

59

59

59

59

59

59

59

59

59

59

59

59

59

59

47

47

61

52

52

61

61

47

54

24

24

52

24

24

24

24

24

24

54

54

54

54

54

54

54

46

46

46

46

46

46

46

46

46

61

47

52

52

52

24

47

47

47

47

24

24

24

24

24

24

24

24

24

24

24

61

74

74

74

74

74

74

65

65

65

65

65

65

34

34

34

34

34

34

34

34

34

34

46

46

54

54

59

91

91

91

18

18

18

18

18

18

46

46

52

46

46

91

18

46

18

47

47

65

65

65

59

61

61

61

61

47

61

61

61

61

18

18

18

71

71

71

71

71

18

34

71

52

52

61

65

74

74

74

65

65

65

61

73

73

73

73

73

50

62

62

50

14

23

23

23

23

23

23

23

23

23

23

23

51

51

51

51

49

49

49

49

49

58

58

58

58

58

58

58

58

58

58

58

58

58

58

58

46

46

60

81

49

49

60

60

46

51

23

23

49

23

23

23

23

23

23

51

51

51

51

51

51

51

28

28

28

28

28

28

28

28

28

81

60

46

49

49

49

23

46

46

46

46

81

23

23

23

23

23

23

23

23

23

23

23

60

59

73

73

73

73

73

73

50

50

50

50

50

50

27

27

27

27

27

27

27

27

27

27

28

28

51

51

81

58

62

62

62

14

14

14

14

14

14

28

28

49

28

28

59

62

14

28

14

46

46

50

50

50

58

81

81

60

60

60

60

46

60

60

60

60

14

14

14

70

70

70

70

70

14

27

59

70

49

49

60

50

73

73

73

50

50

50

60

72

72

72

72

72

27

64

50

50

27

13

62

21

21

21

21

21

21

21

21

21

21

21

50

50

50

50

47

47

47

47

47

57

57

57

57

57

57

57

57

57

57

57

57

57

57

57

45

45

58

58

47

47

58

58

45

50

21

21

47

21

21

21

21

21

21

50

50

50

50

50

50

50

27

27

27

27

27

27

27

27

27

58

58

45

47

47

47

21

45

45

45

45

58

21

21

21

21

21

21

21

21

21

21

21

58

49

72

72

72

72

72

72

27

27

27

27

27

27

26

26

26

26

26

26

26

26

26

26

50

50