Page 1

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

Apple Inc.

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

8

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

IV ALL RIGHTS RESERVED

II NOT TO REPRODUCE OR COPY IT

3

B

7

BRANCH

DRAWING NUMBER

SIZE

D

SHEET

R

DATE

D

A

C

PAGE

A

C

3456

D

B

8 7 6 5 4 2 1

12

APPD

CK

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

DRAWING TITLE

DESCRIPTION OF REVISION

REV ECN

REVISION

PROPRIETARY PROPERTY OF APPLE INC.

CHESTNUT BOM OPTIONS

ALTERNATES

VCM RESISTOR BOM OPTIONS

L46_RF BOM OPTIONS

BOM 639-4501

BRD 820-3581

SCH 051-0143

BOARD_ID RADIO BOM OPTIONS

X64 EVT SINGLE_BRD

NAND BOM OPTIONS

CONFIG ALL/DTD BOM OPTIONS

X64 BOM CALLOUTS

COMPASS BOM OPTIONS

1 OF 49

Tue Mar 19 16:23:08 2013

SCHEM, MLB

051-0143

2013-03-1900018904183ENGINEERING RELEASED

1 OF 22

3.0.0

TI CHESTNUT - 1.5 UH IND

TI CHESTNUT -1.5 UH IND

0 OHM RES

L46_RF_DTD117S0161

131S0447

1 Y

L46_RF

L46_RF_ALLL46_RF

7.5PF CAPACITOR VALUE

Y1

138S0648

118S0765

R56

Y

VCM_RES

1

RES 11.OHM 01005 1%

BATT B2B, TPS, PD FEATURES

N/A

U21

ALTERNATE

338S1213

L81 ALT, SSMC FLOW

338S1116

ALTERNATE

CSD68803W15

376S1060 376S0882

?

197S0482

RF EPSON ALT

ALTERNATE

197S0470

Y1_RF

RF KYOCERA ALT

197S0470

ALTERNATE

197S0491

Y1_RF

RF TDK WIFI ALT

339S0205

ALTERNATE

339S0209

U8_RF

U8_RF

ALTERNATE

RF USI WIFI ALT

339S0205339S0204

U6_RF

ALTERNATE

335S0895

RF WINBOND NOR ALT

335S0874

N/A

BUTTON FLEX B2B

N/A8 8

N/A

L81 AUDIO CODEC

9 N/A9

N/AN/A10

CG FLEX B2B

10

N/AN/A

D404 (TOUCH B2B, DRIVER ICS)

17 18

18

LCM CONNECTOR

N/A N/A19

CHESTNUT_TI_CYN

152S1802

1

L19

Y

CHESTNUT_TI_TY

152S1842

L19

1 Y

152S1849

TI CHESTNUT -1.5 UH IND

CHESTNUT_TI_MU

1

L19

Y

N/A3 N/A3

H5P GPIO & CONTROL

H5P IO POWER

4 N/A4 N/A

N/A

H5P SOC/CPU/SRAM PWR

N/A5 5

7 N/A7

H5P VIDEO

CHESTNUT + BACKLIGHT DRIVER

13 N/A14 N/A

15

SPKR AMP + LED DRIVER

N/A14 N/A

OSCAR + SENSORS

19 N/A N/A20

20

CAM0 CONNECTOR

N/A N/A21

21 N/A N/A22

RADIO_MLB HIERARCH. SYMBOL

22 N/A N/A23

N/A

H5P W/ NAND

N/A6 6

CRITICAL

N49_ALL

1

152S1567 L63_RF

3.3NH +/-0.1NH 180MA 01005

N49_ALL

1

7.5NH 5NH% 140MA 01005

L56_RF152S1408 CRITICAL

N49_ALL

152S1320

7.5NH 0.30A 0201

C115_RF

1

CRITICAL

3.0NH +/-0.1NH 200MA 01005

N49_ALL

1

152S1656 CRITICAL

C249_RF

R25_RF

Y

255K 1% 01005

1

N48_CFG_A

118S0659

N49_DTD

1

118S0652

49.9OHM 1% 01005

L56_RF

49.9OHM 1% 01005

N49_DTD

118S0652

1

L63_RF

H5P JTAG, USB ,PLL

N/A2 2 N/A

N49_DTD

1

118S0652

49.9OHM 1% 01005

C252_RF

N49_DTD

1

118S0407

49.9OHM 1% 0201

C114_RF

N49_ALL

100K 1% 01005

Y1

R25_RF118S0626

N48_CFG_B

147K 1% 01005

Y1

118S0689 R25_RF

N/A11

AGATHA PMU(1/2)

N/A12

COMPASS_POP

639-4024

U16

1

ST GYRO - COMPASS POP

Y

L14

L14 ALTERNATE

152S1803

ALTERNATE

152S1805

152S1836 152S1844

ALTERNATE

L4

L4 ALTERNATE

ALTERNATE

R54 ALTERNATE

?

118S0764 118S0717

?

ALTERNATE

CSD75202W15

376S0774376S1120

ALTERNATE

311S0591

?

IC,74LVCG32 OR GATE

311S0273

ALTERNATE

335S0895

?

U6_RF

335S0874

197S0399

ALTERNATE

?

XTAL,32.768KHZ

197S0392

155S0667

?

FLTR,COMMON MODE,90OHM

ALTERNATE

155S0583

?

ALTERNATE

155S0773

FERR BD,120OHM,210MA

155S0453

CAP,CER,X6S,1UF,20%

ALTERNATE

138S0705

?

138S0746

CAP,CER,X6S,1UF,20%

138S0697

?

ALTERNATE

138S0695

ALTERNATE

CAP,TANT,1UF,20%,25V

127S0164 127S0160

?

CAP,CER,X5R,4.7UF,20%

138S0703

ALTERNATE

?

138S0648

CAP,TANT,1UF,20%,25V

127S0160127S0162

?

ALTERNATE

THERMISTOR,NTC,10K

?

ALTERNATE

107S0146 107S0208

H5P ALTERNATE

ALTERNATE

?

339S0177339S0178

138S0652

?

4.7UF CERM 0402 6.3V

ALTERNATE

?

XTAL,32.768KHZ

ALTERNATE

197S0369 197S0392

118S0650

N49_ALL

499K 1% 01005

1

R26_RF

Y

L41_RF

N49_DTD

1

49.9OHM 1% 0201

118S0407

N49_DTD

50K 1% 01005

118S0732

Y1

R25_RF

Y

118S0626

1

100K 1% 01005

R26_RF

N48_CFG_A

3.6NH +/-1NH 180MA 01005

1

152S1568

NOSTUFF

C93_RF

N49_DTD

C93_RF

49.9OHM 1% 01005

1

118S0652

8.2NH +/-3% 0.25A 0.7OHM 0201

L41_RF

N49_ALL

1

CRITICAL152S1336

118S0407

N49_DTDC115_RF

49.9OHM 1% 0201

1

1.00M 1% 01005 N49_DTD

118S0621

Y1

R26_RF

N49_ALL

1

CRITICAL152S1623

5.1NH 3% 0.16A 01005

L77_RF

N49_DTD

1

118S0652

49.9OHM 1% 01005

L77_RF

N/A

AGATHA PMU(2/2)

12 N/A13

15 N/AN/A

TRISTAR

16

16

DOCKFLEX B2B

N/A N/A17

N48_CFG_B

118S0626

Y1

R26_RF

100K 1% 01005

CAP,CER,610,4.7UF,20%

?

ALTERNATE

138S0702 138S0657

CAP,CER,X6S,1UF,20%

ALTERNATE

138S0739?138S0706

N49_ALL

8.2NH +/-3% 0.25A 0.7OHM 0201

1

CRITICAL152S1336

C114_RF

N49_DTD

1

118S0652

C263_RF

49.9OHM 1% 01005

N49_ALL

1

CRITICAL152S1577

15NH 3% 140MA 01005

C263_RF

335S0878

NAND,19NM,16GX8,MLC,PPN1.5

1

NAND_16GU4

Y

051-0143

Y

SCH, SINGLE_BRD, X64

SCH

?1

820-3581

Y

PCB

PCB, SINGLE_BRD, X64

1 ?

825-6838

EEEE_FF16

1

EEEE_16G

Y

LABEL FOR X64 639-4501

825-6838

1

LABEL FOR X64 639-4768

Y

EEEE_FHFH

EEEE_DTD

CSA PAGEPDF PAGE

DATE

CONTENTS

SYNC MASTER

L11 ALTERNATE

152S1721

?

ALTERNATE

152S1850

311S0591

IC,74LVCG32 OR GATE

?

ALTERNATE

311S0273

335S0874335S0895

U6_RF

?

ALTERNATE

117S0161

N49_DTD

1

0.00OHM 01005

C249_RF

N49_ALL

131S0639

1

CRITICAL

0.8PF 01005

C252_RF

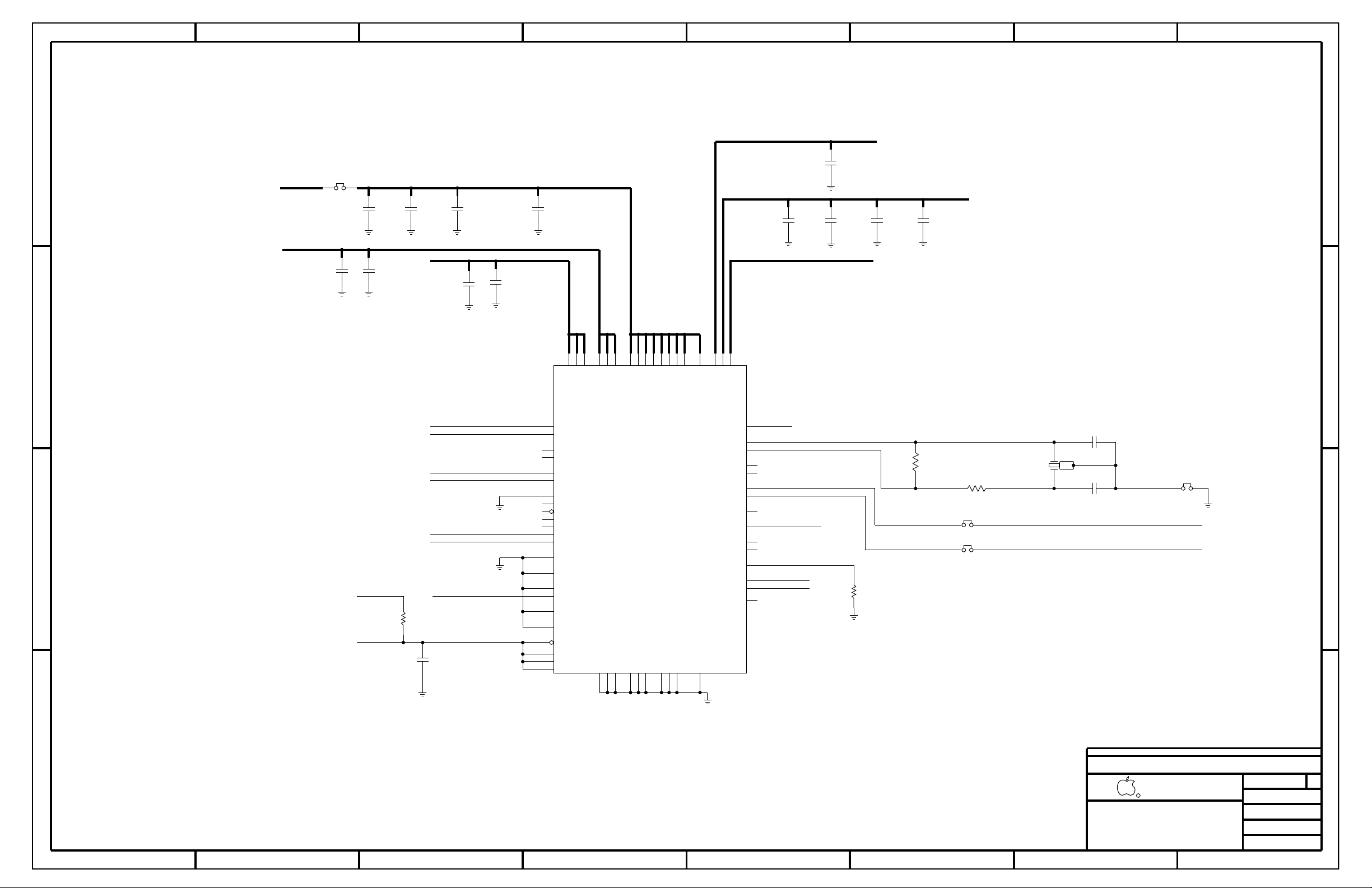

Page 2

FAST_SCAN_CLK

HOLD_RESET

USB_ASW_VSS18

USB_ID

USB_ANALOGTEST

USB_DM

USB_DP

USB11_DM

USB11_DP

USB_BRICKID

TST_STPCLK

JTAG_TRST*

HSIC3_DATA

XI0

WDOG

VDD_ANA_PLLUSB

VDD_ANA_PLL7

VDD_ANA_PLL6

VDD_ANA_PLL5

VDD_ANA_PLL4

VDD_ANA_PLL3

VDD_ANA_PLL2

VDD_ANA_PLL1

USB_VDD330

USB_DVDD

USB_ASW_VDD18

TST_CLKOUT

TESTMODE

JTAG_TRTCK

JTAG_TDO

JTAG_SEL

HSIC1_DVDD101

HSIC_VDD123

HSIC_VDD122

HSIC_VDD121

HSIC2_DVDD102

HSIC3_DVDD103

VDD_ANA_PLL0

HSIC3_STB

HSIC2_STB

CPU0_SWITCH

XO0

USB_VBUS

HSIC1_STB

HSIC1_DATA

HSIC_VSS121

HSIC_VSS122

DDR1_CKEIN

DDR0_CKEIN

CFSB

FUSE1_FSRC

USB_REXT

RESET*

JTAG_TCK

JTAG_TMS

JTAG_TDI

CPU1_SWITCH

USB_BRICKID_DM_MON

USB_VSSA0

USB_VSSA0

USB_VSSA0

HSIC2_DVSS

HSIC1_DVSS

HSIC_VSS123

HSIC3_DVSS

HSIC2_DATA

SYM 1 OF 12

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

PLACE R49 AND C1 CLOSE TO EACH OTHER AND U1 PER EMC

1.8V TOLERANT

(1MA)

BASEBAND

WLAN (TOP)

USBHS ON/OFF TOLERANCE 5V/1.98V

(1MA)

NO_CONNECT OKAY

(2X 1MA)

(3X 11.9MA)

(5.4MA)

(3X 2.7MA)

(2X 1MA)

(1MA)

(1MA)

(1MA)

(28MA)

(22MA)

FINAL XTAL PASSIVES 11/30/2011

SERIAL MODE NAMES

R7

1.00M

1/32W

MF

1%

01005

5%

1.00K

R71

010051/32W

MF

C2

0201

0.22UF

20%

6.3V

X5R

C93

6.3V

20%

X5R

0201

0.22UF

R6

43.2

01005

1/32W

1%

MF

C1

01005

6.3V

1000PF

X5R-CERM

10%

C21

0.01UF

6.3V

X5R

10%

01005

C20

0.01UF

10%

6.3V

01005

X5R

C36

01005

5%

16V

CERM

12PF

C37

16V

CERM

01005

5%

12PF

C392

0201

0.22UF

6.3V

X5R

20%

C33

0.01UF

6.3V

X5R

01005

NOSTUFF

10%

C28

0.22UF

20%

6.3V

0201

X5R

Y1

24.000MHZ-30PPM-9.5PF-60OHM

1.60X1.20MM-SM

XW44

SHORT-10L-0.1MM-SM

XW5

SM

NO_XNET_CONNECTION=TRUE

C141

10V

NP0-C0G

01005

5%

100PF

H5P-SC58950C0E

U1

FCMSP

C35

6.3V

56PF

5%

NP0-C0G

01005

C157

0.22UF

20%

6.3V

X5R

0201

R67

01005

47.0K

5%

1/32W

MF

C128

0402-2

10UF

20%

6.3V

CERM-X5R

XW79

SHORT-01005

SHORT-01005

XW77

C34

01005

X5R

10%

6.3V

0.01UF

C32

01005

6.3V

X5R

0.01UF

10%

H5P JTAG, USB ,PLL

SYNC_DATE=N/A

SYNC_MASTER=N/A

50_AP_BI_WLAN_HSIC3_DATA

PP1V8

RESET_1V8_L

PP1V0

PP1V2

AP_TO_PMU_TEST_CLKOUT

PP1V0

PP1V8

PP1V8

TRISTAR_BI_AP_JTAG_SWDIO

TRISTAR_TO_AP_JTAG_SWCLK

50_AP_BI_WLAN_HSIC3_STB

50_AP_BI_BB_HSIC1_DATA

CPU1_SWITCH

CPU0_SWITCH

WDOG

XTAL_24M_O_R

XTAL_GND

PP1V8_PLL

PP3V3_USB

50_AP_BI_BB_HSIC1_STB

USB_VBUS_DETECT

90_AP_BI_TRISTAR_USB0_N

90_USBHS_H5P_N

90_AP_BI_TRISTAR_USB0_P

90_USBHS_H5P_P

45_XTAL_24M_I

USB_REXT

45_XTAL_24M_O

051-0143

3.0.0

2 OF 22

2 OF 49

1 2

1 2

2

1

2

1

1

2

2

1

2

1

2

1

1 2

1 2

2

1

2

1

2

1

42

1 3

21

1 2

2

1

A19

AP14

H28

E29

E27

A31

A32

D34

C34

F28

AV10

AN13

AV15

A12

AT13

J22

G21

J20

G20

J21

J18

G18

J19

J26

G29

G28

AR16

AT15

AM15

AP15

AN15

M29

AK17

J29

L29

K29

AK16

G19

AU15

E33

AR9

A13

F29

F33

F34

L28

J28

N8

K16

AV13

R28

A30

AV11

AM14

AN16

AM16

AU10

G27

H29

H26

H27

K28

M28

AL17

AL16

E34

2

1

2

1

1

2

2

1

1 2

1 2

2

1

2

1

22

2 3 4 5 6 7 9

10 11 13 17 18

19 20

11 12 13 15 21 22

2 7

11

4

11

12

2 7

11

2 3 4 5 6 7 9

10 11 13 17 18

19 20

2 3 4 5 6 7 9

10 11 13 17 18

19 20

15

15

22

22

11

11

12

11

22

11

15

15

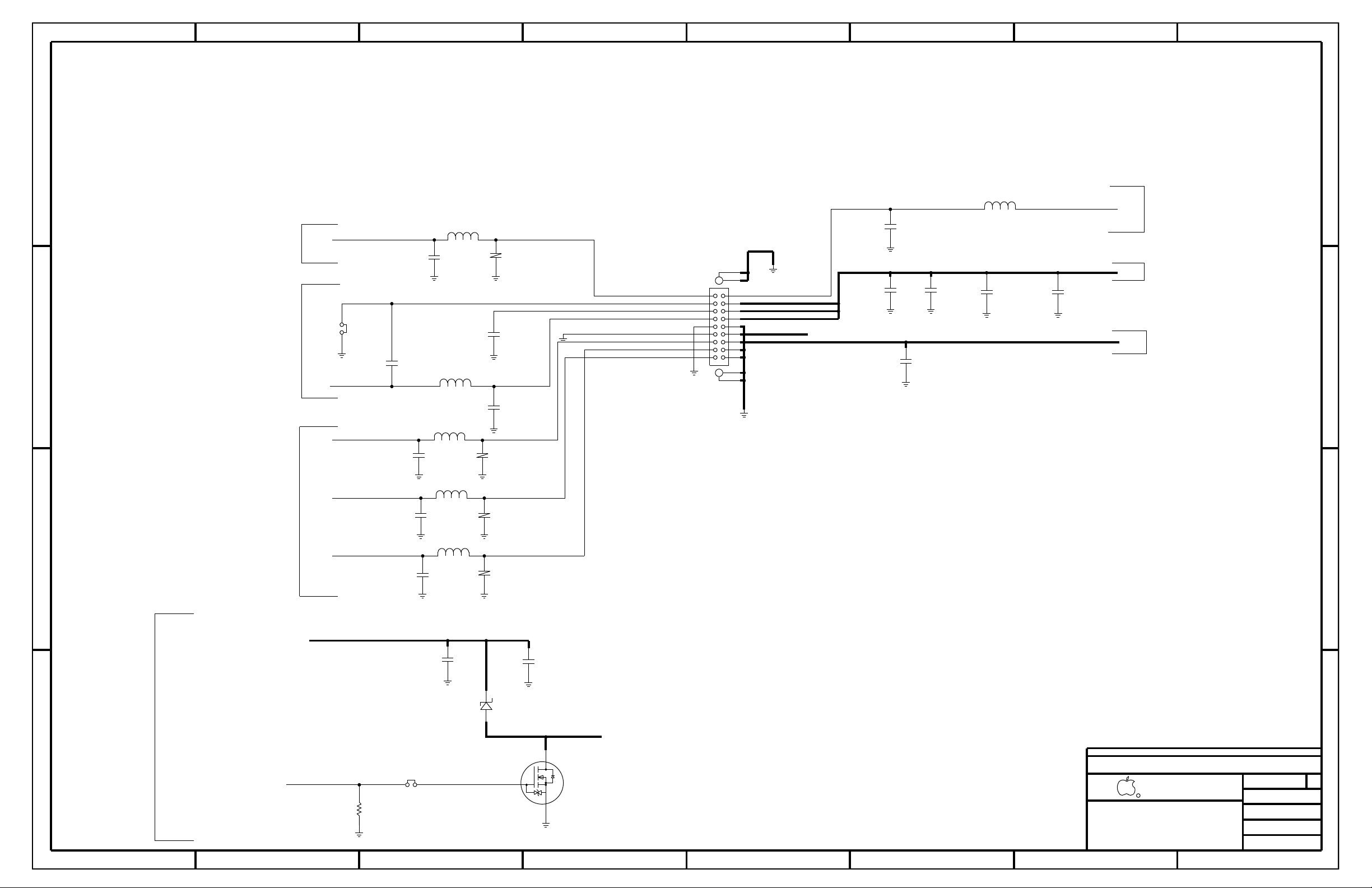

Page 3

PP

PP

1Y

GND

2Y

2A

1A

VCC

PP

SYM 2 OF 12

GPIO7

GPIO9

UART6_TXD

UART6_RXD

UART6_RTSN

UART6_CTSN

UART5_TXD

UART5_RXD

UART3_TXD

UART3_RTSN

UART3_CTSN

UART2_RXD

UART1_RXD

UART1_CTSN

UART0_TXD

UART0_RXD

TMR32_PWM2

TMR32_PWM1

TMR32_PWM0

GPIO_VSEL25_SPI3

GPIO_VSEL25_I2C2

GPIO_SVSEL18_FMI

GPIO_3V1

GPIO_3V0

GPIO8

GPIO6

GPIO5

GPIO4

GPIO39

GPIO38

GPIO37

GPIO36

GPIO35

GPIO34

GPIO33

GPIO32

GPIO31

GPIO30

GPIO3

GPIO29

GPIO28

GPIO27

GPIO26

GPIO25

GPIO24

GPIO23

GPIO22

GPIO21

GPIO20

GPIO2

GPIO19

GPIO18

GPIO17

GPIO16

GPIO1

GPIO0

EHCI_PORT_PWR3

EHCI_PORT_PWR2

EHCI_PORT_PWR1

EHCI_PORT_PWR0

UART3_RXD

GPIO_SVSEL25_FMI

GPIO12/SDIO_D1

GPIO13/SDIO_D0

GPIO14/SDIO_CMD

GPIO15/SDIO_CLK

UART4_CTSN/SPI4_SSIN

UART4_RTSN/SPI4_SCLK

UART4_RXD/SPI4_MISO

UART4_TXD/SPI_MOSI

UART1_RTSN

UART2_TXD

UART2_RTSN

UART2_CTSN

UART1_TXD

GPIO11/SDIO_D2

GPIO10/SDIO_D3

SYM 3 OF 12

SPI3_SSIN

SPI3_MOSI

SPI3_MISO

SPI3_SCLK

I2S4_MCK

I2S4_LRCK

I2S4_DIN

I2S4_BCLK

I2S4_DOUT

SPDIF

SPI0_MISO

SPI0_MOSI

SPI0_SCLK

SPI0_SSIN

SPI1_MISO

SPI1_SCLK

SPI1_MOSI

SPI1_SSIN

SPI2_MISO

SPI2_SCLK

SPI2_MOSI

SPI2_SSIN

I2S1_BCLK

I2S1_MCK

I2S0_DOUT

I2S0_DIN

I2S3_DIN

I2S3_DOUT

SWI_DATA

I2S3_MCK

I2S3_LRCK

I2S3_BCLK

I2S2_MCK

I2S2_LRCK

I2S2_DIN

I2S2_BCLK

I2S1_LRCK

I2S1_DOUT

I2S1_DIN

I2S0_MCK

I2S0_BCLK

I2C2_SDA

DWI_DO

DWI_DI

DWI_CLK

I2S2_DOUT

I2C2_SCL

I2C1_SDA

I2C1_SCL

I2C0_SDA

I2C0_SCL

I2S0_LRCK

PP

PP

PP

PP

PP

PP

PP

PP

PP

PP

PP

PP

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

GRAPE

<--- SELECTED

BOOT_CONFIG[3:0]={GPIO29_CONFIG3,GPIO28_CONFIG2,GPIO25_CONFIG1,GPIO18_CONFIG0}

<--- SELECTED

BOARD_ID[3:0]={GPIO16,SPIO0_MISO,SPI0_MOSI,SPI0_SCLK}

BOARD_REV[3:0]={EHCI_PORT3,EHCI_PORT_PWR2,EHCI_PORT_PWR1,EHCI_PORT_PWR0}

1011 - PROTO1 TRISTAR 2

1010 - EVT TRISTAR 2

FLOAT=LOW, PULLUP=HIGH

<---EVT SELECTED

1000 FMI1 2 CS

BOARD_ID0

BOARD_ID1

0010 SPI0 W/TEST

0001 SPI3

0000 SPI0

FLOAT=LOW, PULLUP=HIGH

1110 X64 MLB

BOARD_ID2

FLOAT=LOW, PULLUP=HIGH

0110 FMI0 4CS W/TEST

CODEC ASP

MENU & POWER / HOLD KEY

BASEBAND

1111 RESERVED

0100111X

1100011X

CHESTNUT:

TRISTAR:

LM3534:

CS35L20 AMP:

0001100X

????????

AP3GDL20-BC GYRO:

AP3DSH ACCEL:

1110 FMI0/1 4/4 CS W/TEST

1100 FMI0/1 2/2 CS

BOARD_ID3

BB_JTAG_TDO

WIFI UART

GAS GAUGE

DFU STATUS

BOOT_CONFIG3

0111 RESERVED

0011 SPI3 W/TEST

SPI3, 0=1.8V | 1=3.0V

I2C2, 0=1.8V | 1=3.0V

DEBUG UART: TOLERANCE 1.98V

AGATHA PMU:

I2C1

<50MHZ

1101010X

0011101X

0011010X

1110100X

CT814 ALS:

0101001X

AK8963C COMPASS:

FMI, 00=1.8V | 01=3.0V | 10=3.3V

CODEC

BT

<50MHZ

0100 FMI0 2CS

RESERVED

BOOT_CONFIG2

DEV_HSIC1_RDY

RESERVED FOR NON-TRISTAR DESIGN --->

BB

I2C0

I2C2

1101 FMI0/1 4/4 CS

1001 FMI1 4 CS

1010 FMI1 4CS W/TEST

0101 FMI0 4CS

NEW --->

(OPEN DRAIN@PMU)

BOOT_CONFIG0

BLUETOOTH

SPKR AMP

BOOT_CONFIG1

CODEC XSP

I2S PROBE POINTS

R12 MUST WIN OVER 6X INTERNAL PULL-DOWNS THAT ARE ~100K

COMMON PULL UP FOR BOARD_REV, BOARD_ID AND BOOT_CONFIG PINS

L19A KEEP (STAYING) ALIVE -->

BB_JTAG_TCK

BB_JTAG_TDI

BB_JTAG_TMS

BOARD_REV2

BOARD_REV1

BOARD_REV3

BOARD_REV0

1/32W

MF

01005

33.2

1%

R16

R12

1.00K

01005

R17

2.2K

01005

MF

5%

1/32W

R18

1/32W

MF

5%

01005

2.2K

R19

01005

MF

5%

2.2K

1/32W

R21

01005

MF

5%

1/32W

2.2K

R5

33.2

1/32W

01005

MF

1%

R52

220K

MF

5%

1/32W

01005

R20

01005

1/32W

MF

392K

1%

R22

MF

1/32W

01005

392K

1%

PP15

P4MM-NSM

SM

PP13

P4MM-NSM

SM

U25

74AUP2G34GN

SOT1115

PP5

P2MM-NSM

SM

R47

1/32W

MF1%

01005

33.2

H5P-SC58950C0E

U1

FCMSP

U1

H5P-SC58950C0E

FCMSP

R91

2.2K

5%

1/32W

MF

01005

R92

MF

5%

2.2K

1/32W

01005

PP196

SM

P2MM-NSM

PP195

SM

P2MM-NSM

PP194

SM

P2MM-NSM

PP201

SM

P2MM-NSM

SM

PP200

P2MM-NSM

PP199

SM

P2MM-NSM

PP198

SM

P2MM-NSM

PP203

SM

P2MM-NSM

PP202

SM

P2MM-NSM

PP197

SM

P2MM-NSM

PP204

SM

P2MM-NSM

PP205

SM

P2MM-NSM

H5P GPIO & CONTROL

SYNC_DATE=N/A

SYNC_MASTER=N/A

AP_TO_CODEC_SPI3_CS_L

CODEC_TO_AP_SPI3_MISO

AP_TO_WLAN_HSIC2_RDY

AP_TO_TOUCH_SPI1_CLK

LCM_TO_AP_PIFA

BOARD_INFO

BOARD_INFO

TOUCH_TO_AP_SPI1_MISO

BB_TO_AP_IPC_GPIO

WLAN_TO_AP_HSIC2_RDY

BB_TO_AP_HSIC1_RDY

CODEC_TO_AP_INT_L

PP1V8

PP1V8

FORCE_DFU

LCM_TO_AP_HIFA_BSYNC

AP_TO_BB_HSIC1_RDY

BOARD_INFO

KEEPACT

AP_TO_BB_JTAG_TCK

PMU_TO_AP_IRQ_L

AP_TO_SPKAMP_BEE_GEES

AP_TO_TOUCH_SPI1_CS_L

AP_TO_TOUCH_SPI1_MOSI

AP_TO_CODEC_SPI3_MOSI

BB_TO_AP_UART1_CTS_L

AP_TO_BB_UART1_RTS_L

TRISTAR_TO_AP_INT

AP_TO_BB_UART1_TXD

BB_TO_AP_UART1_RXD

AP_TO_LEDDRV_EN

45_AP_TO_TOUCH_CLK32K_RESET_L

AP_TO_BT_I2S3_DOUT

BT_TO_AP_I2S3_DIN

45_AP_TO_BT_I2S3_BCLK

45_AP_TO_CODEC_I2S_MCLK

AP_TO_CODEC_ASP_I2S0_DOUT

CODEC_TO_AP_ASP_I2S0_DIN

45_BB_TO_AP_I2S1_BCLK

BB_TO_AP_I2S1_LRCLK

BB_TO_AP_I2S1_DIN

AP_TO_BB_I2S1_DOUT

45_I2S2_MCK_R

45_AP_TO_CODEC_ASP_I2S0_BCLK

AP_TO_CODEC_ASP_I2S0_LRCLK

45_AP_TO_PMU_DWI_DO

45_AP_TO_PMU_DWI_DI

AP_TO_I2C2_SCL

AP_BI_I2C1_SDA

AP_BI_I2C0_SDA

AP_TO_BT_WAKE

BOARD_INFO

BUTTON_TO_AP_MENU_KEY_BUFF_L

PP1V8_ALWAYS

BUTTON_TO_AP_HOLD_KEY_BUFF_L

AP_TO_TRISTAR_DEBUG_UART6_TXD

PP1V8_SDRAM

GYRO_TO_AP_INT1

AP_TO_RADIO_ON_L

BT_TO_AP_UART3_CTS_L

AP_TO_BT_UART3_RTS_L

AP_TO_BT_UART3_TXD

AP_TO_BB_JTAG_TRST_L

WLAN_TO_AP_UART4_RXD

AP_TO_WLAN_UART4_TXD

BB_TO_AP_RESET_DET_L

AP_TO_CAM_RF_VDDCORE_EN

AP_BI_BATTERY_SWI

TRISTAR_TO_AP_DEBUG_UART6_RXD

TRISTAR_TO_AP_ACC_UART2_RXD

AP_TO_TRISTAR_ACC_UART2_TXD

AP_TO_BT_I2S3_LRCLK

45_I2S0_MCK_R

AP_TO_LCM_RESET_L

TOUCH_TO_AP_INT_L

BT_TO_AP_UART3_RXD

AP_TO_BB_JTAG_TMS

BB_TO_AP_HSIC1_REMOTE_WAKE

BUTTON_TO_AP_HOLD_KEY_L

BUTTON_TO_AP_MENU_KEY_BUFF_L

ACCEL_TO_AP_INT1

AP_TO_BB_JTAG_TDI

COMPASS_TO_AP_INT_2

AP_TO_BB_WAKE_MODEM

AP_TO_TOUCH_GRAPE_RESET_L

AP_TO_SPKAMP_RESET_L

BB_TO_AP_PP_SYNC

AP_TO_I2C0_SCL

PP1V8

AP_TO_I2C1_SCL

45_AP_TO_PMU_DWI_CLK_H5P

45_AP_TO_PMU_DWI_CLK

AP_BI_I2C2_SDA

AP_TO_HEADSET_HS4_CTRL

AP_TO_HEADSET_HS3_CTRL

ALS_TO_AP_INT_L

ACCEL_TO_AP_INT2

WLAN_TO_AP_HSIC2_REMOTE_WAKE

AP_TO_CODEC_XSP_I2S4_LRCLK

45_AP_TO_SPKAMP_I2S2_MCLK

AP_TO_SPKAMP_XSP_I2S2_LRCLK

45_AP_TO_SPKAMP_XSP_I2S2_BCLK

SPKAMP_TO_AP_XSP_I2S2_DIN

AP_TO_SPKAMP_XSP_I2S2_DOUT

AP_TO_CODEC_XSP_I2S4_DOUT

45_AP_TO_CODEC_ASP_I2S0_BCLK

45_AP_TO_CODEC_XSP_I2S4_BCLK

CODEC_TO_AP_XSP_I2S4_DIN

AP_TO_SPKAMP_XSP_I2S2_DOUT

SPKAMP_TO_AP_XSP_I2S2_DIN

CODEC_TO_AP_ASP_I2S0_DIN

AP_TO_CODEC_ASP_I2S0_DOUT

BT_TO_AP_I2S3_DIN

AP_TO_BT_I2S3_DOUT

AP_TO_CODEC_XSP_I2S4_DOUT

45_AP_TO_BT_I2S3_BCLK

45_AP_TO_SPKAMP_XSP_I2S2_BCLK

BB_TO_AP_JTAG_TDO

BUTTON_TO_AP_MENU_KEY_L

45_AP_TO_CODEC_XSP_I2S4_BCLK

CODEC_TO_AP_XSP_I2S4_DIN

AP_TO_BB_RST_L

BUTTON_TO_AP_VOL_DOWN_L

BUTTON_TO_AP_VOL_UP_L

BUTTON_TO_AP_HOLD_KEY_BUFF_L

SPKAMP_TO_AP_INT_L

PP1V8

BUTTON_TO_AP_RINGER_A

PP1V8

VIB_PWM

PP1V8

GYRO_TO_AP_INT2

AP_TO_CODEC_SPI3_CLK

051-0143

3.0.0

3 OF 22

3 OF 49

1 2

1 2

1

2

1

2

1

2

1

2

1 2

1

2

1

2

1

2

1

1

6

2

4

3

1

5

1

1 2

M3

P4

AD1

AK3

AL1

AH2

AJ3

AK4

AG4

AB1

AH3

AE2

AB3

AA3

AU12

AR15

AP1

AP8

AT6

AT12

AR13

AU13

AP12

AT11

U3

P3

W2

T4

D19

C19

D20

C20

D21

C21

D22

C22

L32

K32

V3

M32

L34

P31

P30

L33

N32

P32

P33

P34

R31

M4

V4

AC2

V1

T3

N2

W3

AE3

AD4

AD3

AE4

AF4

AR14

R3

N3

M1

AC3

AJ4

AE1

AJ2

AH4

AB2

AF3

AA1

AG3

AF5

M2

W1

AN12

AM9

AP9

AM13

AK30

AP32

AK32

AM32

AR32

AR31

AM4

AR5

AM2

AP3

AN3

AK1

AL3

AR4

AN4

AN6

AM3

AN1

AL31

AK29

AJ30

AH30

AL30

AP31

AP5

AM31

AL28

AK31

AM29

AJ31

AM33

AM28

AN31

AH32

AH29

AP30

AM30

AR8

AM8

AV7

AT7

AN30

AT9

AT3

AV6

AT4

AR7

AH31

1

2

1

2

1

1

1

1

1

1

1

1

1

1

1

1

9

9

22

17

18

3

3

17

22

22

22

9

2 3

4 5 6 7 9

10 11 13 17 18 19

20

2 3

4 5 6 7 9

10 11 13 17 18 19

20

21

17 18

22

3

12

22

12

14

17

17

22

22

12 15

15 22

15 22

14

17

3

22

3

22

3

22

9

3 9

3 9

22

22

22

22

3 9

9

12 13

12

10

19

12 13 14 15 19

22

3

3

12

11

3

12

15

4 9

11 12 13 15 22

19

22

22

22

22

22

22

22

22

20

12 21

15

15

15

22

18

17

22

22

22

8

3

12

19

22

19

22

17

14

22

12 13 14 15 19

2 3 4 5 6 7 9

10 11 13 17 18 19

20

19

12 13

10

16

16

10

19

22

9

14

14

3

14

3

14

3

14

3 9

3 9

3 9

3 9

3

14

3

14

3 9

3 9

3

22

3

22

3 9

3

22

3

14

22

16

3 9

3 9

22

8

12

8

12

3

12

14

2 3 4 5 6 7 9

10 11 13 17 18 19

20

8

12

2 3 4

5 6 7 9

10 11 13 17 18 19 20

8

2 3 4

5 6 7 9

10 11 13 17 18 19 20

19

9

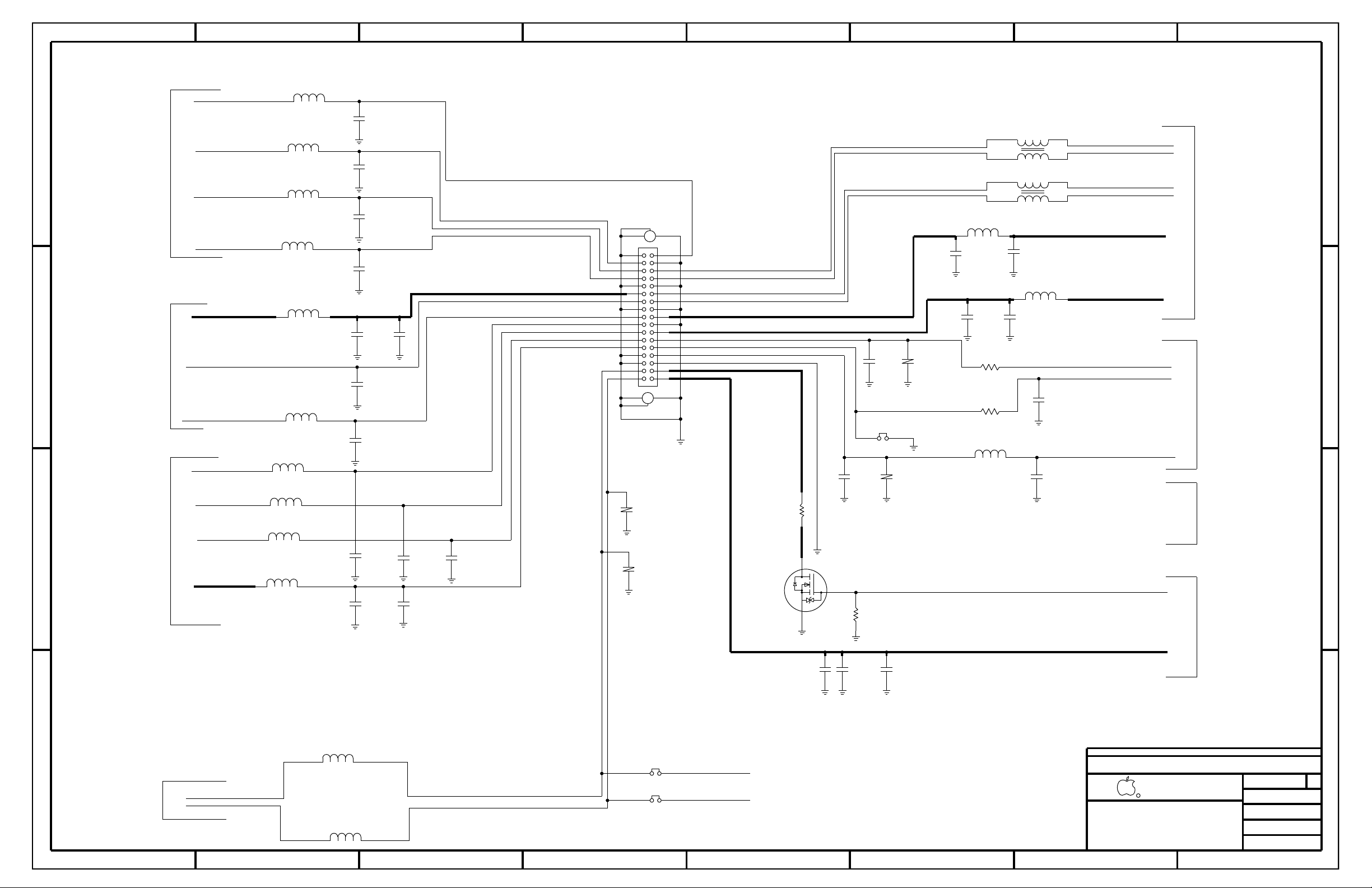

Page 4

SYM 7 OF 12

DDR1_RREF

VDDCA

DDR1_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

VDD2

DDR0_VDD_CKE

DDR1_VDD_CKE

DDR0_ZQ

DDR1_ZQ

DDR0_VREF_CA

VSS

VDD1

VDDQ

DDR0_RREF

SYM 9 OF 12

PVDDP_I2C2_SDA

VDDIO18_GPIO22

VSS

VDDIO18_I2S0_MCK

VDDIO18_GRP2

VDDIO18_GRP1

VDDIOD

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

(DDR IMPEDANCE CONTROL)

(18MA)

(340MA)

CAPS FOR VDDIOD ARE SHARED WITH VDDQ

(<1MA)

(8MA)

(INCLUDED IN VDDQ)

POR CAPS NOV/1/2010

(7MA)

(45MA)

(<1MA)

(20MA)

BUCK4 1P2

(80MA)

POR CAPS 9/1/11

(666MA)

01005

MF

243

1%

1/32W

R34

1%

243

MF

01005

1/32W

R33

01005

10K

MF

1/32W

1%

R13

01005

10K

MF

1%

1/32W

R11

01005

10K

1%

MF

1/32W

R14

01005

10K

MF

1%

1/32W

R24

01005

1%

4.7K

1/32W

MF

R25

01005

4.7K

1%

1/32W

MF

R27

01005

MF

1/32W

1%

4.7K

R28

01005

MF

1/32W

1%

4.7K

R29

0204

X7S

0.47UF

4V

20%

C88

20%

4V

X6S

1UF

0204

C75

20%

4V

4.3UF

X5R-CERM

0610

C87

4V

0.47UF

20%

X7S

0204

C89

20%

4V

0610

4.3UF

X5R-CERM

C85

4V

20%

X6S

0204

1UF

C77

X5R-CERM

4.3UF

0610

20%

4V

C72

01005

X5R-CERM

6.3V

0.1UF

20%

C81

01005

X5R

10%

6.3V

0.01UF

C60

01005

X5R

10%

0.01UF

6.3V

C66

01005

X5R

10%

6.3V

0.01UF

C78

01005

X5R

10%

0.01UF

6.3V

C80

01005

X5R

6.3V

0.01UF

10%

C90

01005

X5R

6.3V

0.01UF

10%

C91

01005

X5R

6.3V

0.01UF

10%

C94

01005

X5R

6.3V

0.01UF

10%

C96

20%

4V

X5R-CERM

0201

2.2UF

C123

0204

X7S

0.47UF

4V

20%

C883

01005

NP0-C0G

5%

6.3V

56PF

C390

56PF

5%

6.3V

01005

NP0-C0G

C388

1KOHM-25%-0.2A

0201

FL40

H5P-SC58950C0E

FCMSP

U1

H5P-SC58950C0E

FCMSP

U1

0.1UF

01005

6.3V

20%

X5R-CERM

NOSTUFF

C816

NP0-C0G-CERM

16V

5%

15PF

01005

C953

0402-2

10UF

20%

6.3V

CERM-X5R

C68

10UF

0402-2

20%

6.3V

CERM-X5R

C76

H5P IO POWER

SYNC_MASTER=N/A

SYNC_DATE=N/A

PP1V8_XTAL

DDR1_ZQ

DDR1_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

PP1V2_SDRAM

DDR0_ZQ

DDR0_VREF_CA

PP1V8_SDRAM

DDR0_ZQ

DDR1_VREF_CA DDR0_VREF_DQ

DDR1_VREF_DQ

DDR0_VREF_CA

PP1V2_SDRAM

PP1V2

PP1V8

PP1V2_SDRAM

PP1V2

DDR1_ZQ

PP1V2

051-0143

3.0.0

4 OF 22

4 OF 49

1 2

1 2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

21

AN34

K3

V2

AT1

AR33

AU14

AK34

B31

R2

AU16

AU7

AN33

L16

N9

AV3

AP34

AV8

A3

AA2

A1

A2

AT30

AV9

B15

C1

C12

C27

D18

D7

E1

E12

E23

F16

F5

G3

G32

H15

J1

K30

L19

M16

N15

P10

R32

R9

T20

U6

V29

W21

W23

W25

Y1

Y12

Y14

Y16

Y18

Y2

Y20

Y22

Y24

Y10

Y29

Y3

Y32

Y4

Y5

Y8

AD33

AJ33

AA34

AF1

AL33

B10

B11

B29

M34

P1

R1

A10

A11

AB33

AF2

AT33

AU3

AV16

B32

M33

T2

AD2

AG2

AK2

AN2

AR2

B12

B14

B17

B20

B22

B25

B27

B30

B5

B7

B9

C33

D2

F2

G33

J2

K33

L2

N33

P2

T33

U2

W33

AU5

AU9

AV4

AT10

R29

AG33

AG31

AF24

AE13

AE15

D33

AR25

AK6

AK5

AK33

AJ9

AJ6

AJ5

AJ32

AJ29

AJ27

AJ25

AJ23

AJ21

AJ19

AJ17

AJ15

AJ13

AJ11

AJ1

AH8

AH6

AH5

AH33

AH28

AH26

AH24

AH22

AH20

AH18

AH16

AH14

AH12

AH10

AG9

AG6

AG5

AG34

AG32

AG30

AG29

AG28

AG27

AG25

AG21

AG19

AG17

AG15

AG13

AG11

AG1

AF8

AF6

AF34

AF32

AF31

AF30

AF29

AF28

AF26

AF22

AF18

AF16

AF14

AF12

AF10

K26

AE27

AE23

AE19

AE17

AK28

AJ28

K21

K20

AK9

AK8

AK7

AK15

AK14

AJ7

AG7

AF7

AE7

AD7

AC7

AB7

AA7

Y7

Y6

W7

W5

V7

V6

U7

U5

T7

T6

R7

R5

P7

P6

N7

N5

M7

M6

K7

J14

J13

J12

AK13

AK12

AK11

AK10

AF33

H12

H10

G17

AG23

AE25

J9

J8

J7

G5

G15

J10

J11

H8

J15

J16

J17

J5

AE21

AH7

K6

L5

L7

G13

G11

AF20

H6

H16

H14

G9

G7

2

1

2

1

2

1

2

1

4

4

4

4

4

11

4

4

3 9

11 12 13 15 22

4

4 4

4

4

4

11

2 4

11

2 3 5 6 7 9

10 11 13 17 18 19

20

4

11

2 4

11

4

2 4

11

Page 5

SYM 8 OF 12

VDD_ANA_TMPSADC0

VDD_ANA_TMPSADC1

VDD_ANA0

VDD_ANA1

PVDDP_FAST_SCAN_CLK

VSS

VDDIOD1

VDDIOD0

VDDIO30_GPIO_3V0

VDDIO30_USB11_DM

VDDIO30_FAST_SCAN_CLK

VDD_SRAM

VDD_CPU1

VDD_CPU0

VDD_CPUB

VDDIOD3

VDDIOD2

SYM 10 OF 12

VDD

VDD

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

POR CAPS 9/1/2011

PER SEG - ZHENGGANG - 09/01/12 PRE-PROTO1

(2MA I2C2)

BUT THEY WERE NOT NEEDED PER P.CODD 1/6/11

THERE WERE 10X 0.01UF HERE

C181,C177,C174 CHANGED FROM 0.47UF TO 1UF

(VDD_SOC 3700MA)

NAND POWER GROUP

(45MA NAND 1CH)

(716MA)

(400MA)

(40MA)

(2MA)

(7MA)

(45MA NAND 1CH)

(5MA)

(5MA)

(5MA)

(2MA SPI3)

POR CAPS 12/14/2011

(1500MA)

(1500MA)

POR CAPS 5/6/2011

C83 MOVED TO CPUB FROM 1V2_SDRAM PER SEG SIM RESULTS

C86 MOVED TO PP1V1_SOC FROM PP1V2, PER SEG SIMS

C104 MOVED TO CPU0 FROM PP1V8 PER SEG SIMS

X7S

0.47UF

0204

20%

4V

C158

X5R-CERM

20%

4V

0610

4.3UF

C117

X7S

20%

0.47UF

4V

0204

C140

0204

20%

4V

X7S

0.47UF

C142

0204

X7S

20%

0.47UF

4V

C154

6.3V

0.22UF

0201

X5R

20%

C139

20%

4.3UF

0610

X5R-CERM

4V

C127

X6S

20%

1UF

4V

0204

C145

4.3UF

20%

4V

X5R-CERM

0610

C112

6.3V

01005

0.1UF

X5R-CERM

20%

C183

0.1UF

20%

01005

X5R-CERM

6.3V

C178

20%

0610

X5R-CERM

4.3UF

4V

C172

4V

0610

4.3UF

20%

X5R-CERM

C164

0204

4V

1UF

X6S

20%

C179

X6S

4V

1UF

20%

0204

C175

SHORT-10L-0.1MM-SM

XW1

SHORT-10L-0.1MM-SM

XW3

SHORT-10L-0.1MM-SM

XW4

0610

X5R-CERM

4V

4.3UF

20%

C115

0%

MF

01005

1/32W

0.00

R46

0.00

01005

0%

1/32W

MF

R53

0610

X5R-CERM

4V

20%

4.3UF

C146

4.3UF

0610

X5R-CERM

4V

20%

C152

20%

0402

CERM

0.47UF

6.3V

C135

4V

20%

1UF

CERM

0402

C151

0402

1UF

20%

4V

CERM

C113

0402

6.3V

0.47UF

CERM

20%

C132

CERM

4V

0402

20%

1UF

C114

0.47UF

0402

20%

CERM

6.3V

C133

CERM

4V

20%

0402

1UF

C166

0402

20%

1UF

4V

CERM

C173

CERM

6.3V

0.47UF

0402

20%

C169

1UF

X6S

0204

20%

4V

C103

0204

X6S

4V

1UF

20%

C101

FCMSP

H5P-SC58950C0E

U1

FCMSP

H5P-SC58950C0E

U1

0204

4V

20%

X6S

1UF

C745

4V

X7S

0204

20%

0.47UF

C746

20%

4V

X5R-CERM

0610

4.3UF

C106

20%

4V

X5R-CERM

0610

4.3UF

C108

01005

1/32W

0%

MF

0.00

R953

56PF

6.3V

01005

NP0-C0G

5%

C148

4V

X6S

1UF

20%

0204

C83

1UF

4V

0204

20%

X6S

C104

4V

0204

X6S

20%

1UF

C86

0204

20%

1UF

4V

X6S

C181

0204

20%

1UF

4V

X6S

C177

1UF

CERM

4V

20%

0402

C174

0402-2

10UF

20%

6.3V

CERM-X5R

C100

CERM-X5R

6.3V

20%

10UF

0402-2

C111

0402-2

10UF

20%

6.3V

CERM-X5R

C134

0402-2

10UF

20%

6.3V

CERM-X5R

C155

6.3V

20%

0402-2

CERM-X5R

10UF

C161

0402-2

10UF

20%

6.3V

CERM-X5R

C162

CERM-X5R

0402-2

20%

6.3V

10UF

C171

SYNC_MASTER=N/A

SYNC_DATE=N/A

H5P SOC/CPU/SRAM PWR

PP1V0_SRAM

PP1V1_SOC

PP1V1_CPU0

PP1V8

PP3V0_IO

PP1V1_CPU1

CPU1_SENSE

CPU0_SW_S

BUCK2_FB

CPU1_SW_S

CPU0_SENSE

PP1V8

PP1V1_CPUB

PP3V0_NAND

051-0143

3.0.0

5 OF 22

5 OF 49

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

2

1

21

21

21

2

1

1 2

1 2

2

1

2

1

143

2

143

2

143

2

143

2

143

2

143

2

143

2

143

2

143

2

2

1

2

1

Y17

K18

AJ18

AJ22

AE11

AE5

AB29

F19

AB5

AB6

AR26

AP33

AA16

AC16

AD27

AP11

AN10

AR10

G30

F20

AF25

AF17

AD19

AD17

AB25

AB19

AB17

AJ24

AH25

AH23

AH21

AG24

AG22

AF23

AJ20

AJ16

AH19

AH17

AG20

AG18

AG16

AF19

AE20

AE18

AE16

AC24

AC18

AA24

AT19

AP16

AN21

AM22

AL13

AK27

AE9

AE6

AD8

AD6

AD5

AD32

AD29

AD26

AD24

AD22

AD20

AD18

AD16

AD14

AD12

AD10

AC9

AC6

AC5

AC4

AC34

AC25

AC23

AC21

AC19

AC17

AC15

AC13

AC11

AC1

AB8

AB4

AB32

AB26

AB24

AB22

AB20

AB18

AB16

AB14

AB12

AB10

AA9

AA6

AA5

AA4

AA33

AA25

AA23

AA21

AA19

AA17

AA15

AA13

AA11

A9

A8

A7

A6

A5

A4

A34

A33

A26

A23

A20

A18

A17

A16

A15

A14

A29

AC22

AC20

AA22

AA20

AA18

AF21

AE24

AE22

AB23

AB21

AD25

AD21

Y26

W27

V27

AC27

AB27

AD23

K15

AE8

AF11

AF13

AF15

AF27

T25

U12

T27

N18

M25

U10

AE14

AA10

AA12

AC12

T13

T15

T17

T19

T21

T23

T9

AC14

U14

U16

U18

U20

U22

U24

U26

U8

V11

AC26

V13

V15

V17

V19

V21

V23

V25

V9

W10

W12

W14

W16

W18

W20

W22

W24

W26

W8

Y11

Y13

Y15

Y9

Y19

Y21

Y23

Y25

AD13

AD15

AD9

AE10

AE12

AA14

AE26

AF9

AG10

AG12

AA26

AG14

AG26

AG8

AH11

AH13

AH15

AH27

AH9

AJ10

AJ12

AA8

AJ14

AJ26

AJ8

K11

K13

K17

K23

K25

AB11

K9

L10

L12

L14

L18

L20

L22

L24

L26

L8

AB13

M11

M13

M15

M17

M19

M21

M23

M27

M9

AB15

N10

N12

N14

N16

N20

N22

N24

N26

P11

AB9

P13

P15

P17

P19

P21

P23

P25

P27

P9

R10

AC10

R12

R14

R16

R18

R20

R22

R24

R26

R8

T11

AC8

AD11

K27

2

1

2

1

2

1

2

1

1 2

2

1

2

1

2

1

2

1

2

1

2

1

143

2

2

1

2

1

2

1

2

1

2

1

2

1

2

1

11

11

11

2 3 4 5 6 7 9

10 11 13 17 18

19 20

11

11

11

11

2 3 4 5 6 7 9

10 11 13 17 18

19 20

11

6

11

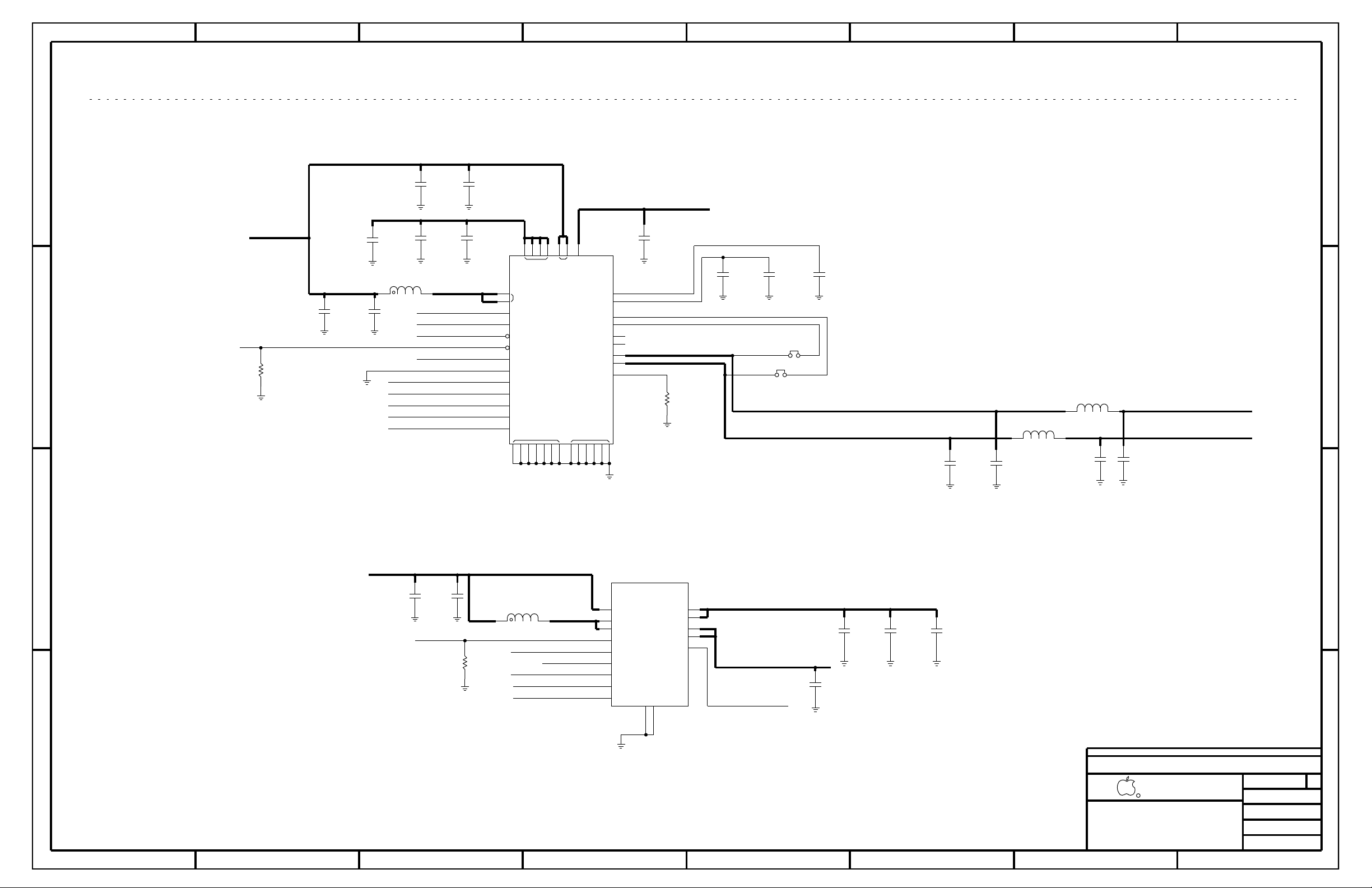

Page 6

IO0-1

IO7-1

IO6-1

IO3-1

IO4-1

IO5-1

IO1-1

IO2-1

IO7-0

IO5-0

IO6-0

IO4-0

IO2-0

IO3-0

IO1-0

IO0-0

VCC

CLE1

CE1*

CLE0

CE0*

WE0*

ALE0

RE0

RE0*

DQS0*

R/B0*

DQS0

ALE1

WE1*

RE1

RE1*

DQS1

DQS1*

R/B1*

ZQ

VREF

VSSQ

VSS

VCCQ

VDDI

TMSC

TCKC

PP

PP

SYM 4 OF 12

FMI1_VREFFMI0_VREF

FMI0_REN

FMI1_WEN

FMI1_DQS

FMI1_REN

FMI0_CLE

FMI0_WEN

FMI0_IO2

FMI0_IO3

FMI0_IO5

FMI1_DQSN

FMI0_ALE

FMI0_CEN0

FMI0_CEN1

FMI0_CEN2

FMI0_CEN3

FMI0_CEN4

FMI0_CEN5

FMI0_CEN6

FMI0_CEN7

FMI0_DQS

FMI0_DQSN

FMI0_DQVREF

FMI0_IO0

FMI0_IO1

FMI0_IO4

FMI0_IO6

FMI0_IO7

FMI1_ALE

FMI1_CEN0

FMI1_CEN1

FMI1_CEN2

FMI1_CEN3

FMI1_CEN4

FMI1_CEN5

FMI1_CEN6

FMI1_CEN7

FMI1_CLE

FMI1_DQVREF

FMI1_IO0

FMI1_IO1

FMI1_IO2

FMI1_IO3

FMI1_IO4

FMI1_IO5

FMI1_IO6

FMI1_IO7

PVDDP_FMI0 PVDDP_FMI1

FMI0_WENN/RE_P FMI1_WENN/RE_P

PP

PP

PP

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

500MA

NAND

1000MA

POR CAPS 1/7/11

NOTE: NAND PADS SHOULD BE SHIELDED FROM TRACES WITH A GROUND PLANE

FOR NAND CURRENT MEASUREMENT

C182

10UF

0402

CERM

6.3V

20%

0204

X6S

4V

20%

1UF

C107

01005

1/32W

MF

243

1%

R8

01005

NOSTUFF

MF

5%

1/32W

100K

R160

U4

LGA-12X17

XXNM-XGBX8-MLC-PPN1.5-ODP

OMIT_TABLE

5%

01005

MF

100K

1/32W

R82

5%

100K

MF

1/32W

01005

R78

X5R

10%

6.3V

0.01UF

01005

C136

0.01UF

01005

X5R

6.3V

10%

C144

C307

0402

CERM

6.3V

10UF

20%

1%

1/32W

MF

50K

01005

R137

50K

1%

1/32W

01005

MF

R143

20%

10UF

0402

CERM

C209

6.3V 6.3V

0402

CERM

C187

10UF

20%

SM

P2MM-NSM

PP17

SM

P2MM-NSM

PP19

C109

15UF

X5R

4V

20%

0402

0201-1

C50

20%

6.3V

X5R

1.0UF

C185

0204

X6S

4V

20%

1UF

X7S

0.47UF

20%

4V

0204

C105

20%

4.3UF

C627

4V

0610

X5R-CERM

20%

4V

X7S

0204

0.47UF

C605

NOSTUFF

100K

01005

MF

1/32W

5%

R48

H5P-SC58950C0E

FCMSP

U1

6.3V

CERM-X5R

0402-2

10UF

20%

C95

SM

P2MM-NSM

PP2

SM

P2MM-NSM

PP3

SM

P2MM-NSM

PP14

0201-1

1.0UF

C26

X5R

6.3V

20%

4V

20%

X6S

1UF

0204

C3

SYNC_MASTER=N/A

SYNC_DATE=N/A

H5P W/ NAND

FMI0_IO<5>

FMI0_IO<6>

PP1V2_NAND_VDDI

PP1V8

FMI0_IO<7>

NAND_RDYBSY0_L

45_FMI1_RE_L

45_FMI1_DQS

NAND_RDYBSY1_L

FMI0_DQVREF

FMI0_IO<0>

FMI1_CLE

FMI1_WE_L

FMI1_CEN0

FMI1_ALE

45_FMI0_RE_L

FMI0_IO<4>

NAND_TCKC

45_FMI0_DQS

PPN_ZQ

FMI0_DQVREF

PP1V8PP1V8

FMI1_IO<6>

FMI1_IO<4>

FMI1_IO<3>

FMI1_IO<2>

FMI0_DQVREF

FMI1_CLE

FMI1_CEN0

FMI1_ALE

FMI0_IO<7>

FMI0_IO<6>

FMI0_DQVREF

45_FMI0_DQS

FMI0_CEN0

FMI0_ALE

FMI0_IO<5>

FMI0_WE_L

FMI0_CLE

45_FMI1_DQS

FMI1_WE_L

45_FMI0_RE_L

FMI0_DQVREF FMI0_DQVREF

FMI1_IO<1>

FMI1_IO<0>

FMI0_IO<4>

FMI0_IO<3>

FMI0_IO<2>

FMI0_IO<1>

FMI0_IO<0>

FMI1_IO<5>

NAND_TMSC

FMI1_IO<7>

45_FMI1_RE_L

FMI0_IO<0>

45_FMI0_RE_L

45_FMI0_DQS

FMI0_IO<1>

FMI0_IO<2>

FMI0_IO<3>

PP1V8

PP3V0_NAND

FMI0_CLE

FMI0_ALE

FMI0_WE_L

FMI0_CEN0

051-0143

3.0.0

6 OF 22

6 OF 49

2

1

2

1

1 2

1

2

G1

G7

J7

N3

N5

L7

J1

L1

H6

K6

J5

L5

J3

K2

H2

G3

F2M6B6

C3

C5

A3

A5

E3

C1

B4

C7

F4

E5

H4

D2

E1

D4

D6

M4

K4

E7

A1

G5

OA8

OF8G0OE0

OD8

OC8

N7

OE8

OD0

OC0

A7M2L3F6B2

OF0

G8

N1

OB8

OB0

OA0

1

2

1

2

2

1

2

1

2

1

1

2

1

2

2

1

2

1

1

1

2

1

2

1

2

1

2

1

2

1

2

1

1

2

Y27

AE28

AC30

V28

V34

W30

AD30

AC29

AB34

AB31

AE31

V33

AC31

AE29

AE30

AE32

AE34

AA29

AB30

AA30

AB28

AC33

AC32

AD28

AA28

AA31

AD31

AD34

AE33

W29

W28

Y34

AA32

Y33

T34

V31

U34

U31

Y28

V30

U33

U29

V32

W32

W34

W31

Y30

Y31

AA27

U27

AC28

U28

2

1

1

1

1

2

1

2

1

6

6

2 3 4 5 6 7 9

10 11 13 17 18

19 20

6

6

6

6

6

6

6

6

6

6

6

6

6

2 3 4 5 6 7 9

10 11 13 17 18

19 20

2 3 4 5 6 7 9

10 11 13 17 18

19 20

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6 6

6

6

6

6

6

6

6

6

6

6

6

6

2 3 4 5 6 7 9

10 11 13 17 18 19

20

5

11

6

6

6

6

Page 7

SYM 11 OF 12

VSS VSS

SYM 12 OF 12

VSSVSS

SYM 5 OF 12

MIPI0D_VDD18

MIPI1D_VDD18

MIPI0D_VDD10_PLL

MIPI1D_VDD10_PLL

MIPI0C_DPDATA1

SENSOR1_RST

MIPI1D_DPCLK

MIPI1D_VREG_0P4V

MIPI0D_VREG_0P4V

MIPI_VDD10

MIPI_VSS

MIPI_VSYNC

MIPI0C_DNCLK

MIPI0C_DNDATA0

MIPI0C_DNDATA1

MIPI0C_DNDATA2

MIPI0C_DNDATA3

MIPI0C_DPCLK

MIPI0C_DPDATA0

MIPI0C_DPDATA2

MIPI0C_DPDATA3

MIPI0D_DNCLK

MIPI0D_DNDATA0

MIPI0D_DNDATA1

MIPI0D_DNDATA2

MIPI0D_DNDATA3

MIPI0D_DPCLK

MIPI0D_DPDATA0

MIPI0D_DPDATA1

MIPI0D_DPDATA2

MIPI0D_DPDATA3

MIPI1C_DPDATA1

SENSOR0_CLK

SENSOR0_RST

SENSOR1_CLK

MIPI1C_DNDATA1

MIPI1C_DPDATA0

ISP1_SDA

MIPI1C_DNDATA0

MIPI1D_DNCLK

MIPI1D_DPDATA1

MIPI1D_DNDATA1

MIPI1D_DPDATA0

MIPI1D_DNDATA0

ISP1_FLASH

ISP1_SCL

ISP0_PRE_FLASH

ISP0_SCL

ISP0_SDA

ISP1_PRE_FLASH

ISP0_FLASH

MIPI1C_DPCLK

MIPI1C_DNCLK

LPDP_PAD_TX0P

LPDP_PAD_TX0N

LPDP_PAD_TX1P

LPDP_PAD_TX1N

LPDP_PAD_R_BIAS

DAC_COMP

DP_PAD_DC_TP

DP_PAD_R_BIAS

LPDP_HPD

LPDP_PAD_AUXP

LPDP_PAD_AUXN

DAC_IREF

DAC_VREF

DAC_AVSS18D

DP_PAD_AVSS_AUX

DP_PAD_AVSS0

DP_PAD_AVSS1

DP_PAD_AVSSP0

DP_PAD_AVSSX

DP_PAD_DVSS

LPDP_PAD_AVSS0

LPDP_PAD_AVSS1

LPDP_PAD_AVSS2

DAC_AVSS18A2

DP_PAD_TX1N

DP_PAD_TX1P

DP_PAD_TX0N

DP_PAD_TX0P

DP_PAD_AUXN

DP_HPD

DAC_OUT1

DP_PAD_AUXP

DAC_OUT2

DAC_OUT3

LPDP_PAD_LN1_AVDD

LPDP_PAD_CMN_AVDD

LPDP_PAD_CMN_AVDDH

LPDP_PAD_LN0_AVDD

DP_PAD_AVDDX

DP_PAD_DVDD

LPDP_PAD_AUX_AVDD

DP_PAD_AVDD0

DP_PAD_AVDD1

DP_PAD_AVDDP0

DP_PAD_AVDD_AUX

DAC_AVDD18D

DAC_AVDD18A

SYM 6 OF 12

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

(1MA)

(28MA)

(15MA)

(11MA)

(12MA)

(12MA)

MAIN CAMERA

SHUTDOWN IS ALSO

RESET CAM1

FF CAMERA

(2MA)

(2MA)

(8MA)

(2X 65MA)

(0MA LPDP)

LPDP NOT USED, NO CAP NEEDED ON THIS PIN

01005

2200PF

6.3V

10%

X5R-CERM

C6

01005

X5R-CERM

10%

6.3V

2200PF

C7

20%

0.1UF

X5R-CERM

6.3V

01005

C191

33.2

1/32W

01005

MF

1%

R38

MF

1%

1/32W

33.2

01005

R40

20%

X5R-CERM

6.3V

0.1UF

01005

C53

X5R-CERM

20%

0.1UF

01005

6.3V

C57

1.00K

01005

5%

MF

1/32W

R37

01005

MF

5%

1/32W

1.00K

R39

01005

MF

5%

1.00K

1/32W

R41

01005

1.00K

5%

1/32W

MF

R42

6.3V

20%

0.1UF

01005

X5R-CERM

C268

20%

0.1UF

01005

X5R-CERM

6.3V

C58

01005

6.3V

NP0-C0G

5%

56PF

C259

NP0-C0G

6.3V

01005

56PF

5%

C274

01005

6.3V

56PF

5%

NP0-C0G

C280

5%

56PF

NP0-C0G

6.3V

01005

C284

20%

4V

4.3UF

X5R-CERM

0610

C266

H5P-SC58950C0E

FCMSP

U1

H5P-SC58950C0E

FCMSP

U1

H5P-SC58950C0E

FCMSP

U1

H5P-SC58950C0E

FCMSP

U1

SYNC_DATE=N/A

SYNC_MASTER=N/A

H5P VIDEO

90_AP_TO_LCM_MIPI_DATA3_P

90_CAM0_TO_AP_MIPI_DATA0_P

90_CAM0_TO_AP_MIPI_DATA3_N

90_CAM1_TO_AP_MIPI_CLK_P

90_CAM1_TO_AP_MIPI_CLK_N

90_CAM1_TO_AP_MIPI_DATA0_P

90_CAM1_TO_AP_MIPI_DATA0_N

45_AP_TO_CAM_FF_CLK_R

AP_TO_CAM_FF_SHUTDOWN

45_AP_TO_CAM_RF_CLK_R

AP_TO_CAM_RF_SHUTDOWN

45_AP_TO_CAM_RF_CLK

45_AP_TO_CAM_FF_CLK

AP_BI_CAM_RF_SDA

AP_TO_CAM_RF_SCL

CAM0_TORCH

AP_BI_CAM_FF_SDA

90_AP_TO_LCM_MIPI_DATA1_P

90_AP_TO_LCM_MIPI_DATA0_P

90_AP_TO_LCM_MIPI_CLK_P

90_AP_TO_LCM_MIPI_DATA3_N

90_AP_TO_LCM_MIPI_DATA0_N

90_AP_TO_LCM_MIPI_CLK_N

90_CAM0_TO_AP_MIPI_DATA2_P

90_CAM0_TO_AP_MIPI_DATA1_N

90_CAM0_TO_AP_MIPI_DATA0_N

MIPI0D_VREG

MIPI1D_VREG

90_CAM0_TO_AP_MIPI_DATA1_P

PP1V0

PP1V8

90_CAM0_TO_AP_MIPI_DATA2_N

90_CAM0_TO_AP_MIPI_DATA3_P

90_AP_TO_LCM_MIPI_DATA2_N

90_AP_TO_LCM_MIPI_DATA1_N

90_CAM0_TO_AP_MIPI_CLK_N

90_CAM0_TO_AP_MIPI_CLK_P

PP1V8

AP_TO_CAM_FF_SCL

90_AP_TO_LCM_MIPI_DATA2_P

PP1V8

PP1V0

051-0143

3.0.0

7 OF 22

7 OF 49

2

1

2

1

2

1

1 2

1 2

2

1

2

1

1

2

1

2

1

2

1

2

2

1

2

1

2

1

2

1

2

1

2

1

2

1

B19

B16

B13

D15

D14

C17

C16

C14

B33

B3

B28

B26

AL9

AM1

AM17

AM18

AM26

AN11

AN18

AN23

AN32

AP10

AR1

AP4

AP26

AP24

AP23

AL10

AL11

AL7

B24

B34

B4

B6

B8

C10

AL8

C11

C13

C15

C18

C2

C23

C24

C25

C26

C28

C29

C3

C30

C31

C32

C4

C5

C6

C7

C8

C9

D1

D10

D11

D12

D13

D16

D17

D23

D24

D25

D26

D27

D28

D29

D3

D30

D31

D32

D4

D5

D6

D8

D9

E10

E11

E13

E14

E15

E16

E17

E18

E19

E2

E20

E21

E22

E24

E25

E26

E28

E3

E30

E4

E5

E6

E7

E8

E9

AM7

AL12

AN14

AN17

AN19

AN20

AN22

AN24

AN25

AL14

AN26

AN5

AN7

AN8

AP13

AP17

AP18

AP19

AL15

AP20

AP21

AP22

AP25

AP7

AL29

AR11

AR17

AR18

AR19

AR20

AR21

AR22

AR23

AR24

AR27

AL32

AR28

AR29

AT14

AT16

AT17

AT18

AT2

AT20

AT21

AT22

AL4

AT23

AT24

AT25

AT26

AT27

AT28

AT29

AT31

AT32

AT5

AL5

AT8

AU1

AU2

AU33

AU34

AU4

AV1

AV14

AV2

AV33

AL6

AV34

AV5

B1

B18

B2

B21

B23

AM5

AM6

L9

M10

J6

F3

W9

W6

W4

W19

W17

W15

W13

W11

V8

V5

V26

V24

V22

V20

V18

V16

V14

V12

V10

U9

U4

U32

U25

U23

U21

U19

U17

U15

U13

U11

U1

T8

T5

T32

T31

T30

T29

T28

T26

T24

T22

T18

T16

T10

T1

R6

R4

R34

R25

R23

R21

R19

R17

R15

R13

R11

P8

P5

P26

P24

P22

P20

P18

P16

P14

P12

N6

N4

N34

N31

N27

N25

N23

N21

N19

N17

N13

N11

N1

M8

M5

M26

M24

M22

M18

M14

M12

L6

L4

L31

L3

L27

L25

L23

L21

L17

L15

L13

L11

L1

K8

K5

K4

K31

K24

K22

K2

K19

U30

K14

K12

K10

K1

J4

J33

J32

J31

J30

J3

J27

H9

H7

H5

H4

H33

H32

H31

H30

H3

H22

H21

H20

H17

H13

H11

H1

G8

G6

G4

G34

G31

M31

G22

G2

G16

G14

G12

G10

G1

F9

F8

F7

F6

F4

F32

F31

F30

F27

F22

F21

F18

F17

F15

F14

F13

F12

F11

F10

F1

E32

E31

R27

R30

R33

M20

T12

T14

H2

H19

H18

AM19

AM25

AM21

AM23

AU20

AM10

AU28

AK23

AK22

AK20

AK19

AM24

AK18

AK21

AM20

AK24

AK25

AK26

AL18

AL19

AL20

AL21

AL22

AL23

AL24

AL25

AL26

AR3

AV19

AV21

AV20

AV18

AV17

AU19

AU21

AU18

AU17

AV24

AV26

AV25

AV23

AV22

AU24

AU26

AU25

AU23

AU22

AU32

AN9

AP6

AP2

AV32

AU30

AU6

AV30

AV28

AU29

AV29

AU27

AV27

AU11

AL2

AM11

AR6

AH1

AM12

AR12

AU31

AV31

AM34

AL34

AJ34

AH34

AR30

P28

G26

F26

AV12

AT34

AR34

P29

N30

M30

H24

H23

F23

F24

F25

H25

AN27

AN28

AN29

N28

A21

A22

A24

A25

A27

AU8

K34

A28

J34

H34

AP29

AM27

AL27

AP28

G25

J25

AP27

J23

G23

G24

J24

L30

N29

18

20

20

10

10

10

10

10

20

20

10

14 20

14 20

14

10

18

18

18

18

18

18

20

20

20

20

2 7

11

2 3 4 5 6 7 9

10 11 13 17 18

19 20

20

20

18

18

20

20

2 3 4 5 6 7 9

10 11 13 17 18

19 20

10

18

2 3 4 5 6 7 9

10 11 13 17 18

19 20

2 7

11

Page 8

G

SYM_VER_1

D

S

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

516S1041 RCPT (FLEX)

MIC2/3 BIAS,

STROBE:

STROBE NTC

STROBE:

LED COOL

HOLD

BUTTONS:

MIC2_P,_N

MIC2 (ANC REF MIC):

BUTTONS:

516S1040 PLUG

VOL_UP/DOWN

VIBE DRIVE

(VIBE DRIVER, BUTTONS, ANC REF MIC, STROBE, STROBE_NTC)

RINGER,

POR TO REMOVE U70 AFTER EVT1 BUILD, TBD

BUTTON FLEX

ON MLB ---->

VIBE RETURN

12V-33PF

01005-1

DZ1

120-OHM-210MA

01005

FL3

100PF

5%

10V

NP0-C0G

01005

C314

120-OHM-210MA

01005

FL7

120-OHM-210MA

01005

FL8

120-OHM-210MA

01005

FL46

01005

NP0-C0G

10V

100PF

5%

C311

01005

10V

100PF

5%

NP0-C0G

C197

5%

NP0-C0G

10V

01005

100PF

C313

12V-33PF

01005-1

DZ2

01005-1

12V-33PF

DZ3

12V-33PF

01005-1

DZ7

M-ST-SM

105847-018

J2

16V

NP0-C0G

5%

100PF

01005

C120

BAS40LP

LLP-DFN1006-2

D3

NP0-C0G

100PF

01005

16V

5%

C1201

1%

MF

01005

1/32W

10K

R9401

DFN1006H4-3

DMN3730UFB4

Q7

SM

XW80

X5R

20%

4.7UF

402

6.3V

C118

01005

5%

16V

NP0-C0G

100PF

C241

01005

27PF

5%

NP0-C0G

16V

C208

NO_XNET_CONNECTION=TRUE

SHORT-10L-0.1MM-SM

XW41

NO_XNET_CONNECTION=TRUE

NP0-C0G

01005

6.3V

5%

56PF

C244

120-OHM-210MA

01005

FL47

NP0-C0G

6.3V

56PF

5%

01005

C45

1.0UF

20%

NO_XNET_CONNECTION=TRUE

0201-1

6.3V

X5R

C216

01005

120-OHM-210MA

FL21

56PF

6.3V

5%

01005

NP0-C0G

C397

5%

01005

16V

15PF

NP0-C0G-CERM

C398

01005

5%

CERM

18PF

16V

C399

SYNC_DATE=N/A

SYNC_MASTER=N/A

BUTTON FLEX B2B

PP3V1_VIBE

CAM_RF_TO_STROBE_NTC

BUTTON_TO_AP_HOLD_KEY_L

BUTTON_TO_AP_RINGER_A

VIB_PWM

VIBE_PWM_G

BUTTON_TO_AP_VOL_DOWN_L

PGND_VIBE_RETURN

BUTTON_TO_AP_VOL_UP_L

PP_CODEC_TO_MIC2_BIAS

BUTTON_TO_AP_HOLD_KEY_CONN_L

BUTTON_TO_AP_VOL_DOWN_CONN_L

MIC2_TO_CODEC_P

MIC2_TO_CODEC_N

BUTTON_TO_AP_VOL_UP_CONN_L

BUTTON_TO_AP_RINGER_A_CONN

CODEC_TO_MIC2_BIAS_CONN

PP3V1_VIBE

PP_STRB_DRIVER_TO_LED

PGND_VIBE_RETURN

CAM_RF_TO_STROBE_NTC_CONN

051-0143

3.0.0

8 OF 22

8 OF 49

1

2

21

2

1

21

21

21

2

1

2

1

2

1

1

2

1

2

1

2

19

18

2

14

1615

13

11

9

7

5

3

1

17

20

21

22

12

10

8

6

4

2

1

K

A

2

1

1

2

3

1

2

1 2

2

1

2

1

2

1

2

1

2

1

2 1

2

1

2

1

2 1

2

1

2

1

2

1

8

11

14

3

3

12

3

3

12

8

3

12

9

9

21

9

8

11

14

8

Page 9

SYM 2 OF 2

DMIC1_SCLK

DMIC2_SD

MCLK

GND13

GND0

TSTI2

TSTI1

TSTI0

GND18

GND17

GND16

GND15

GND14

GND12

GND11

GND10

GND9

GND8

GND7

GND6

GND5

GND4

GND3

GND2

GND1

RESET*

WAKE*

INT*

CDOUT

CDIN

CCLK

XSP_SDOUT

XSP_SDIN_DAC2_MUTE

XSP_LRCK_FSYNC

XSP_SCLK

ASP_SDOUT

ASP_SDIN

ASP_LRCK

ASP_SCLK

DMIC2_SCLK

DMIC1_SD

CS*

MBUS_REF

VEN

VOUT

GND

VIN

SYM 1 OF 2

FLYP

MIC4_BIAS_FILT

AIN3+

AIN1-

FLYN

GNDA

MIC1_BIAS

MIC2_BIAS_FILT_IN

MIC2_BIAS_FILT

MIC2_BIAS

AIN2+

AIN2M

MIC2_BIAS_IN

AIN3-

MIC3_BIAS

MIC3_BIAS_FILT

AIN4+

AIN4-

MIC4_BIAS

GNDP

GNDD

GNDHS

+VCP_FILT

FILT-

FILT+

LINEOUT_REF

LINEOUTB

LINEOUTA

HPDETECT

HS4_REF

HS3_REF

HS4

HS3

HPOUTB

HPOUTA

DN

DP

AOUT2-

AOUT2+

AOUT1_M

AOUT1+

GNDCP

-VCP_FILT

VA

VCP1

VD

VP0VLVP1

VPROG_CP

VPROG_MB

SPEAKER_VQ

AIN1+

MIC1_BIAS_FILT

GNDHS

FLYC

VCP0

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

8 7 6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

DIGITAL SYSTEM I/O

ANC ERROR MIC

VOICE MIC

KEEP THESE CAPS AT CODEC PINS

KEEP THIS CAP AT CODEC PINS

HEADPHONE MIC

POWER, MICBIAS

ANC REF MIC

50PF LIMIT ON AOUTX PINS

KEEP THESE CAPS AT CODEC PINS

MIKEY TO TRISTAR

HEADPHONES

L81 AUDIO CODEC

U21

WLCSP

CS42L81-CWZR-A1

R145

5%

MF

1/32W

1.00K

01005

C412

6.3V

1.0UF

20%

0201-1

X5R

120-OHM-210MA

FL96

01005

C416

6.3V

0.1UF

20%

01005

X5R-CERM

0402-2

CERM-X5R

20%

6.3V

10UF

C414

C413

X5R-CERM

6.3V

01005

20%

0.1UF

CERM

0402

C422

10UF

20%

6.3V

SHORT-10L-0.1MM-SM

XW43

R100

1/32W

2.21K

1%

MF

01005

20%

X5R

0201-1

6.3V

C237

1.0UF

4.7UF

C238

20%

X5R-CERM1

402

6.3V

C218

20%

402

6.3V

X5R-CERM1

4.7UF

NO_XNET_CONNECTION=TRUE

56PF

01005

5%

6.3V

NP0-C0G

C230

NO_XNET_CONNECTION=TRUE

56PF

01005

5%

6.3V

NP0-C0G

C227

0.1UF

01005

20%

X5R-CERM

6.3V

C222

01005

20%

X5R-CERM

6.3V

0.1UF

C223

X5R-CERM1

C234

402

6.3V

20%

4.7UF

C424

CERM-X5R

6.3V

10UF

0402-2

20%

5%

NP0-C0G

10V

100PF

01005

C138

NO_XNET_CONNECTION=TRUE

100PF

10V

5%

C51

01005

NP0-C0G

NOSTUFF

NP0-C0G

10V

01005

5%

100PF

C143

01005

5%

56PF

6.3V

NP0-C0G

C236

56PF

5%

NP0-C0G

01005

6.3V

C235

C425

20%

6.3V

4.7UF

X5R-CERM1

402

C429

402

6.3V

20%

X5R-CERM1

4.7UF

XW48

SHORT-10L-0.1MM-SM

01005

NP0-C0G

5%

6.3V

NO_XNET_CONNECTION=TRUE

56PF

C229

C220

01005

6.3V

X5R-CERM

20%

0.1UF

20%

6.3V

C221

0.1UF

X5R-CERM

01005

C226

01005

5%

56PF

6.3V

NP0-C0G

NO_XNET_CONNECTION=TRUE

NO_XNET_CONNECTION=TRUE

6.3V

5%

01005

NP0-C0G

56PF

C65

NO_XNET_CONNECTION=TRUE

56PF

5%

NP0-C0G

6.3V

01005

C64

01005

20%

0.1UF

X5R-CERM

6.3V

C55

0.1UF

X5R-CERM

6.3V

01005

20%

C61

C219

402

4.7UF

6.3V

20%

X5R-CERM1

C232

20%

X5R-CERM1

4.7UF

402

6.3V

C233

402

20%

4.7UF

6.3V

X5R-CERM1

C224

01005

6.3V

0.1UF

20%

X5R-CERM

C231

56PF

5%

01005

NP0-C0G

6.3V

NO_XNET_CONNECTION=TRUE

C228

56PF

5%

01005

NP0-C0G

6.3V

NO_XNET_CONNECTION=TRUE

C225

20%

6.3V

01005

X5R-CERM

0.1UF

C918

4.7UF

X5R-CERM1

6.3V

402

20%

R592

MF

5%

201

1/20W

1

NOSTUFF

U53

LP5907UVX-3.2V

USMD

R593

01005

150K

1%

MF

1/32W

R594