Page 1

8

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

7

VICE MLB

2/4/2010 PVT

K48-DRI

3456

B

ECNREV

0000854735

DESCRIPTION OF REVISION

PRODUCTION RELEASED

12

CK

APPD

DATE

2010-02-04

PDF CSA

TABLE_TABLEOFCONTENTS_HEAD

D

C

B

1

TABLE_TABLEOFCONTENTS_ITEM

2

TABLE_TABLEOFCONTENTS_ITEM

3

TABLE_TABLEOFCONTENTS_ITEM

4

TABLE_TABLEOFCONTENTS_ITEM

5

TABLE_TABLEOFCONTENTS_ITEM

6

TABLE_TABLEOFCONTENTS_ITEM

7

TABLE_TABLEOFCONTENTS_ITEM

8

TABLE_TABLEOFCONTENTS_ITEM

9

TABLE_TABLEOFCONTENTS_ITEM

10

TABLE_TABLEOFCONTENTS_ITEM

11

TABLE_TABLEOFCONTENTS_ITEM

12

TABLE_TABLEOFCONTENTS_ITEM

13

TABLE_TABLEOFCONTENTS_ITEM

14

TABLE_TABLEOFCONTENTS_ITEM

15

TABLE_TABLEOFCONTENTS_ITEM

16

TABLE_TABLEOFCONTENTS_ITEM

17

TABLE_TABLEOFCONTENTS_ITEM

18

TABLE_TABLEOFCONTENTS_ITEM

19

TABLE_TABLEOFCONTENTS_ITEM

20

TABLE_TABLEOFCONTENTS_ITEM

21

TABLE_TABLEOFCONTENTS_ITEM

22

TABLE_TABLEOFCONTENTS_ITEM

23

TABLE_TABLEOFCONTENTS_ITEM

24

TABLE_TABLEOFCONTENTS_ITEM

25

TABLE_TABLEOFCONTENTS_ITEM

26

TABLE_TABLEOFCONTENTS_ITEM

27

TABLE_TABLEOFCONTENTS_ITEM

28

TABLE_TABLEOFCONTENTS_ITEM

29

TABLE_TABLEOFCONTENTS_ITEM

30

TABLE_TABLEOFCONTENTS_ITEM

31

TABLE_TABLEOFCONTENTS_ITEM

1

2

3

4

5

6

7

8

9

10

11

12

14

15

17

18

19

20

21

24

26

29

30

31

32

34

35

36

37

38

39

CONTENTS

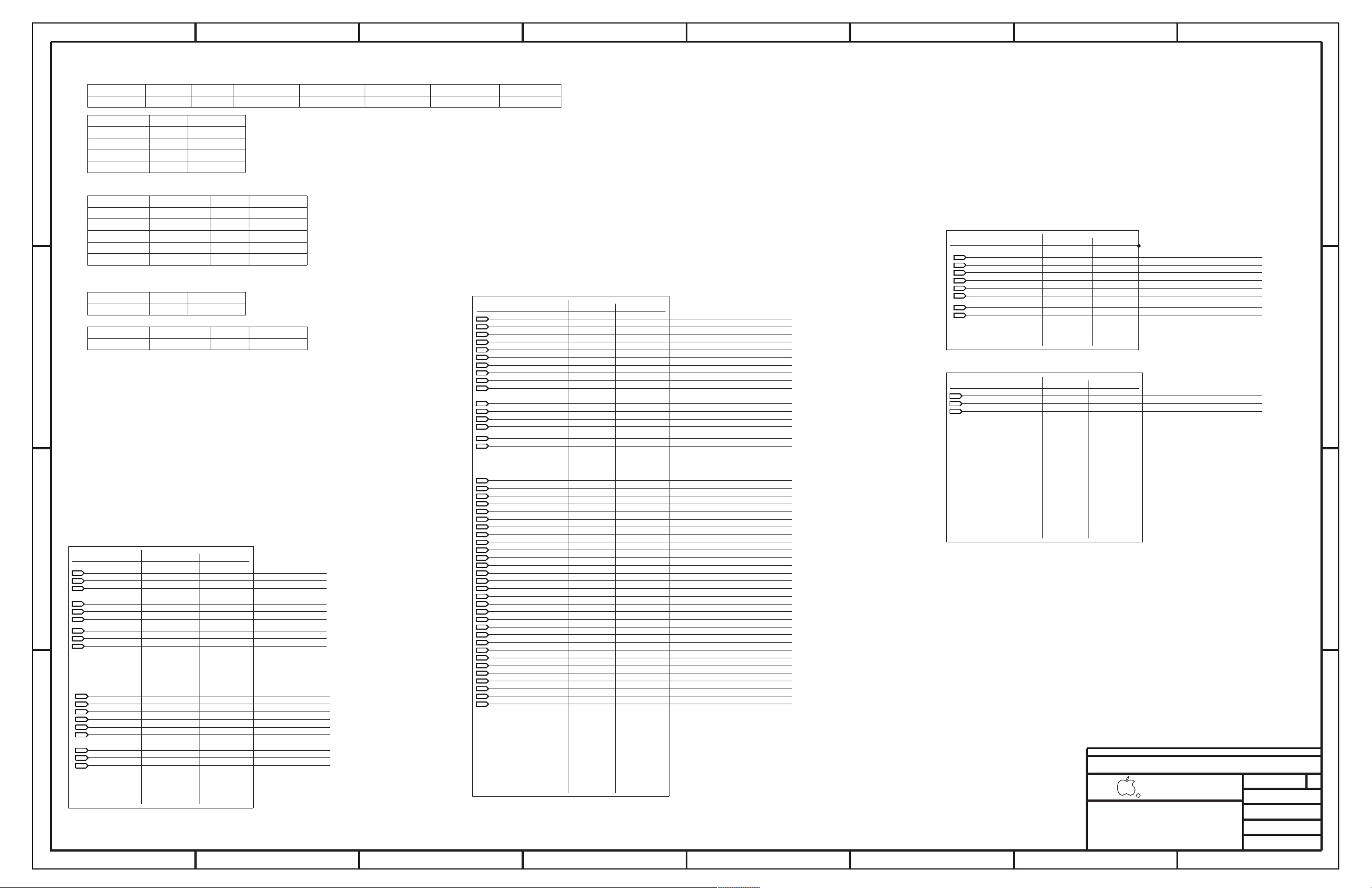

TABLE OF CONTENTS

SYSTEM BLOCK DIAGRAM

POWER BLOCK DIAGRAM

CONFIGURATION OPTIONS

FUNC/ICT TEST/BRACKETS

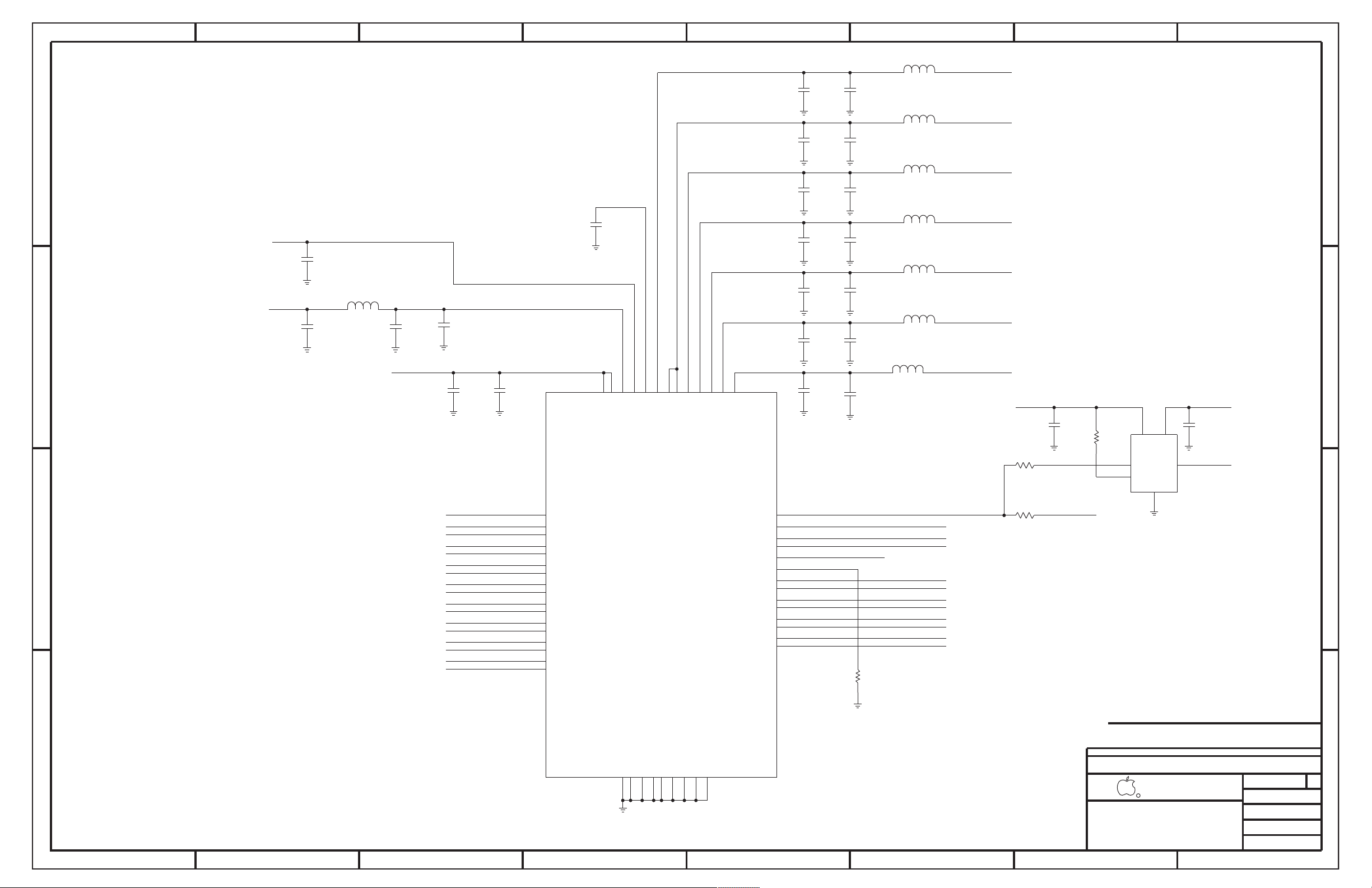

AP MAIN

AP PWR,AP BB&WIFI

AP NAND & GPIO, NOR

AP RGB/CLCD,CAMERA

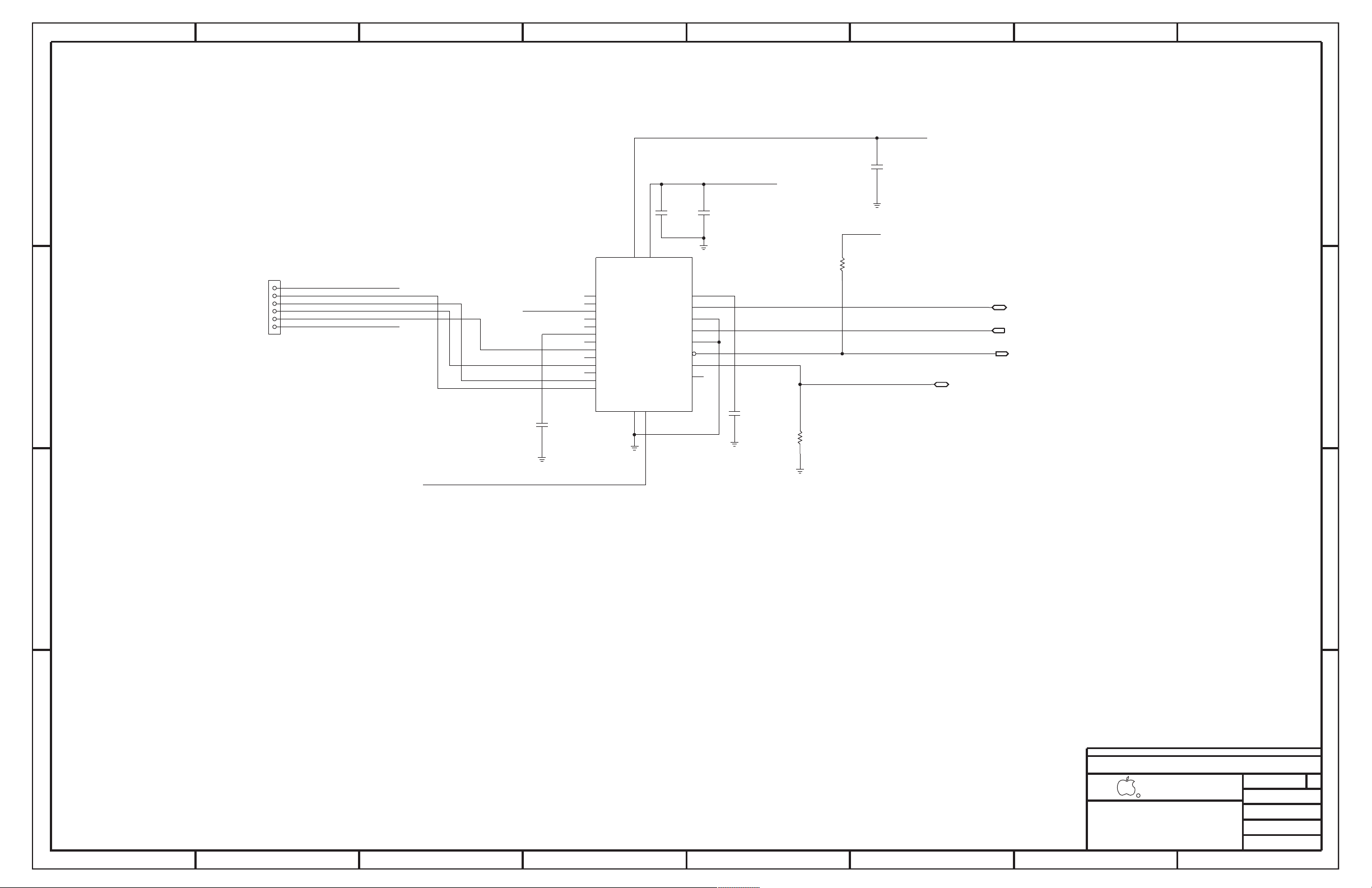

AP TVOUT

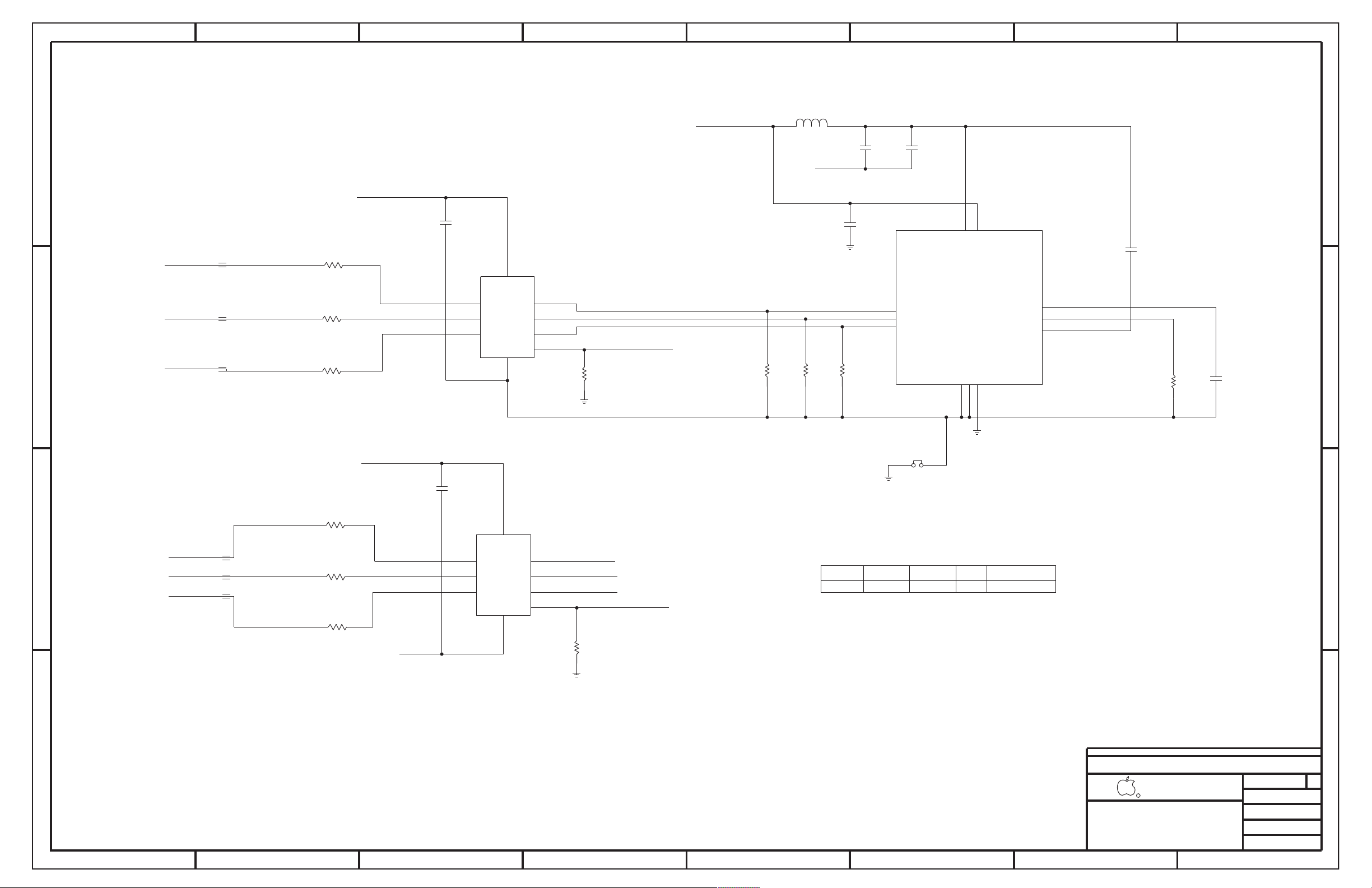

3G AND DEBUG MUXES

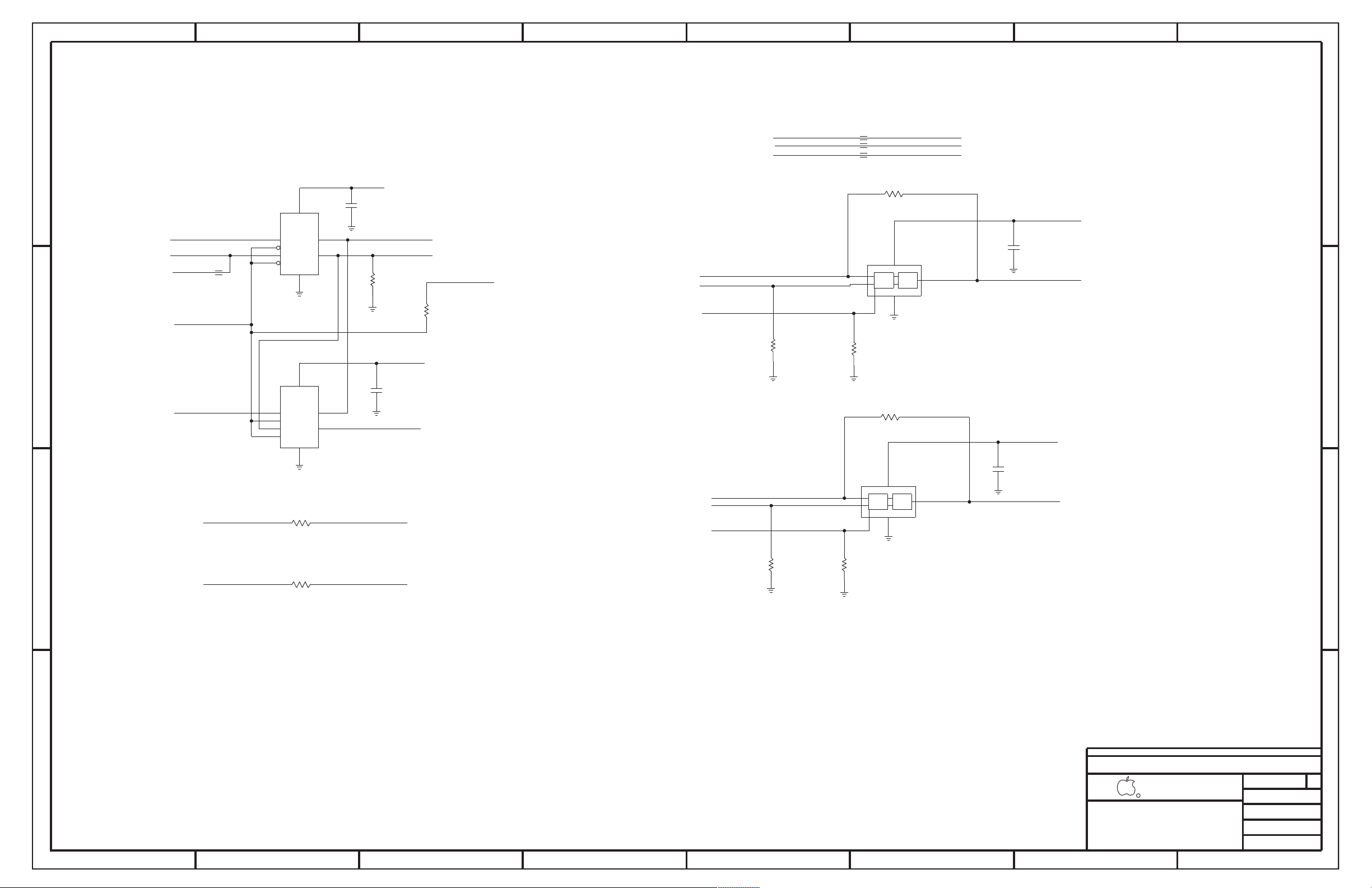

AP MISC & ALIASES

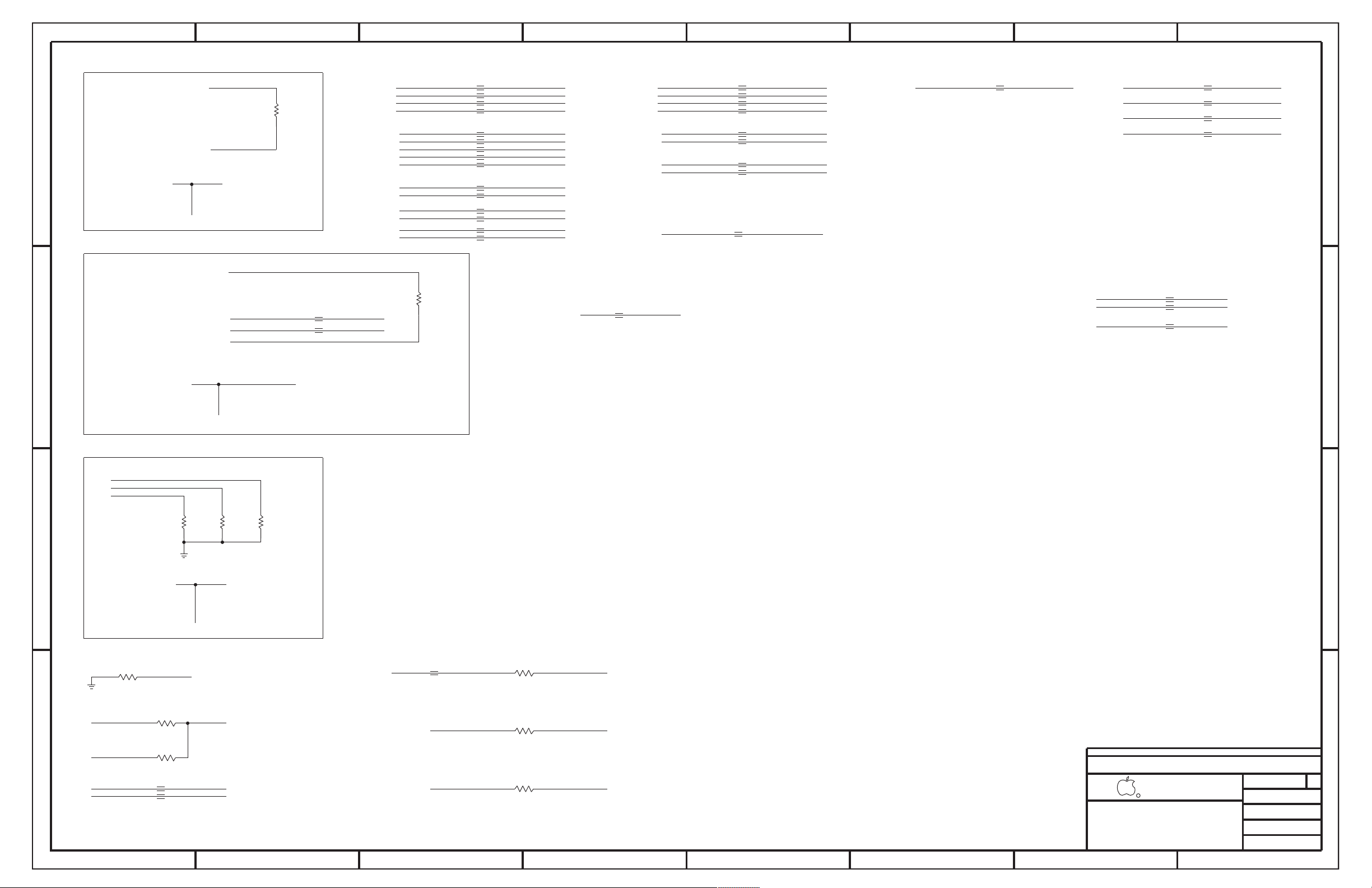

MLC

MLC ALIASES

Power Conn / Alias

DCIN POWER PATH

CHARGER

PMU

PMU

3.3V SUPPLY

LED BACKLIGHT CONTROLLER

DEBUG RESET ACCESS

GRAPE 1 OF 2

GRAPE 2 OF 2

LVDS CONNECTOR

MOTION,GYRO,COMPASS/THERM

USB MUX/BRK DET

L61 AUDIO INTERFACE

AUDIO: SPEAKER AMP

AUDIO:HEADPHONE OUT

AUDIO: LINE OUT DOCK ESD CIRCUIT

SYNC MASTER

ALEX

MARK

MARK

MARK

MARK

MARK

MARK

MARK

MARK

DATE

05/02/2009

12/04/2009

08/06/2009MIAMI

09/16/2009MIAMI

12/21/2009JAMES

12/21/2009JAMES

12/21/2009JAMES

12/21/2009JAMES

12/21/2009JAMES

12/21/2009JAMES

12/21/2009JAMES

09/16/2009MIAMI

09/16/2009MIAMI

12/04/2009

12/04/2009

12/04/2009

12/04/2009

12/04/2009

12/04/2009

12/04/2009

09/16/2009MIAMI

12/21/2009JAMES

12/21/2009JAMES

09/16/2009MIAMI

09/16/2009MIAMI

09/16/2009MIAMI

12/04/2009AUDIO

12/04/2009AUDIO

12/04/2009AUDIO

12/04/2009AUDIO

TABLE_TABLEOFCONTENTS_HEAD

32

TABLE_TABLEOFCONTENTS_ITEM

33

TABLE_TABLEOFCONTENTS_ITEM

34

TABLE_TABLEOFCONTENTS_ITEM

35

TABLE_TABLEOFCONTENTS_ITEM

36

TABLE_TABLEOFCONTENTS_ITEM

37

TABLE_TABLEOFCONTENTS_ITEM

38

TABLE_TABLEOFCONTENTS_ITEM

39

TABLE_TABLEOFCONTENTS_ITEM

40

TABLE_TABLEOFCONTENTS_ITEM

41

TABLE_TABLEOFCONTENTS_ITEM

42

TABLE_TABLEOFCONTENTS_ITEM

43 FLASH

TABLE_TABLEOFCONTENTS_ITEM

44

TABLE_TABLEOFCONTENTS_ITEM

45

TABLE_TABLEOFCONTENTS_ITEM

46

TABLE_TABLEOFCONTENTS_ITEM

47

TABLE_TABLEOFCONTENTS_ITEM

48

TABLE_TABLEOFCONTENTS_ITEM

49

TABLE_TABLEOFCONTENTS_ITEM

50

TABLE_TABLEOFCONTENTS_ITEM

51

TABLE_TABLEOFCONTENTS_ITEM

52

TABLE_TABLEOFCONTENTS_ITEM

53

TABLE_TABLEOFCONTENTS_ITEM

CSAPDF

40

42

43

45

48

49

50

51

54

55

57

67

100

101

106

113

114

115

116

117

118

119

CONTENTS

AUDIO: AUDIENCE

AUDIO: DETECT/MIC BIAS

AUDIO: HP CONN

ALS CONNECTOR

I/O EXPANDER

DISPLAY PORT SWITCH

44-PIN LANDSCAPE DOCK CONN

60-PIN PORTRAIT DOCK CONN

BUTTONS CONNECTOR

3G CONNECTOR

PROX SENSOR

CONSTRAINTS

MORE CONSTRAINTS

PHYSICAL/SPACING RULES

Cross Reference Page

Cross Reference Page

Cross Reference Page

Cross Reference Page

Cross Reference Page

Cross Reference Page

Cross Reference Page

SYNC MASTER

AUDIO

AUDIO

AUDIO

JAMES

JAMES

JAMES

JAMES

MIAMI

MIAMI

MARKSIN

MIAMI

MIAMI

MIAMI

MIAMI

DATE

12/04/2009

12/04/2009

12/04/2009

09/16/2009MIAMI

12/21/2009

12/21/2009

12/21/2009

12/21/2009

09/16/2009

09/16/2009

10/14/2009

09/16/2009

09/16/2009

09/16/2009

09/16/2009

D

C

B

A

DRAWING

TITLE=U230

ABBREV=DRAWING

LAST_MODIFIED=Thu Feb 4 00:41:44 2010

87 6 5 4 21

3

DRAWING TITLE

VICE MLB

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

1 OF 119

SHEET

1 OF 53

SIZE

A

D

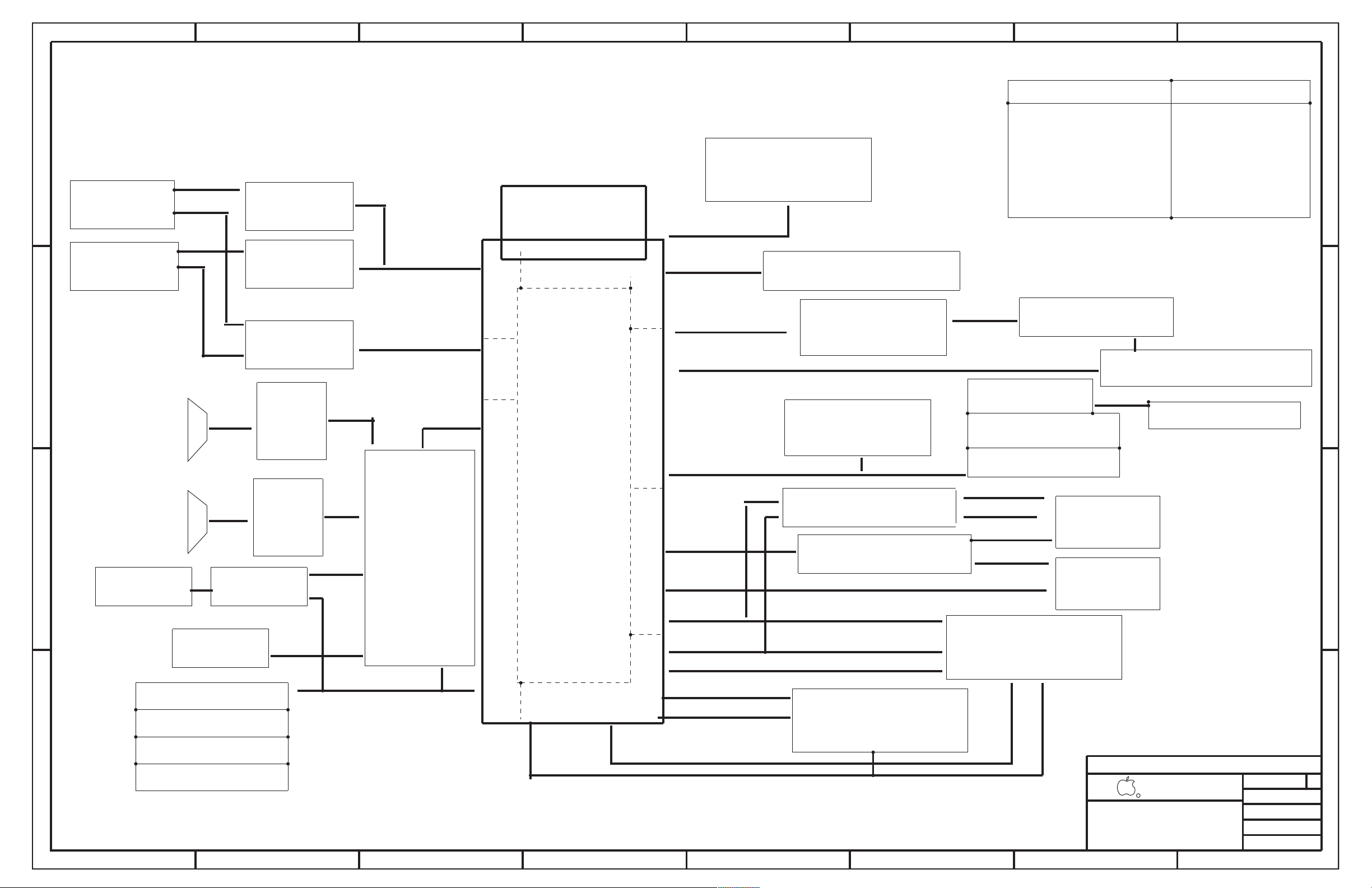

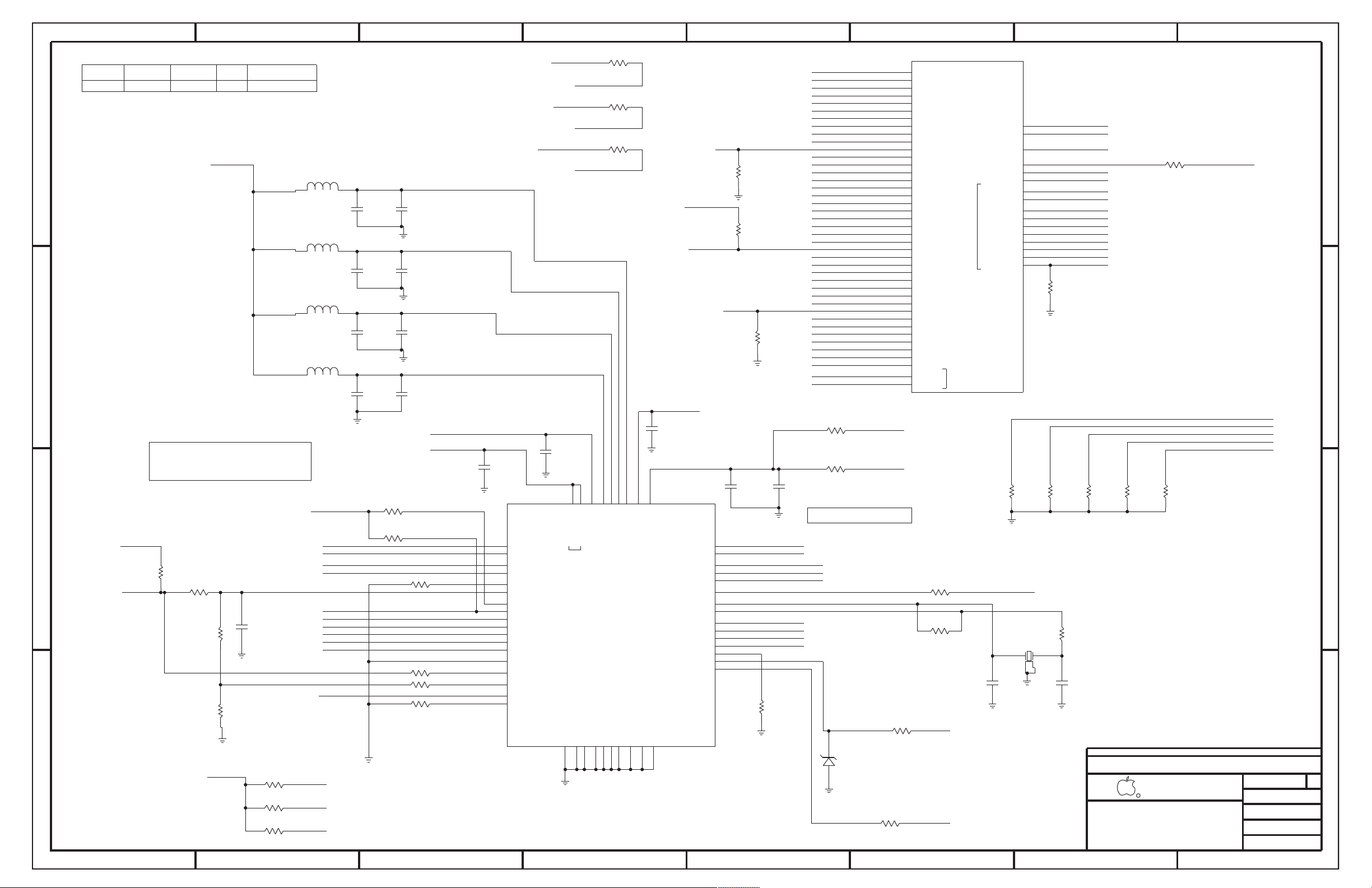

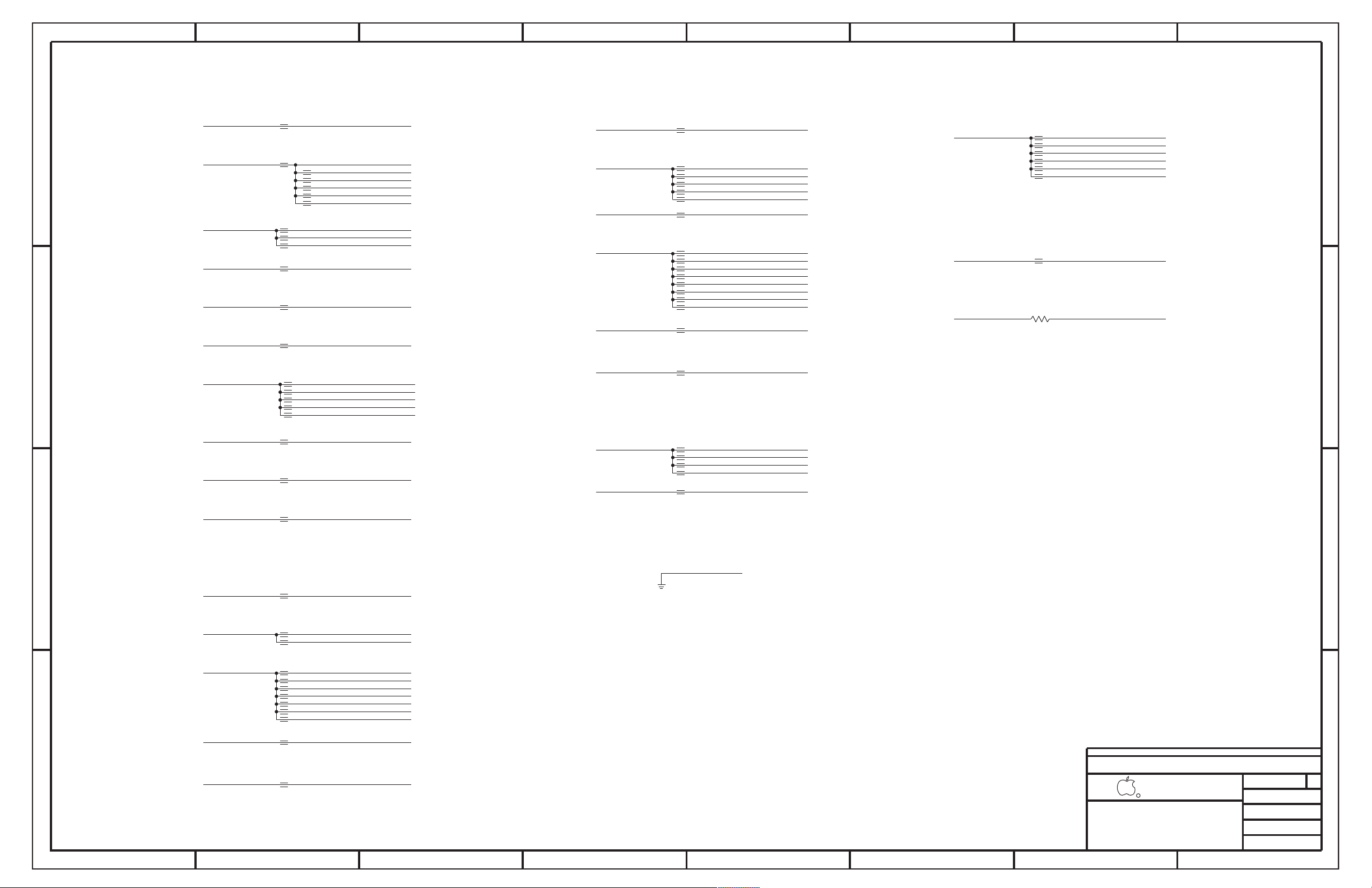

Page 2

345678

21

Voltage Rails

VICE BLOCK DIAGRAM

D

COMPOSITE

COMP/SVIDEO

L. DOCK

PAGE 50

P. DOCK

PAGE 51

C

STERO SPEAKERS

VIDEO AMP

PAGE 10

VIDEO AMP

PAGE 10

DP MUX

PAGE 49

AMP

P37

COMPOSITE

COMP/SVIDEO

DISPLAYPORT

I2S0

MDDR

PG 10

PG 7

H3P

256MB

FMI0-1

PG 8

PG 9

I2C2

SERIAL BOOT

FLASH 8MBIT

PG 8

SPI0

NAND FLASH

8/16/32/64

MIPI->LVDS

MIPI

SPI1

PROX SENS.

MLC

PAGE 14-15

PAGE 57

PG 67

POWER PLANE

LVDS

GYRO SENSOR

PAGE 34

ALS SENSOR

PAGE 45

CAMERA SENSOR FLEX

LAND. 4099

PAGE 19

ON STATE

D

LCD PANEL

P32

C

GRAPE/GROUNDHOG

PAGE 30-31

MOTION SENSOR

PAGE 34

AMP

P37

B

HEADSET L

P39

MIKEY L.

P42

I2S AUDIO

CIRRUS L61

PG 36

PG 7

USB2.0

UART0

PG 6

SERIAL BUFF/MUX

PG 11

USB DOCK MUX

PG 35

UART

JTAG/UART

USB2.0

USB2.0

L. DOCK

PAGE 50

B

P. DOCK

PAGE 51

UART4

MICROPHONE

P39

UART1

SPI2

X15 MODULE

PAGE 55

HIGHWAY BOARD

I2C0

AMANDA PMU

PAGE 20

PG 7

PORTRAIT 4099

PAGE 19

A

COMPASS

PAGE 34

I2S1

I2S2

IO EXPANDER

PAGE 20

87 5 4 21

UART3

SDIO

X7 AIRPORT +BT

PAGE 51

HIGHWAY BOARD

SIZE

A

D

SYNC_MASTER=ALEX

PAGE TITLE

SYSTEM BLOCK DIAGRAM

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=05/02/2009

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

2 OF 119

SHEET

2 OF 53

36

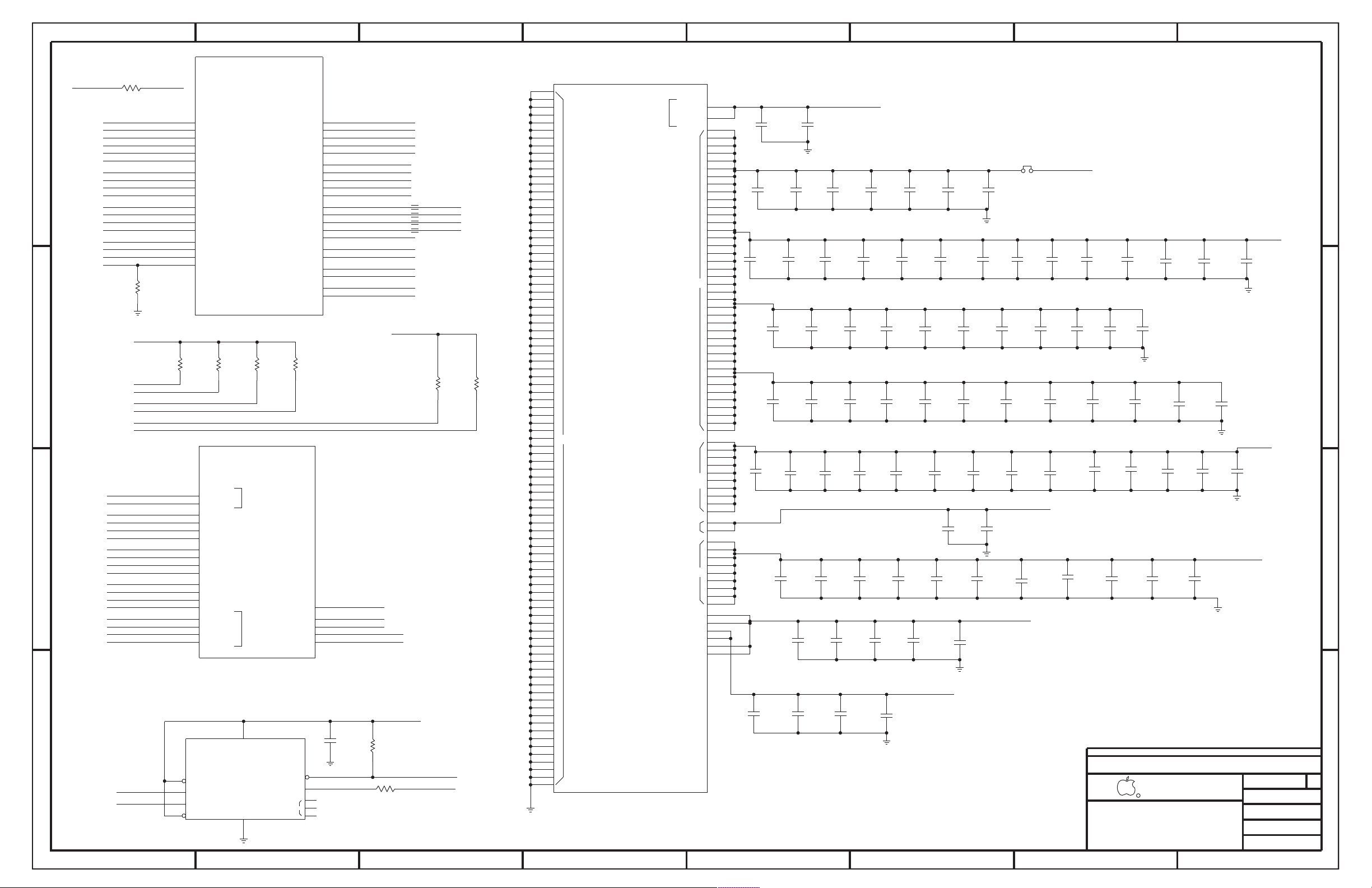

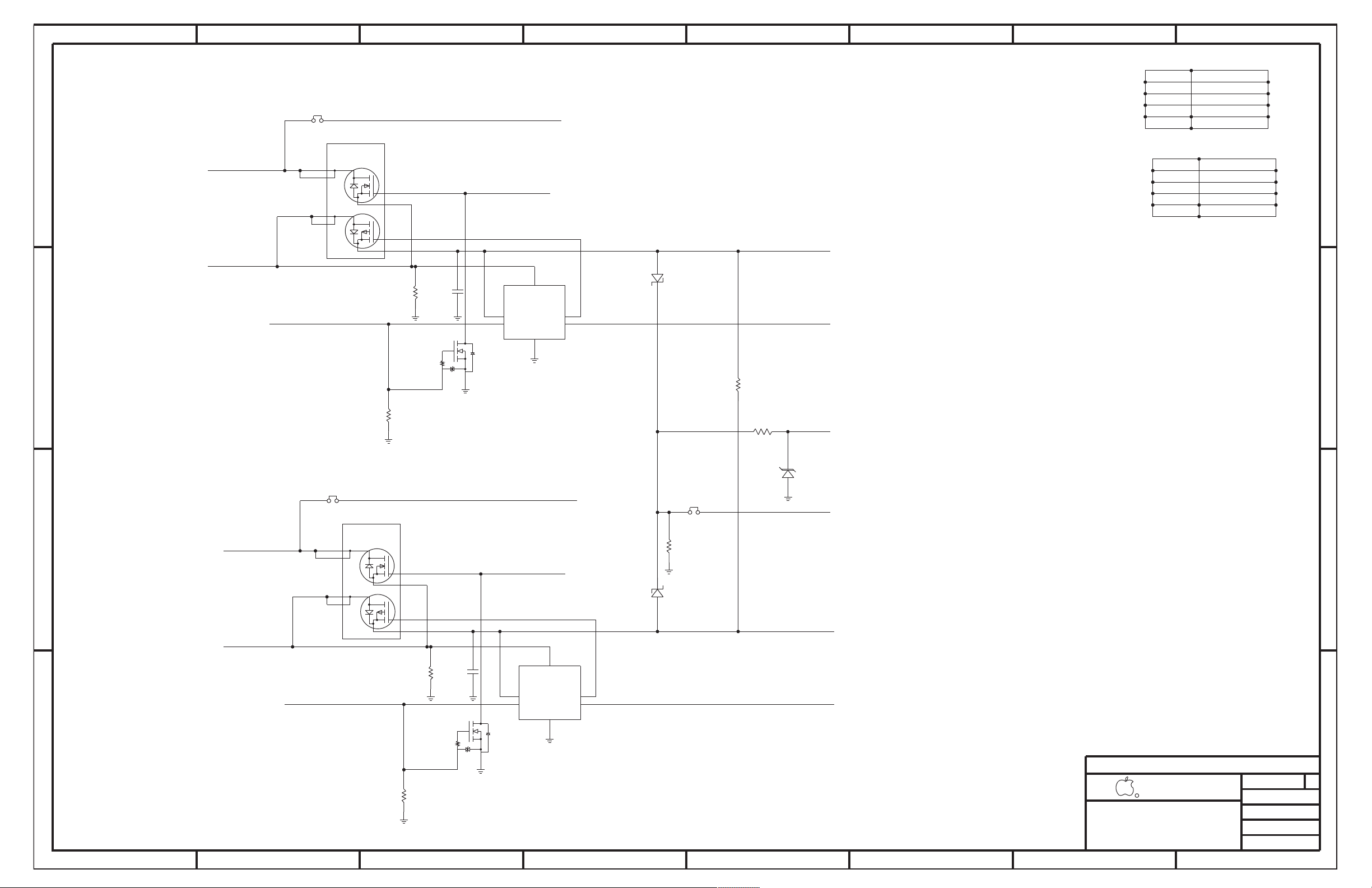

Page 3

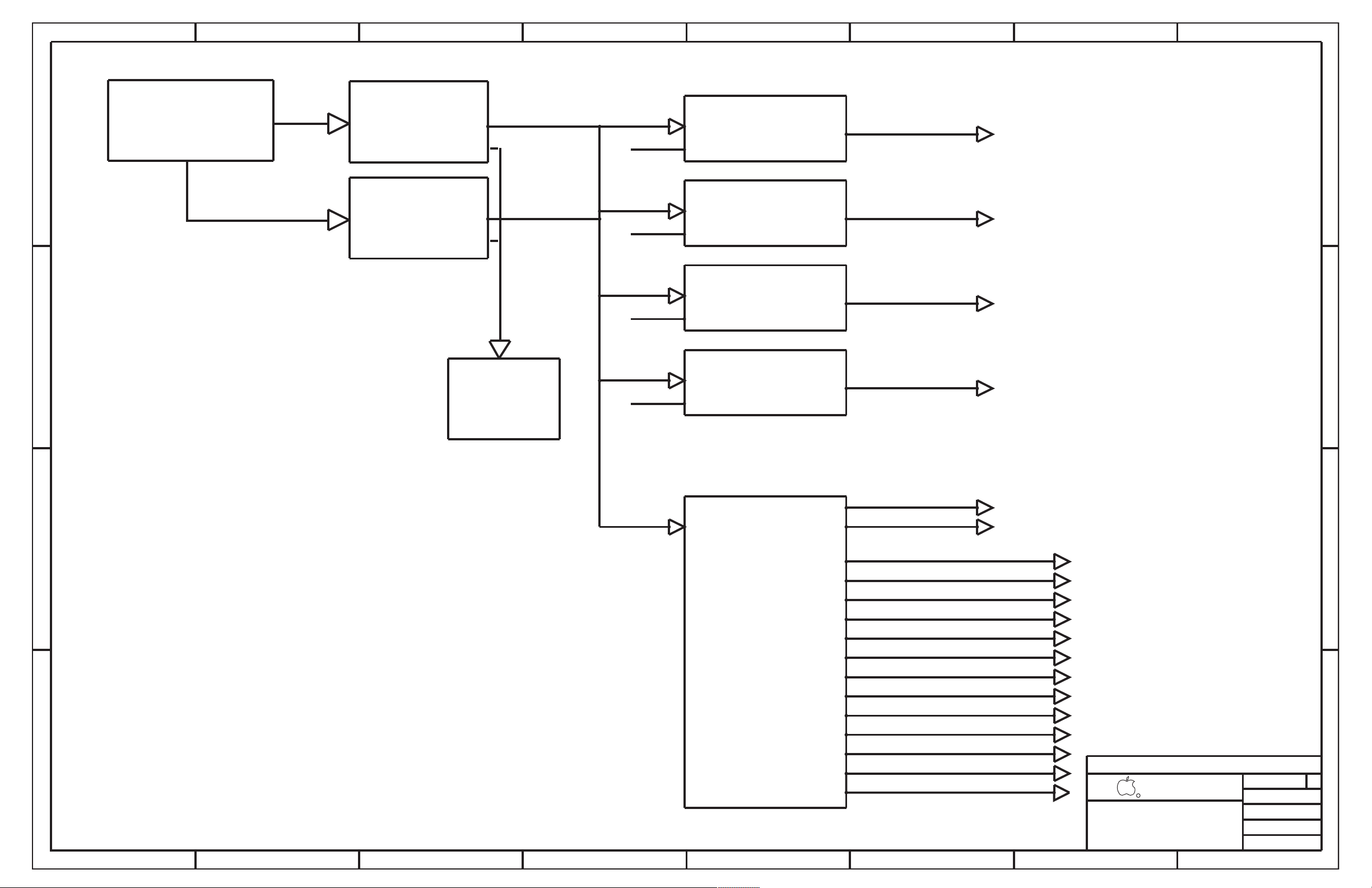

POWER BLOCK DIAGRAM

345678

21

DC INPUT PATH

BUCK / CHARGER

B9 ADAPTER (5V)

USB (5V)

D

USB(5V)

LTC4099

PAGE 19

VCC_MAIN/3.0-4.7V

EN

BUCK / CHARGER

LTC4099

PAGE 19

EN

1.2V POWER

RP200Z121D

LDO

PAGE 20

3V3 POWER

LTC3442

BUCK/BOOST

PAGE 24

1.2V/0.3A

D

3V3/1.2A

LED DRIVER

APP001

EN

BOOST

PAGE 26

C

LED/0.12A

C

GRAPE POWER

BATTERY PACK

EN

TPS61045

BOOST

PAGE 30

18V/1MA

3.0-4.2V

ASHLEY

B

PAGE 20-21

CORE/2.0A MAX

1V8/1.5A MAX

BUCKS

3V3_LAND_ACC/0.15A MAX

B

1V7_VA_VCP/0.10A MAX

3V0_OPTICAL/0.05A MAX

3V0_VIDEO/0.10A MAX

LDOS

3V1_AUDIO/0.25A MAX

3V3_PORT_ACC/0.15A MAX

3V0_IO/0.10A MAX

3V0_LCD/0.01A MAX

1V2_H3/0.30A MAX

3V0_HP_BIAS/0.20A MAX

A

87 5 4 21

3V0_GRAPE/0.15A MAX

1V1_H3_PHY/0.10A MAX

1V8_ALWAYS/0.002A MAX

36

SYNC_MASTER=MARK

PAGE TITLE

POWER BLOCK DIAGRAM

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=12/04/2009

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

3 OF 119

SHEET

3 OF 53

SIZE

A

D

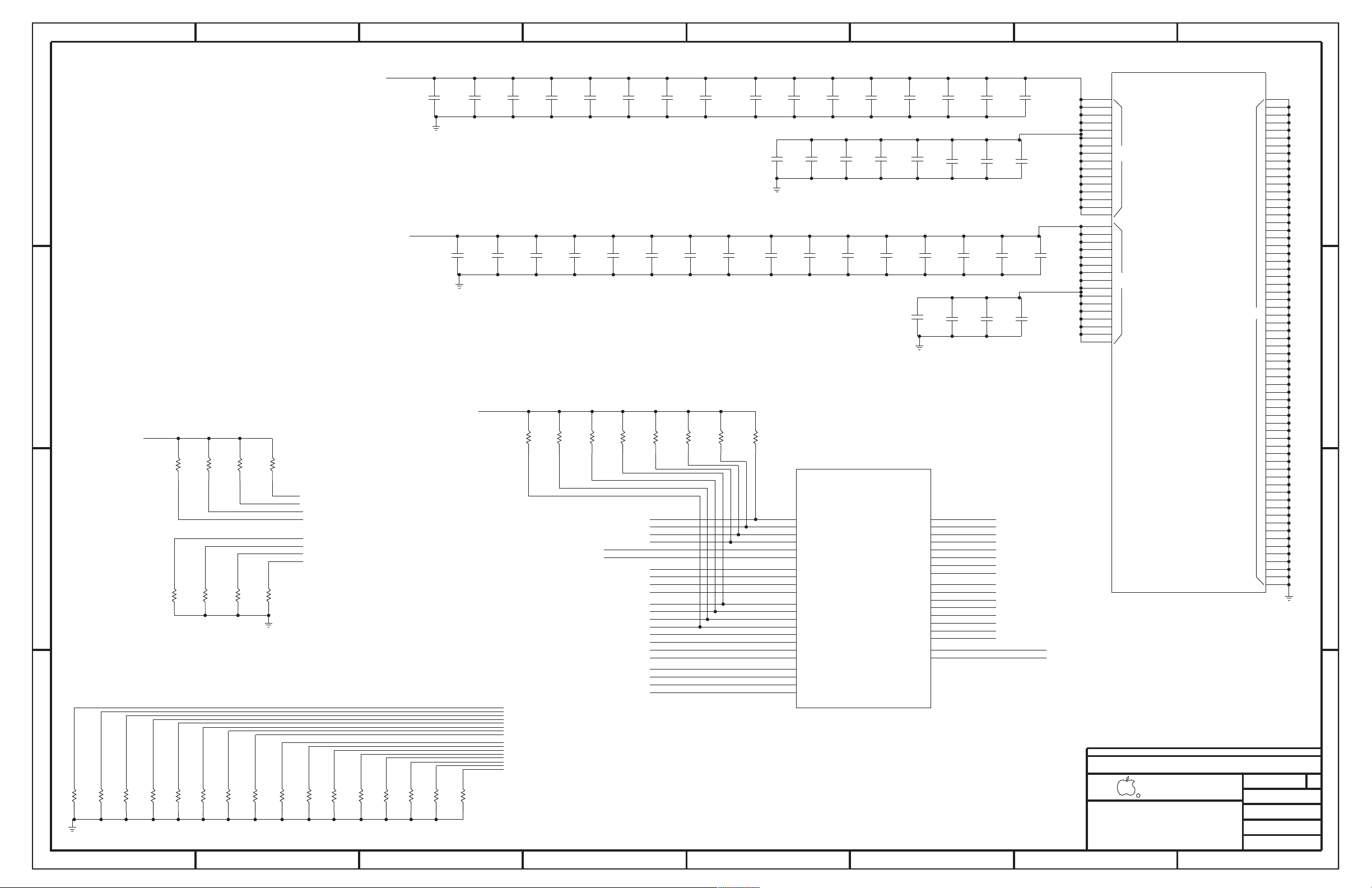

Page 4

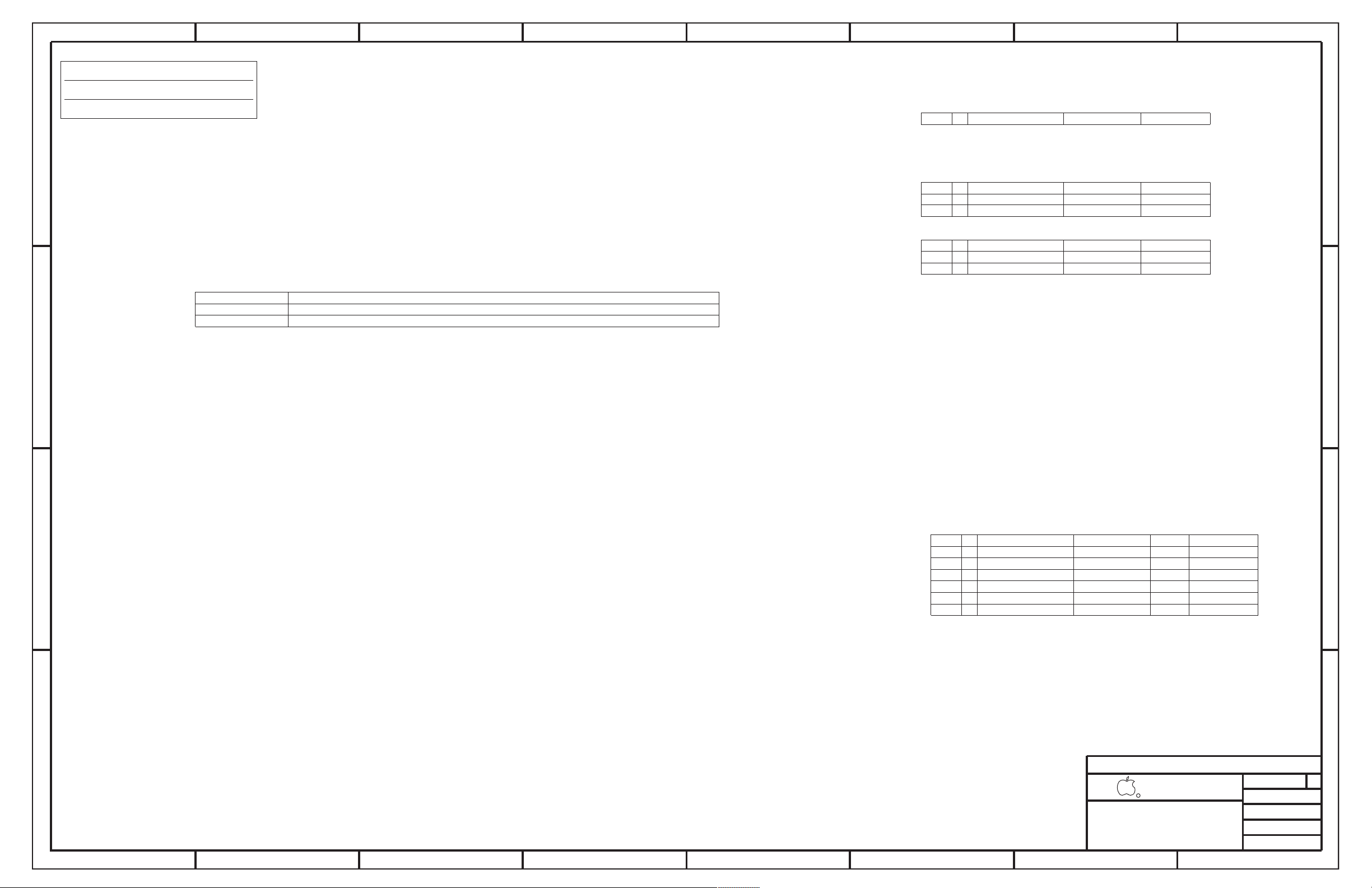

Page Notes

Power aliases required by this page:

(NONE)

Signal aliases required by this page:

(NONE)

BOM options provided by this page:

ALL AVAIL BOM OPTIONS

COMMON

ALTERNATE

D

DPMUX

32GB_FLASH_SAM

32GB_FLASH

16GB_FLASH

16GB_FLASH_TOSH

8GB_FLASH

8GB_FLASH_SAM

BKLT_PLL

CAMERA

JTAG_2_WIRE

JTAG_5_WIRE

PRODUCTION

DEVELOPMENT

AUD10

MIKEY

INTERNAL_MIC

LANDSCAPE_DOCK

LEFT_HS

LINE_OUT_1

LINE_OUT_2

PORTRAIT_DOCK

SPEAKER

ADD DEVELOPMENT AND OTHER BOMS ONCE YOU GET BOM NUMBERS

345678

21

BOM OPTIONS

PROGRAMMABLE PARTS

QTY

PART#

DESCRIPTION

SCH AND BOARD P/N

QTY

PART#

051-8245 SCH1

820-2740

PART#

085-1028

DESCRIPTION

SCHEM,VICE,MLB,K48

1

1

PCBA,VICE,MLB,K48

QTY

DESCRIPTION

DEV,VICE,MLB,K48

1

1

DEV,VICE,MLB,K48M

REFERENCE DESIGNATOR(S)

REFERENCE DESIGNATOR(S)

REFERENCE DESIGNATOR(S)

PCB1

DEV1

DEV1 K48M_DEV085-1133

BOM OPTION

BOM OPTION

BOM OPTION

K48_DEV

TABLE_5_HEAD

VICE

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

D

BOM

OPTIONS

BOM GROUP

BASIC

AUDIO

BOM OPTIONS

COMMON,ALTERNATE

LEFT_HS,SPEAKER,INTERNAL_MIC

C

USE SCHUTIL BOMCONFIG TO GENERATE CONFIG FILE.

PUT CONFIG FILE AT SAME LEVEL AS .CPM FILE

USE "READ BOM-CONFIG" BUTTON ON DMS TO READ IN BOMS

B

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

TABLE_BOMGROUP_ITEM

USE 825-6447

NEED MORE LINE ITEMS FOR OTHER CONFIGURATIONS

BARCODE LABEL/EEE CODES

PART#

825-7456

825-7456

825-7456

825-7456

825-7456

825-7456

DESCRIPTION

QTY

EEE FOR 639-0455 (16G)

1

EEE FOR 639-0601 (32G)

1

EEE FOR 639-0598 (64G)

1

EEE FOR 639-0602 (16G)M

EEE FOR 639-0599 (32G)M

1

EEE FOR 639-0600 (64G)M

1

REFERENCE DESIGNATOR(S)

EEE_BWY

EEE_D66

EEE_D61

EEE_D67

EEE_D62

EEE_D63

CRITICAL BOM OPTION

CRITICAL

CRITICAL

CRITICAL

CRITICAL1EEE_16G_M

CRITICAL

CRITICAL

EEE_16G

EEE_32G

EEE_64G

EEE_32G_M

EEE_64G_M

C

TABLE_5_HEAD

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

B

A

SYNC_MASTER=MIAMI

PAGE TITLE

CONFIGURATION OPTIONS

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

87 5 4 21

36

SYNC_DATE=08/06/2009

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

4 OF 119

SHEET

4 OF 53

SIZE

A

D

Page 5

345678

21

D

NOSTUFF

J0501

TH

J0502

TH

J0503

TH

J0504

TH

1

NOSTUFF

1

NOSTUFF

1

NOSTUFF

1

SL-1.2X0.40-1.95X1.15

C

SL-1.2X0.40-1.95X1.15

SL-1.2X0.40-1.95X1.15

CRITICAL

J0500

MLB-MNT-TAB-K48

SM

1

2

3

4

SL-1.2X0.40-1.95X1.15

D

C

CRITICAL

B

1

J0510

TOP-SM

SHLD-K48-FENCE-MLB-TOP

SHLD-K48-FENCE-MLB-BOT

A

87 5 4 21

1

J0520

CRITICAL

BOT-SM

B

SIZE

A

D

SYNC_MASTER=MIAMI

PAGE TITLE

SYNC_DATE=09/16/2009

FUNC/ICT TEST/BRACKETS

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

5 OF 119

SHEET

5 OF 53

36

Page 6

345678

R0671

=PP1V8_SDRAM_H3

6 8

15

HSIC1_DATA

HSIC1_STB

HSIC2_DATA

HSIC2_STB

TESTMODE

RESETN

JTAG_SEL

JTAG_TRSTN

JTAG_TCK

JTAG_TMS

JTAG_TDI

JTAG_TDO

JTAG_TRTCK

FUSE1_FSRC

CFSB

DDR1_CKEIN

TST_CLKOUT

TST_STPCLK

15

19 39

=PP1V8_ALWAYS

15 19

6

19 40

=PP1V8_SDRAM_H3

6 8

6

19 40

PP1V1_PLL3_F

PP1V1_PLL2_F

PP1V1_PLL1_F

PP1V1_PLL0_F

1

C0642

0.01UF

10%

10V

2

X5R

201

(INT PD)

(INT PU)

(INT PU)

(INT PU)

HSIC_DVSS

L26

HOME_L

6

ONOFF_L

RINGER_A

N17

HSIC_VDD121

1.2V

N16

PART NUMBER

339S0100 339S0084

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

U0652

COMMENTS:

HYNIX DDR

TABLE_ALT_HEAD

TABLE_ALT_ITEM

D

=PP1V1_PLL

C

JTAGSEL

0 - PARALLEL

1 - DAISY-CHAIN (FOR USE WITH 5-WIRE JTAG)

PER RADAR #6755237

=PP3V3_H3_USB

6

B

15

1

R0617

10K

1%

1/20W

R0632

MF

201

2

100K

19 39

RESET_L

12

1%

1/20W

MF

201

1

R0688

42.2K

1%

1/20W

MF

201

2

1

C0618

1000PF

10%

16V

2

X7R

201

AP_DDR1_CKEIN_1V2

1

R0689

84.5K

1%

1/20W

MF

201

2

FL0607

80-OHM-0.2A-0.4-OHM

12

0201-1

FL0606

80-OHM-0.2A-0.4-OHM

12

0201-1

FL0605

80-OHM-0.2A-0.4-OHM

12

0201-1

FL0604

80-OHM-0.2A-0.4-OHM

12

0201-1

=PP1V8_H3

6 7 9

12 15 37

NC_HSIC1_DATA

NC_HSIC1_STB

NC_HSIC2_DATA

NC_HSIC2_STB

RESET_1V8_N

12

AP_TRSTN

12

AP_TCK

6

39 44

AP_TMS

6

39 44

AP_TDI

6

12 44

NC_AP_TDO

12

NC_AP_RTCK

TP_TST_CLKOUT

1

C0647

1UF

10%

6.3V

2

CERM

402

1

C0645

1UF

10%

6.3V

2

CERM

402

1

C0643

1UF

10%

6.3V

2

CERM

402

1

C0606

1UF

10%

6.3V

2

CERM

402

R0664

R0677

R0786

R0602

1

C0648

0.01UF

10%

10V

2

X5R

201

1

C0646

0.01UF

10%

10V

2

X5R

201

1

C0644

0.01UF

10%

10V

2

X5R

201

1

C0608

0.01UF

10%

10V

2

X5R

201

JTAG_TAP

R0662

100K

12

NOSTUFF

R0624

3.92K

12

12

12

12

12

15

15

0

0

0

0

=PP1V1_HSIC

=PP1V2_HSIC

AP_JTAG_SEL

12

AP_TESTMODE

AP_CFSB

AP_DDR1_CKEIN

AP_TST_STPCLK

1

C0641

0.01UF

10%

10V

2

X5R

201

P25

R25

M27

M26

F23

B19

C18

B18

B15

D18

A19

C19

D19

F19

V26

N7

K20

J20

A

12 15 37

=PP1V8_H3

6 7 9

R0645

100K

12

R0646

100K

12

R0647

100K

12

AP_TCK

AP_TMS

AP_TDI

6

39 44

6

39 44

6

12 44

87 5 4 21

12

R0670

12

R0665

12

0.6MM

0.2MM

0.6MM

0.2MM

0.6MM

0.2MM

0.6MM

0.2MM

L27

E14

N18

HSIC_DVDD

HSIC_VDD122

PLL0_AVDD11

U0652

H3P

256MB-DDR-FC

FBGA

SYMBOL 1 OF 9

HSIC_VSS121

HSIC_VSS122

PLL0_AVSS11

PLL1_AVSS11

N19

E15

E13

220K

1%

1/20W

MF

201

220K

1%

1/20W

MF

201

100K

1%

1/20W

MF

201

D13

F15

N23

PLL2_AVDD11

PLL3_AVDD11

PLL1_AVDD11

CRITICAL

USB_VSSAC

PLL2_AVSS11

PLL3_AVSS11

N22

F14

N24

1

C0627

0.01UF

10%

10V

2

X5R

201

PPVDD330_USB_AP

0.6MM

0.2MM

P22

R20

USB_DVDD

USB_VDD330

USB_VSSA0

USB_DVSS

R24

R21

=PP1V8_SDRAM_H3

6 8

15

AUD_MIKEY_ENA

33

=PP1V1_USB

USB11_D+

USB11_D-

EHCI_PORT_PWR0

EHCI_PORT_PWR1

EHCI_PORT_PWR2

WDOG

USB_ANALOGTEST

USB_ID

USB_DP

USB_DM

USB_REXT

USB_VBUS

USB_BRICKID

BB_RST

12

12

15

R26

R27

Y10

Y9

AA9

F22

B12

XI0

A12

XO0

N20

R22

P26

P27

N21

N25

R23

1

R0630

100K

1%

1/20W

MF

201

2

1

R0631

100K

1%

1/20W

MF

201

2

JTAG_TRSTN_CTRL

1

R0721

100K

1%

1/20W

MF

201

2

1

C0640

1UF

10%

6.3V

2

CERM

402

AP_GPIO39_BRD_REV0

AP_GPIO40_BRD_REV1

AP_GPIO41_BRD_REV2

TP_USB_ANALOGTEST

USB_REXT

1

C0630

0.01UF

10%

10V

2

X5R

201

NC_USB11_DP

NC_USB11_DM

AP_WDOG

XTAL_24M_I

XTAL_24M_O

TP_USB_ID

USB_DP

USB_DM

1

R0642

44.2

1%

1/20W

MF

201

2

HOME_L

6

19 39

ONOFF_L

6

19 40

AUD_VOL_UP_L

40

AUD_VOL_DOWN_L

40

RINGER_A

6

19 40

AUD_SPKRAMP_MUTE_N

29

PORT_USB_CHINA_DET

27

BT_WAKE

39

LAND_USB_CHINA_DET

27

RADIO_ON

6

41

RESET_DET_N

41

IPC_SRDY

41

PMU_IRQ_L

19

RESET_L61_N

28

GRAPE_FW_DNLD_EN_L

23

TP_AUDIENCE_RESET_L

IO_XPNDR_INT_L

19 36

CODEC_IRQ_N

28

KEEPACT

6

19

GRAPE_RESET_N

23

AP_GRAPE_HOST_INT_N

23

GPS_STANDBY_L

41

COMPASS_RST_L

6

26 35

AP_GPIO25_BOARD_ID_1

12

FORCE_DFU

6

22

DFU_STATUS

6

AP_GPIO28_BOARD_ID_2

12

AP_GPIO29_BOARD_ID_3

12

GPS_SYNC

41

AP_GPIO32_4_DIAG

GYRO_INT_L

26

LO_LS_REF_SEL

30

COMPASS_INT_L

26 35

ACCEL_INT1_L

26

ALS_INT_L

35

ACCEL_INT2_L

26

PORT_DOCK_VIDEO_AMP_EN

10

TP_CAM_EN

R0680

0

201

12

=PP3V3_H3_USB

NOSTUFF

R0681

0

201

12

EHCI_PORT_PWR[0-2] NOT USED

PER MICHAEL FRANK (EMAIL 2/25/09)

27 44

27 44

12

12

12

=PP3V0_IO_USB

USB_VBUS

2

DZ0600

GDZT2R5.1B

GDZ-0201

1

AP_USB_BRICKID

F6

GPIO0

B6

GPIO1

B7

GPIO2

D9

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24

GPIO25

GPIO26

GPIO27

GPIO28

GPIO29

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

GPIO38

GPIO_3V0

GPIO_3V1

6

15

15

JTAG_TAP_NOT

R0652

12

R0655

12

USB_BRICKID

256MB-DDR-FC

(INT PD)

(INT PD)

(INT PD)

(INT PD)

(INT PD)

(INT PD)

(INT PD)

(INT PD)

(INT PD)

0

5%

1/20W

MF

201

1M

1%

1/20W

MF

201

VBUS_P

D5

A6

A7

B9

E6

A9

C5

C9

C6

D6

F5

E5

F9

F3

F4

C10

F10

E10

A4

B4

E4

E2

D10

E9

L2

G1

G2

E3

B3

A3

B2

H2

L1

H1

E1

W24

W25

(NOSTUFF FOR SCAN DUMP CONFIG)

R0651

100K

12

1%

1/20W

MF

201

R0650

0

12

5%

1/20W

MF

201

36

CRITICAL

U0652

H3P

FBGA

SYMBOL 6 OF 9

SENSOR_CLK

SENSOR_RST

TMR32_PWM0

TMR32_PWM1

TMR32_PWM2

SMII_CLKSEL0

SMII_CLKSEL1

SMII_TXD

SMII_RXD

3.0V

SMII_SYNC

SMII_CLK

SMII_RRDY

SMII_SRDY

SMII_WAKE

SMII_PWR

3.0V

PMU_RESET_IN

C0607

18PF

5% 5%

25V

NP0-C0G

201

16

19 27

1

2

W20

V21

R18

SPDIF

AB25

AB27

AB26

K18

K19

G18

J18

G19

K23

K21

K22

J19

H19

1

R0635

100K

1% 1%

1/20W

MF

201

2

19

CRITICAL

Y0602

SM-2

24.000MHZ-16PF-60PPM

13

24

TP_CAM_SHUTDOWN_L

PORT_DK_DDIS_CHG

LAND_DK_DDIS_CHG

DP_SW_SHUTDOWN_L

1

R0633

100K

1%

1/20W

MF

201

2

1

R0636

100K

1/20W

MF

201

2

21

TP_CAM_CLK

GPS_RESET_L

AP_6MHZ_REFCLK

IO_XPNDR_RST_L

PROX_INT_L

AP_PT_DK_ADPTR

AP_LD_DK_ADPTR

USB_MUX_OE_L

USB_MUX_SEL

BACKLIGHT_EN

MLC_RESET_L

1

R0640

22

5%

1/20W

MF

201

2

24M_O

1

C0613

18PF

25V

2

NP0-C0G

201

41

36

42

12

12

17

17

DP_SW_SEL

37

37

27

27

21

13

1

R0637

100K

1%

1/20W

MF MF

201

2

SYNC_MASTER=JAMES

PAGE TITLE

1

R0638

100K

1%

1/20W

201

2

R0691

0

12

1

R0639

100K

1%

1/20W

MF

201

2

AP MAIN

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

L61_6MHZ_REFCLK

COMPASS_RST_L

FORCE_DFU

DFU_STATUS

SYNC_DATE=12/21/2009

28 15

KEEPACT

RADIO_ON

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

6 OF 119

SHEET

6 OF 53

6

19

6

26 35

6

22

6

6

41

SIZE

D

C

B

A

D

Page 7

345678

21

PLACE NEAR U0652

R0760

0

WLAN_SDIO_CLK

39 45

D

C

B

12

1/20W

WLAN_SDIO_DATA<0>

39 45

WLAN_SDIO_DATA<1>

39 45

WLAN_SDIO_DATA<2>

39 45

WLAN_SDIO_DATA<3>

39 45

WLAN_SDIO_CMD

39 45

H3_SDIO_CLK

7

FLASH_CLK

7

FLASH_DIN

12

7

FLASH_DOUT

7

FLASH_CS_N

7

AP_GRAPE_SCLK

23

AP_GRAPE_MOSI

23

AP_GRAPE_MISO

23

AP_GRAPE_CS_N

23

IPC_SCLK

41

IPC_MOSI

41

IPC_MISO

41

IPC_MRDY

41

12 15 37

17 19 26 28 33 36 44

17 19 26 28 33 36 44

44

44

12 13 17 26 35 44

12 13 17 26 35

AP_UART0_TXD

12

AP_UART0_RXD

12

AP_UART1_TXD

11

AP_UART1_RXD

11

AP_UART1_RTS_L

11

AP_UART1_CTS_L

11

AP_UART2_TXD

11

AP_UART2_RXD

11

BB_USART0_RXD_CTRL

11

UMTS_RXD_CTRL

11

AP_UART3_TXD

12

AP_UART3_RXD

12

AP_UART3_RTS_L

12

AP_UART3_CTS_L

12

AP_UART4_TXD

12

AP_UART4_RXD

12

MLC_WC_L

14

PROX_GPIO

42

H3_SDIO_CLK

5%

MF

201

1

R0720

100K

1%

1/20W

MF

201

2

=PP1V8_H3

6 7 9

I2C0_SDA_1V8

7

I2C0_SCL_1V8

7

I2C1_SDA_1V8

7

I2C1_SCL_1V8

7

I2C2_SDA_3V0

7

I2C2_SCL_3V0

7

7

J24

J25

J26

J27

K25

J21

V4

W7

V6

W3

V3

W8

U2

V2

AA2

AA1

V7

W6

1

R0700

1K

1%

1/20W

MF

201

2

Y27

V27

U1

Y2

V1

Y1

V5

W5

V10

V9

R3

P3

R1

AD5

AD2

AD6

W4

AD1

SDIO0_DATA0

SDIO0_DATA1

SDIO0_DATA2

SDIO0_DATA3

SDIO0_CMD

SDIO0_CLK

SPI0_SCLK

SPI0_MOSI

SPI0_MISO

SPI0_SSIN

SPI1_SCLK

SPI1_MOSI

SPI1_MISO

SPI1_SSIN

SPI2_SCLK

SPI2_MOSI

SPI2_MISO

SPI2_SSIN

UART0_TXD

UART0_RXD

UART1_TXD

UART1_RXD

UART1_RTSN

UART1_CTSN

UART2_TXD

UART2_RXD

UART2_RTSN

UART2_CTSN

UART3_TXD

UART3_RXD

UART3_RTSN

UART3_CTSN

UART4_TXD

UART4_RXD

UART4_RTSN

UART4_CTSN

1.8V SERIAL FLASH

A

FLASH_DIN

7

12

FLASH_CLK

7

SERIAL-SPI-8MB-1.8V

D3

WP*

E2

SI

D2

SCK

C2

HOLD*

87 5 4 21

CRITICAL

U0652

H3P

256MB-DDR-FC

FBGA

SYMBOL 5 OF 9

(INT PU)

1

R0701

1K

1%

1/20W

MF

201

2

CRITICAL

U0652

H3P

256MB-DDR-FC

FBGA

SYMBOL 7 OF 9

3.0V

3.0V

B2

VCC

U0808

WLCSP11

AT25DF081UUN

CRITICAL

GND

E3

1

R0702

1K

1%

1/20W

MF

201

2

I2S0_DIN

I2S0_DOUT

I2S0_BCLK

I2S0_LRCK

I2S0_MCK

I2S1_DIN

I2S1_DOUT

I2S1_BCLK

I2S1_LRCK

I2S1_MCK

I2S2_DIN

I2S2_DOUT

I2S2_BCLK

I2S2_LRCK

I2S2_MCK

I2C0_SDA

I2C0_SCL

I2C1_SDA

I2C1_SCL

I2C2_SDA

I2C2_SCL

1

R0703

1K

1%

1/20W

MF

201

2

UART5_RTXD

UART6_TXD

UART6_RXD

UART6_RTSN

UART6_CTSN

CS*

SO

NC

V8

AC5

AC6

AC3

AC4

B3

C3

A4

F1

F4

W21

W22

V23

V18

V20

V24

W19

V25

V15

AB22

R17

R16

Y26

AB23

W23

AB6

AB5

AB4

AB3

AD15

AC15

BATTERY_SWI

AP_UART6_TXD

AP_UART6_RXD

AP_UART6_RTS_L

AP_UART6_CTS_L

1

C0820

0.1UF

10%

6.3V

2

X5R

201

SFLASH_DOUT

I2S0_DIN

I2S0_DOUT

I2S0_BCLK

I2S0_LRCLK

TP_I2S0_MCK

I2S1_DIN

I2S1_DOUT

I2S1_BCLK

I2S1_LRCLK

I2S1_MCK

I2S2_DIN

I2S2_DOUT

I2S2_BCLK

I2S2_LRCK

TP_I2S2_MCK

I2C0_SDA_1V8

I2C0_SCL_1V8

I2C1_SDA_1V8

I2C1_SCL_1V8

I2C2_SDA_3V0

I2C2_SCL_3V0

=PP3V0_IO_H3

7

11 13 15 37

17 19

12

12

=PP1V8_NOR_FLASH

1

R0750

100K

1%

1/20W

MF

201

2

33

12

R0826

1%

1/20W

MF

201

12

12

12

12

12 44

12 44

12 44

12 44

12

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

7

17 19 26 28 33 36 44

7

17 19 26 28 33 36 44

7

44

7

44

7

12 13 17 26 35 44

7

12 13 17 26 35

12

12

15

(PU IN H3)

FLASH_CS_N

FLASH_DOUT

BB_I2S2_TX

BB_I2S2_RX

BB_I2S2_CLK

BB_I2S2_WA0

1

R0704

1K

1%

1/20W

MF

201

2

A1

A18

C15

A2

A23

AD26

AE22

AD9

AE17

AE2

AF10

AB13

AE9

AF1

41

41

41

41

1

R0705

1K

1%

1/20W

MF

201

2

7

7

AF11

AF23

AF16

AF17

AG12

AB14

AF24

AF27

AG23

AG26

AG27

AA17

AA10

AA11

AA15

AA26

AB11

AB17

AC11

AC13

AC17

AD11

AD17

AF2

AG1

AF4

AF7

AG2

B10

B11

B16

B17

B20

B21

B24

B26

B27

C11

C17

D26

D11

D17

E11

F26

E17

F11

F17

G10

G11

G15

H17

H26

G17

H11

H13

H15

J11

K13

K11

A26

A27

AB2

AB9

AC2

AC9

B1

B5

C2

B8

D2

F2

G9

J1

J2

J3

J4

J5

CRITICAL

U0652

H3P

256MB-DDR-FC

FBGA

VSS

(GPIO_3VX,UART0,CFSB,USB11)

(3.0V - FMI0_CEN[4-5],ENET)

BASE PKG

MDDR CKE

RETENTION

SYMBOL 8 OF 9

1.1V - 800MHZ

1.2V - 1GHZ

BOTTOM PKG

MDDR I/O

(3.0V - UART4)

(3.0V - I2C2)

(3.3V - FMI0)

(3.3V - FMI1)

(3.0V - SMII)

CORE

40 PINS

I/O

(1.2V)

VDDIO30

DDR0VDDQ

DDR1VDDQ

VDD

VDDIO18

I/O

VDDIOD

VDDIOD0

VDDIOD1

VDDIOD2

VDDIOD3

VDDIOD4

VDDIOD5

F13

N6

J10

J12

L12

N12

T12

T13

T14

T15

T16

T17

J13

J14

J15

J16

J17

J9

K10

K12

K9

L10

L13

L14

L15

L16

L17

L9

M10

M12

M9

N10

N13

N14

N15

P10

P12

R10

R12

R14

T10

U12

A10

A16

F1

N1

V22

W10

AB10

AC10

AD10

AE10

T21

U27

G13

H10

H9

J6

J7

J8

K8

N8

R8

AB15

W18

AD22

V19

F18

H18

1

C0718

0.22UF

20%

6.3V

2

X5R

201

C0724

1

0.22UF

20%

6.3V

2

X5R

201

0.22UF

20%

6.3V

X5R

201

1

C0774

27PF

5%

25V

2

NP0-C0G

201

C0732

C0745

1

0.47UF

20%

4V

2

CERM-X5R-1

201

C0755

1

0.47UF

20%

4V

2

CERM-X5R-1

201

C0731

1

2

PLACE THE 27PF IN PAIRS AROUND THE IC

C0700

1

2

1

C0760

82PF

5%

25V

2

CERM

0201

C0725

1

0.22UF

20%

6.3V

2

X5R

201

1

0.22UF

20%

6.3V

2

X5R

201

1

C0775

27PF

5%

25V

2

NP0-C0G

201

0.47UF

20%

4V

CERM-X5R-1

201

1

C0712

0.22UF

20%

6.3V

2

X5R

201

1

C0710

20%

6.3V

2

X5R

201

=PP1V2_SDRAM_MDDR

1

C0719

0.22UF

20%

6.3V

2

X5R

201

C0726

1

0.22UF

20%

6.3V

2

X5R

201

C0733

1

0.22UF

20%

6.3V

2

X5R

201

C0746

1

0.47UF

20%

4V

2

CERM-X5R-1

201

C0757

1

0.47UF

20%

4V

2

CERM-X5R-1

201

1

C0776

27PF

5%

25V

2

NP0-C0G

201

C0701

1

0.47UF

20%

4V

2

CERM-X5R-1

201

1

C0713

0.22UF

20%

6.3V

2

X5R

201

1

2

C0734

1

2

C0747

1

0.47UF

20%

4V

2

CERM-X5R-1

201

C0784

1

0.47UF

20%

4V

2

CERM-X5R-1

201

1

2

C0702

1

2

C0711

0.22UF0.22UF

20%

6.3V

X5R

201

8

C0727

1

0.22UF

20%

6.3V

2

X5R

201

0.22UF

20%

6.3V

X5R

201

C0777

27PF

5%

25V

NP0-C0G

201

0.47UF

20%

4V

CERM-X5R-1

201

1

C0714

0.22UF

20%

6.3V

2

X5R

201

15

C0728

1

0.22UF

20%

6.3V

2

X5R

201

C0735

1

0.22UF

20%

6.3V

2

X5R

201

C0748

1

0.47UF

20%

4V

2

CERM-X5R-1

201

C0785

1

0.47UF

20%

4V

2

CERM-X5R-1

201

1

C0765

0.22UF 0.22UF

20%

6.3V

2

X5R

201

C0703

1

0.47UF

20%

4V

2

CERM-X5R-1

201

1

C0715

2

=PP3V3_NAND

1

C0758

4.7UF

20%

6.3V

2

X5R-CERM

402

1

C0749

2

C0786

1

2

0.22UF

20%

6.3V

X5R

201

C0729

1

2

C0736

1

0.22UF

20%

6.3V

2

X5R

201

0.22UF

20%

6.3V

X5R

201

0.47UF

20%

4V

CERM-X5R-1

201

1

C0766

20%

6.3V

2

X5R

201

1

2

C0704

1

0.47UF

20%

4V

2

CERM-X5R-1

201

0.22UF

20%

6.3V

X5R

201

C0750

1

0.22UF

20%

6.3V

2

X5R

201

C0787

1

0.47UF

20%

4V

2

CERM-X5R-1

201

C0779

0.1UF

10%

6.3V

X5R

201

1

C0723

4.7UF

20%

6.3V

2

X5R

402

8

15 43

1

2

1

C0737

27PF

5%

25V

2

NP0-C0G

201

1

C0767

0.22UF

20%

6.3V

2

X5R

201

1

2

1

C0705

1UF

10%

6.3V

2

CERM

402

=PP3V0_IO_H3

XW0740

C0730

0.22UF

20%

6.3V

X5R

201

1

C0751

0.22UF

20%

6.3V

2

X5R

201

C0798

1

2

=PP3V0_IO_H3

C0780

0.1UF

10%

6.3V

X5R

201

NOSTUFF

SM

12

PPVCORE_FB

PLACE THE 27PF IN PAIRS AROUND THE IC

1

2

0.47UF

20%

4V

CERM-X5R-1

201

1

C0720

2

C0738

27PF

5%

25V

NP0-C0G

201

20%

6.3V

X5R

201

1

C0706

1UF

10%

6.3V

2

CERM

402

1

2

7

11 13 15 37

1

C0739

5%

25V

2

NP0-C0G

201

C0752

10UF

20%

6.3V

X5R

603

C0789

1

0.47UF

20%

4V

2

CERM-X5R-1

201

1

C0721

0.22UF0.22UF

20%

6.3V

2

X5R

201

7

11 13 15 37

1

27PF

2

1

C0753

10UF

20%

6.3V

2

X5R

603

1

C0707

1UF

10%

6.3V

2

CERM

402

SYNC_MASTER=JAMES

PAGE TITLE

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

18

C0740

27PF

5%

25V

NP0-C0G

201

C0790

1

0.47UF

20%

4V

2

CERM-X5R-1

201

1

C0769

1UF

10%

6.3V

2

CERM

402

1

1

C0754

10UF

20%

6.3V

2

X5R

603

C0741

27PF

5%

25V

2

NP0-C0G

201

C0791

1

2

1

2

1

C0756

10UF

20%

6.3V

2

X5R

603

0.47UF

20%

4V

CERM-X5R-1

201

C0770

1UF

10%

6.3V

CERM

402

1

C0742

2

1

2

27PF

5%

25V

NP0-C0G

201

C0792

1

2

C0771

1UF

10%

6.3V

CERM

402

1

2

0.47UF

20%

4V

CERM-X5R-1

201

1

2

C0743

27PF

5%

25V

NP0-C0G

201

C0772

10UF

20% 20%

6.3V

X5R

603

=PP1V2_VDDIOD_H3

C0708

1

2

1UF

10%

6.3V

CERM

402

1

C0709

1UF

10%

6.3V

2

CERM

402

1

C0722

10UF

20%

6.3V

2

X5R

603

AP PWR,AP BB&WIFI

Apple Inc.

R

=PPVCORE_H3

1

C0744

27PF

5%

25V

2

NP0-C0G

201

1

C0793

0.47UF

20%

4V

2

CERM-X5R-1

201

=PP1V8_H3

1

2

C0773

10UF

6.3V

X5R

603

6 7 9

15

SYNC_DATE=12/21/2009

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

7 OF 119

SHEET

7 OF 53

15

12 15 37

SIZE

D

C

B

A

D

36

Page 8

345678

21

=PP1V8_SDRAM_H3

6

15

C0824

1

0.47UF

20%

4V

2

CERM-X5R-1

C0804

1

0.22UF

20%

6.3V

2

X5R

201

C0825

1

20%

6.3V

2

X5R

201201

1

C0805

0.22UF

20%

6.3V

2

X5R

201

C0826

1

0.22UF0.22UF

20%

6.3V

2

X5R

201

C0860

1

20%

6.3V

2

X5R

201

C0850

1

20%

6.3V

2

X5R

201

1

C0861

0.22UF0.22UF

20%

6.3V

2

X5R

201

C0851

1

0.22UF0.22UF

20%

6.3V

2

X5R

201

1

C0862

1UF

10%

6.3V

2

CERM

402

1

2

1

C0852

1UF

10%

6.3V

2

CERM

402

1

2

C0813

27PF

5%

25V

NP0-C0G

201

C0806

1UF

10%

6.3V

CERM

402

1

2

1

2

1

2

C0807

1UF

10%

6.3V

CERM

402

1

C0808

1UF

10%

6.3V

2

CERM

402

PLACE THE 27PF IN PAIRS AROUND THE IC

C0814

27PF

5%

25V

NP0-C0G

201

C0853

1UF

10%

6.3V

CERM

402

1

2

C0815

5%

25V

NP0-C0G

201

1

C0854

1UF

10%

6.3V

2

CERM

402

1

C0816

27PF27PF

5%

25V

2

NP0-C0G

201

1

2

C0827

1UF

10%

6.3V

CERM

402

1

2

C0809

1UF

10%

6.3V

CERM

402

1

C0817

27PF

5%

25V

2

NP0-C0G

201

1

2

C0828

1UF

10%

6.3V

CERM

402

1

C0810

1UF 1UF

10%

6.3V

2

CERM

402

1

C0818

5%

25V

2

NP0-C0G

201

1

C0829

10%

6.3V

2

CERM

402

1

C0811

10%

6.3V

2

CERM

402

1

C0819

27PF27PF

5%

25V

2

NP0-C0G

201

1

C0830

1UF1UF

10%

6.3V

2

CERM

402

PLACE THE 27PF IN PAIRS AROUND THE IC

1

C0870

27PF

5%

25V

2

NP0-C0G

201

1

2

C0871

27PF

5%

25V

NP0-C0G

201

1

C0872

27PF

5%

25V

2

NP0-C0G

201

1

2

1

C0832

27PF

5%

25V

2

NP0-C0G

201

1

C0873

27PF

5%

25V

2

NP0-C0G

201

C0812

1UF

10%

6.3V

CERM

402

1

2

C0831

4.7UF

20%

6.3V

X5R

402

A11

A21

AE1

AG11

AG16

AG24

D27

H27

T27

W27

AG10

F27

AB1

AD27

AA27

A17

A24

AC1

AG4

AG7

K27

N27

A20

D1

VDD_MEM

M1

P1

A5

C1

VDDQ

K1

W1

T1

A8

1

C0800

0.22UF

20%

6.3V

2

X5R

201

1

C0801

0.22UF

20%

6.3V

2

X5R

201

1

C0802

0.22UF

20%

6.3V

2

X5R

201

C0803

1

0.22UF

20%

6.3V

2

X5R

201

D

=PP1V2_SDRAM_MDDR

7

15

1

C0821

0.47UF

20%

4V

2

CERM-X5R-1

201

1

2

C0822

0.47UF

20%

4V

CERM-X5R-1

201

1

C0823

0.47UF

20%

4V

2

CERM-X5R-1

201

C

=PP3V3_NAND

7 8

15 43

=PP3V3_NAND

7 8

15 43

R0850

1

100K

1%

1/20W

MF

201

2

R0851

1

100K

1%

1/20W

MF

201

2

1

2

B

R0857

R0856

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

R0853

1

100K

1%

1/20W

MF

201

2

A

R0866

R0865

R0864

R0863

R0861

1

100K

1%

1/20W

MF

201201

2

R0862

1

100K

1%

1/20W

MF

201

2

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

R0860

1

100K

1%

1/20W

MF

2

R0854

100K

1%

1/20W

MF

201

1

2

R0867

100K

1%

1/20W

MF

201

R0855

1

100K

1%

1/20W

MF

201

2

F0RE_N

F0WE_N

F1RE_N

F1WE_N

R0852

1

100K

1%

1/20W

MF

201

2

F0CLE

F0ALE

F1CLE

F1ALE

R0870

1

100K

1%

1/20W

MF

2

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

F0AD<0>

F0AD<1>

F0AD<2>

F0AD<3>

F0AD<4>

F0AD<5>

F0AD<6>

F0AD<7>

F1AD<0>

F1AD<1>

F1AD<2>

F1AD<3>

F1AD<4>

F1AD<5>

F1AD<6>

F1AD<7>

R0877

R0876

R0875

R0874

R0873

R0872

R0871

1

100K

1%

1/20W

MF

201201

2

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

1

2

100K

1%

1/20W

MF

201

R0832

R0836

1

2

100K

1%

1/20W

MF

201

1

2

1

100K

1%

1/20W

MF

201 201

2

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

8

43 44

R0833

100K

1%

1/20W

MF

201

PORT_DK_HI_I

17

LAND_DK_HI_I

17

R0828

1

100K

1%

1/20W

MF

201

2

43 44

43 44

43 44

43 44

43 44

43 44

43 44

43 44

R0831

1

100K

1%

1/20W

MF

2

F0CE0_N

43 44

F0CE1_N

43 44

F0CE2_N

43 44

F0CE3_N

43 44

F0CLE

8

F0ALE

8

F0RE_N

8

F0WE_N

8

F1CE0_N

43 44

F1CE1_N

43 44

F1CE2_N

43 44

F1CE3_N

43 44

LAND_BRICK_ID_P

27

LAND_BRICK_ID_N

27

PORT_BRICK_ID_P

27

PORT_BRICK_ID_N

27

F1CLE

8

F1ALE

8

F1RE_N

8

F1WE_N

8

1

2

87 5 4 21

R0834

100K

1%

1/20W

MF

201

R0825

1

100K

1%

1/20W

MF

201

2

R0827

1

100K

1%

1/20W

MF

201

2

AC18

AG17

AD18

AB19

J23

F25

AF18

AG19

AF19

AF22

AE27

AF20

AG20

AG18

AG25

AF25

AB24

AD23

AE26

AE23

AF21

AG21

FMI0_CEN0

FMI0_CEN1

FMI0_CEN2

FMI0_CEN3

FMI0_CEN4

FMI0_CEN5

FMI0_CLE

FMI0_ALE

FMI0_REN

FMI0_WEN

FMI1_CEN0

FMI1_CEN1

FMI1_CEN2

FMI1_CEN3

FMI1_CEN4

FMI1_CEN5

FMI1_CEN6

FMI1_CEN7

FMI1_CLE

FMI1_ALE

FMI1_REN

FMI1_WEN

CRITICAL

U0652

H3P

256MB-DDR-FC

FBGA

SYMBOL 4 OF 9

(3.0V FOR ALL I/O’S)

FMI0_IO0

FMI0_IO1

FMI0_IO2

FMI0_IO3

FMI0_IO4

FMI0_IO5

FMI0_IO6

FMI0_IO7

FMI1_IO0

FMI1_IO1

FMI1_IO2

FMI1_IO3

FMI1_IO4

FMI1_IO5

FMI1_IO6

FMI1_IO7

ENET_MDC

ENET_MDIO

AC19

AF15

AE18

AG15

AD19

AE19

AB18

AE15

AF26

AC22

AC23

AC27

AC25

AC26

AC24

AG22

K24

J22

F0AD<0>

8

43 44

F0AD<1>

8

43 44

F0AD<2>

8

43 44

F0AD<3>

8

43 44

F0AD<4>

8

43 44

F0AD<5>

8

43 44

F0AD<6>

8

43 44

F0AD<7>

8

43 44

F1AD<0>

8

43 44

F1AD<1>

8

43 44

F1AD<2>

8

43 44

F1AD<3>

8

43 44

F1AD<4>

8

43 44

F1AD<5>

8

43 44

F1AD<6>

8

43 44

F1AD<7>

8

43 44

LAND_DOCK_VIDEO_AMP_EN

MLC_PWR_EN

20

10

SYNC_MASTER=JAMES

PAGE TITLE

AP NAND & GPIO, NOR

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

36

CRITICAL

U0652

256MB-DDR-FC

SYMBOL 9 OF 9

TOP PKG

MDDR CORE

(1.8V)

TOP PKG

MDDR I/O

(1.2V)

Apple Inc.

R

H3P

FBGA

K14

K15

K16

K17

K2

K26

K3

K4

K5

K6

K7

L11

M11

M13

M14

M15

M16

M17

M2

N11

N2

N26

N3

N4

N5

N9

P11

P13

P14

VSS

P15

P16

P17

P2

P23

P24

P4

P5

P6

P9

R11

R13

R15

R2

R4

R5

R6

R7

R9

T11

T2

T26

U11

U13

U14

U15

U16

U17

U19

U22

U26

W17

W2

W26

W9

SYNC_DATE=12/21/2009

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

8 OF 119

SHEET

8 OF 53

SIZE

D

C

B

A

D

Page 9

345678

FL0907

80-OHM-0.2A-0.4-OHM

H3_DP_AVDD_AUX

0.4MM

0.2MM

H3_DP_AVDD

0.4MM

0.2MM

D

H3_DP_AVDDP0

0.4MM

0.2MM

H3_MIPID_0P4V

1

=PP1V8_MIPI

15

=PP1V1_MIPI_PLL

15

1

C0907

0.01UF

10%

10V

2

X5R

201

FL0900

80-OHM-0.2A-0.4-OHM

12

1

C0906

27PF

5%

25V

2

NP0-C0G

201

0201-1

1

C0905

0.1UF

10%

6.3V

2

X5R

201

1

C0904

27PF

5%

25V

2

NP0-C0G

201

PP1V1_MIPI_PHY

0.4MM

0.2MM

C0902

2.2NF

10%

10V

2

X5R

201

H3_DP_AVDDX

0.4MM

0.2MM

H3_DP_DVDD

0.4MM

0.2MM

H3_SMIA_VDD18

0.4MM

0.2MM

C

=PP1V1_MIPI

15

B

1

C0908

0.47UF

20%

4V

2

CERM-X5R-1

201

DIFF_MIC_SEL

34

H3_MIPID_DATA_P<0>

14 45

H3_MIPID_DATA_N<0>

14 45

H3_MIPID_DATA_P<1>

14 45

H3_MIPID_DATA_N<1>

14 45

H3_MIPID_DATA_P<2>

14 45

H3_MIPID_DATA_N<2>

14 45

H3_MIPID_DATA_P<3>

14 45

H3_MIPID_DATA_N<3>

14 45

H3_MIPID_CLK_P

14 45

H3_MIPID_CLK_N

14 45

TP_H3_MIPIC_DATA_P<0>

TP_H3_MIPIC_DATA_N<0>

TP_H3_MIPIC_DATA_P<1>

TP_H3_MIPIC_DATA_N<1>

TP_H3_MIPIC_CLK_P

TP_H3_MIPIC_CLK_N

1

C0903

0.01UF

10%

10V

2

X5R

201

AG13

AF3

AG6

AF5

AG5

AF13

AF12

AE13

AE14

AG3

AE6

AE5

AF6

AF8

AG8

AG9

AF9

MIPI_VSYNC

MIPID_DPDATA0

MIPID_DNDATA0

MIPID_DPDATA1

MIPID_DNDATA1

MIPID_DPDATA2

MIPID_DNDATA2

MIPID_DPDATA3

MIPID_DNDATA3

MIPID_DPCLK

MIPID_DNCLK

MIPIC_DPDATA0

MIPIC_DNDATA0

MIPIC_DPDATA1

MIPIC_DNDATA1

MIPIC_DPCLK

MIPIC_DNCLK

Y18

Y15

MIPI_VDD11

Y13

C23

V13

W13

MIPID_VDD18

MIPID_VDD11_PLL

MIPID_VREG_0P4V

DP_PAD_AVDD_AUX

U0652

H3P

256MB-DDR-FC

FBGA

SYMBOL 2 OF 9

E22

F24

E23

DP_PAD_AVDD0

DP_PAD_AVDD1

DP_PAD_AVDDP0

CRITICAL

C22

DP_PAD_AVDDX

AA18

AC14

G27

SMIA_VDD18

DP_PAD_DVDD

DP_PAD_DC_TP

DP_PAD_R_BIAS

SMIA_RX_DATA+

SMIA_RX_DATA-

SMIA_RX_CLK+

SMIA_RX_CLK-

H3_SMIA_VDD11

0.4MM

0.2MM

SMIA_VDD11

SWI_DATA

DP_HPD

DP_PAD_AUXP

DP_PAD_AUXN

DP_PAD_TX0+

DP_PAD_TX0-

DP_PAD_TX1+

DP_PAD_TX1-

AA19

R19

E27

E26

A22

E25

C27

C26

A25

B25

AD14

AD13

AF14

AG14

1

C0927

1UF

10%

6.3V

2

CERM

402

1

C0926

1UF

10%

6.3V

2

CERM

402

1

C0925

1UF

10%

6.3V

2

CERM

402

1

C0924

1UF

10%

6.3V

2

CERM

402

1

C0923

1UF

10%

6.3V

2

CERM

402

1

C0922

1UF

10%

6.3V

2

CERM

402

1

C0921

1UF

10%

6.3V

2

CERM

402

H3_DP_R_BIAS

1

C0913

0.1UF

10%

6.3V

2

X5R

201

1

C0912

0.1UF

10%

6.3V

2

X5R

201

1

C0911

0.1UF

10%

6.3V

2

X5R

201

1

C0910

0.1UF

10%

6.3V

2

X5R

201

1

C0909

0.1UF

10%

6.3V

2

X5R

201

1

C0901

0.1UF

10%

6.3V

2

X5R

201

80-OHM-0.2A-0.4-OHM

1

C0900

0.1UF

10%

6.3V

2

X5R

201

AP_SWI

TP_DP_ANALOG_TEST

1

R0920

4.99K

2

12

0201-1

FL0906

80-OHM-0.2A-0.4-OHM

12

0201-1

FL0905

80-OHM-0.2A-0.4-OHM

12

0201-1

FL0904

80-OHM-0.2A-0.4-OHM

12

0201-1

FL0903

80-OHM-0.2A-0.4-OHM

12

0201-1

FL0902

80-OHM-0.2A-0.4-OHM

12

0201-1

FL0901

12

0201-1

H3_DP_HPD

H3_DP_AUX_P

H3_DP_AUX_N

(ANALOG DC TEST PORT)

NOTE: 0.6V ANALOG REF

H3_DP_TX_P<0>

H3_DP_TX_N<0>

H3_DP_TX_P<1>

H3_DP_TX_N<1>

TP_CAM_SMIA_DATA_P

TP_CAM_SMIA_DATA_N

TP_CAM_SMIA_CLK_P

TP_CAM_SMIA_CLK_N

1%

1/20W

MF

201

37

37 45

37 45

37 45

37 45

37 45

37 45

=PP1V8_H3

=PP1V8_H3

=PP1V8_H3

=PP1V8_H3

=PP1V1_DPORT

=PP1V8_SMIA

=PP1V1_SMIA

12 15 37

6 7 9

12 15 37

6 7 9

12 15 37

6 7 9

12 15 37

6 7 9

12 15 37

15

15

15

=PP1V8_H3

6 7 9

R0952

0

12

5%

1/20W

MF

201

R0953

0

5%

1/20W

MF

12

201

1

2

AP_SWI_R

21

=PP3V3_MLC

1

A2

C0951

0.1UF

10%

6.3V

2

X5R

201

P/N 311S0487

C0950

0.1UF

10%

6.3V

X5R

201

SWI_BLCTRL

1

R0950

10K

5%

1/20W

MF

201

2

19

SAME PART AS APN:353S2652 BUT CE PREFERRED PART NUMBER

A1

VCCBVCCA

U0901

SN74AVCH1T45

BGA1

C1 C2

AB

CRITICAL

B2

DIR

GND

B1

MLC_SWI

13 14 15 25

13

D

C

B

A

MIPI_VSS

DP_PAD_AVSS1

DP_PAD_AVSS0

DP_PAD_AVSS_AUX

B23

D22

AA13

E24

W15

87 5 4 21

DP_PAD_DVSS

DP_PAD_AVSSP0

DP_PAD_AVSSX

G26

D23

B22

SMIA_VSS18

Y19

36

SYNC_MASTER=JAMES

PAGE TITLE

AP RGB/CLCD,CAMERA

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

SYNC_DATE=12/21/2009

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

9 OF 119

SHEET

9 OF 53

SIZE

A

D

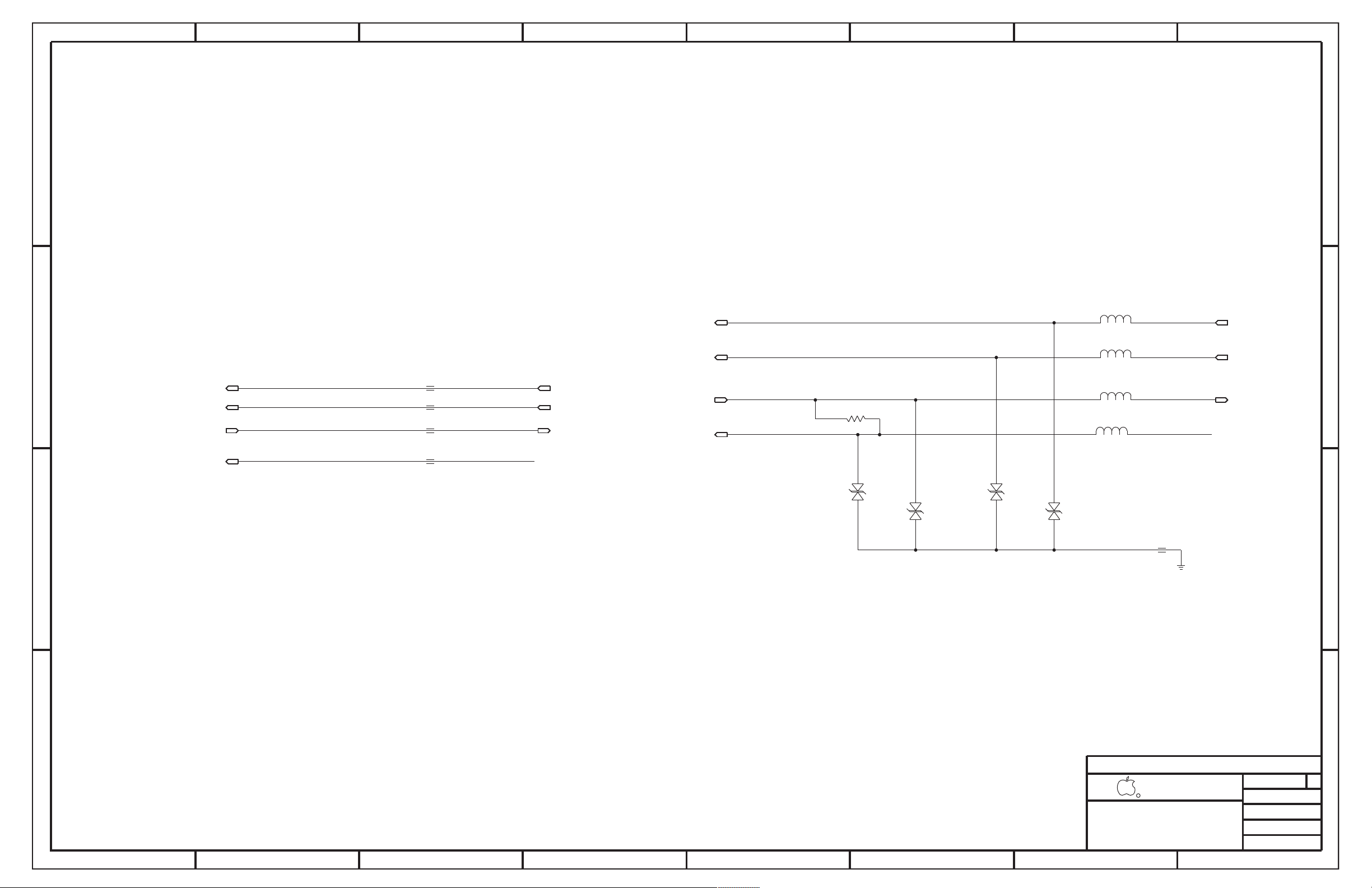

Page 10

345678

FL1000

240-OHM-0.2A-0.8-OHM

=PP3V0_VIDEO_H3

15

D

=PP3V0_VIDEO_BUFFER

10 15

JTAG_DAP

R1003

75

12 39 45

DOCK2_C_Y

12 39 45

DOCK2_CVBS_PB

PORT_DOCK_C_Y

MAKE_BASE=TRUE

PORT_DOCK_COMP_PB

MAKE_BASE=TRUE

C

12 39 45

DOCK2_Y_PR

B

38 45

DOCK1_Y_PR

DOCK1_CVBS_PB

38 45

DOCK1_C_Y

38 45

PORT_DOCK_Y_PR

MAKE_BASE=TRUE

LAND_DOCK_Y_PR

MAKE_BASE=TRUE

LAND_DOCK_COMP_PB

MAKE_BASE=TRUE

LAND_DOCK_C_Y

MAKE_BASE=TRUE

12

1%

1/20W

MF

201

JTAG_DAP

R1004

75

12

1%

1/20W

MF

201

JTAG_DAP

R1043

75

12

1%

1/20W

MF

201

LANDSCAPE_DOCK

R1050

75

12

1%

1/20W

MF

201

LANDSCAPE_DOCK

R1051

75

12

1%

1/20W

MF

201

LANDSCAPE_DOCK

R1052

75

12

1%

1/20W

MF

201

45

PORT_COUT

45

PORT_CVBS_OUT

45

PORT_YOUT

=PP3V0_VIDEO_BUFFER

10 15

45

LAND_YOUT

LAND_CVBS_OUT

45

45

LAND_COUT

10

VIDEO_AGND

PORTRAIT_DOCK

1

C1026

0.1UF

10%

6.3V

2

X5R

201

LANDSCAPE_DOCK

1

C1030

0.1UF

10%

6.3V

2

X5R

201

CH.1OUT

CH.2OUT

CH.3OUT

U1009

THS7319

CH.1OUT

CH.2OUT

CH.3OUT

U1010

THS7319

CRITICAL

PORTRAIT_DOCK

VS+

BGA

CH.1IN

CRITICAL

CH.2IN

CH.3IN

GND

A2 C2

LANDSCAPE_DOCK

VS+

BGA

CH.1IN

CH.2IN

CH.3IN

GND

A2 C2

LANDSCAPE_DOCK

EN

EN

A1A3

B1B3

C1C3

B2

A1A3

B1B3

C1C3

B2

R1008

100K

R1053

100K

1/20W

PORT_DOCK_VIDEO_AMP_EN

1

5%

1/20W

MF

201

2

DAC_OUT3

DAC_OUT2

DAC_OUT1

LAND_DOCK_VIDEO_AMP_EN

1

5%

MF

201

2

10 45

10 45

10 45

(YIN)

(CVBSIN)

(CIN)

CIN

CVBSIN

YIN

10 45

DAC_OUT1

10 45

DAC_OUT2

10 45

DAC_OUT3

6

NOTE: PLACE R1005,R1046-47 NEAR U0652

8

12

0201

VIDEO_AGND

10

R1005

1

200

1%

1/20W

MF

201

2

R1046

1

200

1%

1/20W

MF

201

2

0.4MM

0.2MM

D14

C13

DAC_AVDD30D

DAC_AVDD30A

CRITICAL

1

C1020

0.1UF

10%

6.3V

2

X5R

201

1

C1028

1UF

10%

6.3V

2

CERM

402

1

C1071

0.1UF

10%

6.3V

2

X5R

201

U0652

H3P

256MB-DDR-FC

A15

DAC_OUT1

A14

DAC_OUT2 DAC_IREF

B13

DAC_OUT3

R1047

1

200

1%

1/20W

MF

2

201

NOSTUFF

XW1000

SM

12

PART NUMBER

353S2684 INTERSIL

ALTERNATE FOR

PART NUMBER

353S2493

BOM OPTION

FBGA

SYMBOL 3 OF 9

DAC_AVSS30D

DAC_AVSS30A2

DAC_AVSS30A1

B14

C14

D15

REF DES

U1009,U1010

COMMENTS:

DAC_VREF

DAC_COMP

E19

A13

E18

10

VIDEO_AGND

TABLE_ALT_HEAD

TABLE_ALT_ITEM

21

PP3V0_DAC_AVDD_A

1

C1014

0.1UF

10%

6.3V

2

X5R

201

DAC_VREF

DAC_IREF

DAC_COMP

0.3MM

0.175MM

1

R1012

6.34K

1%

1/20W

MF

201

2

1

C1015

0.1UF

10%

6.3V

2

X5R

201

D

C

B

A

SYNC_MASTER=JAMES

PAGE TITLE

AP TVOUT

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

87 5 4 21

36

SYNC_DATE=12/21/2009

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

10 OF 119

SHEET

10 OF 53

SIZE

A

D

Page 11

345678

21

AP_UART1_CTS_L

7

7

D

BB_USART0_TXD

11 12

AP_UART2_RXD

7

12

UMTS_TXD

DOCK_UART_CTRL

19

U1100

74LVC2G125

2

A1

1

1OE*

5

A2

7

2OE*

VCC

SOT833

GND

K48M

8

CRITICAL

4

Y1

Y2

=PP1V8_SDRAM_MISC

1

C1100

2

6

3

11 15 36

0.1UF

10%

6.3V

X5R

201

LAND_DOCK_POD_TO_ACC

LAND_DOCK_ACC_TO_POD

1

R1101

1M

1%

1/20W

MF

201

2

11 38

11 38

=PP3V0_HP_DET_BIAS

1

R1100

100K

1%

1/20W

MF

201

2

15 27 33 34 36 39

AP_UART1_TXD

7

LAND_DOCK_P17

38

BB_USART0_RXD_CTRL

7

C

K48M

8

CRITICAL

VCC

U1101

74LVC2G126GT/S500

SOT833

AP_UART4_TXD_MUX

11 12

AP_UART4_TXD_MUX

11 12 11 38

2

A1 Y1

1

1OE

5

A2

7

2OE

GND

R1130

12

1/20W

K48

201

6

3

Y2

4

0

5%

MF

LAND_DOCK_POD_TO_ACC

=PP3V0_IO_H3

1

C1101

0.1UF

10%

6.3V

2

X5R

201

AP_UART4_RXD_MUX

11 12

7

13 15 37

AP_UART2_TXD

7

LAND_DOCK_P14

38

UMTS_RXD_CTRL

7

B

K48

R1131

0

LAND_DOCK_ACC_TO_POD

11 38 11 12

12

5%

1/20W

MF

201

AP_UART4_RXD_MUX

AP_UART1_RTS_L

AP_UART1_RXD

7

K48M_DEVELOPMENT

1

R1154

100K

1%

1/20W

MF

201

2

K48M_DEVELOPMENT

1

R1155

100K

1%

1/20W

MF

201

2

K48M_PRODUCTION

1

I1

SELECTOR

3

I0

S

6

K48M_DEVELOPMENT

1

R1104

100K

1%

1/20W

MF

201

2

K48M_PRODUCTION

R1105

I1

1

SELECTOR

I0

3

S

6

K48M_DEVELOPMENT

1

R1106

100K

1%

1/20W

MF

201

2

BB_USART0_RTS_L

BB_USART0_CTS_L

R1103

0

12

5%

1/20W

MF

201

K48M_DEVELOPMENT

U1104

74LVC1G157

SOT891

5

VCC

MUX

OUTPUT

GND

2

0

12

5%

1/20W

MF

201

K48M_DEVELOPMENT

U1105

74LVC1G157

SOT891

5

VCC

MUX

Y

OUTPUT

GND

2

BB_USART0_TXD

4

Y

4

12

12

11 12

=PP1V8_SDRAM_MISC

K48M_DEVELOPMENT

1

C1104

0.1UF

10%

6.3V

2

X5R

201

BB_USART0_RXD

=PP1V8_SDRAM_MISC

K48M_DEVELOPMENT

1

C1105

0.1UF

10%

6.3V

2

X5R

201

UMTS_RXD

D

11 15 36

12

C

11 15 36

12

B

A

SYNC_MASTER=JAMES

PAGE TITLE

3G AND DEBUG MUXES

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

87 5 4 21

36

SYNC_DATE=12/21/2009

DRAWING NUMBER

051-8245

REVISION

B.0.0

BRANCH

PAGE

11 OF 119

SHEET

11 OF 53

SIZE

A

D

Page 12

345678

21

BOARD ID

=PP1V8_H3

12 15 37

6 7 9

D

BOARD ID <5> = BOARD_ID[1]

BOARD ID <4> = BOARD_ID[0]

BOARD ID <6> = BOARD_ID[2]

FLASH_DOUT

FLASH_DIN

7

FLASH_CLK

1

R0625

3.92K

1%

1/20W

MF

201

2

BOARD_ID[2-0]

010

K48 AP

011

K48 DEV

I2S0_DIN

7

I2S0_DOUT

7

I2S0_BCLK

7

I2S0_LRCLK

7

7

44

I2S1_DIN

7

44

I2S1_DOUT

7

44

I2S1_BCLK

7

44

I2S1_LRCLK

7

I2S1_MCK

7

AP_UART0_TXD

7

AP_UART0_RXD

7

AP_UART6_TXD

7

AP_UART6_RXD

7

AP_UART6_RTS_L

7

AP_UART6_CTS_L

ALIASES FROM PAGE 7

MAKE_BASE=TRUE

MAKE_BASE=TRUE

AUD_I2S_BITCLK_L61

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

PORT_DOCK_POD_TO_ACC

MAKE_BASE=TRUE

PORT_DOCK_ACC_TO_POD

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

AUD_I2S_SDOUT_L61

AUD_I2S_SDIN_L61

AUD_I2S_LRC_L61

BB_I2S1_RX

BB_I2S1_TX

BB_I2S1_CLK

BB_I2S1_WA0

L61_I2S_MCLK

GPS_UART_RX

GPS_UART_TX

GPS_UARTS_CTS_L

GPS_UARTS_RTS_L

28

28

28

28

32 41

32 41

32 41

32 41

28

39

39

41

41

41

41

BB_USART0_TXD

11

BB_USART0_RXD

11

BB_USART0_RTS_L

11

BB_USART0_CTS_L

11

UMTS_TXD

11

UMTS_RXD

11

7

AP_UART4_TXD

7

AP_UART4_RXD

6

12

AP_GPIO41_BRD_REV2

ALIASES FROM PAGE 11

BB_USART0_TXD_CONN

MAKE_BASE=TRUE

BB_USART0_RXD_CONN

MAKE_BASE=TRUE

BB_USART0_RTS_L_CONN

MAKE_BASE=TRUE

BB_USART0_CTS_L_CONN

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

MAKE_BASE=TRUE

UMTS_TXD_CONN

UMTS_RXD_CONN

AP_UART4_TXD_MUX

AP_UART4_RXD_MUX

BB_FLASH_ACTIVE

38

41

41

41

41

41

41

11

11

41

LAND_USB_PWR

ALIASES FROM PAGE 50

USB_PWR_A

MAKE_BASE=TRUE

CONN_AP_UART3_RTS_L

16

39

CONN_AP_UART3_CTS_L

39

CONN_AP_UART3_TXD

39

39

CONN_AP_UART3_RXD

ALIASES FROM PAGE 51

AP_UART3_RTS_L

MAKE_BASE=TRUE

AP_UART3_CTS_L

MAKE_BASE=TRUE

AP_UART3_TXD

MAKE_BASE=TRUE

AP_UART3_RXD

MAKE_BASE=TRUE

7

7

7

7

D

BOOT CONFIG ID

=PP1V8_H3

6 7 9

12 15 37

6

BOARD ID <3> = BOOT_CONFIG[3]

BOARD ID <2> = BOOT_CONFIG[2]

BOARD ID <1> = BOOT_CONFIG[1]

C

BOARD ID <0> = BOOT_CONFIG[0]

AP_GPIO29_BOARD_ID_3

6

AP_GPIO28_BOARD_ID_2

AP_GPIO25_BOARD_ID_1

6

CODEC_IRQ_N (GPIO18)

NC_BOARD_ID_3

MAKE_BASE=TRUE

NC_BOARD_ID_2

MAKE_BASE=TRUE

NOSTUFF

1

R0622

3.92K

1%

1/20W

MF

201

2

6

BB_RST

MAKE_BASE=TRUE

BB_RST_RADIO

PROX_SDA_3V0

42

PROX_SCL_3V0

41

42

PROX_ACSHIELD_CONN

42

BOOT_CONFIG[3-0]

SPI0 WITH TEST MODE

0010

SPI0 (DVT AND BEYOND)

0000

ALIASES FOR PAGE 57

I2C2_SDA_3V0

I2C2_SCL_3V0

PROX_ACSHIELD

7

13 17 26 35 44

7

13 17 26 35

42

C

BOARD REVISION

AP_GPIO41_BRD_REV2

6

12

AP_GPIO40_BRD_REV1

6

AP_GPIO39_BRD_REV0

6

B

JTAG_DAP

12

0

AP_JTAG_SEL

R0663

NOSTUFF

R0661

RESET_1V8_N

6

A

JTAG_TRSTN_CTRL

6

6

AP_PT_DK_ADPTR

6

AP_LD_DK_ADPTR

12

H3_A0_DAP

R1203

12

87 5 4 21

BRD_REV[2-0]

000

001

010

0

0

PORT_DK_ADPTR

LAND_DK_ADPTR

NOSTUFF

1

R0627

3.92K

1%

1/20W

MF

201

2

PROTO 3

EVT 1

EVT 2

DVT011

6

AP_TRSTN

NOSTUFF

1

R0628

3.92K

1%

1/20W

MF

201

2

6

12

16

16

1

R0629

3.92K

1%

1/20W

MF

201

2

6

NC_AP_TDO

44

12

AP_TDI

6

AP_TRSTN

6

B

FOR REFERENCE

NOTE: JTAG SCAN DUMP

CURRENT SETTING ->

JTAG_TAP

R1200

0

44

AP_TDO

TRUE

12

5%

1/20W

MF

201

DOCK2_C_Y

10 39 45

JTAG_TAP

R1202

0

12

5%

1/20W

MF

201

DOCK2_Y_PR

10 39 45

JTAG_TAP

R1201

0

12

5%

1/20W

MF

201

DOCK2_CVBS_PB

10 39 45

BOOT_CONFIG[3:0]

0000 SPI0

0001 SPI1

0010 SPI0 W/TEST

0011 SPI1 W/TEST

0100 FMI0 2CS

0101 FMI0 4CS

0110 FMI0 4CS W/TEST

0111 RESERVED

1000 FMI1 2 CS

1001 FMI1 4 CS

1010 FMI1 4CS W/TEST

1100 FMI0/1 2/2 CS

1101 FMI0/1 4/4 CS

1110 FMI0/1 4/4 CS W/TEST

1111 RESERVED

SYNC_MASTER=JAMES

PAGE TITLE

AP MISC & ALIASES

Apple Inc.

R

NOTICE OF PROPRIETARY PROPERTY:

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT