APL5331

3A Bus Termination Regulator

Features General Description (Cont.)

••

• Provide Bi-direction Current

••

- Sourcing or Sinking Current up to 3A

••

• 1.25V/0.9V Output for DDR I/II Applications

••

••

• Fast Transient Response

••

••

• High Output Accuracy

••

- ±20mV over Load, VOUT Offset and

Temperature

••

• Adjustable Output Voltage by External Resistors

••

••

• Current-Limit Protection

••

••

• On-Chip Thermal Shutdown

••

••

• Shutdown for Standby or Suspend Mode

••

••

• Simple SOP-8, SOP-8-P with thermal pad,

••

TO-252- 5 and TO-263-5 Packages

Applications

• DDR I/II SDRAM Termination

• SSTL-2/3 Termination Voltage

On-chip thermal shutdown provides protection against

any combination of overload that would create excessive junction temperature. The output voltage of

APL5331 track the voltage at VREF pin. A resistor

divider connected to VIN, GND and VREF pins is

used to provide a half voltage of VIN to VREF pin. In

addition, an external ceramic capacitor and an opendrain transistor connected to VREF pin provides softstart and shutdown control respectively. Pulling and

holding the VREF to GND shuts off the output. The

output of APL5331 will be high impedance after being shut down by VREF or thermal shutdown function.

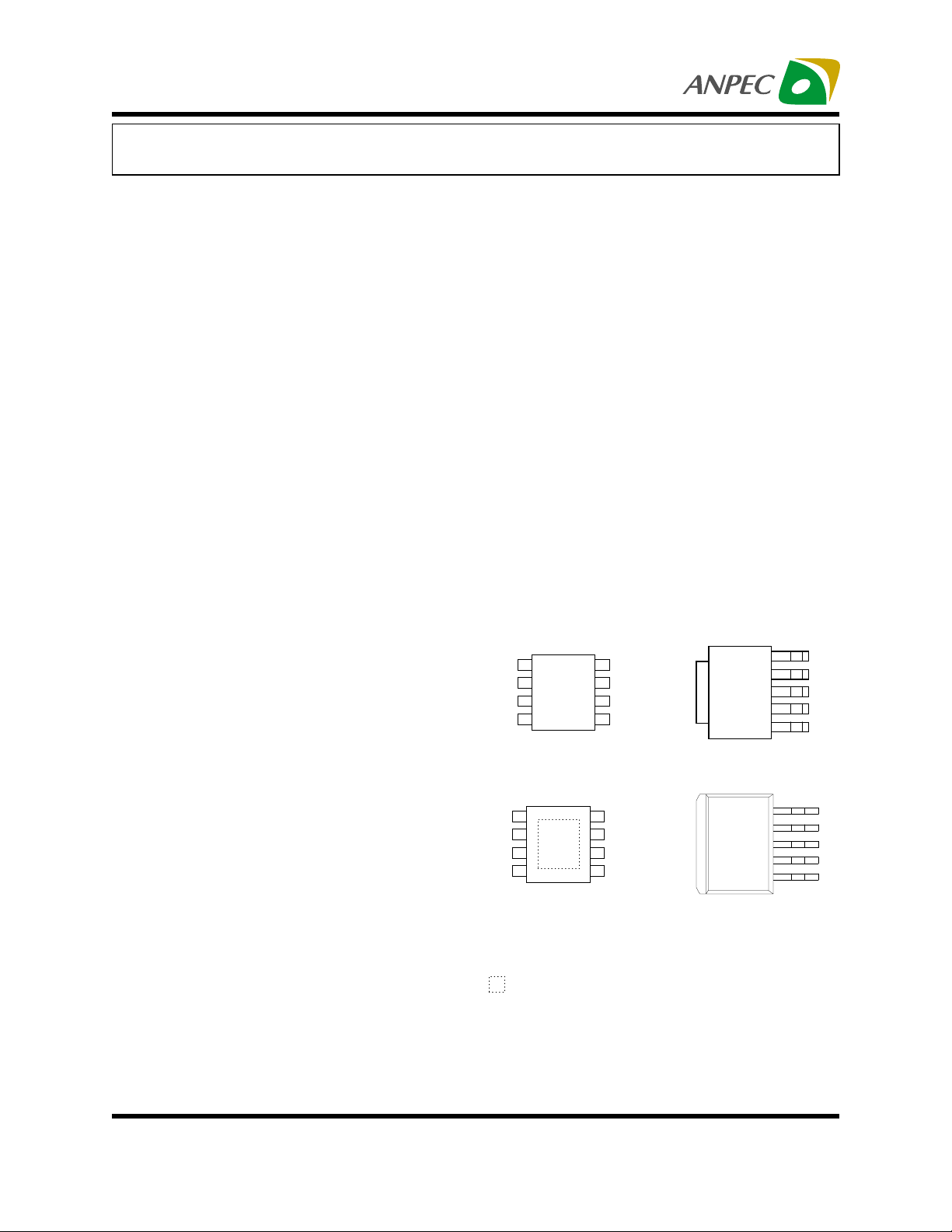

Pin Configuration

12345

VOUT

VREF

VCNTL

GND

VIN

VIN

1

GND

2

VREF

3

VOUT VCNTL

45

VCNTL

8

VCNTL

7

VCNTL

6

TAB is VCNTL

• Applications Requiring the Regulator with

Bi-direction 3A Current Capability

General Description

SOP-8 (Top View)

VIN

1

GND

2

VREF

3

VOUT

45

TO-252-5 (Top View)

NC

8

NC

7

6

VCNTL

NC

TAB is VCNTL

5

4

3

2

1

The APL5331 linear regulator is designed to provide

a regulated voltage with bi-directional output current

SOP-8-P (Top View)

TO-263-5 (Top View)

for DDR-SDRAM termination. The APL5331 integrates

two power transistors to source or sink current up to

3A. It also incorporate current-limit, thermal shutdown and shutdown control functions into a single

NC = No internal connection

= Thermal Pad

(connected to GND plane for better heat

dissipation)

chip. Current-limit circuit limits the short-circuit

current.

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise

customers to obtain the latest version of relevant information to verify before placing orders.

Copyright ANPEC Electronics Corp.

Rev. A.8 - Oct., 2003

www.anpec.com.tw1

VOUT

VREF

VCNTL

GND

VIN

APL5331

Ordering and Marking Information

APL5331

APL5331K C-TR :

APL5331 KAC -TR :

APL5331 U5C -TR :

APL5331 G5C -TR :

Lead Free Code

Handling Code

Tem p. Range

Package Cod e

APL5331

XXXXX

APL5331

XXXXX

Package Cod e

K : SO P-8 KA : SOP-8-P

U5 : TO-252-5 G5 : T O-263-5

Tem p. Range

C : 0 to 7 0

Handling Code

TR : Tape & Re el

Lead Free Code

L : Lead Free Device Blank : Orginal Device

XXXXX - Date Code

XXXXX - Date Code

o

C

Pin Description

PIN NAME I/O DESCRIPTION

Main power input pin. Connect this pin to a voltage source and an input

VIN I

capacitor. The APL5331 sources current to VOUT pin by controlling the upper

NPN pass transistor, providing a current path from VIN pin.

Power and signal ground. Connect this pin to s ystem ground plane with shortest

GND O

traces. The APL5331 sink s current from VOUT pin by controlling the lower NPN

pass transistor, pro viding a current path to GND pin. This pin is also the ground

path fo r inte rn a l co n tr o l c ircu itr y.

Power input pin for internal control circuitry. Connect this pin to a voltage source,

VCNTL I

providing a bias for the internal control circuitry. A bypass capacitor is usually

connected near this pin.

Reference voltage input and active-low shutdown control pin. Apply a voltage to

this pin as a reference voltage for the APL5331. Connect this pin to a resistor

VREF I

divider, between VIN and GND, and a capacitor for soft-start and filtering noise

purposes. Applying and holding this pin low b y an o pen-drain transistor to shut

down th e o u tp u t.

Output pin of the regulator. Connect this pin to load. Output capacitors

VOUT O

connected this pin improves stability and transient response. The output voltage

tracks the reference voltage and is capable of sourcing or sinking current up to

3A.

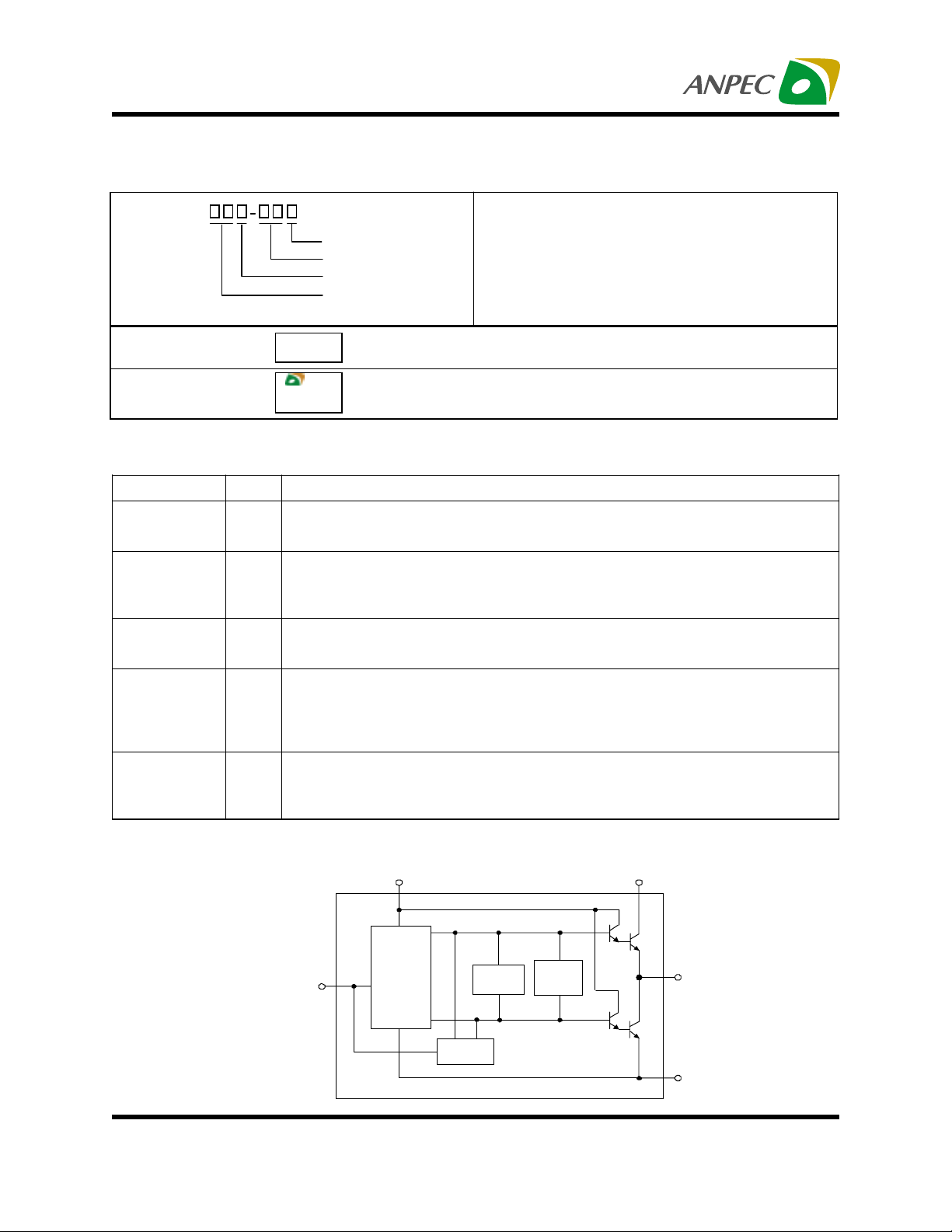

Block Diagram

VCNTL

VIN

VREF

Copyright ANPEC Electronics Corp.

Rev. A.8 - Oct., 2003

Voltage

Regulation

Shutdown

Therm al

Limit

Current

Limit

VOUT

GND

www.anpec.com.tw2

APL5331

Absolute Maximum Ratings

Symbol Parameter Rating Unit

CNTL

V

IN

V

D

P

J

T

STG

T

SDR

T

ESD

V

Thermal Characteristics

VCNTL Supply Voltage, VCNTL to GND -0.2 ~ 7 V

VIN Supply Voltage, VIN to GN D -0.2 ~ 3.9 V

Power Dissipation Internally Limited W

Junction Temperature 150

Storage Temperature -65 ~ 150

Soldering Temperature, 10 Seconds 300

Minimum ESD R ating (Human Body Mode)

±3

o

C

o

C

o

C

kV

Symbol

θ

JA

Thermal Resistance in Free Air

Parameter Rating Unit

SOP-8

SOP-8-P

TO-252-5

TO-263-5

160

80

80

50

°C/W

Recommended Operating Conditions

Symbol Parameter Range Unit

CNTL

V

IN

V

REF

V

OUT

I

J

T

Note1 : The symbol “+” means the VOUT sources current to load; the symbol “-“ means the VOUT sinks

current to GND.

Note2 : The max. IOUT varies with the TJ. Please refer to the typical characteristics.

VCNTL Supply Voltage 3.1 ~ 6V V

VIN Supply Voltage 1.6 ~ 3.5 V

VREF Input Voltage 0.8 ~ 1.75 V

VOUT Output Current (Note1, 2) -3 ~ +3 A

Junction Temperature 0 ~ 125

o

C

Copyright ANPEC Electronics Corp.

Rev. A.8 - Oct., 2003

www.anpec.com.tw3

APL5331

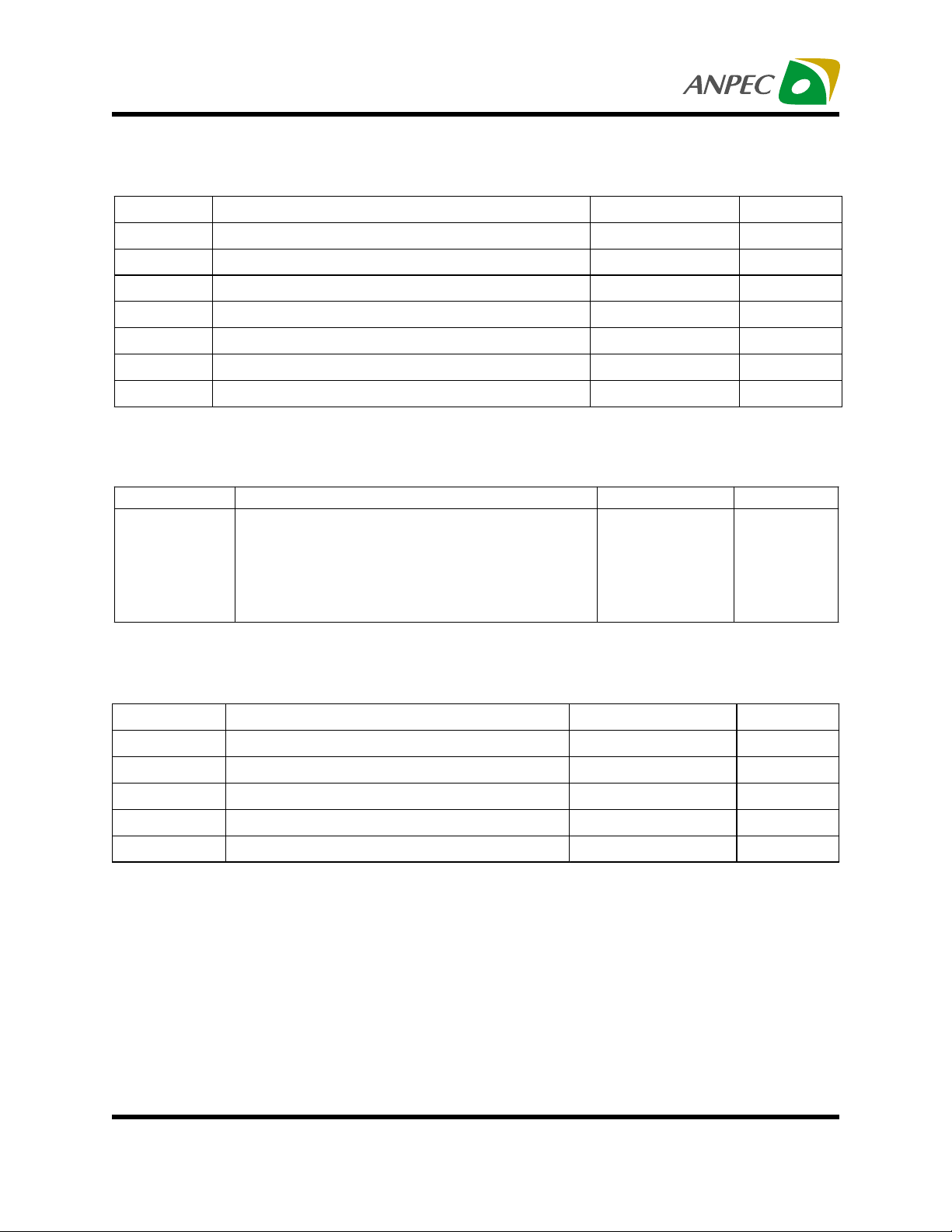

Electrical Characteristics

Refer to the typical application circuit. These specifications apply over, VCNTL=3.3V, VIN=2.5V/1.8V,

VREF=0.5VIN and TJ= 0 to 125°C, unless otherwise specified. Typical values refer to TJ =25°C.

Symbol

Parameter Test Conditions

Output Voltage

VOUT O utput Voltage I

OUT

V

System Accuracy

VOUT O ffset Voltage

OS

V

OUT–VREF

(V

Load Regulation

)

Protection

LIM

Current Limit

I

Thermal Shutdown

SD

T

Tem perature

Therm al Shutdown Hysteres is

Input Current

CNTL

VCNT L Supply Current

I

VREF Bias Current

VREF

I

(The current flows out of VREF)

Shutdown Control

Shutdown Threshold Voltage

APL5331

Min Typ Max

OUT

=0A

Over temperature, VOUT offset, and

load regulation

OUT

I

=+10mA -14

OUT

I

=-10mA

OUT

I

=+10mA to +3A -6

OUT

= -10 mA to -3 A

I

Sourcing Current TJ=25°C

IN

(V

=2.5V) TJ=125°C

Sinking Current TJ=25°C

IN

(V

=2.5V) TJ=125°C

Sourcing Current TJ=25°C

IN

(V

=1.8V) TJ=125°C

J

Sinking Current T

IN

(V

=1.8V) TJ=125°C

Rising T

OUT

I

OUT

I

CNTL

V

REF

V

REF

V

REF

V

J

=0A 2

=±3A (Norm al Operation),

=5V

=GND (S hutdown)

=1.25V/0.9V (Normal Operation)

=GND (Shutdown)

=25°C

-20 20 mV

+3.3 +3.6

-3.3 -3.6

+2.9 +3.2

-2.9 -3.2

0.2

REF

V

-9

2

-3

7

+3.1

-3.1

+2.6

-2.6

150

40

4.5

50 110

2.6

150

20

0.35

Unit

V

mV

8

mV

12

A

o

C

o

C

6

mA

500 nA

40

µA

0.65 V

Copyright ANPEC Electronics Corp.

Rev. A.8 - Oct., 2003

www.anpec.com.tw4

APL5331

Typical Application Circuit

1. VOUT=1.25V/0.9V Application

V

CNTL

+3.3V

V

IN

+2.5V/1.8 V

R

1

1k

R

2

1k

Q

1

470uF

Shutdown

C

IN

V

REF

C

0.1uF

SS

VIN

VREF

GND

VCNTL

VOU T

C

47uF

CNTL

C

OUT

470uF

V

OUT

+1.25V/0.9V

-3~+3A

GND

COUT : 470µF, ESR=25mΩ

R1, R2 : 1kΩ, 1%

Q1 : APM2300 AC

Note : Since R1 and R2 are very small, the voltage offset

caused by the bias current of VREF can be ignore.

2. VOUT=1.4V Application

CNTL

V

+5V

IN

V

+2.8V

IN

C

470µF

R

1k

R

1k

GND

VIN

1

2

VREF

REF

V

SS

C

0.1µF

GND

VCNTL

VOU T

C

47µF

CNTL

OUT

C

470µF

OUT

V

+1.4V/

-3~+3A

GND

Copyright ANPEC Electronics Corp.

Rev. A.8 - Oct., 2003

GND

www.anpec.com.tw5

APL5331

Typical Characteristics

Sourcing Current-Limit

vs Junction T emperature

5.0

4.5

4.0

3.5

3.0

2.5

Current-Limit, ILIM (A)

2.0

VCNTL=5V,VIN=2.5V

VCNTL=3.3V,VIN=2.5V

VCNTL=5V,VIN=1.8V

VCNTL=3.3V,VIN=1.8V

-50 -25 0 25 50 75 100 125

Junction Temperature (°C)

VREF Bias Current

vs Junction T emperature

0.40

V

=1.25V/0.9V

REF

0.35

0.30

0.25

0.20

0.15

0.10

0.05

VREF Bias Current, IVREF (µA)

0.00

-50 -25 0 25 50 75 100 125

Sinking Current-Limit

vs Junction T emperature

-2.0

-2.5

VCNTL=3.3V,VIN=1.8V

-3.0

-3.5

-4.0

Current-Limit, ILIM (A)

-4.5

-5.0

VCNTL=5V,VIN=2.5V

-50 -25 0 25 50 75 100 125

VCNTL=5V,VIN=1.8V

VCNTL=3.3V,VIN=2.5V

Junction Temperature (°C)

VREF Shutdown Threshold

vs Junction T emperature

0.6

0.5

V

=5V

CNTL

0.4

0.3

V

=3.3V

CNTL

0.2

VREF Shutdown Threshold (V)

0.1

-50 -25 0 25 50 75 100 125

Junction Temperature (°C)

Copyright ANPEC Electronics Corp.

Rev. A.8 - Oct., 2003

Junction Temperature (°C)

www.anpec.com.tw6

APL5331

Typical Characteristics (Cont.)

VOUT Offset V oltage

vs Junction T emperature

6

V

=1.25V/0.9V

REF

4

2

0

-2

-4

-6

-8

-10

-12

-14

VOUT Offset V oltage, VOS (mV)

-16

-50 -25 0 25 50 75 100 125

I

OUT

=+10mA

I

OUT

=-10mA

Junction Temperature (°C)

VREF Bias Current

vs VREF Supply Voltage

22

TJ=25°C

20

18

16

14

12

10

8

6

4

VREF Bias Current, IVREF (µA)

2

0

0.0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

Quiescent VCNTL Current

vs Junction T emperature

7.0

I

=0A

6.5

6.0

5.5

5.0

4.5

4.0

3.5

3.0

2.5

Quiescent VCNTL Current (mA)

2.0

OUT

V

=5V

CNTL

V

=3.3V

CNTL

-50-250 255075100125

Junction Temperature (°C)

VREF Supply Votage, VREF (V)

Copyright ANPEC Electronics Corp.

Rev. A.8 - Oct., 2003

www.anpec.com.tw7

Loading...

Loading...