Page 1

a

W5.0

Assembler and Preprocessor Manual

Revision 3.2, March 2009

Part Number:

82-000420-04

Analog Devices, Inc.

One Technology Way

Norwood, Mass. 02062-9106

Page 2

Copyright Information

© 2009 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written

consent from Analog Devices, Inc.

Printed in the USA.

Disclaimer

Analog Devices, Inc. reserves the right to change this product without

prior notice. Information furnished by Analog Devices is believed to be

accurate and reliable. However, no responsibility is assumed by Analog

Devices for its use; nor for any infringement of patents or other rights of

third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

Trademark and Service Mark Notice

The Analog Devices logo, VisualDSP++, Blackfin, SHARC, and TigerSHARC are registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of

their respective owners.

Page 3

CONTENTS

PREFACE

Purpose ......................................................................................... xiii

Intended Audience ........................................................................ xiii

Manual Contents ........................................................................... xiv

What’s New in this Manual ............................................................ xiv

Technical or Customer Support ....................................................... xv

Supported Processors ...................................................................... xvi

Product Information ...................................................................... xvi

Analog Devices Web Site .......................................................... xvi

VisualDSP++ Online Documentation ...................................... xvii

Technical Library CD ............................................................. xviii

Notation Conventions .................................................................. xviii

ASSEMBLER

Assembler Guide ........................................................................... 1-2

Assembler Overview ................................................................ 1-3

Writing Assembly Programs ..................................................... 1-4

Program Content ................................................................ 1-6

Assembly Instructions ..................................................... 1-6

VisualDSP++ 5.0 Assembler and Preprocessor Manual iii

Page 4

CONTENTS

Assembler Directives ....................................................... 1-6

Preprocessor Commands ................................................. 1-7

Program Structure .............................................................. 1-7

Code File Structure for SHARC Processors .................... 1-10

LDF for SHARC Processors .......................................... 1-10

Code File Structure for TigerSHARC Processors ............ 1-13

LDF for TigerSHARC Processors .................................. 1-13

Code File Structure for Blackfin Processors .................... 1-17

LDF for Blackfin Processors .......................................... 1-18

Program Interfacing Requirements .................................... 1-20

Using Assembler Support for C Structs .................................. 1-21

Preprocessing a Program ........................................................ 1-24

Using Assembler Feature Macros ........................................... 1-25

-D__VISUALDSPVERSION__ Predefined Macro ............ 1-31

Generating Make Dependencies ............................................ 1-33

Reading a Listing File ............................................................ 1-34

Enabling Statistical Profiling for Assembly Functions ............. 1-35

Assembler Syntax Reference ........................................................ 1-37

Assembler Keywords and Symbols ......................................... 1-38

Assembler Expressions ........................................................... 1-50

Assembler Operators ............................................................. 1-51

Numeric Formats .................................................................. 1-56

Representation of Constants in Blackfin ............................ 1-56

Fractional Type Support .................................................... 1-57

iv VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 5

CONTENTS

1.31 Fracts .................................................................... 1-58

1.0r Special Case ........................................................... 1-59

Fractional Arithmetic .................................................... 1-59

Mixed Type Arithmetic ................................................. 1-59

Comment Conventions ......................................................... 1-60

Conditional Assembly Directives ............................................ 1-60

C Struct Support in Assembly Built-In Functions ................... 1-63

OFFSETOF Built-In Function .......................................... 1-63

SIZEOF Built-In Function ................................................ 1-63

Struct References ................................................................... 1-64

Assembler Directives .............................................................. 1-67

.ALIGN, Specify an Address Alignment ............................. 1-72

.ALIGN_CODE, Specify an Address Alignment ................ 1-74

.ASCII .............................................................................. 1-76

.BYTE, Declare a Byte Data Variable or Buffer .................. 1-77

ASCII String Initialization Support ............................... 1-79

.COMPRESS, Start Compression ...................................... 1-81

.EXTERN, Refer to a Globally Available Symbol ............... 1-82

.EXTERN STRUCT, Refer to a Struct Defined Elsewhere . 1-83

.FILE, Override the Name of a Source File ........................ 1-85

.FILE_ATTR, Create an Attribute in the Object File ......... 1-86

.FORCECOMPRESS, Compress the Next Instruction ....... 1-87

.GLOBAL, Make a Symbol Available Globally ................... 1-88

.IMPORT, Provide Structure Layout Information .............. 1-90

VisualDSP++ 5.0 Assembler and Preprocessor Manual v

Page 6

CONTENTS

.INC/BINARY, Include Contents of a File ........................ 1-92

.LEFTMARGIN, Set the Margin Width of a Listing File ... 1-93

.LIST/.NOLIST, Listing Source Lines and Opcodes .......... 1-94

.LIST_DATA/.NOLIST_DATA, Listing Data Opcodes ..... 1-95

.LIST_DATFILE/.NOLIST_DATFILE, Listing Data

Initialization Files ........................................................ 1-96

.LIST_DEFTAB, Set the Default Tab Width for Listings ... 1-97

.LIST_LOCTAB, Set the Local Tab Width for Listings ...... 1-99

.LIST_WRAPDATA/.NOLIST_WRAPDATA ................ 1-100

.LONG, Defines and initializes 4-byte data objects .......... 1-101

.MESSAGE, Alter the Severity of an Assembler Message .. 1-102

.NEWPAGE, Insert a Page Break in a Listing File ............ 1-106

.NOCOMPRESS, Terminate Compression ..................... 1-107

.PAGELENGTH, Set the Page Length of a Listing File .... 1-108

.PAGEWIDTH, Set the Page Width of a Listing File ....... 1-109

.PORT, Legacy Directive ................................................. 1-111

.PRECISION, Select Floating-Point Precision ................. 1-112

.PREVIOUS, Revert to the Previously Defined Section ... 1-114

.PRIORITY, Allow Prioritized Symbol Mapping in Linker 1-115

Linker Operation ........................................................ 1-116

.REFERENCE, Provide Better Info in an X-REF File ...... 1-118

.RETAIN_NAME, Stop Linker from Eliminating Symbol 1-118

.ROUND_, Select Floating-Point Rounding .................... 1-119

.SECTION, Declare a Memory Section .......................... 1-122

Common .SECTION Attributes ................................. 1-122

vi VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 7

CONTENTS

DOUBLE* Qualifiers .................................................. 1-123

TigerSHARC-Specific Qualifiers .................................. 1-124

SHARC-Specific Qualifiers .......................................... 1-125

Initialization Section Qualifiers ................................... 1-126

.SEGMENT and .ENDSEG, Legacy Directives ............... 1-128

.SEPARATE_MEM_SEGMENTS ................................... 1-128

.SET, Set a Symbolic Alias ............................................... 1-129

.SHORT, Defines and initializes 2-byte data objects ......... 1-129

.STRUCT, Create a Struct Variable ................................. 1-130

.TYPE, Change Default Symbol Type .............................. 1-134

.VAR, Declare a Data Variable or Buffer .......................... 1-135

.VAR and ASCII String Initialization Support .............. 1-138

.WEAK, Support Weak Symbol Definition and Reference 1-140

Assembler Command-Line Reference ......................................... 1-141

Running the Assembler ........................................................ 1-142

Assembler Command-Line Switch Descriptions .................... 1-144

-align-branch-lines .......................................................... 1-149

-anomaly-detect [id1[,id2...]] .......................................... 1-149

-anomaly-warn {id1[,id2]|all|none} .................................. 1-149

-anomaly-workaround [id] .............................................. 1-150

-char-size-8 ..................................................................... 1-151

-char-size-32 ................................................................... 1-151

-char-size-any .................................................................. 1-151

-default-branch-np .......................................................... 1-151

VisualDSP++ 5.0 Assembler and Preprocessor Manual vii

Page 8

CONTENTS

-default-branch-p ........................................................... 1-152

-Dmacro[=definition] ..................................................... 1-152

-double-size-32 ............................................................... 1-152

-double-size-64 ............................................................... 1-153

-double-size-any ............................................................. 1-153

-expand-symbolic-links ................................................... 1-153

-expand-windows-shortcuts ............................................. 1-154

-file-attr attr[=val] .......................................................... 1-154

-flags-compiler ................................................................ 1-154

-flags-pp -opt1 [,-opt2...] ............................................... 1-156

User-Specified Defines Options ................................... 1-155

Include Options ......................................................... 1-155

-g ................................................................................... 1-156

WARNING ea1121: Missing End Labels ..................... 1-157

-h[elp] ............................................................................ 1-158

-i .................................................................................... 1-158

-l filename ...................................................................... 1-159

-li filename ..................................................................... 1-159

-M ................................................................................. 1-160

-MM .............................................................................. 1-160

-Mo filename .................................................................. 1-161

-Mt filename .................................................................. 1-161

-micaswarn ..................................................................... 1-161

-no-source-dependency ................................................... 1-161

viii VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 9

CONTENTS

-no-anomaly-detect [id1[,id2...]] ..................................... 1-162

-no-anomaly-workaround [id1[,id2...]] ............................ 1-162

-no-expand-symbolic-links .............................................. 1-162

-no-expand-windows-shortcuts ........................................ 1-163

-no-temp-data-file ........................................................... 1-163

-normal-word-code or -nwc ............................................. 1-163

-o filename ..................................................................... 1-164

-pp ................................................................................. 1-164

-proc processor ................................................................ 1-164

-save-temps ..................................................................... 1-165

-short-word-code or -swc ................................................. 1-165

-si-revision version .......................................................... 1-165

-sp .................................................................................. 1-166

-stallcheck ....................................................................... 1-166

-swc-exclude name1[,name2] ........................................... 1-167

-v[erbose] ....................................................................... 1-167

-version .......................................................................... 1-167

-w ................................................................................... 1-167

-Werror number[,number] .............................................. 1-168

-Winfo number[,number] ............................................... 1-168

-Wno-info ...................................................................... 1-168

-Wnumber[,number] ....................................................... 1-168

-Wsuppress number[,number] ......................................... 1-169

-Wwarn number[,number] .............................................. 1-169

VisualDSP++ 5.0 Assembler and Preprocessor Manual ix

Page 10

CONTENTS

-Wwarn-error ................................................................. 1-169

Specifying Assembler Options in VisualDSP++ .................... 1-170

PREPROCESSOR

Preprocessor Guide ....................................................................... 2-2

Writing Preprocessor Commands ............................................. 2-3

Header Files and #include Command ...................................... 2-4

System Header Files ............................................................ 2-5

User Header Files ............................................................... 2-5

Sequence of Tokens ............................................................ 2-6

Include Path Search ............................................................ 2-7

Writing Macros ....................................................................... 2-7

Macro Definition and Usage Guidelines .............................. 2-9

Examples of Multi-Line Code Macros with Arguments ...... 2-12

Debugging Macros ........................................................... 2-13

Using Predefined Preprocessor Macros ................................... 2-15

-D__VISUALDSPVERSION____ Predefined Macro (Preprocessor)

2-21

Specifying Preprocessor Options ............................................ 2-21

Preprocessor Command Reference ............................................... 2-22

Preprocessor Commands and Operators ................................. 2-22

#define ............................................................................. 2-24

Variable-Length Argument Definitions .......................... 2-25

#elif ................................................................................. 2-27

#else ................................................................................. 2-28

x VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 11

CONTENTS

#endif ............................................................................... 2-29

#error ............................................................................... 2-30

#if .................................................................................... 2-31

#ifdef ................................................................................ 2-32

#ifndef .............................................................................. 2-33

#include ........................................................................... 2-34

#line ................................................................................. 2-36

#pragma ........................................................................... 2-37

#undef .............................................................................. 2-38

#warning .......................................................................... 2-39

# (Argument) .................................................................... 2-40

## (Concatenate) .............................................................. 2-42

? (Generate a unique label) ................................................ 2-43

Preprocessor Command-Line Reference ....................................... 2-45

Running the Preprocessor ...................................................... 2-45

Preprocessor Command-Line Switches ................................... 2-46

-cpredef ............................................................................ 2-48

-cs! ................................................................................... 2-49

-cs/* .................................................................................. 2-49

-cs// .................................................................................. 2-50

-cs{ ................................................................................... 2-50

-csall ................................................................................. 2-50

-Dmacro[=def] ................................................................. 2-50

-h[elp] .............................................................................. 2-50

VisualDSP++ 5.0 Assembler and Preprocessor Manual xi

Page 12

CONTENTS

-i ...................................................................................... 2-51

-i ...................................................................................... 2-51

-I- .................................................................................... 2-52

-M ................................................................................... 2-53

-MM ................................................................................ 2-53

-Mo filename .................................................................... 2-53

-Mt filename .................................................................... 2-54

-o filename ....................................................................... 2-54

-stringize .......................................................................... 2-54

-tokenize-dot .................................................................... 2-54

-Uname ............................................................................ 2-55

-v[erbose] ......................................................................... 2-55

-version ............................................................................ 2-55

-w .................................................................................... 2-55

-Wnumber ....................................................................... 2-56

-warn ............................................................................... 2-56

INDEX

xii VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 13

PREFACE

Thank you for purchasing Analog Devices, Inc. development software for

digital signal processing (DSP) applications.

Purpose

The VisualDSP++ 5.0 Assembler and Preprocessor Manual contains infor-

mation about the assembler and preprocessor utilities for the following

Analog Devices, Inc. processor families—Blackfin® (ADSP-BFxxx),

SHARC® (ADSP-21xxx), and TigerSHARC® (ADSP-TSxxx) processors.

The manual describes how to write assembly programs for these processors

and provides reference information about related development software.

It also provides information on new and legacy syntax for assembler and

preprocessor directives and comments, as well as command-line switches.

Intended Audience

The primary audience for this manual is a programmer who is familiar

with Analog Devices processors. This manual assumes that the audience

has a working knowledge of the appropriate processor architecture and

instruction set. Programmers who are unfamiliar with Analog Devices

processors can use this manual, but should supplement it with other texts

(such as the appropriate hardware reference and programming reference

manuals) that describe your target architecture.

VisualDSP++ 5.0 Assembler and Preprocessor Manual xiii

Page 14

Manual Contents

Manual Contents

The manual consists of:

• Chapter 1, “Assembler”

Provides an overview of the process of writing and building

assembly programs. It also provides information about assembler

switches, expressions, keywords, and directives.

• Chapter 2, “Preprocessor”

Provides procedures for using preprocessor commands within

assembly source files as well as the preprocessor’s command-line

interface options and command sets.

What’s New in this Manual

This revision of the VisualDSP++ 5.0 Assembler and Preprocessor Manual

documents assembler and preprocessor functionality that is new to VisualDSP++® 5.0 and updates (up to update 6), including support for new

ADSP-2146x SHARC processors.

In addition, modifications and corrections based on errata reports against

the previous revision of the manual have been made.

xiv VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 15

Technical or Customer Support

You can reach Analog Devices, Inc. Customer Support in the following

ways:

• Visit the Embedded Processing and DSP products Web site at

http://www.analog.com/processors/technical_support

• E-mail tools questions to

processor.tools.support@analog.com

• E-mail processor questions to

processor.support@analog.com (World wide support)

processor.europe@analog.com (Europe support)

processor.china@analog.com (China support)

• Phone questions to 1-800-ANALOGD

Preface

• Contact your Analog Devices, Inc. local sales office or authorized

distributor

• Send questions by mail to:

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

USA

VisualDSP++ 5.0 Assembler and Preprocessor Manual xv

Page 16

Supported Processors

Supported Processors

The assembler and preprocessor of VisualDSP++ 5.0 supports the following Analog Devices, Inc. processors.

• Blackfin (ADSP-BFxxx)

• SHARC (ADSP-21xxx)

• TigerSHARC (ADSP-TSxxx)

The majority of the information in this manual applies to all processors.

For a complete list of processors supported by VisualDSP++ 5.0, refer to

the online Help.

Product Information

Product information can be obtained from the Analog Devices Web site,

VisualDSP++ online Help system, and a technical library CD.

Analog Devices Web Site

The Analog Devices Web site, www.analog.com, provides information

about a broad range of products—analog integrated circuits, amplifiers,

converters, and digital signal processors.

To access a complete technical library for each processor family, go to

http://www.analog.com/processors/technical_library. The manuals

selection opens a list of current manuals related to the product as well as a

link to the previous revisions of the manuals. When locating your manual

title, note a possible errata check mark next to the title that leads to the

current correction report against the manual.

xvi VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 17

Preface

Also note,

MyAnalog.com is a free feature of the Analog Devices Web site

that allows customization of a Web page to display only the latest information about products you are interested in. You can choose to receive

weekly e-mail notifications containing updates to the Web pages that meet

your interests, including documentation errata against all manuals. MyAn-

alog.com

provides access to books, application notes, data sheets, code

examples, and more.

Visit MyAnalog.com to sign up. If you are a registered user, just log on.

Your user name is your e-mail address.

VisualDSP++ Online Documentation

Online documentation comprises the VisualDSP++ Help system, software

tools manuals, hardware tools manuals, processor manuals, Dinkum

Abridged C++ library, and FLEXnet License Tools documentation. You

can search easily across the entire VisualDSP++ documentation set for any

topic of interest.

For easy printing, supplementary Portable Documentation Format (.pdf)

files for all manuals are provided on the VisualDSP++ installation CD.

Each documentation file type is described as follows.

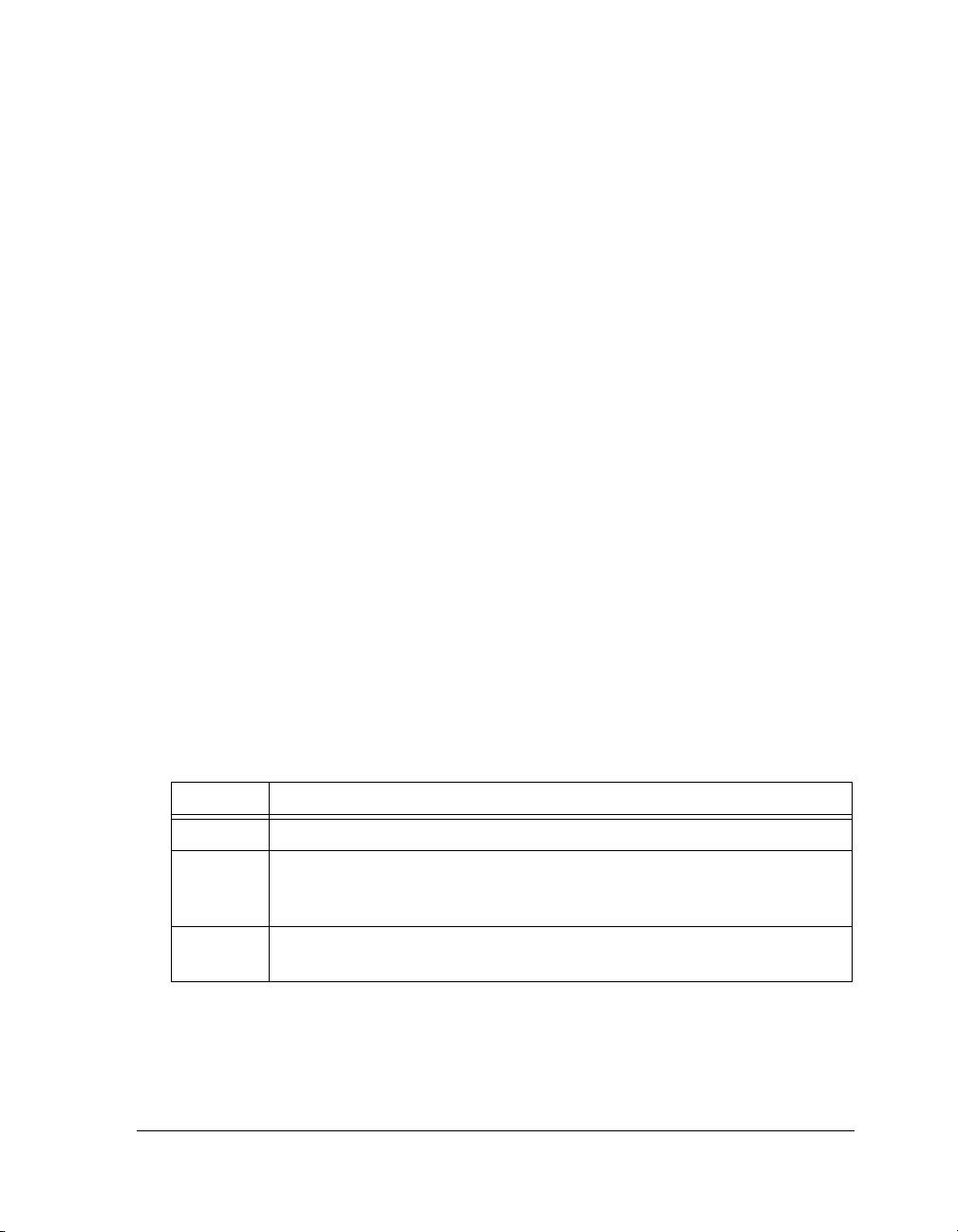

File Description

.chm Help system files and manuals in Microsoft help format

.htm or

.html

.pdf VisualDSP++ and processor manuals in PDF format. Viewing and printing the

Dinkum Abridged C++ library and FLEXnet license tools software

documentation. Viewing and printing the .html files requires a browser, such as

Internet Explorer 6.0 (or higher).

.pdf files requires a PDF reader, such as Adobe Acrobat Reader (4.0 or higher).

VisualDSP++ 5.0 Assembler and Preprocessor Manual xvii

Page 18

Notation Conventions

Technical Library CD

The technical library CD contains seminar materials, product highlights,

a selection guide, and documentation files of processor manuals, VisualDSP++ software manuals, and hardware tools manuals for the following

processor families: Blackfin, SHARC, TigerSHARC, ADSP-218x, and

ADSP-219x.

To order the technical library CD, go to http://www.analog.com/proces-

sors/technical_library

processor, click the request CD check mark, and fill out the order form.

Data sheets, which can be downloaded from the Analog Devices Web site,

change rapidly, and therefore are not included on the technical library

CD. Technical manuals change periodically. Check the Web site for the

latest manual revisions and associated documentation errata.

, navigate to the manuals page for your

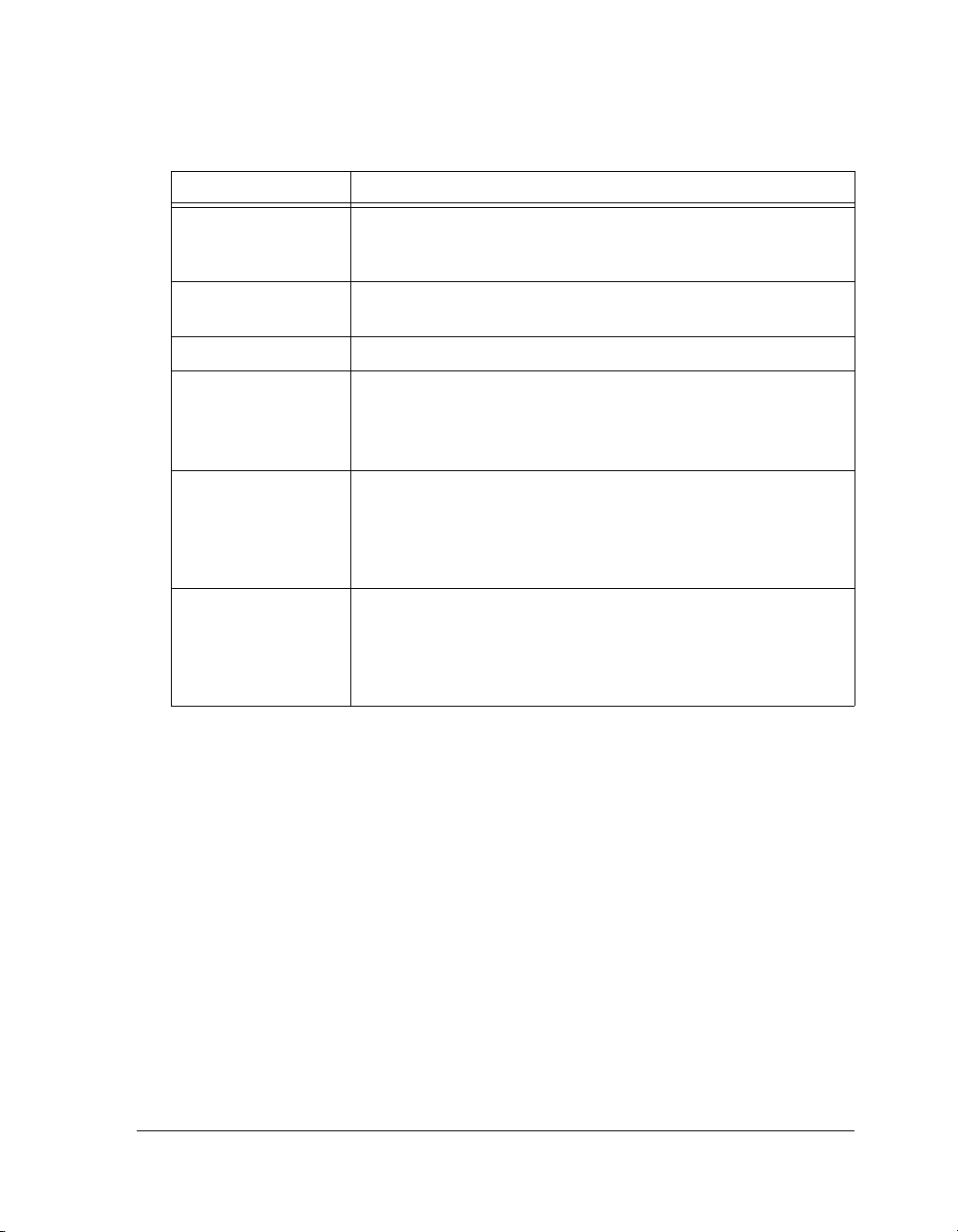

Notation Conventions

Text conventions used in this manual are identified and described as

follows.

L

Example Description

Close command

(File menu)

{this | that} Alternative required items in syntax descriptions appear within curly

[this | that] Optional items in syntax descriptions appear within brackets and sepa-

xviii VisualDSP++ 5.0 Assembler and Preprocessor Manual

Additional conventions, which apply only to specific chapters, may

appear throughout this document.

Titles in in bold style reference sections indicate the location of an item

within the VisualDSP++ environment’s menu system (for example, the

Close command appears on the File menu).

brackets and separated by vertical bars; read the example as

that. One or the other is required.

rated by vertical bars; read the example as an optional

this or

this or that.

Page 19

Preface

L

a

[

Example Description

[this,…] Optional item lists in syntax descriptions appear within brackets

delimited by commas and terminated with an ellipse; read the example

as an optional comma-separated list of

.SECTION Commands, directives, keywords, and feature names are in text with

letter gothic font.

filename Non-keyword placeholders appear in text with italic style format.

Note: For correct operation, ...

A Note provides supplementary information on a related topic. In the

online version of this book, the word Note appears instead of this

symbol.

Caution: Incorrect device operation may result if ...

Caution: Device damage may result if ...

A Caution identifies conditions or inappropriate usage of the product

that could lead to undesirable results or product damage. In the online

version of this book, the word Caution appears instead of this symbol.

Warn in g: Injury to device users may result if ...

A Warning identifies conditions or inappropriate usage of the product

that could lead to conditions that are potentially hazardous for devices

users. In the online version of this book, the word Wa rning appears

instead of this symbol.

this.

VisualDSP++ 5.0 Assembler and Preprocessor Manual xix

Page 20

Notation Conventions

xx VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 21

1 ASSEMBLER

This chapter provides information on how to use the assembler to develop

and assemble programs for SHARC (ADSP-21xxx), TigerSHARC

(ADSP-TSxxx), and Blackfin (ADSP-BFxxx) processors.

The chapter contains the following sections:

• “Assembler Guide” on page 1-2

Describes how to develop new programs using the processor’s

assembly language

• “Assembler Syntax Reference” on page 1-37

Provides the assembler rules and conventions of syntax used to

define symbols (identifiers), expressions, and to describe different

numeric and comment formats

• “Assembler Command-Line Reference” on page 1-141

Provides reference information on the assembler’s switches and

conventions

L

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-1

The code examples in this manual have been compiled using

VisualDSP++ 5.0 The examples compiled with other versions of

VisualDSP++ may result in build errors or different output

although the highlighted algorithms stand and should continue to

stand in future releases of VisualDSP++.

Page 22

Assembler Guide

Assembler Guide

In VisualDSP++ 5.0, you can run the assembler drivers for each processor

family from the VisualDSP++ integrated debugging and development

environment (IDDE) or from an operating system command line The

assembler processes assembly source, data, and header files to produce an

object file. Assembler operations depend on two types of controls:

assembler directives and assembler switches.

VisualDSP++ 5.0 supports the following assembler drivers.

• easm21k.exe (for SHARC processors)

• easmts.exe (for TigerSHARC processors)

• easmblkfn.exe (for Blackfin processors)

This section describes how to develop new programs in the Analog

Devices processor assembly language. It provides information on how to

assemble your programs from the operating system’s command line.

Software developers using the assembler should be familiar with these

topics:

• “Writing Assembly Programs” on page 1-4

• “Using Assembler Support for C Structs” on page 1-21

• “Preprocessing a Program” on page 1-24

• “Using Assembler Feature Macros” on page 1-25

• “Generating Make Dependencies” on page 1-33

• “Reading a Listing File” on page 1-34

1-2 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 23

Assembler

• “Enabling Statistical Profiling for Assembly Functions” on

page 1-35

• “Specifying Assembler Options in VisualDSP++” on page 1-170

For information about a processor’s architecture, including the instruction

set used when writing assembly programs, refer to the Hardware Reference

and the Programming Reference for the appropriate processor.

Assembler Overview

The assembler processes data from assembly source (.asm), data (.dat),

and header (.h) files to generate object files in executable and linkable

format (ELF), an industry-standard format for binary object files. The

object file has a .doj extension.

In addition to the object file, the assembler can produce a listing file

(.lst) that shows the correspondence between the binary code and the

source.

Assembler switches are specified from the VisualDSP++ IDDE or from the

command line used to invoke the assembler. These switches allow you to

control the assembly process of source, data, and header files. Use these

switches to enable and configure assembly features, such as search paths,

output file names, and macro preprocessing. For more information, see

“Assembler Command-Line Reference” on page 1-141.

You can also set assembler options via the Assemble page of the Project

Options dialog box in VisualDSP++. For more information, see “Specify-

ing Assembler Options in VisualDSP++” on page 1-170.

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-3

Page 24

Assembler Guide

Writing Assembly Programs

Assembler directives are coded in assembly source files. The directives

allow you to define variables, set up hardware features, and identify program sections for placement within processor memory. The assembler uses

directives for guidance as it translates a source program into object code.

Write assembly language programs using the VisualDSP++ editor or any

editor that produces text files. Do not use a word processor that embeds

special control codes in the text. Use an .asm extension to source file

names to identify them as assembly source files.

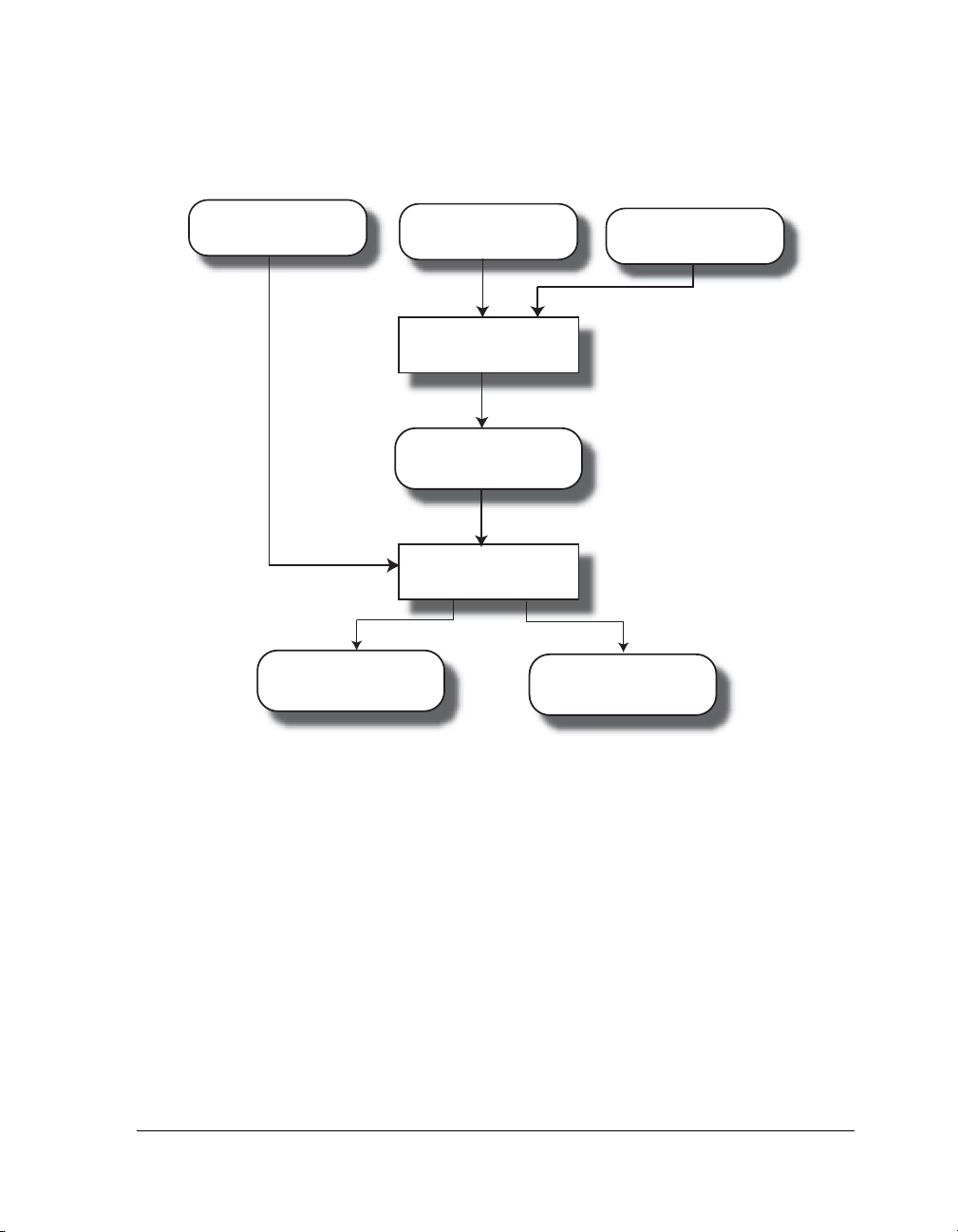

Figure 1-1 shows a graphical overview of the assembly process. The figure

shows the preprocessor processing the assembly source (.asm) and header

(.h) files.

Assemble your source files from the VisualDSP++ environment or using

any mechanism, such as a batch file or makefile, that supports invoking an

appropriate assembler driver with a specified command-line command.

By default, the assembler processes an intermediate file to produce a

binary object file (.doj) and an optional listing file (.lst).

Object files produced by the processor assembler may be used as input to

the linker and archiver. You can archive the output of an assembly process

into a library file (.dlb), which can then be linked with other objects into

an executable. Use the linker to combine separately assembled object files

and objects from library files to produce an executable file. For more

information about the linker and archiver, refer to the VisualDSP++ 5.0

Linker and Utilities Manual.

A binary object file (

.doj) and an optional listing (.lst) file are final

results of the successful assembly.

The assembler listing file is a text file read for information on the results

of the assembly process. The listing file also provides information about

the imported C data structures. The listing file tells which imports were

used within the program, followed by a more detailed section. (See the

1-4 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 25

Assembler

Assembler

Preprocessor

Intermediate

preprocessed

file (.IS)

Assembly source file

(.ASP)

Data initialization file

(.DAT)

Header file

(.H)

Listing file

(.LST)

Object file

(.OBJ)

Figure 1-1. Assembler Input and Output Files

.IMPORT directive on page 1-90.) The file shows the name, total size, and

layout with offset for the members. The information appears at the end of

the listing. You must specify the -l switch (on page 1-159) to produce a

listing file.

The assembly source file may contain preprocessor commands, such as

#include

source program. The preprocessor’s only output, an intermediate source

file (

preprocessor output is a temporary file that is deleted during the assembly

process.

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-5

, that cause the preprocessor to include header files (.h) into the

.is), is the assembler’s primary input. In normal operation, the

Page 26

Assembler Guide

Program Content

Assembly source file statements include assembly instructions, assembler

directives, and preprocessor commands.

Assembly Instructions

Instructions adhere to the processor’s instruction set syntax, which is

documented in the processor’s Programming Reference. Each instruction

line must be terminated by a semicolon (;). On TigerSHARC processors,

each instruction line (which can contain up to 4 instructions) is terminated by an additional semicolon (;;). Figure 1-2 on page 1-8 shows an

example assembly source file.

To mark the location of an instruction, place an address label at the beginning of an instruction line or on the preceding line. End the label with a

colon (:) before beginning the instruction. Your program can then refer to

this memory location using the label instead of an address. The assembler

places no restriction on the number of characters in a label.

Labels are case sensitive. The assembler treats “outer” and “Outer” as

unique labels. For example (in Blackfin processors),

outer: [I1] = R0;

Outer: R1 = 0X1234;

JUMP outer; // jumps back 2 instructions

Assembler Directives

Assembler directives begin with a period (.) and end with a semicolon (;).

The assembler does not differentiate between directives in lowercase or

uppercase.

L

1-6 VisualDSP++ 5.0 Assembler and Preprocessor Manual

This manual prints directives in uppercase to distinguish them

from other assembly statements.

Page 27

Assembler

For example (Blackfin processors):

.SECTION data1;

.BYTE2 sqrt_coeff[2] = 0x5D1D, 0xA9ED;

For a complete description of the assembler’s directive set, see “Assembler

Directives” on page 1-67.

Preprocessor Commands

Preprocessor commands begin with a pound sign (#) and end with a

carriage return. The pound sign must be the first non-white space

character on the line containing the command. If the command is longer

than one line, use a backslash (\) and a carriage return to continue the

command onto the next line.

Do not put any characters between the backslash and the carriage return.

Unlike assembler directives, preprocessor commands are case sensitive and

must be lowercase. For example,

#include "string.h"

#define MAXIMUM 100

For more information, see “Writing Preprocessor Commands” on

page 2-3. For a list of the preprocessor commands, see “Preprocessor

Command-Line Reference” on page 2-45.

Program Structure

An assembly source file defines code (instructions) and data. It also

organizes the instructions and data to allow the use of the linker description file (

.ldf) to describe how code and data are mapped into the

memory on your target processor. The way you structure your code and

data into memory should follow the memory architecture of the target

processor.

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-7

Page 28

Assembler Guide

Use the

.SECTION directive to organize the code and data in assembly

source files. The .SECTION directive defines a grouping of instructions and

data that occupies contiguous memory addresses in the processor. The

name given in a .SECTION directive corresponds to an input section name

in the linker description file.

Table 1-1, Table 1-2, and Table 1-3 show suggested input section names

for data and code that can be used in your assembly source for various

processors. Using these predefined names in your sources makes it easier

to take advantage of the default .ldf file included in your DSP system.

However, you may also define your own sections. For information on

.ldf files, refer to the VisualDSP++ 5.0 Linker and Utilities Manual.

Table 1-1. Suggested Input Section Names for a SHARC .ldf File

.SECTION Name Description

seg_pmco A section in program memory that holds code

seg_dmda A section in data memory that holds data

seg_pmda A section in program memory that holds data

seg_rth A section in program memory that holds system initialization code

and interrupt service routines

seg_swco A section in short word memory that holds instructions encoded for

execution from short word memory.

NOTE: Applies to the ADSP-2146x processors only.

Table 1-2. Suggested Input Section Names for a TigerSHARC .ldf File

.SECTION Name Description

data1 A section that holds data in memory block M1

data2 A section that holds data in memory block M2 (specified with the

PM memory qualifier)

program A section that holds code

1-8 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 29

Assembler

Table 1-3. Suggested Input Section Names for a Blackfin .ldf File

.SECTION Name Description

data1 A section that holds data

program A section that holds code

constdata A section that holds global data (which is declared as constant) and

literal constants such as strings and array initializers

Use sections in a program to group elements to meet hardware constraints.

For example, the ADSP-BF535 processor has a separate program and data

memory in Level 1 memory only. Level 2 memory and external memory

are not separated into instruction and data memory.

To group the code that resides in off-chip memory, declare a section for

that code and place that section in the selected memory with the linker.

The example assembly program defines three sections. Each section begins

with a

.SECTION directive or end-of-file.

.SECTION directive and ends with the occurrence of the next

Table 1-4 lists the sections in the source program:

Table 1-4. Sections in Source Programs

Section Blackfin SHARC TigerSHARC

Data Section

Variables and buffers are declared and can be

initialized

Program Section

Data, instructions, and possibly other types of

statements are in this section, including statements that are needed for conditional assembly

data1

constdata

seg_rth

program

seg_dmda data1

data2

seg_pmco program

Figure 1-2, Figure 1-3 on page 1-14, and Figure 1-4 on page 1-17

describe assembly code file structure for each processor family. They show

how a program divides into sections that match the memory segmentation

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-9

Page 30

Assembler Guide

of a DSP system. Notice that an assembly source may contain preprocessor commands (such as

#ifdef

SECTIONS{} commands define the .SECTION placements in the system’s

(for conditional assembly), or #define (to define macros). The

#include to include other files in source code),

physical memory as defined by the linker’s MEMORY{} command. Assembler

directives, such as .VAR (or .BYTE for Blackfin processors), appear within

sections to declare and initialize variables.

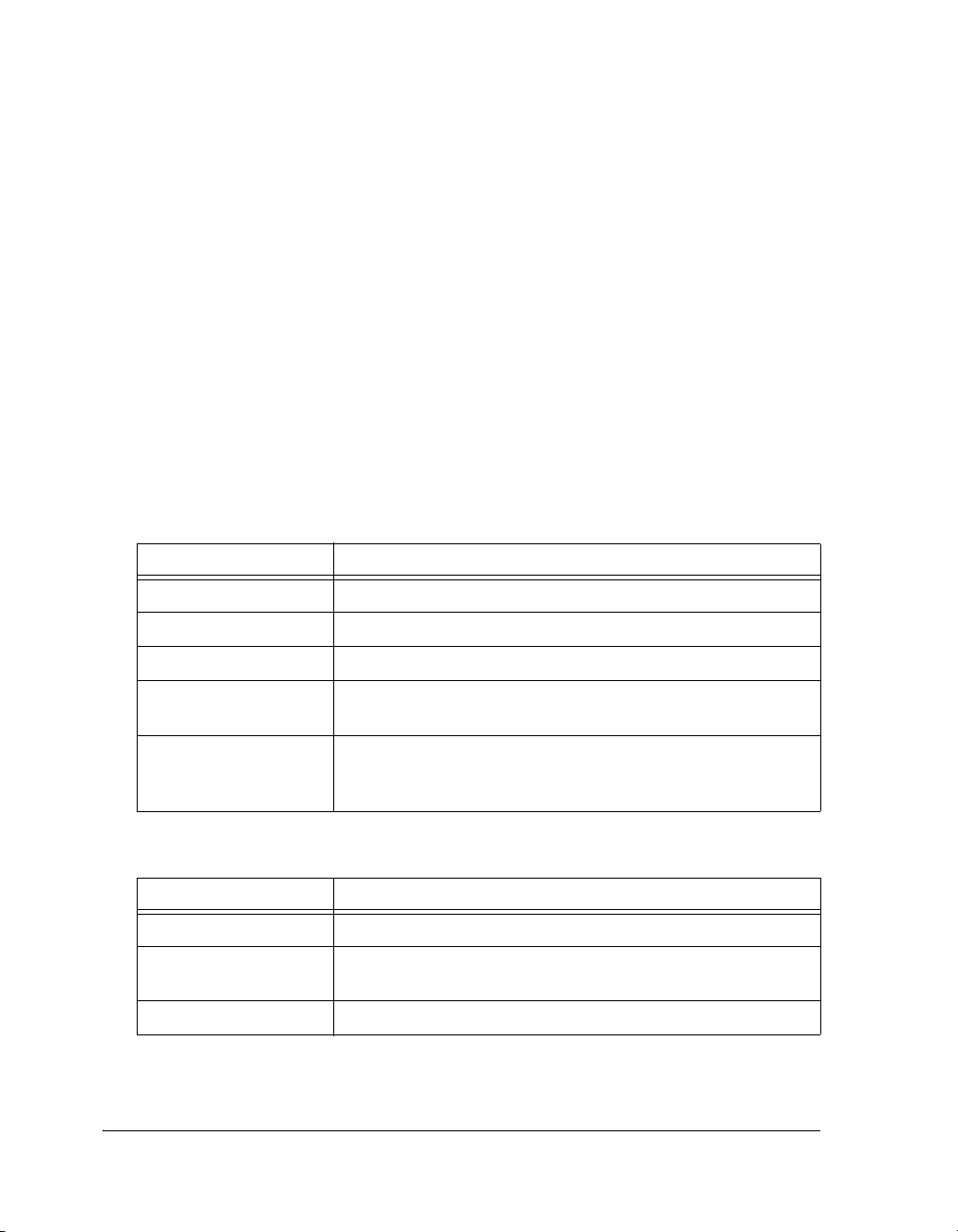

Code File Structure for SHARC Processors

Figure 1-2 describes assembly code file structure for SHARC processors.

Looking at Figure 1-2, notice that the .PRECISION and .ROUND_ZERO

directives inform the assembler to store floating-point data with 40-bit

precision and to round a floating-point value to a closer-to-zero value if it

does not fit in the 40-bit format.

LDF for SHARC Processors

Listing 1-1 shows a sample user-defined .ldf file for SHARC processors.

Looking at the file’s SECTIONS{} command, notice that the INPUT_SECTION

commands map to the names of memory sections (such as program, data1,

data2, ctor, heaptab, and so on) used in the example assembly sample

program.

Listing 1-1. LDF Example for SHARC Processors

ARCHITECTURE(ADSP-21062)

SEARCH_DIR( $ADI_DSP\21k\lib )

$LIBRARIES = lib060.dlb, libc.dlb;

$OBJECTS = $COMMAND_LINE_OBJECTS, 060_hdr.doj;

MEMORY {

seg_rth {TYPE(PM RAM) START(0x20000) END(0x20fff) WIDTH(48)}

seg_init{TYPE(PM RAM) START(0x21000) END(0x2100f) WIDTH(48)}

seg_pmco{TYPE(PM RAM) START(0x21010) END(0x24fff) WIDTH(48)}

1-10 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 31

Assembler

.PRECISION 40;

.ROUND_ZERO;

Data Section

Preprocessor Commands

for Conditional Assembly

Preprocessor Commands

.#include "const.h"

#define PI 3.14159

.SECTION/DM seg_dmda;

.VAR fxd[10] = 1,2,3,4,5,6,7,8,9,0xA;

.VAR rad;

.SECTION/PM seg_pmda;

.VAR flt[5] = PI,PI/2,1.0,2.0,2.0/3.0;

.SECTION/PM seg_pmco;

/* instructions */

function1:

I0 = fxd;

M0 = 1;

I8 = flt;

M8 = 1;

R0 = LENGTH(flt);

LCNTR = R0, DO this_loop UNTIL LCE;

R0 = DM(I0,M0), R1 = PM(I8,M8);

R2 = FIX F1 BY R0;

this_loop:

R3 = R3 + R2;

DM(rad) = R3;

Assembler Label

#ifdef duplicate_write

DM(rad) = R3;

#endif

function1.end:

Assembler Label

Assembler Directives

Code Section

Figure 1-2. Assembly Code File Structure for SHARC Processors

seg_pmda{TYPE(DM RAM) START(0x28000) END(0x28fff) WIDTH(32)}

seg_dmda{TYPE(DM RAM) START(0x29000) END(0x29fff) WIDTH(32)}

seg_stak{TYPE(DM RAM) START(0x2e000) END(0x2ffff) WIDTH(32)}

/* memory declarations for default heap */

seg_heap{TYPE(DM RAM) START(0x2a000) END(0x2bfff) WIDTH(32)}

/* memory declarations for custom heap */

seg_heaq{TYPE(DM RAM) START(0x2c000) END(0x2dfff) WIDTH(32)}

} // End MEMORY

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-11

Page 32

Assembler Guide

PROCESSOR p0 {

LINK_AGAINST( $COMMAND_LINE_LINK_AGAINST)

OUTPUT( $COMMAND_LINE_OUTPUT_FILE )

SECTIONS {

.seg_rth {

INPUT_SECTIONS( $OBJECTS(seg_rth) $LIBRARIES(seg_rth))

} > seg_rth

.seg_init {

INPUT_SECTIONS( $OBJECTS(seg_init) $LIBRARIES(seg_init))

} > seg_init

.seg_pmco {

INPUT_SECTIONS( $OBJECTS(seg_pmco) $LIBRARIES(seg_pmco))

} > seg_pmco

.seg_pmda {

INPUT_SECTIONS( $OBJECTS(seg_pmda) $LIBRARIES(seg_pmda))

} > seg_pmda

.seg_dmda {

INPUT_SECTIONS( $OBJECTS(seg_dmda) $LIBRARIES(seg_dmda))

} > seg_dmda

.stackseg {

ldf_stack_space = .;

ldf_stack_length = 0x2000;

} > seg_stak

/* section placement for default heap */

.heap {

ldf_heap_space = .;

ldf_heap_end = ldf_heap_space + 0x2000;

ldf_heap_length = ldf_heap_end - ldf_heap_space;

} > seg_heap

/* section placement for additional custom heap */

1-12 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 33

Assembler

.heaq {

ldf_heaq_space = .;

ldf_heaq_end = ldf_heaq_space + 0x2000;

ldf_heaq_length = ldf_heaq_end - ldf_heaq_space;

} > seg_heaq

} // End SECTIONS

} // End P0

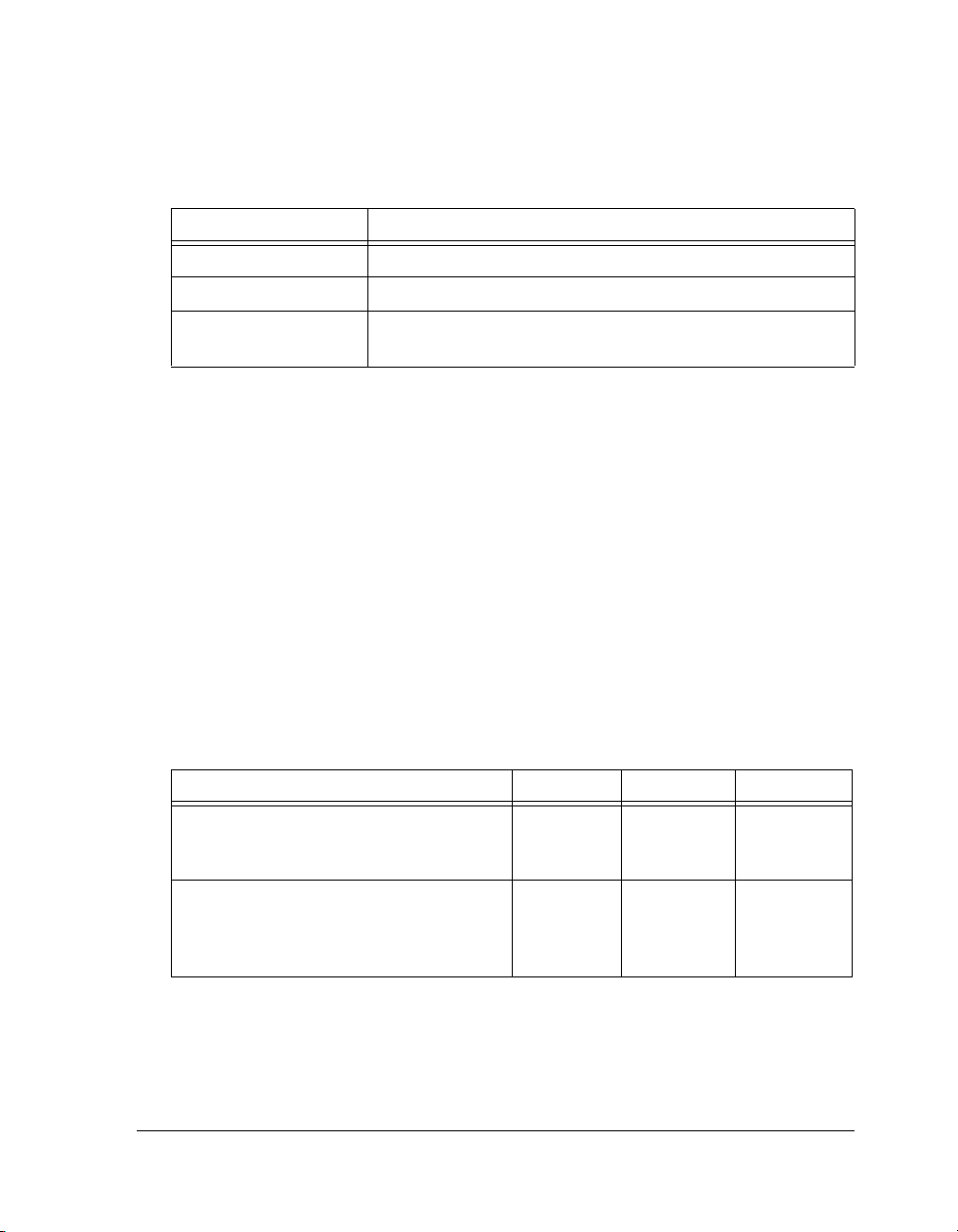

Code File Structure for TigerSHARC Processors

Figure 1-3 describes assembly code file structure for TigerSHARC

processors. Looking at Figure 1-3, notice that an assembly source may

contain preprocessor commands, such as #include (to include other files

in source code), #ifdef (for conditional assembly), or #define (to define

macros).

Assembler directives, such as .VAR, appear within sections to declare and

initialize variables.

LDF for TigerSHARC Processors

Listing 1-2 shows a sample user-defined .ldf file for TigerSHARC

processors. Looking at the file’s SECTIONS{} command, notice that the

INPUT_SECTION commands map to the names of memory sections (such as

program, data1, data2, ctor, heaptab, and so on) used in the example

assembly sample program.

Listing 1-2. Example Linker Description File for TigerSHARC Processors

ARCHITECTURE(ADSP-TS101)

SEARCH_DIR( $ADI_DSP\TS\lib )

$OBJECTS = $COMMAND_LINE_OBJECTS;

/* Internal memory blocks are 0x10000 (64k) */

MEMORY

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-13

Page 34

Assembler Guide

.SECTION data1;

.VAR buffer1 [0x100] = 'buffer .dat.';

.SECTION data2;

.VAR buffer2;

.SECTION program;

start:

#ifdef XR0_SET_TO_2

xR0=0x2;;

#else

xR0=0x1;;

#endif

J1 = buffer1;;

JL1 = 0;;

J2 = 1;;

LC0 = 0x100;;

this loop: [J+=J2] = XRO;;

IF NLCOE, JUMP this_loop;;

Data Section

Assembly Instructions

Code Section

Assembler Directive

Data Section

Assembler Label

Preprocessor Commands

for Conditional Assembly

Figure 1-3. Assembly Code File Structure for TigerSHARC Processors

{

M0Code { TYPE(RAM) START(0x00000000) END(0x0000FFFF) WIDTH(32)

}

M1Data { TYPE(RAM) START(0x00080000) END(0x0008BFFF) WIDTH(32)

}

M1Heap { TYPE(RAM) START(0x0008C000) END(0x0008C7FF) WIDTH(32)

}

M1Stack { TYPE(RAM) START(0x0008C800) END(0x0008FFFF) WIDTH(32)

}

M2Data { TYPE(RAM) START(0x00100000) END(0x0010BFFF) WIDTH(32)

}

M2Stack { TYPE(RAM) START(0x0010C000) END(0x0010FFFF) WIDTH(32)

}

SDRAM { TYPE(RAM) START(0x04000000) END(0x07FFFFFF) WIDTH(32)

}

1-14 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 35

Assembler

MS0 { TYPE(RAM) START(0x08000000) END(0x0BFFFFFF) WIDTH(32)

}

MS1 { TYPE(RAM) START(0x0C000000) END(0x0FFFFFFF) WIDTH(32)

}

}

PROCESSOR p0 /* The processor in the system *

{

OUTPUT($COMMAND_LINE_OUTPUT_FILE)

SECTIONS

{ /* List of sections for processor P0 */

code

{

FILL(0xb3c00000)

INPUT_SECTION_ALIGN(4)

INPUT_SECTIONS( $OBJECTS(program) )

} >M0Code

data1

{

INPUT_SECTIONS( $OBJECTS(data1) )

} >M1Data

data2

{

INPUT_SECTIONS( $OBJECTS(data2) )

} >M2Data

/

/* Provide support for initialization, including C++ static

initialization. This section builds a table of

initialization function pointers. */

ctor

{

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-15

Page 36

Assembler Guide

INPUT_SECTIONS( $OBJECTS(ctor0) )

INPUT_SECTIONS( $OBJECTS(ctor1) )

INPUT_SECTIONS( $OBJECTS(ctor2) )

INPUT_SECTIONS( $OBJECTS(ctor3) )

INPUT_SECTIONS( $OBJECTS(ctor) )

} >M1Data

/* Table containing heap segment descriptors */

heaptab

{

INPUT_SECTIONS( $OBJECTS(heaptab) )

} >M1Data

/* Allocate stacks for the application */

jstackseg

{

ldf_jstack_limit = .;

ldf_jstack_base = . + MEMORY_SIZEOF(M1Stack);

} >M1Stack

kstackseg

{

ldf_kstack_limit = .;

ldf_kstack_base = . + MEMORY_SIZEOF(M2Stack);

} >M2Stack

/* The default heap occupies its own memory block */

defheapseg

{

ldf_defheap_base = .;

ldf_defheap_size = MEMORY_SIZEOF(M1Heap);

} >M1Heap

}

}

1-16 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 37

Assembler

.SECTION constdata;

.VAR buffer1 [ 6 ] = "buffer1.dat";

.SECTION data1;

.VAR buffer2[ 0x100];

#ifdef INCLUDE_BUFFER3

.VAR buffer3[ 0x100];

#endif

.SECTION program;

.global my_function;

P0 = R0;

I0 = R1;

P1 = 19;

R0 = 0;

R1 = [P0++];

R2 = [I0++];

LSETUP (begin_loop, end_loop) LC0 = P1;

begin_loop:

R1 *= R2;

R2 = [I0++];

end_loop:

R0= R0 + R1 (NS) || R1 = [P0++] || NOP;

R1 *= R2;

R0 = R0 + R1;

Data Section

Assembly Instructions

Code (program) Section

Assembler Directive

Data Section

Assembler Label

Preprocessor Commands

for Conditional Assembly

Assembler Directive

my_function.end:

Assembler Label

my_function:

Code File Structure for Blackfin Pro cessors

Figure 1-4 describes the Blackfin processor’s assembly code file structure

and shows how a program divides into sections that match the memory

segmentation of Blackfin processors.

Figure 1-4. Assembly Source File Structure for Blackfin Processors

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-17

Page 38

Assembler Guide

You can use sections in a program to group elements to meet hardware

constraints. For example, the ADSP-BF535 processor has a separate program and data memory in Level 1 memory only. Level 2 memory and

external memory are not separated into instruction and data memory.

LDF for Blackfin Processors

Listing 1-3 on page 1-18 shows a sample user-defined linker description

file (.ldf). Looking at the file’s SECTIONS{} command, notice that the

INPUT_SECTION commands map to sections program, data1, and

constdata.

Listing 1-3. Example Linker Description File for Blackfin Processors

ARCHITECTURE(ADSP-BF535)

SEARCH_DIR($ADI_DSP\Blackfin\lib)

#define LIBS libc.dlb, libdsp.dlb

$LIBRARIES = LIBS, librt535.dlb;

$OBJECTS = $COMMAND_LINE_OBJECTS;

MEMORY /* Define/label system memory */

{ /* List of global Memory Segments */

MEM_PROGRAM { TYPE(RAM) START(0xF0000000) END(0xF002FFFF)

WIDTH(8) }

MEM_HEAP { TYPE(RAM) START(0xF0030000) END(0xF0037FFF)

WIDTH(8) }

MEM_STACK { TYPE(RAM) START(0xF0038000) END(0xF003DFFF)

WIDTH(8) }

MEM_SYSSTACK { TYPE(RAM) START(0xF003E000) END(0xF003FDFF)

WIDTH(8) }

MEM_ARGV { TYPE(RAM) START(0xF003FE00) END(0xF003FFFF)

WIDTH(8) }

}

PROCESSOR p0 /* The processor in the system */

1-18 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 39

Assembler

{

OUTPUT($COMMAND_LINE_OUTPUT_FILE)

SECTIONS

{ /* List of sections for processor P0 */

program

{ /* Align all code sections on 2 byte boundary */

INPUT_SECTION_ALIGN(2)

INPUT_SECTIONS( $OBJECTS(program) $LIBRARIES(program))

INPUT_SECTION_ALIGN(1)

INPUT_SECTIONS( $OBJECTS(data1) $LIBRARIES(data1))

INPUT_SECTION_ALIGN(1)

INPUT_SECTIONS(

$OBJECTS(constdata)$LIBRARIES(constdata))

INPUT_SECTION_ALIGN(1)

INPUT_SECTIONS( $OBJECTS(ctor) $LIBRARIES(ctor))

INPUT_SECTION_ALIGN(2)

INPUT_SECTIONS( $OBJECTS(seg_rth))

} >MEM_PROGRAM

stack

{

ldf_stack_space = .;

ldf_stack_end = ldf_stack_space +

MEMORY_SIZEOF(MEM_STACK) - 4;

} >MEM_STACK

sysstack

{

ldf_sysstack_space = .;

ldf_sysstack_end = ldf_sysstack_space +

MEMORY_SIZEOF(MEM_SYSSTACK) - 4;

} >MEM_SYSSTACK

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-19

Page 40

Assembler Guide

heap

{ /* Allocate a heap for the application */

ldf_heap_space = .;

ldf

_

heap_end = ldf_heap_space + MEMORY_SIZEOF(MEM_HEAP) - 1;

ldf_heap_length = ldf_heap_end - ldf_heap_space;

} >MEM_HEAP

argv

{ /* Allocate argv space for the application */

ldf_argv_space = .;

ldf

_

argv_end = ldf_argv_space + MEMORY_SIZEOF(MEM_ARGV) - 1;

ldf_argv_length = ldf_argv_end - ldf_argv_space;

} >MEM_ARGV

}

}

Program Interfacing Requirements

You can interface your assembly program with a C or C++ program.

The C/C++ compiler supports two methods for mixing C/C++ and

assembly language:

• Embedding assembly code in C or C++ programs

• Linking together C or C++ and assembly routines

To embed (inline) assembly code in your C or C++ program, use the

asm() construct. To link together programs that contain C/C++ and

assembly routines, use assembly interface macros. These macros facilitate

the assembly of mixed routines. For more information about these

methods, see the VisualDSP++ 5.0 C/C++ Compiler and Library Manual

for the appropriate target processor.

1-20 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 41

Assembler

When writing a C or C++ program that interfaces with assembly, observe

the same rules that the compiler follows as it produces code to run on the

processor. These rules for compiled code define the compiler’s run-time

environment. Complying with a run-time environment means following

rules for memory usage, register usage, and variable names.

The definition of the run-time environment for the C/C++ compiler is

provided in the VisualDSP++ 5.0 C/C++ Compiler and Library Manual for

the appropriate target processor, which also includes a series of examples

to demonstrate how to mix C/C++ and assembly code.

Using Assembler Support for C Structs

The assembler supports C typedef/struct declarations within assembly

source. These assembler data directives and built-ins provide high-level

programming features with C structs in the assembler.

Data Directives:

.IMPORT (see on page 1-90)

.EXTERN STRUCT (see on page 1-83)

.STRUCT (see on page 1-130)

C Struct in Assembly Built-Ins:

OFFSETOF(struct/typedef,field (see on page 1-63)

SIZEOF(struct/typedef) (see on page 1-63)

Struct References:

struct->field (support nests; see “Struct References” on page 1-64)

For more information on C struct support, refer to the “-flags-compiler”

command-line switch on page 1-154 and to “Reading a Listing File” on

page 1-34.

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-21

Page 42

Assembler Guide

C structs in assembly features accept the full set of legal C symbol names,

including those that are otherwise reserved in the appropriate assembler.

For example,

• In the SHARC assembler,

I1, I2, and I3 are reserved keywords,

but it is legal to reference them in the context of the C struct in

assembly features.

• In the TigerSHARC assembler, J1, J2, and J3 are reserved

keywords, but it is legal to reference them in the context of the C

struct in assembly features.

• In the Blackfin assembler, as an example, “X” and “Z” are reserved

keywords, but it is legal to reference them in the context of the C

struct in assembly features.

The examples below show how to access the parts of the struct defined in

the header file, but they are not complete programs on their own. Refer to

your DSP project files for complete code examples.

Blackfin Example:

.IMPORT "Coordinate.h";

/* typedef struct Coordinate {

int X;

int Y;

int Z;

} Coordinate;*/

.SECTION data1;

.STRUCT Coordinate Coord1 = {

X = 1,

Y = 4,

Z = 7

};

1-22 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 43

.SECTION program;

P0.l = Coord1->X;

P0.h = Coord1->X;

P1.l = Coord1->Y;

P1.h = Coord1->Y;

P2.l = Coord1->Z;

P2.h = Coord1->Z;

P3.l = Coord1+OFFSETOF(Coordinate,Z);

P3.h = Coord1+OFFSETOF(Coordinate,Z);

SHARC Example:

.IMPORT "Samples.h";

/* typedef struct Samples {

int I1;

int I2;

int I3;

} Samples; */

Assembler

.SECTION/DM seg_dmda;

.STRUCT Samples Sample1 ={

I1 = 0x1000,

I2 = 0x2000,

I3 = 0x3000

};

.SECTION/PM seg_pmco;

doubleMe:

/* The code may look confusing, but I2 can be used both

as a register and a struct member name */

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-23

Page 44

Assembler Guide

B2 = Sample1;

M2 = OFFSETOF(Sample1,I2);

R0 = DM(M2,I2);

R0 = R0+R0;

DM(M2,I2) = R0;

L

that have the same spelling as assembler keywords. This may not

always be possible if your application needs to use an existing set of

C header files.

Preprocessing a Program

The assembler includes a preprocessor that allows the use of C-style

preprocessor commands in your assembly source files. The preprocessor

automatically runs before the assembler unless you use the assembler’s -sp

(skip preprocessor) switch. Table 2-5 on page 2-23 lists preprocessor

commands and provides a brief description of each command.

You can see the command line that the assembler uses to invoke the preprocessor by adding the -v switch (on page 1-167) to the assembler

command line or by selecting the Generate verbose output option on the

Assemble page of the Project Options dialog box. See “Specifying Assem-

bler Options in VisualDSP++” on page 1-170.

Use preprocessor commands to modify assembly code. For example,

you can use the #include command to fill memory, load configuration

registers, or set up processor parameters. You can use the #define command to define constants and aliases for frequently used instruction

sequences. The preprocessor replaces each occurrence of the macro

reference with the corresponding value or series of instructions.

For better code readability, avoid using .STRUCT member names

For example, the

with the number

MAXIMUM macro from #define MAXIMUM 100 is replaced

100 during preprocessing.

1-24 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 45

Assembler

For more information on the preprocessor command set, see “Preproces-

sor Command Reference” on page 2-22. For more information on the

preprocessor usage, see “-flags-pp -opt1 [,-opt2...]” on page 1-156.

L

For example,

#define EXTERN ox123

.EXTERN Coordinate; /* EXTERN not affected by macro */

#define MY_REG P0

MY_REG.1 = 14; /* MY_REG.1 is not expanded; */

There is one important difference between the assembler preprocessor and compiler preprocessor. The assembler preprocessor

treats the “.” character as part of an identifier. Thus, .EXTERN is a

single identifier and will not match a preprocessor macro EXTERN.

This behavior can affect how macro expansion is done for some

instructions.

/* "." is part of token */

Using Assembler Feature Macros

The assembler includes the command to invoke preprocessor macros to

define the context, such as the source language, the architecture, and the

specific processor. These feature macros allow programmers to use prepro-

cessor conditional commands to configure the source for assembly based

on the context.

Table 1-5 lists the set of feature macros for Blackfin processors. Table 1-6

on page 1-28 lists the set of feature macros for SHARC processors.

Table 1-7 on page 1-30 lists the set of feature macros for TigerSHARC

processors.

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-25

Page 46

Assembler Guide

Table 1-5. Feature Macros for Blackfin Processors

-D_LANGUAGE_ASM=1 Always present

-D__ADSPBLACKFIN__ =1 Always present

-D__ADSPLPBLACKFIN__ =1 Always present for non-ADSP-BF535 processors

-D__ADSPBF51x__=1 Present when running:

easmblkfn -proc ADSP-BF512

easmblkfn -proc ADSP-BF514

easmblkfn -proc ADSP-BF516

-D__ADSPBF52x__=1 Present when running:

easmblkfn -proc ADSP-BF522

easmblkfn -proc ADSP-BF523

easmblkfn -proc ADSP-BF524

easmblkfn -proc ADSP-BF525

easmblkfn -proc ADSP-BF526

easmblkfn -proc ADSP-BF527

-D__ADSPBF54x__=1 Present when running:

easmblkfn -proc ADSP-BF542

easmblkfn -proc ADSP-BF544

easmblkfn -proc ADSP-BF547

easmblkfn -proc ADSP-BF548

easmblkfn -proc ADSP-BF549

-D__ADSPBF512__=1 Present when running easmblkfn -proc ADSP-BF512

with the ADSP-BF512 processor

-D__ADSPBF514__=1 Present when running easmblkfn -proc ADSP-BF514

with the ADSP-BF514 processor

-D__ADSPBF516__=1 Present when running easmblkfn -proc ADSP-BF516

with the ADSP-BF516 processor

-D__ADSPBF522__=1 Present when running easmblkfn -proc ADSP-BF522

with the ADSP-BF522 processor

-D__ADSPBF523__=1 Present when running easmblkfn -proc ADSP-BF523

with the ADSP-BF523 processor

-D__ADSPBF524__=1 Present when running easmblkfn -proc ADSP-BF524

with the ADSP-BF524 processor

-D__ADSPBF525__=1 Present when running easmblkfn -proc ADSP-BF525

with the ADSP-BF525 processor

1-26 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 47

Assembler

Table 1-5. Feature Macros for Blackfin Processors (Cont’d)

-D__ADSPBF526__=1 Present when running easmblkfn -proc ADSP-BF526

with the ADSP-BF526 processor

-D__ADSPBF527__=1 Present when running easmblkfn -proc ADSP-BF527

with the ADSP-BF527 processor

-D__ADSPBF531__=1

-D__ADSP21531__=1

-D__ADSPBF532__=1

-D__ADSP21532__=1

-D__ADSPBF533__=1

-D__ADSP21533__=1

-D__ADSPBF534__=1 Present when running easmblkfn -proc ADSP-BF534

Present when running easmblkfn -proc ADSP-BF531

with the ADSP-BF531 processor

Present when running easmblkfn -proc ADSP-BF532

with the ADSP-BF532 processor

Present when running easmblkfn -proc ADSP-BF533

with the ADSP-BF533 processor

with the ADSP-BF534 processor

-D__ADSPBF535__=1

-D__ADSP21535__=1

-D__ADSPBF536__=1 Present when running easmblkfn -proc ADSP-BF536

Present when running easmblkfn -proc ADSP-BF535

with the ADSP-BF535 processor

with the ADSP-BF536 processor

-D__ADSPBF537__=1 Present when running easmblkfn -proc ADSP-BF537

with the ADSP-BF537 processor

-D__ADSPBF538__=1 Present when running easmblkfn -proc ADSP-BF538

with the ADSP-BF538 processor

-D__ADSPBF539__=1 Present when running easmblkfn -proc ADSP-BF539

with the ADSP-BF539 processor

-D__ADSPBF542__=1 Present when running easmblkfn -proc ADSP-BF542

with the ADSP-BF542 processor

-D__ADSPBF544__=1 Present when running easmblkfn -proc ADSP-BF544

with the ADSP-BF544 processor

-D__ADSPBF547__=1 Present when running easmblkfn -proc ADSP-BF547

with the ADSP-BF547processor

-D__ADSPBF548__=1 Present when running easmblkfn -proc ADSP-BF548

with the ADSP-BF548 processor

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-27

Page 48

Assembler Guide

Table 1-5. Feature Macros for Blackfin Processors (Cont’d)

-D__ADSPBF549__=1 Present when running easmblkfn -proc ADSP-BF549

with the ADSP-BF549 processor

-D__ADSPBF561__=1 Present when running easmblkfn -proc ADSP-BF561

with the ADSP-BF561 processor

Table 1-6. Feature Macros for SHARC Processors

-D_LANGUAGE_ASM=1 Always present

-D__ADSP21000__=1 Always present

-D__ADSP21020__=1

-D__2102x__=1

-D__ADSP21060__=1

-D__2106x__=1

-D__ADSP21061__=1

-D__2106x__=1

-D__ADSP21062__=1

-D__2106x__=1

-D__ADSP21065L__=1

-D__2106x__=1

-D__ADSP21160__=1

-D__2116x__=1

-D__ADSP21161__=1

-D__2116x__=1

-D__ADSP21261__=1

-D__2126x__=1

-D__ADSP21262__=1

-D__2126x__=1

-D__ADSP21266__=1

-D__2126x__=1

-D__ADSP21267__=1

-D__2126x__=1

Present when running easm21K -proc ADSP-21020

with the ADSP-21020 processors

Present when running easm21K -proc ADSP-21060

with the ADSP-21060 processors

Present when running easm21K -proc ADSP-21061

with the ADSP-21061 processors

Present when running easm21K -proc ADSP-21062

with the ADSP-21062 processors

Present when running easm21K -proc ADSP-21065L

with the ADSP-21065L processors

Present when running easm21K -proc ADSP-21160

with the ADSP-21160 processors

Present when running easm21K -proc ADSP-21161

with the ADSP-21161 processors

Present when running easm21K -proc ADSP-21261

with the ADSP-21261 processors

Present when running easm21K -proc ADSP-21262

with the ADSP-21262 processors

Present when running easm21K -proc ADSP-21266

with the ADSP-21266 processors

Present when running easm21K -proc ADSP-21267

with the ADSP-21267 processors

1-28 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 49

Table 1-6. Feature Macros for SHARC Processors (Cont’d)

Assembler

-D__ADSP21362__=1

-D__2136x__=1

-D__ADSP21363__=1

-D__2136x__=1

-D__ADSP21364__=1

-D__2136x__=1

-D__ADSP21365__=1

-D__2136x__=1

-D__ADSP21366__=1

-D__2136x__=1

-D__ADSP21367__=1

-D__2136x__=1

-D__ADSP21368__=1

-D__2136x__=1

-D__ADSP21369__=1

-D__2136x__=1

-D__ADSP2137x__=1

-D__2137x__=1

-D__ADSP21371__=1

-D__2137x__=1

-D__ADSP21375__=1

-D__2137x__=1

Present when running easm21K -proc ADSP-21362

with the ADSP-21362 processors

Present when running easm21K -proc ADSP-21363

with the ADSP-21363 processors

Present when running easm21K -proc ADSP-21364

with the ADSP-21364 processors

Present when running easm21K -proc ADSP-21365

with the ADSP-21365 processors

Present when running easm21K -proc ADSP-21366

with the ADSP-21366 processors

Present when running easm21K -proc ADSP-21367

with the ADSP-21367 processors

Present when running easm21K -proc ADSP-21368

with the ADSP-21368 processors

Present when running easm21K -proc ADSP-21369

with the ADSP-21369 processors

Present when running easm21K -proc ADSP-2137x

with the ADSP-2137x processors

Present when running easm21K -proc ADSP-21371

with the ADSP-21371 processors

Present when running easm21K -proc ADSP-21375

with the ADSP-21375 processors

-D__ADSP21462__=1

-D__2146x__=1

-D__214xx__=1

-D__ADSP21465__=1

-D__2146x__=1

-D__214xx__=1

-D__ADSP21467__=1

-D__2146x__=1

-D__214xx__=1

Present when running easm21K -proc ADSP-21462

with the ADSP-21462 processors

Present when running easm21K -proc ADSP-21465

with the ADSP-21465 processors

Present when running easm21K -proc ADSP-21467

with the ADSP-21467 processors

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-29

Page 50

Assembler Guide

Table 1-6. Feature Macros for SHARC Processors (Cont’d)

-D__ADSP21469__=1

-D__2146x__=1

-D__214xx__=1

-D__NORMAL_WORD_CODE__=1 Present when running

Present when running easm21K -proc ADSP-21469

with the ADSP-21469 processors

easm21K -proc ADSP-21462

easm21K -proc ADSP-21465

easm21K -proc ADSP-21467

easm21K -proc ADSP-21469 and building in normal-word

mode

-D__SHORT_WORD_CODE__=1 Present when running

easm21K -proc ADSP-21462

easm21K -proc ADSP-21465

easm21K -proc ADSP-21467

easm21K -proc ADSP-21469 and building in short-word

mode

Table 1-7. Feature Macros for TigerSHARC Processors

-D_LANGUAGE_ASM =1 Always present

-D__ADSPTS__ =1 Always present

-D__ADSPTS101__ =1 Present when running easmts -proc ADSP-TS101

with the ADSP-TS101 processor

-D__ADSPTS201__ =1 Present when running easmts -proc ADSP-TS201

with the ADSP-TS201 processor

-D__ADSPTS202__ =1 Present when running easmts -proc ADSP-TS202

with the ADSP-TS202 processor

-D__ADSPTS203__ =1 Present when running easmts -proc ADSP-TS203

with the ADSP-TS203 processor

-D__ADSPTS20x__ =1 Present when running

easmts -proc ADSP-TS201 with the ADSP-TS201 processor

easmts -proc ADSP-TS202 with the ADSP-TS202 processor

asmts -proc ADSP-TS203 with the ADSP-TS203 processor

1-30 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 51

Assembler

For

.IMPORT headers, the assembler calls the compiler driver with the

appropriate processor option, and the compiler sets the machine constants

accordingly (and defines -D_LANGUAGE_C=1). This macro is present when

used for C compiler calls to specify headers. It replaces -D_LANGUAGE_ASM.

For example,

easm21k -proc adsp-21262 assembly --> cc21K -proc adsp-21262

easmts -proc -ADSP-TS101

easmblkfn -proc ADSP-BF535 assembly --> ccblkfn -proc ADSP-BF535

L

-D__VISUALDSPVERSION__ Predefined Macro

Use the -verbose switch to verify what macro is default-defined.

Refer to Chapter 1 in the VisualDSP++ 5.0 C/C++ Compiler and

Library Manual of the appropriate target processor for more

information.

The macro applies to all Analog Devices processors.

assembly --> ccts -proc ADSP-TS101

L

The -D__VISUALDSPVERSION__ predefined macro provides product version

information to VisualDSP++. The macro allows a preprocessing check to

be placed within code and is used to differentiate between VisualDSP++

releases and updates.

Syntax:

-D__VISUALDSPVERSION__=0xMMmmUUxx

Table 1-8 explains the macro parameters.

The

0xMMmmUUxx information is obtained from the <install_path>\Sys-

tem\VisualDSP.ini

If an unexpected problem occurs while trying to locate VisualDSP.ini or

while extracting information from the

__VISUALDSPVERSION__ macro is not encoded to the VisualDSP++ product

VisualDSP++ 5.0 Assembler and Preprocessor Manual 1-31

file. Initially, xx is set to “00”.

VisualDSP.ini file, the

Page 52

Assembler Guide

Table 1-8. -D__VISUALDSPVERSION__ Decoding of Hex Value

Parameter Description

MM VersionMajor. The major release number; for example, 4 in release 4.5.

mm VersionMinor. The minor release number; for example, 5 in release 4.5.

UU VersionPatch. The number of the release update; for example, 6 in release 4.5,

update 6.

xx Reserved for future use (always 00 initially)

version. In the Error Check example below, the

0xffffffff

string is displayed as part of an error message when the version

-D__VISUALDSPVERSION__

information is unable to be encoded.

Code Example (Legacy ):

#if !defined(__VISUALDSPVERSION__)

#warning Building with VisualDSP++ 4.5 Update 5 or prior. No

__VISUALDSPVERSION__ available.

#endif

Code Example (VisualDSP++ 4.5 Update 6 or Later):

#if __VISUALDSPVERSION__ >= 0x04050600

#warning Building with VisualDSP++ 4.5 Update 6 or later

#endif

Code Example (Error Check):

#if __VISUALDSPVERSION__ == 0xffffffff

#error Unexpected build problems, unknown VisualDSP++ Version

#endif

Code Examples (Assembly):

#if __VISUALDSPVERSION__ == 0x05000000

/* Building with VisualDSP++ 5.0 */

.VAR VersionBuildString[] = ‘Building with VisualDSP++ 5.0’;

1-32 VisualDSP++ 5.0 Assembler and Preprocessor Manual

Page 53

Assembler

#elif __VISUALDSPVERSION__ == 0x04050600

/* Building with VisualDSP++ 4.5, Update 6 */

.VAR VersionBuildString[] = 'Building with VisualDSP++ 4.5 Update

6';

#else

/* Building with unknown VisualDSP++ version */

.VAR VersionBuildString[] = 'Building with unknown VisualDSP++

version?';

#endif

Generating Make Dependencies

The assembler can generate make dependencies for a file, allowing

VisualDSP++ and other makefile-based build environments to determine

when to rebuild an object file due to changes in the input files. The assembly source file and any files identified in the #include commands, .IMPORT

directives, or buffer initializations (in .VAR and .STRUCT directives) constitute the make dependencies for an object file.

When you request make dependencies for the assembly, the assembler

produces the dependencies from buffer initializations. The assembler also

invokes the preprocessor to determine the make dependency from