Page 1

W 4.0

Loader Manual

Analog Devices, Inc.

One Technology Way

Norwood, Mass. 02062-9106

Revision 1.0, January 2005

Part Number

82-000420-05

a

a

Page 2

Copyright Information

© 2005 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written

consent from Analog Devices, Inc.

Printed in the USA.

Disclaimer

Analog Devices, Inc. reserves the right to change this product without

prior notice. Information furnished by Analog Devices is believed to be

accurate and reliable. However, no responsibility is assumed by Analog

Devices for its use; nor for any infringement of patents or other rights of

third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

Trademark and Service Mark Notice

The Analog Devices logo, VisualDSP++, the VisualDSP logo, Blackfin,

the Blackfin logo, SHARC, the SHARC logo, TigerSHARC, the TigerSHARC logo, Crosscore, the Crosscore logo, and EZ-KIT Lite are

registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of

their respective owners.

Page 3

CONTENTS

PREFACE

Purpose of This Manual ................................................................ xiii

Intended Audience ........................................................................ xiii

Manual Contents ........................................................................... xiv

What’s New in This Manual ........................................................... xiv

Technical or Customer Support ....................................................... xv

Supported Processors ...................................................................... xvi

Product Information ..................................................................... xvii

MyAnalog.com ........................................................................ xvii

Processor Product Information ................................................ xviii

Related Documents ................................................................ xviii

Online Technical Documentation ............................................. xix

Accessing Documentation From VisualDSP++ ....................... xx

Accessing Documentation From Windows ............................. xx

Accessing Documentation From the Web .............................. xxi

Printed Manuals ....................................................................... xxi

VisualDSP++ Documentation Set ......................................... xxi

Hardware Tools Manuals ..................................................... xxii

Processor Manuals ............................................................... xxii

VisualDSP++ 4.0 Loader Manual iii

Page 4

CONTENTS

Data Sheets ........................................................................ xxii

Notation Conventions ................................................................. xxiii

INTRODUCTION

Program Development Flow .......................................................... 1-2

Compiling and Assembling ..................................................... 1-2

Linking ................................................................................... 1-3

Loading, Splitting, or Both ...................................................... 1-3

Non-bootable Files Versus Boot-loadable Files ......................... 1-4

Loader Operations .............................................................. 1-5

Splitter Operations ............................................................. 1-6

Booting Modes ............................................................................. 1-6

No-Boot Mode ....................................................................... 1-7

PROM Boot Mode ................................................................. 1-7

Host Boot Mode ..................................................................... 1-8

Boot Kernels ................................................................................ 1-8

Loader Tasks ................................................................................. 1-9

Boot Streams .............................................................................. 1-10

File Searches ......................................................................... 1-11

LOADER/SPLITTER FOR BLACKFIN PROCESSORS

Blackfin Processor Booting ............................................................ 2-2

ADSP-BF535 Processor Booting .............................................. 2-2

ADSP-BF535 Processor On-Chip Boot ROM ..................... 2-3

ADSP-BF535 Processor Second-Stage Loader ...................... 2-5

iv VisualDSP++ 4.0 Loader Manual

Page 5

CONTENTS

ADSP-BF535 Processor Boot Streams .................................. 2-8

Loader Files Without a Second-Stage Loader .................... 2-9

Loader Files With a Second-Stage Loader ....................... 2-11

Global Headers ............................................................. 2-13

Blocks, Block Headers, and Flags ................................... 2-14

ADSP-BF535 Processor Memory Ranges ........................... 2-15

Second-Stage Loader Restrictions ................................... 2-16

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 Processor Booting ........................................ 2-17

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 Processor On-Chip Boot ROM ................ 2-19

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 Processor Boot Streams ............................ 2-21

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 Blocks, Block Headers, and Flags ......... 2-21

Initialization Blocks ...................................................... 2-24

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 Processor Memory Ranges ........................ 2-28

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 Processor SPI Slave Mode Boot via

Master Host (BMODE = 10) .......................................... 2-30

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 Processor SPI Master Mode Boot via

SPI Memory (BMODE = 11) ......................................... 2-32

SPI Memory Detection Routine .................................... 2-34

ADSP-BF534/BF536/BF537 Processor Booting ................. 2-35

ADSP-BF561 and ADSP-BF566 Processor Booting ................ 2-37

VisualDSP++ 4.0 Loader Manual v

Page 6

CONTENTS

ADSP-BF561 Processor Boot Streams ............................... 2-38

ADSP-BF561/BF566 Processor Memory Ranges ............... 2-43

ADSP-BF561/BF566 Processor Initialization Blocks .......... 2-44

ADSP-BF561/BF566 Multiple .DXE Booting ............... 2-45

ADSP-BF53x and ADSP-BF561/BF566 Multiple .DXE

Booting .............................................................................. 2-46

Blackfin Processor Loader Guide ................................................. 2-49

Using the ADSP-BF5xx Blackfin Loader Command Line ....... 2-49

File Searches ..................................................................... 2-50

File Extensions ................................................................. 2-51

Command-Line Switches .................................................. 2-51

Using the Base Loader ........................................................... 2-57

Using the Second-Stage Loader .............................................. 2-59

Using the ROM Splitter ........................................................ 2-62

No-Boot Mode ................................................................. 2-62

LOADER FOR ADSP-TSXXX TIGERSHARC PROCESSORS

ADSP-TSxxx TigerSHARC Processor Booting ............................... 3-2

Boot Type Selection ................................................................ 3-3

Boot Kernels ........................................................................... 3-4

Boot Kernel Modification ................................................... 3-5

TigerSHARC Loader Guide .......................................................... 3-5

Using TigerSHARC Loader Command Line ............................ 3-6

File Searches ....................................................................... 3-8

File Extensions ................................................................... 3-8

vi VisualDSP++ 4.0 Loader Manual

Page 7

CONTENTS

Command-Line Switches ..................................................... 3-8

Using VisualDSP++ Interface (Load Page) .............................. 3-12

LOADER FOR ADSP-2106X/21160 SHARC PROCESSORS

ADSP-2106x/21160 Processor Booting .......................................... 4-2

Power-Up Booting Process ....................................................... 4-3

Boot Mode Selection ............................................................... 4-5

Boot Types .............................................................................. 4-7

EPROM Booting ................................................................ 4-7

Host Booting .................................................................... 4-11

Link Booting .................................................................... 4-15

No-Boot Mode ................................................................. 4-16

Boot Kernels ......................................................................... 4-16

Blocks and Block Headers ................................................. 4-17

Boot Kernel Modification and Loader Issues ...................... 4-19

Interrupt Vector Table ........................................................... 4-22

Multiprocessor EPROM Booting ........................................... 4-23

Processor ID Numbers ........................................................... 4-24

ADSP-2106x/21160 Processor Loader Guide ............................... 4-25

Using the ADSP-2106x/21160 Loader Command Line .......... 4-26

File Searches ..................................................................... 4-27

File Extensions .................................................................. 4-27

Loader Command-Line Switches ....................................... 4-28

Using the VisualDSP++ Interface (Load Page) ........................ 4-31

VisualDSP++ 4.0 Loader Manual vii

Page 8

CONTENTS

LOADER FOR ADSP-21161 SHARC PROCESSORS

ADSP-21161 Processor Booting .................................................... 5-2

Power-Up Booting Process ....................................................... 5-3

Boot Mode Selection ............................................................... 5-3

Boot Types .............................................................................. 5-4

EPROM Booting ................................................................ 5-5

Host Booting ...................................................................... 5-9

Link Port Booting ............................................................. 5-12

SPI Port Booting .............................................................. 5-14

No-Boot Mode ................................................................. 5-16

Boot Kernels ......................................................................... 5-16

Blocks and Block Headers ................................................. 5-17

Boot Kernel Modification and Loader Issues .......................... 5-18

Rebuilding a Boot Kernel File ........................................... 5-18

Rebuilding a Boot Kernel Using Command Lines .............. 5-19

Loader File Issues .............................................................. 5-20

Interrupt Vector Table ........................................................... 5-21

Multiprocessor EPROM Booting ........................................... 5-21

Booting From a Single EPROM ........................................ 5-22

Sequential EPROM Booting ............................................. 5-22

Processor ID Numbers ...................................................... 5-23

ADSP-21161 Processor Loader Guide ......................................... 5-24

Using ADSP-21161 Loader Command Line .......................... 5-24

File Searches ..................................................................... 5-26

viii VisualDSP++ 4.0 Loader Manual

Page 9

CONTENTS

File Extensions .................................................................. 5-27

Loader Command-Line Switches ....................................... 5-27

Using VisualDSP++ Interface (Load Page) .............................. 5-27

LOADER FOR ADSP-2126X/2136X SHARC PROCESSORS

ADSP-2126x/2136x Processor Booting .......................................... 6-2

Power-Up Booting Process ....................................................... 6-3

Boot Type Selection ................................................................. 6-4

Boot Types .............................................................................. 6-4

PROM Boot Mode ............................................................. 6-5

Packing Options for External Memory ............................. 6-6

Packing and Padding Details ............................................ 6-7

SPI Port Boot Modes ........................................................... 6-8

SPI Slave Boot Mode ....................................................... 6-9

SPI Master Boot Mode .................................................. 6-10

Booting From an SPI Flash ............................................ 6-14

Booting From an SPI PROM (16-Bit Address) ............... 6-16

Booting From an SPI Host Processor ............................. 6-16

Internal Boot Mode .......................................................... 6-17

Boot Kernels ......................................................................... 6-18

Boot Kernel Modification and Loader Issues ...................... 6-19

Rebuilding a Boot Kernel File ........................................ 6-19

Rebuilding a Boot Kernel Using Command Lines .......... 6-20

Loader File Issues .......................................................... 6-20

Interrupt Vector Table ........................................................... 6-21

VisualDSP++ 4.0 Loader Manual ix

Page 10

CONTENTS

Loader File Section Header .................................................... 6-22

ADSP-2126x/2136x Data Tags ......................................... 6-22

INIT_L48 Blocks ......................................................... 6-24

INIT_L16 Blocks ......................................................... 6-26

INIT_L64 Blocks ......................................................... 6-26

FINAL_INIT Blocks .................................................... 6-27

ADSP-2126x/2136x Processor Loader Guide ............................... 6-32

Using the ADSP-2126x/2136x Loader Command Line .......... 6-32

File Searches ..................................................................... 6-34

File Extensions ................................................................. 6-34

Loader Command-Line Switches ....................................... 6-34

Using the VisualDSP++ Interface (Load Page) ........................ 6-34

SPLITTER FOR SHARC AND TIGERSHARC

PROCESSORS

SHARC and TigerSHARC Splitter Command Line ....................... 7-2

File Searches ........................................................................... 7-4

Output File Extensions ........................................................... 7-4

Command-Line Switches ......................................................... 7-5

VisualDSP++ Interface (Split Page) ............................................... 7-8

FILE FORMATS

Source Files .................................................................................. A-2

C/C++ Source Files ................................................................. A-2

Assembly Source Files .............................................................. A-3

x VisualDSP++ 4.0 Loader Manual

Page 11

CONTENTS

Assembly Initialization Data Files ........................................... A-3

Header Files ........................................................................... A-4

Linker Description Files ......................................................... A-4

Linker Command-Line Files ................................................... A-5

Build Files ................................................................................... A-5

Assembler Object Files ............................................................ A-6

Library Files ........................................................................... A-6

Linker Output Files ................................................................ A-6

Memory Map Files ................................................................. A-7

Loader Output Files in Intel Hex-32 Format ........................... A-7

HEXUTIL Utility .............................................................. A-9

Loader Output Files in Include Format ................................. A-10

Loader Output Files in Binary Format ................................... A-11

Splitter Output Files in Motorola S-Record Format ............... A-11

Splitter Output Files in Intel Hex-32 Format ........................ A-13

Splitter Output Files in Byte Stacked Format ......................... A-13

Splitter Output Files in ASCII Format .................................. A-15

Debugger Files ........................................................................... A-15

Format References ...................................................................... A-17

INDEX

VisualDSP++ 4.0 Loader Manual xi

Page 12

CONTENTS

xii VisualDSP++ 4.0 Loader Manual

Page 13

PREFACE

Thank you for purchasing VisualDSP++® 4.0, Analog Devices, Inc. development software for digital signal processing (DSP) applications.

Purpose of This Manual

The VisualDSP++ 4.0 Loader Manual contains information about the

loader/splitter program for the following Analog Devices, Inc. processors—SHARC

Blackfin

The manual describes the loader/splitter operations for these processors

and references information about related development software. It also

provides information about the loader and splitter command-line

interfaces.

®

®

(ADSP-21xxx), TigerSHARC® (ADSP-TSxxx), and

(ADSP-BFxxx).

Intended Audience

The primary audience for this manual is a programmer who is familiar

with Analog Devices processors. This manual assumes that the audience

has a working knowledge of the appropriate processor architecture and

instruction set. Programmers who are unfamiliar with Analog Devices

processors can use this manual, but should supplement it with other texts

(such as the appropriate hardware reference and programming reference

manuals) that describe your target architecture.

VisualDSP++ 4.0 Loader Manual xiii

Page 14

Manual Contents

Manual Contents

The manual contains:

• Chapter 1, “Introduction”

• Chapter 2, “Loader/Splitter for Blackfin Processors”

• Chapter 3, “Loader for ADSP-TSxxx TigerSHARC Processors”

• Chapter 4, “Loader for ADSP-2106x/21160 SHARC Processors”

• Chapter 5, “Loader for ADSP-21161 SHARC Processors”

• Chapter 6, “Loader for ADSP-2126x/2136x SHARC Processors”

• Chapter 7, “Splitter for SHARC and TigerSHARC Processors”

• Appendix A, “File Formats”

What’s New in This Manual

Information in this VisualDSP++ 4.0 Loader Manual applies to all Analog

Devices, Inc. processors listed in “Supported Processors”.

Refer to VisualDSP++ 4.0 Product Release Bulletin for information on new

and updated VisualDSP++ 4.0 features and other product release

information.

xiv VisualDSP++ 4.0 Loader Manual

Page 15

Technical or Customer Support

You can reach Analog Devices, Inc. Customer Support in the following

ways:

• Visit the Embedded Processing and DSP products Web site at

http://www.analog.com/processors/technicalSupport

• E-mail tools questions to

dsptools.support@analog.com

• E-mail processor questions to

dsp.support@analog.com

• Phone questions to 1-800-ANALOGD

• Contact your Analog Devices, Inc. local sales office or authorized

distributor

Preface

• Send questions by mail to:

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

USA

VisualDSP++ 4.0 Loader Manual xv

Page 16

Supported Processors

Supported Processors

The following is the list of Analog Devices, Inc. processors supported in

VisualDSP++ 4.0.

Blackfin (ADSP-BFxxx) Processors

The name “Blackfin” refers to a family of 16-bit, embedded processors.

VisualDSP++ currently supports the following Blackfin processors.

ADSP-BF531 ADSP-BF532 (formerly ADSP-21532)

ADSP-BF533 ADSP-BF534

ADSP-BF535 (formerly ADSP-21535) ADSP-BF536

ADSP-BF537 ADSP-BF538

ADSP-BF539 ADSP-BF561

ADSP-BF566 AD6532

SHARC (ADSP-21xxx) Processors

The name “SHARC” refers to a family of high-performance, 32-bit,

floating-point processors that can be used in speech, sound, graphics, and

imaging applications. VisualDSP++ currently supports the following

SHARC processors.

ADSP-21020 ADSP-21060 ADSP-21061 ADSP-21062

ADSP-21065L ADSP-21160 ADSP-21161 ADSP-21261

ADSP-21262 ADSP-21266 ADSP-21267 ADSP-21363

ADSP-21364 ADSP-21365 ADSP-21366 ADSP-21367

ADSP-21368 ADSP-21369

xvi VisualDSP++ 4.0 Loader Manual

Page 17

Preface

TigerSHARC (ADSP-TSxxx) Processors

The name “TigerSHARC” refers to a family of floating-point and

fixed-point [8-bit, 16-bit, and 32-bit] processors. VisualDSP++ currently

supports the following TigerSHARC processors.

ADSP-TS101 ADSP-TS201 ADSP-TS202 ADSP-TS203

Product Information

You can obtain product information from the Analog Devices Web site,

from the product CD-ROM, or from the printed publications (manuals).

Analog Devices is online at

www.analog.com. Our Web site provides infor-

mation about a broad range of products—analog integrated circuits,

amplifiers, converters, and digital signal processors.

MyAnalog.com

MyAnalog.com is a free feature of the Analog Devices Web site that allows

customization of a Web page to display only the latest information on

products you are interested in. You can also choose to receive weekly

e-mail notifications containing updates to the Web pages that meet your

interests.

sheets, code examples, and more.

Registration

Visit

Registration takes about five minutes and serves as a means to select the

information you want to receive.

If you are already a registered user, just log on. Your user name is your

e-mail address.

MyAnalog.com provides access to books, application notes, data

www.myanalog.com to sign up. Click Register to use MyAnalog.com.

VisualDSP++ 4.0 Loader Manual xvii

Page 18

Product Information

Processor Product Information

For information on embedded processors and DSPs, visit our Web site at

www.analog.com/processors, which provides access to technical publica-

tions, data sheets, application notes, product overviews, and product

announcements.

You may also obtain additional information about Analog Devices and its

products in any of the following ways.

• E-mail questions or requests for information to

dsp.support@analog.com

• Fax questions or requests for information to

1-781-461-3010 (North America)

+49-89-76903-157 (Europe)

• Access the FTP Web site at

ftp ftp.analog.com (or ftp 137.71.25.69)

ftp://ftp.analog.com

Related Documents

For information on product related development software, see these

publications:

• VisualDSP++ 4.0 User’s Guide

• VisualDSP++ 4.0 Getting Started Guide

• VisualDSP++ 4.0 C/C++ Compiler and Library Manual for SHARC

Processors

• VisualDSP++ 4.0 C/C++ Compiler and Library Manual for

TigerSHARC Processors

• VisualDSP++ 4.0 C/C++ Compiler and Library Manual for Blackfin

Processors

xviii VisualDSP++ 4.0 Loader Manual

Page 19

Preface

• VisualDSP++ 4.0 Linker and Utilities Manual

• VisualDSP++ 4.0 Assembler and Preprocessor Manual

• VisualDSP++ 4.0 Product Release Bulletin

• VisualDSP++ 4.0 Kernel (VDK) User’s Guide

• VisualDSP++ 4.0 Quick Installation Reference Card

For hardware information, refer to your processors’s hardware reference,

programming reference, or data sheet. All documentation is available

online. Most documentation is available in printed form.

Visit the Technical Library Web site to access all processor and tools manuals and data sheets:

http://www.analog.com/processors/resources/technicalLibrary

Online Technical Documentation

Online documentation comprises the VisualDSP++ Help system, software

tools manuals, hardware tools manuals, processor manuals, the Dinkum

Abridged C++ library, and Flexible License Manager (FlexLM) network

license manager software documentation. You can easily search across the

entire VisualDSP++ documentation set for any topic of interest. For easy

printing, supplementary

VisualDSP++ 4.0 Loader Manual xix

.PDF files of most manuals are also provided.

Page 20

Product Information

Each documentation file type is described as follows.

File Description

.CHM Help system files and manuals in Help format

.HTM or

.HTML

.PDF VisualDSP++ and processor manuals in Portable Documentation Format (PDF).

Dinkum Abridged C++ library and FlexLM network license manager software documentation. Viewing and printing the

Internet Explorer 4.0 (or higher).

Viewing and printing the

Reader (4.0 or higher).

.PDF files requires a PDF reader, such as Adobe Acrobat

.HTML files requires a browser, such as

If documentation is not installed on your system as part of the software

installation, you can add it from the VisualDSP++ CD-ROM at any time

by running the Tools installation. Access the online documentation from

the VisualDSP++ environment, Windows

®

Explorer, or the Analog

Devices Web site.

Accessing Documentation From VisualDSP++

From the VisualDSP++ environment:

• Access VisualDSP++ online Help from the Help menu’s Contents,

Search, and Index commands.

• Open online Help from context-sensitive user interface items (toolbar buttons, menu commands, and windows).

Accessing Documentation From Windows

In addition to any shortcuts you may have constructed, there are many

ways to open VisualDSP++ online Help or the supplementary documentation from Windows.

xx VisualDSP++ 4.0 Loader Manual

Page 21

Preface

Help system files (.

located in the

The

Docs folder also contains the Dinkum Abridged C++ library and the

CHM) are located in the Help folder, and .PDF files are

Docs folder of your VisualDSP++ installation CD-ROM.

FlexLM network license manager software documentation.

Using Windows Explorer

• Double-click the

tem, to access all the other

vdsp-help.chm file, which is the master Help sys-

.CHM files.

• Double-click any file that is part of the VisualDSP++ documentation set.

Using the Windows Start Button

• Access VisualDSP++ online Help by clicking the Start button and

choosing Programs, Analog Devices, VisualDSP++, and

VisualDSP++ Documentation.

Accessing Documentation From the Web

Download manuals at the following Web site:

http://www.analog.com/processors/resources/technicalLibrary/manuals

Select a processor family and book title. Download archive (.ZIP) files, one

for each manual. Use any archive management software, such as WinZip,

to decompress downloaded files.

Printed Manuals

For general questions regarding literature ordering, call the Literature

Center at 1-800-ANALOGD (1-800-262-5643) and follow the prompts.

VisualDSP++ Documentation Set

To purchase VisualDSP++ manuals, call 1-603-883-2430. The manuals

may be purchased only as a kit.

VisualDSP++ 4.0 Loader Manual xxi

Page 22

Product Information

If you do not have an account with Analog Devices, you are referred to

Analog Devices distributors. For information on our distributors, log onto

http://www.analog.com/salesdir/continent.asp.

Hardware Tools Manuals

To purchase EZ-KIT Lite™ and In-Circuit Emulator (ICE) manuals, call

1-603-883-2430. The manuals may be ordered by title or by product

number located on the back cover of each manual.

Processor Manuals

Hardware reference and instruction set reference manuals may be ordered

through the Literature Center at 1-800-ANALOGD (1-800-262-5643),

or downloaded from the Analog Devices Web site. Manuals may be

ordered by title or by product number located on the back cover of each

manual.

Data Sheets

All data sheets (preliminary and production) may be downloaded from the

Analog Devices Web site. Only production (final) data sheets (Rev. 0, A,

B, C, and so on) can be obtained from the Literature Center at

1-800-ANALOGD (1-800-262-5643); they also can be downloaded from

the Web site.

To have a data sheet faxed to you, call the Analog Devices Faxback System

at 1-800-446-6212. Follow the prompts and a list of data sheet code

numbers will be faxed to you. If the data sheet you want is not listed,

check for it on the Web site.

xxii VisualDSP++ 4.0 Loader Manual

Page 23

Notation Conventions

Text conventions used in this manual are identified and described as

follows.

Example Description

Preface

Close command

(File menu)

{this | that} Alternative required items in syntax descriptions appear within curly

[this | that] Optional items in syntax descriptions appear within brackets and sepa-

[this,…] Optional item lists in syntax descriptions appear within brackets

.SECTION Commands, directives, keywords, and feature names are in text with

filename Non-keyword placeholders appear in text with italic style format.

L

a

Titles in reference sections indicate the location of an item within the

VisualDSP++ environment’s menu system (for example, the Close

command appears on the File menu).

brackets and separated by vertical bars; read the example as

that. One or the other is required.

rated by vertical bars; read the example as an optional

delimited by commas and terminated with an ellipse; read the example

as an optional comma-separated list of

letter gothic font.

Note: For correct operation, ...

A Note provides supplementary information on a related topic. In the

online version of this book, the word Note appears instead of this

symbol.

Caution: Incorrect device operation may result if ...

Caution: Device damage may result if ...

A Caution identifies conditions or inappropriate usage of the product

that could lead to undesirable results or product damage. In the online

version of this book, the word Caution appears instead of this symbol.

this.

this or

this or that.

Warn in g: Injury to device users may result if ...

A Warning identifies conditions or inappropriate usage of the product

[

that could lead to conditions that are potentially hazardous for devices

users. In the online version of this book, the word Wa rnin g appears

instead of this symbol.

VisualDSP++ 4.0 Loader Manual xxiii

Page 24

Notation Conventions

L

Additional conventions, which apply only to specific chapters, may

appear throughout this document.

xxiv VisualDSP++ 4.0 Loader Manual

Page 25

1 INTRODUCTION

The majority of this manual describes the loader program (or loader utility) as well as the process of loading and splitting, the final phase of an

application program’s development flow.

Most of this chapter applies to all 8-, 16-, and 32-bit data processors.

Information applicable to a particular target processor, or to a particular

processor family, is provided in the following chapters.

• Chapter 2, “Loader/Splitter for Blackfin Processors”

• Chapter 3, “Loader for ADSP-TSxxx TigerSHARC Processors”

• Chapter 4, “Loader for ADSP-2106x/21160 SHARC Processors”

• Chapter 5, “Loader for ADSP-21161 SHARC Processors”

• Chapter 6, “Loader for ADSP-2126x/2136x SHARC Processors”

• Chapter 7, “Splitter for SHARC and TigerSHARC Processors”

L

VisualDSP++ 4.0 Loader Manual 1-1

The code examples in this manual have been compiled using

VisualDSP++ 4.0. The examples compiled with another version of

VisualDSP++ may result in build errors or different output;

although, the highlighted algorithms stand and should continue to

stand in future releases of VisualDSP++.

Page 26

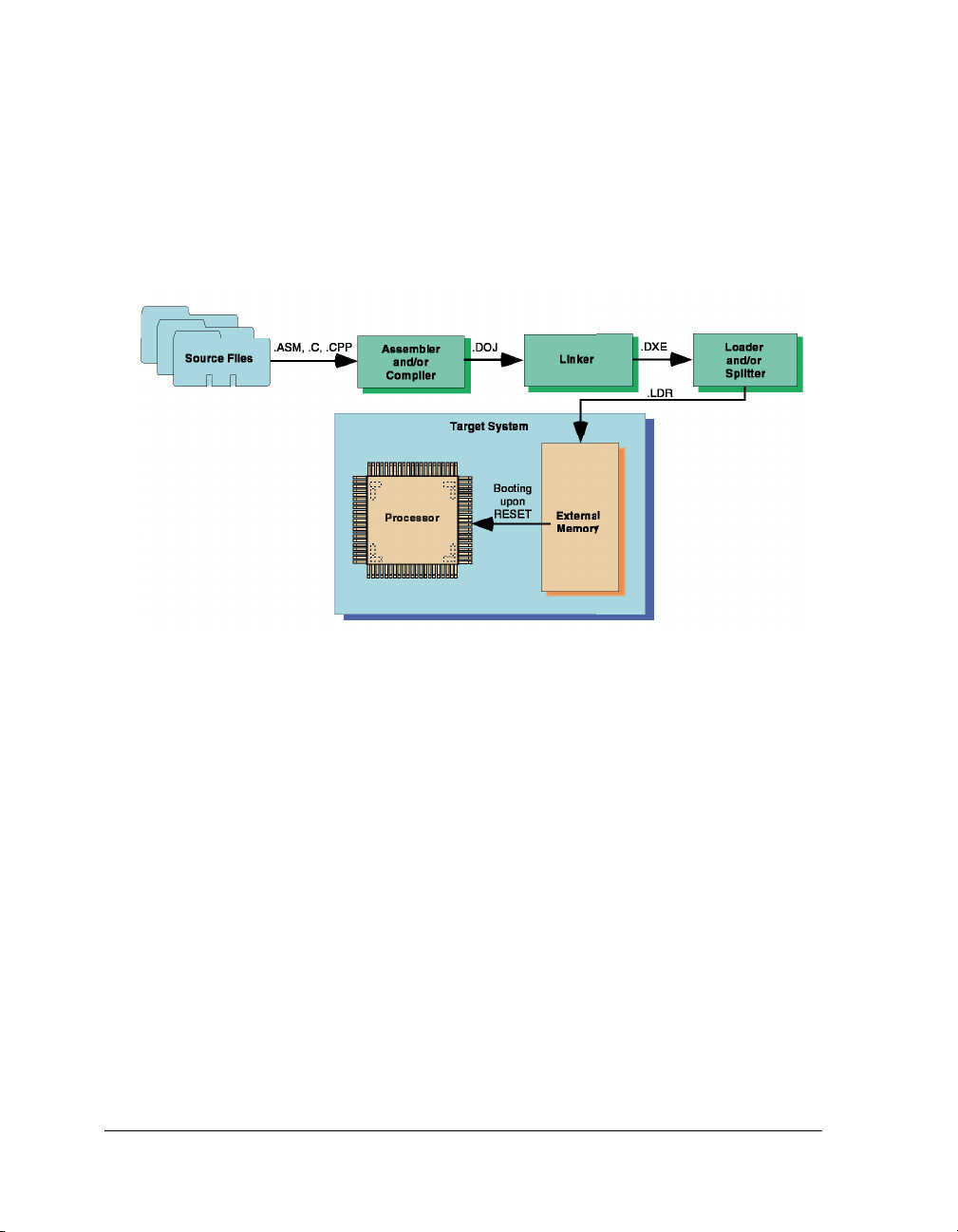

Program Development Flow

Program Development Flow

Figure 1-1 is a simplified view of the application development flow.

Figure 1-1. Program Development Flow and Booting Sequence

The development flow can be split into three phases:

1. “Compiling and Assembling”

2. “Linking”

3. “Loading, Splitting, or Both”

A brief description of each phase follows.

Compiling and Assembling

Input source files are compiled and assembled to yield object files. Source

files are text files containing C/C++ code, compiler directives, possibly a

mixture of assembly code and directives, and, typically, preprocessor commands. Refer to the VisualDSP++ 4.0 Assembler and Preprocessor Manual

1-2 VisualDSP++ 4.0 Loader Manual

Page 27

Introduction

or the VisualDSP++ 4.0 C/C++ Compiler and Library Manual for your

processor, and online help for information about the assembler and

compiler.

Linking

Under the direction of the Linker Description File (LDF) and linker settings, the linker consumes separately-assembled object and library files to

yield an executable file. If specified, the linker also produces the shared

memory files and overlay files. The linker output (.

the Executable and Linkable Format (ELF), an industry-standard format

for executable files. The linker also produces map files and other embedded information (DWARF-2) used by the debugger.

These executable files are not readable by the processor hardware directly.

They are neither supposed to be burned onto an EPROM or flash memory

device. Executable files are intended for VisualDSP++ debugging targets,

such as the simulator or emulator. Refer to the VisualDSP++ 4.0 Linker

and Utilities Manual and online Help for information about linking and

debugging.

DXE files) conforms to

Loading, Splitting, or Both

Upon completing the debug cycle, the processor hardware needs to run on

its own, without any debugging tools connected. After power-up, the

processor’s on-chip and off-chip memories need to be initialized. The process of initializing memories is often referred to as booting. Therefore, the

linker output must be transformed to a format readable by the processor.

This process is handled by the loader/splitter program. The loader/splitter

uses the debugged and tested executable files as well as shared memory and

overlay files as inputs to yield a processor-loadable file.

VisualDSP++ 4.0 Loader Manual 1-3

Page 28

Program Development Flow

VisualDSP++ 4.0 includes these loader/splitter programs:

•

elfloader.exe (loader) for Blackfin, TigerSHARC, and SHARC

processors. The loader for Blackfin processors acts also as a ROM

splitter when invoked with the corresponding option settings or

switches.

•

elfspl21k.exe (splitter) for TigerSHARC and SHARC processors.

The loader/splitter output is either a boot-loadable or non-bootable file.

The output is meant to be loaded onto the target. There are several ways

to use the output:

• Download the loadable file into the processor PROM space on an

EZ-KIT Lite

®

board via the Flash Programmer plug-in. Refer to

VisualDSP++ Help for information on the Flash Programmer.

• Use VisualDSP++ to simulate booting in a simulator session (where

supported). Load the loader file and then reset the processor to

debug the booting routines. No hardware is required: just point to

the location of the loader file, letting the simulator to do the rest.

You can step through the boot kernel code as it brings the rest of

the code into memory.

• Store the loader file in an array on a multiprocessor system. A master (host) processor has the array in its memory, allowing a full

control to reset and load the file into the memory of a slave

processor.

Non-bootable Files Versus Boot-loadable Files

A non-bootable file executes from an external memory of the processor,

while a boot-loadable file is transported into and executes from an internal

memory of the processor. The boot-loadable file is then programmed

(burned into EPROM) into an external memory device within your target

system. The loader outputs loadable files in formats readable by most

1-4 VisualDSP++ 4.0 Loader Manual

Page 29

Introduction

EPROM burners, such as Intel hex-32 and Motorola S formats. For

advanced usage, other file formats and boot modes are supported. (See

“File Formats” on page A-1.)

A non-bootable EPROM image file executes from an external memory of

the processor, bypassing the built-in boot mechanisms. Preparing a

non-bootable EPROM image is called splitting. In most cases (except for

Blackfin processors), developers working with floating- and fixed-point

processors use the splitter instead of the loader to produce a non-bootable

memory image file.

A booting sequence of the processor and application program design dictate the way loader/splitter program is called to consume and transform

executable files:

• For Blackfin processors, splitter and loader operations are handled

by the loader program,

elfloader.exe. The splitter is invoked by a

different set of command-line switches than the loader.

• For TigerSHARC and SHARC processors, splitter operations are

handled by the splitter program,

elfspl21k.exe.

Loader Operations

You can run the loader from the IDDE. In order to do so, change the

project type from DSP Executable to DSP Loader File.

Loader operations depend on loader options, which control how the

loader processes executable files into boot-loadable files, letting you select

features such as kernels, boot modes, and output file formats. These

options are set on the Load page of the Project Options dialog box in the

VisualDSP++ Integrated Development and Development Environment

(IDDE) or on the loader command line. Option settings on the Load page

correspond to switches typed on the

elfloader.exe command line.

VisualDSP++ 4.0 Loader Manual 1-5

Page 30

Booting Modes

Splitter Operations

Splitter operations depend on splitter options, which control how the

splitter processes executable files into non-bootable files:

• For Blackfin processor, the loader program includes the ROM

splitter capabilities invoked through the Load page, the ROM

splitter options category of the Project Options dialog box. Refer

to “Using the ROM Splitter” on page 2-62. Option settings on the

Load page correspond to switches typed on the

command line.

• For ADSP-21xxx SHARC and ADSP-TSxxx TigerSHARC processors, change the project type to DSP splitter file. The splitter

options are set via the Split page of the Project Options dialog box.

Refer to “Splitter for SHARC and TigerSHARC Processors” on

page 7-1. Option settings on the Splitter page correspond to

switches typed on the

elfspl21k.exe command line.

elfloader.exe

Booting Modes

Once an executable file is fully debugged, the loader is ready to convert

the executable file into a processor-loadable (or boot-loadable) file. The

loadable file can be automatically downloaded (booted) to the processor

after power-up or after a software reset. The way the loader creates a

boot-loadable file depends upon how the loadable file is booted into the

processor.

The boot mode of the processor is determined by sampling one or more of

the input flag pins. Booting sequences, highly processor-specific, are

detailed in the following chapters.

1-6 VisualDSP++ 4.0 Loader Manual

Page 31

Introduction

Analog Devices processors support different boot mechanisms. In general,

the following schemes can be used to provide program instructions to the

processors after reset.

• “No-Boot Mode”

• “PROM Boot Mode”

• “Host Boot Mode”

No-Boot Mode

After reset, the processor starts fetching and executing instructions from

EPROM/flash memory devices directly. This scheme does not require any

loader mechanism. It is up to the user program to initialize volatile

memories.

The splitter utility generates a file that can be burned into the PROM

memory.

PROM Boot Mode

After reset, the processor starts reading data from a parallel or serial

PROM device. The PROM stores a formatted boot stream rather than raw

instruction code. Beside application data, the boot stream contains additional data, such as destination addresses and word counts. A small

program called kernel, loader kernel, or boot kernel (described on page 1-8)

parses the boot stream and initializes memories accordingly. The loader

kernel runs on the target processor. Depending on the architecture, the

loader kernel may execute from on-chip boot RAM or may be preloaded

from the PROM device into on-chip SRAM and execute from there.

The loader utility generates the boot stream from the linker output (an

executable file) and stores it to file format that can be burned into the

PROM.

VisualDSP++ 4.0 Loader Manual 1-7

Page 32

Boot Kernels

Host Boot Mode

In this scheme, the target processor is a slave to a host system. After reset,

the processor delays program execution until the slave gets signalled by the

host system that the boot process has completed. Depending on hardware

capabilities, there are two different methods of host booting. In the first

case, the host system has full control over all target memories. The host

halts the target while initializing all memories as required. In the second

case, the host communicates by a certain handshake with the loader kernel

running on the target processor. This kernel may execute from on-chip

ROM or may be preloaded by the host devices into the processor’s SRAM

by any bootstrapping scheme.

The loader/splitter utility generates a file that can be consumed by the

host device. It depends on the intelligence of the host device and on the

target architecture whether the host expects raw application data or a formatted boot stream.

In this context, a boot-loadable file differs from a non-bootable file in that

it stores instruction code in a formatted manner in order to be processed

by a boot kernel. A non-bootable file stores raw instruction code.

Boot Kernels

A boot kernel (or loader kernel) refers to the resident program in the boot

ROM space responsible for booting the processor. Alternatively (or in

absence of the boot ROM), the boot kernel can be preloaded from the

boot source by a bootstrapping scheme.

When a reset signal is sent to the processor, the processor starts booting

from a PROM, host device, or through a communication port. For example, an ADSP-2106x/2116x processor brings a 256-word program into

internal memory for execution. This small program is a boot kernel.

1-8 VisualDSP++ 4.0 Loader Manual

Page 33

Introduction

The boot kernel then brings the rest of the application code into the processor’s memory. Finally, the boot kernel overwrites itself with the final

block of application code and jumps to the beginning of the application

program.

Some of the newer Blackfin processors (ADSP-BF531, ADSP-BF532,

ADSP-BF533, ADSP-BF534, ADSP-BF535, ADSP-BF536,

ADSP-BF537, ADSP-BF538, and ADSP-BF539) do not require a boot

kernel—the on-chip boot ROM allows the entire application program’s

body to be booted into the internal memory of the processor. The on-chip

boot ROM for the former Blackfin processors behaves similar to the

second-stage loader of the ADSP-BF535 processors. The boot ROM has

the capability to parse address and count information for each bootable

block.

Loader Tasks

Common tasks performed by the loader include:

• Processing loader option settings or command-line switches.

• Formatting the output

Supported formats are binary, ASCII, hex-32, and more. Valid file

formats are described in “File Formats” on page A-1.

• Packing the code for a particular data format: 8-, 16- or 32-bit for

some processors.

• Adding the code and data from a specified initialization executable

file to the loader file, if applicable.

• Adding a boot kernel on top of the user code.

VisualDSP++ 4.0 Loader Manual 1-9

.LDR file according to user specifications.

Page 34

Boot Streams

g

• If specified, preprogramming the location of the

.LDR file in a

specified PROM space.

• Specifying processor IDs for multiple input

.DXE files for a

multiprocessor system, if applicable.

Boot Streams

The loader output (.LDR file) is essentially the same executable code as in

the input .DXE file; the loader simply repackages the executable as shown

in Figure 1-2).

.DXE FILE

CODE

DATA

SYMBOLS

DEBUG

INFORMATION

.LDR FILE

CODE

DATA

SYMBO LS

DEBUG

INF ORM ATION

A.DXEfileincludes:

- DSP instructions (code and data)

- Symbol table and section information

-Target processor me m ory layout

- Debu

inform a tio n

An .LDR file includes:

- DSP instructions (code and data)

- Rudimentary formatting

(all debug inform ation has

been taken out)

Figure 1-2. A .DXE File Versus an .LDR File

Processor code and data in a loader file (also called a boot stream) is split

into blocks. Each code block is marked with a tag that contains information about the block, such as the number of words or destination in the

processor’s memory. Depending on the processor family, there may be

1-10 VisualDSP++ 4.0 Loader Manual

Page 35

Introduction

additional information in the tag. Common block types are “zero” (memory is filled with 0s); nonzero (code or data); and final (code or data).

Depending on the processor family, there may be other block types.

Refer to the following chapters to learn more about boot streams.

File Searches

File searches are important in the loader operation. The loader supports

relative and absolute directory names and default directories. File searches

occur as follows.

• Specified path—If relative or absolute path information is included

in a file name, the loader searches only in that location for the file.

• Default directory—If path information is not included in the file

name, the loader searches for the file in the current working

directory.

• Overlay and shared memory files—The loader recognizes overlay

and shared memory files but does not expect these files on the

command line. Place the files in the directory that contains the

executable file that refers to them, or place them in the current

working directory. The loader can locate them when processing the

executable file.

When providing an input or output file name as a loader/splitter command-line parameter, use these guidelines:

• Enclose long file names within straight quotes,

“long file name”.

• Append the appropriate file extension to each file.

VisualDSP++ 4.0 Loader Manual 1-11

Page 36

Boot Streams

1-12 VisualDSP++ 4.0 Loader Manual

Page 37

2 LOADER/SPLITTER FOR

BLACKFIN PROCESSORS

This chapter explains how the loader/splitter program (elfloader.exe) is

used to convert executable (.

files for the ADSP-BF5xx Blackfin processors.

Refer to “Introduction” on page 1-1 for the loader overview; the introduc-

tory material applies to all processor families. Loader operations specific to

ADSP-BF5xx Blackfin processors are detailed in the following sections.

• “Blackfin Processor Booting” on page 2-2

Provides general information on various booting modes, including

information on second-stage kernels:

DXE) files into boot-loadable or non-bootable

• “ADSP-BF535 Processor Booting” on page 2-2

• “ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 Processor Booting” on page 2-17

• “ADSP-BF561 and ADSP-BF566 Processor Booting” on

page 2-37

• “Blackfin Processor Loader Guide” on page 2-49

Provides reference information on the loader’s command-line

syntax and switches.

VisualDSP++ 4.0 Loader Manual 2-1

Page 38

Blackfin Processor Booting

Blackfin Processor Booting

A Blackfin processor can be booted from an 8- or 16-bit flash/PROM

memory or an 8-,16-, or 24-bit addressable SPI memory. (Only the

ADSP-BF531/BF532/BF533/BF534/BF535/BF536/BF537/BF538/

BF539 processors support 24-bit addressable SPI memory booting.) There

is also a no-boot option (bypass mode) in which execution occurs from a

16-bit external memory.

At power-up, after the reset, the processor transitions into a boot mode

sequence configured by the

bits in the System Reset Configuration Register (

are dedicated mode-control pins; that is, no other functions are shared

with these pins.

BMODE pins. These pins can be read through

SYSCR). The BMODE pins

L

more information on system configuration, peripherals, registers,

and operating modes.

ADSP-BF535 Processor Booting

Upon reset, an ADSP-BF535 processor jumps to an external 16-bit memory for execution (if BMODE = 000) or to the on-chip boot ROM (if

BMODE = 001, 010, 011). Table 2-1 summarizes booting modes and code

execution start addresses for ADSP-BF535 processors.

Table 2-1. ADSP-BF535 Processor Boot Mode Selections

Boot Source BMODE[2:0] Execution Start Address

Refer to the processor’s Data Sheet and Hardware Reference for

Execute from a 16-bit external memory (Async Bank

0); no-boot mode (bypass on-chip boot ROM)

Boot from an 8-bit/16-bit flash memory 001 0xF000 0000

Boot from an 8-bit address SPI0 serial EEPROM 010 0xF000 0000

000 0x2000 0000

1

1

2-2 VisualDSP++ 4.0 Loader Manual

Page 39

Loader/Splitter for Blackfin Processors

Table 2-1. ADSP-BF535 Processor Boot Mode Selections (Cont’d)

Boot Source BMODE[2:0] Execution Start Address

Boot from a 16-bit address SPI0 serial EEPROM 011 0xF000 0000

Reserved 111—100 N/A

1 The processor jumps to this location after the booting is complete.

1

A description of each boot mode is as follows.

• “ADSP-BF535 Processor On-Chip Boot ROM” on page 2-3

• “ADSP-BF535 Processor Second-Stage Loader” on page 2-5

• “ADSP-BF535 Processor Boot Streams” on page 2-8

• “ADSP-BF535 Processor Memory Ranges” on page 2-15

ADSP-BF535 Processor On-Chip Boot ROM

The on-chip boot ROM for the ADSP-BF535 processor does the following (Figure 2-1).

1. Sets up Supervisor mode by exiting the

RESET interrupt service rou-

tine and jumping into the lowest priority interrupt (IVG15).

2. Checks whether the RESET was a software reset and if so, whether to

skip the entire boot sequence and jump to the start of L2 memory

(

0xF000 0000) for execution. The on-chip boot ROM does this by

checking bit 4 of the System Reset Configuration Register (

SYSCR).

If bit 4 is not set, the on-chip boot ROM performs the full boot

sequence. If bit 4 is set, the on-chip boot ROM bypasses the full

boot sequence and jumps to

0xF000 0000. The register settings are

shown in Figure 2-2.

VisualDSP++ 4.0 Loader Manual 2-3

Page 40

Blackfin Processor Booting

ADSP-BF535 Processor

0xEF00 0000

On-Chip

BootROM

L2 Memory

(0xF000 0000)

2ndStage

2ndStage Lo ader

Loader

or

or

Application

Code

Application

PROM/Flash or SPI Device

4-Byte Header (N)

2ndStage Loader

or

Application

Code

Figure 2-1. ADSP-BF535 Processors: On-Chip Boot ROM

0x0

N

Bytes

System Reset Configuration Register (SYSCR)

X - state is initialized from mode pins during hardware reset

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

00000000 00 00XXX

No Boot on Software Reset

0 - Use BMODE to determine

boot source.

1 - Start executing from the

beginning of on-chip L2 memory

(or the beginning of ASYNC Bank 0

when BMODE[2:0] = b#000).

0

Reset = dependent on pin values

BMODE 2-0 - RO

000 - Bypass boot ROM,

execute from 16-bit-wide

external memory.

001 - Use boot ROM to load

from 8-bit/16-bit flash.

010 - Use boot ROM to configure

and load boot code from

SPI0 serial ROM

(8-bit address range).

011 - Use boot ROM to configure

and load boot code from

SPI0 serial ROM

(16-bit address range).

100-111 - Reserved

Figure 2-2. ADSP-BF535 Processors: System Reset Configuration Register

2-4 VisualDSP++ 4.0 Loader Manual

Page 41

Loader/Splitter for Blackfin Processors

3. Finally, if bit 4 of the

SYSCR register is not set, performs the full

boot sequence. The full boot sequence includes:

D Checking the boot source (either flash/PROM or SPI mem-

ory) by reading

D Reading the first four bytes from location 0x0 of the exter-

BMODE[2:0] from the SYSCR register.

nal memory device. These four bytes contain the byte

count (

D Booting in N bytes into internal L2 memory starting at loca-

tion

D Jumping to the start of L2 memory for execution.

N), which specifies the number of bytes to boot in.

0xF000 0000.

The on-chip boot ROM boots in N bytes from the external memory. These

N bytes can define the size of the actual application code or a second-stage

loader (called a boot kernel) that boots in the application code.

ADSP-BF535 Processor Second-Stage Loader

The only situation where a second-stage loader is unnecessary is when the

application code contains only one section starting at the beginning of L2

memory (

0xF000 0000).

A second-stage loader must be used in applications in which multiple segments reside in L2 memory or in L1 memory and/or SDRAM. In

addition, a second-stage loader must be used to change the wait states or

hold time cycles for a flash/PROM booting or to change the baud rate for

an SPI boot (see “Command-Line Switches” on page 2-51 for more information on these features).

VisualDSP++ 4.0 Loader Manual 2-5

Page 42

Blackfin Processor Booting

When a second-stage loader is used for booting, the following sequence

occurs.

1. Upon

second-stage loader) from external memory to address

RESET, the on-chip boot ROM downloads N bytes (the

0xF000 0000

in L2 memory (Figure 2-3).

ADSP-BF535 Processor

0xEF00 0000

On-Chip

Boot ROM

L2 Memory

(0xF000 0000)

2ndStage Load er

PROM/Flash or SPI Device

4-Byte H eader (N)

2ndStageLoader

Application

Code/Data

0x0

Bytes

N

Figure 2-3. ADSP-BF535 Processors: Booting With Second-Stage Loader

2-6 VisualDSP++ 4.0 Loader Manual

Page 43

Loader/Splitter for Blackfin Processors

2. The second-stage loader copies itself to the bottom of L2 memory.

ADSP-BF535 Processor

0xEF00 0000

On-Chip

Boot ROM

L2 Memory

(0xF000 0000)

2ndStageLoader

2ndStage Loader

or

Application

Code

2ndStage Loader

PROM/Flash or SPI Dev ice

4-Byte H eader (N )

2ndStage Loader

Application

Code/Data

0x0

Figure 2-4. ADSP-BF535 Processors: Copying Second-Stage Loader

3. The second-stage loader boots in the application code/data into the

various memories of the Blackfin processor (Figure 2-5).

ADSP-BF535 Processor

0xEF000000

On-C hip

Boot ROM

L1 M em o ry

B

L2 Memory

(0x F00 0 0 000)

2ndStage Loader

A

2ndStage Loader

or

Application

2ndStage Loader

Code

PROM/Flash or SP IDevice

4-By te H eader (N )

2ndStage Loader

A

B

C

SDR AM

C

0x0

App li catio n

Cod e/ Data

Figure 2-5. ADSP-BF535 Processors: Booting Application Code

VisualDSP++ 4.0 Loader Manual 2-7

Page 44

Blackfin Processor Booting

4. Finally, after booting, the second-stage loader jumps to the start of

L2 memory (

0xF000 0000) for application code execution

(Figure 2-6).

ADSP-BF535 Processor

0xEF00 0000

On-Chip

Boot ROM

L1 Memory

B

L2 Memory

(0xF000 0000)

A

2nd Stage Loader

PROM/Flash or SPI Device

4-Byte Header (N)

2nd Stage Loader

A

B

C

SDRAM

C

0x0

Application

Code/Data

Figure 2-6. ADSP-BF535 Processors: Starting Application Code

ADSP-BF535 Processor Boot Streams

The loader generates the boot stream and places the boot stream in the

output loader (.

LDR) file. The loader prepares the boot stream in a way that

enables the on-chip boot ROM and the second-stage loader to load the

application code and data to the processor memory correctly. Therefore,

the boot stream contains not only the user application code but also

header and flag information that is used by the on-chip boot ROM and

the second-stage loader.

2-8 VisualDSP++ 4.0 Loader Manual

Page 45

Loader/Splitter for Blackfin Processors

Diagrams in this section illustrate boot streams utilized by the

ADSP-BF535 processor’s boot kernel:

• “Loader Files Without a Second-Stage Loader” on page 2-9

• “Loader Files With a Second-Stage Loader” on page 2-11

• “Global Headers” on page 2-13

• “Blocks, Block Headers, and Flags” on page 2-14

Loader Files Without a Second-Stage Loader

Figure 2-7 is a graphical representation of an output loader file for 8-bit

PROM/flash booting and 8-/16-bit addressable SPI booting without the

second-stage loader (kernel).

Output . LDR File

4-Byte Heade rfor

Byte Count (N)

Byte Count for

Application Code

Byte 0

Byte 1

Byte 2

Byte 3

........

........

........

D7

Figure 2-7. Loader

Application

Code

(N Words)

D0

File for 8-/16-bit PROM/Flash Booting Without Kernel

VisualDSP++ 4.0 Loader Manual 2-9

Page 46

Blackfin Processor Booting

Figure 2-8 is a graphical representation of an output loader file for 16-bit

PROM/flash booting without the second-stage loader (kernel).

Output .LDR Fi le

0x00

4-Byte Headerfor

Byte Count (N)

Byte Count for

Application Code

0x00

0x00

0x00

0x00

0x00

0x00

0x00

D15 D8 D7 D0

Figure 2-8. Loader

Byte 0

Byte 1

Byte 2

Byte 3

........

........

........

File for 16-bit PROM/Flash Booting Without Kernel

Application

Code

(N Words)

2-10 VisualDSP++ 4.0 Loader Manual

Page 47

Loader/Splitter for Blackfin Processors

Loader Files With a Second-Stage Loader

Figure 2-9 is a graphical representation of an output loader file for 8-bit

PROM/flash booting and 8- or 16-bit addressable SPI booting with the

second-stage loader (kernel).

Output .LDR File

4-Byte Header for

Byte Coun t(N)

Byte 0

Byte Count for

nd

2

Stage Loader

Byte 1

Byte 2

........

Byte 0

Byte 1

Byte 2

........

D7

Figure 2-9. Loader

2ndStage Loader

(N Bytes)

Application

Code

(in Blocks)

D0

File for 8-/16-bit PROM/Flash/SPI Booting With Kernel

See also

Figure 2-12

See also

Figure 2-14

VisualDSP++ 4.0 Loader Manual 2-11

Page 48

Blackfin Processor Booting

An output loader file for 16-bit PROM/flash booting with the

second-stage loader is illustrated in Figure 2-10.

Out put .L DR Fi le

0x00

0x00

0x00

0x00

0x00

4-ByteH eaderfor

Byte Count (N)

Byte 0

Byte 1

Byte 2

........

Byte Count for

nd

2

Stage Loader

2ndStage

Loader

See also

Figure 2-12

Byte 1

Byte 3

Byte 5

........

D15 D8 D7 D0

Byte 0

Byte 2

Byte 4

........

Application

Code

(in Blocks)

See also

Figure 2-14

Figure 2-10. Loader File for 16-bit PROM/Flash Booting With Kernel for

ADSP-BF531/BF532/BF533 Silicon Revision 0.2 and Below

2-12 VisualDSP++ 4.0 Loader Manual

Page 49

Loader/Splitter for Blackfin Processors

Global Headers

Following the second-stage loader code and address in a loader file, there

is a 4-byte global header. The header provides the global settings for a

booting process (see Figure 2-11).

Output .LDRFile

4Bytes

Byte Count (N)

Byte Count for

nd

2

Stage Loader

NBytes

4Bytes

4Bytes

4Bytes

N1 Bytes

nd

Stage Loader

2

2nd Stage Loader

Address

Global Header

Size of Application

Code (N1)

Application C ode

Address of the Bottom of L2 Memory

from which 2

See Figure 2-13

nd

Stage Loader runs

Figure 2-11. Global Header

A global header for 8- and 16-bit PROM/flash booting is illustrated in

Figure 2-12.

15

14 13 12

Number of hold time cycles: 3 (default)

Number of wait states: 15 (default)

1 = 16-bit PROM/flash, 0 = 8-bit PROM/flash: 0 (default)

11

10

9

8

76

5

3

4

0

2

1

Figure 2-12. PROM/Flash Booting: Global Header Bits

VisualDSP++ 4.0 Loader Manual 2-13

Page 50

Blackfin Processor Booting

A global header for 8- and 16-bit addressable SPI booting is illustrated in

Figure 2-13.

015 14 13 12 11 10 9 8 7 6 5

Baud rate: 0 = 500 kHz (default), 1 = 1 MHz, 2 = 2 MHz

321

4

Figure 2-13. Addressable SPI Booting: Global Header Bits

Blocks, Block Headers, and Flags

A block is the basic structure of the output

.LDR file for application code

when the second-stage loader is used. All the application code is grouped

into blocks. A block always has a block header and a block body if it is a

non-zero block. A block does not have a block body if it is a zero block. A

block header is illustrated in Figure 2-14.

4Bytes

NBytes

4Bytes

4Bytes

4Bytes

N1 Bytes

Output . LDR Fi le

Byte Count (N)

nd

2

Stage Loade r

2ndStage Loader

Address

Global Header

Size of Application

Code (N1)

Ap plica tio n Co d e

Sizeof Ap plication

Code (N1)

Start Address

of Block1

Byte Count

of Block 1

Flag for Blo ck 1

Body of B lock 1

Start Address

of Block2

Byte Count

of Block2

......

4Bytes

4Bytes

2Bytes

Block

Header

Block

Figure 2-14. Application Block

2-14 VisualDSP++ 4.0 Loader Manual

Page 51

Loader/Splitter for Blackfin Processors

A block header has three words: 4-byte clock start address, 4-byte block

byte count, and 2-byte flag word.

The ADSP-BF535 block flag word’s bits are illustrated in Figure 2-15.

015 14 13 12 11 10 9 8 7 6 5

Bit 15: 1 = Last Block, 0 = Not Last Block

321

4

Bit 0: 1 = Zero-Fill, 0 = No Zero-Fill

Figure 2-15. Block Flag Word Bits

ADSP-BF535 Processor Memory Ranges

Second-stage loaders are available for ADSP-BF535 processors in

VisualDSP++ 3.0 and higher. They allow booting to:

• L2 memory (

0xF000 0000)

• L1 memory

D Data Bank A SRAM (0xFF80 0000)

D Data Bank B SRAM (0xFF90 0000)

D Instruction SRAM (0xFFA0 0000)

D Scratchpad SRAM (0xFFB0 0000)

•SDRAM

D Bank 0 (0x0000 0000)

D Bank 1 (0x0800 0000)

D Bank 2 (0x1000 0000)

D Bank 3 (0x1800 0000)

SDRAM must be initialized by user code before any instructions or

L

data are loaded into it.

VisualDSP++ 4.0 Loader Manual 2-15

Page 52

Blackfin Processor Booting

For more information, see “Using the Second-Stage Loader” on

page 2-59.

Second-Stage Loader Restrictions

Using the second-stage loader imposes the following restrictions.

• The bottom of L2 memory must be reserved during booting. These

locations can be reallocated during runtime. The following locations pertain to the current second-stage loaders.

D For 8- and 16-bit PROM/flash booting, reserve

0xF003 FE00—0xF003 FFFF (last 512 bytes).

D For 8- and 16-bit addressable SPI booting, reserve

0xF003 FD00—0xF003 FFFF (last 768 bytes).

• If segments reside in SDRAM memory, configure the SDRAM registers accordingly in the second-stage loader kernels before booting.

D Modify section of code called “SDRAM setup” in the

second-stage loader and rebuild the second-stage loader.

• Any segments residing in L1 instruction memory

(

0xFFA0 0000–0xFFA0 3FFF) must be 8-byte aligned.

D Declare segments, within the .LDF file, that reside in L1

instruction memory at starting locations that are 8-byte

aligned (for example,

0xFFA0 0010, and so on).

D Use the .ALIGN 8; directives in the application code.

0xFFA0 0000, 0xFFA0 0008,

2-16 VisualDSP++ 4.0 Loader Manual

Page 53

Loader/Splitter for Blackfin Processors

L

The two reasons for these restrictions are:

• Core writes into L1 instruction memory are not allowed.

• DMA from an 8-bit external memory is not possible since

the minimum width of the External Bus Interface Unit

(EBIU) is 16 bits.

Load bytes into L1 instruction memory by using the instruction test command and data registers, as described in the Memory chapter of the

appropriate Hardware Reference manual. These registers transfer 8-byte

sections of data from external memory to internal L1 instruction memory.

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/ BF538/BF539 Processor Booting

Upon reset, an ADSP-BF531/BF532/BF533/BF534/BF536/BF537/

BF538/BF539 processor jumps to the on-chip boot ROM (if

11) or jumps to 16-bit external memory for execution (if BMODE = 00)

located at

start addresses for ADSP-BF531, ADSP-BF532, ADSP-BF533,

ADSP-BF534, ADSP-BF536, ADSP-BF537, ADSP-BF538, and

ADSP-BF539 processors.

0xEF00 0000. Table 2-2 shows booting modes and execution

BMODE = 01,

VisualDSP++ 4.0 Loader Manual 2-17

Page 54

Blackfin Processor Booting

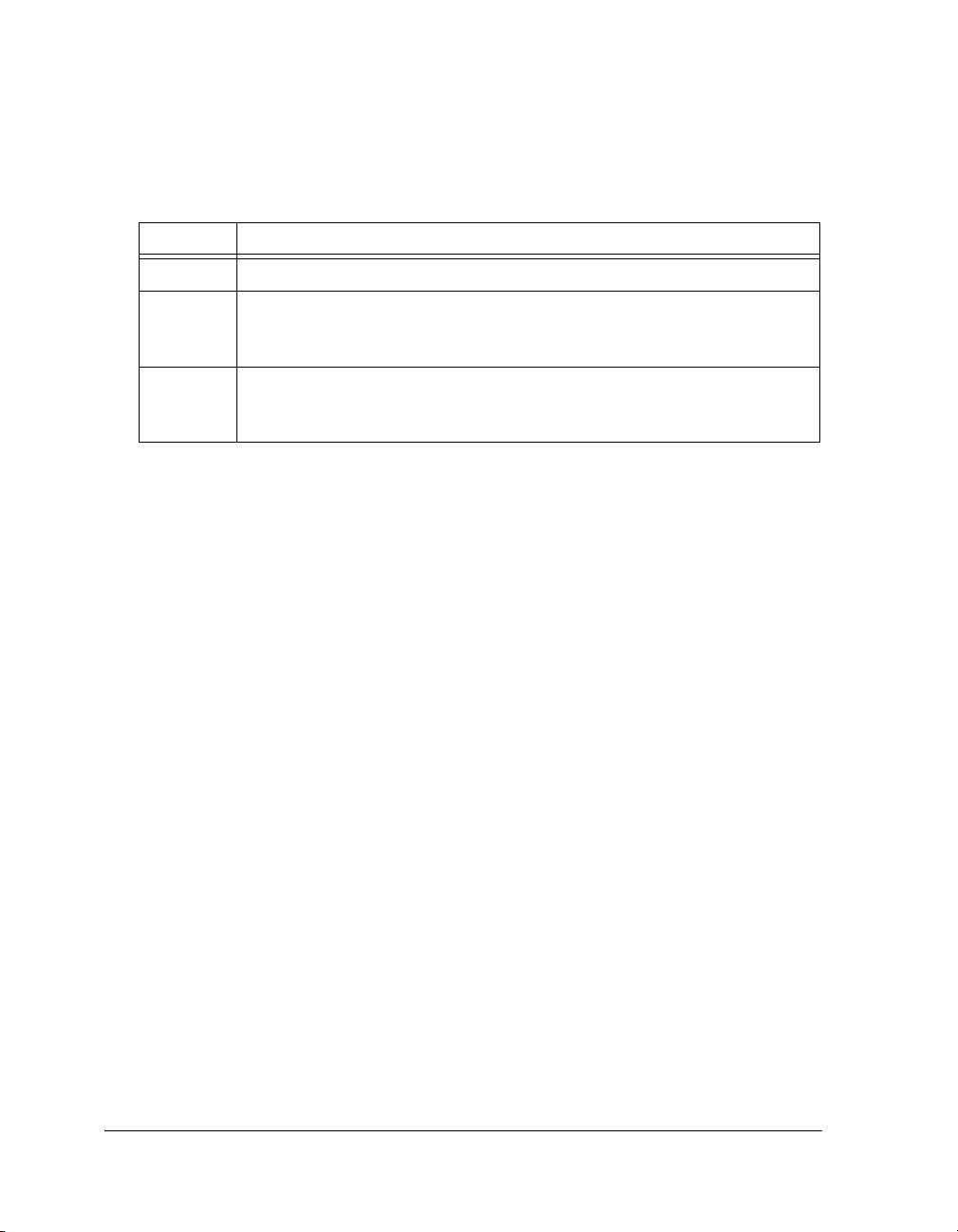

Table 2-2. Processor Boot Mode Selections for ADSP-BF531/BF532/

BF533/BF534/BF536/BF537/BF538/BF539 Processors

Execution Start Address

Boot Source BMODE[1:0]

ADSP-BF531

ADSP-BF532

ADSP-BF538

Processors

ADSP-BF533

ADSP-BF534

ADSP-BF536

ADSP-BF537

ADSP-BF539

Processors

Execute from 16-bit External

ASYNC Bank0 memory (no-boot

mode or bypass on-chip boot ROM)

Boot from 8- or 16-bit PROM/flash 01 0xFFA0 8000 0xFFA0 0000

Boot from SPI Host via SPI Slave

Mode

Boot from a 8-, 16-, or 24-bit

addressable SPI memory

00 0x2000 0000 0x2000 0000

10 0xFFA0 8000 0xFFA0 0000

11 0xFFA0 8000 0xFFA0 0000

A description of each boot mode is as follows.

• “ADSP-BF531/BF532/BF533/BF534/BF536/BF537/BF538/BF539

Processor On-Chip Boot ROM” on page 2-19

• “ADSP-BF531/BF532/BF533/BF534/BF536/BF537/BF538/BF539

Processor Boot Streams” on page 2-21

2-18 VisualDSP++ 4.0 Loader Manual

Page 55

Loader/Splitter for Blackfin Processors

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/BF538/BF539 Processor On-Chip Boot ROM

The on-chip boot ROM for ADSP-BF531/BF532/BF533/BF534/

BF536/BF537/BF538/BF539 processors does the following.

1. Sets up Supervisor mode by exiting the

routine and jumping into the lowest priority interrupt (

2. Checks whether the

RESET was a software reset and, if so, whether

to skip the entire sequence and jump to the start of L1 memory

(

0xFFA0 0000 for ADSP-BF533/BF534/BF536/BF537/BF539

processors;

0xFFA0 8000 for ADSP-BF531/BF532/BF538) for

execution. The on-chip boot ROM does this by checking bit 4 of

the System Reset Configuration Register (

If bit 4 is not set, the on-chip boot ROM performs the full boot

sequence. If bit 4 is set, the on-chip boot ROM bypasses the full

boot sequence and jumps to the start of L1 memory.

System Reset Configuration Register (SYSCR)

X - state is initialized from mode pins during hardware reset

0xFFC0 0104

No Boot on Software Reset

0 - Use BMODE to determine

boot source.

1 - Start executing from the

beginning of on-chip L1

memory (or the beginning of

ASYNC Bank 0 when

BMODE[1:0] = b#00).

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0

0000000 0 XX

0

RESET interrupt service

IVG15).

SYSCR). See Figure 2-16.

Reset = dependent on pin

0

values

0000

BMODE[1:0] (Boot Mode) - RO

00 - Bypass boot ROM,

execute from 16-bit

external memory.

01 - Use boot ROM to load

from 8-bit flash.

10 - Use boot ROM to configure

and load boot code from

SPI serial ROM

(8-bit address range).

11 - Use boot ROM to configure

and load boot code from

SPI serial ROM

(16-bit address range).

Figure 2-16. ADSP-BF533 Processors: SYSCR Register

VisualDSP++ 4.0 Loader Manual 2-19

Page 56

Blackfin Processor Booting

3. Eventually, if bit 4 of the

SYSCR register is not set, performs the full

boot sequence (Figure 2-17).

ADSP-BF531/BF532/BF533 Processor

L1 Memory

0xEF00 0000

On-Chip

Boot ROM

Block 1

Block 3

........

PRO M/Fla sh or SPI Device

10-Byte Hea der for Block 1

Block 1

10-Byte Hea der for Block 2

Block 2

10-Byte Hea der for Block 3

Block 3

........

10-Byt e Header for Bloc k n

Block n

SDRAM

Block 2

App.

Code/

Data

Figure 2-17. ADSP-BF531/BF532/BF533/BF534/BF536/BF537/BF538/

BF539 Processors: Booting Sequence

The booting sequence for ADSP-BF531/BF532/BF533/BF534/BF536/

BF537/BF538/BF539 processors is quite different from that for

ADSP-BF535 processors. The on-chip boot ROM for the former

processors behaves similar to the second-stage loader of ADSP-BF535

processors. The boot ROM has the capability to parse address and count

information for each bootable block. This alleviates the need for a

second-stage loader for ADSP-BF531/BF532/BF533/BF534/BF536/

BF537/BF538/BF539 processors because a full application can be booted

to the various memories with just the on-chip boot ROM.

The loader converts the application code (.

DXE) into the loadable file by

parsing the code and creating a file that consists of different blocks. Each

block is encapsulated within a 10-byte header, which is illustrated in

Figure 2-17 and detailed in the following section. These headers, in turn,

are read and parsed by the on-chip boot ROM during booting.

2-20 VisualDSP++ 4.0 Loader Manual

Page 57

Loader/Splitter for Blackfin Processors

The 10-byte header provides all the information the on-chip boot ROM

requires—where to boot the block to, how many bytes to boot in, and

what to do with the block.

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/BF538/BF539 Processor Boot Streams

The following sections describe the boot stream, header, and flag framework for the ADSP-BF531, ADSP-BF532, ADSP-BF533, ADSP-BF534,

ADSP-BF536, ADSP-BF537, ADSP-BF538, and ADSP-BF539

processors.

• “ADSP-BF531/BF532/BF533/BF534/BF536/BF537/BF538/BF539

Blocks, Block Headers, and Flags” on page 2-21

• “Initialization Blocks” on page 2-24

The ADSP-BF531/BF532/BF533 processor boot stream is similar to the

boot stream that uses a second-stage kernel of ADSP-BF535 processors

(detailed in “Loader Files With a Second-Stage Loader” on page 2-11).

However, since the former processors do not employ a kernel, their boot

streams do not include the kernel code and the associated 4-byte header

on the top of the kernel code. There is also no 4-byte global header.

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/BF538/BF539 Blocks, Block Headers, and Flags

As the loader converts the code from an input

.DXE file into blocks com-

prising the output loader file, each block is getting preceded by a 10-byte

header (Figure 2-18), followed by a block body (if it is a nonzero block) or

no block body (if it is a zero block). A description of the header structure

can be found in Table 2-3.

VisualDSP++ 4.0 Loader Manual 2-21

Page 58

Blackfin Processor Booting

Table 2-3. ADSP-BF531/BF532/BF533 Block Header Structure

Bit Field Description

Address 4-byte address at which the block resides in memory.

Count 4-byte number of bytes to boot.

Flag 2-byte flag containing information about the block; the following text

describes the flag structure.

Block

Header of DXE1 Count

10-Byte Header

4-Byte Address

4-Byte Count

2-Byte Flag

Boot Stream of the

First Executable (DXE1)

DXE1 Byte Count

Header of Block 1

Body of Block 2

Header for Block 2

Body of Block 2

......

......

Header of DXE2 Count

Boot Stream of the

Second Executable (DXE2)

Figure 2-18.

ADSP-BF531/BF532/BF533/BF534/BF536/BF537/BF538

DXE2 Byte Count

......

......

BF539 Processors: Boot Stream Structur

e

See Flag Information

/

2-22 VisualDSP++ 4.0 Loader Manual

Page 59

Loader/Splitter for Blackfin Processors

Refer to Figure 2-19 and Table 2-4 for the flag’s bit descriptions.

Table 2-4. Flag Structure

Bit Field Description