Page 1

W4.0

Linker and Utilities Manual

Analog Devices, Inc.

One Technology Way

Norwood, Mass. 02062-9106

Revision 1.0, January 2005

Part Number

82-000420-03

a

Page 2

Copyright Information

© 2005 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written

consent from Analog Devices, Inc.

Printed in the USA.

Disclaimer

Analog Devices, Inc. reserves the right to change this product without

prior notice. Information furnished by Analog Devices is believed to be

accurate and reliable. However, no responsibility is assumed by Analog

Devices for its use; nor for any infringement of patents or other rights of

third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

Trademark and Service Mark Notice

The Analog Devices logo, the CROSSCORE logo, VisualDSP++,

Blackfin, SHARC, TigerSHARC, and EZ-KIT Lite are registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of

their respective owners.

Page 3

CONTENTS

PREFACE

Purpose of This Manual ................................................................. xix

Intended Audience ......................................................................... xix

Manual Contents ............................................................................ xx

What’s New in This Manual ........................................................... xxi

Technical or Customer Support ..................................................... xxii

Supported Processors ................................................................... xxiii

Product Information .................................................................... xxiv

MyAnalog.com ....................................................................... xxiv

Processor Product Information ................................................. xxv

Related Documents ................................................................ xxvi

Online Technical Documentation .......................................... xxvii

Accessing Documentation From VisualDSP++ ................... xxvii

Accessing Documentation From Windows ........................ xxviii

Accessing Documentation From the Web .......................... xxviii

Printed Manuals ..................................................................... xxix

VisualDSP++ Documentation Set ....................................... xxix

Hardware Tools Manuals .................................................... xxix

Processor Manuals .............................................................. xxix

VisualDSP++ 4.0 Linker and Utilities Manual iii

Page 4

CONTENTS

Data Sheets ....................................................................... xxix

Notation Conventions .................................................................. xxx

INTRODUCTION

Software Development Flow ......................................................... 1-2

Compiling and Assembling ........................................................... 1-3

Inputs – C/C++ and Assembly Sources .................................... 1-3

Input Section Directives in Assembly Code .............................. 1-4

Input Section Directives in C/C++ Source Files ........................ 1-5

Linking ........................................................................................ 1-7

Linker and Assembler Preprocessor .......................................... 1-8

Loading and Splitting ................................................................. 1-10

LINKER

Linker Operation .......................................................................... 2-2

Directing Linker Operation ..................................................... 2-3

Linking Process Rules .............................................................. 2-4

Linker Description File Overview ............................................ 2-5

Linking Environment ................................................................... 2-6

Project Builds ......................................................................... 2-6

Expert Linker ........................................................................ 2-14

Linker Warning and Error Messages ...................................... 2-15

Link Target Description .............................................................. 2-16

Representing Memory Architecture ........................................ 2-17

Specifying the Memory Map ................................................. 2-17

iv VisualDSP++ 4.0 Linker and Utilities Manual

Page 5

CONTENTS

Memory Usage and Default Memory Sections .................... 2-18

Default Memory Sections for SHARC Processors ............... 2-19

seg_rth .......................................................................... 2-19

seg_init ......................................................................... 2-20

seg_int_code ................................................................. 2-20

seg_pmco ...................................................................... 2-20

seg_pmda ...................................................................... 2-20

seg_argv ........................................................................ 2-20

seg_ctdm ...................................................................... 2-20

seg_dmda ...................................................................... 2-21

seg_heap ....................................................................... 2-21

seg_stak ........................................................................ 2-21

seg_vtbl ........................................................................ 2-21

Other Memory Sections ................................................ 2-21

Default Memory Sections for TigerSHARC Processors ....... 2-22

program ........................................................................ 2-23

data1 ............................................................................ 2-23

data2 ............................................................................ 2-23

mem_argv ..................................................................... 2-23

ctor ............................................................................... 2-23

heaptab ......................................................................... 2-24

bsz ................................................................................ 2-24

bsz_init ......................................................................... 2-24

M1Stack ....................................................................... 2-24

VisualDSP++ 4.0 Linker and Utilities Manual v

Page 6

CONTENTS

Default Memory Sections for Blackfin Processors .............. 2-25

M2Stack ....................................................................... 2-24

M1Heap ....................................................................... 2-24

vtbl .............................................................................. 2-25

program ....................................................................... 2-26

data1 ............................................................................ 2-26

cplb_code ..................................................................... 2-26

constdata ...................................................................... 2-27

cplb_data ..................................................................... 2-27

L1_DATA_A ................................................................ 2-27

L1_DATA_B ................................................................ 2-27

voldata ......................................................................... 2-27

argv .............................................................................. 2-28

ctor .............................................................................. 2-28

bsz ............................................................................... 2-28

bsz_init ........................................................................ 2-28

stack ............................................................................. 2-29

heap ............................................................................. 2-29

noncache_code ............................................................. 2-29

sdram0 ......................................................................... 2-29

vtbl .............................................................................. 2-29

Other Memory Sections ................................................ 2-30

Special “Table” Memory Sections ...................................... 2-30

.gdt .............................................................................. 2-30

vi VisualDSP++ 4.0 Linker and Utilities Manual

Page 7

CONTENTS

.gdtl .............................................................................. 2-30

.edt ............................................................................... 2-30

.edtl .............................................................................. 2-31

.cht ............................................................................... 2-31

.chtl .............................................................................. 2-31

.frt ................................................................................ 2-31

.frtl ............................................................................... 2-31

Memory Characteristics Overview ..................................... 2-31

SHARC Memory Characteristics ................................... 2-32

TigerSHARC Memory Characteristics ........................... 2-34

Blackfin Processor Memory Characteristics .................... 2-36

Linker MEMORY{} Command in .LDF File ...................... 2-38

Placing Code on the Target .................................................... 2-40

Specifying Two Buffers in Different Memory Segments ...... 2-44

Profile-Guided Optimization Support .................................... 2-45

Passing Arguments for Simulation or Emulation ..................... 2-46

Linker Command-Line Reference ................................................ 2-47

Linker Command-Line Syntax ............................................... 2-47

Command-Line Object Files ............................................. 2-48

Command-Line File Names ............................................... 2-49

Object File Types .............................................................. 2-51

Linker Command-Line Switches ............................................ 2-51

Linker Switch Summary and Descriptions .......................... 2-53

@filename ......................................................................... 2-55

VisualDSP++ 4.0 Linker and Utilities Manual vii

Page 8

CONTENTS

-Dprocessor ...................................................................... 2-55

-L path ............................................................................. 2-56

-M ................................................................................... 2-56

-MM ................................................................................ 2-56

-Map filename .................................................................. 2-56

-MDmacro[=def] .............................................................. 2-57

-MUDmacro .................................................................... 2-57

-S ..................................................................................... 2-57

-T filename ...................................................................... 2-58

-Wwarn [number] ............................................................ 2-58

-Wnumber[,number] ........................................................ 2-58

-e ..................................................................................... 2-59

-ek sectionName ............................................................... 2-59

-es sectionName ............................................................... 2-59

-ev ................................................................................... 2-59

-flags-meminit -opt1[,-opt2... .......................................... 2-60

-flags-pp-opt1[,-opt2...] ................................................... 2-60

-h[elp] .............................................................................. 2-60

-i|I directory ..................................................................... 2-60

-ip .................................................................................... 2-60

-jcs2l ................................................................................ 2-61

-jcs2l+ .............................................................................. 2-62

-keep symbolName ........................................................... 2-62

-meminit .......................................................................... 2-62

viii VisualDSP++ 4.0 Linker and Utilities Manual

Page 9

CONTENTS

-nonmemcheck ................................................................. 2-62

-o filename ....................................................................... 2-63

-od directory ..................................................................... 2-63

-pp ................................................................................... 2-63

-proc processor .................................................................. 2-63

-s ...................................................................................... 2-64

-save-temps ....................................................................... 2-64

-si-revision version ............................................................ 2-64

-sp .................................................................................... 2-65

-t ...................................................................................... 2-65

-v[erbose] ......................................................................... 2-65

-version ............................................................................ 2-66

-warnonce ......................................................................... 2-66

-xref filename .................................................................... 2-66

LINKER DESCRIPTION FILE

LDF File Overview ....................................................................... 3-3

Default LDFs .......................................................................... 3-3

Example 1 – Basic .LDF File for Blackfin Processors ................. 3-6

Memory Usage in Blackfin Processors .................................. 3-8

Example 2 – Basic .LDF File for TigerSHARC Processors ......... 3-9

Example 3 – Basic .LDF File for SHARC Processors ............... 3-10

Notes on Basic .LDF File Examples ........................................ 3-11

LDF Structure ............................................................................ 3-16

Command Scoping ................................................................ 3-17

VisualDSP++ 4.0 Linker and Utilities Manual ix

Page 10

CONTENTS

LDF Expressions ........................................................................ 3-18

LDF Keywords, Commands, and Operators ................................ 3-19

Miscellaneous LDF Keywords ................................................ 3-20

LDF Operators ........................................................................... 3-21

ABSOLUTE() Operator ........................................................ 3-21

ADDR() Operator ................................................................ 3-22

DEFINED() Operator .......................................................... 3-23

MEMORY_SIZEOF() Operator ............................................ 3-24

SIZEOF() Operator .............................................................. 3-24

Location Counter (.) ............................................................. 3-25

LDF Macros ............................................................................... 3-26

Built-In LDF Macros ............................................................ 3-27

User-Declared Macros ........................................................... 3-28

LDF Macros and Command-Line Interaction ........................ 3-28

LDF Commands ........................................................................ 3-29

ALIGN() .............................................................................. 3-30

ARCHITECTURE() ............................................................. 3-30

ELIMINATE() ...................................................................... 3-31

ELIMINATE_SECTIONS() ................................................. 3-32

INCLUDE() ......................................................................... 3-32

INPUT_SECTION_ALIGN() .............................................. 3-32

KEEP() ................................................................................. 3-33

KEEP_SECTIONS() ............................................................ 3-34

LINK_AGAINST() ............................................................... 3-34

x VisualDSP++ 4.0 Linker and Utilities Manual

Page 11

CONTENTS

MAP() .................................................................................. 3-35

MEMORY{} .......................................................................... 3-35

Segment Declarations ........................................................ 3-37

MPMEMORY{} .................................................................... 3-38

OVERLAY_GROUP{} ........................................................... 3-39

PACKING() .......................................................................... 3-39

Packing in SHARC Processors ........................................... 3-41

Overlay Packing Formats in SHARC Processors ............. 3-42

External Execution Packing in SHARC Processors .......... 3-43

PLIT{} .................................................................................. 3-45

PROCESSOR{} ..................................................................... 3-45

RESOLVE() .......................................................................... 3-47

SEARCH_DIR() ................................................................... 3-47

SECTIONS{} ........................................................................ 3-48

INPUT_SECTIONS() ...................................................... 3-51

expression ......................................................................... 3-52

FILL(hex number) ............................................................ 3-52

PLIT{plit_commands} ...................................................... 3-52

OVERLAY_INPUT{overlay_commands} ........................... 3-53

SHARED_MEMORY{} ......................................................... 3-55

EXPERT LINKER

Expert Linker Overview ................................................................ 4-2

Launching the Create LDF Wizard ................................................ 4-4

Step 1: Specifying Project Information ..................................... 4-5

VisualDSP++ 4.0 Linker and Utilities Manual xi

Page 12

CONTENTS

Step 2: Specifying System Information ..................................... 4-6

Step 3: Completing the LDF Wizard ....................................... 4-9

Expert Linker Window Overview ................................................ 4-10

Input Sections Pane .................................................................... 4-12

Input Sections Menu ............................................................. 4-12

Mapping an Input Section to an Output Section .................... 4-14

Viewing Icons and Colors ...................................................... 4-15

Sorting Objects ..................................................................... 4-17

Memory Map Pane ..................................................................... 4-19

Context Menu ...................................................................... 4-22

Tree View Memory Map Representation ................................ 4-24

Graphical View Memory Map Representation ........................ 4-25

Specifying Pre- and Post-Link Memory Map View ................. 4-31

Zooming In and Out on the Memory Map ............................ 4-32

Adding a Memory Segment ................................................... 4-33

Inserting a Gap Into a Memory Segment ............................... 4-35

Working With Overlays ........................................................ 4-36

Viewing Section Contents ..................................................... 4-38

Viewing Symbols .................................................................. 4-41

Profiling Object Sections ....................................................... 4-42

Adding Shared Memory Segments and Linking Object Files ... 4-46

Managing Object Properties ........................................................ 4-51

Managing General Global Properties ..................................... 4-52

Managing Processor Properties .............................................. 4-53

xii VisualDSP++ 4.0 Linker and Utilities Manual

Page 13

Managing PLIT Properties for Overlays ................................. 4-55

Managing Elimination Properties ........................................... 4-56

Managing Symbols Properties ................................................ 4-58

Managing Memory Segment Properties .................................. 4-61

Managing Output Section Properties ..................................... 4-62

Managing Packing Properties ................................................. 4-65

Managing Alignment and Fill Properties ................................ 4-67

Managing Overlay Properties ................................................. 4-69

Managing Stack and Heap in Processor Memory .................... 4-71

Managing Shared Memory Properties ..................................... 4-74

MEMORY OVERLAYS AND ADVANCED LDF

COMMANDS

Overview ...................................................................................... 5-2

Memory Management Using Overlays ........................................... 5-4

Introduction to Memory Overlays ............................................ 5-5

Overlay Managers .................................................................... 5-7

Breakpoints on Overlays ...................................................... 5-7

Memory Overlay Support ........................................................ 5-8

Example – Managing Two Overlays ....................................... 5-13

Linker-Generated Constants .................................................. 5-16

Overlay Word Sizes ................................................................ 5-16

Storing Overlay ID ................................................................ 5-19

Overlay Manager Function Summary ..................................... 5-20

Reducing Overlay Manager Overhead .................................... 5-20

VisualDSP++ 4.0 Linker and Utilities Manual xiii

Page 14

Using PLIT{} and Overlay Manager ....................................... 5-25

Inter-Overlay Calls ........................................................... 5-27

Inter-Processor Calls ......................................................... 5-27

Advanced LDF Commands ......................................................... 5-30

MPMEMORY{} .................................................................... 5-30

OVERLAY_GROUP{} .......................................................... 5-32

Ungrouped Overlay Execution .......................................... 5-33

Grouped Overlay Execution .............................................. 5-35

PLIT{} .................................................................................. 5-36

PLIT Syntax ..................................................................... 5-36

Command Evaluation and Setup ................................... 5-37

Overlay PLIT Requirements and PLIT Examples ............... 5-38

PLIT – Summary .............................................................. 5-40

SHARED_MEMORY{} ........................................................ 5-40

ARCHIVER

Archiver Guide ............................................................................. 6-2

Creating a Library From VisualDSP++ ..................................... 6-3

Making Archived Functions Usable ......................................... 6-3

Writing Archive Routines: Creating Entry Points ................. 6-4

Accessing Archived Functions From Your Code ................... 6-5

Archiver File Searches ......................................................... 6-6

Tagging an Archive With Version Information ..................... 6-6

Basic Version Information ............................................... 6-6

User-Defined Version Information .................................. 6-7

xiv VisualDSP++ 4.0 Linker and Utilities Manual

Page 15

Printing Version Information ........................................... 6-8

Removing Version Information From an Archive .............. 6-9

Checking Version Number .............................................. 6-9

Adding Text to Version Information .............................. 6-10

Archiver Command-Line Reference ............................................. 6-11

elfar Command Syntax .......................................................... 6-11

Archiver Parameters and Switches .......................................... 6-12

Command-Line Constraints .................................................. 6-14

Archiver Symbol Name Encryption ........................................ 6-15

MEMORY INITIALIZER

Memory Initializer Overview ......................................................... 7-2

Basic Operation of Memory Initializer ........................................... 7-3

Input and Output Files ............................................................ 7-3

Initialization Stream Structure ....................................................... 7-5

Run-Time Library Routine Basic Operation ................................... 7-6

Using the Memory Initializer ......................................................... 7-7

Preparing the Linker Description File (.LDF) ........................... 7-7

Preparing the Source Files ........................................................ 7-8

Invoking the Memory Initializer ............................................ 7-10

Invoking Memory Initializer from the VisualDSP++ IDDE 7-10

Invoking Memory Initializer from Command Line ............. 7-11

Invoking Memory Initializer from Linker’s Command Line 7-11

Invoking Memory Initializer from Compiler’s Command Line 7-11

Invoking Memory Initializer with Callback Executables ..... 7-11

VisualDSP++ 4.0 Linker and Utilities Manual xv

Page 16

Memory Initializer Command-Line Switches ............................... 7-13

-BeginInit Initsymbol ............................................................ 7-14

-h ......................................................................................... 7-15

-IgnoreSection Sectionname .................................................. 7-15

-Init Initcode.dxe .................................................................. 7-15

InputFile.dxe ........................................................................ 7-16

-NoAuto ............................................................................... 7-16

-NoErase ............................................................................... 7-16

-o Outputfile.dxe .................................................................. 7-17

-Section Sectionname ............................................................ 7-17

-SectDestination Sectionname ............................................... 7-17

-v ......................................................................................... 7-18

FILE FORMATS

Source Files .................................................................................. A-2

C/C++ Source Files ................................................................. A-2

Assembly Source Files (.ASM) ................................................. A-3

Assembly Initialization Data Files (.DAT) ................................ A-3

Header Files (.H) .................................................................... A-4

Linker Description Files (.LDF) .............................................. A-4

Linker Command-Line Files (.TXT) ........................................ A-5

Build Files .................................................................................... A-5

Assembler Object Files (.DOJ) ................................................ A-5

Library Files (.DLB) ................................................................ A-5

Linker Output Files (.DXE, .SM, and .OVL) ........................... A-6

xvi VisualDSP++ 4.0 Linker and Utilities Manual

Page 17

Memory Map Files (.XML) ..................................................... A-6

Loader Output Files in Intel Hex-32 Format (.LDR) ............... A-6

Splitter Output Files in ASCII Format (.LDR) ........................ A-8

Debugger Files ............................................................................. A-9

Format References ...................................................................... A-10

UTILITIES

elfdump – ELF File Dumper ........................................................ B-1

Disassembling a Library Member ............................................ B-3

Dumping Overlay Library Files ............................................... B-4

LDF PROGRAMMING EXAMPLES FOR TIGERSHARC

PROCESSORS

Linking a Single-Processor System ................................................ C-2

Linking Large Uninitialized or Zero-InitializedVariables ................ C-4

Linking an ADSP-TS101 MP Shared Memory System .................. C-6

Linking for Overlay Memory ...................................................... C-12

LDF PROGRAMMING EXAMPLES FOR SHARC

PROCESSORS

Linking a Single-Processor SHARC System ................................... D-2

Linking Large Uninitialized Variables ........................................... D-4

Linking for MP and Shared Memory ............................................ D-6

Reflective Semaphores .......................................................... D-11

Linking for Overlay Memory ...................................................... D-13

LDF PROGRAMMING EXAMPLES FOR BLACKFIN

VisualDSP++ 4.0 Linker and Utilities Manual xvii

Page 18

PROCESSORS

Linking for a Single-Processor System ........................................... E-2

Linking Large Uninitialized or Zero-initialized Variables ................ E-4

Linking for Assembly Source File .................................................. E-6

Linking for C Source File – Example 1 .......................................... E-8

Linking for Complex C Source File – Example 2 ......................... E-11

Linking for Overlay Memory ...................................................... E-17

INDEX

xviii VisualDSP++ 4.0 Linker and Utilities Manual

Page 19

PREFACE

Thank you for purchasing Analog Devices development software for digital signal processors (DSPs).

Purpose of This Manual

The VisualDSP++ 4.0 Linker and Utilities Manual contains information

about the linker and utilities programs for 16-bit fixed-point Blackfin®

(ADSP-BFxxx) processors, and 32-bit (floating-point and fixed-point)

TigerSHARC® (ADSP-TSxxx) and SHARC® (ADSP-21xxx) processors

which set a new standard of performance for digital signal processors,

combining multiple computation units for floating-point and fixed-point

processing as well as wide word width.

This manual provides information on the linking process and describes

the syntax for the linker’s command language—a scripting language that

the linker reads from the linker description file. The manual leads you

through using the linker, archiver, and utilities to produce DSP programs

and provides reference information on the file utility software.

Intended Audience

The primary audience for this manual is a programmer who is familiar

with Analog Devices processors. This manual assumes that the audience

has a working knowledge of the appropriate processor architecture and

instruction set. Programmers who are unfamiliar with Analog Devices

VisualDSP++ 4.0 Linker and Utilities Manual xix

Page 20

Manual Contents

processors can use this manual, but should supplement it with other texts

(such as the appropriate hardware reference and programming reference

manuals) that describe your target architecture.

Manual Contents

The manual contains:

• Chapter 1, “Introduction”

This chapter provides an overview of the linker and utilities.

• Chapter 2, “Linker”

This chapter describes how to combine object files into reusable

library files to link routines referenced by other object files.

• Chapter 3, “Linker Description File”

This chapter describes how to write an .LDF file to define the

target.

• Chapter 4, “Expert Linker”

This chapter describes Expert Linker, which is an interactive

graphical tool to set up and map processor memory.

• Chapter 5, “Memory Overlays and Advanced LDF Commands”

This chapter describes how overlays and advanced LDF commands

are used for memory management.

• Chapter 6 “Archiver”

This chapter describes the

object files into library files, which serve as reusable resources for

code development.

• Chapter 7 “Memory Initializer”

This chapter describes the Memory Initializer utility that is used to

generate a single initialization stream and save it in a section in the

output executable file.

xx VisualDSP++ 4.0 Linker and Utilities Manual

elfar archiver utility used to combine

Page 21

Preface

• Appendix A, “File Formats”

This appendix lists and describes the file formats that the development tools use as inputs or produce as outputs.

• Appendix B, “Utilities”

This appendix describes the utilities that provide legacy and file

conversion support.

• Appendix C, “LDF Programming Examples for TigerSHARC Pro-

cessors”

This appendix provides code examples of .LDF files used with

TigerSHARC processors.

• Appendix D, “LDF Programming Examples for SHARC Proces-

sors”

This appendix provides code examples of .LDF files used with

SHARC processors.

• Appendix E, “LDF Programming Examples for Blackfin Proces-

sors”

This appendix provides code examples of .LDF files used with

Blackfin processors.

What’s New in This Manual

This is a new manual that documents linking support for all currently

available Analog Devices 32-bit floating-point and fixed-point SHARC

and TigerSHARC

processors.

Loader/splitter information is now available in a separate Loader manual.

Refer to VisualDSP++ 4.0 Product Bulletin for information on all new and

updated features and other release information.

VisualDSP++ 4.0 Linker and Utilities Manual xxi

processors, as well as 16-bit fixed-point Blackfin

Page 22

Technical or Customer Support

Technical or Customer Support

You can reach Analog Devices, Inc. Customer Support in the following

ways:

• Visit the Embedded Processing and DSP products Web site at

http://www.analog.com/processors/technicalSupport

• E-mail tools questions to

dsptools.support@analog.com

• E-mail processor questions to

dsp.support@analog.com

• Phone questions to 1-800-ANALOGD

• Contact your Analog Devices, Inc. local sales office or authorized

distributor

• Send questions by mail to:

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

USA

xxii VisualDSP++ 4.0 Linker and Utilities Manual

Page 23

Preface

Supported Processors

The following is the list of Analog Devices, Inc. processors supported in

VisualDSP++ 4.0.

TigerSHARC (ADSP-TSxxx) Processors

The name “TigerSHARC” refers to a family of floating-point and

fixed-point [8-bit, 16-bit, and 32-bit] processors. VisualDSP++ currently

supports the following TigerSHARC processors:

ADSP-TS101 ADSP-TS201 ADSP-TS202 ADSP-TS203

SHARC (ADSP-21xxx) Processors

The name “SHARC” refers to a family of high-performance, 32-bit,

floating-point processors that can be used in speech, sound, graphics, and

imaging applications. VisualDSP++ currently supports the following

SHARC processors:

ADSP-21020 ADSP-21060 ADSP-21061 ADSP-21062

ADSP-21065L ADSP-21160 ADSP-21161 ADSP-21261

ADSP-21262 ADSP-21266 ADSP-21267 ADSP-21363

ADSP-21364 ADSP-21365 ADSP-21366 ADSP-21367

ADSP-21368 ADSP-21369

VisualDSP++ 4.0 Linker and Utilities Manual xxiii

Page 24

Product Information

Blackfin (ADSP-BFxxx) Processors

The name “Blackfin” refers to a family of 16-bit, embedded processors.

VisualDSP++ currently supports the following Blackfin processors:

ADSP-BF531 ADSP-BF532 (formerly ADSP-21532)

ADSP-BF533 ADSP-BF535 (formerly ADSP-21535)

ADSP-BF536 ADSP-BF537

ADSP-BF538 ADSP-BF539

ADSP-BF561 ADSP-BF566

AD6532

Product Information

You can obtain product information from the Analog Devices Web site,

from the product CD-ROM, or from the printed publications (manuals).

Analog Devices is online at www.analog.com. Our Web site provides information about a broad range of products—analog integrated circuits,

amplifiers, converters, and digital signal processors.

MyAnalog.com

MyAnalog.com is a free feature of the Analog Devices Web site that allows

customization of a Web page to display only the latest information on

products you are interested in. You can also choose to receive weekly

e-mail notifications containing updates to the Web pages that meet your

interests. MyAnalog.com provides access to books, application notes, data

sheets, code examples, and more.

xxiv VisualDSP++ 4.0 Linker and Utilities Manual

Page 25

Preface

Registration

Visit www.myanalog.com to sign up. Click Register to use MyAnalog.com.

Registration takes about five minutes and serves as a means to select the

information you want to receive.

If you are already a registered user, just log on. Your user name is your

e-mail address.

Processor Product Information

For information on embedded processors and DSPs, visit our Web site at

www.analog.com/processors, which provides access to technical publica-

tions, data sheets, application notes, product overviews, and product

announcements.

You may also obtain additional information about Analog Devices and its

products in any of the following ways.

• E-mail questions or requests for information to

dsp.support@analog.com

• Fax questions or requests for information to

1-781-461-3010 (North America)

089/76 903-557 (Europe)

• Access the FTP Web site at

ftp ftp.analog.com or ftp 137.71.23.21

ftp://ftp.analog.com

VisualDSP++ 4.0 Linker and Utilities Manual xxv

Page 26

Product Information

Related Documents

For information on product related development software, see these

publications:

• VisualDSP++ 4.0 Getting Started Guide

• VisualDSP++ 4.0 User’s Guide

• VisualDSP++ 4.0 C/C++ Compiler and Library Manual for SHARC

Processors

• VisualDSP++ 4.0 C/C++ Compiler and Library Manual for

TigerSHARC Processors

• VisualDSP++ 4.0 C/C++ Compiler and Library Manual for Blackfin

Processors

• VisualDSP++ 4.0 Assembler and Preprocessor Manual

• VisualDSP++ 4.0 Linker and Utilities Manual

• VisualDSP++ 4.0 Product Release Bulletin

• VisualDSP++ Kernel (VDK) User’s Guide

• Quick Installation Reference Card

For hardware information, refer to your processors’s hardware reference,

programming reference, or data sheet. All documentation is available

online. Most documentation is available in printed form.

Visit the Technical Library Web site to access all processor and tools manuals and data sheets:

http://www.analog.com/processors/resources/technicalLibrary

xxvi VisualDSP++ 4.0 Linker and Utilities Manual

Page 27

Preface

Online Technical Documentation

Online documentation includes the VisualDSP++ Help system, software

tools manuals, hardware tools manuals, processor manuals, Dinkum

Abridged C++ library, and Flexible License Manager (FlexLM) network

license manager software documentation. You can easily search across the

entire VisualDSP++ documentation set for any topic of interest using the

Search function of VisualDSP++ Help system. For easy printing, supplementary .PDF files of most manuals are also provided.

Each documentation file type is described as follows.

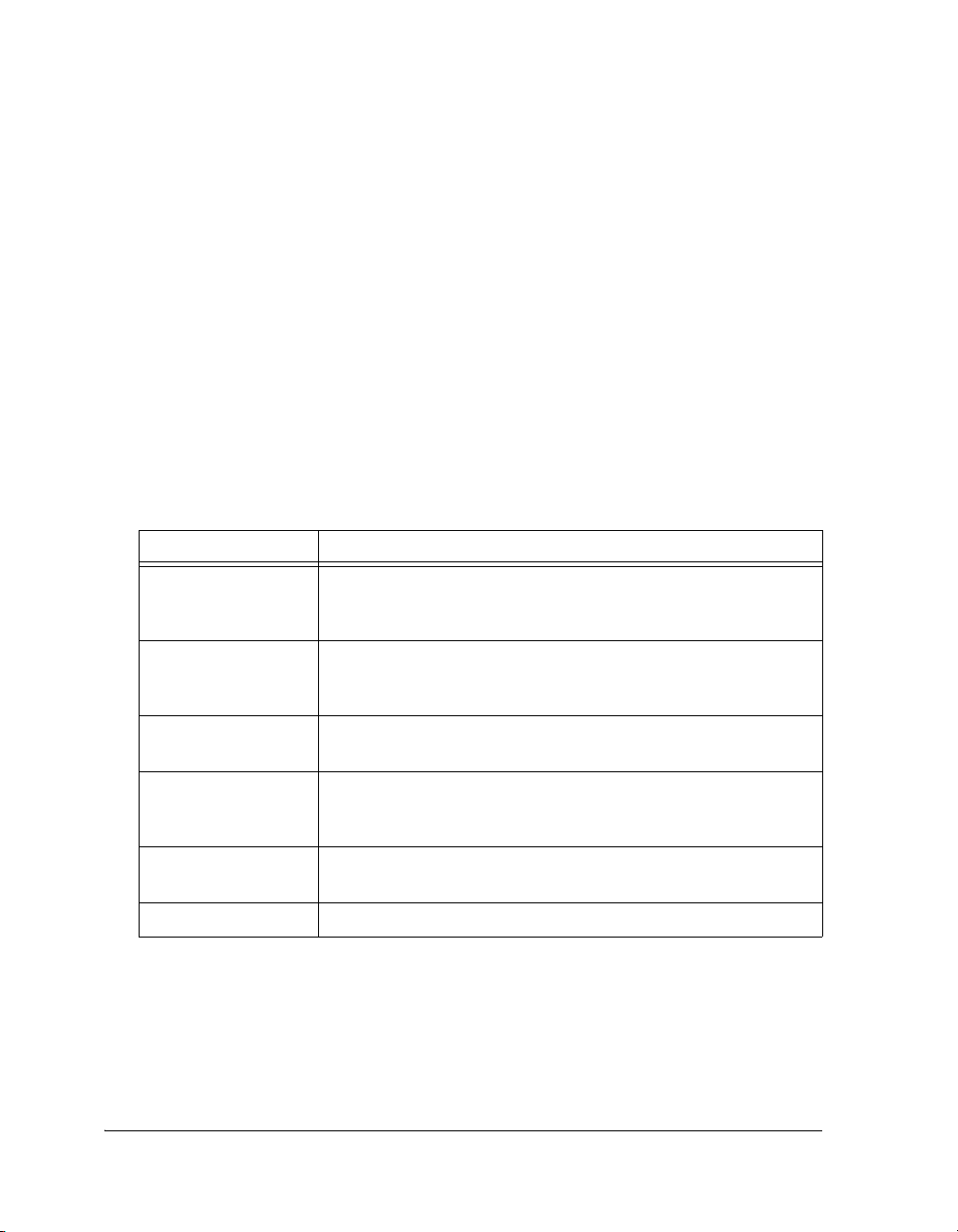

File Description

.CHM Help system files and manuals in Help format

.HTM or

.HTML

.PDF VisualDSP++ and processor manuals in Portable Documentation Format (PDF).

Dinkum Abridged C++ library and FlexLM network license manager software documentation. Viewing and printing the .HTML files requires a browser, such as

Internet Explorer 4.0 (or higher).

Viewing and printing the .PDF files requires a PDF reader, such as Adobe Acrobat

Reader (4.0 or higher).

Access the online documentation from the VisualDSP++ environment,

Windows® Explorer, or the Analog Devices Web site.

Accessing Documentation From VisualDSP++

From the VisualDSP++ environment:

• Access VisualDSP++ online Help from the Help menu’s Contents,

Search, and Index commands.

• Open online Help from context-sensitive user interface items (toolbar buttons, menu commands, and windows).

VisualDSP++ 4.0 Linker and Utilities Manual xxvii

Page 28

Product Information

Accessing Documentation From Windows

In addition to any shortcuts you may have constructed, there are many

ways to open VisualDSP++ online Help or the supplementary documentation from Windows.

Help system files (.CHM) are located in the Help folder of VisualDSP++

environment. The .PDF files are located in the Docs folder of your

VisualDSP++ installation CD-ROM. The Docs folder also contains the

Dinkum Abridged C++ library and the FlexLM network license manager

software documentation.

Using Windows Explorer

• Double-click the vdsp-help.chm file, which is the master Help system, to access all the other .CHM files.

• Open your VisualDSP++ installation CD-ROM and double-click

any file that is part of the VisualDSP++ documentation set.

Using the Windows Start Button

• Access VisualDSP++ online Help by clicking the Start button and

choosing Programs, Analog Devices, VisualDSP++, and

VisualDSP++ Documentation.

Accessing Documentation From the Web

Download manuals in PDF format at the following Web site:

http://www.analog.com/processors/resources/technicalLibrary/manuals

Select a processor family and book title. Download archive (.ZIP) files, one

for each manual. Use any archive management software, such as WinZip,

to decompress downloaded files.

xxviii VisualDSP++ 4.0 Linker and Utilities Manual

Page 29

Preface

Printed Manuals

For general questions regarding literature ordering, call the Literature

Center at 1-800-ANALOGD (1-800-262-5643) and follow the prompts.

VisualDSP++ Documentation Set

To purchase VisualDSP++ manuals, call 1-603-883-2430. The manuals

may be purchased only as a kit.

If you do not have an account with Analog Devices, you are referred to

Analog Devices distributors. For information on our distributors, log onto

http://www.analog.com/salesdir/continent.asp.

Hardware Tools Manuals

To purchase EZ-KIT Lite® and In-Circuit Emulator (ICE) manuals, call

1-603-883-2430. The manuals may be ordered by title or by product

number located on the back cover of each manual.

Processor Manuals

Hardware reference and instruction set reference manuals may be ordered

through the Literature Center at 1-800-ANALOGD (1-800-262-5643),

or downloaded from the Analog Devices Web site. Manuals may be

ordered by title or by product number located on the back cover of each

manual.

Data Sheets

All data sheets (preliminary and production) may be downloaded from the

Analog Devices Web site. Only production (final) data sheets (Rev. 0, A,

B, C, and so on) can be obtained from the Literature Center at

1-800-ANALOGD (1-800-262-5643); they also can be downloaded from

the Web site.

VisualDSP++ 4.0 Linker and Utilities Manual xxix

Page 30

Notation Conventions

To have a data sheet faxed to you, call the Analog Devices Faxback System

at 1-800-446-6212. Follow the prompts and a list of data sheet code

numbers will be faxed to you. If the data sheet you want is not listed,

check for it on the Web site.

Notation Conventions

Text conventions used in this manual are identified and described as

follows.

L

Example Description

Close command

(File menu)

{this | that} Alternative required items in syntax descriptions appear within curly

[this | that] Optional items in syntax descriptions appear within brackets and sepa-

[this,…] Optional item lists in syntax descriptions appear within brackets

.SECTION Commands, directives, keywords, and feature names are in text with

filename Non-keyword placeholders appear in text with italic style format.

appear throughout this document.

Titles in reference sections indicate the location of an item within the

VisualDSP++ environment’s menu system (for example, the Close

command appears on the File menu).

brackets and separated by vertical bars; read the example as this or

that. One or the other is required.

rated by vertical bars; read the example as an optional this or that.

delimited by commas and terminated with an ellipse; read the example

as an optional comma-separated list of

letter gothic font.

this.

Additional conventions, which apply only to specific chapters, may

xxx VisualDSP++ 4.0 Linker and Utilities Manual

Page 31

Example Description

Note: For correct operation, ...

A Note provides supplementary information on a related topic. In the

L

a

[

online version of this book, the word Note appears instead of this

symbol.

Caution: Incorrect device operation may result if ...

Caution: Device damage may result if ...

A Caution identifies conditions or inappropriate usage of the product

that could lead to undesirable results or product damage. In the online

version of this book, the word Caution appears instead of this symbol.

Warn in g: Injury to device users may result if ...

A Warning identifies conditions or inappropriate usage of the product

that could lead to conditions that are potentially hazardous for devices

users. In the online version of this book, the word Wa rnin g appears

instead of this symbol.

Preface

VisualDSP++ 4.0 Linker and Utilities Manual xxxi

Page 32

Notation Conventions

xxxii VisualDSP++ 4.0 Linker and Utilities Manual

Page 33

1 INTRODUCTION

This chapter provides an overview of VisualDSP++ development tools and

their use in the [DSP] project development process.

L

This chapter includes:

The code examples in this manual have been compiled using

VisualDSP++ 4.0. The examples compiled with other versions of

VisualDSP++ may result in build errors or different output

although the highlighted algorithms stand and should continue to

stand in future releases of VisualDSP++.

• “Software Development Flow” on page 1-2

Shows how linking, loading, and splitting fit into the project development process.

• “Compiling and Assembling” on page 1-3

Shows how compiling and assembling the code fits into the project

development process.

• “Linking” on page 1-7

Shows how linking fits into the project development process.

• “Loading and Splitting” on page 1-10

Shows how loading and splitting fit into the project development

process.

VisualDSP++ 4.0 Linker and Utilities Manual 1-1

Page 34

Software Development Flow

Software Development Flow

The majority of this manual describes linking, a critical stage in the

program development process for embedded applications.

The linker tool (linker.exe) consumes object and library files to produce

executable files, which can be loaded onto a simulator or target processor.

The linker also produces map files and other output that contain information used by the debugger. Debug information is embedded in the

executable file.

After running the linker, you test the output with a simulator or emulator.

Refer to the VisualDSP++ 4.0 User’s Guide and online Help for information about debugging.

Finally, you process the debugged executable file(s) through the loader or

splitter to create output for use on the actual processor. The output file

may reside on another processor (host) or may be burned into a PROM.

The VisualDSP++ 4.0 Loader Manual describes loader/splitter functionality for the target processors.

The processor software development flow can be split into three phases:

1. Compiling and Assembling – Input source files C (.C), C++ (.CPP),

and assembly (.ASM) yield object files (.DOJ)

2. Linking – Under the direction of the Linker Description File

.LDF), a linker command line, and VisualDSP++ Project Options

(

dialog box settings, the linker utility consumes object files (.DOJ)

to yield an executable (.DXE) file. If specified, shared memory (.SM)

and overlay (

3. Loading or Splitting – The executable (.DXE) file, as well as shared

memory (.SM) and overlay (.OVL) files, are processed to yield

output file(s). For TigerSHARC and Blackfin processors, these are

boot-loadable (LDR) files or non-bootable PROM image files, which

execute from the processor’s external memory.

1-2 VisualDSP++ 4.0 Linker and Utilities Manual

.OVL) files are also produced.

Page 35

Introduction

Compiling and Assembling

The process starts with source files written in C, C++, or assembly. The

compiler (or a code developer who writes assembly code) organizes each

distinct sequence of instructions or data into named sections, which

become the main components acted upon by the linker.

Inputs – C/C++ and Assembly Sources

The first step towards producing an executable file is to compile or assemble C, C++, or assembly source files into object files. The VisualDSP++

development software assigns a .DOJ extension to object files (Figure 1-1).

Figure 1-1. Compiling and Assembling

Object files produced by the compiler (via the assembler) and by the

assembler itself consist of input sections. Each input section contains

a particular type of compiled/assembled source code. For example, an

input section may consist of program opcodes or data, such as variables

of various widths.

Some input sections may contain information to enable source-level

debugging and other VisualDSP++ features. The linker maps each input

section (via a corresponding output section in the executable) to a memory

segment, a contiguous range of memory addresses on the target system.

VisualDSP++ 4.0 Linker and Utilities Manual 1-3

Page 36

Compiling and Assembling

Each input section in the .LDF file requires a unique name, as specified in

the source code. Depending on whether the source is C, C++, or assembly,

different conventions are used to name an input section (see Chapter 3,

“Linker Description File”).

Input Section Directives in Assembly Code

A .SECTION directive defines a section in assembly source. This directive

must precede its code or data.

SHARC Code Example

.SECTION/DM asmdata; // Declares section asmdata

.VAR input[3]; // Declares data buffer in asmdata

.SECTION/PM asmcode; // Declares section asmcode

R0 = 0x1234; // Three lines of code in asmcode

R1 = 0x4567;

R3 = R1 + R2;

In this example, the /dm asmdata input section contains the array input,

and the /pm asmcode input section contains the three line of code.

Blackfin Code Example

.SECTION Library_Code_Space; /* Section Directive */

.global _abs;

_abs:

R0 = ABS R0; /* Take absolute value of input */

RTS;

_abc.end

In this example, the assembler places the global symbol/label _abs and the

code after the label into the input section Library_Code_Space, as it processes this file into object code.

1-4 VisualDSP++ 4.0 Linker and Utilities Manual

Page 37

Introduction

Input Section Directives in C/C++ Source Files

Typically, C/C++ code does not specify an input section name, so the

compiler uses a default name. By default, the input section names program

(for code) and data1 (for data) are used. Additional input section names

are defined in .LDF files (see “Specifying the Memory Map” on page 2-17

for more information on memory mapping).

In C/C++ source files, you can use the optional section(“name”) C language extension to define sections.

Example 1

While processing the following code, the compiler stores the temp variable

in the ext_data input section of the .DOJ file and also stores the code generated from func1 in an input section named extern.

...

section ("ext_data") int temp; /* Section directive */

section ("extern") void func1(void) { int x = 1; }

...

Example 2

In the following example, section ("extern") is optional. Note the new

function (funct2) does not require section ("extern"). For more information on LDF sections, refer to “Specifying the Memory Map” on

page 2-17.

section ("ext_data") int temp;

section ("extern") void func1(void) { int x = 1; }

int func2(void) { return 13; } /* New */

VisualDSP++ 4.0 Linker and Utilities Manual 1-5

Page 38

Compiling and Assembling

For information on compiler default section names, refer to the

VisualDSP++ 4.0 C/C++ Compiler and Library Manual for appropriate

target processors and “Placing Code on the Target” on page 2-40.

L

Identify the difference between input section names, output section names, and memory segment names because these types of

names appear in the .LDF file. Usually, default names are used.

However, in some situations you may want to use non-default

names. One such situation is when various functions or variables

(in the same source file) are to be placed into different memory

segments.

1-6 VisualDSP++ 4.0 Linker and Utilities Manual

Page 39

Introduction

Linking

After you have (compiled and) assembled source files into object files, use

the linker to combine the object files into an executable file. By default,

the development software gives executable files a .DXE extension

(Figure 1-2).

Figure 1-2. Linking Diagram

Linking enables your code to run efficiently in the target environment.

Linking is described in detail in Chapter 2, “Linker”.

L

VisualDSP++ 4.0 Linker and Utilities Manual 1-7

When developing a new project, use the Expert Linker to generate

the project’s

information.

.LDF file. See Chapter 4, “Expert Linker” for more

Page 40

Linking

Linker and Assembler Preprocessor

The linker and assembler preprocessor program (pp.exe) evaluates and

processes preprocessor commands in source files. With these commands,

you direct the preprocessor to define macros and symbolic constants,

include header files, test for errors, and control conditional assembly and

compilation.

The pp preprocessor is run by the assembler or linker from the operating

system’s command line or within the VisualDSP++ environment. These

tools accept and pass this command information to the preprocessor. The

preprocessor can also operate from the command line using its own command-line switches.

Assembler/Linker Preprocessor treats the character “.” as part of an

identifier

The preprocessor matches the assembler which uses “.” as part of assembler directives and as a legal character in labels. This behavior does create a

possible problem for users that have written preprocessor macros that rely

on identifiers to break when encountering the “.” character, usually seen

when processing register names. For example,

#define Loadd(reg, val) \

reg.l = val;\

reg.h = val;

The above example would not work in VisualDSP++ 4.0 becauseVisualDSP++ 4.0 does not provide any replacement since

reg is not parsed as a

separate identifier. The macro has to be rewritten using the operator ##

such as:

#define Loadd(reg, val)\

reg ## .l = val;\

reg ## .h = val;

1-8 VisualDSP++ 4.0 Linker and Utilities Manual

Page 41

Introduction

L

L

The preprocessor supports ANSI C standard preprocessing with

extensions but differs from the ANSI C standard preprocessor in

several ways. For more information on the pp preprocessor, see the

VisualDSP++ 4.0 Assembler and Preprocessor Manual.

The compiler has it own preprocessor that allows you to use preprocessor commands within your C/C++ source. The compiler

preprocessor automatically runs before the compiler. For more

information, see the VisualDSP++ 4.0 C/C++ Compiler and Library

Manual for the appropriate target archtecture.

VisualDSP++ 4.0 Linker and Utilities Manual 1-9

Page 42

Loading and Splitting

Loading and Splitting

After debugging the .DXE file, you process it through a loader or splitter to

create output files used by the actual processor. The file(s) may reside on

another processor (host) or may be burned into a PROM.

For more information, refer to the VisualDSP++ 4.0 Loader Manual

which provides detailed descriptions of the processes and options used to

generate boot-loadable .LDR (loader) files for the approprate target processors. This manual also describes the splitting utility, which (when used)

creates the non-bootloadable files that execute from the processor’s external memory.

In general:

• The SHARC ADSP-2106x/ADSP-21160 processors use the loader

(elfloader.exe) to yield a boot-loadable image (.LDR file), which

resides in memory external to the processor (PROM or host processor). Use the splitter utility (elfspl21k.exe) to generate

non-bootable PROM image files, which execute from the processor’s external memory (often used with the ADSP-21065L

processors).

• The SHARC ADSP-2116x/2126x/2136x processors use the loader

(elfloader.exe) to yield a boot-loadable image (.LDR file), which

transported to (and run from) processor memory. To make a loadable file, the loader processes data from a boot-kernel file (.

and one or more other executable files (.

DXE).

DXE)

• The TigerSHARC processors use the loader (elfloader.exe) to

yield a boot-loadable image (

.LDR file), which transported to (and

run from) processor memory. To make a loadable file, the loader

processes data from a boot-kernel file (.

executable files (.

DXE).

DXE) and one or more other

1-10 VisualDSP++ 4.0 Linker and Utilities Manual

Page 43

Introduction

• Both TigerSHARC and SHARC processors use the splitter utility

(elfspl21k.exe) to generate non-bootable PROM image files,

which execute from the processor’s external memory.

• The Blackfin processors use the loader (elfloader.exe) to yield a

boot-loadable image (.LDR file), which resides in memory external

to the processor (PROM or host processor. To make a loadable file,

the loader processes data from a boot-kernel file (.DXE) and one or

more other executable files (.DXE).

Figure 1-3 shows a simple application of the loader. In this example, the

loader’s input is a single executable (.DXE) file. The loader can accommodate up to two .DXE files as input plus one boot kernel file (.DXE).

Figure 1-3. Loading Diagram

VisualDSP++ 4.0 Linker and Utilities Manual 1-11

Page 44

Loading and Splitting

For example, when a TigerSHARC processor is reset, the boot kernel portion of the image is transferred to the processor’s core. Then, the

instruction and data portion of the image are loaded into the processor’s

internal RAM (as shown in Figure 1-4) by the boot kernel.

Figure 1-4. Booting from a Bootloadable (.LDR) File

VisualDSP++ includes boot kernel files (.DXE), which are automatically

used when you run the loader. You can also customize boot kernel source

files (included with VisualDSP++) by modifying and rebuilding them.

Figure 1-5 shows how multiple input files—in this case, two executable

(.DXE) files, a shared memory (.SM) file, and overlay (.OVL) files—are

consumed by the loader to create a single image file (

illustrate the generation of a loader file for a multiprocessor architecture.

L

This example has two executable files that share memory. Overlays are also

included. The resulting output is a compilation of all the inputs.

1-12 VisualDSP++ 4.0 Linker and Utilities Manual

The .SM and .OVL files must reside in the same directory that contains the input

your system does not use shared memory or overlays, .SM and .OVL

files are not required.

.DXE file(s) or in the current working directory. If

.LDR). This example

Page 45

Introduction

Figure 1-5. Input Files for a Multiprocessor System

VisualDSP++ 4.0 Linker and Utilities Manual 1-13

Page 46

Loading and Splitting

1-14 VisualDSP++ 4.0 Linker and Utilities Manual

Page 47

2LINKER

Linking assigns code and data to processor memory. For a simple single

processor architecture, a single .DXE file is generated. A single invocation

of the linker may create multiple executable (.DXE) files for multiprocessor

(MP) architectures. Linking can also produce a shared memory (.SM) file

for an MP system. A large executable file can be split into a smaller executable file and overlays (.OVL) files, which contain code that is called in

(swapped into internal processor memory) as needed. The linker

(linker.exe) performs this task.

You can run the linker from a command line or from the VisualDSP++

Integrated Development and Debugging Environment (IDDE).

You can load the link output into the VisualDSP++ debugger for simulation, testing, and profiling.

This chapter includes:

• “Linker Operation” on page 2-2

• “Linking Environment” on page 2-6

• “Link Target Description” on page 2-16

• “Linker Command-Line Reference” on page 2-47

VisualDSP++ 4.0 Linker and Utilities Manual 2-1

Page 48

Linker Operation

Linker Operation

Figure 2-1 illustrates a basic linking operation. The figure shows several

object (.DOJ) files being linked into a single executable (.DXE) file. The

Linker Description File (.LDF) directs the linking process.

Figure 2-1. Linking Object Files to Produce an Executable File

L

In a multiprocessor system, a .DXE file for each processor is generated. For

example, for a two-processor system, you must generate two

The processors in a multiprocessor architecture may share memory. When

directed by statements in the

ory (.SM) executable file, whose code is used by multiple processors.

Overlay files, another linker output, support applications that require

more program instructions and data than the processor’s internal memory

can accommodate. Refer to “Memory Management Using Overlays” on

page 5-4 for more information.

2-2 VisualDSP++ 4.0 Linker and Utilities Manual

When developing a new project, use the Expert Linker to generate

the project’s .LDF file. See Chapter 4, “Expert Linker” for more

information.

.DXE files.

.LDF file, the linker produce a shared mem-

Page 49

Linker

Similar to object files, executable files are partitioned into output sections

with unique names. Output sections are defined by the Executable and

Linking Format (ELF) file standard to which VisualDSP++ conforms.

L

The executable file(s) (.DXE) and auxiliary files (.SM and .OVL) are not

loaded into the processor or burned onto an EPROM. These files are used

to debug the system.

The executable’s input section names and output section names

occupy different namespaces. Because the namespaces are independent, the same section names may be used. The linker uses input

section names as labels to locate corresponding input sections

within object files.

Directing Linker Operation

Linker operations are directed by these options and commands:

• Linker (linker.exe) command-line switches (options). Refer to

“Linker Command-Line Reference” on page 2-47.

• Settings (options) on the Link page of the Project Options dialog

box. See “Project Builds” on page 2-6.

• LDF commands. Refer to “LDF Commands” on page 3-29 for a

detailed description.

Linker options control how the linker processes object files and library

files. These options specify various criteria such as search directories, map

file output, and dead code elimination. You select linker options via linker

command-line switches or by settings on the Link page of the Project

Options dialog box within the VisualDSP++ environment.

LDF commands in a Linker Description File (.LDF) define the target

memory map and the placement of program sections within processor

memory. The text of these commands provides the information needed to

link your code.

VisualDSP++ 4.0 Linker and Utilities Manual 2-3

Page 50

Linker Operation

L

Using directives in the .LDF file, the linker:

The VisualDSP++ Project window displays the .LDF file as a source

file, though the file provides linker command input.

• Reads input sections in the object files and maps them to output

sections in the executable file. More than one input section may be

placed in an output section.

• Maps each output section in the executable to a memory segment,

a contiguous range of memory addresses on the target processor.

More than one output section may be placed in a single memory

segment.

Linking Process Rules

The linking process observes these rules:

• Each source file produces one object file.

• Source files may specify one or more input sections as destinations

for compiled/assembled object(s).

• The compiler and assembler produce object code with labels that

direct one or more portions to particular output sections.

• As directed by the .LDF file, the linker maps each input section

in the object code to an output section in the

• As directed by the .LDF file, the linker maps each output section

to a memory segment.

• Each input section may contain multiple code items, but a code

item may appear in one input section only.

• More than one input section may be placed in an output section.

• Each memory segment must have a specified width.

2-4 VisualDSP++ 4.0 Linker and Utilities Manual

.DXE file.

Page 51

• Contiguous addresses on different-width hardware must reside in

different memory segments.

• More than one output section may map to a memory segment if

the output sections fit completely within the memory segment.

Linker Description File Overview

Whether you are linking C/C++ functions or assembly routines, the mechanism is the same. After converting the source files into object files, the

linker uses directives in an

able (.DXE) file, which may be loaded into a simulator for testing.

.LDF file to combine the objects into an execut-

Linker

L

Each project must include one .LDF file that specifies the linking process

by defining the target memory and mapping the code and data into that

memory. You can write your own .LDF file, or you can modify an existing

file; modification is often the easier alternative when there are few changes

in your system’s hardware or software. VisualDSP++ provides an .LDF file

that supports the default mapping of each processor type.

L

Similar to an object (.DOJ) file, an executable (.DXE) file consists of

different segments, called output sections. Input section names are independent of output section names. Because they exist in different

namespaces, input section names can be the same as output section names.

Refer to Chapter 3, “Linker Description File” for further information.

Executable file structure conforms to the Executable and Linkable

Format (ELF) standard.

When developing a new project, use the Expert Linker to generate

the project’s .LDF file, as described in Chapter 4, “Expert Linker”.

VisualDSP++ 4.0 Linker and Utilities Manual 2-5

Page 52

Linking Environment

Linking Environment

The linking environment refers to Windows command-prompt windows

and the VisualDSP++ IDDE. At a minimum, run development tools (such

as the linker) via a command line and view output in standard output.

VisualDSP++ provides an environment that simplifies the processor program build process. From VisualDSP++, you specify build options from

the Project Options dialog box and modify files, including the Linker

Description File (.LDF). The Project Options dialog box’s Type option

allows you to choose whether to build a library (.DLB) file, an executable

(.DXE) file, or an image file (.LDR or others). Error and warning messages

appear in the Output window.

Project Builds

The linker runs from an operating system command line, issued from the

VisualDSP++ IDDE, or a command prompt window. Figure 2-2 shows

the VisualDSP++ environment with the Project window and an .LDF file

open in an Editor window.

The VisualDSP++ IDDE provides an intuitive interface for processor programming. When you open VisualDSP++, a work area contains everything

needed to build, manage, and debug a DSP project. You can easily create

or edit an .

on the target.

L

2-6 VisualDSP++ 4.0 Linker and Utilities Manual

LDF file, which maps code or data to specific memory segments

For information about the VisualDSP++ environment, refer to the

VisualDSP++ User’s Guide for the appropriate target architecture or

online Help. Online Help provides powerful search capabilities. To

obtain information on a code item, parameter, or error, select text

in an VisualDSP++ IDDE Editor window or Output window and

press the keyboard’s F1 key.

Page 53

Linker

Figure 2-2. VisualDSP++ Environment

Within VisualDSP++, specify tool settings for project builds. Use the

Project menu to open Project Options dialog box.

Figure 2-3, Figure 2-4, and Figure 2-5 show the project option selections

for SHARC, TigerSHARC, and Blackfin processors, respectively.

These dialog boxes allow you to select the target processor, type and and

name of the executable file, as well as VisualDSP++ tools available for use

with the selected processor.

When using the VisualDSP++ IDDE, use the Link option from the

Project Options dialog box (Figure 2-6) to select and/or set linker func-

tional options.

VisualDSP++ 4.0 Linker and Utilities Manual 2-7

Page 54

Linking Environment

Figure 2-3. Project Options Dialog Box (SHARC Processors)

Figure 2-4. Project Options Dialog Box (TigerSHARC Processors)

2-8 VisualDSP++ 4.0 Linker and Utilities Manual

Page 55

Linker

Figure 2-5. Project Options Dialog Box (Blackfin Processors)

There are four subpages you can access—General, LDF Preprocessing,

Elimination, and Processor. Almost every setting option has a corresponding compiler command-line switch described in “Linker

Command-Line Switches” on page 2-51.

The Additional options field in each sub-page is used to enter the appropriate file names and options that do not have corresponding controls on

the Link sub-page but are available as compiler switches.

Due to different processor architectures, the processors may provide different Link tab selection options. For example, Figure 2-7 shows Blackfin

processor options page.

Figure 2-8 shows SHARC processor options page.

VisualDSP++ 4.0 Linker and Utilities Manual 2-9

Page 56

Linking Environment

Figure 2-6. Project Options – Link Page

2-10 VisualDSP++ 4.0 Linker and Utilities Manual

Page 57

Linker

Figure 2-7. Project Options – Link (Processor) Blackfin Page

VisualDSP++ 4.0 Linker and Utilities Manual 2-11

Page 58

Linking Environment

Figure 2-8. Project Options – Link (Processor) SHARC Page

2-12 VisualDSP++ 4.0 Linker and Utilities Manual

Page 59

Figure 2-9 shows TigerSHARC processor options page.

Linker

Figure 2-9. Project Options – Link (Processor) TigerSHARC Page

Use the VisualDSP++ context-sensitive online Help for each target architecture to obtain information on linker options you can specify in

VisualDSP++. To do that, click on the ? button and then click in a field or

box you need information about.

VisualDSP++ 4.0 Linker and Utilities Manual 2-13

Page 60

Linking Environment

Expert Linker

The VisualDSP++ IDDE features an interactive tool, Expert Linker,

to map code or data to specific memory segments. When developing

a new project, use the Expert Linker to generate the .LDF file.

Expert Linker graphically displays the .LDF information (object files, LDF

macros, libraries, and a target memory description). With Expert Linker,

use drag-and-drop operations to arrange the object files in a graphical

memory mapping representation. When you are satisfied with the memory

layout, generate the executable (

Figure 2-10 shows the Expert Linker window, which comprises two panes:

Input Sections and Memory Map (output sections). Refer to Chapter 4,

“Expert Linker”, for detailed information.

.DXE) file.

Figure 2-10. Expert Linker Window

2-14 VisualDSP++ 4.0 Linker and Utilities Manual

Page 61

Linker Warning and Error Messages

Linker messages are written to the VisualDSP++ Output window

(standard output when the linker is run from a command line). Messages

describe problems the linker encountered while processing the .LDF file.

Warnings indicate processing errors that do not prevent the linker from

producing a valid output file, such as unused symbols in your code. Errors

are issued when the linker encounters situations that prevent the production of a valid output file.

Typically, these messages include the name of the .LDF file, the line number containing the message, a six-character code, and a brief description of

the condition.