Matched Monolithic

a

FEATURES

Low Offset Voltage: 200 V max

High Current Gain: 400 min

Excellent Current Gain Match: 2% max

Low Noise Voltage at 100 Hz, 1 mA: 2.5 nV/√Hz max

Excellent Log Conformance: rBE = 0.6 ⍀ max

Matching Guaranteed for All Transistors

Available in Die Form

PRODUCT DESCRIPTION

The MAT04 is a quad monolithic NPN transistor that offers excellent parametric matching for precision amplifier and nonlinear circuit applications. Performance characteristics of the

MAT04 include high gain (400 minimum) over a wide range of

collector current, low noise (2.5 nV/√Hz maximum at 100 Hz,

= 1 mA) and excellent logarithmic conformance. The

I

C

MAT04 also features a low offset voltage of 200 µV and tight

current gain matching, to within 2%. Each transistor of the

MAT04 is individually tested to data sheet specifications. For

matching parameters (offset voltage, input offset current, and

gain match), each of the dual transistor combinations are

Quad Transistor

MAT04

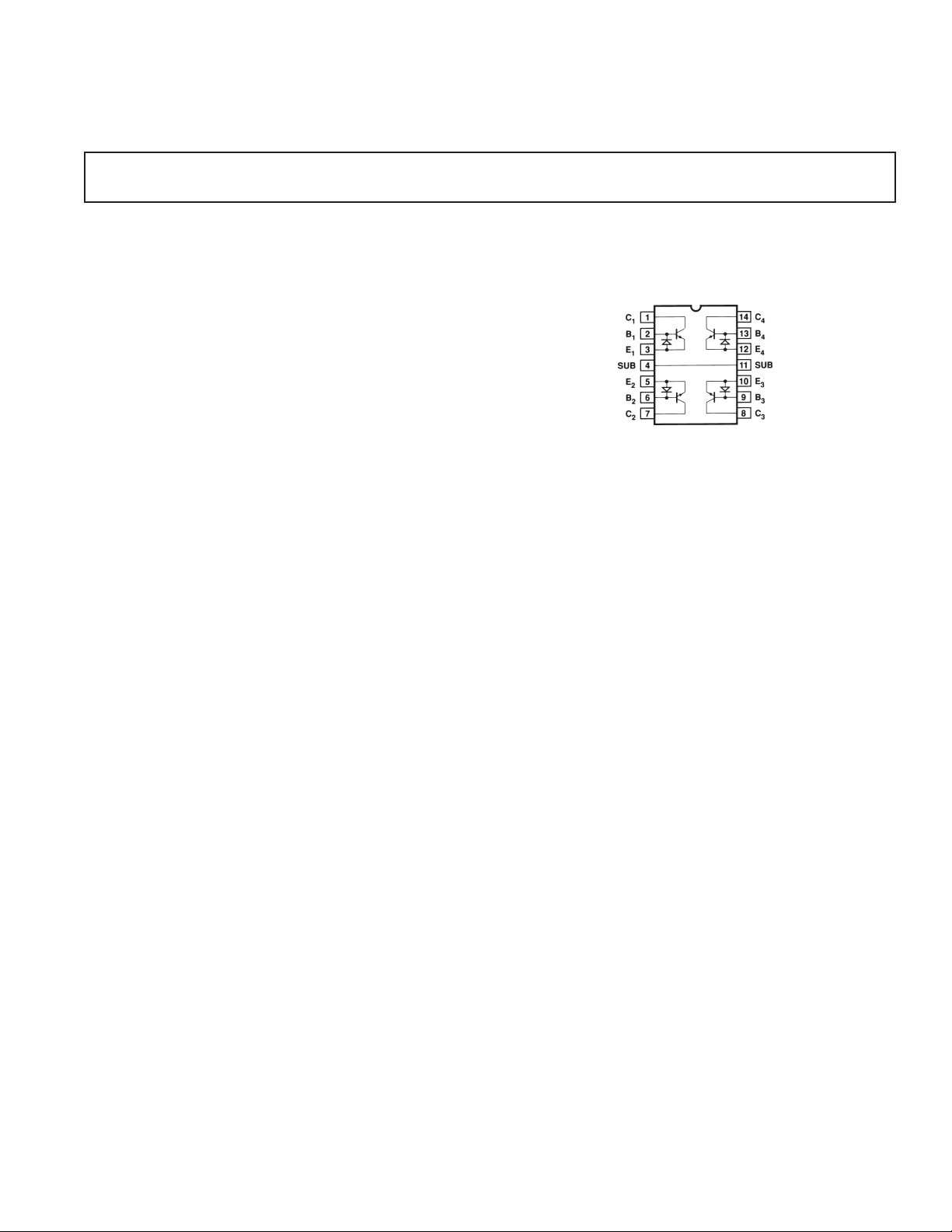

PIN CONNECTIONS

14-Lead Cerdip (Y Suffix)

14-Lead Plastic DIP (P Suffix)

14-Lead SO (S Suffix)

verified to meet stated limits. Device performance is guaranteed

at 25°C and over the industrial and military temperature ranges.

The long-term stability of matching parameters is guaranteed by

the protection diodes across the base-emitter junction of each

transistor. These diodes prevent degradation of beta and matching characteristics due to reverse bias base-emitter current.

The superior logarithmic conformance and accurate matching

characteristics of the MAT04 makes it an excellent choice for

use in log and antilog circuits. The MAT04 is an ideal choice in

applications where low noise and high gain are required.

REV. D

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

MAT04–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(@ TA = 25ⴗC unless otherwise noted. Each transistor is individually tested. For matching

parameters (VOS, IOS, ∆hFE) each dual transistor combination is verified to meet stated limits. All tests made at endpoints unless otherwise noted.)

MAT04E MAT04F

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

Current Gain h

Current Gain Match ∆h

Offset Voltage V

Offset Voltage Change vs. ∆V

FE

OS

FE

OS

/∆I

Collector Current V

Offset Voltage Change vs. V

Bulk Emitter Resistance r

Input Bias Current I

Input Offset Current I

Breakdown Voltage BV

Collector Saturation Voltage V

Collector-Base Leakage Current I

Noise Voltage Density e

Gain Bandwidth Product f

Output Capacitance C

∆VOS/∆VCB10 µA ≤ IC ≤ 1 mA

CB

BE

B

OS

CEO

CE(SAT)

CBO

n

T

OBO

10 µA ≤ IC ≤ 1 mA

0 V ≤ V

IC = 100 µA

0 V ≤ V

10 µA ≤ IC ≤ 1 mA

0 V ≤ V

10 µA ≤ IC ≤ 1 mA

C

= 0 V

CB

0 V ≤ V

10 µA ≤ IC ≤ 1 mA

V

= 0 V

CB

CB

CB

CB

CB

≤ 30 V

≤ 30 V

≤ 30 V

3

≤ 30 V

4

1

2

3

400 800 300 600

0.5 2 1 4 %

50 200 100 400 µV

525 1050µV

3

50 100 100 200 µV

0.4 0.6 0.4 0.6 Ω

IC = 100 µA

0 V ≤ V

≤ 30 V 125 250 165 330 nA

CB

IC = 100 µA; VCB = 0 V 0.6 5 2 13 nA

IC = 10 µA40 40 V

IB = 100 µA; IC = 1 mA 0.03 0.06 0.03 0.06 V

VCB = 40 V 5 5 pA

VCB = 0 V; fO = 10 Hz 2 3 2 4 nV/√Hz

= 1 mA; fO = 100 Hz 1.8 2.5 1.8 3 nV/√Hz

I

C

f

= 1 kHz

O

5

1.8 2.5 1.8 3 nV/√Hz

IC = 1 mA; VCE = 10 V 300 300 MHz

VCB = 15 V; IE = 0

f = 1 MHz 10 10 pF

Input Capacitance C

EBO

VBE = 0 V; IC = 0

f = 1 MHz 40 40 pF

NOTES

1

Current gain measured at IC = 10 µA, 100 µA and 1 mA.

Ih

2

Current gain match is defined as:

3

Measured at IC = 10 µA and guaranteed by design over the specified range of IC.

4

Guaranteed by design.

5

Sample tested.

Specifications subject to change without notice.

∆∆h

100( )( )

=

FE

MIN

BFE

I

C

–2–

REV. D

MAT04

ELECTRICAL CHARACTERISTICS

(at –25ⴗC ≤ TA ⴞ 85ⴗC for MAT04E, –40ⴗC ≤ TA ⴞ 85ⴗC for MAT04F, unless

otherwise noted. Each transistor is individually tested. For matching parameters (VOS, IOS) each dual transistor combination is

verified to meet stated limits. All tests made at endpoints unless otherwise noted.)

Parameter Symbol Conditions Min Typ Max Min Typ Max Unit

Current Gain h

Offset Voltage V

Average Offset TCV

FE

OS

OS

Voltage Drift V

Input Bias Current I

Input Offset Current I

Average Offset TCI

B

OS

OS

Current Drift V

Breakdown Voltage BV

Collector-Base I

CEO

CBO

10 µA ≤ IC ≤ 1 mA

0 V ≤ V

CB

10 µA ≤ IC ≤ 1 mA

0 V ≤ V

CB

IC = 100 µA

= 0 V

CB

≤ 30 V

≤ 30 V

3

1

2

IC = 100 µA

0 V ≤ V

≤ 30 V 160 445 200 500 nA

CB

IC = 100 µA

= 0 V 4 20 8 40 nA

V

CB

IC = 100 µA

= 0 V 50 100 pA/°C

CB

IC = 10 µA4040V

VCB = 40 V

MAT04E MAT04F

225 625 200 500

60 260 120 520 µV

0.2 1 0.4 2 µV/°C

Leakage Current 0.5 0.5 nA

Collector-Emitter I

CES

VCE = 40 V

Leakage Current 5 5 nA

Collector-Substrate I

CS

VCS = 40 V

Leakage Current 0.7 0.7 nA

REV. D

–3–

MAT04

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Collector-Base Voltage (BV

CBO

Collector-Emitter Voltage (BV

Collector-Collector Voltage (BV

Emitter-Emitter Voltage (BV

EE

1

) . . . . . . . . . . . . . . . . . . . 40 V

) . . . . . . . . . . . . . . . . . 40 V

CEO

) . . . . . . . . . . . . . . . . . 40 V

CC

) . . . . . . . . . . . . . . . . . . . 40 V

Collector Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 mA

Emitter Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 mA

Substrate (Pin-4 to Pin-11) Current . . . . . . . . . . . . . . . 30 mA

Operating Temperature Range

MAT04EY . . . . . . . . . . . . . . . . . . . . . . . . . –25°C to +85°C

MAT04FY, FP, FS . . . . . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature

Y Package . . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +150°C

P Package . . . . . . . . . . . . . . . . . . . . . . . . . –65°C to +125°C

Lead Temperature (Soldering, 60 sec) . . . . . . . . . . . . +300°C

Package Type

2

JA

JC

Units

14-Lead Cerdip 108 16 °C/W

14-Lead Plastic DIP 83 39 °C/W

14-Lead SO 120 36 °C/W

NOTES

1

Absolute maximum ratings apply to both DICE and packaged parts, unless

otherwise noted.

2

JA is specified for worst case mounting conditions, i.e., JA is specified for

device in socket for cerdip and P-DIP packages; JA is specified for device

soldered to printed circuit board for SO package.

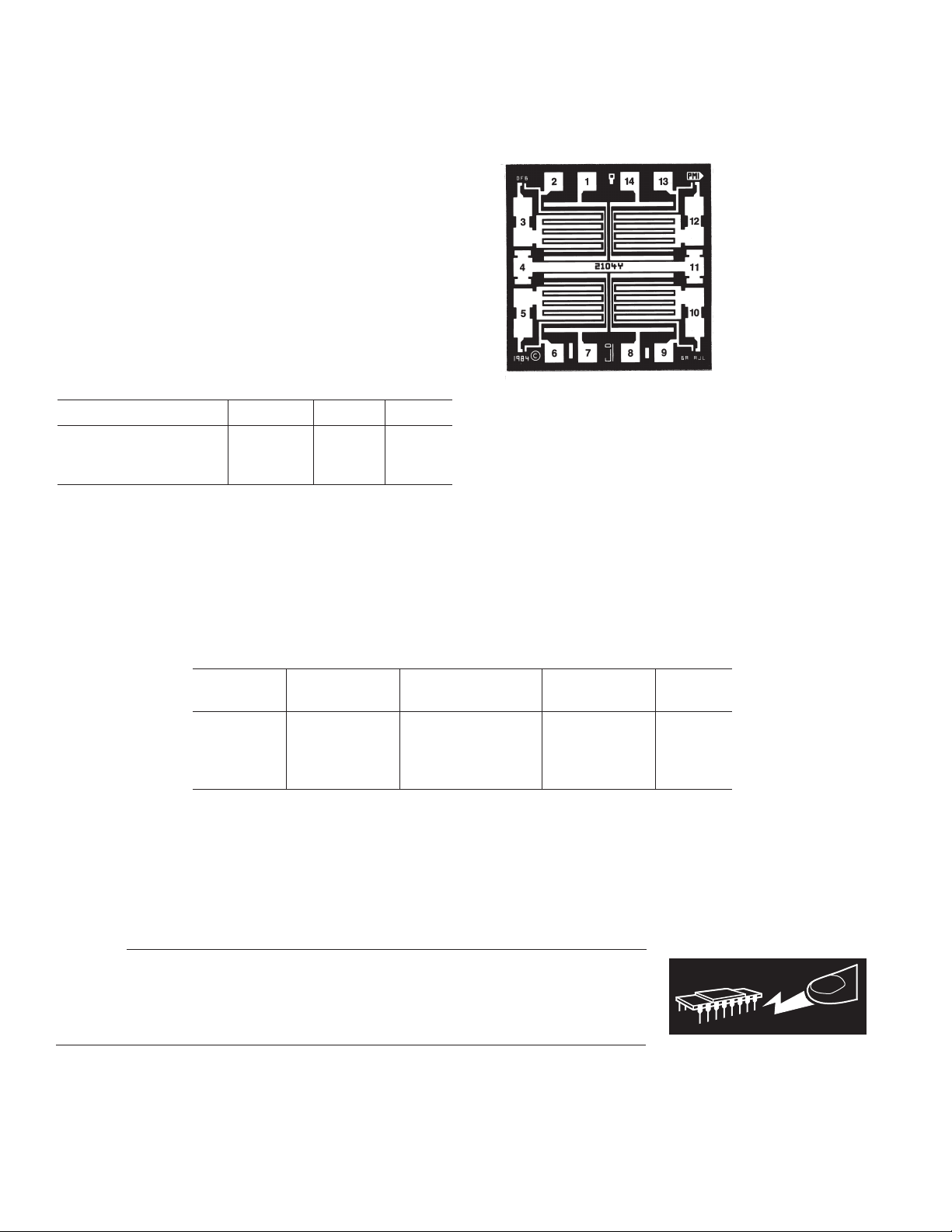

DICE CHARACTERISTICS

Die Size 0.060 × 0.060 Inch, 3600 Sq. mm

(1.52

×

1.52 mm, 2.31 sq. mm)

1. Q1 COLLECTOR

2. Q1 BASE

3. Q1 EMITTER

4. SUBSTRATE

5. Q2 EMITTER

6. Q2 BASE

7. Q2 COLLECTOR

8. Q3 COLLECTOR

9. Q3 BASE

10. Q3 EMITTER

11. SUBSTRATE

12. Q4 EMITTER

13. Q4 BASE

14. Q4 COLLECTOR

ORDERING GUIDE

TA = 25ⴗC Temperature Package Package

Model VOS max Range Description Option

*

MAT04EY

MAT04FY

200 µV –25°C to +85°C Cerdip Q-14

*

400 µV –40°C to +85°C Cerdip Q-14

MAT04FP 400 µV –40°C to +85°C P-DIP-14 N-14

MAT04FS 400 µV –40°C to +85°C 14-Lead SO SO-14

NOTES

*

Not for new designs; obsolete April 2002.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the MAT04 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–4–

REV. D

Loading...

Loading...