Circuit Note

engineers. Standard engineering practices have been employed in the design and construction of

each circuit, and their function and performance have been tested and verified in a lab environment at

ure. However, you are solely responsible for testing the circuit and determining its

suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices

AD8275

7

4

5

6

8

2

50kΩ

0.1µF

50kΩ

20kΩ

20kΩ

10kΩ

3

+IN

– IN

REF2

REF1

– V

S

+V

S

+5V

OUT

SENSE

1µF

10µF

1

AD7685

VDD

GND

REF

IN +

IN –

ADP1720

VIO

SDI

SCK

S

DO

CNV

+15V

−15V

+15V

+15V

+5V

+4.5V

+4.25V

+2.25V

+0.25V

ADR439

+10V

−10V

0V

AD8226

VIO

+2.25V

0.1µF

IN

EN

OUT

GND

V

INVOUT

GND

AIN+

AIN−

*R

G

*OMIT R

G

FOR G = 1

REF

09859-001

CN-0213

Devices Connected/Referenced

16-Bit , 250 kSPS PulSAR® ADC in

MSOP/QFN

Wide Supply Range, Rail-to-Rail Output

Instrumentation Amplifier

50 mA, High Voltage, Micropower Linear

Regulator

Circuits from the Lab™ reference circuits are engineered and

tested for quick and easy system integration to help solve today’s

analog, mixed-signal, and RF design challenges. For more

information and/or support, visit www.analog.com/CN0213.

AD7685

AD8226

AD8275 G = 0.2, Level Translation, 16-Bit ADC Driver

ADP1720

ADR439 Ultralow Noise XFET® Voltage Reference

Complete High Speed, High CMRR Precision Analog Front End for Process Control

EVALUATION AND DESIGN SUPPORT

Design and Integration Files

Schematics, Layout Files, Bill of Materials

CIRCUIT FUNCTION AND BENEFITS

Signal levels in industrial process control systems generally fall

into one of the following categories: single-ended current

(4 mA-to-20 mA), single-ended, differential voltage (0 V to 5V,

0 V to 10 V, ±5 V, ±10 V), or small signal inputs from sensors

such as thermocouples or load cells. Large common-mode

voltage swings are also typical, especially for small signal

differential inputs; therefore good common-mode rejection is

an important specification in the analog signal processing

system.

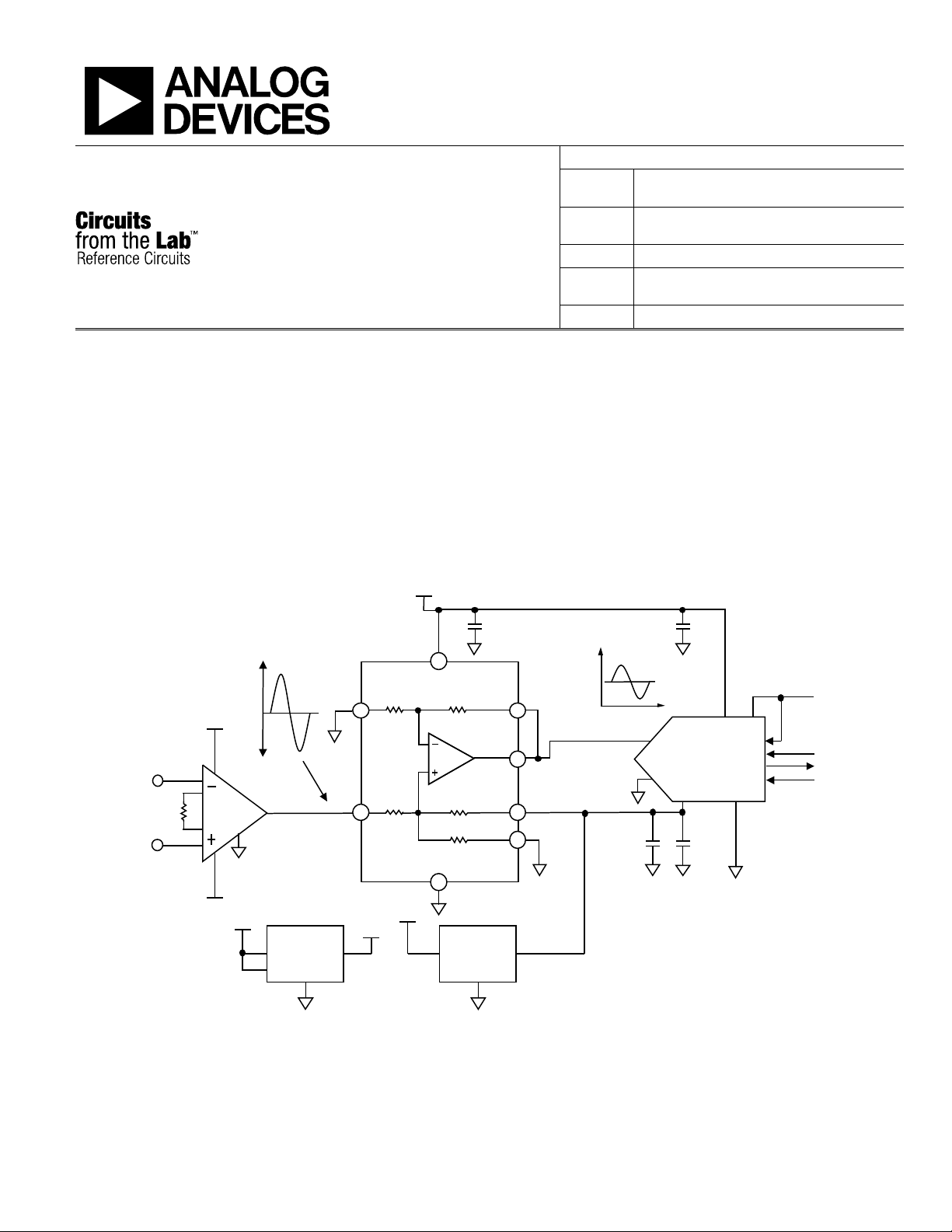

The analog front-end circuit shown in Figure 1 is optimized

for high precision and high common-mode rejection ratio

(CMRR) when processing these types of industrial-level signals.

Figure 1. High Performance Analog Front End for Process Control (Simplified Schematic: All Connections and Decoupling Not Shown)

Rev.0

Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices

room temperat

be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause

whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

www.analog.com

CN-0213 Circuit Note

The circuit level shifts and attenuates the signals so they

are compatible with the input range requirements of most

modern single-supply SAR ADCs, such as the AD7685 high

performance 16-bit 250 kSPS PulSAR® ADC.

With an 18 V p-p input signal, the circuit achieves

approximately 105 dB common-mode rejection (CMR) at

100 Hz and 80 dB CMR at 5 kHz.

High precision, high input impedance, and high CMR are

provided by the AD8226 instrumentation amplifier. For high

precision applications, a high input impedance is required to

minimize system gain errors and also to achieve good CMR.

The AD8226 gain is resistor-programmable from 1 to 1000.

A resistive level shifter/attenuator stage directly on the input

would inevitably degrade CMR performance due to the

mismatch between the resistors. The AD8226 provides the

excellent CMR required for both small signal and large signal

inputs. The AD8275 level shifter/attenuator/driver performs the

attenuation and level shifting function in the circuit, without

any need for external components.

Traditionally, sigma-delta ADCs have been used in high

resolution measurement systems because signal bandwidths are

quite low, and the sigma-delta architecture provides excellent

noise performance at low update rates. However, there is an

increased trend for higher update rates, especially in

multichannel systems, to allow faster per-channel update, or for

increased channel density. In such cases a high performance

SAR ADC is a good alternative. The circuit shown in Figure 1

uses the AD7685 250 kSPS 16 bit ADC, with the AD8226 high

performance in-amp, and the AD8275 attenuator/level shifter

amplifier implemented as a complete system solution without

the need for any external components.

CIRCUIT DESCRIPTION

This circuit is comprised of an AD8226 rail-to-rail output inamp, connected to the positive input of the AD8275 G = 0.2

difference amplifier, whose output is then connected to the

input of the AD7685, a 16-bit, 250 kSPS PulSAR ADC in

MSOP/QFN. The AD8226 is set for a gain-of-one mode (high

voltage/current inputs), and its output is referenced to ground.

Single-ended or differential inputs can be used. The output of

the AD8226 is a bipolar signal, which drives the AD8275 input.

The AD8275 acts to attenuate and level shift the bipolar input,

providing for a gain of 0.2. Hence, differential inputs of 20 V p-p

at its inputs will yield a 4 V p-p single-ended range on the

output. The ADR439 precision 4.5 V reference is used to

provide both the internal common-mode bias voltage for the

AD8275 (VREF/2 = 2.25V), as well as the external reference

voltage for the AD7685 ADC. Under these conditions, the

output of the AD8275 swings from +0.25 V to +4.25 V, which is

within the range of the AD7685, 0 V to +4.5 V.

The ADP1720 is used to provide the 5 V supply for the AD8275

and the AD7685. The ADP1720 was chosen because it has a

high input voltage range (up to 28 V). In this circuit, the

ADP1720 is only required to supply approximately 4 mA to the

AD8275 and AD7685, so the worst case power dissipation in

the regulator with 28 V input is about 90 mW. This allows the

complete system to run from the external

±15 V supplies.

System Level Common-Mode Rejection Performance

Initial testing was to verify the performance of the AD8226

common-mode rejection at a system level through to the ADC.

Input test tones of 10 Hz, 100 Hz, 500 Hz, 1 kHz, 2 kHz, 3 kHz,

4 kHz, 5 kHz were used, with an 18 V p-p input signal. The test

results are summarized in Table 1. In Test 1 the AIN+ and AIN−

signals are shorted together and connected to the ac test tone,

and the results measured with an FFT. The AD8226 should

reject the ac signal because its inputs are connected together. In

Tes t 2 the signal is applied to AIN+, and AIN− is connected to

ground. Under these conditions, the FFT measures the level of

the tone. The common-mode rejection can then be calculated

as the difference in the FFT results between Test 1 and Test 2.

Tabl e 1 summarizes the CMR values obtained at different

frequencies. It is important to note that the CMR of the AD8226

is specified at 80 dB at 5 kHz, so no loss in CMR performance is

realized at the system level.

System Level AC Performance

The ac accuracy of the system was also tested at a system level

with the AD7685 operating at a sampling rate of 250 kSPS.

Figure 2 shows an FFT test result for a 5 V p-p input at 10 kHz.

The results shown in the plot are given below:

• SNR = 87.13 dBFS

• SINAD = 85.95 dBFS

• SFDR = 81.82 dBc

• THD = −78.02 dBc

Rev. 0 | Page 2 of 5

Loading...

Loading...