高速差動

R

+

+

高速差動 ADC

高速差動高速差動

ADC ドライバの設計についての考察

ドライバの設計についての考察

ADCADC

ドライバの設計についての考察ドライバの設計についての考察

by John Ardizzoni and Jonathan Pearson

はじめに

はじめに

はじめにはじめに

ほとんどの最新の高性能 ADC は差動入力を使用して、同

相ノイズと干渉を除去し、ダイナミック・レンジをファク

タ 2 増大し、平衡した信号送信により全体の性能を改善し

ています。差動入力 ADC はシングル・エンド入力信号も

入力可能ですが、やはり入力信号が差動の時に最適な特性

が得られます。ADCドライバ(このような信号を出力す

るためにしばしば特別に開発された回路。)は振幅スケー

リング、シングル・エンド to差動入力変換、バッファ・

アンプ、同相オフセット調整、フィルタを含む多数の重要

な機能を実行します。 AD8138の紹介以来、差動 ADC

ドライバはデータ・アクウィジション・システムで必要不

可欠な信号処理部品になりました。

F1

R

G1

V

V

+

IP

V

IN, dm

V

–

IN

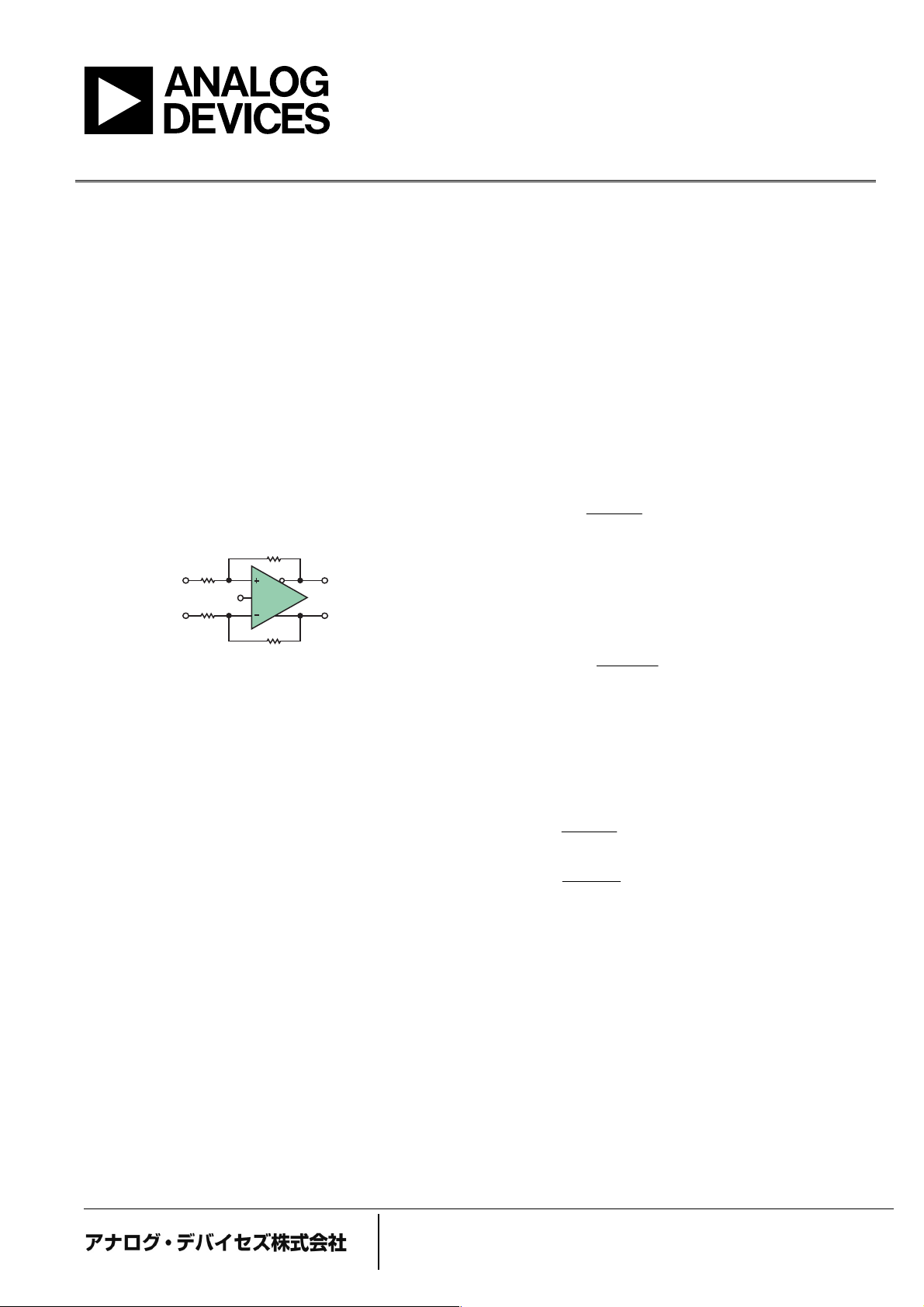

基本的な完璧に差動の電圧フィードバック ADC ドライバ

を図 1 に示します。従来のオペアンプ帰還回路とは 2 つの

点で違いがある事がわかります。差動 ADCドライバには

新たに出力端子(VON) と入力端子(V

これらの端子は差動入力の ADCに信号をインターフェー

スする時非常に便利です。

差動 ADC ドライバはシングル・エンド出力の代わりに、

V

基準に VOP と VON.の間で平衡な差動出力を生じます。

OCM

(P は正を、N は負を表します。)V

電圧をコントロールします。入出力信号が規定範囲内であ

る限り、出力同相電圧は V

しくなります。負帰還と高オープンループ・ゲインにより、

アンプ入力端子電圧の VA+ と VA–は基本的に等しくなり

ます。

A

V

OCM

V

R

A

G2

図 1.差動アンプ

OCM

V

–

ON

V

OUT, dm

V

+

R

F2

OP

08263-001

)が追加されています。

OCM

入力は出力同相

OCM

入力に印加された電圧に等

AN-1026

APPLICATION NOTE

今後の説明のために、いくつかの定義を順に説明します。

入力信号が平衡であれば、VIP と VINは通常 同相基準電圧

を基準にして振幅は同じで位相が反対になります。入力が

シングル・エンドの場合は、一方の入力が固定電圧で他方

がその電圧を基準に変化します。いずれの場合も、入力信

号は VIP – VINとして規定されます。

差動モード入力電圧、V

1 と式 2 で規定されます。

V

= VIP – VIN (1)

IN, dm

VV

V

IN, cm

=

INIP

2

この同相の定義は入力が平衡の時には直感的に理解できま

すが、入力がシングル・エンドでも有効です。

出力も又差動モードと同相モードがあり、式 3 と式 4 で規

定されます。

V

= VOP – VON (3)

OUT, dm

V

OUT, cm

=

VV

2

実際の出力同相モード電圧 V

設定する)V

入力端子との間の差に注意してください。

OCM

差動 ADC ドライバの解析は従来のオペアンプの解析より

もかなり複雑です。代数を簡略化するために式 5、式 6 で

与えられたように 2 つの帰還係数 β1 、β

利です。

R

β

1

β

G1

=

F1

=

2

F

(5)

RR

+

G1

R

2

G

(6)

RR

+

2

2

G

と同相入力電圧、V

IN, dm

(2)

ONOP

(4)

,と(出力同相レベルを

OUT, cm

を定義すると便

2

IN, cm

, は式

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の利用に関して、あるいは利用によって

生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示

的または暗示的に許諾するものでもありません。仕様は、予告なく変更される場合があります。本紙記載の商標および登録商標は、各社の所有に属

します。※日本語資料は REVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

Rev. 0

©2010 Analog Devices, Inc. All rights reserved.

本 社/〒105-6891 東京都港区海岸 1-16-1 ニューピア竹芝サウスタワービル

大阪営業所/〒532-0003 大阪府大阪市淀川区宮原 3-5-36 新大阪トラストタワー

電話 03(5402)8200

電話 06(6350)6868

AN-1026 APPLICATION NOTE

目次

目次

目次目次

はじめに

改定履歴 .......................................................................... 2

改訂履歴

改訂履歴

改訂履歴改訂履歴

11/09—Revision 0:初版

........................................................................... 1

ADC ドライバに対する入力の終端 .............................. 3

入力同相電圧範囲(ICMVR)

入力結合および出力結合:AC又は DC ....................... 6

出力振幅 ....................................................................... 7

.............................................. 5

ノイズ ...........................................................................7

電源電圧 ........................................................................9

高調波歪み ..................................................................10

帯域とスルーレート .................................................... 11

安定性 ......................................................................... 11

PC 基板レイアウト .....................................................12

Rev. 0 | Page 2 of 16

APPLICATION NOTE

R

200Ω

R

ほとんどの ADCドライバでは β1 = β

タのミスマッチが性能にどのように影響するかついて理解

するのに、VIP, VIN, V

, β1, β2の項をもつ V

OCM

的な閉ループ公式は役に立ちます。図 7 に示す V

式にはアンプの有限で周波数に依存するオープンループ電

圧ゲイン、A(s)が含まれています。

V

β

OUT,dm

1

≠ β2の時、差動出力電圧は V

=

2

+

ββ

21

( ) ( ) ( )

OCM

21

+

1

OCM

差動出力にオフセットと余分なノイズを生じるので、望ま

しくない結果になります。 電圧帰還回路のゲイン帯域幅

積(GB 積)は一定です。興味ある事に、ゲイン帯域幅積

(GB 積)のゲインは 2 つの帰還率の平均の逆数です。

β

= β2 ≡ ≡β の時、式 7 は式 8 のように短縮されます。

1

V

,

dmOUT

V

=

,

dmIN

R

F

R

G

1

1

+

1

( )

β

)(

sA

これはよく知られている式です;理想的な閉ループゲイン

は、A(s) → ∞の時単純な RF/RGになります。 ゲイン帯

域幅積(GB 積)も又、ノイズゲインが 1/β になるので、

ちょうど従来のオペアンプの場合のようによく知られた形

になります。

帰還率がマッチングしている差動 ADC ドライバの理想的

な閉ループゲインは式 9 になります。

A ==

V

V

V

R

dmOUT

,

F

(9)

R

G

dmIN

,

差動 ADC ドライバの重要な性能基準である出力平衡には、

振幅平衡と位相平衡の 2 つの要素があります。 振幅平衡

は 2 つの出力の振幅がどのくらい一致しているかを表す尺

度です;理想的なアンプではそれらは正確に一致していま

す。出力位相平衡は 2 つの出力間の位相差がどのくらい

180°に近いかを表す尺度です。出力振幅又は出力位相のど

のような不平衡も出力に好ましくない同相成分を生じます。

出力平衡誤差(式 10)は差動入力信号によって生成される

出力同相電圧の、(同じ入力信号によって生成される)出

力差動モード電圧に対する対数比で、デシベルで表されま

す。

=

ErrorBalanceOutput

内部の同相帰還ループにより V

log20

OUT, cm

される電圧に等しくなり、優れた出力平衡を生みます。

です。しかしベー

2

の一般

OUT, dm

の

OUT, dm

−−−+−

βVβVββV

11

IP

( )

( )

1

2

+

ββsA

21

2

IN

に依存します。これは

(8)

∆

V

10

∆

V

が V

cmOUT

,

dmOUT

,

入力に印加

OCM

(10)

(7)

AN-1026

ADC

ADC ドライバ

ドライバに対する

ADCADC

ドライバドライバ

ADC ドライバは高速信号を処理するシステムで頻繁に使

用されます。信号波長の小片以上に分離されたデバイスは

信号のもとの波形を損なわないようにインピーダンス整合

された電気伝送ラインで接続されなければなりません。伝

送ラインの両端を特性インピーダンスで終端した時、最適

の性能が得られます。ドライバは一般的に ADC の近くに

配置されるのでそれらの間にインピーダンス整合した接続

の必要はありませんが、しばしば ADC ドライバ入力まで

の信号経路が長いことがあるので、その場合適切な抵抗で

終端してインピーダンス整合した接続をする必要がありま

す。

終端抵抗 R

抗値にできるように、(差動であろうとシングル・エンド

であろうと)ADCドライバの入力抵抗は、所望の終端抵

抗より大きいか等しくなければなりません。ここで検討す

る例に出てくるすべての ADC ドライバは

たようにバランスのとれたフィードバック比を持つように

設計されています。

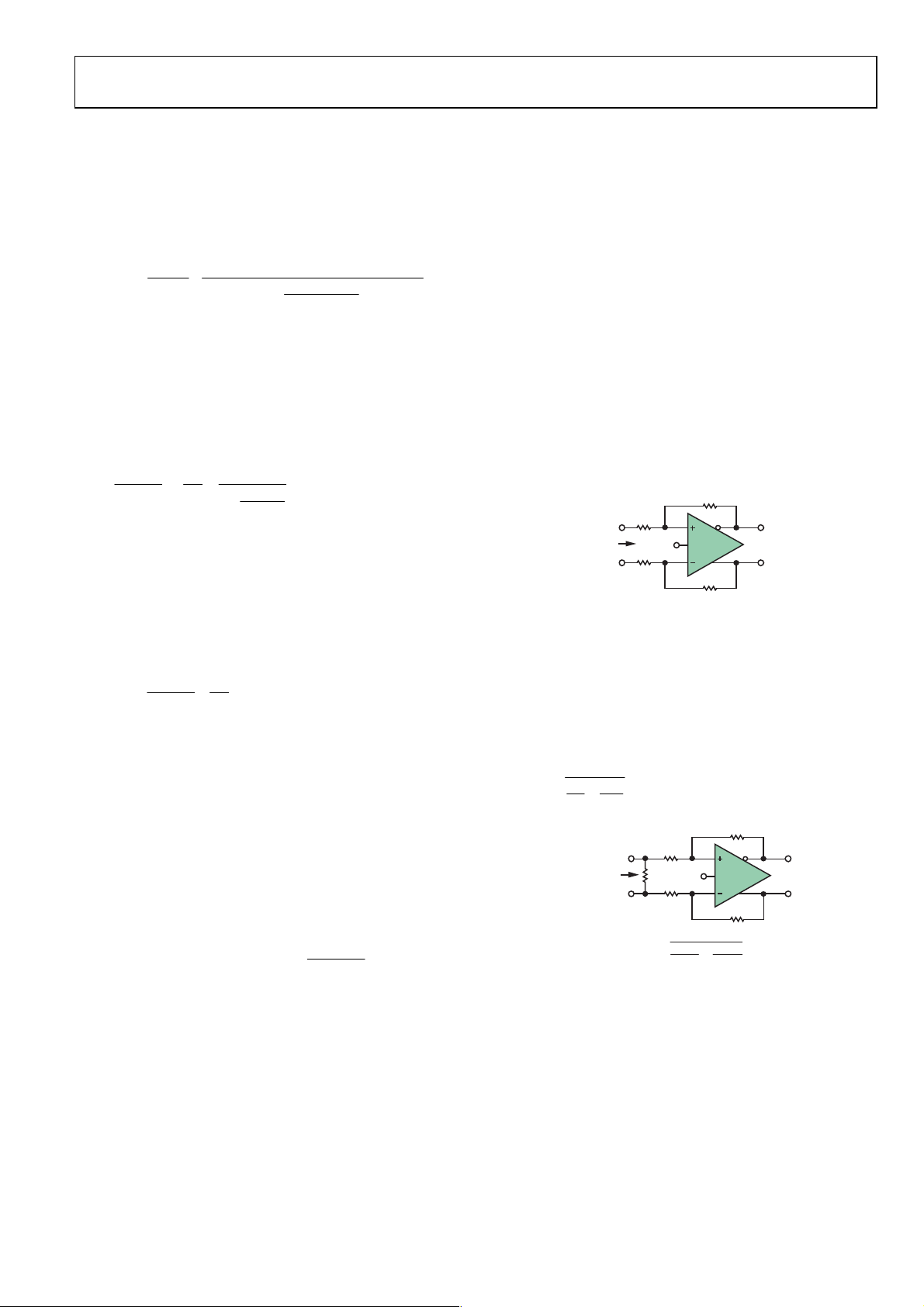

アンプの 2 つの入力間電圧は負帰還によりゼロになるよう

に動作するので、これらは仮想的に接続され、差動入力抵

抗 RIN,は単純な 2 × RGになります。伝送ライン抵抗 R

整合させるために、差動入力の間に式 11で計算した値の

RTを接続します。図 3.図 3 に標準的な抵抗 RF = RG = 200

Ω, 要求される抵抗 R

ます。

R

=

T

に対する入力の終端

に対するに対する

をアンプ入力と並列に追加して要求される抵

T

入力の終端

入力の終端入力の終端

図 2.

F

R

G

R

IN, dm

図 2.差動アンプ入力インピーダンス

1

−

= 100Ω V

L, dm

V

OCM

R

G

L, dm

11

RR

INL

R

T

R

T

図 3.100Ω ラインに整合

R

= 100 Ω, と RT = 133 Ω.を示し

200Ω

OCM

200Ω

1

=

1

−

100Ω

F

200Ω

1

400Ω

= 133Ω

図 2 に示し

L

に

(11)

Rev. 0 | Page 3 of 16

AN-1026 APPLICATION NOTE

–2V

3.5V

200Ω

2V p-p

R

1.1V p-p

R

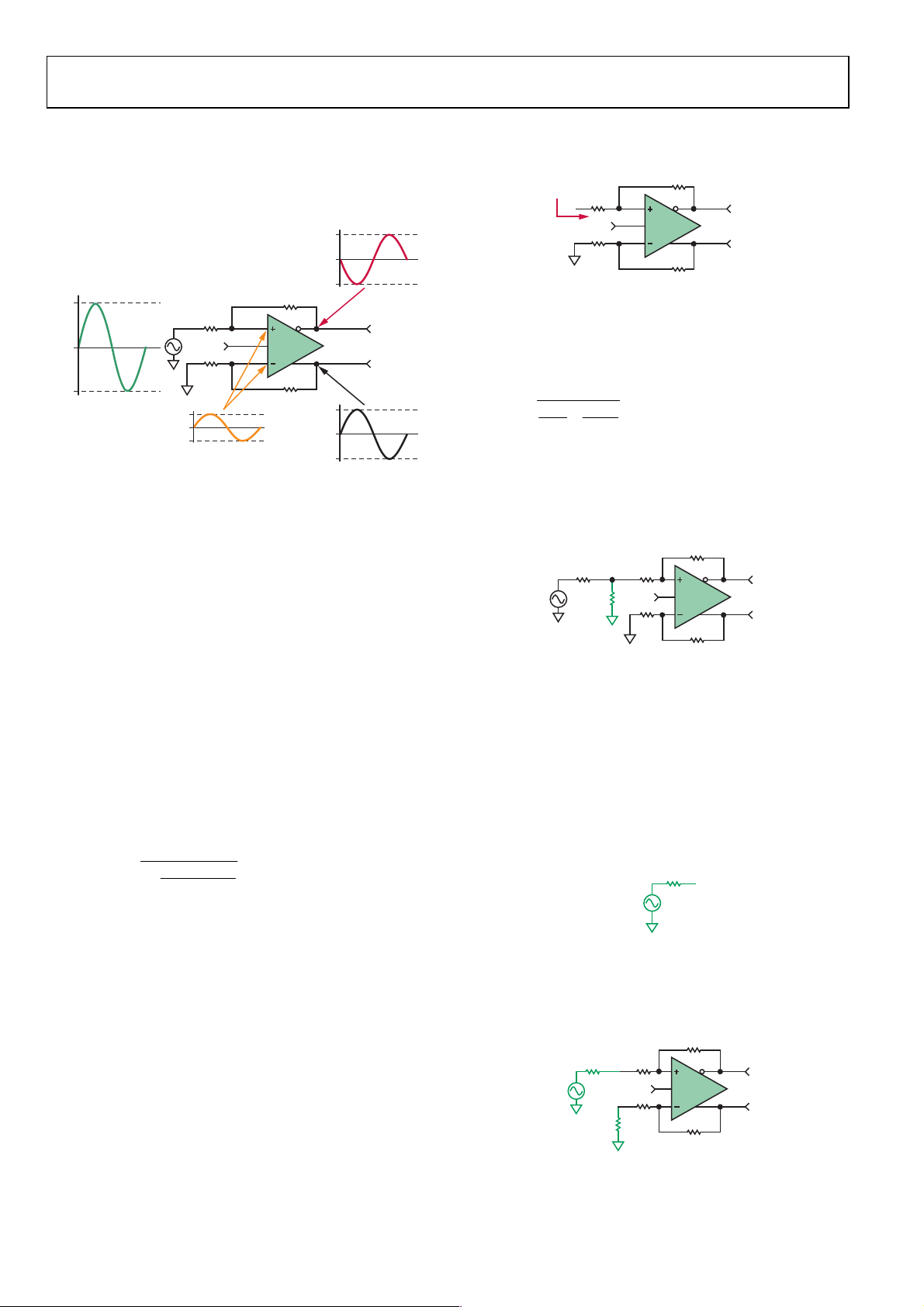

シングル・エンド入力を終端する事はより多くの努力を必

要とします。図 4 はシングル・エンド入力、差動出力回路

の ADC ドライバがどのように動作するかを示しています。

2.5V

1.5V

R

F

V

500Ω

OCM

R

500Ω

V

ON

–

V

OUT, dm

+

V

OP

F

3.5V

2.5V

1.5V

2V

V

0V

IN

1.75V

1.25V

0.75V

R

500Ω

2.5V

R

500Ω

G

G

図 4.ADC ドライバへのシングル・エンド入力の例

入力はシングル・エンドですが、V

ります。抵抗 RF と R

は等しくバランスがとれているの

G

IN, dm

は V

に等しくな

IN

で、ゲインは1で、差動出力、VOP − VON,は入力電圧、す

なわち、4Vp-p に等しくなります。V

V に等しく、又入力電圧 VA+ と V

は、下側の帰還回路の

A−

OUT, cm

は V

OCM

= 2.5

フィードバックにより、 VOP/2に等しくなります。

式 3 と 式 4を使うと、VOP = V

に±1 V同相スウィングします。又 VON = V

+ VIN/2となり 2.5 V基準

OCM

– VIN/2とな

OCM

り 2.5 V.基準に±1 V逆相スウィングします。 従って VA+

と VA− は 1.25 V基準に±0.5 Vスウィングします。 VIN か

ら供給しなければならない電流の AC成分は(2 V – 0.5

V)/500 Ω = 3 mAです。従って VIN から見て整合をとらなけ

ればならないグラウンドに対する抵抗は、667 Ω です。

各々のループの帰還率がマッチングしている時、このシン

グル・エンド入力抵抗を計算する一般的な公式は式 12 で

表せます。ここで RIN, seはシングル・エンド入力抵抗です。

=

R

seIN

,

1

−

2

R

G

R

( )

F

+×

RR

F

G

(12)

これは終端抵抗を計算するスタート点です。ここで、アン

プ・ゲインの式は入力源インピーダンスをゼロと仮定して

いる事に注意する事が重要です。本質的にシングル・エン

ド入力のために生ずる不平衡の状態で、信号源インピーダ

ンスを整合させなければならないので、上側の R

を追加します。 平衡を保つために、これを下側の R

に抵抗

G

G

に抵

抗を追加してマッチングさせなければなりませんが、それ

はゲインに影響します。

シングル・エンド信号を終端する事の問題に対して閉形式

解を決めることは可能かもしれませんが、再計算法が一般

的に使用されます。その必要性は次の例で明らかです。

図 5 は、シングル・エンド to 差動のゲインが 1, 入力終端

抵抗が 50Ω、そしてノイズを低く保つために、フィード

バック抵抗とゲイン抵抗を約 200Ω 付近の値にしています。

267Ω

200Ω

2.5V

200Ω

図 5.シングル・エンド入力インピーダンス

200Ω

V

OCM

200Ω

–

V

OUT, dm

+

V

ON

V

OP

式 12 からシングル・エンド入力抵抗は 267 Ω になります。

式 13 から入力抵抗 267 Ω を 50 Ω に落とすためには、並

列抵抗、R

61.5Ω にしなければならないことがわかり

Tを

ます。

=TR

図 6 は信号源抵抗と終端抵抗を示した回路です。 信号源

08263-004

1

1

−

Ω50

61.5

=

1

(13)

Ω267

の解放回路電圧は 2 V p-p で、信号源抵抗は 50 Ω です。

信号源が 50 Ω に終端されると、入力電圧は 1 V p-p に減

少します。これは又ユニティゲイン・ドライバの差動出力

電圧になります。

200Ω50Ω

R

61.5Ω

T

2.5V

200Ω

V

OCM

200Ω

図 6.信号源と終端抵抗を加えたシングル・エンド回路

–

V

OUT, dm

+

V

V

この回路は一見完全に見えますが、50 Ω と並行にミスマ

ッチした抵抗 61.5 Ω が上側の R

のみに追加されていま

G

す。これはゲインとシングル・エンド入力抵抗を変え、帰

還率をミスマッチさせます。ゲインが小さいので、入力抵

抗の変化は小さくしばらく無視されます、しかし帰還率は

マッチングしていなければなりません。これを可能するも

っとも簡単な方法は下側の R

に抵抗を加えることです。

G

図 7 はテブナン等価回路を示しますが、ここで前述した並

列組み合わせ回路が信号源抵抗として働きます。

V

TH

27.6Ω

TH

08263-007

図 7.入力信号源のテブナン等価回路

図 8 に示すように、ループ帰還率をマッチングさせるため

に、この置き換え回路に合わせて下側ループに 27.6 Ω 抵

抗, R

を追加します。

TS

V

1.1V p-p

TH

R

TH

27.6Ω

27.6Ω

F

200Ω

R

G

200Ω

V

2.5V

R

TS

200Ω

OCM

R

G

R

F

200Ω

–

V

OUT, dm

+

V

V

図 8.平衡シングル・エンド終端回路

ON

OP

ON

OP

08263-008

Rev. 0 | Page 4 of 16

APPLICATION NOTE

R

2V p-p

+

(

)

+

(

)

−+−

+

(

)

−+=

1.1 V p-p のテブナン電圧は適切に終端された電圧 1 V p-p

よりも大きくなり、ゲイン抵抗はそれぞれ 27.6 Ω 増える

ので、閉ループゲインが減少する事に注意してください。

これら出力電圧に対して相反する影響は抵抗が大きく (>1

kΩ) 、ゲインが小さい(1 又は 2)場合は,互いに相殺する傾

向にありますが、抵抗が小さくゲインが高い場合には完全

には相殺されません。

図 8 の回路は簡単に解析する事ができ、差動出力電圧は式

14 で計算する事ができます。

V

=

dmOUT,

p-pV 1.1 =

差動出力電圧は所望の電圧 1 V p-pより多少小さくなりま

すが、式 15 に示したようにフィードバック抵抗を変更す

ることにより最終的な独立したゲイン調整が可能です。

Ω227.6

=

R

F

Ω27.62

p-pV 0.1

p-pV 1.1

図 9 に完成した回路を示します。ここで使用する抵抗の値

は標準 1%です。

R

R

S

50Ω

R

T

61.9Ω

R

TS

28Ω

図 1.完全シングル・エンド終端回路

図 9 の回路に関して、ドライバのシングル・エンド入力抵

抗 RIN, seは RFと R

の変更により変わります。ドライバ

G

の上側ループのゲイン抵抗は 200 Ω で、下側ループのゲ

イン抵抗は 200 Ω + 28 Ω = 228 Ω です。ゲイン抵抗が違

う場合は、R

の計算を行う前に式 16 と式 17 に示すよ

IN, se

うに 2 つベータ値を計算する必要があります。

R

G

=

β

1

β

2

入力抵抗 R

R

+

RR

GF

RR

=

IN, se

=

,

seIN

TSG

++

RRR

TSGF

は式 18 に示すように計算します。

ββR

( )

1

+

ββ

21

21

G

この値は始めに計算した値 267 Ω とほとんど変わらず、

RTの計算に大きな影響はありません。なぜなら R

RTとは並列だからです。

もしもっと正確な全体のゲインが必要であれば、より高精

度な抵抗又は直列トリム抵抗を使用する事ができます。

IN, se

=

Ω200

Ω227.6

,

dmOUT

=

p-pV 1.1

Ω206.9

F

205Ω

G

V

OCM

G

R

F

205Ω

(16)

494.0

==

Ω228

527.0

==

Ω433

Ω271

(18)

=

200Ω

2.5V

200Ω

Ω200

Ω405

VDesired

R

R

p-p V 0.97

(15)

V

ON

–

V

OUT, dm

+

V

OP

(17)

は

IN, se

(14)

AN-1026

ここで述べた1度の再計算方法は閉ループゲインが 1 又は

2 の時はよく当てはまります。ゲインがさらに高い場合、

RTSの値は RGの値に近くなり、式 18 で計算した R

値と式 12で計算した値の差は大きくなります。このよう

な場合には何回かの再計算が必要です。

これは困難ではありません:最近リリースされた差動アン

プ計算ツール、ADIsimDiffAmp™ と ADI Diff Amp

Calculator™はすべての厄介な仕事を行います;それらは

前述の計算を数秒で行います。詳細については、

www.analog.comを参照してください。

入力同相電圧範囲

入力同相電圧範囲(ICMVR)

入力同相電圧範囲入力同相電圧範囲

ICMVR は通常動作で差動アンプ入力に加える事のできる

電圧範囲を規定します。差動アンプ入力に現れる電圧は

ICMV, V

, 又は V

acm

と呼ばれています。この仕様はしばし

A±

ば誤解されます。差動アンプ入力での実際の電圧を(得に

入力電圧基準に)決めるのはかなり困難です。アンプ入力

電圧(VA±)は変数 V

IN, cm

、 β、 V

が既知の時、βsが異な

OCM

る場合は一般的な式 19 を使い、βsが同じ場合は簡略化し

た式 20 を使って計算することができます。

V

V

ββ

VorV

acm

A

±

acm

A

V

は常に入力信号のスケールを小さくしたバージョンで

A

21

=

VVorV

cmIN

,

±

OCM

IP

β

ββ

ββ

+

21

VV

(20)

ICMOCM

ある(図 4 に示すように)事に注意してください。入力同

相電圧範囲はアンプのタイプによって異なります。アナロ

グ・デバイセズ(株)の高速差動 ADC ドライバには

ICMVR が電源の中点を中心に設定されているもの

(centered)と ICMVR の中点が電源の中点からシフトされ

たもの(shifted)の 2 種類の入力段構成があります。ICMVR

が電源の中点を中心に設定されている ADC ドライバは

各々の電源レールから約1V のヘッドルームがあります。

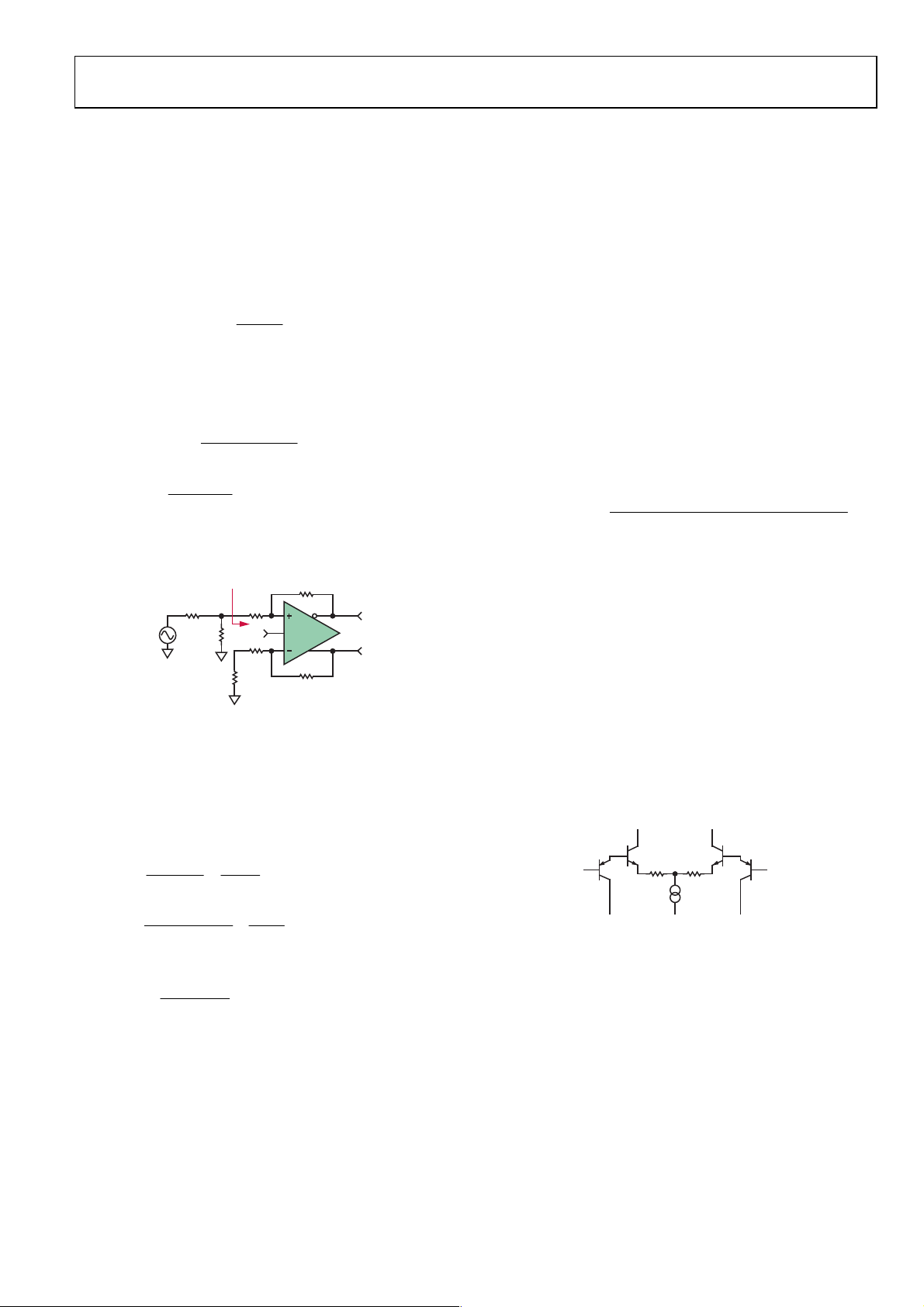

(それ故”centered”と呼ばれます)ICMVR の中点がシフト

された入力段には2つのトランジスタが追加されており、

入力が–V

レールにより近くスウィングできるようになっ

S

ています。図 10 は代表的な差動アンプの簡略化した入力

回路を示します。 (Q2 と Q3)。

A

–IN +IN

Q2 Q3

Q1 Q4

図 10.シフトされた ICMVRの簡略化した差動アンプ

ICMVR をシフトした入力回路構成の差動アンプは、例え

単電源駆動でもバイポーラ入力信号の処理が可能で、入力

がグラウンド又はそれ以下になる単電源アプリケーション

に十分対応できます。 入力に追加した PNP トランジス

タ(Q1 と Q4)により、差動ペアへ入力する入力電圧が1ト

ランジスタ Vbe分上にシフトします。 例えば –IN に–0.3 V

を印加した時、A点は 0.7 V になり差動ペアが正常に動作

します。PNP(入力段)が無い場合は、A点が–0.3 V とな

り NPN 差動ペアが逆バイアスとなり通常動作が停止しま

す。

IN, se

ββ

21IN12

の

)1(1V2

(19)

Rev. 0 | Page 5 of 16

Loading...

Loading...