REV. D

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

AMP01*

Low Noise, Precision

Instrumentation Amplifier

GENERAL DESCRIPTION

The AMP01 is a monolithic instrumentation amplifier designed

for high-precision data acquisition and instrumentation applications. The design combines the conventional features of an

instrumentation amplifier with a high current output stage. The

output remains stable with high capacitance loads (1 µF), a

unique ability for an instrumentation amplifier. Consequently,

the AMP01 can amplify low level signals for transmission

through long cables without requiring an output buffer. The output

stage may be configured as a voltage or current generator.

Input offset voltage is very low (20 µV), which generally elimi-

nates the external null potentiometer. Temperature changes

have minimal effect on offset; TCV

IOS

is typically 0.15 µV/°C.

Excellent low-frequency noise performance is achieved with a

minimal compromise on input protection. Bias current is very

low, less than 10 nA over the military temperature range. High

common-mode rejection of 130 dB, 16-bit linearity at a gain of

1000, and 50 mA peak output current are achievable simultaneously. This combination takes the instrumentation amplifier

one step further towards the ideal amplifier.

AC performance complements the superb dc specifications. The

AMP01 slews at 4.5 V/µs into capacitive loads of up to 15 nF,

settles in 50 µs to 0.01% at a gain of 1000, and boasts a healthy

26 MHz gain-bandwidth product. These features make the

AMP01 ideal for high speed data acquisition systems.

Gain is set by the ratio of two external resistors over a range of

0.1 to 10,000. A very low gain temperature coefficient of

10 ppm/°C is achievable over the whole gain range. Output

voltage swing is guaranteed with three load resistances; 50 Ω,

500 Ω, and 2 kΩ. Loaded with 500 Ω, the output delivers

±13.0 V minimum. A thermal shutdown circuit prevents de-

struction of the output transistors during overload conditions.

The AMP01 can also be configured as a high performance operational amplifier. In many applications, the AMP01 can be

used in place of op amp/power-buffer combinations.

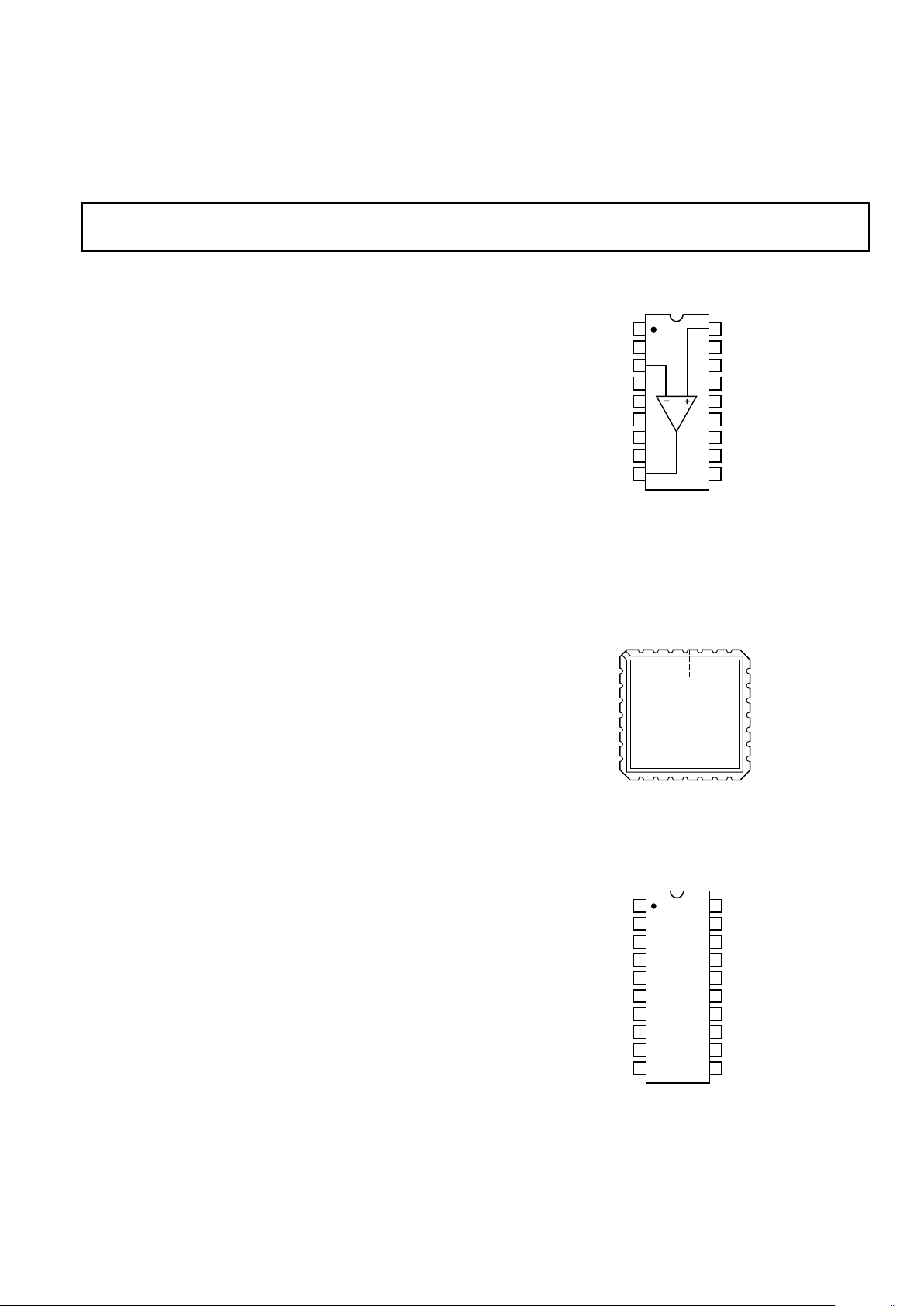

PIN CONFIGURATIONS

18-Lead Cerdip

TOP VIEW

(Not to Scale)

18

17

16

15

14

13

12

11

10

1

2

3

4

5

6

7

8

9

AMP01

OUTPUT

REFERENCE

R

G

R

G

–IN

V

OOS

NULL

SENSE

TEST PIN*

V

OOS

NULL

–V

OP

V–

+IN

V

IOS

NULL

V

IOS

NULL

R

S

V+

+V

OP

R

S

*MAKE NO ELECTRICAL CONNECTION

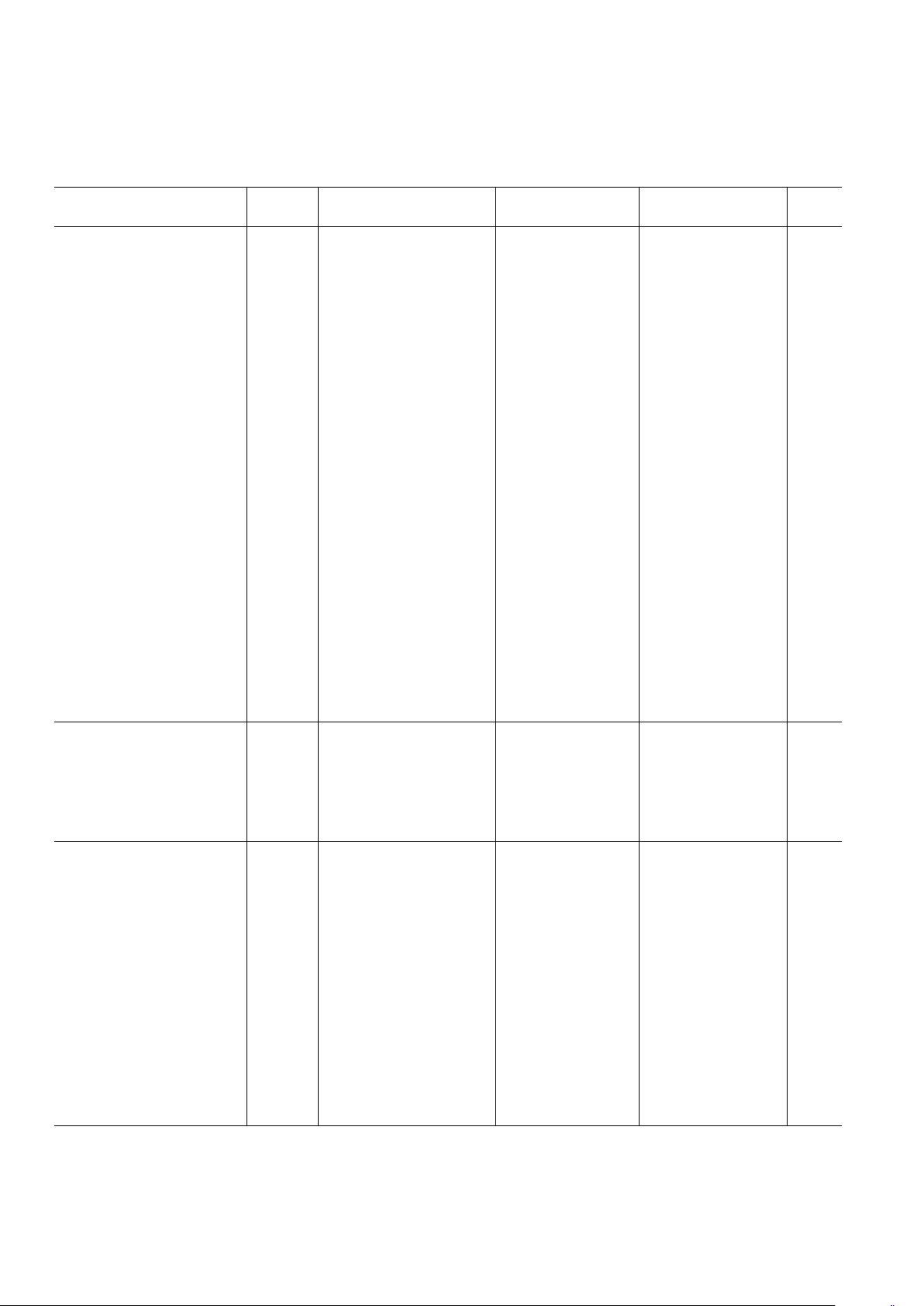

AMP01 BTC/883

28-Terminal LCC

NC = NO CONNECT

TOP VIEW

(Not to Scale)

28 27123426

25

21

22

23

24

19

20

5

6

7

8

9

10

11

12

13 14 15 16 17 18

AMP01

NC

V

OOS

NULL

NC

V

OOS

NULL

NC

TEST PIN*

NC

V

IOS

NULL

NC

R

S

R

S

+V

OP

NC

V+

–IN

R

G

R

G

NC

+IN

NC

V

IOS

NULL

SENSE

REF

OUT

NC

–V

OP

NC

V–

*MAKE NO ELECTRICAL CONNECTION

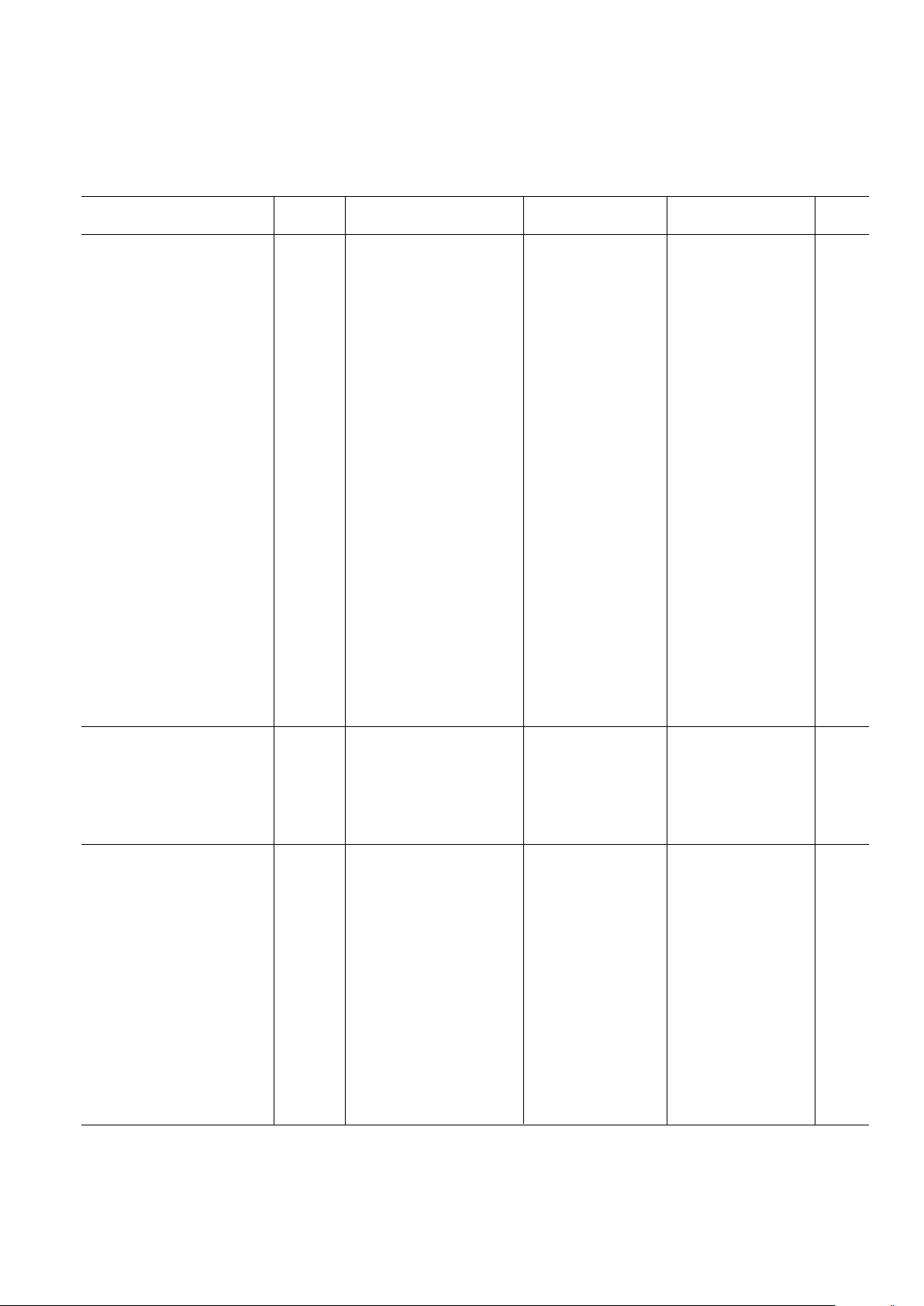

20-Lead SOIC

TOP VIEW

(Not to Scale)

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

10

AMP01

–V

OP

OUTPUT

REFERENCE

TEST PIN*

–IN

V

OOS

NULL

SENSE

TEST PIN*

V

OOS

NULL

V–

V+

+V

OP

TEST PIN*

+IN

V

IOS

NULL

R

S

R

S

R

G

R

G

V

IOS

NULL

*MAKE NO ELECTRICAL CONNECTION

FEATURES

Low Offset Voltage: 50 V Max

Very Low Offset Voltage Drift: 0.3 V/ⴗC Max

Low Noise: 0.12 V p-p (0.1 Hz to 10 Hz)

Excellent Output Drive: ⴞ10 V at ⴞ50 mA

Capacitive Load Stability: to 1 F

Gain Range: 0.1 to 10,000

Excellent Linearity: 16-Bit at G = 1000

High CMR: 125 dB min (G = 1000)

Low Bias Current: 4 nA Max

May Be Configured as a Precision Op Amp

Output-Stage Thermal Shutdown

Available in Die Form

*Protected under U.S. Patent Numbers 4,471,321 and 4,503,381.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

REV. D–2–

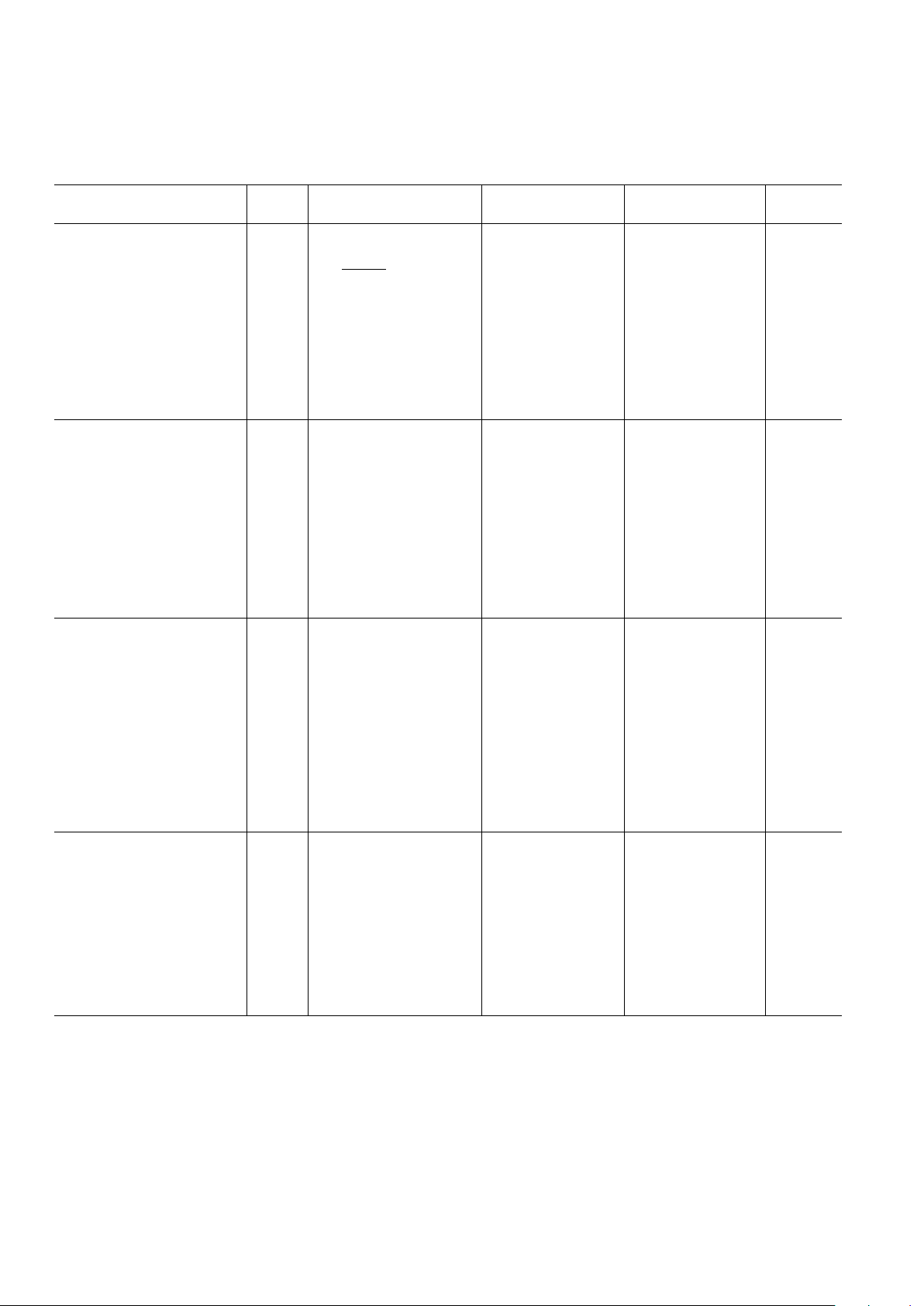

AMP01–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(@ VS = ⴞ15 V, RS = 10 k⍀, RL = 2 k⍀, TA = +25ⴗC, unless otherwise noted)

AMP01A AMP01B

Parameter Symbol Conditions Min Typ Max Min Typ Max Units

OFFSET VOLTAGE

Input Offset Voltage V

IOS

T

A

= +25°C 2050 40100 µV

–55°C ≤ T

A

≤ +125°C 4080 60150 µV

Input Offset Voltage Drift TCV

IOS

–55°C ≤ TA ≤ +125°C 0.15 0.3 0.3 1.0 µV/°C

Output Offset Voltage V

OOS

T

A

= +25°C1326mV

–55°C ≤ T

A

≤ +125°C36610mV

Output Offset Voltage Drift TCV

OOSRG

=

∞

–55°C ≤ TA ≤ +125°C 2050 50120 µV/°C

Offset Referred to Input PSR G = 1000 120 130 110 120 dB

vs. Positive Supply G = 100 110 130 100 120 dB

V+ = +5 V to +15 V G = 10 95 110 90 100 dB

G = 1 75 90 70 80 dB

–55°C ≤ T

A

≤ +125°C

G = 1000 120 130 110 120 dB

G = 100 110 130 100 120 dB

G = 10 95 110 90 100 dB

G = 1 75 90 70 80 dB

Offset Referred to Input PSR G = 1000 105 125 105 115 dB

vs. Negative Supply G = 100 90 105 90 95 dB

V– = –5 V to –15 V G = 10 70 85 70 75 dB

G = 1 50 65 50 60 dB

–55°C ≤ T

A

≤ +125°C

G = 1000 105 125 105 115 dB

G = 100 90 105 90 95 dB

G = 10 70 85 70 75 dB

G = 1 50 85 50 60 dB

Input Offset Voltage Trim

Range V

S

= ±4.5 V to ±18 V

1

±6 ±6mV

Output Offset Voltage Trim

Range V

S

= ±4.5 V to ±18 V

1

±100 ±100 mV

INPUT CURRENT

Input Bias Current I

B

T

A

= +25°C1426nA

–55°C ≤ T

A

≤ +125°C410615nA

Input Bias Current Drift TCI

B

–55°C ≤ TA ≤ +125°C 40 50 pA/°C

Input Offset Current I

OS

T

A

= +25°C 0.2 1.0 0.5 2.0 nA

–55°C ≤ T

A

≤ +125°C 0.5 3.0 1.0 6.0 nA

Input Offset Current Drift TCI

OS

–55°C ≤ TA ≤ +125°C 3 5 pA/°C

INPUT

Input Resistance R

IN

Differential, G = 1000 1 1 GΩ

Differential, G ≤ 100 10 10 GΩ

Common Mode, G = 1000 20 20 GΩ

Input Voltage Range IVR T

A

= +25°C

2

±10.5 ±10.5 V

–55°C ≤ T

A

≤ +125°C ±10.0 ±10.0 V

Common-Mode Rejection CMR V

CM

= ±10 V, 1 kΩ

Source Imbalance

G = 1000 125 130 115 125 dB

G = 100 120 130 110 125 dB

G = 10 100 120 95 110 dB

G = 1 85 100 75 90 dB

–55°C ≤ T

A

≤ +125°C

G = 1000 120 125 110 120 dB

G = 100 115 125 105 120 dB

G = 10 95 115 90 105 dB

G = 1 80 95 75 90 dB

NOTES

1

V

IOS

and V

OOS

nulling has minimal affect on TCV

IOS

and TCV

OOS

respectively.

2

Refer to section on common-mode rejection.

Specifications subject to change without notice.

ELECTRICAL CHARACTERISTICS

AMP01E AMP01F/G

Parameter Symbol Conditions Min Typ Max Min Typ Max Units

OFFSET VOLTAGE

Input Offset Voltage V

IOS

T

A

= +25°C 2050 40100 µV

T

MIN

≤ TA ≤ T

MAX

40 80 60 150 µV

Input Offset Voltage Drift TCV

IOS

T

MIN

≤ TA ≤ T

MAX

1

0.15 0.3 0.3 1.0 µV/°C

Output Offset Voltage V

OOS

T

A

= +25°C1326mV

T

MIN

≤ TA ≤ T

MAX

36 610 mV

Output Offset Voltage Drift TCV

OOSRG

=

∞

1

T

MIN

≤ TA ≤ T

MAX

20 100 50 120 µV/°C

Offset Referred to Input PSR G = 1000 120 130 110 120 dB

vs. Positive Supply G = 100 110 130 100 120 dB

V+ = +5 V to +15 V G = 10 95 110 90 100 dB

G = 1 75 90 70 80 dB

T

MIN

≤ TA ≤ T

MAX

G = 1000 120 130 110 120 dB

G = 100 110 130 100 120 dB

G = 10 95 110 90 100 dB

G = 1 75 90 70 80 dB

Offset Referred to Input PSR G = 1000 110 125 105 115 dB

vs. Negative Supply G = 100 95 105 90 95 dB

V– = –5 V to –15 V G = 10 75 85 70 75 dB

G = 1 55 65 50 60 dB

T

MIN

≤ TA ≤ T

MAX

G = 1000 110 125 105 115 dB

G = 100 95 105 90 95 dB

G = 10 75 85 70 75 dB

G = 1 55 85 50 60 dB

Input Offset Voltage Trim

Range V

S

= ±4.5 V to ±18 V

2

±6 ±6mV

Output Offset Voltage Trim

Range V

S

= ±4.5 V to ±18 V

2

±100 ±100 mV

INPUT CURRENT

Input Bias Current I

B

T

A

= +25°C1426mV

T

MIN

≤ TA ≤ T

MAX

410 615 mV

Input Bias Current Drift TCI

B

T

MIN

≤ TA ≤ T

MAX

40 50 pA/°C

Input Offset Current I

OS

T

A

= +25°C 0.2 1.0 0.5 2.0 mV

T

MIN

≤ TA ≤ T

MAX

0.5 3.0 1.0 6.0 mV

Input Offset Current Drift TCI

OS

T

MIN

≤ TA ≤ T

MAX

3 5 pA/°C

INPUT

Input Resistance R

IN

Differential, G = 1000 1 1 GΩ

Differential, G ≤ 100 10 10 GΩ

Common Mode, G = 1000 20 20 GΩ

Input Voltage Range IVR T

A

= +25°C

3

±10.5 ±10.5 V

T

MIN

≤ TA ≤ T

MAX

±10.0 ±10.0 V

Common-Mode Rejection CMR V

CM

= ±10 V, 1 kΩ

Source Imbalance

G = 1000 125 130 115 125 dB

G = 100 120 130 110 125 dB

G = 10 100 120 95 110 dB

G = 1 85 100 75 90 dB

T

MIN

≤ TA ≤ T

MAX

G = 1000 120 125 110 120 dB

G = 100 115 125 105 120 dB

G = 10 95 115 90 105 dB

G = 1 80 95 75 90 dB

NOTES

1

Sample tested.

2

V

IOS

and V

OOS

nulling has minimal affect on TCV

IOS

and TCV

OOS

, respectively.

3

Refer to section on common-mode rejection.

Specifications subject to change without notice.

(@ VS = ⴞ15 V, RS = 10 k⍀, RL = 2 k⍀, T

A

= +25ⴗC, –25ⴗC ≤

T

A

≤ +85ⴗC for E, F

grades, 0ⴗC ≤ TA ≤ +70ⴗC for G grade, unless otherwise noted)

AMP01

–3–

REV. D

AMP01

–4–

REV. D

ELECTRICAL CHARACTERISTICS

(@ VS = ⴞ15 V, RS = 10 k⍀, RL = 2 k⍀, TA = +25ⴗC, unless otherwise noted)

AMP01A/E AMP01B/F/G

Parameter Symbol Conditions Min Typ Max Min Typ Max Units

GAIN

Gain Equation Accuracy G =

20 × R

S

R

G

0.3 0.6 0.5 0.8 %

Accuracy Measured

from G = 1 to 1000

Gain Range G 0.1 10k 0.1 10k V/V

Nonlinearity G = 1000

1

0.0007 0.005 0.0007 0.005 %

G = 100

1

0.005 0.005 %

G = 10

1

0.005 0.007 %

G = 1

1

0.010 0.015 %

Temperature Coefficient G

TC

1 ≤ G ≤ 1000

1, 2

5 10 5 15 ppm°C

OUTPUT RATING

Output Voltage Swing V

OUT

R

L

= 2 kΩ±13.0 ±13.8 ±13.0 ±13.8 V

R

L

= 500 Ω±13.0 ±13.5 ±13.0 ±13.5 V

R

L

= 50 Ω±2.5 ±4.0 ±2.5 ±4.0 V

R

L

= 2 kΩ Over Temp. ±12.0 ±13.8 ±12.0 ±13.8 V

R

L

= 500 Ω

3

±12.0 ±13.5 ±12.0 ±13.5 V

Positive Current Limit Output-to-Ground Short 60 100 120 60 100 120 mA

Negative Current Limit Output-to-Ground Short 60 90 120 60 90 120 mA

Capacitive Load Stability 1 ≤ G ≤ 1000

No Oscillations

1

0.1 1 0.1 1 µF

Thermal Shutdown

Temperature Junction Temperature 165 165 °C

NOISE

Voltage Density, RTI e

n

fO = 1 kHz

e

n

G = 1000 5 5 nV/√Hz

e

n

G = 100 10 10 nV/√Hz

e

n

G = 10 59 59 nV/√Hz

e

n

G = 1 540 540 nV/√Hz

Noise Current Density, RTI i

n

f

O

= 1 kHz, G = 1000 0.15 0.15 pA/√Hz

Input Noise Voltage e

n

p-p 0.1 Hz to 10 Hz

e

n

p-p G = 1000 0.12 0.12 µV p-p

e

n

p-p G = 100 0.16 0.16 µV

p-p

e

n

p-p G = 10 1.4 1.4 µV p-p

e

n

p-p G = 1 13 13 µV p-p

Input Noise Current in p-p 0.1 Hz to 10 Hz, G = 1000 2 2 pA p-p

DYNAMIC RESPONSE

Small-Signal G = 1 570 570 kHz

Bandwidth (–3 dB) BW G = 10 100 100 kHz

G = 100 82 82 kHz

G = 1000 26 26 kHz

Slew Rate SR G = 10 3.5 4.5 3.0 4.5 V/µs

Settling Time t

S

To 0.01%, 20 V step

G = 1 12 12 µs

G = 10 13 13 µs

G = 100 15 15 µs

G = 1000 50 50 µs

NOTES

1

Guaranteed by design.

2

Gain tempco does not include the effects of gain and scale resistor tempco match.

3

–55°C ≤ TA ≤ +125°C for A/B grades, –25°C ≤ TA ≤ +85°C for E/F grades, 0°C ≤ TA ≤ 70°C for G grades.

Specifications subject to change without notice.

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AMP01AX –55°C to +125°C 18-Lead Cerdip Q-18

AMP01AX/883C –55°C to +125°C 18-Lead Cerdip Q-18

AMP01BTC/883C –55°C to +125°C 28-Terminal LCC E-28A

AMP01BX –55°C to +125°C 18-Lead Cerdip Q-18

AMP01BX/883C –55°C to +125°C 18-Lead Cerdip Q-18

AMP01EX –25°C to +85°C 18-Lead Cerdip Q-18

AMP01FX –25°C to +85°C 18-Lead Cerdip Q-18

AMP01GBC Die

AMP01GS 0°C to +70°C 20-Lead SOIC R-20

AMP01GS-REEL 0°C to +70°C13" Tape and Reel R-20

AMP01NBC Die

5962-8863001VA* –55°C to +125°C 18-Lead Cerdip Q-18

5962-88630023A* –55°C to +125°C 28-Terminal LCC E-28A

5962-8863002VA* –55°C to +125°C 18-Lead Cerdip Q-18

*Standard military drawing available.

ELECTRICAL CHARACTERISTICS

(@ VS = ⴞ15 V, RS = 10 k⍀, RL = 2 k⍀, TA = +25ⴗC, unless otherwise noted)

AMP01A/E AMP01B/F/G

Parameter Symbol Conditions Min Typ Max Min Typ Max Units

SENSE INPUT

Input Resistance R

IN

35 50 65 35 50 65 kΩ

Input Current I

IN

Referenced to V– 280 280 µA

Voltage Range (Note 1) –10.5 +15 –10.5 +15 V

REFERENCE INPUT

Input Resistance R

IN

35 50 65 35 50 65 kΩ

Input Current I

IN

Referenced to V– 280 280 µA

Voltage Range (Note 1) –10.5 +15 –10.5 +15 V

Gain to Output 1 1 V/V

POWER SUPPLY –25°C ≤ T

A

≤ +85°C for E/F Grades, –55°C ≤ TA ≤ +125°C for A/B Grades

Supply Voltage Range V

S

+V linked to +V

OP

±4.5 ±18 ±4.5 ±18 V

V

S

–V linked to –V

OP

±4.5 ±18 ±4.5 ±18 V

Quiescent Current I

Q

+V linked to +V

OP

3.0 4.8 3.0 4.8 mA

I

Q

–V linked to –V

OP

3.4 4.8 3.4 4.8 mA

NOTE

1

Guaranteed by design.

Specifications subject to change without notice.

AMP01

–5–

REV. D

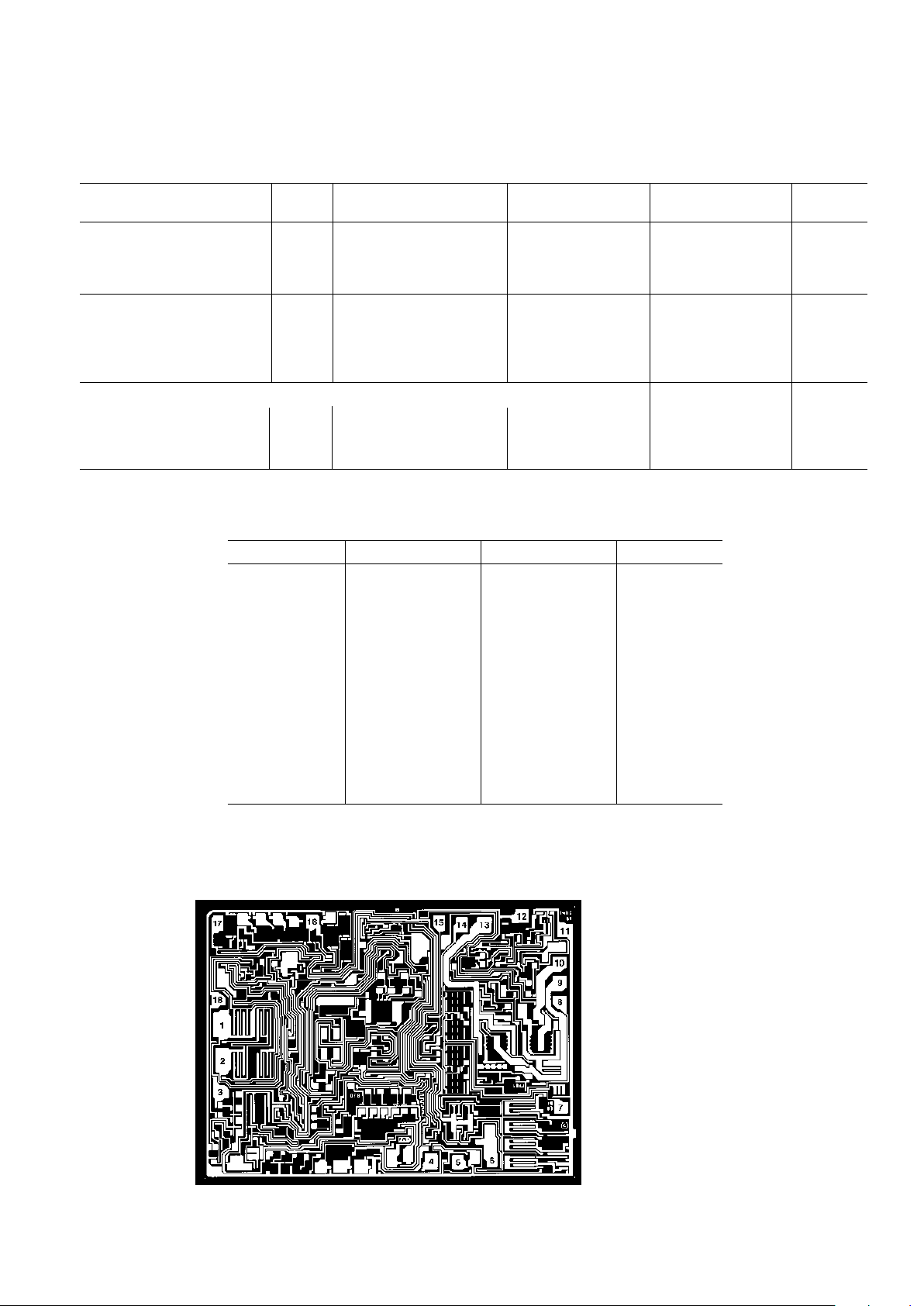

1. R

G

2. R

G

3. –INPUT

4. V

OOS

NULL

5. V

OOS

NULL

6. TEST PIN*

7. SENSE

8. REFERENCE

9. OUTPUT

10. V– (OUTPUT)

11. V–

12. V+

13. V+ (OUTPUT)

14. R

S

15. R

S

16. V

IOS

NULL

17. V

IOS

NULL

18. +INPUT

*MAKE NO ELECTRICAL CONNECTION

DICE CHARACTERISTICS

Die Size 0.111 × 0.149 inch, 16,539 sq. mils

(2.82 × 3.78 mm, 10.67 sq. mm)

AMP01

–6–

REV. D

WAFER TEST LIMITS

(@ VS = ⴞ15 V, RS = 10 k⍀, RL = 2 k⍀, TA = +25ⴗC, unless otherwise noted)

AMP01NBC AMP01GBC

Parameter Symbol Conditions Limit Limit Units

Input Offset Voltage V

IOS

60 120 µV max

Output Offset Voltage V

OOS

4 8 mV max

Offset Referred to Input PSR V+ = +5 V to +15 V dB min

vs. Positive Supply G = 1000 120 110 dB min

G = 100 110 100 dB min

G = 10 95 90 dB min

G = 1 75 70 dB min

Offset Referred to Input PSR V– = –5 V to –15 V dB min

vs. Negative Supply G = 1000 105 105 dB min

G = 100 90 90 dB min

G = 10 70 70 dB min

G = 1 50 50 dB min

Input Bias Current I

B

48nA max

Input Offset Current I

OS

13nA max

Input Voltage Range IVR Guaranteed by CMR Tests ±10 ±10 V min

Common Mode Rejection CMR V

CM

= ±10 V dB min

G = 1000 125 115 dB min

G = 100 120 110 dB min

G = 10 100 95 dB min

G = 1 85 75 dB min

Gain Equation Accuracy G =

20 × R

S

R

G

0.6 0.8 % max

Output Voltage Swing V

OUT

R

L

= 2 kΩ±13 ±13 V min

V

OUT

R

L

= 500 Ω±13 ±13 V min

V

OUT

R

L

= 50 Ω±2.5 ±2.5 V min

Output Current Limit Output to Ground Short ±60 ±60 mA min

Output Current Limit Output to Ground Short ±120 ±120 mA max

Quiescent Current I

Q

+V Linked to +V

OP

4.8 4.8 mA max

–V Linked to –V

OP

4.8 4.8 mA max

NOTE

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed

for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

V

IOS

NULL

R

GAIN

R

SCALE

V

OOS

NULL

R1

47.5kV

R2

2.5kV

R4

2.5kV

R3

47.5kV

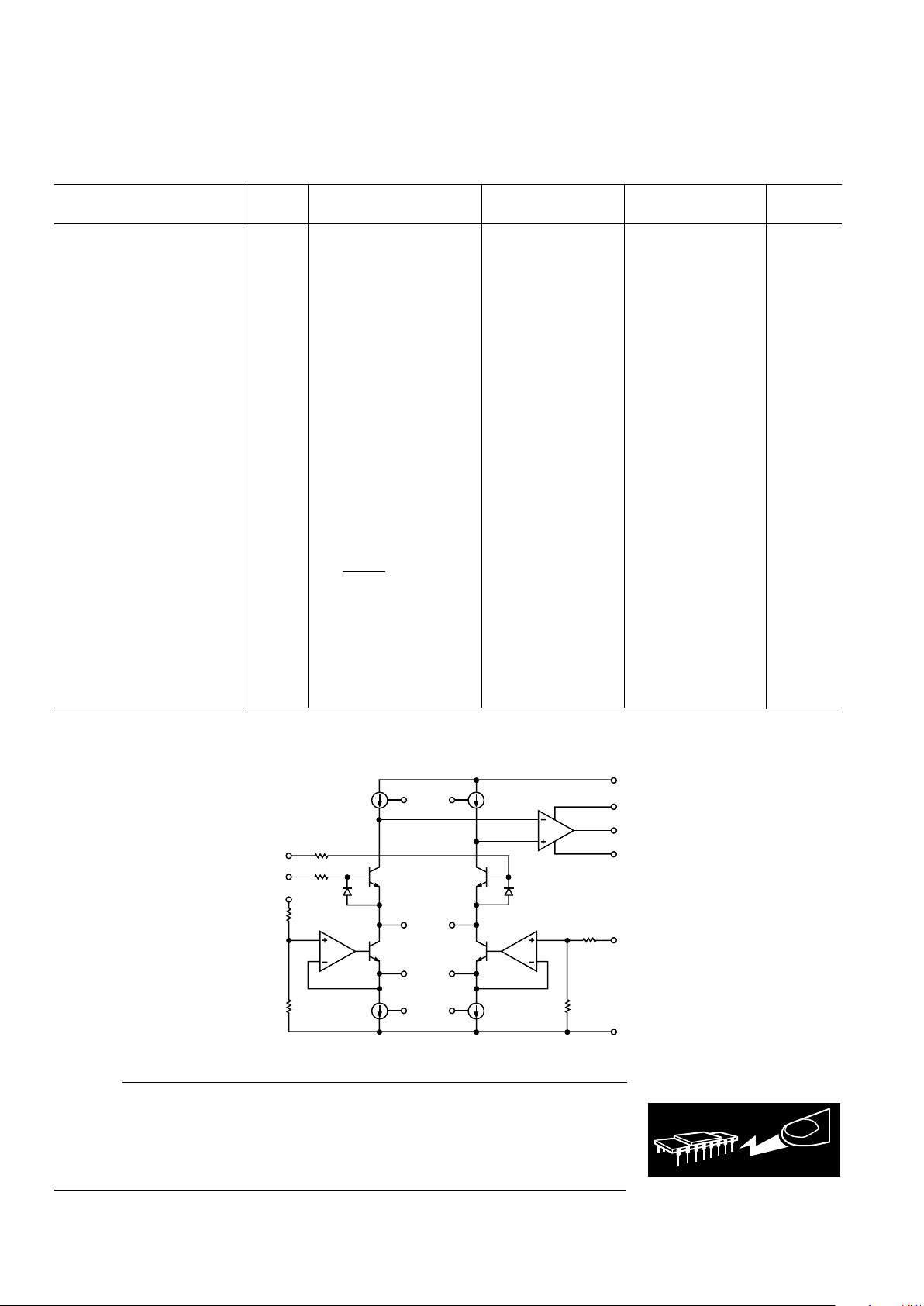

A1

A3A2

Q1 Q2

250V

250V

–IN

+IN

REFERENCE

V+

+V

OP

OUTPUT

–V

OP

SENSE

V–

Figure 1. Simplified Schematic

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AMP01 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

AMP01

–7–

REV. D

ELECTRICAL CHARACTERISTICS

(@ VS = ⴞ15 V, RS = 10 k⍀, RL = 2 k⍀, TA = +25ⴗC, unless otherwise noted)

AMP01NBC AMP01GBC

Parameter Symbol Conditions Typical Typical Units

Input Offset Voltage Drift TCV

IOS

0.15 0.30 µV/°C

Output Offset Voltage Drift TCV

OOS

RG =

∞

20 50 µV/°C

Input Bias Current Drift TCI

B

40 50 pA/°C

Input Offset Current Drift TCI

OS

3 5 pA/°C

Nonlinearity G = 1000 0.0007 0.0007 %

Voltage Noise Density e

n

G = 1000

f

O

= 1 kHz 5 5 nV/√Hz

Current Noise Density i

n

G = 1000

f

O

= 1 kHz 0.15 0.15 pA/√Hz

Voltage Noise e

n

p-p G = 1000

0.1 Hz to 10 Hz 0.12 0.12 µV p-p

Current Noise i

n

p-p G = 1000 2 2 pA p-p

0.1 Hz to 10 Hz

Small-Signal Bandwidth (–3 dB) BW G = 1000 26 26 kHz

Slew Rate SR G = 10 4.5 4.5 V/µs

Settling Time t

S

To 0.01%, 20 V Step

G = 1000 50 50 µs

NOTE

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed

for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

AMP01

–8–

REV. D

TEMPERATURE – 8C

–75 –50 150

–25 0 25 75 100 12550

INPUT OFFSET VOLTAGE – mV

50

40

–40

0

–10

–20

–30

30

10

20

VS = 615V

Figure 2. Input Offset Voltage

vs. Temperature

POWER SUPPLY VOLTAGE – Volts

OUTPUT OFFSET VOLTAGE CHANGE – mV

2.5

2.0

–1.0

0

65 625610 615 620

1.0

0.5

0

–0.5

1.5

TA = +258C

Figure 5. Output Offset Voltage

Change vs. Supply Voltage

TEMPERATURE – 8C

INPUT OFFSET CURRENT – nA

0.8

–0.6

–75 –50 150

–25025 75 100 12550

0.6

0.2

0.0

–0.2

–0.4

0.4

VS = 615V

Figure 8. Input Offset Current

vs. Temperature

POWER SUPPLY VOLTAGE – Volts

INPUT OFFSET VOLTAGE – mV

8

6

–6

0

65 620610 615

2

0

–2

–4

4

TA = +258C

UNIT NO.

1

2

3

4

Figure 3. Input Offset Voltage

vs. Supply Voltage

TEMPERATURE – 8C

INPUT BIAS CURRENT – nA

5

–2

–75 –50 150

–25025 75 100 12550

4

2

1

0

–1

3

VS = 615V

Figure 6. Input Bias Current

vs. Temperature

VOLTAGE GAIN – G

COMMON-MODE REJECTION – dB

140

100

1 10k

120

10 100 1k

130

110

VS = 615V

T

A

= +258C

Figure 9. Common-Mode Rejection

vs. Voltage Gain

TEMPERATURE – 8C

–75 –50 150

–25 0 25 75 100 12550

OUTPUT OFFSET VOLTAGE – mV

5

4

–4

0

–1

–2

–3

3

1

2

–5

VS = 615V

Figure 4. Output Offset Voltage

vs. Temperature

POWER SUPPLY VOLTAGE – Volts

INPUT BIAS CURRENT – nA

2.0

1.5

–1.5

0

65 620610 615

0.5

0

–0.5

–1.0

1.0

TA = +258C

Figure 7. Input Bias Current

vs. Supply Voltage

FREQUENCY – Hz

COMMON-MODE REJECTION – dB

140

0

1 10 100k100 1k 10k

120

100

80

60

40

20

VCM = 2V p-p

V

S

= 615V

T

A

= +258C

G = 1000

G = 100

G = 1

G = 10

Figure 10. Common-Mode Rejection

vs. Frequency

–Typical Performance Characteristics

AMP01

–9–

REV. D

TEMPERATURE – 8C

COMMON-MODE INPUT VOLTAGE – Volts

16

0

–75 –50 150

–25025 75 100 12550

14

8

6

4

2

12

10

VDM = 0

VS = 615V

VS = 610V

VS = 65V

Figure 11. Common-Mode Voltage

Range vs. Temperature

LOAD RESISTANCE – V

OUITPUT VOLTAGE – Volts

18

10

10k

14

10 100 1k

16

12

8

6

4

2

0

VS = 615V

Figure 14. Maximum Output Voltage

vs. Load Resistance

FREQUENCY – Hz

VOLTAGE GAIN – dB

80

0

100 1M

40

1k 10k 100k

60

20

–20

–40

101

VS = 615V

T

A

= +258C

G = 1000

G = 100

G = 10

G = 1

Figure 17. Closed-Loop Voltage

Gain vs. Frequency

FREQUENCY – Hz

POWER SUPPLY REJECTION – dB

140

0

1 10 100k100 1k 10k

120

100

80

60

40

20

VS = 615V

T

A

= +258C

DV

S

= 61V

G = 1000

G = 100

G = 10

G = 1

Figure 12. Positive PSR

vs. Frequency

FREQUENCY – Hz

PEAK-TO-PEAK AMPLITUDE – Volts

30

10

100 1M

20

1k 10k 100k

25

15

VS = 615V

R

L

= 2kV

5

0

Figure 15. Maximum Output Swing

vs. Frequency

FREQUENCY – Hz

TOTAL HARMONIC DISTORTION – %

0.08

0.04

10k

0.06

10 100 1k

0.07

0.05

0.03

0.02

0.01

0

G = 1000

G = 100

G = 10

G = 1

VS = 615V

R

L

= 600V

V

OUT

= 20V p-p

Figure 18. Total Harmonic Distortion

vs. Frequency

FREQUENCY – Hz

POWER SUPPLY REJECTION – dB

140

0

1 10 100k100 1k 10k

120

100

80

60

40

20

VS = 615V

T

A

= +258C

DV

S

= 61V

G = 1000

G = 100

G = 10

G = 1

Figure 13. Negative PSR

vs. Frequency

FREQUENCY – Hz

OUTPUT IMPEDANCE – V

100

10 100 1M1k 10k 100k

10

1.0

0.1

0.01

0.001

VS = 615V

I

OUT

= 20mA p-p

G = 1000

G = 1

Figure 16. Closed-Loop Output

Impedance vs. Frequency

LOAD RESISTANCE – V

TOTAL HARMONIC DISTORTION – %

0.02

0.01

10k100 1k

0

VS = 615V

G = 100

f = 1kHz

V

OUT

= 20V p-p

Figure 19. Total Harmonic Distortion

vs. Load Resistance

AMP01

–10–

REV. D

LOAD CAPACITANCE – F

SLEW RATE – V/ms

6

2

100p 1m

4

1n 10n 100n

5

3

VS = 615V

1

0

Figure 21. Slew Rate vs.

Load Capacitance

VOLTAGE GAIN – G

1k

1

1k

10

1 10 100

100

VS = 615V

f = 1kHz

VOLTAGE NOISE – nV/ Hz

Figure 24. RTI Voltage Noise

Density vs. Gain

TEMPERATURE – 8C

POSITIVE SUPPLY CURRENT – mA

6

0

–75 –50 150–25 0 25 75 100 12550

5

4

3

2

1

VS = 615V

Figure 27. Positive Supply Current

vs. Temperature

VOLTAGE GAIN – G

SLEW RATE – V/ms

6

3

1k

4

1 10 100

5

2

1

0

VS = 615V

Figure 20. Slew Rate vs.

Voltage Gain

FREQUENCY – Hz

VOLTAGE NOISE – nV/ Hz

15

5

1 10k

10

10 100 1k

0

G = 1000

Figure 23. Voltage Noise Density

vs. Frequency

POWER SUPPLY VOLTAGE – Volts

NEGATIVE SUPPLY CURRENT – mA

–8

–7

0

0

65 620

610 615

–4

–3

–2

–1

–6

–5

TA = +258C

Figure 26. Negative Supply Current

vs. Supply Voltage

VOLTAGE GAIN – G

SETTLING TIME – ms

70

40

1k

50

1 10 100

60

30

20

10

VS = 615V

20V STEP

Figure 22. Settling Time to 0.01%

vs. Voltage Gain

POWER SUPPLY VOLTAGE – Volts

POSITIVE SUPPLY CURRENT – mA

8

7

0

0

65 620

610 615

4

3

2

1

6

5

TA = +258C

Figure 25. Positive Supply Current

vs. Supply Voltage

TEMPERATURE – 8C

NEGATIVE SUPPLY CURRENT – mA

–6

0

–75 –50 150–25 0 25 75 100 12550

–5

–4

–3

–2

–1

VS = 615V

V

SENSE

= V

REF

= 0V

Figure 28. Negative Supply Current

vs. Temperature

AMP01

–11–

REV. D

GAIN

The AMP01 uses two external resistors for setting voltage gain

over the range 0.1 to 10,000. The magnitudes of the scale resistor, R

S

, and gain-set resistor, RG, are related by the formula:

G = 20 × R

S/RG

, where G is the selected voltage gain (refer to

Figure 29).

REFERENCE

OUTPUT

V+

V–

R

S

R

G

+IN

–IN

VOLTAGE GAIN, G =

20 3 R

S

R

G

( )

SENSE

AMP01

14

15

13

12

7

9

8

11

10

3

2

1

18

Figure 29. Basic AMP01 Connections for Gains

0.1 to 10,000

The magnitude of RS affects linearity and output referred errors.

Circuit performance is characterized using R

S

= 10 kΩ when

operating on ±15 volt supplies and driving a ±10 volt output. R

S

may be reduced to 5 kΩ in many applications particularly when

operating on ±5 volt supplies or if the output voltage swing is

limited to ±5 volts. Bandwidth is improved with R

S

= 5 kΩ and

this also increases common-mode rejection by approximately

6 dB at low gain. Lowering the value below 5 kΩ can cause

instability in some circuit configurations and usually has no

advantage. High voltage gains between two and ten thousand

would require very low values of R

G

. For R

S

= 10 kΩ and

A

V

= 2000 we get R

G

= 100 Ω; this value is the practical lower

limit for R

G

. Below 100 Ω, mismatch of wirebond and resistor

temperature coefficients will introduce significant gain tempco

errors. Therefore, for gains above 2,000, R

G

should be kept

constant at 100 Ω and R

S

increased. The maximum gain of

10,000 is obtained with R

S

set to 50 kΩ.

Metal-film or wirewound resistors are recommended for best

results. The absolute values and TCs are not too important,

only the ratiometric parameters.

AC amplifiers require good gain stability with temperature and

time, but dc performance is unimportant. Therefore, low cost

metal-film types with TCs of 50 ppm/°C are usually adequate

for R

S

and RG. Realizing the full potential of the AMP01’s offset

voltage and gain stability requires precision metal-film or wire-

wound resistors. Achieving a 15 ppm/°C gain tempco at all gains

requires R

S

and RG temperature coefficient matching to

5 ppm/°C or better.

INPUT AND OUTPUT OFFSET VOLTAGES

Instrumentation amplifiers have independent offset voltages

associated with the input and output stages. While the initial

offsets may be adjusted to zero, temperature variations will

cause shifts in offsets. Systems with auto-zero can correct for

offset errors, so initial adjustment would be unnecessary. However, many high-gain applications don’t have auto zero. For

these applications, both offsets can be nulled, which has minimal effect on TCV

IOS

and TCV

OOS

The input offset component is directly multiplied by the amplifier gain, whereas output offset is independent of gain. Therefore, at low gain, output-offset errors dominate, while at high

gain, input-offset errors dominate. Overall offset voltage, V

OS

,

referred to the output (RTO) is calculated as follows;

V

OS

(RTO) = (V

IOS

× G) + V

OOS

(1)

where V

IOS

and V

OOS

are the input and output offset voltage

specifications and G is the amplifier gain. Input offset nulling

alone is recommended with amplifiers having fixed gain above

50. Output offset nulling alone is recommended when gain is

fixed at 50 or below.

In applications requiring both initial offsets to be nulled, the

input offset is nulled first by short-circuiting R

G

, then the output

offset is nulled with the short removed.

The overall offset voltage drift TCV

OS

, referred to the output, is

a combination of input and output drift specifications. Input

offset voltage drift is multiplied by the amplifier gain, G, and

summed with the output offset drift;

TCV

OS

(RTO) = (TCV

IOS

× G) + TCV

OOS

(2)

where TCV

IOS

is the input offset voltage drift, and TCV

OOS

is

the output offset voltage specification. Frequently, the amplifier

drift is referred back to the input (RTI), which is then equivalent to an input signal change;

TCV

OS

(RTI) = TCV

IOS

TCV

OOS

G

(3)

For example, the maximum input-referred drift of an AMP01 EX

set to G = 1000 becomes;

TCVOS (RTI ) = 0.3

µ

V/°C +

100

1000

µVC/°

= 0.4

µ

V/°C max

INPUT BIAS AND OFFSET CURRENTS

Input transistor bias currents are additional error sources that

can degrade the input signal. Bias currents flowing through the

signal source resistance appear as an additional offset voltage.

Equal source resistance on both inputs of an IA will minimize

offset changes due to bias current variations with signal voltage

and temperature. However, the difference between the two bias

currents, the input offset current, produces a nontrimmable

error. The magnitude of the error is the offset current times the

source resistance.

A current path must always be provided between the differential

inputs and analog ground to ensure correct amplifier operation.

Floating inputs, such as thermocouples, should be grounded

close to the signal source for best common-mode rejection.

AMP01

–12–

REV. D

VOLTAGE GAIN

1M

1 10k

RESISTANCE – V

10k

10 100 1k

VS = 615V

100k

1k

100

R

S

R

G

Figure 30. RG and RS Selection

Gain accuracy is determined by the ratio accuracy of RS and R

G

combined with the gain equation error of the AMP01 (0.6%

max for A/E grades).

All instrumentation amplifiers require attention to layout so

thermocouple effects are minimized. Thermocouples formed

between copper and dissimilar metals can easily destroy the

TCV

OS

performance of the AMP01 which is typically

0.15 µV/°C. Resistors themselves can generate thermoelectric

EMF’s when mounted parallel to a thermal gradient. “Vishay”

resistors are recommended because a maximum value for thermoelectric generation is specified. However, where thermal

gradients are low and gain TCs of 20 ppm–50 ppm are sufficient, general-purpose metal-film resistors can be used for R

G

and RS.

COMMON-MODE REJECTION

Ideally, an instrumentation amplifier responds only to the difference between the two input signals and rejects commonmode voltages and noise. In practice, there is a small change in

output voltage when both inputs experience the same commonmode voltage change; the ratio of these voltages is called the

common-mode gain. Common-mode rejection (CMR) is the

logarithm of the ratio of differential-mode gain to commonmode gain, expressed in dB. CMR specifications are normally

measured with a full-range input voltage change and a specified

source resistance unbalance.

The current-feedback design used in the AMP01 inherently

yields high common-mode rejection. Unlike resistive feedback

designs, typified by the three-op-amp IA, the CMR is not degraded by small resistances in series with the reference input. A

slight, but trimmable, output offset voltage change results from

resistance in series with the reference input.

The common-mode input voltage range, CMVR, for linear

operation may be calculated from the formula:

CMVR = ±

IVR –

|V

OUT

|

2G

(4)

IVR is the data sheet specification for input voltage range; V

OUT

is the maximum output signal; G is the chosen voltage gain. For

example, at +25°C, IVR is specified as ±10.5 volt minimum

with ±15 volt supplies. Using a ±10 volt maximum swing out-

put and substituting the figures in (4) simplifies the formula to:

CMVR = ±

10.5 –

5

G

(5)

For all gains greater than or equal to 10, CMVR is ±10 volt

minimum; at gains below 10, CMVR is reduced.

ACTIVE GUARD DRIVE

Rejection of common-mode noise and line pick-up can be improved by using shielded cable between the signal source and

the IA. Shielding reduces pick-up, but increases input capacitance, which in turn degrades the settling-time for signal

changes. Further, any imbalance in the source resistance between the inverting and noninverting inputs, when capacitively

loaded, converts the common-mode voltage into a differential

voltage. This effect reduces the benefits of shielding. AC

common-mode rejection is improved by “bootstrapping” the

input cable capacitance to the input signal, a technique called

“guard driving.” This technique effectively reduces the input

capacitance. A single guard-driving signal is adequate at gains

above 100 and should be the average value of the two inputs.

The value of external gain resistor R

G

is split between two resis-

tors R

G1

and RG2; the center tap provides the required signal to

drive the buffer amplifier (Figure 31).

GROUNDING

The majority of instruments and data acquisition systems have

separate grounds for analog and digital signals. Analog ground

may also be divided into two or more grounds which will be tied

together at one point, usually the analog power-supply ground.

In addition, the digital and analog grounds may be joined, normally at the analog ground pin on the A-to-D converter. Following this basic grounding practice is essential for good circuit

performance (Figure 32).

Mixing grounds causes interactions between digital circuits and

the analog signals. Since the ground returns have finite resistance and inductance, hundreds of millivolts can be developed

between the system ground and the data acquisition components. Using separate ground returns minimizes the current flow

in the sensitive analog return path to the system ground point.

Consequently, noisy ground currents from logic gates do not

interact with the analog signals.

Inevitably, two or more circuits will be joined together with their

grounds at differential potentials. In these situations, the differential input of an instrumentation amplifier, with its high CMR,

can accurately transfer analog information from one circuit to

another.

SENSE AND REFERENCE TERMINALS

The sense terminal completes the feedback path for the instrumentation amplifier output stage and is normally connected

directly to the output. The output signal is specified with respect to the reference terminal, which is normally connected to

analog ground.

AMP01

–13–

REV. D

VOLTAGE GAIN, G =

20 3 R

S

R

G1

( )

AV = 500 WITH COMPONENTS SHOWN

*

+15V

C1

0.047mF

+

C5

10mF

R5

*

*

SENSE

OUTPUT

*SOLDER LINK

REFERENCE

*

GROUND

R3

C4

0.047mF

+

C6

10mF

C2

0.047mF

VR1

100kV

VR2

100kV

R

G1

400V

+IN

–IN

R

G3

200V

R

G2

200V

741

+15V

–15V

GUARD

DRIVE

R2

1MV

R1

1MV

SIGNAL

GROUND

R

S

10kV

C3

0.047mF

–15V

R4

R

S

NC

*

AMP01

R

S

V

IOS

NULL

V

OOS

NULL

V+

V–

R

G

R

G

15

14

6

13

12

7

18

1

2

3

16

17

4

5

10

11

8

9

7

6

4

3

2

Figure 31. AMP01 Evaluation Circuit Showing Guard-Drive Connection

HOLD

CAPACITOR

C = 0.047mF CERAMIC CAPACITORS

DIGITAL

DATA

OUTPUT

ANALOG

GROUND

DIGITAL

GROUND

ADC

CC

7

8

9

OUTPUT

REFERENCE

SMP-11

SAMPLE AND HOLD

C

+

4.7mF

DIGITAL

GROUND

CC

0V +5V

DIGITAL

POWER SUPPLY

–15V+15V 0V

ANALOG

POWER SUPPLY

CC

AMP01

Figure 32. Basic Grounding Practice

AMP01

–14–

REV. D

If heavy output currents are expected and the load is situated

some distance from the amplifier, voltage drops due to track or

wire resistance will cause errors. Voltage drops are particularly

troublesome when driving 50 Ω loads. Under these conditions,

the sense and reference terminals can be used to “remote sense”

the load as shown in Figure 33. This method of connection puts

the I×R drops inside the feedback loop and virtually eliminates

the error. An unbalance in the lead resistances from the sense

and reference pins does not degrade CMR, but will change the

output offset voltage. For example, a large unbalance of 3 Ω will

change the output offset by only 1 mV.

DRIVING 50 ⍀ LOADS

Output currents of 50 mA are guaranteed into loads of up to

50 Ω and 26 mA into 500 Ω. In addition, the output is stable

and free from oscillation even with a high load capacitance. The

combination of these unique features in an instrumentation

amplifier allows low-level transducer signals to be conditioned

and directly transmitted through long cables in voltage or current form. Increased output current brings increased internal

dissipation, especially with 50 Ω loads. For this reason, the

power-supply connections are split into two pairs; pins 10 and

13 connect to the output stage only and pins 11 and 12 provide

power to the input and following stages. Dual supply pins allow

dropper resistors to be connected in series with the output stage

so excess power is dissipated outside the package. Additional

decoupling is necessary between pins 10 and 13 to ground to

maintain stability when dropper resistors are used. Figure 34

shows a complete circuit for driving 50 Ω loads.

AMP01

+IN

–IN

R

G

18

1

2

3

14

15

12

13

7

9

8

10

11

V–

V+

SENSE

REFERENCE

*

*

OUTPUT

GROUND

TWISTED

PAIRS

REMOTE

LOAD

IN4148 DIODES ARE OPTIONAL. DIODES LIMIT THE OUTPUT

VOLTAGE EXCURSION IF SENSE AND/OR REFERENCE LINES

BECOME DISCONNECTED FROM THE LOAD.

*

R

S

Figure 33. Remote Load Sensing

+IN

–IN

R

G

AMP01

14

15

12

13

7

9

8

10

11

18

1

2

3

R

S

5kV

R1

130V

1W

C1

0.047mF

0.047mF

+15V

SENSE

REFERENCE

V

OUT

63V MAX

50V

LOAD

C2

0.047mF

R2

130V

1W

0.047mF

–15V

POWER BANDWIDTH, G = 100, 130kHz

POWER BANDWIDTH, G = 10, 200kHz

T.H.D.~0.04% @ 1kHz, 2Vrms

VOLTAGE GAIN, G =

( )

20 3 R

S

R

G

RESISTERS R1 AND R2 REDUCE IC DISSIPATION

Figure 34. Driving 50 Ω Loads

AMP01

–15–

REV. D

HEATSINKING

To maintain high reliability, the die temperature of any IC

should be kept as low as practicable, preferably below 100°C.

Although most AMP01 application circuits will produce very

little internal heat — little more than the quiescent dissipation

of 90 mW—some circuits will raise that to several hundred

milliwatts (for example, the 4-20 mA current transmitter application, Figure 37). Excessive dissipation will cause thermal

shutdown of the output stage thus protecting the device from

damage. A heatsink is recommended in power applications to

reduce the die temperature.

Several appropriate heatsinks are available; the Thermalloy

6010B is especially easy to use and is inexpensive. Intended for

dual-in-line packages, the heatsink may be attached with a

cyanoacrylate adhesive. This heatsink reduces the thermal resistance between the junction and ambient environment to ap-

proximately 80°C/W. Junction (die) temperature can then be

calculated by using the relationship:

P

d

=

TJ– T

A

θ

JA

where TJ and TA are the junction and ambient temperatures

respectively, θ

JA

is the thermal resistance from junction to ambi-

ent, and P

d

is the device’s internal dissipation.

OVERVOLTAGE PROTECTION

Instrumentation amplifiers invariably sit at the front end of

instrumentation systems where there is a high probability of

exposure to overloads. Voltage transients, failure of a transducer, or removal of the amplifier power supply while the signal

source is connected may destroy or degrade the performance of

an unprotected amplifier. Although it is impractical to protect

an IC internally against connection to power lines, it is relatively

easy to provide protection against typical system overloads.

The AMP01 is internally protected against overloads for gains

of up to 100. At higher gains, the protection is reduced and

some external measures may be required. Limited internal overload protection is used so that noise performance would not be

significantly degraded.

AMP01 noise level approaches the theoretical noise floor of the

input stage which would be 4 nV/√Hz at 1 kHz when the gain is

set at 1000. Noise is the result of shot noise in the input devices

and Johnson noise in the resistors. Resistor noise is calculated

from the values of R

G

(200 Ω at a gain of 1000) and the input

protection resistors (250 Ω). Active loads for the input transistors contribute less than 1 nV/√Hz of noise. The measured noise

level is typically 5 nV/√Hz.

Diodes across the input transistor’s base-emitter junctions,

combined with 250 Ω input resistors and R

G

, protect against

differential inputs of up to ±20 V for gains of up to 100. The

diodes also prevent avalanche breakdown that would degrade

the I

B

and IOS specifications. Decreasing the value of RG for

gains above 100 limits the maximum input overload protection

to ±10 V.

External series resistors could be added to guard against higher

voltage levels at the input, but resistors alone increase the input

noise and degrade the signal-to-noise ratio, especially at high

gains.

Protection can also be achieved by connecting back-to-back

9.1 V Zener diodes across the differential inputs. This technique

does not affect the input noise level and can be used down to a

gain of 2 with minimal increase in input current. Although

voltage-clamping elements look like short circuits at the limiting

voltage, the majority of signal sources provide less than 50 mA,

producing power levels that are easily handled by low-power

Zeners.

Simultaneous connection of the differential inputs to a low

impedance signal above 10 V during normal circuit operation is

unlikely. However, additional protection involves adding 100 Ω

current-limiting resistors in each signal path prior to the voltage

clamp, the resistors increase the input noise level to just

5.4 nV/√Hz (refer to Figure 35).

Input components, whether multiplexers or resistors, should be

carefully selected to prevent the formation of thermocouple

junctions that would degrade the input signal.

V

OUT

+15V

+IN

–IN

AMP01

9.1V 1W

ZENERS

100V

1W

*

100V

1W*

OPTIONAL PROTECTION

RESISTORS, SEE TEXT.

*

LINEAR INPUT RANGE,

65V MAXIMUM

DIFFERENTIAL PROTECTION

TO 630V

–15V

Figure 35. Input Overvoltage Protection for Gains

2 to 10,000

POWER SUPPLY CONSIDERATIONS

Achieving the rated performance of precision amplifiers in a

practical circuit requires careful attention to external influences.

For example, supply noise and changes in the nominal voltage

directly affect the input offset voltage. A PSR of 80 dB means

that a change of 100 mV on the supply, not an uncommon

value, will produce a 10 µV input offset change. Consequently,

care should be taken in choosing a power unit that has a low

output noise level, good line and load regulation, and good

temperature stability.

AMP01

–16–

REV. D

6I

OUT

R1

100V

R2

200V

R

OUT

TRIM

SENSE

7

9

8

REFERENCE

10

11

15

14

12

13

18

1

2

3

R

G

2kV

+IN

–IN

V

IN

R

S

2kV

–15V

0.047mF

0.047mF

+15V

COMPLIANCE, TYPICALLY 610V

LINEARITY ~0.01%

OUTPUT RESISTANCE AT 20mA ~5MV

POWER BANDWIDTH (–3dB) ~60kHz

INTO 500V LOAD

I

OUT

= V

IN

( )

20 3 R

S

RG 3 R1

AMP01

R1 = 100V FOR I

OUT

= 620mA

V

IN

= 6100mV FOR 620mA FULL SCALE

R

G

R

G

R

S

R

S

V+

V–

Figure 36. High Compliance Bipolar Current Source with 13-Bit Linearity

R

OUT

TRIM

7

9

8

10

11

15

14

12

13

18

1

2

3

R

G

2.75kV

+IN

–IN

0V

R

S

2kV

0.047mF

AMP01

COMPLIANCE OF I

OUT

, +20V WITH +30V SUPPLY (OUTPUT w.r.t. 0V)

DIFFERENTIAL INPUT OF 100mV FOR 16mA SPAN

OUTPUT RESISTANCE ~5MV AT I

OUT

= 20mA

LINEARITY 0.01% OF SPAN

0.047mF

R5

2.21kV

R6

500V

ZERO TRIM

R2

200V

REF-02

R3

100V

4

6

2

R1

100V

+15V

TO +30V

I

OUT

4mA TO 20mA

–5V

ALL RESISTORS 1% METAL FILM

R

S

R

S

R

G

R

G

V–

V+

R4

100V

Figure 37. 13-Bit Linear 4–20 mA Transmitter Constructed by Adding a Voltage Reference.

Thermocouple Signals Can Be Accepted Without Preamplification.

AMP01

–17–

REV. D

+

+IN

–IN

R

G

14

15

12

13

7

9

8

10

11

18

1

2

3

10kV

SENSE

REFERENCE

0.047mF

VOLTAGE GAIN, G = 100

POWER BANDWIDTH (–3dB), 60kHz

QUIESCENT CURRENT, 4mA

LINEARITY

~0.01% @ FULL OUTPUT INTO 10V

10mF

+

0.047mF

100V

0.047mF

2N4921

2N4918

+15V

V

OUT

(610V INTO 10V)

–15V

AMP01

R

S

R

S

V+

V–

R

G

R

G

GND

Figure 38. Adding Two Transistors Increases Output Current to ±1 A Without Affecting the Quiescent Current of 4 mA.

Power Bandwidth is 60 kHz.

0.047mF

OUT

100kV100kV

+IN

–IN

IC2

+15V

–15V

7

6

4

3

2

R

S

10kV

R

S

AMP01

R

S

V

IOS

NULL

V

OOS

NULL

V+

V–

R

G

R

G

15

14

13

12

7

18

1

2

3

16

17

4

5

10

11

8

9

SENSE

REFERENCE

GND

0.047mF

–15V

++++

10

8

6

4

3

IC1

+15V

G1 G10 G100 G1000

57911

TTL COMPATIBLE INPUTS

27kV

2.7kV

12

131412

47kV

47kV

47kV

47kV

200kV 20kV 2kV 196V

Q4

Q5

Q3

Q2

Q1

+15V

Q1, Q2...........J110

Q3, Q4, Q5....J107

IC1 ...............CMP-04

IC2 ...............OP15GZ

LINEARITY~0.005%, G = 10 AND 100

~0.02%, G = 1 AND 1000

GAIN ACCURACY, UNTRIMMED~0.5%

SETTLING TIME TO 0.01%, ALL GAINS,

LESS THAN 75ms

GAIN SWITCHING TIME, LESS THAN 100ms

Figure 39. The AMP01 Makes an Excellent Programmable-Gain Instrumentation Amplifier. Combined Gain-Switching

and Settling Time to 13 Bits Falls Below 100

µ

s. Linearity Is Better than 12 Bits over a Gain Range 1 to 1000.

AMP01

–18–

REV. D

15

14

18

1

2

3

R

G

–IN

R

S

10kV

MAXIMUM OUTPUT, 20V p-p INTO 600V

T.H.D. 0.01% @ 1kHz, 20V p-p INTO 600V, G = 10

( )

20 3 R

S

R

G

VOLTAGE GAIN, G =

AMP01

R

G

R

G

R

S

R

S

+

R

L

DIFFERENTIAL

OUTPUT

OUTPUT

COMMON-MODE

REFERENCE

(65V MAX)

OP37

2

3

7

6

4

470pF

1.5kV

*5kV

*5kV

*MATCHED TO 0.1%

7

8

9

13

10

12

11

0V

V+

V–

–15V

+15V

0V

0.047mF

0.047mF

0V

SENSE

+IN

REFERENCE

Figure 40. A Differential Input Instrumentation Amplifier with Differential Output Replaces a Transformer in Many

Applications. The Output will Drive a 600

Ω

Load at Low Distortion, (0.01%).

18

1

2

3

R1

390V

CLOSED-LOOP VOLTAGE GAIN MUST BE

GREATER THAN 50 FOR STABLE OPERATION

( )

R2

R3

1 +

VOLTAGE GAIN, G =

V

IN

AMP01

R

G

R

G

R

S

R

S

7

8

9

13

10

12

11

V+

V–

V

OUT

+15V

NC NC –15V

0.047mF

+

10mF

R2

4.95kV

R3

50V

R

L

C

L

15

14

POWER BANDWIDTH (–3dB)

~150kHz

TOTAL HARMONIC DISTORTION

~0.006%

@1kHz, 20V p-p INTO 500V // 1000pF

0.047mF

+

10mF

REF

SENSE

NC = NO CONNECT

Figure 41. Configuring the AMP01 as a Noninverting Operational Amplifier Provides Exceptional Performance. The

Output Handles Low Load Impedances at Very Low Distortion, 0.006%.

AMP01

–19–

REV. D

18

1

2

3

R4

V

IN

7

8

9

10

11

V

OUT

R1 =

R2

GAIN (G)

R3 = R1 // R2

R4 = 1.5kV @ G = 1

1.2kV @ G = 10

120V @ G = 100 AND 1000

–15V

+

10mF

15

14

20V p-p INTO 500V // 1000pF.

TOTAL HARMONIC DISTORTION:

<0.005% @ 1kHz, V

OUT

= 20V p-p

NC NC

R2

220kV

0.01mF

4.7kV

R3

+15V

AMP01

R

G

R

G

R

S

R

S

SENSE

V–

REF

0.047mF 0.047mF

10mF

+

G = 1 TO 1000

R1

12

13

V–

Figure 42. The Inverting Operational Amplifier Configuration has Excellent Linearity over the Gain Range 1 to 1000, Typically

0.005%. Offset Voltage Drift at Unity Gain Is Improved over the Drift in the Instrumentation Amplifier Configuration.

18

1

2

3

R

G

3kV

V

IN

AMP01

R

G

R

G

REF

SENSE

7

8

9

13

10

12

11

V+

V–

V

OUT

+15V

NC

NC

–15V

0.047mF

+

10mF

R2

4.7kV

R

L

C

L

15

14

POWER BANDWIDTH (–3dB)

~60kHz

TOTAL HARMONIC DISTORTION

~0.001%

@1kHz, 20V p-p INTO 500V // 1000pF

NC = NO CONNECT

0.047mF

+

10mF

680pF

0.01mF

R3

330V

R1

4.7kV

R

S

R

S

Figure 43. Stability with Large Capacitive Loads Combined with High Output Current Capability make the AMP01 Ideal

for Line Driving Applications. Offset Voltage Drift Approaches the TCV

IOS

Limit, (0.3 µV/°C).

AMP01

–20–

REV. D

18

1

2

3

9

13

10

12

11

V–

200kV 20kV 2kV 200V

G

1

G

10

G

100

G

1000

V+

R

G

R

G

7

8

1/2 OP215

+

–

8

4

V–

V+

1

2

3

1.82kV

1mF

16.2kV

OUTPUT

1/2 OP215

+

–

1.62MV

9.09kV

G

1000

G

1,10,100

100V

1kV

8

AMP01

14

15

10kV

R

S

R

S

R

G

R

G

16.2kV

1mF

e

n

(G = 1, 10, 100) =

e

OUT

1000 3 G

e

n

(G = 1000) =

e

OUT

100 3 G

1mF

5

6

7

Figure 44. Noise Test Circuit (0.1 Hz to 10 Hz)

18

1

2

3

9

13

10

12

11

200kV

0.1%

20kV

0.1%

2kV

0.1%

200V

0.1%

G

1

G

10

G

100

G

1000

R

G

R

G

7

8

8

14

15

0.047mF 0.047mF

V+ V–

10kV

0.1%

10V

0.1%

102V

0.1%

1.1kV

0.1%

G

1000

G

100

G

1

G

10

10kV

0.1%

2kV

0.1%

R

G

R

G

AMP01

R

S

R

S

1.91kV

0.1%

200V

10T

2 3 HSCH-1001

V

IN

20V p-p

V

OUT

Figure 45. Settling-Time Test Circuit

AMP01

–21–

REV. D

0.047mF

V

OUT

R

S

10kV

15

14

13

12

7

18

1

2

3

10

11

8

9

SENSE

REFERENCE

R

S

AMP01

R

S

V+

V–

R

G

R

G

R

G

200V

DG390

ANALOG

SWITCH

1

3

6

8

+IN

–IN

16

9

10

15

4

5

14 13

13

4

1, 2

16

3

0.01mF

R1

100V

15kV

61mA

7.5kV

14

7.5kV

TTL INPUT

"OFFSET"

0V

–15V

TTL INPUT

"ZERO"

+15V

VOLTAGE GAIN, G =

20 3 R

S

R

G

( )

15

DAC-08

11

0.047mF

Figure 46. Instrumentation Amplifier with Autozero

+18V

–18V

10kV

SENSE

AMP01

14

15

13

12

7

9

8

11

10

3

2

1

18

0.047mF

V

OUT

10kV

0.047mF

R

S

R

S

R

G

R

G

Figure 47. Burn-In Circuit

AMP01

–22–

REV. D

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

18-Lead Cerdip

(Q-18)

18

1

9

10

0.310 (7.87)

0.220 (5.59)

PIN 1

0.005 (0.13) MIN

0.098 (2.49) MAX

SEATING

PLANE

0.023 (0.58)

0.014 (0.36)

0.200 (5.08)

MAX

0.960 (24.38) MAX

0.150

(3.81)

MIN

0.070 (1.78)

0.030 (0.76)

0.200 (5.08)

0.125 (3.18)

0.100

(2.54)

BSC

0.060 (1.52)

0.015 (0.38)

158

08

0.320 (8.13)

0.290 (7.37)

0.015 (0.38)

0.008 (0.20)

20-Lead SOIC

(R-20)

SEATING

PLANE

0.0118 (0.30)

0.0040 (0.10)

0.0192 (0.49)

0.0138 (0.35)

0.1043 (2.65)

0.0926 (2.35)

0.0500

(1.27)

BSC

0.0125 (0.32)

0.0091 (0.23)

0.0500 (1.27)

0.0157 (0.40)

88

08

0.0291 (0.74)

0.0098 (0.25)

3 458

20 11

101

0.5118 (13.00)

0.4961 (12.60)

0.4193 (10.65)

0.3937 (10.00)

0.2992 (7.60)

0.2914 (7.40)

PIN 1

28-Terminal Ceramic Leadless Chip Carrier

(E-28A)

1

28

5

11

12

18

26

BOTTOM

VIEW

19

4

25

0.028 (0.71)

0.022 (0.56)

458 TYP

0.015 (0.38)

MIN

0.055 (1.40)

0.045 (1.14)

0.050

(1.27)

BSC

0.075

(1.91)

REF

0.011 (0.28)

0.007 (0.18)

R TYP

0.095 (2.41)

0.075 (1.90)

0.150

(3.51)

BSC

0.300 (7.62)

BSC

0.200

(5.08)

BSC

0.075

(1.91)

REF

0.458 (11.63)

0.442 (11.23)

SQ

0.458

(11.63)

MAX

SQ

0.100 (2.54)

0.064 (1.63)

0.088 (2.24)

0.054 (1.37)

C3103b–0–12/99

PRINTED IN U.S.A.

Loading...

Loading...