a

ADSP-21489 EZ-Board

TM

Evaluation System Manual

Revision 1.0, April 2010

Part Number

82-000228-01

Analog Devices, Inc.

One Technology Way

Norwood, Mass. 02062-9106

Copyright Information

© 2010 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written

consent from Analog Devices, Inc.

Printed in the USA.

Disclaimer

Analog Devices, Inc. reserves the right to change this product without

prior notice. Information furnished by Analog Devices is believed to be

accurate and reliable. However, no responsibility is assumed by Analog

Devices for its use; nor for any infringement of patents or other rights of

third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

Trademark and Service Mark Notice

The Analog Devices logo, VisualDSP++, SHARC, EZ-KIT Lite, and

EZ-Extender are registered trademarks of Analog Devices, Inc.

EZ-Board is a trademark of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of

their respective owners.

Regulatory Compliance

The ADSP-21489 EZ-Board is designed to be used solely in a laboratory

environment. The board is not intended for use as a consumer end product or as a portion of a consumer end product. The board is an open

system design which does not include a shielded enclosure and therefore

may cause interference to other electrical devices in close proximity. This

board should not be used in or near any medical equipment or RF devices.

The ADSP-21489 EZ-Board is currently being processed for certification

that it complies with the essential requirements of the European EMC

directive 89/336/EEC amended by 93/68/EEC and therefore carries the

“CE” mark.

The EZ-Board evaluation system contains ESD (electrostatic discharge)

sensitive devices. Electrostatic charges readily accumulate on the human

body and equipment and can discharge without detection. Permanent damage may occur on devices subjected to high-energy discharges. Proper ESD

precautions are recommended to avoid performance degradation or loss of

functionality. Store unused EZ-Boards in the protective shipping package.

CONTENTS

PREFACE

Product Overview ........................................................................ viii

Purpose of This Manual ................................................................. xi

Intended Audience ......................................................................... xi

Manual Contents .......................................................................... xii

What’s New in This Manual .......................................................... xii

Technical or Customer Support .................................................... xiii

Supported Processors .................................................................... xiii

Product Information .................................................................... xiv

Analog Devices Web Site ........................................................ xiv

VisualDSP++ Online Documentation ..................................... xiv

Technical Library CD .............................................................. xv

EngineerZone ......................................................................... xvi

Social Networking Web Sites .................................................. xvi

Related Documents ...................................................................... xvi

Notation Conventions ................................................................ xviii

USING ADSP-21489 EZ-BOARD

Package Contents .......................................................................... 1-2

ADSP-21489 EZ-Board Evaluation System Manual i

Contents

Default Configuration .................................................................. 1-3

EZ-Board Installation ................................................................... 1-5

EZ-Board Session Startup ............................................................. 1-6

Evaluation License Restrictions ..................................................... 1-8

Memory Map ............................................................................... 1-8

SDRAM Interface ....................................................................... 1-10

SRAM Interface .......................................................................... 1-10

Parallel Flash Memory Interface .................................................. 1-11

SPI Interface .............................................................................. 1-12

Watch Dog Timer Interface ........................................................ 1-12

Temperature Sensor Interface ...................................................... 1-13

S/PDIF Interface ........................................................................ 1-14

Audio Interface ........................................................................... 1-15

UART Interface .......................................................................... 1-17

LEDs and Push Buttons .............................................................. 1-17

JTAG Interface ........................................................................... 1-19

Expansion Interface II ................................................................. 1-20

Power Measurements .................................................................. 1-21

Power-On-Self Test ..................................................................... 1-22

Example Programs ...................................................................... 1-22

Background Telemetry Channel .................................................. 1-22

Reference Design Information ..................................................... 1-23

ADSP-21489 EZ-BOARD HARDWARE REFERENCE

System Architecture ...................................................................... 2-2

ii ADSP-21489 EZ-Board Evaluation System Manual

Contents

DAI Interface .......................................................................... 2-3

DPI Interface .......................................................................... 2-4

Flags and Memory Selects .............................................................. 2-6

Push Buttons and Switches ............................................................ 2-7

DAI [1–8] Enable Switch (SW1) .............................................. 2-8

DAI [9–16] Enable Switch (SW2) ............................................ 2-8

DPI [1–8] Enable Switch (SW3) .............................................. 2-9

Boot Mode Select Switch (SW4) ............................................ 2-10

DSP Clock Configuration Switch (SW5) ................................ 2-10

DAI [17–20] Enable Switch (SW7) ........................................ 2-11

Programmable Flag Push Buttons (SW8–11) .......................... 2-12

Reset Push Button (SW12) .................................................... 2-12

External Port Enable Switch (SW13) ...................................... 2-12

DPI [9–14] Enable Switch (SW14) ........................................ 2-13

Audio In1 Left Selection Switch (SW15) ................................ 2-14

Audio In1 Right Selection Switch (SW16) .............................. 2-14

Audio In2 Right Selection Switch (SW17) .............................. 2-15

Audio In2 Left Selection Switch (SW18) ................................ 2-16

JTAG Switches (SW19–22) .................................................... 2-16

Headphone Enable Switch (SW23) ........................................ 2-18

Audio Loopback Switches (SW24–25) ................................... 2-18

Jumpers ...................................................................................... 2-19

Flash WP Jumper (JP1) ......................................................... 2-20

S/PDIF Loopback Jumper (JP2) ............................................ 2-20

ADSP-21489 EZ-Board Evaluation System Manual iii

Contents

UART RTS/CTS Jumper (JP3) ............................................. 2-20

UART Loopback Jumper (JP4) .............................................. 2-20

DSP Audio Oscillator Jumper (JP5) ....................................... 2-20

LEDs ......................................................................................... 2-21

GPIO LEDs (LED1–8) ......................................................... 2-22

Power LED (LED9) .............................................................. 2-22

Reset LED (LED10) ............................................................. 2-22

Thermal Limit LED (LED11) ............................................... 2-23

Connectors ................................................................................. 2-24

Expansion Interface II Connector (J1) ................................... 2-25

RS-232 Connector (J2) ......................................................... 2-25

MP JTAG Connector (J3) ..................................................... 2-25

RCA Audio Connector (J4) ................................................... 2-26

RCA Audio Connector (J5) ................................................... 2-26

S/PDIF In Connector (J6) ..................................................... 2-26

S/PDIF Out Connector (J7) .................................................. 2-26

Headphone Out Connector (J8) ............................................ 2-27

JTAG Connector (P1) ........................................................... 2-27

Expansion Interface II Connector (P2) .................................. 2-27

Differential In/Out Connectors (P8–9) .................................. 2-28

MP JTAG Out Connector (P12) ........................................... 2-28

VDDINT Power Connector (P14) ........................................ 2-28

VDDEXT Power Connector (P15) ........................................ 2-29

Power Connector (P16) ......................................................... 2-29

iv ADSP-21489 EZ-Board Evaluation System Manual

Contents

Standalone Debug Agent Connector (ZP1) ............................ 2-29

ADSP-21489 EZ-BOARD BILL OF MATERIALS

ADSP-21489 EZ-BOARD SCHEMATIC

Title Page .................................................................................... B-1

Processor - External Port .............................................................. B-2

Memory - Parallel ........................................................................ B-3

Processor - DAI, DPI Interfaces .................................................... B-4

Processor - Power, CLKIN ............................................................ B-5

S/PDIF, RS-232, JTAG Interfaces ................................................. B-6

Reset Circuit, Push Buttons, LEDs ............................................... B-7

Audio Page 1 ................................................................................ B-8

Audio Page 2 ................................................................................ B-9

Audio Page 3 .............................................................................. B-10

Audio Page 4 .............................................................................. B-11

Audio Page 5 .............................................................................. B-12

Audio Page 6 .............................................................................. B-13

Audio Page 7 .............................................................................. B-14

Expansion II Interface ................................................................ B-15

Power ........................................................................................ B-16

INDEX

ADSP-21489 EZ-Board Evaluation System Manual v

Contents

vi ADSP-21489 EZ-Board Evaluation System Manual

PREFACE

Thank you for purchasing the ADSP-21489 EZ-Board™, Analog

Devices, Inc. evaluation system for SHARC® processors.

SHARC processors are based on a 32-bit super Harvard architecture that

includes a unique memory architecture comprised of two large on-chip,

dual-ported SRAM blocks coupled with a sophisticated IO processor,

which gives a SHARC processor the bandwidth for sustained high-speed

computations. SHARC processors represents today’s de facto standard for

floating-point processing, targeted toward premium audio applications.

The evaluation board is designed to be used in conjunction with the Visu-

alDSP++® development environment to test the capabilities of the

ADSP-21489 SHARC processors. The VisualDSP++ development environment aids advanced application code development and debug, such as:

• Create, compile, assemble, and link application programs written

in C++, C, and assembly

• Load, run, step, halt, and set breakpoints in application programs

• Read and write data and program memory

• Read and write core and peripheral registers

• Plot memory

Access to the processor from a personal computer (PC) is achieved

through a USB port or an external JTAG emulator. The USB interface of

the standalone debug agent gives unrestricted access to the processor and

evaluation board’s peripherals. Analog Devices JTAG emulators offer

ADSP-21489 EZ-Board Evaluation System Manual vii

Product Overview

faster communication between the host PC and target hardware. To learn

more about Analog Devices emulators and processor development tools,

go to

http://www.analog.com/dsp/tools/.

The ADSP-21489 EZ-Board provides example programs to demonstrate

the product capabilities.

L

The ADSP-21489 EZ-Board installation is part of the VisualDSP++ update 8 or later installation. As an EZ-KIT Lite, an

EZ-Board is a licensed product that offers an unrestricted evaluation license for the first 90 days. For details about evaluation

license restrictions after the 90 days, refer to “Evaluation License

Restrictions” on page 1-8 and the VisualDSP++ Installation Quick

Reference Card.

Product Overview

The board features:

• Analog Devices ADSP-21489 SHARC processor

• Core performance up to 400 MHz

• 176-pin LQFP package

•25MHz

• 5 Mb of internal RAM memory

CLKIN oscillator

• Parallel flash memory

• Numonyx M29W320EB – 4 MB (4M x 8 bits)

• SDRAM memory

• Micron MT48LC16M16A2P-6A – 16 Mbx x 16 bits

(256 Mb or 32 MB)

viii ADSP-21489 EZ-Board Evaluation System Manual

• Asynchronous memory (SRAM)

• ISSI IS61WV102416BLL-10TLI – 1M x 16 bits (2 MB)

• SPI flash memory

• Numonyx M25P16 – 16 Mb

• Analog audio interface

• Analog Devices AD1939 audio codec

• 4 x 2 RCA phono jack for eight channels of stereo output

• 4 x 1 RCA phono jack for four channel of stereo input

• Two DB25 connectors for differential inputs/outputs

• 3.5 mm headphone jack with volume control connected to

one of the stereo outputs

Preface

• Supports all eight DACs and four ADCs in TDM and I

2

S

modes at 48 KHz, 96 KHz, and 192 KHz sample rates

• Digital audio interface (S/PDIF)

• RCA phono jack output

• RCA phono jack input

• Temperature monitor

• ON Semiconductor ADM1032

• Local and remote temperature sensing

• Universal asynchronous receiver/transmitter (UART)

• ADM3202 RS-232 line driver/receiver

• DB9 female connector

ADSP-21489 EZ-Board Evaluation System Manual ix

Product Overview

•LEDs

• Eleven LEDs: one board reset (red), eight general-purpose

(amber), one temperature sensor (amber), and one power

(green)

• Push buttons

• Five push buttons: one reset, two connected to the DAI,

and two connected to

• Expansion interface II

• Next generation of the expansion interface design, provides

access to most of the processor signals

• Power supply

• 5V @ 3.6 Amps

FLAG pins of the processor

• Other features

• Watch dog timer (WDT) system reset implementation

• SHARC power measurement jumpers

• JTAG ICE 14-pin header

• USB cable

For information about hardware components of the EZ-Board, refer to

“ADSP-21489 EZ-Board Hardware Reference” on page 2-1.

x ADSP-21489 EZ-Board Evaluation System Manual

Preface

Purpose of This Manual

The ADSP-21489 EZ-Board Evaluation System Manual provides instructions for installing the product hardware (board). The text describes

operation and configuration of the board components and provides guidelines for running your own code on the ADSP-21489 EZ-Board. Finally, a

schematic and a bill of materials are provided for reference.

The product software installation is detailed in the VisualDSP++ Installa-

tion Quick Reference Card.

Intended Audience

The primary audience for this manual is a programmer who is familiar

with Analog Devices processors. This manual assumes that the audience

has a working knowledge of the appropriate processor architecture and

instruction set. Programmers who are unfamiliar with Analog Devices

processors can use this manual, but should supplement it with other texts

(such as the ADSP-214xx SHARC Processor Hardware Reference and

SHARC Processor Instruction Set Reference) that describe your target

architecture.

Programmers who are unfamiliar with VisualDSP++ should refer to the

VisualDSP++ online Help and user’s or getting started guides. For the

locations of these documents, see “Related Documents”.

ADSP-21489 EZ-Board Evaluation System Manual xi

Manual Contents

Manual Contents

The manual consists of:

• Chapter 1, “Using ADSP-21489 EZ-Board” on page 1-1

Describes EZ-Board functionality from a programmer’s perspective

and provides a simplified memory map.

• Chapter 2, “ADSP-21489 EZ-Board Hardware Reference” on

page 2-1

Provides information about the EZ-Board hardware components.

• Appendix A, “ADSP-21489 EZ-Board Bill Of Materials” on

page A-1

Provides a list of components used to manufacture the EZ-Board.

• Appendix B, “ADSP-21489 EZ-Board Schematic” on page B-1

Provides resources for board-level debugging, can be used as a reference guide.

What’s New in This Manual

This is the first revision of the ADSP-21489 EZ-Board Evaluation System

Manual.

xii ADSP-21489 EZ-Board Evaluation System Manual

Technical or Customer Support

You can reach Analog Devices, Inc. Customer Support in the following

ways:

• Visit the Embedded Processing and DSP products Web site at

http://www.analog.com/processors/technical_support

• E-mail tools questions to

processor.tools.support@analog.com

• E-mail processor questions to

processor.support@analog.com (World wide support)

processor.europe@analog.com (Europe support)

processor.china@analog.com (China support)

• Phone questions to 1-800-ANALOGD

Preface

• Contact your Analog Devices, Inc. local sales office or authorized

distributor

• Send questions by mail to:

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

USA

Supported Processors

This evaluation system supports Analog Devices ADSP-21489 SHARC

embedded processors. Functionality of the ADSP-21483, ADSP-21486,

ADSP-21487, and ADSP-21488 processors can be evaluated using the

same product because the processors have many similarities.

ADSP-21489 EZ-Board Evaluation System Manual xiii

Product Information

Product Information

Product information can be obtained from the Analog Devices Web site,

VisualDSP++ online Help system, and a technical library CD.

Analog Devices Web Site

The Analog Devices Web site, www.analog.com, provides information

about a broad range of products—analog integrated circuits, amplifiers,

converters, and digital signal processors.

To access a complete technical library for each processor family, go to

http://www.analog.com/processors/technical_library. The manuals

selection opens a list of current manuals related to the product as well as a

link to the previous revisions of the manuals. When locating your manual

title, note a possible errata check mark next to the title that leads to the

current correction report against the manual.

Also note, MyAnalog.com is a free feature of the Analog Devices Web site

that allows customization of a Web page to display only the latest information about products you are interested in. You can choose to receive

weekly e-mail notifications containing updates to the Web pages that meet

your interests, including documentation errata against all manuals.

MyAnalog.com provides access to books, application notes, data sheets,

code examples, and more.

MyAnalog.com to sign up. If you are a registered user, just log on.

Visit

Your user name is your e-mail address.

VisualDSP++ Online Documentation

Online documentation comprises the VisualDSP++ Help system, software

tools manuals, hardware tools manuals, processor manuals, Dinkum

Abridged C++ library, and FLEXnet License Tools software documenta-

xiv ADSP-21489 EZ-Board Evaluation System Manual

Preface

tion. You can search easily across the entire VisualDSP++ documentation

set for any topic of interest.

For easy printing, supplementary Portable Documentation Format (

files for all manuals are provided on the VisualDSP++ installation CD.

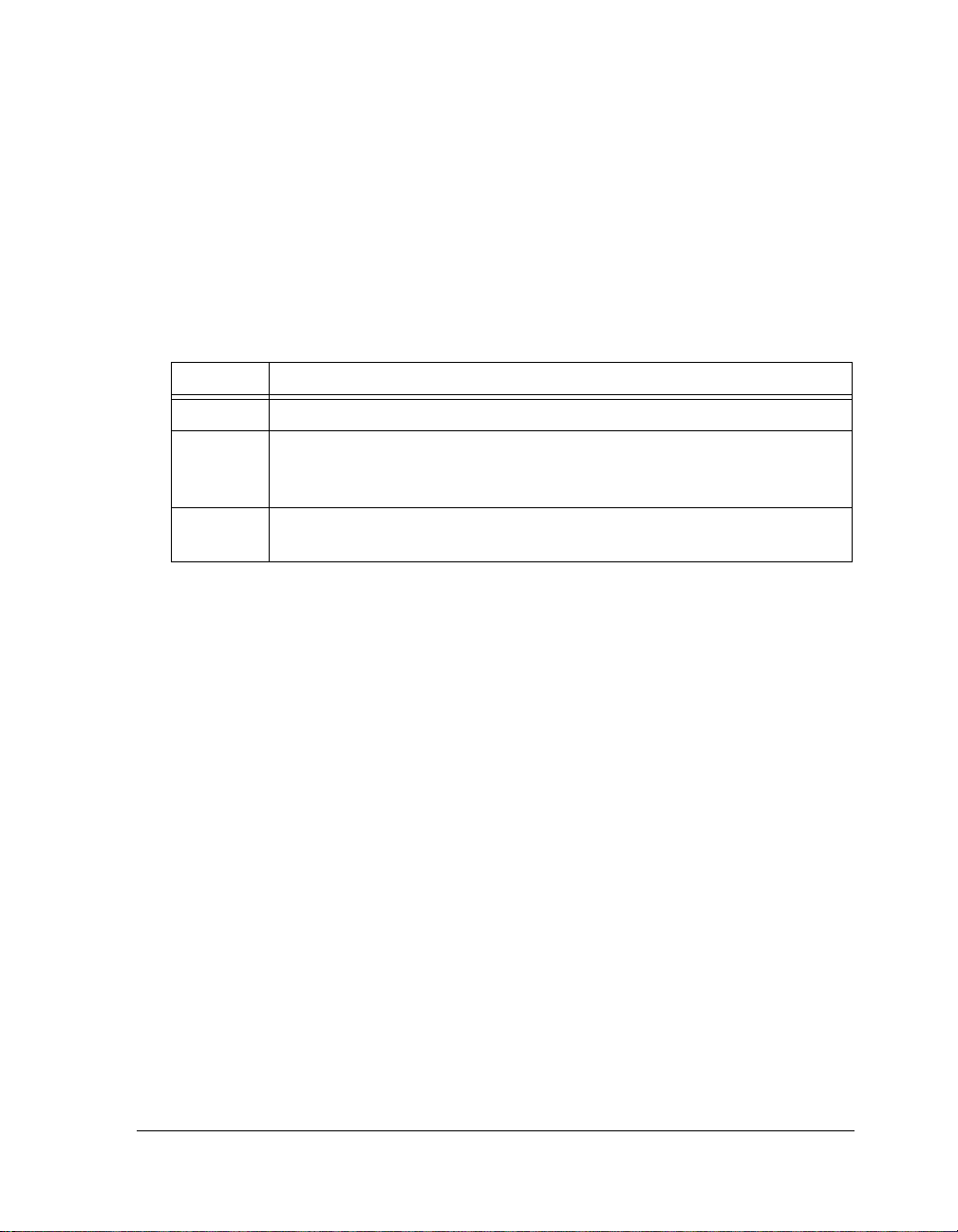

Each documentation file type is described as follows.

File Description

.chm Help system files and manuals in Microsoft help format

.htm or

.html

.pdf VisualDSP++ and processor manuals in PDF format. Viewing and printing the

Dinkum Abridged C++ library and FLEXnet License Tools software documentation. Viewing and printing the .html files requires a browser, such as Internet

Explorer 6.0 (or higher).

.pdf files requires a PDF reader, such as Adobe Acrobat Reader (4.0 or higher).

Technical Library CD

The technical library CD contains seminar materials, product highlights, a

selection guide, and documentation files of processor manuals, VisualDSP++ software manuals, and hardware tools manuals for the following

processor families: Blackfin, SHARC, TigerSHARC, ADSP-218x, and

ADSP-219x.

.pdf)

To order the technical library CD, go to

sors/technical_library

, navigate to the manuals page for your

http://www.analog.com/proces-

processor, click the request CD check mark, and fill out the order form.

Data sheets, which can be downloaded from the Analog Devices Web site,

change rapidly, and therefore are not included on the technical library

CD. Technical manuals change periodically. Check the Web site for the

latest manual revisions and associated documentation errata.

ADSP-21489 EZ-Board Evaluation System Manual xv

Related Documents

EngineerZone

EngineerZone is a technical support forum from Analog Devices. It allows

you direct access to ADI technical support engineers. You can search

FAQs and technical information to get quick answers to your embedded

processing and DSP design questions.

Use EngineerZone to connect with other DSP developers who face similar

design challenges. You can also use this open forum to share knowledge

and collaborate with the ADI support team and your peers. Visit

http://ez.analog.com to sign up.

Social Networking Web Sites

You can now follow Analog Devices processor development on Twitter

and LinkedIn. To access:

• Twitter: http://twitter.com/ADIsharc and

http://twitter.com/blackfin

• LinkedIn: Network with the LinkedIn group, Analog Devices

SHARC or Analog Devices Blackfin: http://www.linkedin.com

Related Documents

For information on product related development software, see the following publications.

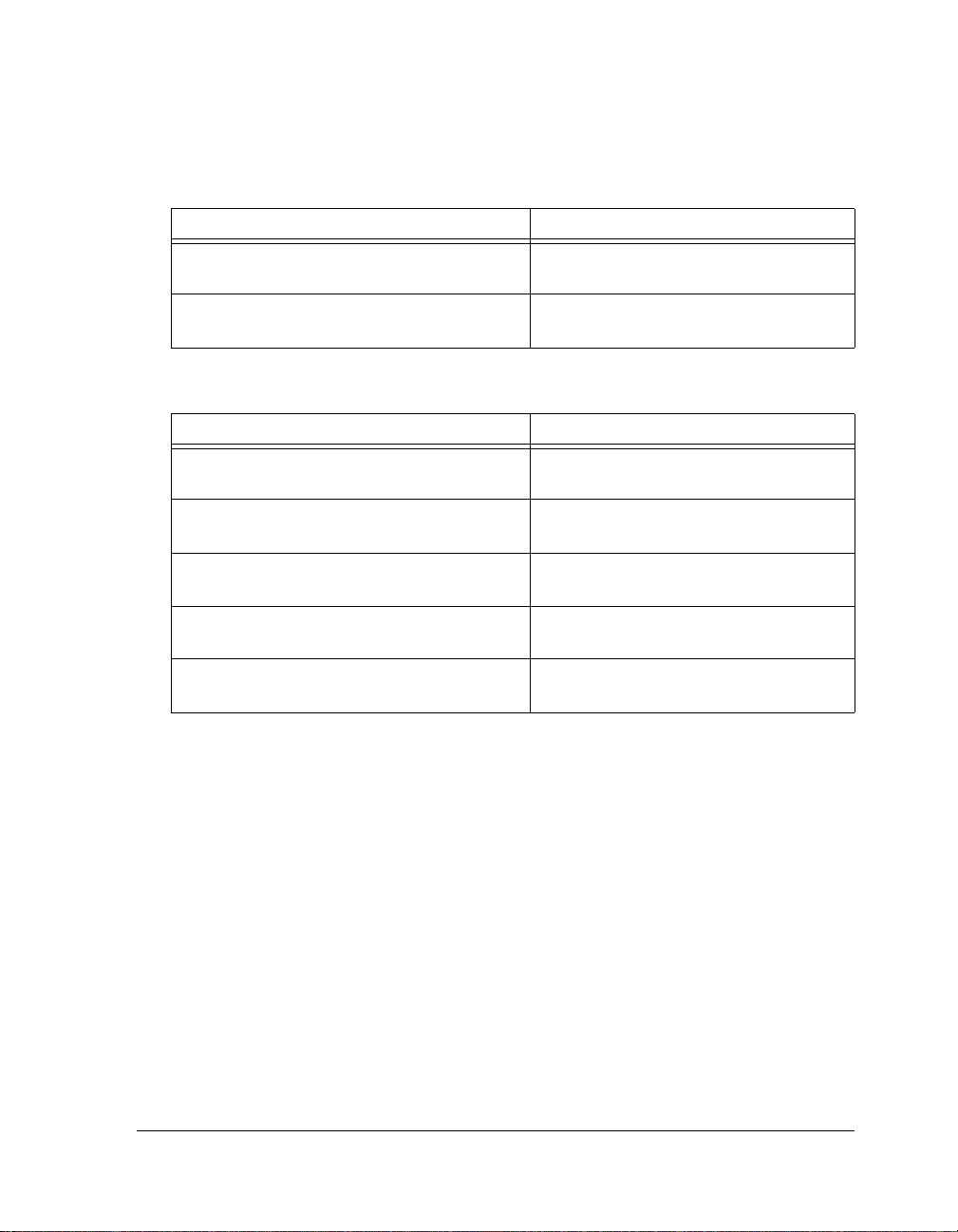

Table 1. Related Processor Publications

Title Description

ADSP-21484/21486/21487/21489 SHARC Proces-

sor Preliminary Data Sheet

xvi ADSP-21489 EZ-Board Evaluation System Manual

General functional description, pinout, and

timing of the processor.

Preface

Table 1. Related Processor Publications (Cont’d)

Title Description

ADSP-214xx SHARC Processor Hardware Reference Description of internal processor architecture

and all register functions.

SHARC Processor Programming Reference

Description of all allowed processor assembly

instructions.

Table 2. Related VisualDSP++ Publications

Title Description

VisualDSP++ Assembler and Preprocessor Manuals Description of the assembler function and

commands.

VisualDSP++ C/C++ Compiler Manual for SHARC

Processors

Description of the complier functions and

commands for SHARC processors.

VisualDSP++ Run-Time Library Manual for

SHARC Processors

VisualDSP++ Linker and Utilities Manual Description of the linker function and com-

VisualDSP++ Loader and Utilities Manual Description of the loader/splitter function

Description of the run-time library functions

for SHARC processors.

mands.

and commands.

ADSP-21489 EZ-Board Evaluation System Manual xvii

Notation Conventions

L

a

[

Notation Conventions

Text conventions used in this manual are identified and described as

follows.

Example Description

Close command

(File menu)

{this | that} Alternative required items in syntax descriptions appear within curly

[this | that] Optional items in syntax descriptions appear within brackets and sepa-

[this,…] Optional item lists in syntax descriptions appear within brackets delim-

.SECTION Commands, directives, keywords, and feature names are in text with

filename Non-keyword placeholders appear in text with italic style format.

Titles in reference sections indicate the location of an item within the

VisualDSP++ environment’s menu system (for example, the Close command appears on the File menu).

brackets and separated by vertical bars; read the example as this or

that. One or the other is required.

rated by vertical bars; read the example as an optional

ited by commas and terminated with an ellipse; read the example as an

optional comma-separated list of this.

letter gothic font.

Note: For correct operation, ...

A Note provides supplementary information on a related topic. In the

online version of this book, the word Note appears instead of this

symbol.

Caution: Incorrect device operation may result if ...

Caution: Device damage may result if ...

A Caution identifies conditions or inappropriate usage of the product

that could lead to undesirable results or product damage. In the online

version of this book, the word Caution appears instead of this symbol.

this or that.

Warn in g: Injury to device users may result if ...

A Warning identifies conditions or inappropriate usage of the product

that could lead to conditions that are potentially hazardous for the

devices users. In the online version of this book, the word Wa rn in g

appears instead of this symbol.

xviii ADSP-21489 EZ-Board Evaluation System Manual

1 USING ADSP-21489

EZ-BOARD

This chapter provides information to assist you with development of programs for the ADSP-21489 EZ-Board evaluation system.

The following topics are covered.

• “Package Contents” on page 1-2

• “Default Configuration” on page 1-3

• “EZ-Board Installation” on page 1-5

• “EZ-Board Session Startup” on page 1-6

• “Evaluation License Restrictions” on page 1-8

• “Memory Map” on page 1-8

• “SDRAM Interface” on page 1-10

• “SRAM Interface” on page 1-10

• “Parallel Flash Memory Interface” on page 1-11

• “SPI Interface” on page 1-12

• “Watch Dog Timer Interface” on page 1-12

• “Temperature Sensor Interface” on page 1-13

• “S/PDIF Interface” on page 1-14

• “Audio Interface” on page 1-15

ADSP-21489 EZ-Board Evaluation System Manual 1-1

Package Contents

• “UART Interface” on page 1-17

• “LEDs and Push Buttons” on page 1-17

• “JTAG Interface” on page 1-19

• “Expansion Interface II” on page 1-20

• “Power Measurements” on page 1-21

• “Power-On-Self Test” on page 1-22

• “Example Programs” on page 1-22

• “Background Telemetry Channel” on page 1-22

• “Reference Design Information” on page 1-23

For information about VisualDSP++, including the boot loading, target

options, and other facilities, refer to the online Help.

For more information about the ADSP-21489 SHARC processor, see documents referred to as “Related Documents”.

Package Contents

Your ADSP-21489 EZ-Board package contains the following items.

• ADSP-21489 EZ-Board

• VisualDSP++ Installation Quick Reference Card

• CD containing:

• VisualDSP++ software

• ADSP-21489 EZ-Board debug software

1-2 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

• USB driver files

• Example programs

• Universal 5.0V DC power supply

• 3.5 mm stereo headphones

• 6-foot RCA audio cable

• 6-foot 3.5 mm/RCA x 2 Y-cable

• 3.5 mm stereo female to RCA male Y-cable

Contact the vendor where you purchased your EZ-Board or contact Analog Devices, Inc. If any item is missing.

Default Configuration

The EZ-Board evaluation system contains ESD (electrostatic discharge) sensitive devices. Electrostatic charges readily accumulate on the human body

and equipment and can discharge without detection. Permanent damage may

occur on devices subjected to high-energy discharges. Proper ESD precautions are recommended to avoid performance degradation or loss of functionality. Store unused EZ-Boards in the protective shipping package.

The ADSP-21489 EZ-Board board is designed to run outside your personal computer as a stand-alone unit. You do not have to open your

computer case.

When removing the EZ-Board from the package, handle the board carefully to avoid the discharge of static electricity, which can damage some

components. Figure 1-1 shows the default jumper and switch settings,

ADSP-21489 EZ-Board Evaluation System Manual 1-3

Default Configuration

connector locations, and LEDs used in installation. Confirm that your

board is in the default configuration before using the board.

Figure 1-1. Default EZ-Board Hardware Setup

1-4 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

EZ-Board Installation

For correct operation, install the software in the order presented in the

VisualDSP++ Installation Quick Reference Card. Substitute instructions in

step 3 with instructions in this section.

There are two options to connect the EZ-Board hardware to a personal

computer (PC) running VisualDSP++ 5.0: via an Analog Devices emulator or via a standalone debug agent module. The standalone debug agent

allows a debug agent to interface to the ADSP-21489 EZ-Board. The

standalone debug agent is shipped with the kit.

To connect the EZ-Board to a PC via an emulator:

1. Plug the 5V adaptor into connector P16 (labeled 5.0V).

2. Attach the emulator header to connector P1 (labeled JTAG) on the

back side of the EZ-Board.

To connect the EZ-Board to a PC via a standalone debug agent:

a

ADSP-21489 EZ-Board Evaluation System Manual 1-5

The debug agent can be used only when power is supplied from the

wall adaptor.

1. Attach the standalone debug agent to connectors P1 (labeled JTAG)

and ZP1 on the backside of the EZ-Board, watching for the keying

pin of

2. Plug the 5V adaptor into connector

3. Plug one side of the provided USB cable into a USB connector of

the standalone debug agent. Plug the other side of the cable into

a USB port of the PC running VisualDSP++ 5.0 update 8 or later.

4. Verify that the yellow USB monitor LED on the standalone debug

agent (

fies that the board is communicating properly with the host PC

and ready to run VisualDSP++.

P1 to connect correctly.

P16 (labeled 5.0V).

LED4, located on the back side of the board) is lit. This signi-

EZ-Board Session Startup

EZ-Board Session Startup

1. If you are running VisualDSP++ for the first time, navigate to the

VisualDSP++ environment via the Start–>Programs menu. The

main window appears. Note that VisualDSP++ is not connected to

any session. Skip the rest of this step to step 2.

If you have run VisualDSP++ previously, the last opened session

appears on the screen. You can override the default behavior and

force VisualDSP++ to start a new session by pressing and holding

down the Ctrl key while starting VisualDSP++. Do not release the

Ctrl key until the Session Wizard appears on the screen. Go to

step 3.

2. To connect to a new EZ-Board session, start Session Wizard by

selecting one of the following.

• From the Session menu, New Session.

• From the Session menu, Session List. Then click New Ses-

sion from the Session List dialog box.

• From the Session menu, Connect to Target.

3. The Select Processor page of the wizard appears on the screen.

Ensure SHARC is selected in Processor family. In Choose a target

processor, select ADSP-21489. Click Next.

4. The Select Connection Type page of the wizard appears on the

screen. For standalone debug agent connections, select EZ-KIT

Lite and click Next. For emulator connections, select Emulator

and click Next.

5. The Select Platform page of the wizard appears on the screen.

For standalone debug agent connections, ensure that the selected

platform is ADSP-21489 EZ-KIT Lite via Debug Agent. For emulator connections, choose the type of emulator that is connected.

1-6 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

Specify your own Session name for the session or accept the default

name.

The session name can be a string of any length; although, the box

displays approximately 32 characters. The session name can

include space characters. If you do not specify a session name,

VisualDSP++ creates a session name by combining the name of the

selected platform with the selected processor. The only way to

change a session name later is to delete the session and open a new

session.

Click Next.

6. The Finish page of the wizard appears on the screen. The page dis-

plays your selections. Check the selections. If you are not satisfied,

click Back to make changes; otherwise, click Finish. VisualDSP++

creates the new session and connects to the EZ-Board. Once connected, the main window’s title is changed to include the session

name set in step 5.

L

ADSP-21489 EZ-Board Evaluation System Manual 1-7

To disconnect from a session, click the disconnect button

or select Session–>Disconnect from Target.

To delete a session, select Session –> Session List. Select the session name from the list and click Delete. Click OK.

Evaluation License Restrictions

Evaluation License Restrictions

The ADSP-21489 EZ-Board installation is part of the VisualDSP++ 5.0

update 8. The EZ-Board is a licensed product that offers an unrestricted

evaluation license for the first 90 days. Once the initial unrestricted

90-day evaluation license expires:

• VisualDSP++ restricts a connection to the ADSP-21489 EZ-Board

via the USB port of the standalone debug agent interface only.

Connections to simulators and emulation products are no longer

allowed.

• The linker restricts a user program to 27306 PM words for code

space with no restrictions for data space.

• The EZ-Board hardware must be connected and powered up to use

VisualDSP++ with a valid evaluation or permanent license.

Refer to the VisualDSP++ Installation Quick Reference Card for details.

Memory Map

The ADSP-21489 processor has internal static random access memory

(SRAM) for instructions and data storage. See Table 1-1. The internal

memory details can be found in the ADSP-214xx SHARC Processor Hard-

ware Reference.

The EZ-Board includes three types of external memory: synchronous

dynamic random access memory (SDRAM), serial peripheral interconnect

1-8 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

(SPI) flash, and parallel flash. See Table 1-2. For more information about

a specific memory type, go to the respective section in this chapter.

Table 1-1. EZ-Board Internal (Core-Accessible) Memory Map

Start Address End Address Contents

0x0000 0000 0x0003 FFFF IOP Registers

0x0004 0000 0x0004 7FFF Block 0 ROM (Reserved)

0x0004 8000 0x0004 8FFF Reserved

0x0004 9000 0x0004 EFFF Block 0 SRAM

0x0004 F000 0x0004 FFFF Reserved

0x0005 0000 0x0005 7FFF Block 1 ROM (Reserved)

0x0005 8000 0x0005 8FFF Reserved

0x0005 9000 0x0005 EFFF Block 1 SRAM

0x0005 F000 0x0005 FFFF Reserved

0x0006 0000 0x0006 3FFF Block 2 SRAM

0x0006 4000 0x0006 FFFF Reserved

0x0007 0000 0x0007 3FFF Block 3 SRAM

0x0007 4000 0x0007 FFFF Reserved

Table 1-2. EZ-Board External (Interface-Accessible) Memory Map

Start Address End Address Content

0x0020 0000 0x009F FFFF SDRAM (

0x0400 0000 0x043F FFFF Flash memory (

0x0800 0000

0x0C00 0000

0x0C00 0000

0x0C00 0000

0x08FF FFFF

0x0BFF FFFF

0x0C0F FFFF

0x0C07 FFFF

Unused chip select (

Unused chip select (

SRAM (

SRAM (

~MS0)

~MS1)

~MS2) for non-SDRAM addresses

~MS2) for SDRAM addresses

~MS3) for 16-bit address space

~MS3) for 32-bit address space

ADSP-21489 EZ-Board Evaluation System Manual 1-9

SDRAM Interface

SDRAM Interface

The ADSP-21489 processor connects to a 32 MB Micron

MT48LC16M16A2P-6A chip through the SDRAM controller. The

SDRAM memory controller on the processor and SDRAM memory chip

are powered by the on-board 3.3V regulator. The SDRAM controller and

memory on the EZ-Board can operate at a maximum clock frequency of

166 MHz.

With a VisualDSP++ session running and connected to the EZ-Board via

the USB standalone debug agent, the SDRAM registers are configured

automatically each time the processor is reset. The values are used whenever SDRAM is accessed through the debugger (for example, when

viewing memory windows or loading a program).

To disable the automatic setting of SDRAM registers, select Target

Options from the Settings menu in VisualDSP++ and uncheck Use XML

reset values. For more information on changing reset values, refer to the

online Help.

An example program is included in the EZ-Board installation directory to

demonstrate how to setup and access the SDRAM interface. For more

information on how to initialize the registers after a reset, search the VisualDSP++ online Help for “reset values”.

SRAM Interface

The board has a 1M x 16-bit flash memory connected to the processor’s

AMI (asynchronous memory interface). The SRAM can be accessed via

the asynchronous memory select 3 pin. It allows access to 16 bits of data

and interfaces to address line 0 through 19 of the processor.

An example program is included in the EZ-Board installation directory to

demonstrate how to setup and access the SRAM interface. For more infor-

1-10 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

mation on how to initialize the registers after a reset, search the

VisualDSP++ online Help for “reset values”.

Parallel Flash Memory Interface

The parallel flash memory interface of the ADSP-21489 EZ-Board contains a 4 MB (4M x 8 bits) Numonyx M29W320EB chip. Flash memory

is connected to the 8-bit data bus and address lines 0 through 21. Chip

enable is decoded by the MS1 select line (default) through switch SW13

position 2. See “External Port Enable Switch (SW13)” on page 2-12. The

address range for flash memory is 0x0400 0000 to 0x043F FFFF.

Flash memory is pre-loaded with boot code for the power-on-self test

(POST) program. For more information, refer to “Power-On-Self Test”

on page 1-22.

By default, the EZ-Board boots from the 8-bit parallel flash memory. The

processor boots from flash memory if the boot mode select switch (SW4) is

set to position 2; see “Boot Mode Select Switch (SW4)” on page 2-10.

Flash memory code can be modified. For instructions, refer to the online

Help and example program included in the EZ-Board installation

directory.

For more information about the parallel flash device, refer to the Numonyx Web site:

ADSP-21489 EZ-Board Evaluation System Manual 1-11

http://www.numonyx.com.

SPI Interface

SPI Interface

The ADSP-21489 processor has two SPI ports, which can be accessed via

the digital peripheral interface (DPI) pins.

The SPI flash memory, a 16 Mb ST M25P16 device, connects to the SPI

port of the processor and designates:

• DPI pin 5 (DPI_P5) as a chip select

• DPI pin 3 (DPI_P3) as the SPI clock

• DPI pin 1 (DPI_P1) as the master out slave in (MOSI) pin

• DPI pin 2 (DPI_P2) as the master in slave out (MISO) pin

The same SPI port and DPI pins are connected to the serial flash memory

and audio codec via switch SW3. See “DPI [1–8] Enable Switch (SW3)” on

page 2-9. The DPI pins also are available on the expansion interface II.

By default, the EZ-Board boots from the 8-bit flash parallel memory. SPI

flash can be selected as the boot source by setting the boot mode select

switch (SW4) to position 1. See “Boot Mode Select Switch (SW4)” on

page 2-10.

The audio codec is set up to use DPI pin 4 as the SPI chip select. For more

information, refer to “Audio Interface” on page 1-15.

Watch Dog Timer Interface

The ADSP-21489 processor includes a 32-bit watch dog timer (WDT)

that can be used to implement a software watch dog function. A software

watch dog can improve system reliability by forcing the processor to a

known state through generation of a system reset if the timer expires

before being reloaded by software. Software initializes the count value of

the timer and then enables the timer.

1-12 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

The watch dog timer resets both the core and internal peripherals. After

an external reset, the WDT must be disabled by default. Software must be

able to determine if the watch dog has been the source of the hardware

reset by interrogating a status bit in the watch dog timer control register.

Be default, the watch timer interface is turned off. In order to use the feature, a user needs to turn switch

SW13 position 8 ON. SW13 connects the

watch dog reset out pin to the ADM708 system reset circuit. See “External

Port Enable Switch (SW13)” on page 2-12. Special attention must be paid

to this function because it can cause the processor and EZ-Board to

remain in a permanent reset.

Example programs are included in the EZ-Board installation directory to

demonstrate watch dog timer functionality.

Temperature Sensor Interface

Two external pins (THD_P and THD_M) of the processor are connected to an

internal thermal diode. The EZ-Board uses ON Semiconductor’s

ADM1032 digital thermometer and under/over temperature alarm to

monitor the processor’s temperature as well as the thermal diode’s (inside

the ADM1032 device). The thermometer uses the I2C bus, DPI pins, and

flag pins of the processor. The following DPI and flag pins are used for

temperature monitoring.

• DPI pin 8 (

• DPI pin 7 (

DPI_P8) as the serial clock signal (SCK)

DPI_P7) as the serial data signal (SDA)

• Flag 0 as the IRQ (not used by default)

• Flag 3 as the thermal limit (not used by default)

The two DPI pins are required: the pins are connected to the temperature

sensing monitor via a switch (

SW3) and can be shut off if the pins are used

on the expansion II interface. The thermal limit flag is connected to

ADSP-21489 EZ-Board Evaluation System Manual 1-13

S/PDIF Interface

an LED (

mal limit flag and ADM1032 IRQ connect to the flag pins of the

processor, but are nonessential for temperature monitoring. Consequently, the SW13 switch positions that control the flag pins are OFF by

default.

See “DPI [1–8] Enable Switch (SW3)” on page 2-9 and “External Port

Enable Switch (SW13)” on page 2-12 for more information.

Example programs are included in the EZ-Board installation directory to

demonstrate sensor operations.

LED11) for a visual alarm if the temp exceeds the limit. The ther-

S/PDIF Interface

The ADSP-21489 processor has a built-in S/PDIF transmitter and

receiver for digital audio applications. The EZ-Board supports the S/PDIF

interface and brings out both the transmitter and receiver via RCA connectors J6 and J7, respectively. The S/PDIF’s in and out pins are

connected by DAI pins via switches SW1 and SW7:

• DAI pin 1 (DAI_P1) as SPDIF_OUT

• DAI pin 18 (DPI_P18) as SPDIF_IN

SW1

and SW7 can be turned OFF to disconnect the DAI pins from the RCA

connectors if the pins are used on the expansion II interface. See “DAI [1–

8] Enable Switch (SW1)” on page 2-8 and “DAI [17–20] Enable Switch

(SW7)” on page 2-11 for more information.

1-14 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

Audio Interface

The AD1939 device is a high-performance, single-chip codec featuring

eight digital-to-analog converters (DACs) for audio output and four analog-to-digital converters (ADCs) for audio input. This translates to four

stereo channels of audio out and two stereo channels of audio in.

The codec can input and output data at a sample rate of up to 192 kHz on

all channels.

The analog audio channels are available via single-ended RCA connectors

(J4 and J5) or differential DB25 connectors (P8 and P9). By default, the

EZ-Board is shipped with the RCA connectors used by the AD1939 codec

for audio in and out. To use the differential connectors, change DIP

switches SW15–18. A standard, off the shelf DB25 connector to XLR cables

is required to operate in this mode.

For more information, see “Audio In1 Left Selection Switch (SW15)” on

page 2-14 through “Audio In2 Left Selection Switch (SW18)” on

page 2-16, and “ADSP-21489 EZ-Board Schematic” on page B-1.

The processor interfaces with the codec via DAI and DPI pins. The DAI

pins can be configured to transfer serial data from the codec in Time-Divi-

sion Multiplexing (TDM) or Integrated Interchip Sound (I2S) mode. See

“DAI Interface” on page 2-3 for more information about the AD1939

connection to the DAI. The DPI interface pins can be configured to use

the SPI interface of the processor to set up the codec’s control registers.

See “DPI Interface” on page 2-4 for more information about the AD1939

connection to the DPI.

The master input clock (MCLK) of the codec is generated by the on-board

12.288 MHz oscillator. The internal PLL of the codec is used to generate

varying sample rates. The codec can be set up for 48 KHz, 96 KHz, or

192 KHz frequencies. The codec can run at these frequencies in both

2

TDM and I

ADSP-21489 EZ-Board Evaluation System Manual 1-15

S modes with all ADCs inputs and DACs outputs. To run

Audio Interface

192 KHz with all ADCs and DACs in TDM mode, the codec must run in

dual-line TDM mode.

For information on how to configure the multi-channel codec, refer to the

product datasheet at:

http://www.analog.com/en/audiovideo-products/audio-codecs/ad1939/products/product.html

.

The EZ-Board is connected to the AD1939 codec in master mode. The

internal PLL drives the ABCLK and ALRCLK clock signals out. Both clocks

are driven back to the codec’s DBCLK and DLRCLK pins via the R257 and R258

resistors. The ABCLK and ALRCLK clocks that are driven by the codec also

connect to the processor’s serial ports via the DAI pins. Resistors R262 and

R263 are used to feed the bit clock and frame sync signals of the processor’s

serial ports. Connecting the codec in this manner enables a flexible audio

sample rate and allows the processor to run at the maximum core

frequency.

The audio interface also has a 3.5 mm connector (J8) for headphones. The

headphones share the output with the external DAC5 and DAC6 circuits of

the analog audio interface. Switch SW23 must be enabled for the headphones. A volume control potentiometer (R493) is used to increase or

decrease the headphone’s volume. For more information, see “Headphone

Enable Switch (SW23)” on page 2-18.

Example programs are included in the EZ-Board installation directory to

demonstrate how to configure and use the board’s analog audio interface.

The DAI and DPI pins going to the AD1939 device can be disabled, then

used again on the expansion II interface. Refer to “DAI Interface” on

page 2-3 and “DPI Interface” on page 2-4 for more information about the

DAI and DPI switches.

1-16 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

UART Interface

The ADSP-21489 processor features a built-in universal asynchronous

receiver and transmitter (UART). The UART interface supports full

RS-232 functionality via the Analog Devices 3.3V ADM3202 line driver

and receiver (U8). The UART signals are available on the EZ-Board via a

DIP switch (SW14). The UART signals routed through the DIP switch can

be disconnected from the respective DPI interface and used on the expansion II interface. The following DPI pins are used for the RS-232

interface.

• DPI pin 9 (DPI_P9) as UART_TX

• DPI pin 10 (DPI_P10) as UART_RX

• DPI pin 11 (DPI_P11) as UART_RTS

• DPI pin 12 (DPI_P12) as UART_CTS

Example programs are included in the EZ-Board installation directory to

demonstrate UART and RS-232 operations.

For more information about the UART interface, refer to the

ADSP-214xx SHARC Processor Hardware Reference.

LEDs and Push Buttons

The EZ-Board has eight general-purpose user LEDs connected directly to

the processor, one LED connected to the temperature sensing monitor

(ADM1032), one EZ-Board power LED, and one board reset LED. The

EZ-board also has five push buttons: four general-purpose push buttons

connected directly to the processor and one push button for a board reset.

Table 1-3 summarizes LED connections to the processor. To use the

LEDs connected to DAI or DPI, configure the respective registers of the

ADSP-21489 EZ-Board Evaluation System Manual 1-17

LEDs and Push Buttons

processor. For more information, refer to the ADSP-214xx SHARC Processor Hardware Reference.

Table 1-3. LED Connections

LED Reference Designator Processor Pin Connected via Switch

LED1 DPI_P6 SW3.6

LED2 DPI_P13 SW14.5

LED3 DPI_P14 SW14.6

LED4 DAI_P3 SW1.3

LED5 DAI_P4 SW1.4

LED6 DAI_P15 SW2.7

LED7 DAI_P16 SW2.8

LED8 DAI_P17 SW7.1

Two general-purpose push buttons are attached to the flag pins of the processor, while the other two are attached to the DAI pins. All of the push

buttons and LEDs are connected to the processor through DIP switches.

The DIP switches can disconnect the processor pins, which in turn are

connected to the push buttons and LEDs. See the respective switch section

in “ADSP-21489 EZ-Board Hardware Reference” on page 2-1.

The state of the push buttons connected to the flag pins can be determined by reading the

FLAG register. The push buttons connected to the

DAI pins must be configured as interrupts. It is necessary to set up an

interrupt routine to determine each pin’s state. Table 1-3 shows the push

button and processor connections.

Table 1-4. Push Button Connections

PB Reference Designator Processor Pin Connected via Switch

SW8 (PB1) FLAG1/IRQ1 SW13.4

SW9

(PB2) FLAG2/IRQ2/MS2 SW13.5

1-18 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

Table 1-4. Push Button Connections (Cont’d)

PB Reference Designator Processor Pin Connected via Switch

SW10 (PB3) DAI_P19 SW7.3

SW11 (PB4) DAI_P20 SW7.4

An example program is included in the ADSP-21489 installation directory

to demonstrate functionality of the LEDs and push buttons.

JTAG Interface

The JTAG connector (P1) allows the standalone debug agent module to

connect a VisualDSP++ debug session to the ADSP-21489 processor. The

debug agent operates only when the external 5V wall adaptor (P16) is

used.

The standalone debug agent can be replaced by an external emulator, such

as the Analog Devices high-performance USB-based emulator. Be careful

not to damage the connectors when removing the debug agent. The emulator is connected to P1 on the back side of the board. See “EZ-Board

Installation” on page 1-5 for more information.

The ADSP-21489 EZ-Board can be set up as a single- or multi-processor

system. By default, the board is set up in single-processor mode. In single-processor mode, create a VisualDSP++ session based on a standalone

debug agent or an external emulator. To use the EZ-Board in multi-processor mode, install an external emulator. Only one external emulator is

required for the main EZ-Board; other EZ-Boards in the JTAG chain do

not require an emulator. In this mode, create a VisualDSP++ platform

based on the number of JTAG devices in the JTAG chain using the VisualDSP++ Configurator. Then create a session in VisualDSP++ based on

the newly created platform.

ADSP-21489 EZ-Board Evaluation System Manual 1-19

Expansion Interface II

For a dual ADSP-21489 EZ-Board session, connect two EZ-Boards via

connectors

J3 and P12. Flip one of the two EZ-Boards by 180 degrees to

allow the boards to mate. To switch between single- and multi-processor

modes, use DIP switches SW19–22. For more information, see “JTAG

Switches (SW19–22)” on page 2-16.

For three or more ADSP-21489 EZ-Board sessions, connect each of the

EZ-Board with JTAG cables. The cables connect JTAG pins of each

EZ-Board. By using the cables, you put the EZ-Board in a JTAG serial

chain. For three EZ-Boards, three JTAG cables are required. Similarly, for

four EZ-Boards, four JTAG cables are required. Note that each respective

EZ-board also requires its own power supply.

Part numbers for Samtec standard, off the shelf link port cables can be

found in “MP JTAG Out Connector (P12)” on page 2-28.

For more information about emulators, contact Analog Devices or go to:

http://www.analog.com/en/embedded-processing-dsp/sharc/content/sharc_development_tools/fca.html

.

Expansion Interface II

The expansion interface II allows an Analog Devices EZ-Extender or a

custom-design daughter board to be tested across various hardware platforms with identical expansion interfaces.

The expansion interface II implemented on the ADSP-21489 EZ-Board

consists of two connectors: a 0.1 in. shrouded header (

QMS series header (

J1). The connectors contain a majority of the

ADSP-21489 processor’s signals.

For pinout information, go to “ADSP-21489 EZ-Board Schematic” on

page B-1. The mechanical dimensions of the expansion connectors can be

obtained by contacting Technical or Customer Support.

1-20 ADSP-21489 EZ-Board Evaluation System Manual

P2) and a Samtec

Using ADSP-21489 EZ-Board

For more information about daughter boards, visit the Analog Devices

Web site at:

http://www.analog.com/en/embedded-processing-dsp/sharc/content/sharc_development_tools/fca.html

Limits to current and interface speed must be taken into consideration

when using the expansion interface II. Current for the expansion

interface II is sourced from the EZ-Board; therefore, the current should be

limited to 1A for 5V and 500 mA for the 3.3V planes. If more current is

required, then a separate power connector and a regulator must be

designed on a daughter card. Additional circuitry can add extra loading to

signals, decreasing their maximum effective speed.

.

L

Analog Devices does not support and is not responsible for the

effects of additional circuitry.

Power Measurements

Several locations are provided for measuring the current draw from various power planes. Precision 0.05 ohm shunt resistors are available on the

VDDINT and VDDEXT voltage domains. For current draw measurements, the associated jumper on connectors P14—15 must be removed.

Once the jumper is removed, voltage across the resistor can be measured

using an oscilloscope. Once voltage is measured, current can be calculated

by dividing voltage by 0.05. For the highest accuracy, a differential probe

should be used for measuring voltage across the resistor.

For more information, see “VDDINT Power Connector (P14)” on

page 2-28 and “VDDEXT Power Connector (P15)” on page 2-29.

ADSP-21489 EZ-Board Evaluation System Manual 1-21

Power-On-Self Test

Power-On-Self Test

The power-on-self-test program (POST) tests all EZ-Board peripherals

and validates functionality as well as connectivity to the processor. Once

assembled, each EZ-Board is fully tested for an extended period of time

with a POST. All EZ-Boards are shipped with the POST preloaded into

one of their on-board flash memories. The POST is executed by resetting

the board and pressing the proper push button(s). The POST also can be

used for reference in custom software designs or hardware troubleshooting. Note that the source code for the POST program is included in the

VisualDSP++ installation directory along with the readme text file, which

describes how the board is configured to run a POST.

Example Programs

Example programs are provided with the ADSP-21489 EZ-Board to demonstrate various capabilities of the product. The programs are installed

with the VisualDSP++ software and can be found in the

<install_path>\214xx\Examples\ADSP-21489 EZ-Board directory. Refer

to the readme file provided with each example for more information.

Background Telemetry Channel

The USB debug agent supports the background telemetry channel (BTC),

which facilitates data exchange between VisualDSP++ and the processor

without interrupting processor execution.

The BTC allows you to read and write data in real time while the processor continues to execute. For increased performance of the BTC,

including faster reading and writing, please check our latest line of processor emulators at:

http://www.analog.com/en/embedded-processing-dsp/sharc/USB-EMU-

1-22 ADSP-21489 EZ-Board Evaluation System Manual

Using ADSP-21489 EZ-Board

LATOR/products/product.html. For more information about BTC, see the

online help.

Reference Design Information

A reference design info package is available for download on the Analog

Devices Web site. The package provides information on the design, layout, fabrication, and assembly of the EZ-KIT Lite and EZ-Board

products.

The information can be found at:

http://www.analog.com/en/evaluation-boards-kits/resources/embedded-processing-dsp/blackfin/index.html.

ADSP-21489 EZ-Board Evaluation System Manual 1-23

Reference Design Information

1-24 ADSP-21489 EZ-Board Evaluation System Manual

2 ADSP-21489 EZ-BOARD

HARDWARE REFERENCE

This chapter describes the hardware design of the ADSP-21489 EZ-Board

board.

The following topics are covered.

• “System Architecture” on page 2-2

Describes the board’s configuration and explains how the board

components interface with the processor.

• “Flags and Memory Selects” on page 2-6

Shows the locations and describes the DAI pins, DPI pins, general

purpose flags, and asynchronous memory select lines.

• “Push Buttons and Switches” on page 2-7

Shows the locations and describes the push buttons and switches.

• “Jumpers” on page 2-19

Shows the locations and describes the configuration jumpers.

• “LEDs” on page 2-21

Shows the locations and describes the LEDs.

• “Connectors” on page 2-24

Shows the locations and provides part numbers for the on-board

connectors. In addition, the manufacturer and part number information is provided for the mating parts.

ADSP-21489 EZ-Board Evaluation System Manual 2-1

System Architecture

ADSP-21489

Processor

400 MHz

176-lead LQFP

JTAG

Port

32 MB

SDRAM

(16Mb x 16)

25 MHz

Oscillator

DPI

Power

Regulation

AD1939

CODEC

Mic

In

Aud

In

(4)

Head

Out

Aud

Out

(8)

External

Port

4 MB

Flash

(4M x 16 )

DAI

CLK

TEMP

Sensor

MP

JTAG

IN

JTAG

CONN

Stand

Alone

Debug

Agent

ADM1032

SPI

Flash

16Mb

ADM3202

RS232

CONN

SPDIF

CIRC

SPDIF

IN

SPDIF

OUT

I2C

5V

PWR

IN

3.3V (Adjustable)

1.1V (Adjustable)

Sharc Expansion Interface II.

DAI = 0.1" Header

DPI = 0.1" Header

Ext. Port = High Speed Conn.

Ext. Port

DAI

DPI

PBs/

LEDs

MP

JTAG

OUT

WDT

DSP

Reset

ADM708

Reset

Supervisor

Jumper

2 MB

SRAM

(1M x 16)

Ext

Clock

Test Point/

Crystal

System Architecture

This section describes the processor’s configuration on the EZ-Board

(Figure 2-1).

Figure 2-1. EZ-Board Block Diagram

The EZ-Board is designed to demonstrate the ADSP-21489 SHARC processor capabilities. The processor runs at 400 MHz and has an I/O voltage

of 3.3V. The core voltage of the processor is 1.1V.

2-2 ADSP-21489 EZ-Board Evaluation System Manual

ADSP-21489 EZ-Board Hardware Reference

The input clock is 25 MHz. The default boot mode of the processor is

external parallel flash boot. See “Boot Mode Select Switch (SW4)” on

page 2-10 for information on how to change the default boot mode.

DAI Interface

The digital application interface (DAI) pins are connected to the signal

routing unit (SRU) of the processor. The SRU is a flexible routing system

providing a large system of signal flows within the processor. The SRU

allows you to route the DAI pins to different internal peripherals in various combinations.

The DAI connects various peripherals on the EZ-Board. Table 2-1 shows

the DAI pin names, associated peripheral and net names, switch designators through which the pins are connected to the peripherals, and default

switch settings.

Table 2-1. DAI Connections

DAI Pin Peripheral Peripheral Net Connected via

Switch

DAI_P1 S/PDIF SPDIF_OUT SW1.1 ON

DAI_P2 AD1939 SOFT_RESET SW1.2 ON

DAI_P3 LEDs LED4 SW1.3 ON

DAI_P4

DAI_P5 AD1939 ASDATA1 SW1.5 ON

DAI_P6 AD1939 ASDATA2 SW1.6 ON

DAI_P7

DAI_P8

DAI_P9 AD1939 DSDATA4 SW2.1 ON

DAI_P10

DAI_P11

DAI_P12

LEDs LED5 SW1.4 ON

AD1939 ABCLK SW1.7 ON

AD1939 ALRCLK SW1.8 ON

AD1939 DSDATA3 SW2.2 ON

AD1939 DSDATA2 SW2.3 ON

AD1939 DSDATA1 SW2.4 ON

Switch Setting

(Default)

ADSP-21489 EZ-Board Evaluation System Manual 2-3

System Architecture

Table 2-1. DAI Connections (Cont’d)

DAI Pin Peripheral Peripheral Net Connected via

Switch

DAI_P13 AD1939 DBCLK SW2.5 OFF

DAI_P14 AD1939 DLRCLK SW2.6 OFF

DAI_P15 LEDs LED6 SW2.7 ON

DAI_P16 LEDs LED7 SW2.8 ON

DAI_P17 LEDs LED8 SW7.1 ON

DAI_P18 S/PDIF SPDIF_IN SW7.2 ON

DAI_P19 Push buttons PB3 SW7.3 ON

DAI_P20 Push buttons PB4 SW7.4 ON

Switch Setting

(Default)

To use the DAI on the expansion II interface, disable any signal driving a

DAI pin with the associated switch. The pinout of the expansion connectors can be found in “ADSP-21489 EZ-Board Schematic” on page B-1.

DPI Interface

The digital peripheral interface (DPI) pins are connected to a second signal routing unit of the processor (SRU2). The SRU2 unit, similar to the

SRU, is a flexible routing system providing a large system of signal flows

within the processor. The SRU2 allows you to route the DPI pins to different internal peripherals in various combinations.

The DPI connects various peripherals on the EZ-Board. Table 2-2 shows

the DPI pin names, associated peripheral and net names, switch designa-

2-4 ADSP-21489 EZ-Board Evaluation System Manual

ADSP-21489 EZ-Board Hardware Reference

tors through which the pins are connected to the peripherals, and default

switch settings.

Table 2-2. DPI Connections

DPI Pin Peripheral Peripheral Net Connected via

Switch

DPI_P1 SPI memory/

SPI_MOSI SW3.1 ON

Switch Setting

(Default)

AD1939

DPI_P2 SPI memory/

SPI_MISO SW3.2 ON

AD1939

DPI_P3 SPI memory/

SPI_CLK SW3.3 ON

AD1939

DPI_P4 AD1939 AD1939_CS SW3.4 ON

DPI_P5 SPI memory SPI_CS SW3.5 ON

DPI_P6 LEDs LED1 SW3.6 ON

DPI_P7 Temp sensor TEMP_SDA SW3.7 ON

DPI_P8 Temp sensor TEMP_SCK SW3.8 ON

DPI_P9 UART UART_TX SW14.1 ON

DPI_P10 UART UART_RX SW14.2 ON

DPI_P11 UART UART_RTS SW14.3 OFF

DPI_P12 UART UART_CTS SW14.4 OFF

DPI_P13

DPI_P14 UART LED3 SW14.6 ON

UART LED2 SW14.5 ON

To use the DPI on the expansion II interface, disable any signal driving a

DPI pin with the associated switch. The pinout of the expansion connectors can be found in “ADSP-21489 EZ-Board Schematic” on page B-1.

ADSP-21489 EZ-Board Evaluation System Manual 2-5

Flags and Memory Selects

Flags and Memory Selects

The processor has four asynchronous memory selects, four flag pins, three

interrupt request pins, and one timer expired pin. All flag/memory pins

are multi-functional and depend on the ADSP-21489 processor setup.

Table 2-3 shows the pin names, corresponding peripheral and net names,

switch designators through which the pins are connected to the peripherals, and default switch settings.

To use the flags or memory selects on the expansion II interface, disable

any signal driving a flag or memory pin with the associated switch. The

pinout of the expansion connectors can be found in “ADSP-21489

EZ-Board Schematic” on page B-1.

Table 2-3. Flags and Memory Select Connections

Flag/Memory Pin Peripheral Peripheral Net Connected via

Switch

MS0 SDRAM SDRAM_CS SW13.1 ON

MS1 Parallel flash memory FLASH_CS SW13.2 ON

FLAG0/IRQ0 Temp sensor TEMP_IRQ SW13.3 OFF

FLAG1/IRQ1 Push buttons PB1 SW13.4 ON

FLAG2/IRQ2/MS2 Push buttons PB2 SW13.5 ON

/TIMEXP/MS3 Temp Sensor TEMP_THERM SW13.6 OFF

FLAG3

FLAG3/TIMEXP/MS3 SRAM SRAM_CS SW13.7 ON

WDTRSTO_Z Reset Supervisory IC WDTRSTO SW13.8 OFF

Switch

Setting

(Default)

2-6 ADSP-21489 EZ-Board Evaluation System Manual

ADSP-21489 EZ-Board Hardware Reference

Push Buttons and Switches

This section describes operation of the push buttons and switches. The

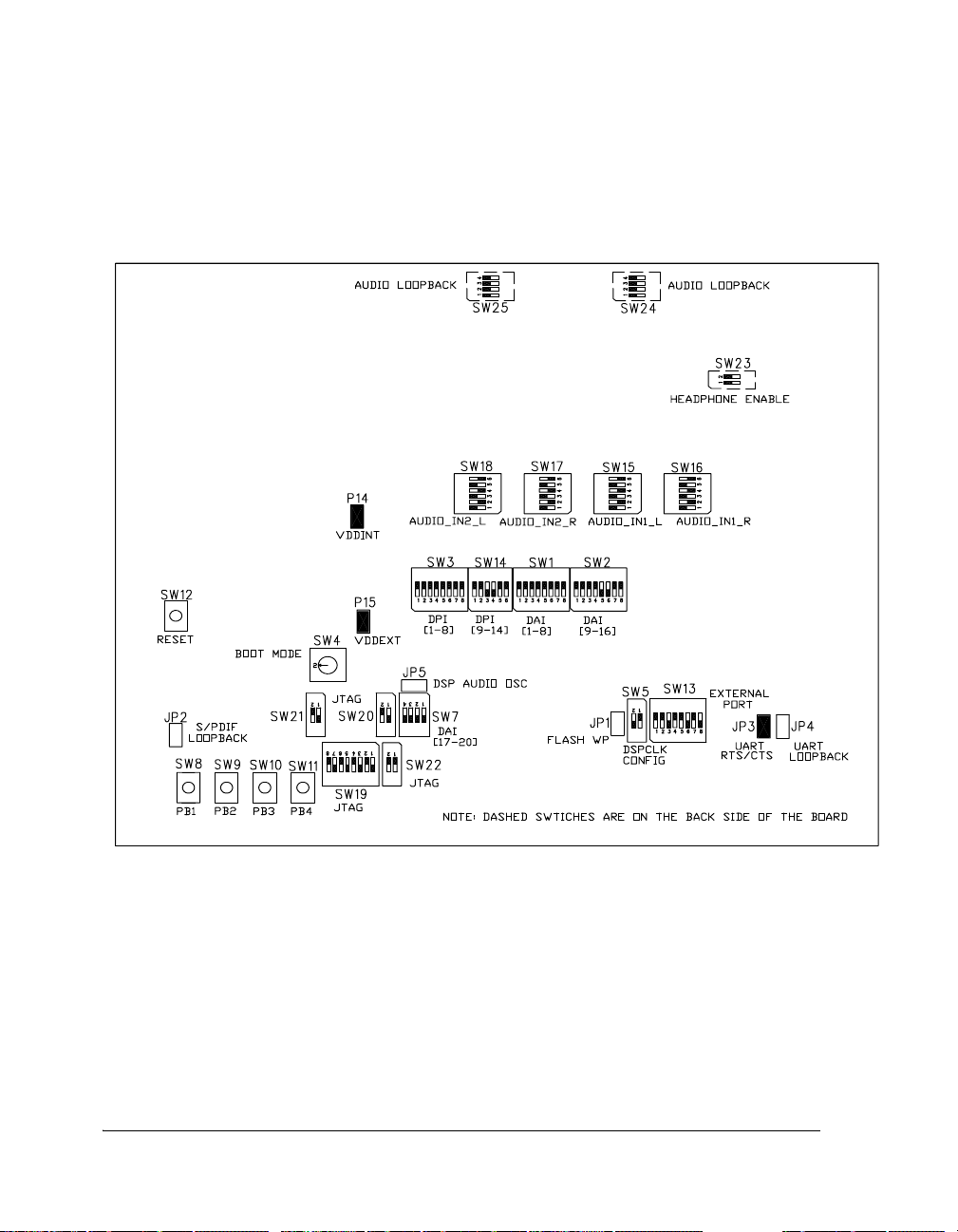

push button and switch locations are shown in Figure 2-2.

Figure 2-2. Push Button and Switch Locations

ADSP-21489 EZ-Board Evaluation System Manual 2-7

Push Buttons and Switches

DAI [1–8] Enable Switch (SW1)

The DAI [1–8] enable switch (SW1) disconnects DAI pins one through

eight on the processor from the associated peripherals on the EZ-Board

and allows the DAI signals to be used on the expansion II interface. See

Table 2-4.

Table 2-4. DAI [1–8] Enable Switch (SW1)

SW1 Position DAI Pin Peripheral Peripheral Net Switch Setting

(Default)

SW1.1 DAI_P1 S/PDIF SPDIF_OUT ON

SW1.2 DAI_P2 AD1939 AD1939_SOFT_RESET ON

SW1.3 DAI_P3 LEDs LED4 ON

SW1.4 DAI_P4 LEDs LED5 ON

SW1.5 DAI_P5 AD1939 ASDATA1 ON

SW1.6 DAI_P6 AD1939 ASDATA2 ON

SW1.7 DAI_P7 AD1939 ABCLK ON

SW1.8 DAI_P8 AD1939 ALRCLK ON

DAI [9–16] Enable Switch (SW2)

The DAI [9–16] enable switch (SW2) disconnects DAI pins nine

through 16 on the processor from the associated peripherals on the

EZ-Board and allows the DAI signals to be used on the expansion II interface. See Table 2-5.

Table 2-5. DAI [9–16] Enable Switch (SW2)

SW2 Position DAI Pin Peripheral Peripheral Net Switch Setting

(Default)

SW2.1 DAI_P9 AD1939 DSDATA4 ON

SW2.2 DAI_P10 AD1939 DSDATA3 ON

2-8 ADSP-21489 EZ-Board Evaluation System Manual

ADSP-21489 EZ-Board Hardware Reference

Table 2-5. DAI [9–16] Enable Switch (SW2) (Cont’d)

SW2 Position DAI Pin Peripheral Peripheral Net Switch Setting

(Default)

SW2.3 DAI_P11 AD1939 DSDATA2 ON

SW2.4 DAI_P12 AD1939 DSDATA1 ON

SW2.5 DAI_P13 AD1939 DBCLK OFF

SW2.6 DAI_P14 AD1939 DLRCLK OFF

SW2.7 DAI_P15 LEDs LED6 ON

SW2.8 DAI_P16 LEDs LED7 ON

DPI [1–8] Enable Switch (SW3)

The DPI [1–8] enable switch (SW3) disconnects DPI pins one through

eight on the processor from the associated peripherals on the EZ-Board

and allows the DPI signals to be used on the expansion II interface. See

Table 2-6.

Table 2-6. DPI [1–8] Enable Switch (SW3)

SW3 Position DPI Pin Peripheral Peripheral Net Switch Setting

(Default)

SW3.1 DPI_P1 SPI memory

AD1939

SW3.2 DPI_P2

SW3.3 DPI_P3 SPI memory

SW3.4 DPI_P4 AD1939 AD1939_CS ON

SW3.5 DPI_P5 SPI memory SPI_CS ON

SW3.6 DPI_P6

SW3.7 DPI_P7

SW3.8 DPI_P8

SPI memory

AD1939

AD1939

LEDs LED1 ON

Temp sensor TEMP_SDA ON

Temp sensor TEMP_SCK ON

SPI_MOSI ON

SPI_MISO ON

SPI_CLK ON

ADSP-21489 EZ-Board Evaluation System Manual 2-9

Push Buttons and Switches

Boot Mode Select Switch (SW4)

The boot mode select switch (SW4) determines the boot mode of the processor. Table 2-7 shows the available boot mode settings. By default, the

processor boots from the on-board parallel flash memory.

The selected position of

SW4 is marked by the notch down the entire rotat-

ing portion of the switch, not the small arrow.

Table 2-7. Boot Mode Select Switch (SW4)

SW4 Position Processor Boot Mode

0 SPI slave boot

1 Boot from SPI flash memory (SPI master boot)

2 Boot from 8-bit external parallel flash memory (default)

3 Reserved

4 Reserved

5 Reserved

6 Reserved

7 Reserved

DSP Clock Configuration Switch (SW5)

The clock configuration switch (SW5) controls the core frequency of the

processor at power up. The core to clock-in ratio is multiplied by the

25 MHz oscillator (

shows the switch settings.

U7) to produce the power up core frequency. Table 2-8

The core clock frequency can be increased or decreased via software by

writing to the PMCTL register. For more information on changing the core

2-10 ADSP-21489 EZ-Board Evaluation System Manual

ADSP-21489 EZ-Board Hardware Reference

clock frequency and other settings, refer to the ADSP-214xx SHARC Processor Hardware Reference.

Table 2-8. Processor Clock Configuration Switch (SW5)

Position 1

CLKCFG0

ON ON Reserved

ON OFF 32:1

OFF ON 16:1 (default)

OFF OFF 6:1

Position 2

CLKCFG0

Clock Ratio

Core: Clock

DAI [17–20] Enable Switch (SW7)

The DAI [17–20] enable switch (SW7) disconnects DAI pins 17 through

20 on the processor from the associated peripherals on the EZ-Board and

allows the DAI signals to be used on the expansion II interface. See

Table 2-9.

Table 2-9. DAI [17–20] Enable Switch (SW7)

SW7 Position DAI Pin Peripheral Peripheral Net Switch Setting

(Default)

SW7.1 DAI_P17 LEDs LED8 ON

SW7.2 DAI_P18

SW7.3 DAI_P19 Push buttons PB3 ON

S/PDIF SPDIF_IN ON

SW7.4 DAI_P20

Push buttons PB4 ON

ADSP-21489 EZ-Board Evaluation System Manual 2-11

Push Buttons and Switches

Programmable Flag Push Buttons (SW8–11)

Four momentary push buttons (SW8–11) are provided for general-purpose

user input. The buttons are connected to the GPIO pins of the processor.

The push buttons are active high and, when pressed, send a high (1) to the

processor. Switches SW7 and SW13 disconnect the push buttons from the

responding signals. Refer to “DAI [17–20] Enable Switch (SW7)” on

page 2-11 and “External Port Enable Switch (SW13)” on page 2-12 for

more information.

Reset Push Button (SW12)

The reset push button (SW12) resets the following ICs:

• ADSP-21489 processor (U1)

• AD1939 audio codec (U45)

• Parallel flash memory (U18)

The reset also is linked to the expansion II interface; any daughter card

connected to the expansion interface that requires a reset can use SW12.

The reset push button does not reset the standalone debug agent once the

debug agent is connected to a personal computer (PC). After communication between the debug agent and PC is initialized, pushing a reset button

does not reset the USB chip on the debug agent. The only way to reset the

USB chip on the debug agent is to power down the EZ-Board.

External Port Enable Switch (SW13)

The external port enable switch (SW13) disconnects the control pins of the

processor from the associated peripherals on the EZ-Board and allows the

2-12 ADSP-21489 EZ-Board Evaluation System Manual

ADSP-21489 EZ-Board Hardware Reference

respective control signals to be used on the expansion II interface. See

Table 2-10.

Table 2-10. External Port Enable Switch (SW13)

SW13

Position

SW13.1 MS0 SDRAM SDRAM_CS ON

SW13.2 MS1 Parallel flash

SW13.3 FLAG0/IRQ0 Temp sensor TEMP_IRQ OFF

SW13.4 FLAG1/IRQ1 Push buttons PB1 ON

SW13.5 FLAG2/IRQ2/MS2 Push buttons PB2 ON

SW13.6 FLAG3/TIMEXP/MS3 Temp sensor TEMP_THERM OFF

SW13.7 FLAG3/TIMEXP/MS3 SRAM SRAM_CS ON

SW13.8 WDTRSTO (Watch Dog

Processor Pin Peripheral Peripheral Net Switch Setting

(Default)

FLASH_CS ON

memory

Rest Out)

Reset Supervisory IC

WDTRSTO OFF

DPI [9–14] Enable Switch (SW14)

The DPI [9–14] enable switch (SW14) disconnects DPI pins nine through

14 on the processors from the associated peripherals on the EZ-Board and

allows the DPI signals to be used on the expansion II interface. See

Table 2-11.

Table 2-11. DPI [9–14] Enable Switch (SW14)

SW14

Position

SW14.1 DPI_P9 UART UART_TX ON

SW14.2 DPI_P10 UART UART_RX ON

SW14.3 DPI_P11

SW14.4 DPI_P12

DPI Pin Peripheral Peripheral Net Switch Setting

(Default)

UART UART_RTS OFF

UART UART_CTS OFF

ADSP-21489 EZ-Board Evaluation System Manual 2-13

Push Buttons and Switches

Table 2-11. DPI [9–14] Enable Switch (SW14) (Cont’d)

SW14

Position

SW14.5 DPI_P13 LEDs LED2 ON

SW14.6 DPI_P14 LEDs LED3 ON

DPI Pin Peripheral Peripheral Net Switch Setting

(Default)

Audio In1 Left Selection Switch (SW15)

The audio selection switch (SW15) connects the left channel of the In1 line,

connected to the AD1939’s ADC1 circuit, to either the single-ended RCA

connectors or the differential DB25 connector. By default, SW15 is set up