ANALOG DEVICES ADRF6701 Service Manual

400 MHz to 1250 MHz Quadrature Modulator with

V

V

V

V

V

V

V

750 MHz to 1150 MHz Frac-N PLL and Integrated VCO

Data Sheet

FEATURES

IQ modulator with integrated fractional-N PLL

Output frequency range: 400 MHz to 1250 MHz

Internal LO frequency range: 750 MHz to 1150 MHz

Output P1dB: 10.3 dBm @ 1100 MHz

Output IP3: 30.1 dBm @ 1100 MHz

Noise floor: −159.4 dBm/Hz @ 1100 MHz

Baseband bandwidth: 750 MHz (3 dB)

SPI serial interface for PLL programming

Integrated LDOs and LO buffer

Power supply: 5 V/240 mA

40-lead 6 mm × 6 mm LFCSP

APPLICATIONS

Cellular communications systems

GSM/EDGE, CDMA2000, W-CDMA, TD-SCDMA, LTE

Broadband wireless access systems

Satellite modems

GENERAL DESCRIPTION

The ADRF6701 provides a quadrature modulator and

synthesizer solution within a small 6 mm × 6 mm footprint

while requiring minimal external components.

The ADRF6701 is designed for RF outputs from 400 MHz to

1250 MHz. The low phase noise VCO and high performance

quadrature modulator make the ADRF6701 suitable for next

generation communication systems requiring high signal

dynamic range and linearity. The integration of the IQ

ADRF6701

modulator, PLL, and VCO provides for significant board

savings and reduces the BOM and design complexity.

The integrated fractional-N PLL/synthesizer generates a 2× f

input to the IQ modulator. The phase detector together with an

external loop filter is used to control the VCO output. The VCO

output is applied to a quadrature divider. To reduce spurious

components, a sigma-delta (Σ-) modulator controls the

programmable PLL divider.

The IQ modulator has wideband differential I and Q inputs,

which support baseband as well as complex IF architectures.

The single-ended modulator output is designed to drive a

50 Ω load impedance and can be disabled.

The ADRF6701 is fabricated using an advanced silicongermanium BiCMOS process. It is available in a 40-lead,

exposed-paddle, Pb-free, 6 mm × 6 mm LFCSP package.

Performance is specified from −40°C to +85°C. A lead-free

evaluation board is available.

Table 1.

IQ Modulator

Part No. Internal LO Range

±3 dB RF Output Range

ADRF6701 750 MHz 400 MHz

1150 MHz 1250 MHz

ADRF6702 1550 MHz 1200 MHz

2150 MHz 2400 MHz

ADRF6703 2100 MHz 1550 MHz

2600 MHz 2650 MHz

LO

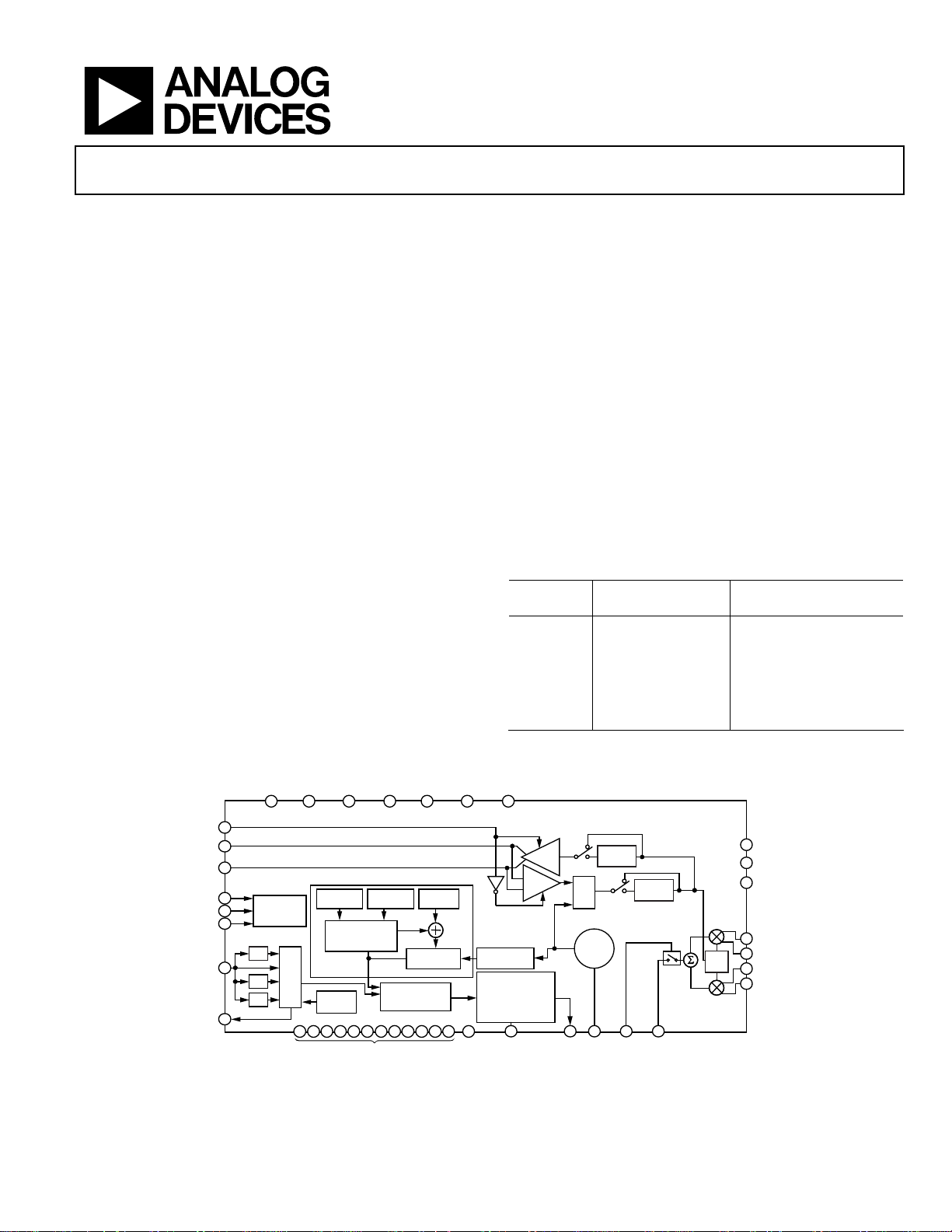

FUNCTIONAL BLOCK DIAGRAM

CC3

CC4

CC5

CC6

CC7

29

34

36

LOSEL

LON

37

38

LOP

12

DATA

13

CLK

14

LE

6

REFIN

8

MUXOUT

NOTES

1. NC = NO CONNEC T. DO NOT CONNECT TO THIS P IN.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

SPI

INTERFACE

×2

MUX

÷2

÷4

27 17 10 122

FRACTION

SENSOR

4

7 11 15 20 21 23 2425 28 30 31 35

MODULUS

REG

THIRD-ORDER

FRACTIONAL

INTERPOL ATOR

TEMP

GND

N COUNTER

–

PHASE

+

FREQUENCY

DETECTOR

21 TO 123

INTEGER

REG

CC1

CC2

PRESCALER

÷2

CHARGE PUMP

250µA,

500µA (DEFAULT ),

750µA,

1000µA

RSET CP VTUNE

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

BUFFER

BUFFER

2:1

MUX

VCO

CORE

DIVIDER

÷2

ENOP

ADRF6701

DIVIDER

÷2

26163935

RFOUTNC

0/90

40

DECL3

9

DECL2

2

DECL1

18

QP

19

QN

÷2

32

IN

33

IP

08567-001

ADRF6701 Data Sheet

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Timing Characteristics ................................................................ 6

Absolute Maximum Ratings............................................................ 7

ESD Caution.................................................................................. 7

Pin Configuration and Function Descriptions............................. 8

Typical Performance Characteristics ........................................... 10

Theory of Operation ...................................................................... 16

PLL + VCO.................................................................................. 16

Basic Connections for Operation............................................. 16

External LO ................................................................................. 16

Loop Filter ................................................................................... 17

DAC-to-IQ Modulator Interfacing ..........................................18

Adding a Swing-Limiting Resistor........................................... 18

IQ Filtering.................................................................................. 19

Baseband Bandwidth ................................................................. 19

Device Programming and Register Sequencing..................... 19

Register Summary .......................................................................... 20

Register Description....................................................................... 21

Register 0—Integer Divide Control (Default: 0x0001C0) .... 21

Register 1—Modulus Divide Control (Default: 0x003001).. 22

Register 2—Fractional Divide Control (Default: 0x001802) 22

Register 3—Σ- Modulator Dither Control (Default:

0x10000B).................................................................................... 23

Register 4—PLL Charge Pump, PFD, and Reference Path

Control (Default: 0x0AA7E4)................................................... 24

Register 5—LO Path and Modulator Control (Default:

0x0000D5)................................................................................... 26

Register 6—VCO Control and VCO Enable (Default:

0x1E2106).................................................................................... 27

Register 7—External VCO Enable and Second lo divider.... 27

Characterization Setups................................................................. 28

Evaluation Board............................................................................ 30

Evaluation Board Control Software......................................... 30

Outline Dimensions....................................................................... 35

Ordering Guide .......................................................................... 35

REVISION HISTORY

9/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 36

Data Sheet ADRF6701

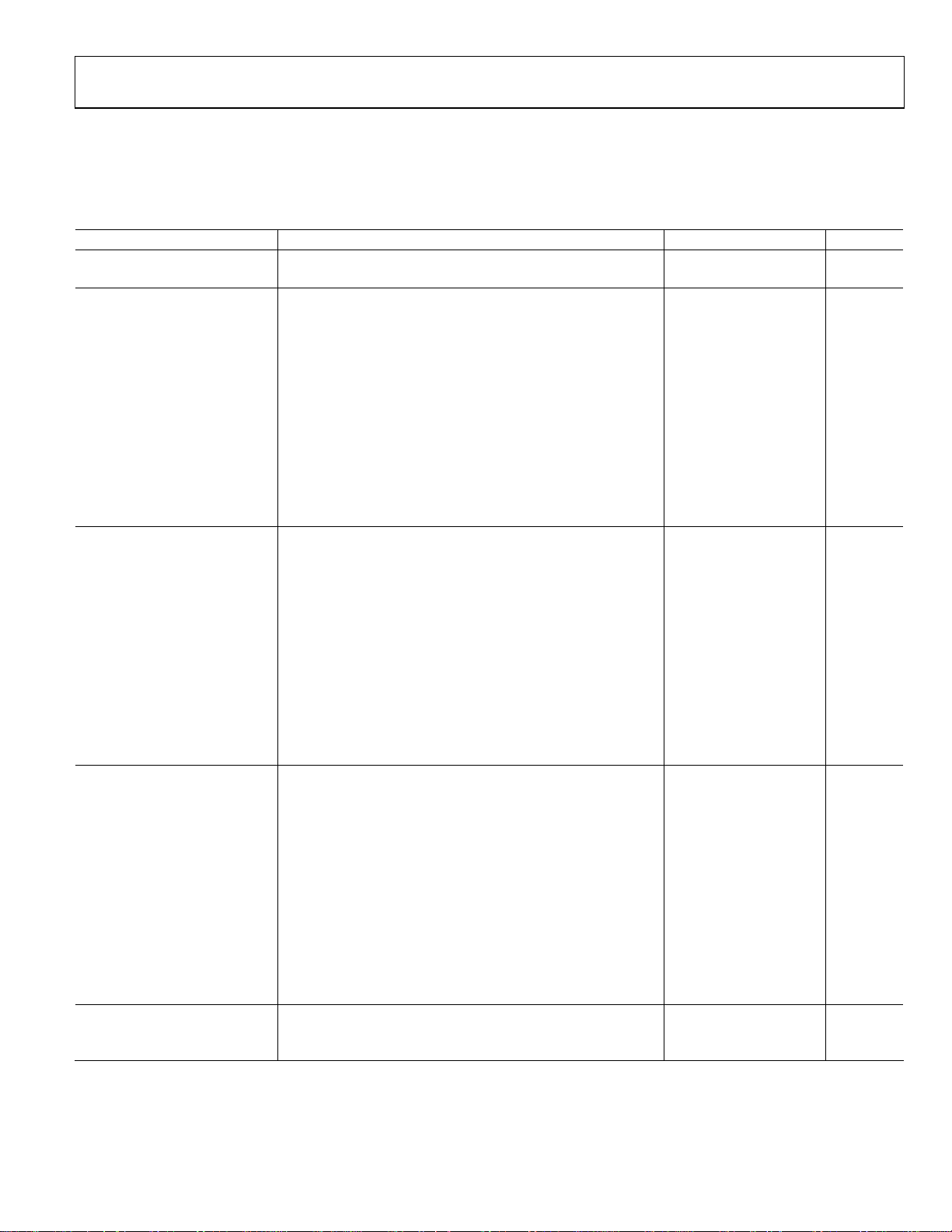

SPECIFICATIONS

VS = 5 V; TA = 25°C; baseband I/Q amplitude = 1 V p-p differential sine waves in quadrature with a 500 mV dc bias; baseband I/Q

frequency (f

Table 2.

Parameter Test Conditions/Comments Min Typ Max Unit

OPERATING FREQUENCY RANGE IQ modulator (±3 dB RF output range) 400 1250 MHz

PLL LO range 750 1150 MHz

RF OUTPUT = 800 MHz RFOUT pin

Nominal Output Power Baseband VIQ = 1 V p-p differential 4.4 dBm

IQ Modulator Voltage Gain RF output divided by baseband input voltage 0.4 dB

OP1dB 12.5 dBm

Carrier Feedthrough −49.9 dBm

Sideband Suppression −53.9 dBc

Quadrature Error −0.75 Degrees

I/Q Amplitude Balance 0.03 dB

Second Harmonic P

Third Harmonic P

Output IP2 f1BB = 3.5 MHz, f2BB = 4.5 MHz, P

Output IP3 f1BB = 3.5 MHz, f2BB = 4.5 MHz, P

Noise Floor I/Q inputs = 0 V differential with 500 mV dc bias, 20 MHz carrier offset −157.9 dBm/Hz

RF OUTPUT = 950 MHz RFOUT pin

Nominal Output Power Baseband VIQ = 1 V p-p differential 3.8 dBm

IQ Modulator Voltage Gain RF output divided by baseband input voltage −0.2 dB

OP1dB 11.2 dBm

Carrier Feedthrough −46.2 dBm

Sideband Suppression −45.4 dBc

Quadrature Error −0.5 Degrees

I/Q Amplitude Balance 0.03 dB

Second Harmonic P

Third Harmonic P

Output IP2 f1BB = 3.5 MHz, f2BB = 4.5 MHz, P

Output IP3 f1BB = 3.5 MHz, f2BB = 4.5 MHz, P

Noise Floor I/Q inputs = 0 V differential with 500 mV dc bias, 20 MHz carrier offset −157.9 dBm/Hz

RF OUTPUT = 1100 MHz RFOUT pin

Nominal Output Power Baseband VIQ = 1 V p-p differential 2.1 dBm

IQ Modulator Voltage Gain RF output divided by baseband input voltage −1.9 dB

OP1dB 10.3 dBm

Carrier Feedthrough −49.9 dBm

Sideband Suppression −47.2 dBc

Quadrature Error −0.5 Degrees

I/Q Amplitude Balance 0.03 dB

Second Harmonic P

Third Harmonic P

Output IP2 f1BB = 3.5 MHz, f2BB = 4.5 MHz, P

Output IP3 f1BB = 3.5 MHz, f2BB = 4.5 MHz, P

Noise Floor I/Q inputs = 0 V differential with 500 mV dc bias, 20 MHz carrier offset −159.4 dBm/Hz

SYNTHESIZER SPECIFICATIONS Synthesizer specifications referenced to the modulator output

Internal LO Range 750 1150 MHz

Figure of Merit (FOM)1 −222 dBc/Hz/Hz

) = 1 MHz; f

BB

= 38.4 MHz; f

PFD

OUT

OUT

OUT

OUT

OUT

OUT

= 153.6 MHz at +4 dBm Re:50 (1 V p-p); 130 kHz loop filter, unless otherwise noted.

REF

− P (fLO ± (2 × fBB)) −81.9 dBc

− P (fLO ± (3 × fBB)) −58.8 dBc

≈ −2 dBm per tone >70 dBm

OUT

≈ −2 dBm per tone 30.8 dBm

OUT

− P (fLO ± (2 × fBB)) −76.5 dBc

− P (fLO ± (3 × fBB)) −59.1 dBc

≈ −2 dBm per tone >70 dBm

OUT

≈ −2 dBm per tone 31.7 dBm

OUT

− P (fLO ± (2 × fBB)) −77.7 dBc

− P (fLO ± (3 × fBB)) −60.3 dBc

≈ −2 dBm per tone >70 dBm

OUT

≈ −2 dBm per tone) 30.1 dBm

OUT

Rev. 0 | Page 3 of 36

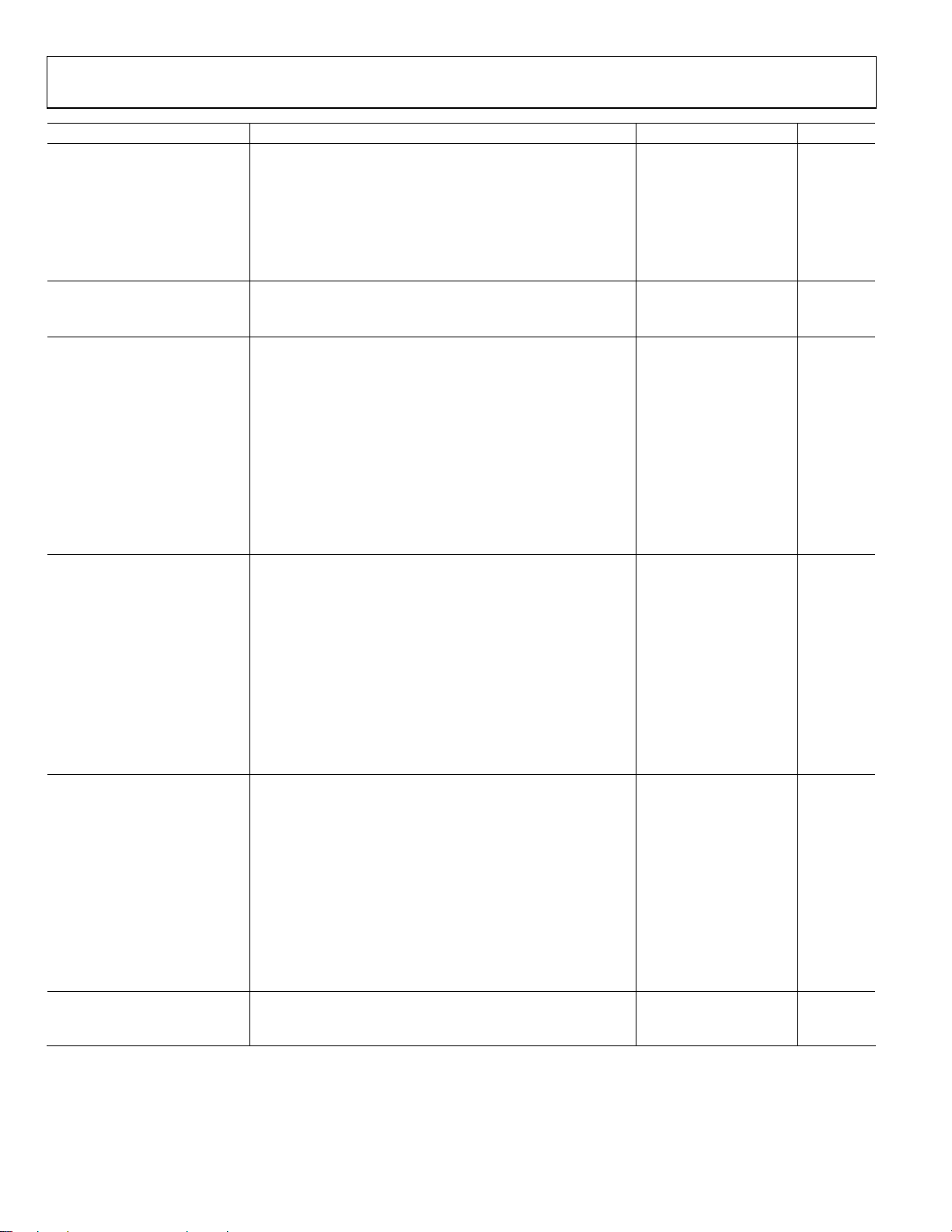

ADRF6701 Data Sheet

Parameter Test Conditions/Comments Min Typ Max Unit

REFERENCE CHARACTERISTICS REFIN, MUXOUT pins

REFIN Input Frequency 12 160 MHz

REFIN Input Capacitance 4 pF

Phase Detector Frequency 20 40 MHz

MUXOUT Output Level Low (lock detect output selected) 0.25 V

High (lock detect output selected) 2.7 V

MUXOUT Duty Cycle 50 %

CHARGE PUMP

Charge Pump Current Programmable to 250 µA, 500 µA, 750 µA, 1000 µA 500 µA

Output Compliance Range 1 2.8 V

PHASE NOISE (FREQUENCY =

800 MHz, f

= 38.4 MHz)

PFD

Closed loop operation (see

Figure 35 for loop filter design)

10 kHz offset −114 dBc/Hz

100 kHz offset −112 dBc/Hz

1 MHz offset −135 dBc/Hz

10 MHz offset −154 dBc/Hz

Integrated Phase Noise 1 kHz to 10 MHz integration bandwidth 0.09

Reference Spurs f

f

f

f

f

PHASE NOISE (FREQUENCY =

950 MHz, f

= 38.4 MHz)

PFD

/2 −113 dBc

PFD

−101 dBc

PFD

× 2 −99 dBc

PFD

× 3 −108 dBc

PFD

× 4 −99 dBc

PFD

Closed loop operation (see Figure 35 for loop filter design)

10 kHz offset −112 dBc/Hz

100 kHz offset −111 dBc/Hz

1 MHz offset −133 dBc/Hz

10 MHz offset −153 dBc/Hz

Integrated Phase Noise 1 kHz to 10 MHz integration bandwidth 0.11

Reference Spurs f

f

f

f

f

PHASE NOISE (FREQUENCY =

1100 MHz, f

= 38.4 MHz)

PFD

/2 −113 dBc

PFD

−106 dBc

PFD

× 2 −104 dBc

PFD

× 3 −100 dBc

PFD

× 4 −107 dBc

PFD

Closed loop operation (see Figure 35 for loop filter design)

10 kHz offset −113 dBc/Hz

100 kHz offset −108 dBc/Hz

1 MHz offset −135 dBc/Hz

10 MHz offset −153 dBc/Hz

Integrated Phase Noise 1 kHz to 10 MHz integration bandwidth 0.12

Reference Spurs f

f

f

f

f

/2 −112 dBc

PFD

−93 dBc

PFD

× 2 −93 dBc

PFD

× 3 −105 dBc

PFD

× 4 −103 dBc

PFD

RF OUTPUT HARMONICS Measured at RFOUT, frequency = 1100 MHz

Second harmonic −61 dBc

Third harmonic −73 dBc

°rms

°rms

°rms

Rev. 0 | Page 4 of 36

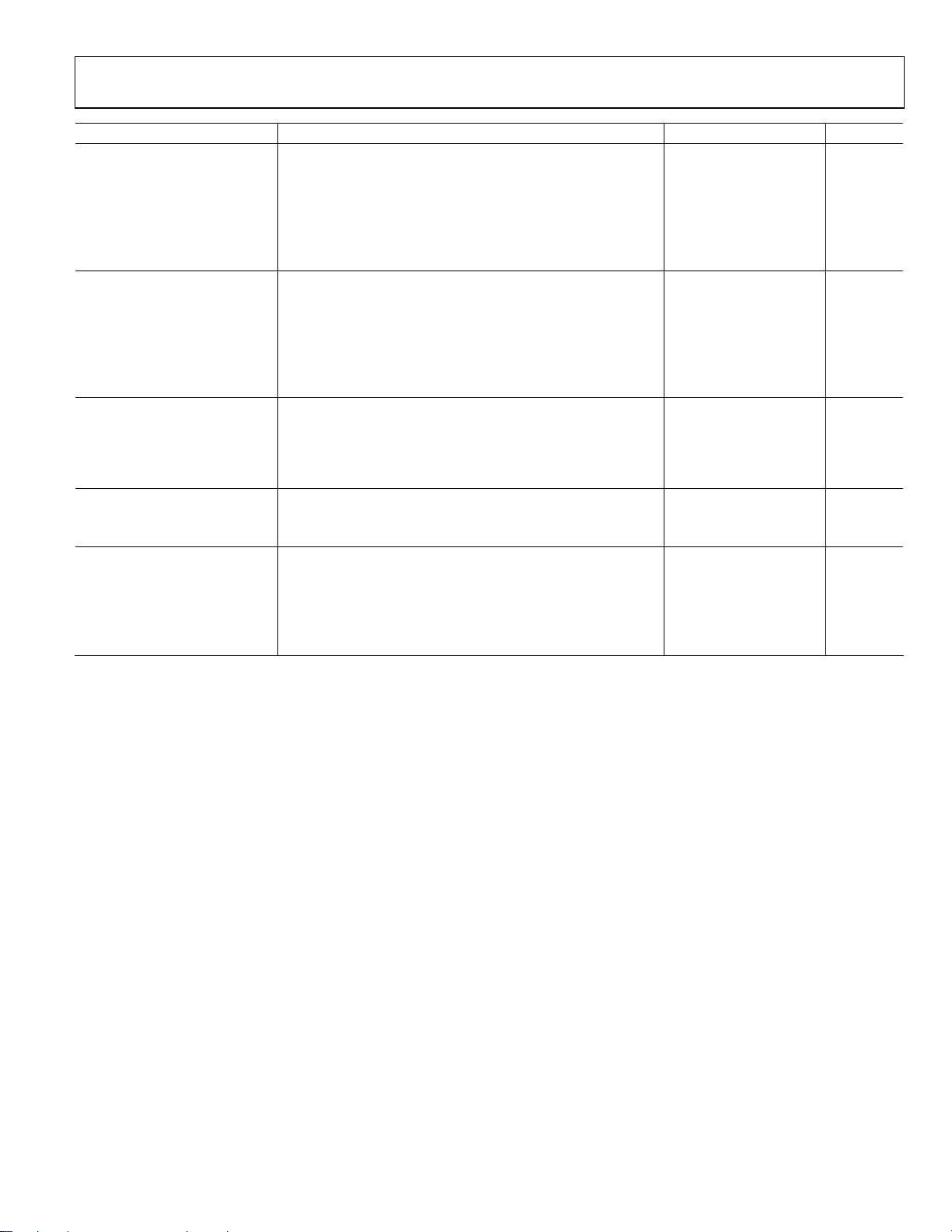

Data Sheet ADRF6701

Parameter Test Conditions/Comments Min Typ Max Unit

LO INPUT/OUTPUT LOP, LON

Output Frequency Range Divide by 4 circuit in LO path enabled 750 1150 MHz

Divide by 2 circuit in LO path disabled 1500 2300 MHz

Dividers in LO path disabled 3000 4600 MHz

LO Output Level at 950 MHz 2× LO or 1× LO mode, into a 50 Ω load, LO buffer enabled 2.5 dBm

LO Input Level Externally applied 2× LO, PLL disabled 0 dBm

LO Input Impedance Externally applied 2× LO, PLL disabled 50 Ω

BASEBAND INPUTS IP, IN, QP, QN pins

I and Q Input DC Bias Level 400 500 600 mV

Bandwidth P

0.5 dB 350 MHz

3 dB 750 MHz

Differential Input Impedance 920 Ω

Differential Input Capacitance 1 pF

LOGIC INPUTS CLK, DATA, LE, ENOP, LOSEL

Input High Voltage, V

Input Low Voltage, V

Input Current, I

1.4 3.3 V

INH

0 0.7 V

INL

0.1 µA

INH/IINL

Input Capacitance, CIN 5 pF

TEMPERATURE SENSOR VPTAT voltage measured at MUXOUT

Output Voltage

Temperature Coefficient

POWER SUPPLIES VCC1, VCC2, VCC3, VCC4, VCC5, VCC6, VCC7

Voltage Range 4.75 5 5.25 V

Supply Current Normal Tx mode (PLL and IQMOD enabled, LO buffer disabled) 240 mA

Tx mode using external LO input (internal VCO/PLL disabled) 130 mA

Tx mode with LO buffer enabled 290 mA

Power-down mode 22 µA

1

The figure of merit (FOM) is computed as phase noise (dBc/Hz) – 10log10(f

f

power = 10 dBm (500 V/s slew rate) with a 40 MHz f

REF

≈ −7 dBm, RF flatness of IQ modulator output calibrated out

OUT

= 25°C, RL ≥10 kΩ (LO buffer disabled)

T

A

= −40°C to +85°C, RL ≥10 kΩ

T

A

) – 20log10(fLO/f

. The FOM was computed at 50 kHz offset.

PFD

PFD

). The FOM was measured across the full LO range, with f

PFD

1.63 V

3.75

mV/°C

= 80 MHz,

REF

Rev. 0 | Page 5 of 36

ADRF6701 Data Sheet

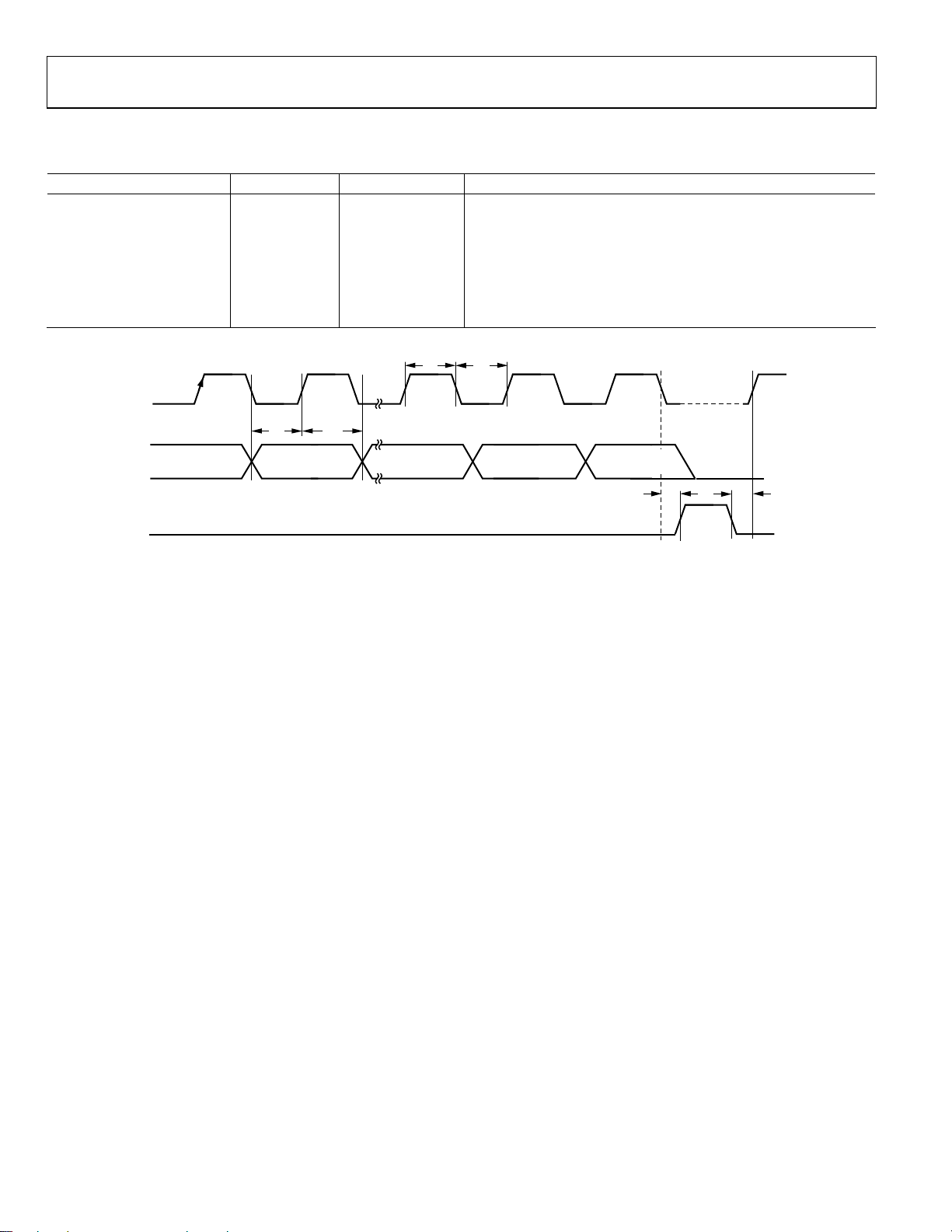

TIMING CHARACTERISTICS

Table 3.

Parameter Limit Unit Test Conditions/Comments

t1 20 ns min LE to CLK setup time

t2 10 ns min DATA to CLK setup time

t3 10 ns min DATA to CLK hold time

t4 25 ns min CLK high duration

t5 25 ns min CLK low duration

t6 10 ns min CLK to LE setup time

t7 20 ns min LE pulse width

CLK

t

4

t

5

DATA

DB23 (MSB) DB 22

LE

t

2

t

3

DB2 DB1

(CONTROL BIT C2)(CONTROL BIT C3)

DB0 (L SB)

(CONTROL BIT C1)

t

t

t

7

6

1

08567-002

Figure 2. Timing Diagram

Rev. 0 | Page 6 of 36

Data Sheet ADRF6701

ABSOLUTE MAXIMUM RATINGS

Table 4.

Parameter Rating

Supply Voltage (VCC1 to VCC7) 5.5 V

Digital I/O, CLK, DATA, LE −0.3 V to +3.6 V

LOP, LON 18 dBm

IP, IN, QP, QN −0.5 V to +1.5 V

REFIN −0.3 V to +3.6 V

θJA (Exposed Paddle Soldered Down)1 35°C/W

Maximum Junction Temperature 150°C

Operating Temperature Range −40°C to +85°C

Storage Temperature Range −65°C to +150°C

1

Per JDEC standard JESD 51-2.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 7 of 36

ADRF6701 Data Sheet

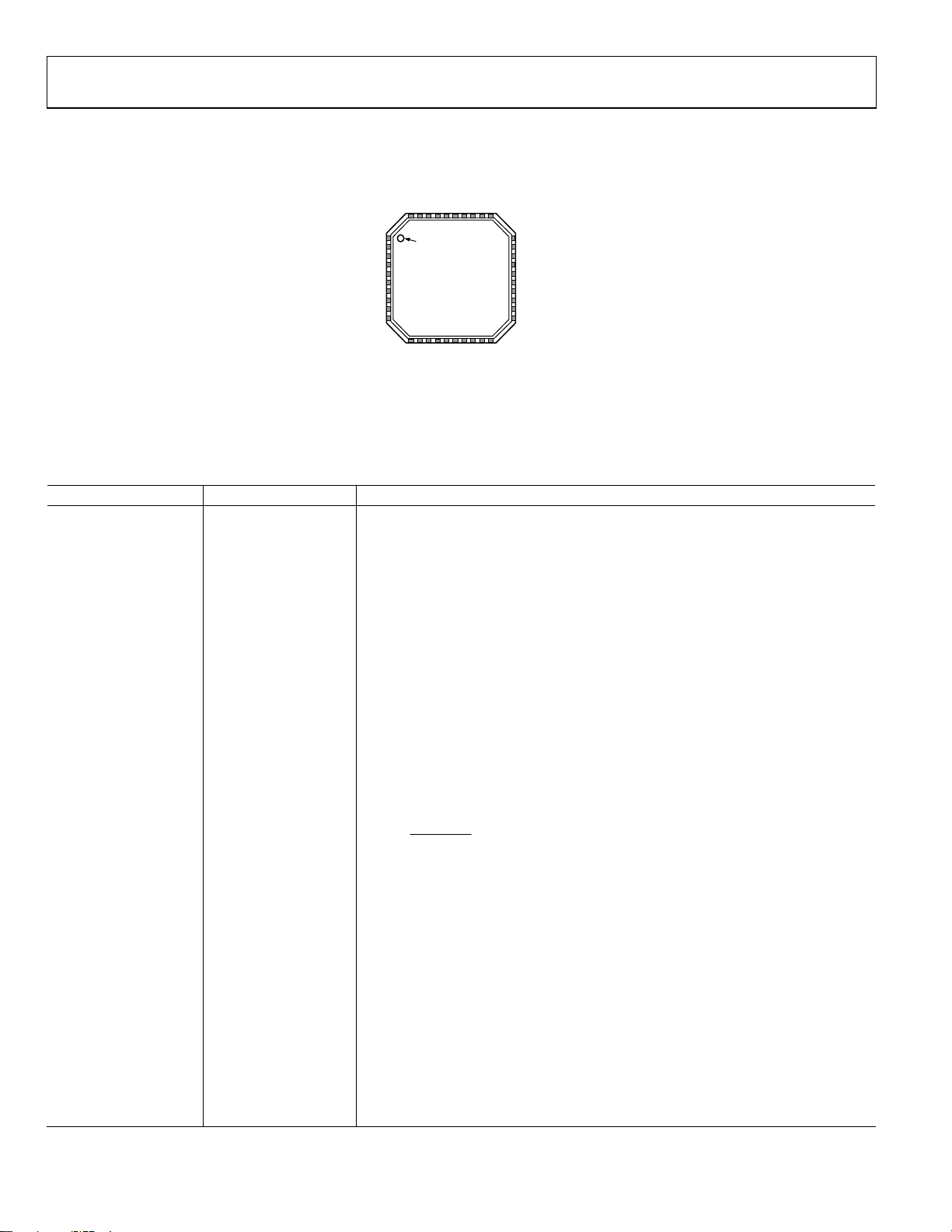

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

IP

VCC7

GND

LOSEL

LON

LOP

VTUNE

DECL3

37

38

39

40

PIN 1

1VCC1

INDICATOR

2DECL1

3CP

4

GND

RSET

REFIN

GND

MUXOUT

DECL2

10

VCC2

NOTES

1. NC = NO CONNECT. DO NOT CONNECT TO THIS PIN.

2. THE EXPOSED PADDLE SHOULD BE SOLDERED TO A

LOW IMPEDANCE GROUND PLANE.

5

6

7

8

9

ADRF6701

TOP VIEW

(Not to Scale)

11

12

13

14

LE

ND

CLK

G

DATA

Figure 3. Pin Configuration

Table 5. Pin Function Descriptions

Pin No. Mnemonic Description

1, 10, 17, 22, 27, 29, 34

2 DECL1

VCC1, VCC2, VCC3,

VCC4, VCC5, VCC6,

VCC7

Power Supply Pins. The power supply voltage range is 4.75 V to 5.25 V. Drive all of

these pins from the same power supply voltage. Decouple each pin with 100 pF and

0.1 µF capacitors located close to the pin.

Decoupling Node for Internal 3.3 V LDO. Decouple this pin with 100 pF and 0.1 µF

capacitors located close to the pin.

3 CP

Charge Pump Output Pin. Connect VTUNE to this pin through the loop filter. If

an external VCO is being used, connect the output of the loop filter to the VCO’s

voltage control pin. The PLL control loop should then be closed by routing the VCO’s

frequency output back into the ADRF6701 through the LON and LOP pins.

4, 7, 11, 15, 20, 21, 23,

GND Ground. Connect these pins to a low impedance ground plane.

25, 28, 30, 31, 35

24 NC Do not connect to this pin.

5 RSET

Charge Pump Current. The nominal charge pump current can be set to 250 µA, 500 µA,

750 µA, or 1000 µA using DB10 and DB11 of Register 4 and by setting DB18 to 0 (CP

reference source).

In this mode, no external RSET is required. If DB18 is set to 1, the four nominal charge

pump currents (I

equation:

×

4.217

⎛

⎜

= 8.37

R

SET

⎜

I

NOMINAL

⎝

where I

is the base charge pump current in microamps. For further details on the

CP

charge pump current, see the Register 4—PLL Charge Pump, PFD, and Reference Path

Control section.

6 REFIN

Reference Input. The nominal input level is 1 V p-p. Input range is 12 MHz to 160 MHz.

This pin has high input impedance and should be ac-coupled. If REFIN is being driven

by laboratory test equipment, the pin should be externally terminated with a 50 Ω

resistor (place the ac-coupling capacitor between the pin and the resistor). When

driven from an 50 Ω RF signal generator, the recommended input level is 4 dBm.

8 MUXOUT

Multiplexer Output. This output allows a digital lock detect signal, a voltage

proportional to absolute temperature (VPTAT), or a buffered, frequency-scaled

reference signal to be accessed externally. The output is selected by programming

DB21 to DB23 in Register 4.

9 DECL2

Decoupling Node for 2.5 V LDO. Connect 100 pF, 0.1 µF, and 10 µF capacitors between this

pin and ground.

12 DATA

Serial Data Input. The serial data input is loaded MSB first with the three LSBs being

the control bits.

GND

IN

3

32

31

3

34

35

36

30 GND

29 VCC6

28 GND

27 VCC5

RFOUT

26

25

GND

24 NC

23 GND

22 VCC4

21

GND

5

9

1

17

16

20

1

18

QP

QN

GND

GND

VCC3

ENOP

08567-003

) can be externally tweaked according to the following

NOMINAL

I

⎞

CP

⎟

Ω−

⎟

⎠

Rev. 0 | Page 8 of 36

Data Sheet ADRF6701

Pin No. Mnemonic Description

13 CLK

14 LE

16 ENOP Modulator Output Enable/Disable. See Table 6.

18, 19, 32, 33 QP, QN, IN, IP

26 RFOUT

36 LOSEL

37, 38 LON, LOP

39 VTUNE

40 DECL3

EP

Serial Clock Input. This serial clock input is used to clock in the serial data to the

registers. The data is latched into the 24-bit shift register on the CLK rising edge.

Maximum clock frequency is 20 MHz.

Latch Enable. When the LE input pin goes high, the data stored in the shift registers is

loaded into one of the six registers, the relevant latch being selected by the first three

control bits of the 24-bit word.

Modulator Baseband Inputs. Differential in-phase and quadrature baseband inputs.

These inputs should be dc-biased to 0.5 V.

RF Output. Single-ended, 50 Ω internally biased RF output. RFOUT must be ac-coupled

to its load.

LO Select. This digital input pin determines whether the LOP and LON pins operate as

inputs or outputs. This pin should not be left floating. LOP and LON become inputs if

the LOSEL pin is set low and the LDRV bit of Register 5 is set low. In addition to setting

LOSEL and LDRV low and providing an external 2× LO, the LXL bit of Register 5 (DB4)

must be set to 1 to direct the external LO to the IQ modulator. LON and LOP become

outputs when LOSEL is high or if the LDRV bit of Register 5 (DB3) is set to 1. A 1× LO or

2× LO output can be selected by setting the LDIV bit of Register 5 (DB5) to 1 or 0

respectively (see Tab le 7).

Local Oscillator Input/Output. The internally generated 1× LO or 2× LO is available on

these pins. When internal LO generation is disabled, an external 1× LO or 2× LO can be

applied to these pins.

VCO Control Voltage Input. This pin is driven by the output of the loop filter. Nominal

input voltage range on this pin is 1.3 V to 2.5 V. If the external VCO mode is activated,

this pin can be left open.

Decoupling Node for VCO LDO. Connect a 100 pF capacitor and a 10 µF capacitor

between this pin and ground.

Exposed Paddle. The exposed paddle should be soldered to a low impedance

ground plane.

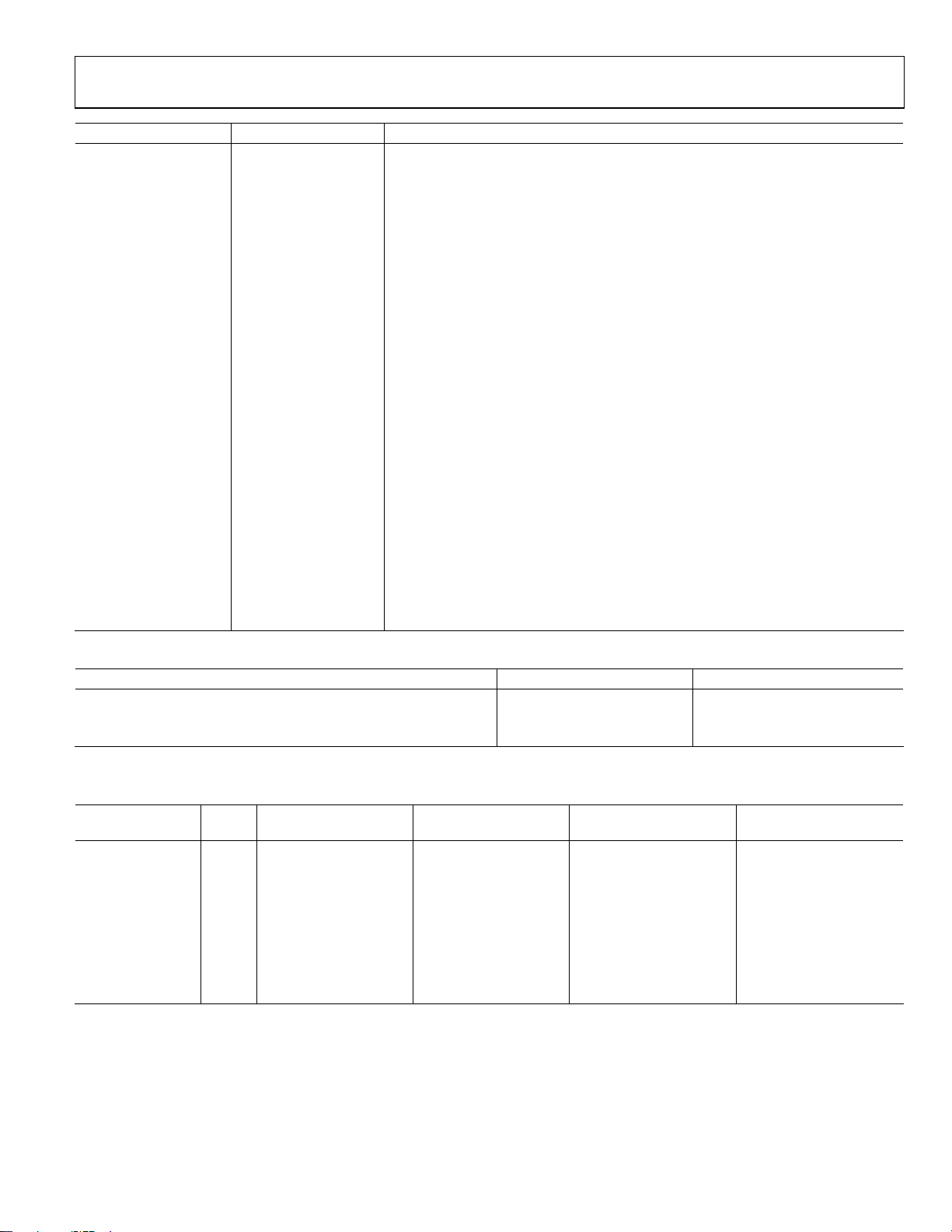

Table 6. Enabling RFOUT

ENOP Register 5 Bit DB6 RFOUT

X1 0 Disabled

0 X1 Disabled

1 1 Enabled

1

X = don’t care.

Table 7. LO Port Configuration

LON/LOP

Function LOSEL

Input (4× LO) 0 X 1 0 0

Input (2× LO) 0 X 1 0 1

Output (Disabled) 0 X 0 0 X

Output (1× LO) 0 0 0 1 0

Output (1× LO) 1 0 0 0 0

Output (1× LO) 1 0 0 1 0

Output (2× LO) 0 1 0 1 0

Output (2× LO) 1 1 0 0 0

Output (2× LO) 1 1 0 1 0

1

X = don’t care.

2

LOSEL should not be left floating.

1, 2

Register 5 Bit

DB5 (LDIV)

Register 5 Bit

DB4 (LXL)

Register 5 Bit

DB3 (LDRV)

Register 7 Bit

DB4 (LDIV2)

Rev. 0 | Page 9 of 36

ADRF6701 Data Sheet

TYPICAL PERFORMANCE CHARACTERISTICS

VS = 5 V; TA = 25°C; baseband I/Q amplitude = 1 V p-p differential sine waves in quadrature with a 500 mV dc bias; baseband I/Q

frequency (f

SSB OUTPUT POWER (d Bm)

1dB OUTPUT COMPRESSION (dBm)

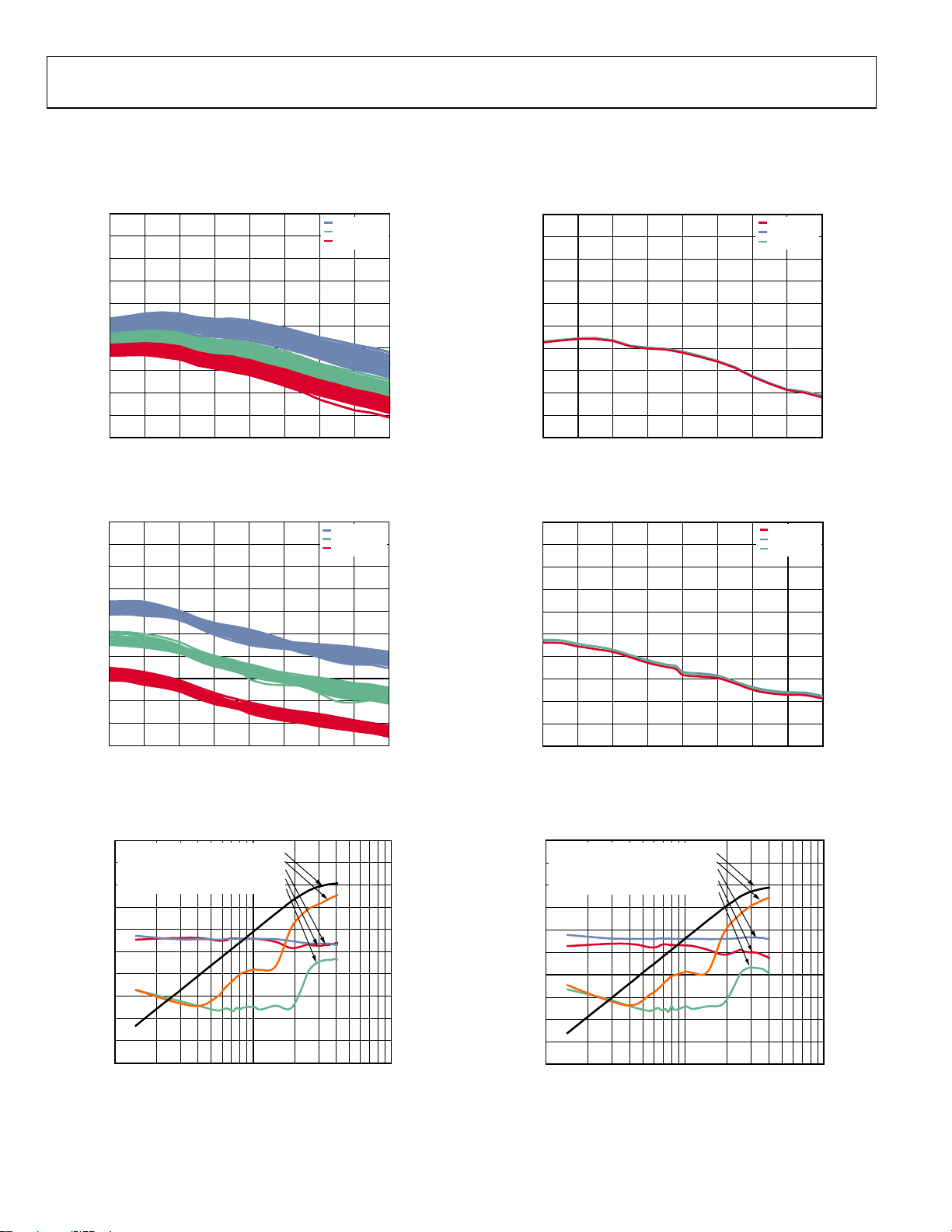

Figure 5. SSB Output 1dB Compression Point (OP1dB) vs. LO Frequency (f

) = 1 MHz; f

BB

10

9

8

7

6

5

4

3

2

1

0

800 850 900 950 1000 1050 1100

750 1150

Figure 4. Single Sideband (SSB) Output Power (P

LO Frequency (f

18

17

16

15

14

13

12

11

10

9

8

750 800 850 900 950 1000 1050 1100 1150

LO

= 38.4 MHz; f

PFD

LO FREQ UENCY (MHz)

= 153.6 MHz at +4 dBm Re:50 (1 V p-p); 130 kHz loop filter, unless otherwise noted.

REF

TA = –40°C

T

= +25°C

A

T

= +85C

A

) vs.

OUT

) and Temperature; Multiple Devices Shown

TA = –40°C

T

= +25°C

A

T

= +85°C

A

LO FRE QUENCY (MHz)

and Temperature; Multiple Devices Shown

10

9

8

7

6

5

4

3

SSB OUTPUT POWER ( dBm)

2

1

0

750 800 850 900 950 1000 1050 1100 1150

08567-104

LO FREQUENCY (MHz)

Figure 7. Single Sideband (SSB) Output Power (P

LO Frequency (f

18

17

16

15

14

13

12

11

10

1dB OUTPUT COMPRESSION (dBm)

9

8

750 800 850 900 950 1000 1050 1100 1150

08567-105

)

LO

Figure 8. SSB Output 1dB Compression Point (OP1dB) vs. LO Frequency (f

) and Power Supply; Multiple Devices Shown

LO

LO FREQUENCY (MHz)

VS = 4.75V

= 5.00V

V

S

= 5.25V

V

S

) vs.

OUT

VS = 4.75V

= 5.00V

V

S

= 5.25V

V

S

08567-107

08567-108

LO

and Power Supply

)

0

–10

–20

–30

–40

–50

–60

–70

THIRD-O RDER DIS TORTION (d Bc)

SECOND-O RDER DISTORT ION ( dBc),

–80

–90

–100

0.1 1 10

CARRIER FEEDT HROUGH ( dBm), SIDEBAND SU PPRESSIO N (dBc),

SSB OUTPUT P OWER (dBm)

THIRD-ORDER DI STORTI ON (dBc)

SIDEBAND SUPPRESSI ON (dBc)

CARRIER FEEDTHRO UGH (dBm)

SECOND-ORDER DI STORTI ON (dBc)

BASEBAND INPUT VO LTAGE (V p-p Diff erential)

20

16

12

8

4

0

–4

–8

–12

–16

–20

Figure 6. SSB Output Power, Second- and Third-Order Distortion, Carrier

Feedthrough and Sideband Suppression vs. Baseband Differential Input

Voltage (f

= 950 MHz)

OUT

SSB OUTPUT P OWER (dBm)

08567-106

CARRIER FEEDTHROUGH ( dBm), SI DEBAND SUPPRESSION ( dBc),

Figure 9. SSB Output Power, Second- and Third-Order Distortion, Carrier

Feedthrough and Sideband Suppression vs. Baseband Differential Input

Rev. 0 | Page 10 of 36

0

–10

–20

–30

–40

–50

–60

–70

THIRD- ORDER DIS TORTION (dBc)

SECOND-ORDER DI STO RTION ( dBc),

–80

–90

–100

0.1 1 10

SSB OUTP UT POW ER (dBm)

THIRD-ORDER DISTORTI ON (dBc)

SIDEBAND SUPPRESSION (dBc)

CARRIER FEEDTHROUGH (dBm)

SECOND-OR DER DISTO RTION (dBc)

BASEBAND INPUT VOLTAGE (V p-p Differential)

Voltage (f

= 1100 MHz)

OUT

20

16

12

8

4

0

–4

–8

–12

–16

–20

SSB OUTPUT POWE R (dBm)

08567-109

Data Sheet ADRF6701

–

–10

0

TA = –40°C

TA = +25°C

TA = +85°C

–10

0

TA = –40°C

= +25°C

T

A

= +85°C

T

A

–20

–30

–40

–50

–60

CARRIER FEEDTHRO UGH (dBm)

–70

–80

750 800 850 900 950 1000 1050 1100 1150

LO FREQ UENCY (MHz)

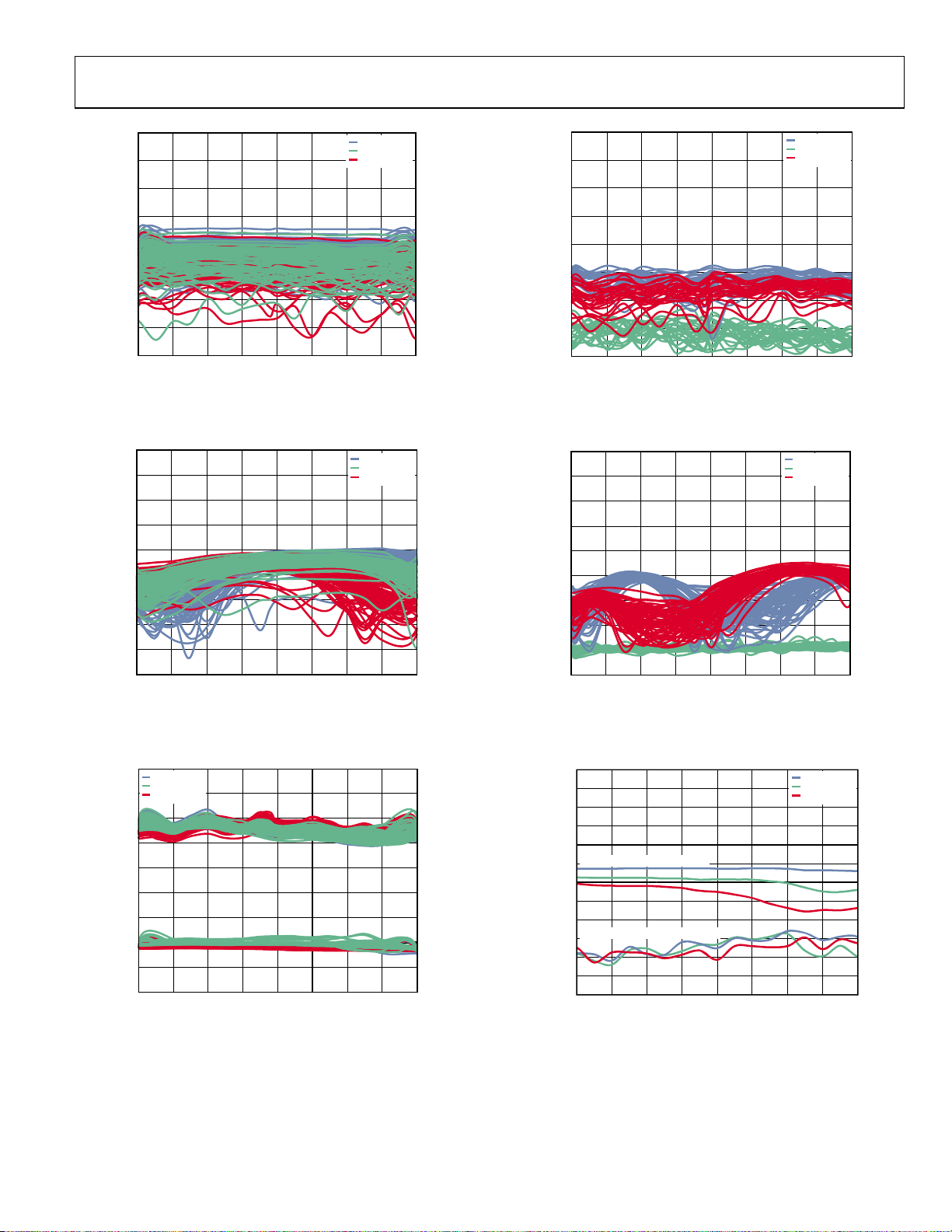

Figure 10. Carrier Feedthrough vs. LO Frequency (f

LO

Multiple Devices Shown

0

–10

–20

–30

–40

–50

–60

–70

SIDEBAND SUPPRESION (dBc)

–80

–90

750 800 850 900 950 1000 1050 1100 1150

LO FREQUENCY (MHz)

Figure 11. Sideband Suppression vs. LO Frequency (f

LO

Multiple Devices Shown

) and Temperature;

TA = –40°C

T

= +25°C

A

T

= +85°C

A

) and Temperature;

–20

–30

–40

–50

–60

CARRIER FEEDTHROUG H (dBm)

–70

–80

750 800 850 900 950 1000 1050 1100 1150

08567-110

Figure 13. Carrier Feedthrough vs. LO Frequency (f

LO FREQUENCY (MHz)

) and Temperature After

LO

08567-113

Nulling at 25°C; Multiple Devices Shown

0

–10

–20

–30

–40

–50

–60

–70

UNDESIRED SIDEBAND NULLED (d Bc)

–80

–90

750 850 950 1050 1150

08567-111

LO FREQ UENCY (MHz)

Figure 14. Sideband Suppression vs. LO Frequency (f

TA = –40°C

T

= +25°C

A

T

= +85°C

A

) and Temperature

LO

08567-114

After Nulling at 25°C; Multiple Devices Shown

100

TA = –40°C

= +25°C

T

A

90

= +85°C

T

A

80

70

60

50

40

OIP3 AND OIP2 (dBm)

30

20

10

750 800 850 900 950 1000 1050 1100 1150

LO FREQ UENCY (MHz)

Figure 12. OIP3 and OIP2 vs. LO Frequency (f

≈ −2 dBm per Tone); Multiple Devices Shown

(P

OUT

OIP2

OIP3

) and Temperature

LO

08567-112

Figure 15. Second- and Third-Order Distortion vs. LO Frequency (f

Rev. 0 | Page 11 of 36

30

–35

–40

–45

–50

THIRD-ORDER DISTORTION

–55

–60

–65

–70

SECOND- ORDER DIS TORT ION

–75

THIRD-ORDER DIS TORT ION (d Bc)

–80

SECOND-ORDER DI STORTION ( dBc)

–85

–90

750 800 850 900 950 1000 1050 1100 1150

LO FREQUENCY (MHz)

Temperature

TA =–40°C

T

= +25°C

A

T

= +85°C

A

LO

) and

08567-115

Loading...

Loading...