Precision Micropower, OVP, RRIO

+

D

FEATURES

Single-supply operation: 3.0 V to 30 V

Wide input voltage range

Rail-to-rail output swing

Low supply current: 200 μA/amplifier

Wide bandwidth: 1.2 MHz

Slew rate: 0.46 V/μs

Low offset voltage: 250 μV maximum

No phase reversal

Overvoltage protection (OVP)

25 V above/below supply rails at ±5 V

12 V above/below supply rails at ±15 V

APPLICATIONS

Industrial process control

Battery-powered instrumentation

Power supply control and protection

Telecommunications

Remote sensors

Low voltage strain gage amplifiers

DAC output amplifiers

GENERAL DESCRIPTION

The ADA4091-2 dual and ADA4091-4 quad are micropower,

single-supply, 1.2 MHz bandwidth amplifiers featuring rail-torail inputs and outputs. They are guaranteed to operate from a

+3.0 V to +30 V single supply as well as from ±1.5 V to ±15 V

dual supplies.

The ADA4091 family features a unique input stage that allows

the input voltage to exceed either supply safely without any phase

reversal or latch-up; this is called overvoltage protection, or OVP.

Applications for these amplifiers include portable telecommunications equipment, power supply control and protection,

and interface for transducers with wide output ranges. Sensors

requiring a rail-to-rail input amplifier include Hall effect, piezoelectric, and resistive transducers.

The ability to swing rail-to-rail at both the input and output enables

designers, for example, to build multistage filters in single-supply

systems and to maintain high signal-to-noise ratios (SNR).

The ADA4091 family is specified over the extended industrial

temperature range of −40°C to +125°C. The ADA4091 family is

part of the growing selection of 36 V, low power op amps from

Analog Devices, Inc., (see Table 1).

Operational Amplifier

ADA4091-2/ADA4091-4

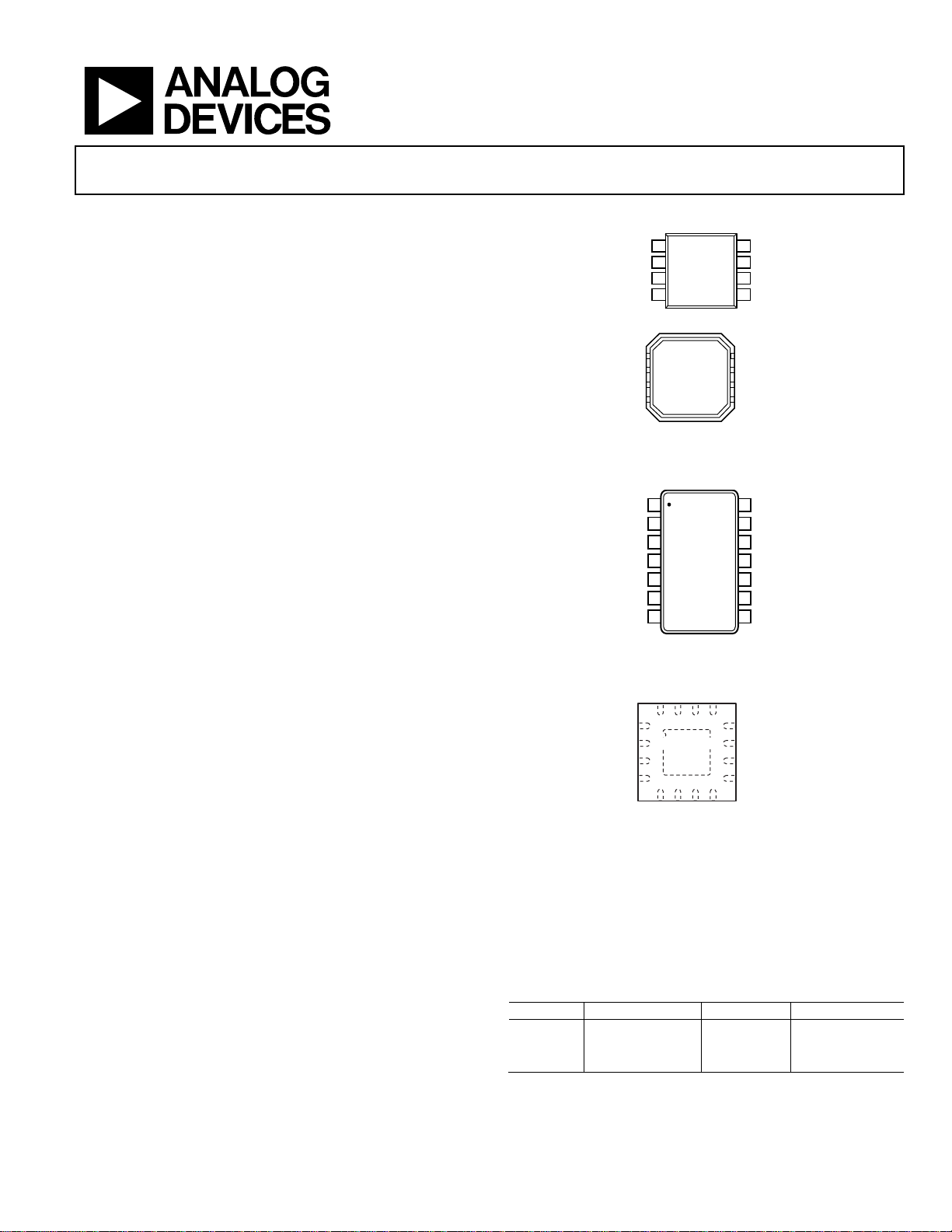

PIN CONFIGURATIONS

OUTA

1

2

–INA

ADA4091-2

3

+INA

–V

TOP VIEW

(Not to Scale)

4

Figure 1. 8-Lead, Narrow-Body SOIC (R-8)

1OUTA

2–INA

ADA4091-2

3+INA

TOP VIEW

(Not to Scale)

4–V

NOTES

1. IT I S RECOMMENDED T O CONNECT T HE

EXPOSED PAD TO V–.

Figure 2. 8-Lead LFCSP (CP-8-9)

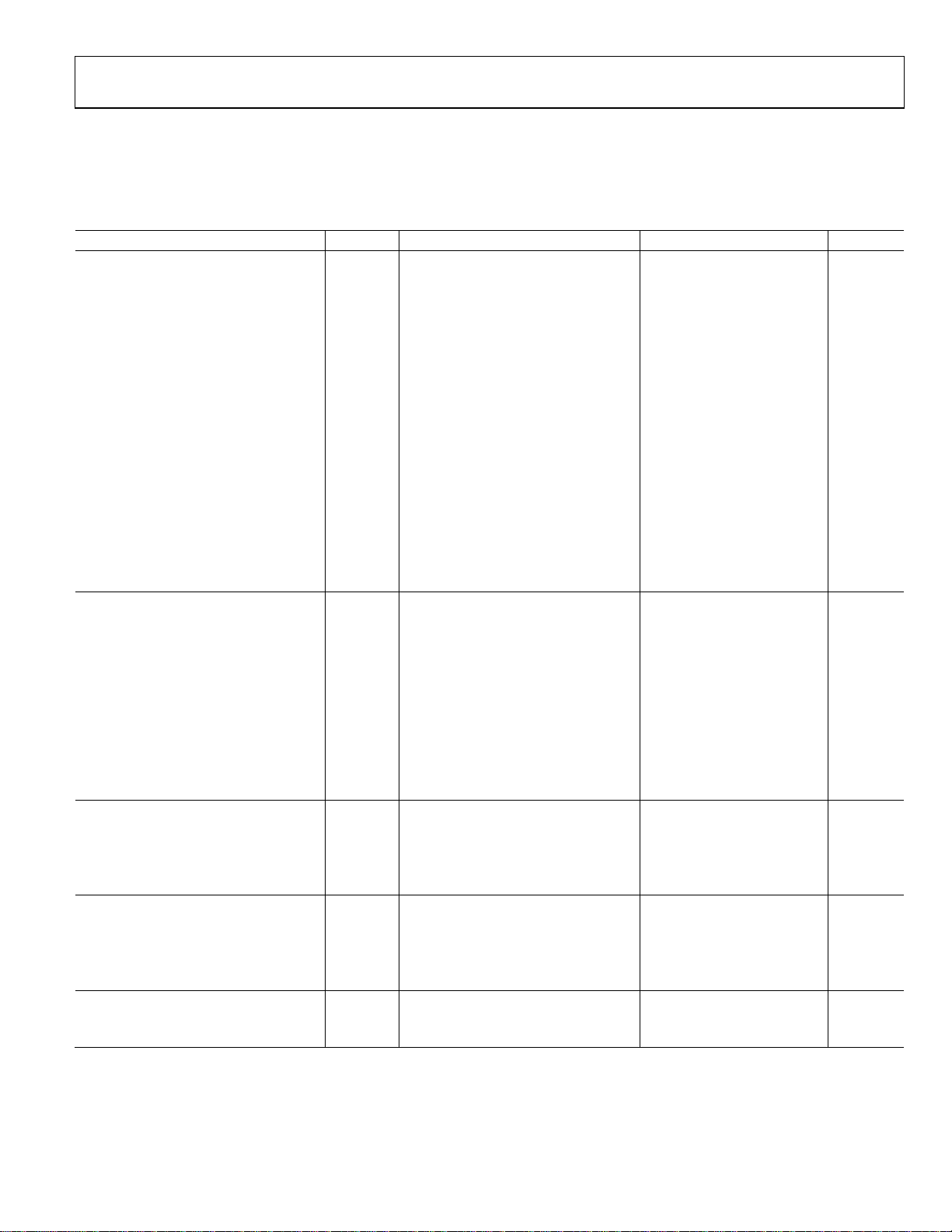

1

OUTA

2

–INA

3

+INA

ADA4091-4

4

+V

TOP VIEW

(Not to Scale)

5

+INB

6

–INB

7

OUTB

Figure 3. 14-Lead TSSOP (RU-14)

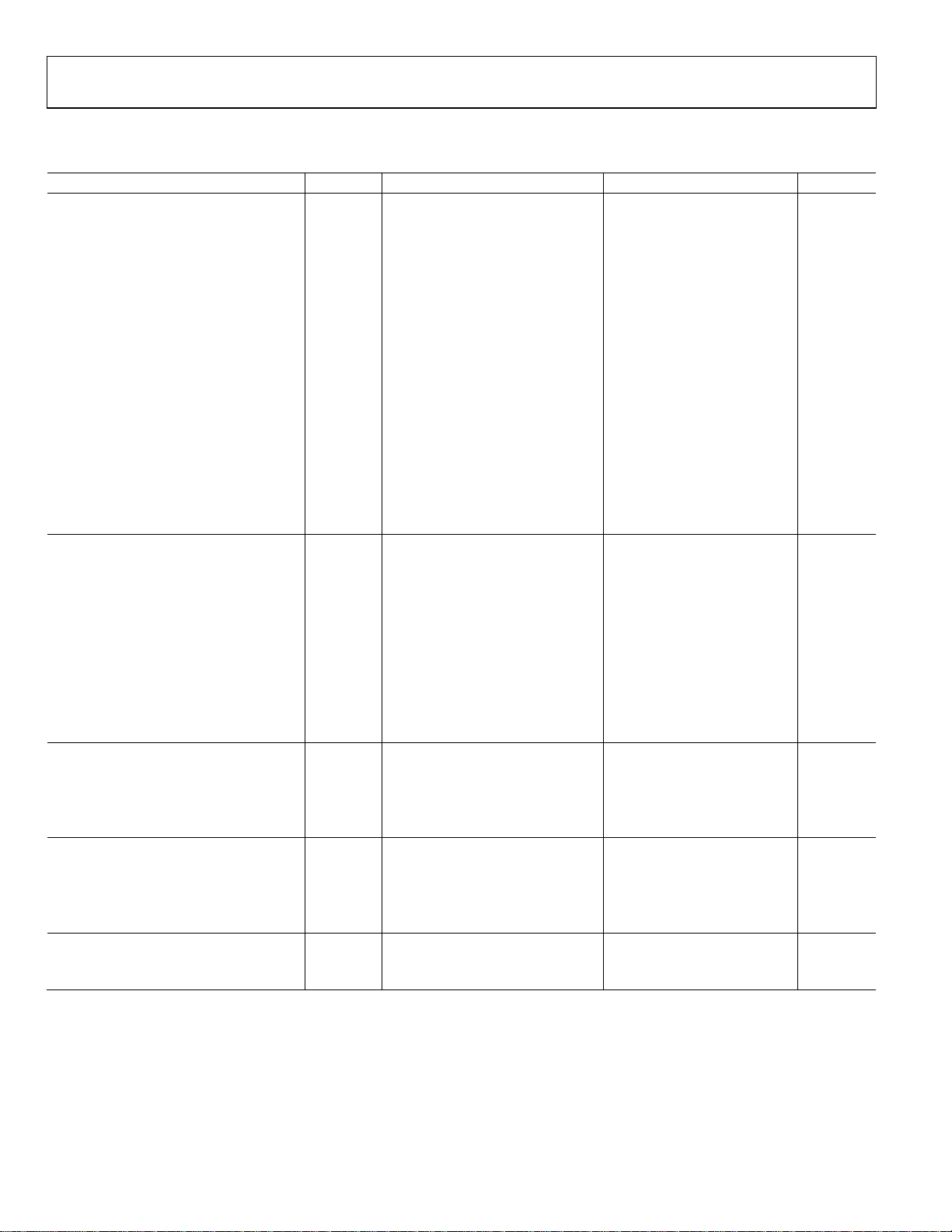

NC

OUTA

OUT

16

15

14

1

–INA

2

+INA

INB

NOTES

1. NC = NO CONNECT.

2. IT IS RECOMMENDED T O CONNECT T HE

ADA4091-4

5

–INB

TOP

VIEW

6

OUTB

3

V+

4

EXPOSED PAD TO V–.

7

OUTC

Figure 4. 16-Lead LFCSP (CP-16-17)

The ADA4091-2 is available in 8-lead, plastic SOIC and 8-lead

LFCSP packages. The ADA4091-4 is available in 14–lead TSSOP

and 16-lead LFCSP surface-mount packages.

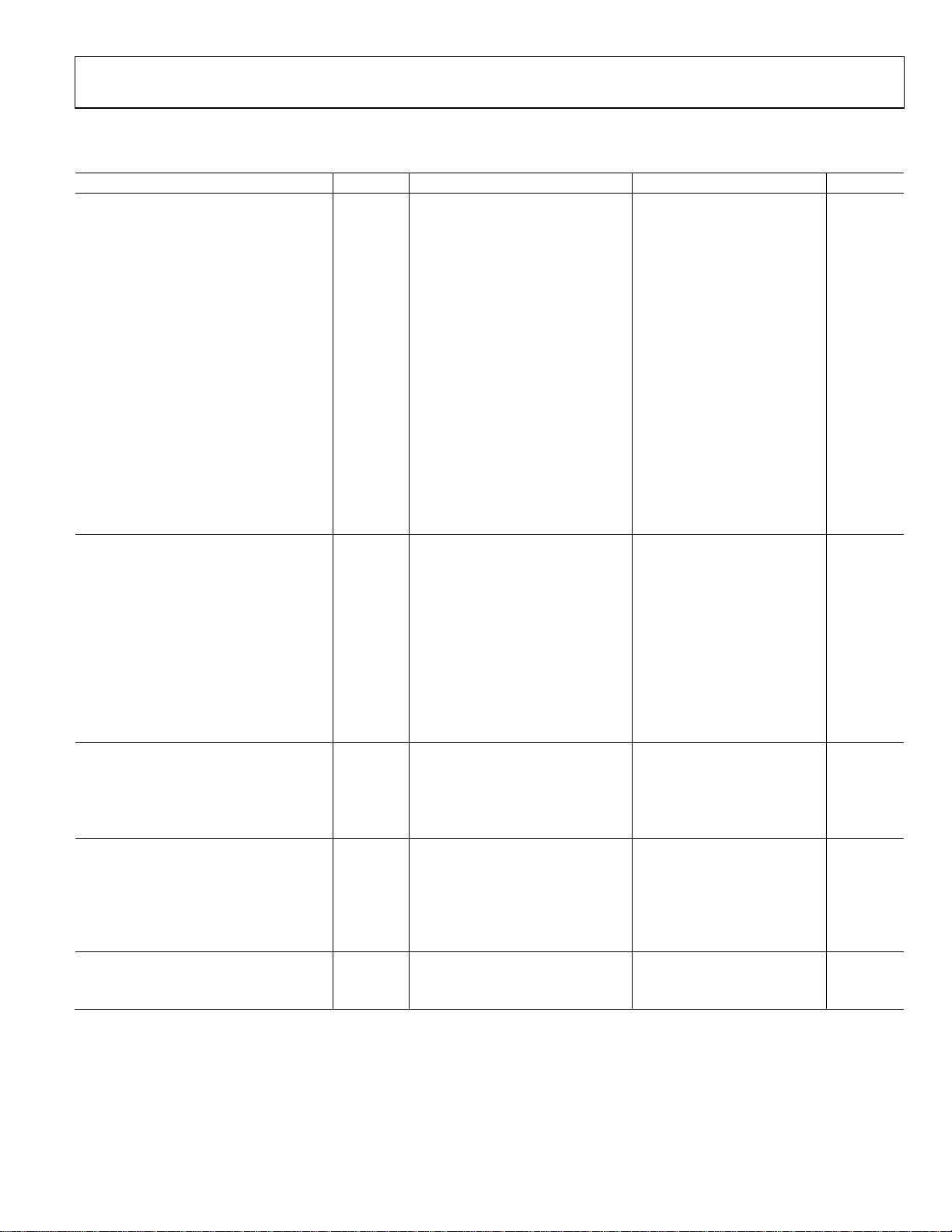

Table 1. Low Power, 36 V Operational Amplifiers

Family Rail-to-Rail I/O PJFET Low Noise

Single OP1177

Dual ADA4091-2 AD8682 OP2177

Quad ADA4091-4 AD8684 OP4177

NC

13

8

–INC

+V

8

7

OUTB

6

–INB

5

+INB

8+V

7OUTB

6–INB

5+INB

14

OUTD

13

–IND

12

+IND

11

–V

10

+INC

9

–INC

8

OUTC

12

–IND

11

+IND

10

V–

9

+INC

07671-001

07571-102

07671-101

07671-103

Rev. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008–2010 Analog Devices, Inc. All rights reserved.

ADA4091-2/ADA4091-4

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

General Description ......................................................................... 1

Pin Configurations ........................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

Electrical Specifications ............................................................... 3

Absolute Maximum Ratings ............................................................ 6

Thermal Resistance ...................................................................... 6

REVISION HISTORY

10/10—Rev. E. to Rev. F

Changes to Features Section and General Description Section . 1

Changes to Outline Dimensions ................................................... 17

5/10—Rev. D. to Rev. E

Changes to Data Sheet Title ............................................................ 1

Changes to Table 2, Input Characteristics, Offset Voltage .......... 3

Changes to Table 3, Input Characteristics, Offset Voltage .......... 4

Changes to Table 4, Input Characteristics, Offset Voltage .......... 5

4/10—Rev. C to Rev. D

Changes to Table 2, Added LFCSP to Input Characteristics ...... 3

Changes to Table 3, Added LFCSP to Input Characteristics ...... 4

Changes to Table 4, Added LFCSP to Input Characteristics ...... 5

10/09—Rev. B to Rev. C

Added 8-Lead LFCSP and 16-Lead LFCSP ..................... Universal

Change to Features Section ............................................................. 1

Updated Outline Dimensions ....................................................... 16

Changes to Ordering Guide .......................................................... 18

ESD Caution...................................................................................6

Typical Performance Characteristics ..............................................7

Theory of Operation ...................................................................... 14

Input Stage ................................................................................... 14

Output Stage ................................................................................ 14

Input Overvoltage Protection ................................................... 15

Outline Dimensions ....................................................................... 16

Ordering Guide .......................................................................... 18

7/09—Rev. A to Rev. B

Added New Part ADA4091-4 ........................................... Universal

Changes to Features Section, General Description Section, and

Figure 4 ............................................................................................... 1

Added Figure 2, Renumbered Sequentially ................................... 1

Changes to Table 1 ............................................................................. 1

Changes to Table 2 ............................................................................. 3

Changes to Table 3 ............................................................................. 4

Changes to Table 4 ............................................................................. 5

Changes to Table 5 ............................................................................. 6

Changes to Table 6 ............................................................................. 6

Updated Outline Dimensions ....................................................... 16

Changes to Ordering Guide .......................................................... 16

7/09—Rev. 0 to Rev. A

Changes to Data Sheet Title ............................................................. 1

Changes to Features .......................................................................... 1

Changes to Table 2 ............................................................................. 3

Changes to Table 3 ............................................................................. 4

Changes to Table 4 ............................................................................. 5

Added Input Current Parameter, Table 5 ....................................... 6

Added New Figure 12 and Figure 13, Renumbered

Sequentially ........................................................................................ 8

Added New Figure 24 and Figure 25 ........................................... 10

Added New Figure 36 and Figure 37 ........................................... 12

Added New Figure 43 .................................................................... 13

Changes to Input Overvoltage Protection Section ..................... 15

Changes to Ordering Guide .......................................................... 16

10/08—Revision 0: Initial Version

Rev. F | Page 2 of 20

ADA4091-2/ADA4091-4

SPECIFICATIONS

ELECTRICAL SPECIFICATIONS

VSY = ±1.5 V, VCM = 0.0 V, TA = 25°C, unless otherwise noted.

Table 2.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS −250 −40 +250 μV

ADA4091-4 LFCSP package −400 −40 +400 μV

−40°C ≤ TA ≤ +125°C −600 +600 μV

Offset Voltage Drift ∆VOS/∆T 2.5 μV/°C

Input Bias Current IB −55 −44 nA

−40°C ≤ TA ≤ +85°C −55 +55 nA

−40°C ≤ TA ≤ +125°C −275 +275 nA

Input Offset Current IOS −3 0.5 +3 nA

−40°C ≤ TA ≤ +85°C −5 +5 nA

−40°C ≤ TA ≤ +125°C −75 +75 nA

Input Voltage Range −1.5 +1.5 V

Common-Mode Rejection Ratio CMRR VCM = −1.35 V to +1.35 V 84 100 dB

−40°C ≤ TA ≤ +125°C 78 dB

Large Signal Voltage Gain AVO RL = 100 kΩ, VO = −1.2 V to +1.2 V 106 113 dB

−40°C ≤ TA ≤ +125°C 101 dB

R

−40°C ≤ TA ≤ +125°C 85 dB

OUTPUT CHARACTERISTICS

Output Voltage High VOH RL = 100 kΩ to GND 1.490 1.495 V

−40°C ≤ TA ≤ +125°C 1.490 V

R

−40°C to +125°C 1.455 V

Output Voltage Low VOL RL = 100 kΩ to GND −1.499 −1.495 V

−40°C ≤ TA ≤ +125°C −1.495 V

R

−40°C ≤ TA ≤ +125°C −1.490 V

Short-Circuit Limit ISC Source/sink ±31 mA

Open-Loop Impedance Z

POWER SUPPLY

Power Supply Rejection Ratio PSRR VSY = 2.7 V to 36 V 108 126 dB

−40°C ≤ TA ≤ +125°C 100 dB

Supply Current per Amplifier ISY IO = 0 mA 165 200 μA

−40°C ≤ TA ≤ +125°C 300 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ, CL = 30 pF 0.46 V/μs

Settling Time tS To 0.01% 22 μs

Gain Bandwidth Product GBP 1.22 MHz

Phase Margin ΦM 69 Degrees

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 0.8 μV p-p

Voltage Noise Density en f = 1 kHz 24 nV/√Hz

f = 1 MHz, AV = 1 102 Ω

OUT

= 10 kΩ, VO = −1.2 V to +1.2 V 92 94 dB

L

= 10 kΩ to GND 1.475 1.485 V

L

= 10 kΩ to GND −1.495 −1.490 V

L

Rev. F | Page 3 of 20

ADA4091-2/ADA4091-4

VSY = ±5.0 V, VCM = 0.0 V, TA = 25°C, unless otherwise noted.

Table 3.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS −250 −45 +250 μV

ADA4091-4 LFCSP package −400 −40 +400 μV

−40°C ≤ TA ≤ +125°C −600 +600 μV

Offset Voltage Drift ∆VOS/∆T 2.5 μV/°C

Input Bias Current IB −60 −50 nA

−40°C ≤ TA ≤ +85°C −80 +80 nA

−40°C ≤ TA ≤ +125°C −350 +350 nA

Input Offset Current IOS −3 0.5 +3 nA

−40°C ≤ TA ≤ +85°C −7 +7 nA

−40°C ≤ TA ≤ +125°C −100 +100 nA

Input Voltage Range −5 +5 V

Common-Mode Rejection Ratio CMRR VCM = −4.85 V to +4.85 V 95 113 dB

−40°C ≤ TA ≤ +125°C 88 dB

Large Signal Voltage Gain AVO RL = 100 kΩ, VO = ±4.7 V 113 117 dB

−40°C ≤ TA ≤ +125°C 106 dB

R

−40°C ≤ TA ≤ +125°C 90 dB

OUTPUT CHARACTERISTICS

Output Voltage High VOH RL = 100 kΩ to GND 4.980 4.990 V

−40°C ≤ TA ≤ +125°C 4.980 V

R

−40°C ≤ TA ≤ +125°C 4.900 V

Output Voltage Low VOL RL = 100 kΩ to GND −4.998 −4.990 V

−40°C ≤ TA ≤ +125°C −4.980 V

R

−40°C ≤ TA ≤ +125°C −4.975 V

Short-Circuit Limit ISC Source/sink ±20 mA

Open-Loop Impedance Z

f = 1 MHz, AV = 1 77 Ω

OUT

POWER SUPPLY

Power Supply Rejection Ratio PSRR VSY = 2.7 V to 36 V 108 126 dB

−40°C ≤ TA ≤ +125°C 100 dB

Supply Current per Amplifier ISY IO = 0 mA 180 225 μA

−40°C ≤ TA ≤ +125°C 300 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ, CL = 30 pF 0.46 V/μs

Settling Time tS To 0.01% 22 μs

Gain Bandwidth Product GBP 1.22 MHz

Phase Margin ΦM 70 Degrees

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 0.8 μV p-p

Voltage Noise Density en f = 1 kHz 24 nV/√Hz

= 10 kΩ, VO = ±4.7 V 98 100 dB

L

= 10 kΩ to GND 4.950 4.960 V

L

= 10 kΩ to GND −4.990 −4.980 V

L

Rev. F | Page 4 of 20

ADA4091-2/ADA4091-4

VSY = ±15.0 V, VCM = 0.0 V, VO = 0.0 V, TA = 25°C, unless otherwise noted.

Table 4.

Parameter Symbol Test Conditions/Comments Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS −250 −35 +250 μV

ADA4091-4 LFCSP package −400 −40 +400 μV

−40°C ≤ TA ≤ +125°C −600 +600 μV

Offset Voltage Drift ∆VOS/∆T 3.0 μV/°C

Input Bias Current IB −60 −50 nA

−40°C ≤ TA ≤ +85°C −80 +80 nA

−40°C ≤ TA ≤ +125°C −510 +510 nA

Input Offset Current IOS −3 0.5 +3 nA

−40°C ≤ TA ≤ +85°C −10 +10 nA

−40°C ≤ TA ≤ +125°C −140 +140 nA

Input Voltage Range −15 +15 V

Common-Mode Rejection Ratio CMRR VCM = −14.85 V to +14.85 V 104 121 dB

−40°C ≤ TA ≤ +125°C 95 dB

Large Signal Voltage Gain AVO RL = 100 kΩ, VO = ±14.7 V 116 119 dB

−40°C ≤ TA ≤ +125°C 108 dB

R

−40°C ≤ TA ≤ +125°C 93 dB

OUTPUT CHARACTERISTICS

Output Voltage High VOH R

−40°C ≤ TA ≤ +125°C 14.950 V

R

−40°C ≤ TA ≤ +125°C 14.800 V

Output Voltage Low VOL RL = 100 kΩ to GND −14.996 −14.990 V

−40°C ≤ TA ≤ +125°C −14.985 V

R

−40°C ≤ TA ≤ +125°C −14.940 V

Short-Circuit Limit ISC Source/sink ±20 mA

Open-Loop Impedance Z

f = 1 MHz, AV = 1 71 Ω

OUT

POWER SUPPLY

Power Supply Rejection Ratio PSRR VSY = 2.7 V to 36 V 108 126 dB

−40°C ≤ TA ≤ +125°C 100 dB

Supply Current per Amplifier ISY IO = 0 mA 200 250 μA

−40°C ≤ TA ≤ +125°C 350 μA

DYNAMIC PERFORMANCE

Slew Rate SR RL = 100 kΩ, CL = 30 pF 0.46 V/μs

Settling Time tS To 0.01% 22 μs

Gain Bandwidth Product GBP 1.27 MHz

Phase Margin ΦM 72 Degrees

Channel Separation CS f = 1 kHz 100 dB

NOISE PERFORMANCE

Voltage Noise en p-p 0.1 Hz to 10 Hz 0.8 μV p-p

Voltage Noise Density en f = 1 kHz 25 nV/√Hz

= 10 kΩ, VO = ±14.7 V 102 104 dB

L

= 100 kΩ to GND 14.975 14.980 V

L

= 10 kΩ to GND 14.900 14.920 V

L

= 10 kΩ to GND −14.975 −14.950 V

L

Rev. F | Page 5 of 20

ADA4091-2/ADA4091-4

ABSOLUTE MAXIMUM RATINGS

Table 5.

Parameter Rating

Supply Voltage 36 V

Input Voltage

Differential Input Voltage1 ±VSY

Input Current ±5 mA

Output Short-Circuit Duration to GND Indefinite

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +125°C

Junction Temperature Range −65°C to +150°C

Lead Temperature (Soldering, 60 sec) 300°C

1

Input current should be limited to ±5 mA.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Refer to the Input

Overvoltage Protection

section

THERMAL RESISTANCE

θJA is specified for the device soldered on a 4-layer JEDEC standard

PCB with zero airflow. The exposed pad is soldered to the

application board.

Table 6. Thermal Resistance

Package Type θJA θJC Unit

8-Lead SOIC (R-8) 155 45 °C/W

14-Lead TSSOP (RU-14) 112 35 °C/W

8-Lead LFCSP (CP-8-9) 75 12 °C/W

16-Lead LFCSP (CP-16-17) 55 14 °C/W

ESD CAUTION

Rev. F | Page 6 of 20

ADA4091-2/ADA4091-4

TYPICAL PERFORMANCE CHARACTERISTICS

200

180

160

140

120

100

80

60

NUMBER OF AMPLI FIERS

40

20

0

–250 –200 –150 –100 –50 0 50 100 150 200 250

VOS (µV)

Figure 5. Input Offset Voltage Distribution

300

250

ADA4091-2

–40°C T

= ±1.5V

V

SY

ADA4091-2

T

= 25°C

A

V

= ±1.5V

SY

+125°C

A

07671-034

10,000

1000

100

VDD – V

TO RAIL ( mV)

10

OUT

V

1

0.1

0.001 0. 01 0.1 1 10 100

OH

VOL – V

SS

LOAD CURRENT (mA)

ADA4091-2

V

Figure 8. Dropout Voltage vs. Load Current

100

PHASE

80

= ±1.5V

SY

07671-017

100

80

200

150

100

NUMBER OF AMPLIFIERS

50

0

–1012345678

TCVOS (µV/°C)

Figure 6. TCVOS Distribution

350

ADA4091-2

V

= ±1.5V

SY

300

250

200

150

100

(nA)

B

I

50

0

–50

–100

–150

–1.5 –1.0 –0.5 0 0.5 1.0 1.5

+85°C

–40°C

+125°C

+25°C

VCM (V)

Figure 7. Input Bias Current vs. Common-Mode Voltage

60

40

20

OPEN-LOOP GAIN (dB)

ADA4091-2

0

V

= ±1.5V

SY

R

= 1M

L

C

= 35pF

L

–20

1k 10k 100k 1M 10M

07671-035

GAIN

FREQUENCY (Hz)

60

40

20

0

–20

PHASE (Degrees)

07671-007

Figure 9. Open-Loop Gain and Phase vs. Frequency

50

AV = 100

40

30

AV = 10

20

10

AV = 1

0

CLOSED-LOOP GAIN (dB)

ADA4091-2

–10

V

= ±1.5V

SY

R

= 1M

L

C

= 35pF

L

–20

10 100 1k 10k 100k 1M 10M

07671-033

FREQUENCY (Hz)

07671-010

Figure 10. Closed-Loop Gain vs. Frequency

Rev. F | Page 7 of 20

ADA4091-2/ADA4091-4

1k

100

AV = 100

()

10

OUT

Z

0.1

AV = 10

1

10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

AV = 1

ADA4091-2

T

V

Figure 11. Output Impedance vs. Frequency

2.0

1.5

1.0

0.5

(V)

0

OUT

V

–0.5

–1.0

–1.5

–2.0

0 5 10 15 20 25 30 35 40 45 50

ADA4091-2

V

= ±1.5V

SY

T

= 25°C

A

R

= 100k

L

C

= 100pF

L

A

= +1

V

TIME (µs)

Figure 12. Large Signal Transient Response

0.06

= 25°C

A

= ±1.5V

SY

07671-013

07671-025

3.0

2.5

2.0

1.5

SWING (V)

OUT

V

1.0

ADA4091-2

0.5

V

= ±1.5V

SY

V

= 2.8V p-p

IN

R

= 100k

L

0

100 1k 10k 100k 1M

FREQUENCY (Hz)

Figure 14. Output Swing vs. Frequency

1.6

1.4

1.2

1.0

0.8

0.6

0.4

OUTPUT VOLTAGE (V)

0.2

ADA4091-2

0

= 25°C

T

A

= ±1.5V

V

SY

–0.2

0 102030405060708090

TIME (µs)

Figure 15. Positive Overload Recovery

0

07671-036

07671-051

0.04

0.02

0

(V)

OUT

–0.02

V

–0.04

–0.06

–0.08

01234567891011121314151617181920

ADA4091-2

V

= ±1.5V

SY

T

= 25°C

A

R

= 100k

L

C

= 100pF

L

A

= +1

V

TIME (µs)

Figure 13. Small Signal Transient Response

07671-028

Rev. F | Page 8 of 20

–0.2

–0.4

–0.6

–0.8

–1.0

OUTPUT VO LTAGE (V)

–1.2

–1.4

–1.6

0 102030405060 708090

TIME (µs)

ADA4091-2

T

V

Figure 16. Negative Overload Recovery

= 25°C

A

= ±1.5V

SY

07671-045

ADA4091-2/ADA4091-4

225

200

175

150

125

100

75

NUMBER OF AMPLIFIERS

50

25

0

–250 –200 –150 –100 –50 0 50 100 150 200 250

VOS (µV)

ADA4091-2

T

A

V

SY

Figure 17. Input Offset Voltage Distribution

400

350

300

250

200

150

NUMBER OF AMPLIFIERS

100

50

0

–1012345678

TCVOS (µV/°C)

ADA4091-2

–40°C T

= ±5V

V

SY

Figure 18. TCVOS Distribution

6

4

= 25°C

= ±5V

+125°C

A

07671-037

07671-038

0.06

0.04

0.02

0

(V)

OUT

–0.02

V

–0.04

–0.06

–0.08

01234567891011121314151617181920

ADA4091-2

V

= ±5V

SY

T

= 25°C

A

R

= 100k

L

C

= 100pF

L

A

= +1

V

TIME (µs)

Figure 20. Small Signal Transient Response

500

ADA4091-2

V

= ±5V

SY

400

300

200

(nA)

B

I

100

0

–100

–200

–5 –4 –3 –2 –1 0 3214

+125°C

+85°C

–40°C

VCM (V)

+25°C

Figure 21. Input Bias Current vs. Common-Mode Voltage

100

PHASE

80

07671-029

5

07671-032

100

80

2

(V)

0

OUT

V

–2

–4

–6

0 5 10 15 20 25 30 35 40 45 50

ADA4091-2

V

= ±5V

SY

T

= 25°C

A

R

= 100k

L

C

= 100pF

L

A

= +1

V

TIME (µs)

Figure 19. Large Signal Transient Response

07671-026

Rev. F | Page 9 of 20

60

40

20

OPEN-LOOP GAIN (dB)

ADA4091-2

0

V

= ±5V

SY

R

= 1M

L

C

= 35pF

L

–20

1k 10k 100k 1M 10M

GAIN

FREQUENCY (Hz)

Figure 22. Open-Loop Gain and Phase vs. Frequency

60

40

20

0

–20

PHASE (Degrees)

07671-005

ADA4091-2/ADA4091-4

1k

100

()

OUT

Z

AV = 100

10

AV = 10

1

AV = 1

0.1

10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 23. Output Impedance vs. Frequency

10

9

8

7

6

5

SWING (V)

4

OUT

V

3

2

ADA4091-2

V

= ±5V

SY

1

V

= 9.8V p-p

IN

R

= 100k

L

0

100 1k 10k 100k 1M

FREQUENCY (Hz)

Figure 24. Output Voltage Swing vs. Frequency

10,000

ADA4091-2

= 25°C

T

A

= ±5V

V

SY

07671-012

07671-015

50

AV = 100

40

30

AV = 10

20

10

AV = 1

0

CLOSED-LOOP GAIN (dB)

ADA4091-2

–10

V

= ±5V

SY

R

= 1M

L

C

= 35pF

L

–20

10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz)

Figure 26. Closed-Loop Gain vs. Frequency

6

5

4

3

2

OUTPUT VOLTAGE (V)

1

ADA4091-2

= 25°C

T

A

= ±5V

V

SY

0

0 102030405060708090

TIME (µs)

Figure 27. Positive Overload Recovery

1

07671-009

07671-046

1000

VDD – V

100

TO RAIL (mV)

10

OUT

V

1

0.1

0.001 0.01 0.1 1 10 100

LOAD CURRENT (mA)

OH

VOL – V

SS

ADA4091-2

V

SY

Figure 25. Dropout Voltage vs. Load Current

= ±5V

07671-018

Rev. F | Page 10 of 20

0

–1

–2

–3

–4

OUTPUT VO LTAGE (V )

–5

–6

0 10 20 30 40 50 60 70 80

TIME (µs)

ADA4091-2

T

A

V

SY

Figure 28. Negative Overload Recovery

= 25°C

= ±5V

07671-047

ADA4091-2/ADA4091-4

250

200

ADA4091-2

T

= 25°C

A

V

= ±15V

SY

100

PHASE

80

100

80

150

100

NUMBER OF AMPLI FIERS

50

0

–250 –200 –150 –100 –50 0 50 100 150 200 250

VOS (µV)

Figure 29. Input Offset Voltage Distribution

NUMBER OF AMPLIFIERS

350

300

250

200

150

100

50

ADA4091-2

–40°C T

V

= ±15V

SY

+125°C

A

60

40

20

OPEN-LOOP GAIN (dB)

ADA4091-2

0

V

= ±15V

SY

R

= 1M

L

C

= 35pF

L

–20

1k 10k 100k 1M 10M

07671-041

GAIN

FREQUENCY (Hz)

60

40

20

0

–20

PHASE (Degrees)

07671-006

Figure 32. Open-Loop Gain and Phase vs. Frequency

20

15

10

5

(V)

0

OUT

V

–5

–10

–15

ADA4091-2

V

= ±15V

SY

T

= 25°C

A

R

= 100k

L

C

= 100pF

L

A

= +1

V

0

–1012345678

TCVOS (µV/°C)

Figure 30. TCVOS Distribution

700

ADA4091-2

V

= ±15V

SY

600

500

400

300

200

(nA)

B

I

100

0

–100

–200

–300

–15 –10 –5 0 5 10 15

+85°C

VCM (V)

+125°C

+25°C

–40°C

Figure 31. Input Bias Current vs. Common-Mode Voltage

–20

–25 0 25 50 75 100 125 150 175 200

07671-042

TIME (µs)

07671-027

Figure 33. Large Signal Transient Response

0.06

0.04

0.02

0

(V)

OUT

–0.02

V

–0.04

–0.06

–0.08

01234567891011121314151617181920

07671-031

ADA4091-2

V

= ±15V

SY

T

= 25°C

A

R

= 100k

L

C

= 100pF

L

A

= +1

V

TIME (µs)

07671-030

Figure 34. Small Signal Transient Response

Rev. F | Page 11 of 20

ADA4091-2/ADA4091-4

35

30

25

20

SWING (V)

15

OUT

V

10

ADA4091-2

5

V

= ±15V

SY

V

= 29.8V p-p

IN

R

= 100k

L

0

100 1k 10k 100k 1M

FREQUENCY (Hz)

Figure 35. Output Voltage Swing vs. Frequency

10,000

1000

100

TO RAIL ( mV)

10

OUT

V

1

0.1

0.001 0. 01 0.1 1 10 100

Figure 36. Dropout Voltage vs. Load Current

1k

100

()

Z

AV = 100

10

OUT

AV = 10

1

AV = 1

0.1

10 100 1k 10k 100k 1M 10M

Figure 37. Output Impedance vs. Frequency

VDD – V

LOAD CURRENT (mA)

FREQUENCY (Hz)

OH

VOL – V

SS

ADA4091-2

V

= ±15V

SY

ADA4091-2

= 25°C

T

A

= ±15V

V

SY

50

AV = 100

40

30

AV = 10

20

10

AV = 1

0

CLOSED-LOOP GAIN (dB)

–10

ADA4091-2

= ±15V

V

SY

–20

R

= 1M

L

C

= 35pF

L

–30

10 100 1k 10k 100k 1M 10M

07671-016

FREQUENCY (Hz)

07671-008

Figure 38. Closed-Loop Gain vs. Frequency

16

14

12

10

8

6

4

OUTPUT VOLTAGE (V)

2

ADA4091-2

0

= 25°C

T

A

= ±15V

V

SY

–2

07671-019

0 102030405060708090

TIME (µs)

07671-048

Figure 39. Positive Overload Recovery

2

0

–2

–4

–6

–8

–10

OUTPUT VOLTAGE (V)

–12

–14

–16

07671-011

01020304050607080

TIME (µs)

ADA4091-2

= 25°C

T

A

= ±15V

V

SY

07671-049

Figure 40. Negative Overload Recovery

Rev. F | Page 12 of 20

ADA4091-2/ADA4091-4

–

0.5

0.4

0.3

0.2

0.1

0

–0.1

NOISE (µV p-p)

–0.2

–0.3

–0.4

ADA4091-2

= ±15V

V

SY

–0.5

012345678910

TIME (S econds)

Figure 41.Peak-to-Peak Voltage Noise

60

ADA4091-2

= ±15V

V

SY

–70

–80

–90

–100

–110

CHANNEL SEPARATIO N (dB)

–120

–130

10 1k 10k 100k

100

FREQUENCY (Hz)

Figure 42. Channel Separation vs. Frequency

110

100

90

80

70

60

50

CMRR (dB)

40

30

20

10

0

100 1k 10k 100k 1M 10M

VSY = ±5V, ±15V

VSY = ±1.5V

FREQUENCY (Hz)

ADA4091-2

Figure 43. CMRR vs. Frequency

07671-043

07671-044

07671-002

100

V

80

60

40

PSRR (dB)

20

0

–20

100 1k 10k 100k 1M 10M

PSRR–

FREQUENCY (Hz)

PSRR+

ADA4091-2

= ±1.5V, ±5V, ±15V

SY

Figure 44. PSRR vs. Frequency

500

ADA4091-2

= 25°C

T

A

450

400

350

300

250

(µA)

SY

I

200

150

100

50

0

0 5 10 15 20 25 30 35

VSY (V)

Figure 45. Supply Current vs. Supply Voltage

1k

100

VOLTAGE NOISE (nV/ Hz)

ADA4091-2

= 25°C

T

A

= ±5V

V

SY

10

0.01 0.1 1 10 100 1k

FREQUENCY (Hz)

Figure 46. Voltage Noise Density

07671-003

07671-004

07671-050

Rev. F | Page 13 of 20

ADA4091-2/ADA4091-4

THEORY OF OPERATION

The ADA4091 family is a single-supply, micropower amplifier

featuring rail-to-rail inputs and outputs. To achieve wide input

and output ranges, these amplifiers employ unique input and

output stages.

INPUT STAGE

In Figure 47, the input stage comprises two differential pairs, a

PNP pair (PNP input stage) and an NPN pair (NPN input

stage). These input stages do not work in parallel. Instead, only

one stage is on for any given input common-mode signal level.

The PNP stage (Transistor Q1 and Transistor Q2) is required to

ensure that the amplifier remains in the linear region when the

input voltage approaches and reaches the negative rail. Alternatively, the NPN stage (Transistor Q5 and Transistor Q6) is

needed for input voltages up to, and including, the positive rail.

For the majority of the input common-mode range, the PNP

stage is active, as shown in Figure 7, Figure 21, and Figure 31.

Notice that the bias current switches direction at approximately

1.5 V below the positive rail. At voltages below this level, the

bias current flows out of the ADA4091-x input, from the PNP

input stage. Above this voltage, however, the bias current enters

the device, due to the NPN stage. The actual mechanism within

the amplifier for switching between the input stages comprises

Transistor Q3, Transistor Q4, and Transistor Q7. As the input

common-mode voltage increases, the emitters of Q1 and Q2

follow that voltage plus a diode drop. Eventually, the emitters of

Q1 and Q2 are high enough to turn on Q3, which diverts the

tail current away from the PNP input stage, turning it off. The

tail current of the PNP pair is diverted to the Q4/Q7 current

mirror to activate the NPN input stage.

A common practice in bipolar amplifiers to protect the input

transistors from large differential voltages is to include series

resistors and differential diodes. See Figure 48 for the full input

protection circuitry. These diodes turn on whenever the differential voltage exceeds approximately 0.6 V. In this condition,

current flows between the input pins, limited only by the two

5 kΩ resistors. Evaluate each application carefully to make sure

that the increase in current does not affect performance.

OUTPUT STAGE

The output stage in the ADA4091-x device uses a PNP and

an NPN transistor, as do most output stages. However, Q32

and Q33, the output transistors, connect with their collectors

to the output pin to achieve the rail-to-rail output swing.

As the output voltage approaches either the positive or negative

rail, these transistors begin to saturate. Thus, the final limit

on output voltage is the saturation voltage of these transistors,

which is about 50 mV. The output stage has inherent gain arising

from the transistor output impedance, as well as any external load

impedance; consequently, the open-loop gain of the op amp is

dependent on the load resistance and decreases when the output

voltage is close to either rail.

+IN

Q1

Q2

Q4

Q3

–IN

Q5 Q6

Q7

Figure 47. Simplified Schematic Without Input Protection (see Figure 48)

Q9

Q10Q8

Q11

Q14Q12

Q13 Q15

Q16

Q18 Q19

Q17

Q32

Q33

OUT

07671-024

Rev. F | Page 14 of 20

ADA4091-2/ADA4091-4

INPUT OVERVOLTAGE PROTECTION

The ADA4091-x has two different ESD circuits for enhanced

protection, as shown in Figure 48.

+V

D3 D1

R1

D7

Figure 48. Complete Input Protection Network

D5

R2

D8

D6

D2

D4

–V

07671-023

One circuit is a series resistor of 5 k to the internal inputs and

diodes (D1 and D2 or D5 and D6) from the internal inputs to

the supply rails. The other protection circuit is a circuit with

two DIACs (D3 and D4 or D7 and D8) to the supply rails. A

DIAC can be considered a bidirectional Zener diode with a

transfer characteristic, as shown in Figure 49.

5

4

3

2

For a worst-case design analysis, consider two cases. The

ADA4091-x has a normal ESD structure from the internal op

amp inputs to the supply rails. In addition, it has 42 V DIACs

from the external inputs to the rails, as shown in Figure 47.

Therefore, two conditions need to be considered to determine

which case is the limiting factor.

• Condition 1. Consider, for example, that when operating

on ±15 V, the inputs can go +42 V above the negative

supply rail. With the −V pin equal to −15 V, +42 V above

this supply (the negative supply) is +27 V.

• Condition 2. There is a restriction on the input current of

5 mA through a 5 k resistor to the ESD structure to the

positive rail. In Condition 1, +27 V through the 5 k

resistor to +15 V gives a current of 2.4 mA. Thus, the

DIAC is the limiting factor. If the ADA4091-x supply

voltages are changed to ±5 V, then −5 V + 42 V = +37 V.

However, +5 V + (5 k × 5 mA) = 30 V. Thus, the normal

resistor diode structure is the limitation when running on

lower supply voltages.

Additional resistance can be added externally in series with

each input to protect against higher peak voltages; however, the

additional thermal noise of the resistors must be considered.

The flatband voltage noise of the ADA4091-x is approximately

24 nV/√Hz, and a 5 k resistor has a noise of 9 nV/√Hz. Adding

an additional 5 k resistor increases the total noise by less than

15% root sum square (rss). Therefore, maintain resistor values

below this value (5 k) when overall noise performance is critical.

Note that this represents input protection under abnormal conditions only. The correct amplifier operation input voltage range

(IVR) is specified in Tab le 2 , Tabl e 3, and Tab le 4 .

1

0

CURRENT (mA)

–1

–2

–3

–40–50 –20 0 20 30–30 10–10 40 50

VOLTAGE (V)

Figure 49. DIAC Transfer Characteristic

07671-100

Rev. F | Page 15 of 20

ADA4091-2/ADA4091-4

OUTLINE DIMENSIONS

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

85

1

1.27 (0.0500)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-AA

BSC

6.20 (0.2441)

5.80 (0.2284)

4

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

8°

0°

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

1.27 (0.0500)

0.40 (0.0157)

45°

012407-A

Figure 50. 8-Lead Standard Small Outline Package [SOIC_N]

Narrow Body

(R-8)

Dimensions shown in millimeters and (inches)

INDICATOR

0.90 MAX

0.85 NOM

SEATING

PLANE

3.25

3.00 SQ

PIN 1

12° MAX

2.75

TOP VIEW

0.70 MAX

0.65 TYP

0.30

0.23

0.18

2.95

2.75 SQ

2.55

0.05 MAX

0.01 NOM

0.20 REF

0.60 MAX

Figure 51. 8-Lead Lead Frame Chip Scale Package [LFCSP_VD]

3 mm × 3 mm Body, Very Thin, Dual Lead

(CP-8-9)

Dimensions shown in millimeters

0.60 MAX

5

EXPOSED

PAD

0.50

0.40

0.30

4

BOTTOM VIEW

FOR PROPER CONNECTION OF

THE EXPOSED PAD, REFER TO

THE PIN CONFIGURATION AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

0.50

BSC

8

1.60

1.50

1.40

1

2.23

2.13

2.03

PIN 1

INDICATOR

051909-A

Rev. F | Page 16 of 20

ADA4091-2/ADA4091-4

S

C

5.10

5.00

4.90

14

4.50

4.40

4.30

1

8

6.40

BSC

7

PIN 1

0.65 BSC

1.05

1.00

0.80

0.15

0.05

COPLANARITY

0.10

0.30

0.19

COMPLIANT TO JEDEC STANDARDS MO-153-AB-1

1.20

MAX

SEATING

PLANE

0.20

0.09

8°

0°

0.60

0.45

061908-A

0.75

Figure 52. 14-Lead Thin Shrink Small Outline Package [TSSOP]

(RU-14)

Dimensions shown in millimeters

INDI

EATING

PLANE

PIN 1

ATO R

0.80

0.75

0.70

4.10

4.00 SQ

3.90

0.65

BSC

0.45

0.40

0.35

0.05 MAX

0.02 NOM

0.20 REF

0.35

0.30

0.25

13

12

9

8

BOTTOM VIEWTOP VIEW

COPLANARITY

0.08

N

1

P

I

D

C

I

A

N

I

16

EXPOSED

1

PAD

4

5

FOR PROPER CONNECTION O F

THE EXPOSE D PAD, REFER T O

THE PIN CONF IGURATIO N AND

FUNCTION DESCRIPTIONS

SECTION OF THIS DATA SHEET.

2.70

2.60 SQ

2.50

0.25 MIN

R

O

T

COMPLIANT

TO

JEDEC STANDARDS MO-220-WGG C.

012909-B

Figure 53. 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]

4 mm × 4 mm Body, Very Very Thin Quad

(CP-16-17)

Dimensions are millimeters

Rev. F | Page 17 of 20

ADA4091-2/ADA4091-4

ORDERING GUIDE

Model1 Temperature Range Package Description Package Option Branding

ADA4091-2ARZ −40°C to +125°C 8-Lead Standard Small Outline Package (SOIC_N) R-8

ADA4091-2ARZ-R7 −40°C to +125°C 8-Lead Standard Small Outline Package (SOIC_N) R-8

ADA4091-2ARZ-RL −40°C to +125°C 8-Lead Standard Small Outline Package (SOIC_N) R-8

ADA4091-2ACPZ-R2 −40°C to +125°C 8-Lead Frame Chip Scale Package (LFCSP_VD) CP-8-9 A1Z

ADA4091-2ACPZ-R7 −40°C to +125°C 8-Lead Frame Chip Scale Package (LFCSP_VD) CP-8-9 A1Z

ADA4091-2ACPZ-RL −40°C to +125°C 8-Lead Frame Chip Scale Package (LFCSP_VD) CP-8-9 A1Z

ADA4091-4ARUZ −40°C to +125°C 14-Lead Thin Shrink Small Outline Package (TSSOP) RU-14

ADA4091-4ARUZ-RL −40°C to +125°C 14-Lead Thin Shrink Small Outline Package (TSSOP) RU-14

ADA4091-4ACPZ-R2 −40°C to +125°C 16-Lead Lead Frame Chip Scale Package (LFCSP_WQ) CP-16-17

ADA4091-4ACPZ-R7 −40°C to +125°C 16-Lead Lead Frame Chip Scale Package (LFCSP_WQ) CP-16-17

ADA4091-4ACPZ-RL −40°C to +125°C 16-Lead Lead Frame Chip Scale Package (LFCSP_WQ) CP-16-17

1

Z = RoHS Compliant Part.

Rev. F | Page 18 of 20

ADA4091-2/ADA4091-4

NOTES

Rev. F | Page 19 of 20

ADA4091-2/ADA4091-4

NOTES

©2008–2010 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D07671-0-10/10(F)

Rev. F | Page 20 of 20

Loading...

Loading...