Low Cost, Precision JFET

O

www.BDTIC.com/ADI

FEATURES

High slew rate: 20 V/μs

Fast settling time

Low offset voltage: 1.70 mV maximum

Bias current: 40 pA maximum

±4 V to

±18 V operation

Low voltage noise: 16 nV/√Hz

Unity gain stable

Common-mode voltage includes +V

Wide bandwidth: 5 MHz

APPLICATIONS

Reference gain/buffers

Level shift/driving

Active filters

Power line monitoring/control

Current/voltage sense or monitoring

Data acquisition

Sample-and-hold circuits

Integrators

GENERAL DESCRIPTION

The ADA4000-1/ADA4000-2/ADA4000-4 are JFET input

operational amplifiers featuring precision, very low bias current,

and low power. Combining high input impedance, low input

bias current, wide bandwidth, fast slew rate, and fast settling

time, the ADA4000-1/ADA4000-2/ADA4000-4 are ideal

amplifiers for driving analog-to-digital inputs and buffering

digital-to-analog converter outputs. The input common-mode

voltage includes the positive power supply, which makes the

part an excellent choice for high-side signal conditioning.

Additional applications for the ADA4000-1/ADA4000-2/

A4000-4 include electronic instruments, ATE amplification,

AD

buffering, integrator circuits, instrumentation-quality photodiode

amplification, and fast precision filters (including PLL filters).

The parts also include utility functions, such as reference

buffering, level shifting, control I/O interface, power supply

control, and monitoring functions.

S

Input Operational Amplifiers

ADA4000-1/ADA4000-2/ADA4000-4

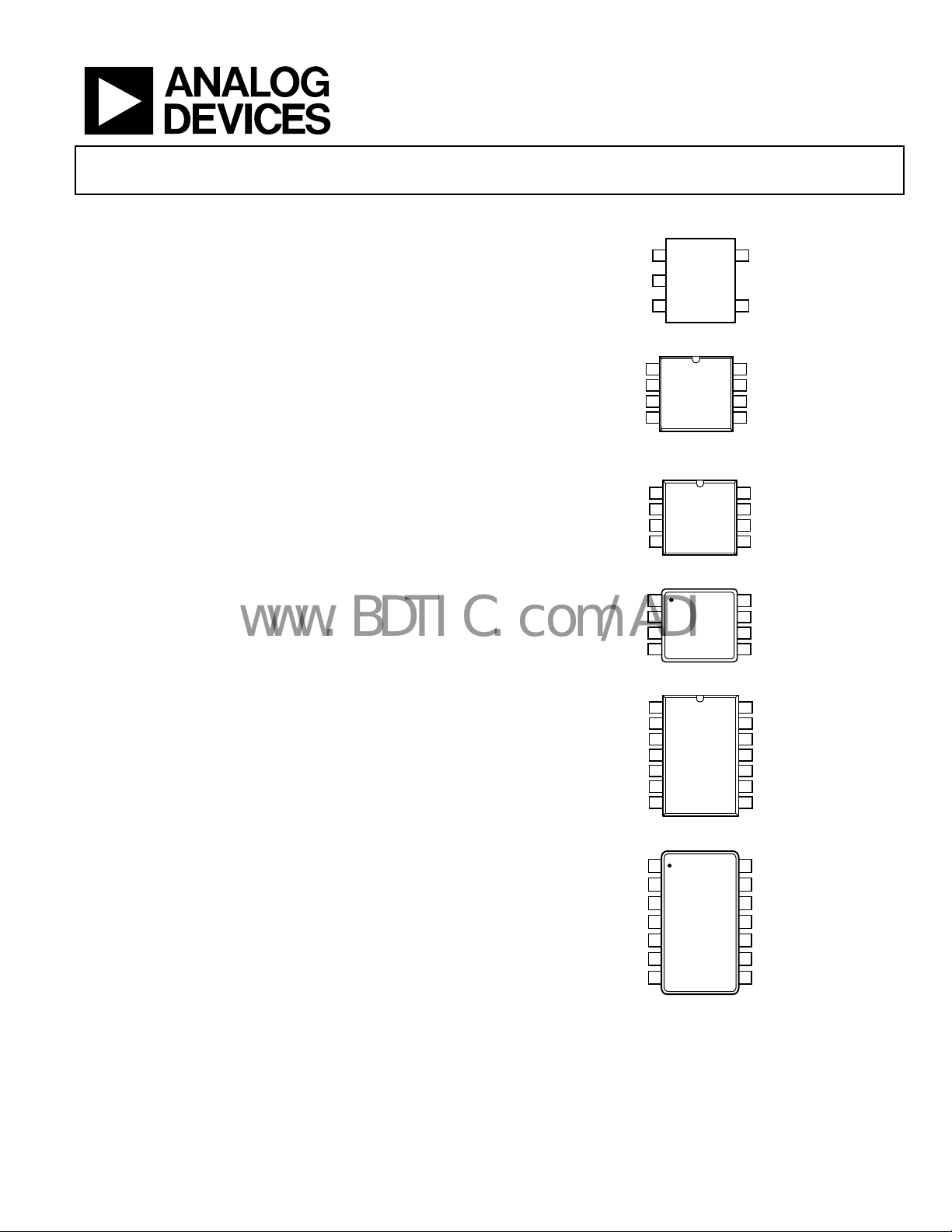

PIN CONFIGURATIONS

UT

1

ADA4000-1

TOP VIEW

V–

2

(Not to Scale)

+IN

3

Figure 1. 5-Lead TSOT (UJ-5)

NC

1

–IN

2

ADA4000-1

TOP VIEW

3

+IN

(Not to Scale)

V–

4

NC = NO CON NECT

Figure 2. 8-Lead SOIC (R-8)

1

OUT A

–IN A

2

ADA4000-2

–V

TOP VIEW

3

(Not to Scale)

4

+IN A

Figure 3. 8-Lead SOIC (R-8)

OUT A

1

2

–IN A

+IN A

–V

ADA4000-2

TOP VIEW

3

(Not to Scale)

4

Figure 4. 8-Lead MSOP (RM-8)

1

OUT A

–IN A

2

+IN A

3

ADA4000-4

4

+V

TOP VIEW

+IN B

–IN B

OUT B

(Not to Scale)

5

6

7

Figure 5. 14-Lead SOIC (R-14)

1

OUT A

2

–IN A

3

+IN A

+IN B

–IN B

OUT B

+V

ADA4000-4

TOP VIEW

4

(Not to S cale)

5

6

7

Figure 6. 14-Lead TSSOP (RU-14)

8

7

6

5

5

4

8

7

6

5

8

7

6

5

14

13

12

11

10

14

13

12

11

10

9

8

9

8

V+

–IN

NC

V+

OUT

NC

+V

OUT B

–IN B

+IN B

+V

OUT B

–IN B

+IN B

OUT D

–IN D

+IN D

–V

+IN C

–IN C

OUT C

OUT D

–IN D

+IN D

–V

+IN C

–IN C

OUT C

05791-001

05791-002

05791-027

05791-028

05791-029

05791-030

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

General Description ......................................................................... 1

Pin Configurations ........................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Electrical Characteristics ............................................................. 3

Absolute Maximum Ratings............................................................ 5

Thermal Resistance ...................................................................... 5

REVISION HISTORY

5/07—Revision 0: Initial Version

Power Sequencing.........................................................................5

ESD Caution...................................................................................5

Typical Performance Characteristics..............................................6

Applications..................................................................................... 10

Output Phase Reversal and Input Noise ................................. 10

Capacitive Load Drive ............................................................... 10

Settling Time............................................................................... 11

Outline Dimensions....................................................................... 12

Ordering Guide .......................................................................... 14

Rev. 0 | Page 2 of 16

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

VS = ±15.0 V, VCM = VS/2 V, TA = 25°C, unless otherwise specified.

Table 1.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS 0.2 1.70 mV

−40°C ≤ TA ≤ +125°C 3.0 mV

Input Bias Current IB 5 40 pA

−40°C ≤ TA ≤ +85°C 170 pA

−40°C ≤ TA ≤ +125°C 4.5 nA

Input Offset Current IOS 2 40 pA

−40°C ≤ TA ≤ +85°C 80 pA

−40°C ≤ TA ≤ +125°C 500 pA

Input Voltage Range IVR −11 +15 V

Common-Mode Rejection Ratio CMRR −11 V ≤ VCM ≤ +15 V 80 100 dB

−40°C ≤ TA ≤ +125°C 100 dB

Open-Loop Gain AVO R

Offset Voltage Drift ΔVOS/ΔT −40°C ≤ TA ≤ +125°C 2 μV/°C

OUTPUT CHARACTERISTICS

Output Voltage High VOH R

−40°C ≤ TA ≤ +125°C 13.40 V

Output Voltage Low VOL R

−40°C ≤ TA ≤ +125°C −12.80 V

Short-Circuit Current ISC ±28 mA

POWER SUPPLY

Power Supply Rejection Ratio PSRR VS = ±4.0 V to ±18.0 V 82 92 dB

Supply Current/Amplifier ISY 1.35 1.65 mA

−40°C ≤ TA ≤ +125°C 1.80 mA

DYNAMIC PERFORMANCE

Slew Rate SR VI = 10 V, RL = 2 kΩ 20 V/μs

Gain Bandwidth Product GBP 5 MHz

Phase Margin ΦM 60 Degrees

NOISE PERFORMANCE

Voltage Noise e

Voltage Noise Density en f = 1 kHz 16 nV/√Hz

Current Noise Density in f = 1 kHz 0.01 pA/√Hz

INPUT IMPEDANCE

Differential Mode (R||C)

Common Mode (R||C)

0.1 Hz to 10 Hz 1 μV p-p

n p-p

IN-DIFF

INCM

= 2 kΩ, VO = ±10 V 100 110 dB

L

= 2 kΩ to ground 13.60 13.90 V

L

= 2 kΩ to ground −13.4 −13.0 V

L

10||4 GΩ||pF

103||5.5 GΩ||pF

Rev. 0 | Page 3 of 16

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

VS = ±5 V, VCM = VS/2 V, TA = 25°C, unless otherwise specified.

Table 2.

Parameter Symbol Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Offset Voltage VOS 0.20 1.70 mV

−40°C ≤ TA ≤ +125°C 3.0 mV

Input Bias Current IB 5 40 pA

−40°C ≤ TA ≤ +85°C 170 pA

−40°C ≤ TA ≤ +125°C 3 nA

Input Offset Current IOS 2 40 pA

−40°C ≤ TA ≤ +85°C 80 pA

−40°C ≤ TA ≤ +125°C 500 pA

Input Voltage Range IVR −1.5 +5.0 V

Common-Mode Rejection Ratio CMRR −1.5 V ≤ VCM ≤ +3.5 V 72 80 dB

−40°C ≤ TA ≤ +125°C 80 dB

Open-Loop Gain AVO R

Offset Voltage Drift ΔVOS/ΔT −40°C ≤ TA ≤ +125°C 2 μV/°C

OUTPUT CHARACTERISTICS

Output Voltage High VOH R

−40°C ≤ TA ≤ +125°C 3.80 V

Output Voltage Low VOL R

−40°C ≤ TA ≤ +125°C −3.00 V

Short-Circuit Current ISC ±28 mA

POWER SUPPLY

Supply Current/Amplifier ISY 1.25 1.65 mA

−40°C ≤ TA ≤ +125°C 1.80 mA

DYNAMIC PERFORMANCE

Slew Rate SR VI = 10 V, RL = 2 kΩ 20 V/μs

Gain Bandwidth Product GBP 5 MHz

Phase Margin ΦM 55 Degrees

NOISE PERFORMANCE

Voltage Noise e

Voltage Noise Density en f = 1 kHz 16

Current Noise Density in f = 1 kHz 0.01

INPUT IMPEDANCE

Differential Mode (R||C)

Common Mode (R||C)

0.1 Hz to 10 Hz 1 μV p-p

n p-p

IN-DIFF

INCM

= 2 kΩ, VO = ±2.5 V 106 114 dB

L

= 2 kΩ to ground 4.0 4.20 V

L

= 2 kΩ to ground −3.45 −3.20 V

L

nV/√Hz

pA/√Hz

10||4 GΩ||pF

103||5.5 GΩ||pF

Rev. 0 | Page 4 of 16

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage ±18 V

Input Voltage ±V supply

Differential Input Voltage ±V supply

Output Short-Circuit Duration to GND Indefinite

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +125°C

Junction Temperature Range −65°C to +150°C

Lead Temperature (Soldering, 10 sec) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, that is, a device

soldered in a circuit board for surface-mount packages.

Table 4. Thermal Resistance

Package Type θJA θJC Unit

5-Lead TSOT (UJ-5) 172.92 61.76 °C/W

8-Lead SOIC (R-8) 112.38 61.6 °C/W

8-Lead MSOP (RM-8) 141.9 43.7 °C/W

14-Lead SOIC (R-14) 88.2 56.3 °C/W

14-Lead TSSOP (RU-14) 114 23.3 °C/W

POWER SEQUENCING

The op amp supply voltages must be established simultaneously

with, or before, any input signals are applied. If this is not

possible, the input current must be limited to 10 mA.

ESD CAUTION

Rev. 0 | Page 5 of 16

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

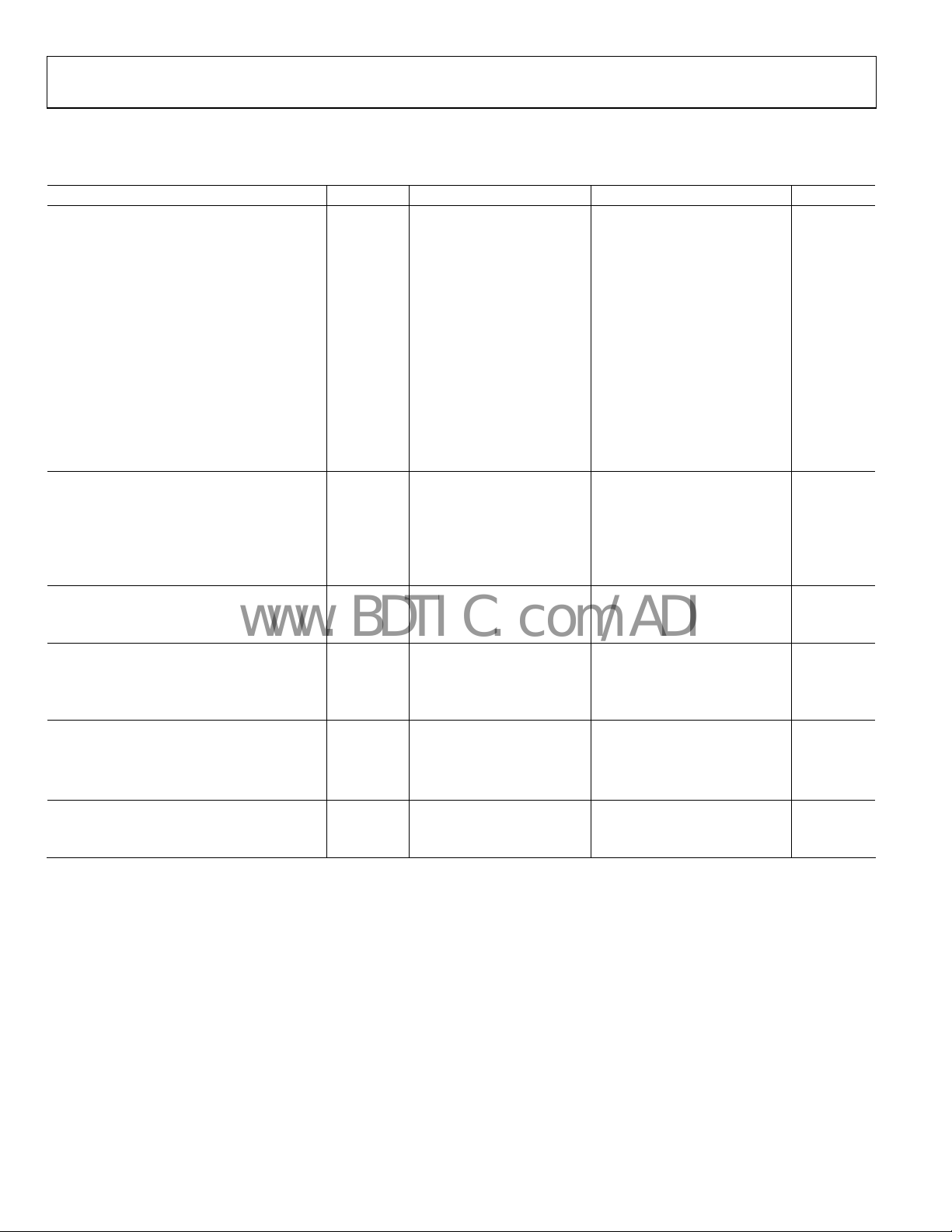

TYPICAL PERFORMANCE CHARACTERISTICS

50

VS = ±15V

45

T

= 25°C

A

V

= 0V

CM

40

35

30

25

20

15

NUMBER OF AMPLIF IERS

10

5

0

–2.0 –1.5 –1.0 –0.5 0 0.5 1.0 1.5 2. 0

Figure 7. Input Offset Voltage Distribution, V

OFFSET VOLTAGE (mV)

= ±15 V

S

05791-003

50

VS = ±5V

45

T

= 25°C

A

V

= 0V

CM

40

35

30

25

20

15

NUMBER OF AMPLI FIERS

10

5

0

–2.0 –1.5 –1.0 –0.5 0 0.5 1.0 1.5 2.0

Figure 10. Input Offset Voltage Distribution, V

OFFSET VOLTAGE (mV)

= ±5 V

S

05791-018

18

16

14

12

10

8

6

NUMBER OF AMPLIFIERS

4

2

0

024 68101214161820

Figure 8. Offset Voltage Drift Distribution, V

80

60

40

GAIN (dB)

20

0

TCVOS (µV/°C)

60°

= ±15 V

S

VS = ±15V

T

A

C

L

VS = ±15V

= 25°C

= 35pF

180

135

90

45

0

14

12

10

8

6

4

NUMBER OF AMPLIFIERS

2

0

05791-004

024 68101214161820

TCVOS (µV/°C)

Figure 11. Offset Voltage Drift Distribution, V

80

60

40

GAIN (dB)

20

PHASE MARGIN (Degrees)

0

55°

VS = ±5V

= ±5 V

S

VS = ±5V

= 25°C

T

A

= 35pF

C

L

180

135

90

45

0

05791-019

PHASE MARGIN (Deg rees)

–20

1k 100M

10k 100k 1M 10M

FREQUENCY (Hz)

Figure 9. Open-Loop Gain and Phase Margin vs. Frequency, V

–45

= ±15 V

S

05791-010

Rev. 0 | Page 6 of 16

–20

1k 100M

10k 100k 1M 10M

FREQUENCY (Hz)

Figure 12. Open-Loop Gain and Phase Margin vs. Temperature, V

–45

= ±5 V

S

05791-020

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

120

100

80

CMRR (dB)

60

VS = ±15V

T

= 25°C

A

100

VS = ±5V

T

= 25°C

A

80

60

CMRR (dB)

40

20

100 10M

1k 10k 100k 1M

FREQUENCY (Hz)

Figure 13. Common-Mode Rejection Ratio vs. Frequency, V

15

10

5

0

VOLTAGE (V)

–5

–10

–15

TIME (1µs/DIV)

Figure 14. Large Signal Transient Response, V

VS = ±15V

A

V

R

L

T

A

= ±15 V

S

VS = ±15V

C

= 300pF

L

A

= +1

V

T

= 25°C

A

= ±15 V

S

= +1

= 2kΩ

= 25°C

40

20

1k 10M

05791-013

Figure 16. Common-Mode Rejection Ratio vs. Frequency, V

4

3

2

1

0

VOLTAGE (V)

–1

–2

–3

05791-015

–4

Figure 17. Large Signal Transient Response, V

10k 100k 1M

FREQUENCY (Hz)

VS = ±5V

= –1

A

V

= 2kΩ

R

L

T

= 25°C

A

TIME (1µs/DIV)

= ±5 V

S

VS = ±5V

C

= 300pF

L

A

= +1

V

T

= 25°C

A

= ±5 V

S

05791-021

05791-023

VOLTAGE (20mV/DIV)

TIME (2µs/DIV)

Figure 15. Small Signal Transient Response, V

= ±15 V

S

05791-016

Rev. 0 | Page 7 of 16

VOLTAGE (20mV/DIV)

TIME (2µs/DIV)

Figure 18. Small Signal Transient Response, V

= ±5 V

S

05791-024

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

3.5

3.0

TA = 25°C

1.40

1.35

TA = 25°C

NO LOA D

2.5

2.0

INPUT BIAS CURRENT (pA)

1.5

1.0

±5 ±15

±6 ±7 ±8 ±9 ±10 ±11 ±12 ±13 ±14

SUPPLY VOLTAGE (V)

Figure 19. Input Bias Current vs. Supply Voltage

10000

1000

100

10

INPUT BIAS CURRENT (pA)

1

0.1

–40

VS = ±15V

VS = ±5V

–25 –10 5 20 35 50 65 80 95 110 125

TEMPERATURE ( °C)

Figure 20. Input Bias Current vs. Temperature

1.30

1.25

1.20

SUPPLY CURRENT (mA)

1.15

1.10

±4 ±5 ±6 ±7 ±8 ±9 ±10 ±11 ±12 ±13 ±14 ±15

05791-006

SUPPLY VOLTAGE (V)

05791-008

Figure 22. Supply Current vs. Supply Voltage

16

VS = ±15V

14

12

10

8

6

OUTPUT VOLTAGE (V)

4

2

0

0 25.0

2.5 5.0 7.5 10.0 12.5 15.0 17.5 20.0 22.5

05791-005

LOAD CURRENT (mA)

|VOL|

V

OH

|VOL|

V

OH

VS = ±5V

05791-009

Figure 23. Output Voltage vs. Load Current

1.44

1.40

1.36

1.32

1.28

SUPPLY CURRENT (mA)

1.24

1.20

–25 –10 5 20 35 50 65 80 95 110

–40 125

TEMPERATURE (° C)

VS = ±15V

VS = ±5V

Figure 21. Supply Current vs. Temperature

05791-012

Rev. 0 | Page 8 of 16

120

100

80

60

40

PSRR (dB)

20

0

–20

100 10M

PSRR+

1k 10k 100k 1M

FREQUENCY (Hz)

PSRR–

VS = ±5V, ±15V

Figure 24. PSRR vs. Frequency

05791-014

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

100

VS = ±5V, ±15V

T

= 25°C

A

0.6

VS = ±5V, ±15V

0.4

0.2

10

VOLTAGE NOISE DENSITY (nV/√Hz)

1

1 10k

10 100 1k

FREQUENCY (Hz)

Figure 25. Voltage Noise Density vs. Frequency

120

100

80

(Ω)

60

OUT

Z

40

Av = +100

20

0

1k 100M

Figure 26. Output Imped

60

VIN = 100mV p-p

= ±5V, ±15V

V

S

50

= 0

R

L

= +1

A

V

40

30

OVERSHOOT (%)

20

Av = +10 Av = +1

10k 100k 1M 10M

FREQUENCY (Hz)

ance vs. Frequency

+OVERSHOOT

–OVERSHOOT

VS = ±15V

T

= 25°C

A

0

V p-p (µV)

–0.2

–0.4

–0.6

–4 –3 –2 –1 0 1 2 3 4

–5

05791-026

TIME (S econds)

5

05791-025

Figure 28. 0.1 Hz to 10 Hz Input Voltage Noise

50

AV = +100

40

30

AV = +10

20

10

AV = +1

0

CLOSED-LOOP GAIN (dB)

–10

–20

–30

100 1k 100M

05791-017

10k 100k 1M 10M

FREQUENCY (Hz)

VS = ±5V, ±15V

05791-011

Figure 29. Closed-Loop Gain vs. Frequency

10

0

0600400200

Figure 27. Overshoot v

LOAD CAPACITANCE (pF)

s. Load Capacitance

800 1000

05791-022

Rev. 0 | Page 9 of 16

ADA4000-1/ADA4000-2/ADA4000-4

V

www.BDTIC.com/ADI

APPLICATIONS

OUTPUT PHASE REVERSAL AND INPUT NOISE

Phase reversal is a change of polarity in the transfer function of

the amplifier. This can occur when the voltage applied at the

input of the amplifier exceeds the maximum common-mode

voltage. Phase reversal happens when the part is configured in

the gain of 1.

Most JFET amplifiers invert the phase of the input signal if the

put exceeds the common-mode input. Phase reversal is a

in

temporary behavior of the ADA4000-x family. Each part

returns to normal operation by bringing back the commonmode voltage. The cause of this effect is saturation of the input

stage, which leads to the forward-biasing of a drain-gate diode.

In noninverting applications, a simple fix for this is to insert a

series resistor between the input signal and the noninverting

terminal of the amplifier. The value of the resistor depends on

the application, because adding a resistor adds to the total input

noise of the amplifier. The total noise density of the circuit is

nTOTAL

2

2

()

nn

kTRRiee 4

++=

SS

The advantage of this compensation method is that the swing at

the output is not reduced because R

is out of the feedback

S

network, and the gain accuracy does not change. Depending on

the capacitive loading of the circuit, the values of R

and CS

S

change, and the optimum value can be determined empirically.

In

Figure 31, the oscilloscope image shows the output of the

A4000-x family in response to a 400 mV pulse. The circuit is

AD

configured in the unity gain configuration with 500 pF in

parallel with 10 kΩ of load capacitive.

INPUT SIGNAL

VOLTAGE (200mV/DIV)

OUTPUT SIGNAL

where:

is the input voltage noise density of the part.

e

n

i

is the input current noise density of the part.

n

is the source resistance at the noninverting terminal.

R

S

k is Boltzmann’s constant (1.38 × 10

−23

J/K).

T is the ambient temperature in Kelvin (T = 273 + °C).

In general, it is good practice to limit the input current to less

t

han 5 mA to avoid driving a great deal of current into the

amplifier inputs.

CAPACITIVE LOAD DRIVE

The ADA4000-1/ADA4000-2/ADA4000-4 are stable at all gains

in both inverting and noninverting configurations. The parts

are capable of driving up to 1000 pF of capacitive loads without

oscillations in unity gain configurations.

However, as with most amplifiers, driving larger capacitive loads

in a u

nity gain configuration can cause excessive overshoot and

ringing. A simple solution to this problem is to use a snubber

network (see

400mV p-p

Figure 30).

3

V1

ADA4000-1

2

0

+15

V+

V–

–15V

SNUBBER NETWORK

U1

1

R

S

C

S

C

L

500pF

R

L

10kΩ

TIME (1µs/DIV)

Figure 31. Capacitive Load Drive Without Snubber Network

05791-032

When the snubber circuit is used, the overshoot is reduced from

30% to 6% with the same load capacitance. Ringing is virtually

eliminated, as shown in Figure 32. In this circuit, R

C

is 10 nF.

S

INPUT SIGNAL

VOLTAGE (200mV/DIV)

Figure 32. Capacitive Load with Snubber Network

OUTPUT SI GNAL

TIME (1µs/DIV)

is 41 Ω and

S

05791-033

0

Figure 30. Snubber Network Configuration

05791-031

Rev. 0 | Page 10 of 16

ADA4000-1/ADA4000-2/ADA4000-4

V

p

www.BDTIC.com/ADI

SETTLING TIME

Settling time is the amount of time it takes the amplifier output

to reach and remain within a percentage of its final value. This

is an important parameter in data acquisition systems. Because

most bipolar DAC converters have current output, an external

op amp is required to convert the current to voltage. Therefore,

the amplifier settling time plays a role in the total settling time

of the output signal. A good approximation for the total settling

time is

22

()(

+=

The ADA4000-1/ADA4000-2/ADA4000-4 settle to within 0.1%

o

f their final value in less than 1.2 μs. The settling time has been

tested by using the configuration circuit in

10V p-

AMPtDACtTotalt

SSS

V1

)

Figure 34.

3

0

ADA4000-1

10kΩ

2

+15

V+

V–

–15V

10kΩ

1

Figure 34. Settling Time Test Circuit

10kΩ

10kΩ

The input signal is a 10 V pulse and the output is the error

gnal for the settling time shown in

si

200ns/DIV

Figure 33. Settling Time Measurement Using the False Summing Node Method

+15V

8

V+

AD828

V–

4

–15V

1kΩ

20kΩ

Figure 33.

V

OUT

05791-034

5V/DIV

200mV/DIV

05791-035

Rev. 0 | Page 11 of 16

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

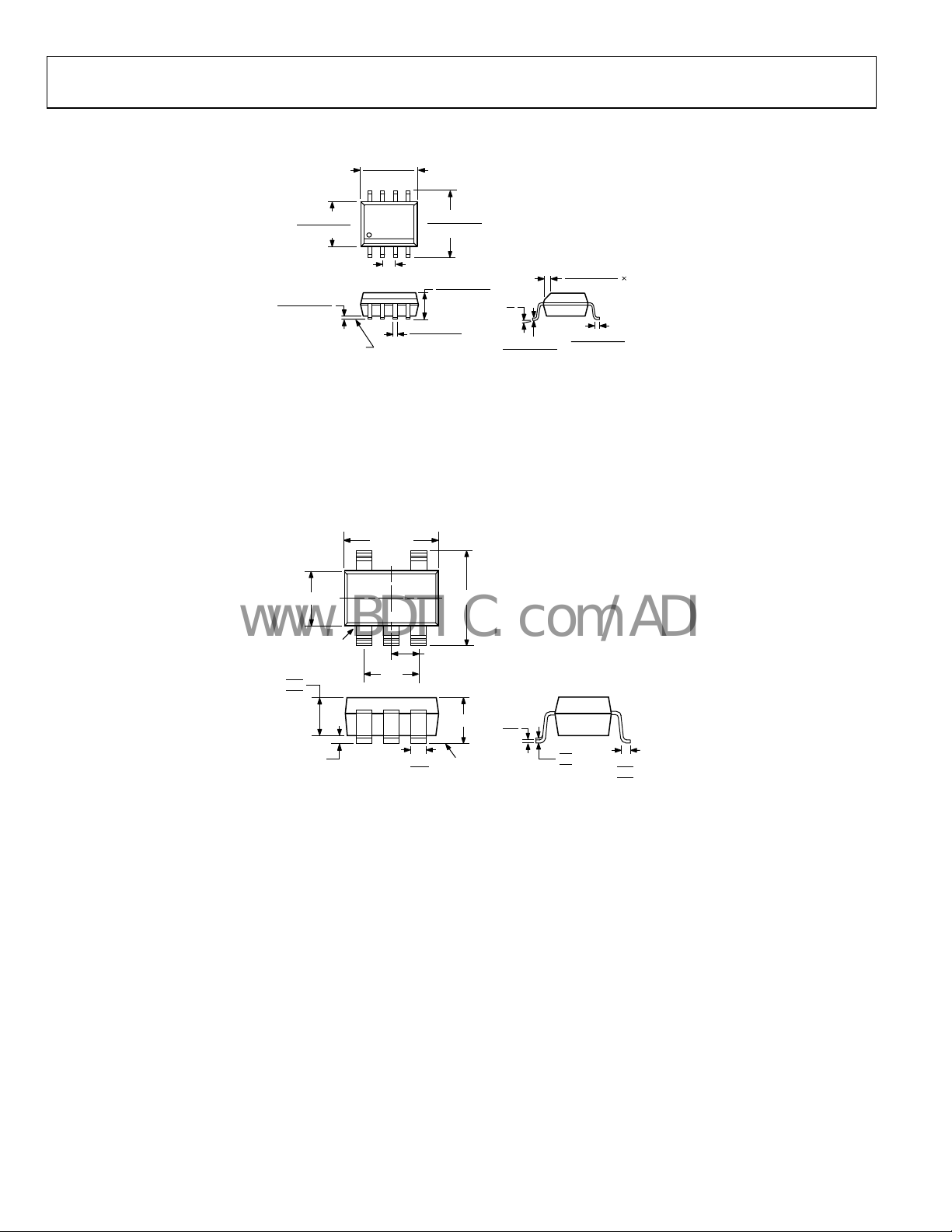

OUTLINE DIMENSIONS

5.00 (0.1968)

4.80 (0.1890)

4.00 (0.1574)

3.80 (0.1497)

0.25 (0.0098)

0.10 (0.0040)

COPLANARITY

0.10

CONTROLL ING DIMENSI ONS ARE IN MILLIM ETERS; INCH DI MENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRI ATE FOR USE IN DES IGN.

85

1

1.27 (0.0500)

SEATING

PLANE

COMPLIANT TO JEDEC STANDARDS MS-012-A A

BSC

6.20 (0.2441)

5.80 (0.2284)

4

1.75 (0.0688)

1.35 (0.0532)

0.51 (0.0201)

0.31 (0.0122)

8°

0°

0.25 (0.0098)

0.17 (0.0067)

0.50 (0.0196)

0.25 (0.0099)

1.27 (0.0500)

0.40 (0.0157)

45°

012407-A

Figure 35. 8-Lead Standard Small Outline Package [SOIC_N]

row Body

Nar

(R-8)

Dimensions shown in millimeters and (inches)

2.90 BSC

54

1.60 BSC

123

PIN 1

*

0.90

0.87

0.84

0.10 MAX

*

COMPLIANT TO JEDEC STANDARDS MO-193-AB WITH

THE EXCEPTION OF PACKAGE HEIGHT AND THICKNESS.

1.90

BSC

Figure 36. 5-Lead Thin Small Outline Transistor Package [TSOT]

Dim

2.80 BSC

0.95 BSC

*

0.50

0.30

1.00 MAX

SEATING

PLANE

0.20

0.08

(UJ-5)

ensions shown in millimeters

8°

4°

0°

0.60

0.45

0.30

Rev. 0 | Page 12 of 16

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

0.95

0.85

0.75

0.15

0.00

COPLANARITY

3.20

3.00

2.80

8

5

4

SEATING

PLANE

5.15

4.90

4.65

1.10 MAX

0.23

0.08

3.20

3.00

1

2.80

PIN 1

0.65 BSC

0.38

0.22

0.10

COMPLIANT TO JEDEC STANDARDS MO-187-AA

8°

0°

0.80

0.60

0.40

Figure 37. 8-Lead Mini Small Outline Package [MSOP]

(RM-8)

Dim

ensions shown in millimeters

5.10

5.00

4.90

14

4.50

4.40

4.30

PIN 1

1.05

1.00

0.80

0.65

BSC

0.15

0.05

COMPLIANT TO JEDEC STANDARDS MO-153-AB-1

Figure 38. 14-Lead Standard Small Outline Package [TSSOP]

8

6.40

BSC

71

0.20

1.20

0.09

MAX

0.30

SEATING

0.19

PLANE

COPLANARITY

0.10

(R

U-14)

Dimensions shown in millimeters

8°

0°

0.75

0.60

0.45

8.75 (0.3445)

8.55 (0.3366)

BSC

8

6.20 (0.2441)

5.80 (0.2283)

7

1.75 (0.0689)

1.35 (0.0531)

SEATING

PLANE

4.00 (0.1575)

3.80 (0.1496)

0.25 (0.0098)

0.10 (0.0039)

COPLANARIT Y

0.10

CONTROLL ING DIMENSIONS ARE IN MILLI METERS; INCH DIMENSI ONS

(IN PARENTHESES) ARE ROUNDED-OFF MI LLIMETER EQUIVALENTS FOR

REFERENCE ON LY AND ARE NOT APPROP RIATE FOR USE I N DESIGN.

14

1

1.27 (0.0500)

0.51 (0.0201)

0.31 (0.0122)

COMPLIANT TO JEDEC STANDARDS MS-012-AB

Figure 39. 14-Lead Standard Small Outline Package [SOIC_N]

Dimensions shown in millimeters

Rev. 0 | Page 13 of 16

0.50 (0.0197)

0.25 (0.0098)

8°

0°

0.25 (0.0098)

0.17 (0.0067)

-14)

(R

1.27 (0.0500)

0.40 (0.0157)

45°

060606-A

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

ORDERING GUIDE

Model Temperature Range Package Description Package Option Branding

ADA4000-1ARZ

ADA4000-1ARZ-R7

ADA4000-1ARZ-RL

ADA4000-1AUJZ-R21 −40°C to +125°C 5-Lead TSOT UJ-5 A14

ADA4000-1AUJZ-R7

ADA4000-1AUJZ-RL

ADA4000-2ARZ

ADA4000-2ARZ-R7

ADA4000-2ARZ-RL

ADA4000-2ARMZ-R2

ADA4000-2ARMZ-RL

ADA4000-4ARZ

ADA4000-4ARZ-R7

ADA4000-4ARZ-RL

ADA4000-4ARUZ1 −40°C to +125°C 14-Lead TSSOP RU-14

ADA4000-4ARUZ-RL

1

Z = RoHS Compliant Part.

1

1

1

1

1

1

1

1

1

1

1

1

−40°C to +125°C 8-Lead SOIC_N R-8

−40°C to +125°C 8-Lead SOIC_N R-8

−40°C to +125°C 8-Lead SOIC_N R-8

−40°C to +125°C 5-Lead TSOT UJ-5 A14

−40°C to +125°C 5-Lead TSOT UJ-5 A14

−40°C to +125°C 8-Lead SOIC_N R-8

−40°C to +125°C 8-Lead SOIC_N R-8

−40°C to +125°C 8-Lead SOIC_N R-8

1

−40°C to +125°C 8-Lead MSOP RM-8 A1H

1

−40°C to +125°C 8-Lead MSOP RM-8 A1H

−40°C to +125°C 14-Lead SOIC_N R-14

−40°C to +125°C 14-Lead SOIC_N R-14

−40°C to +125°C 14-Lead SOIC_N R-14

−40°C to +125°C 14-Lead TSSOP RU-14

Rev. 0 | Page 14 of 16

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

NOTES

Rev. 0 | Page 15 of 16

ADA4000-1/ADA4000-2/ADA4000-4

www.BDTIC.com/ADI

NOTES

©2007 Analog Devices, Inc. All rights reserved. Trademarks and

registered trademarks are the property of their respective owners.

D05791-0-5/07(0)

Rev. 0 | Page 16 of 16

Loading...

Loading...