Analog Devices AD9975 Datasheet

Broadband Modem

a

FEATURES

Low Cost, 3.3 V-CMOS, Mixed Signal, Front End

Converter for Broadband Modems

10-Bit D/A Converter (TxDAC+

50 MSPS Input Word Rate

2ⴛ Interpolating Low-Pass Transmit Filter

100 MSPS DAC Output Update Rate

Wide (21 MHz) Transmit Bandwidth

Power-Down Modes

10-Bit, 50 MSPS A/D Converter

Fourth Order LPF with Selectable Cutoff Frequency

Dual Mode Programmable Gain Amplifier

Internal Clock Multiplier (PLL)

Two Auxiliary Clock Outputs

48-Lead LQFP Package

APPLICATIONS

Powerline Networking

Home Phone Networking

®

)

TXEN

RXEN

TXCLK

RXCLK

ADIO[9:0]

AGC [2:0]

SPORT

Mixed-Signal Front End

AD9975

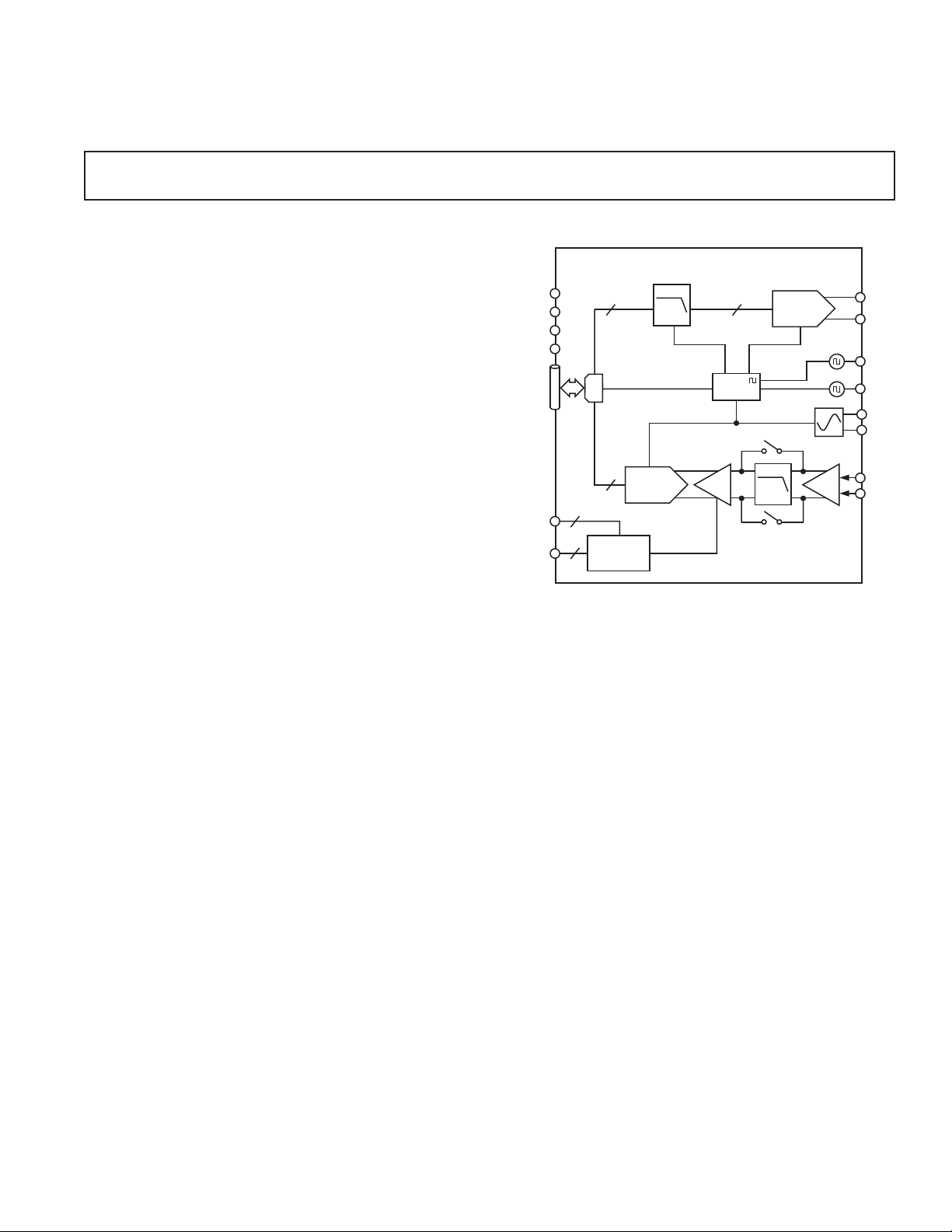

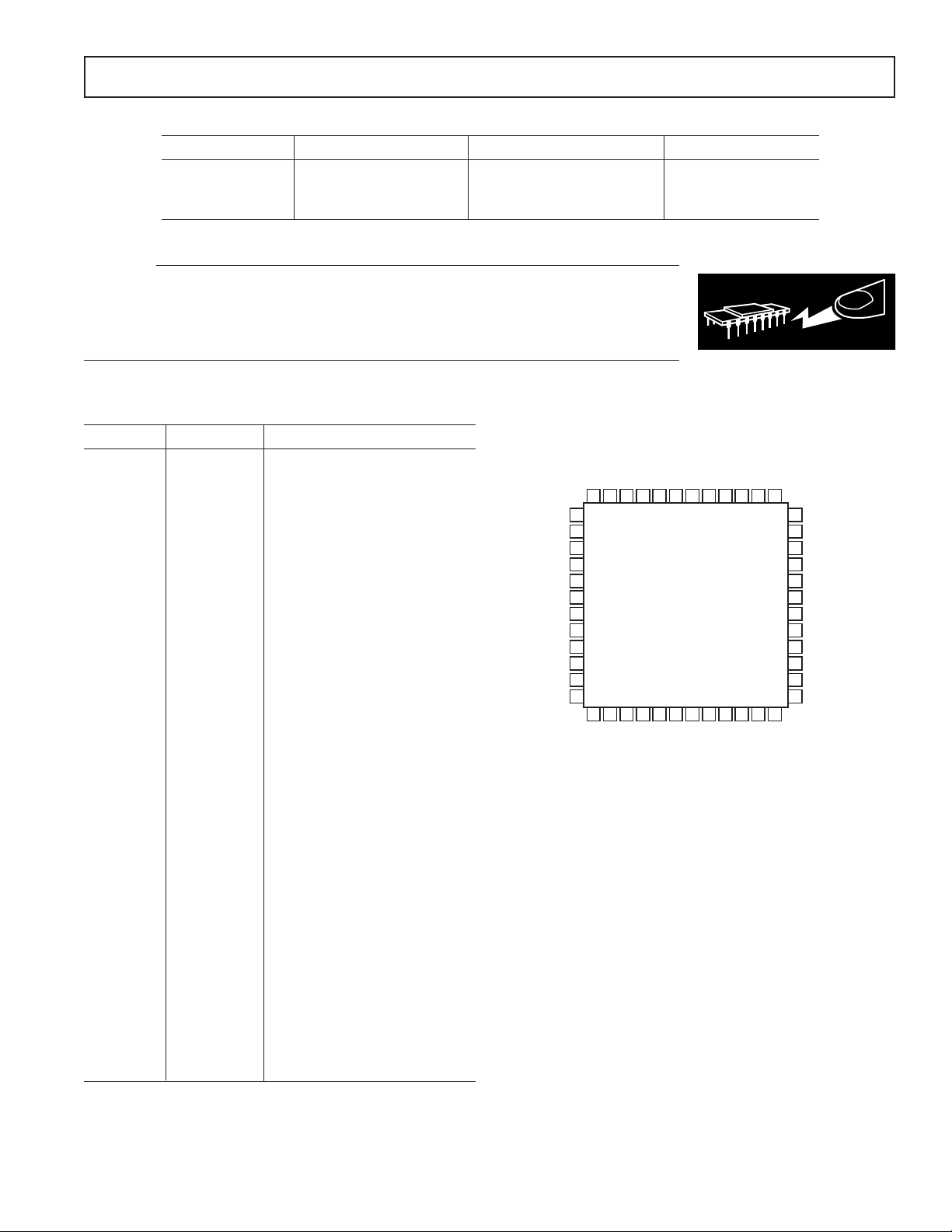

FUNCTIONAL BLOCK DIAGRAM

AD9975

10 10

10

3

3

REGISTER

CONTROL

ADC

K

CLK-GEN

PGA

LPF

TxDAC+

PGA

TX+

TX–

CLK1

CLK2

OSCIN

XTAL

RX+

RX–

GENERAL DESCRIPTION

The AD9975 is a single-supply, broadband modem, mixed

signal, front end (MxFE™) IC. The device contains a transmit

path interpolation filter and DAC and a receive path PGA,

LPF, and ADC required for a variety of broadband modem

applications. Also on-chip is a PLL clock multiplier that provides all required clocks from a single crystal or clock input.

The TxDAC+ uses a digital 2× interpolation low-pass filter to

oversample the transmit data and ease the complexity of analog

reconstruction filtering. The transmit path bandwidth is 21 MHz

when sampled at 100 MSPS. The 10-bit DAC provides differential current outputs. The DAC full-scale current can be adjusted

from 2 to 20 mA by a single resistor, providing 20 dB of additional

gain range.

The receive path consists of a PGA, LPF, and ADC. The programmable gain amplifier (PGA) has two modes of operation. One

mode allows programming through the serial port and provides a

gain range from –6 dB to +36 dB in 2 dB steps. The other mode

allows the gain to be controlled through an asynchronous 3-pin

port and offers a gain range from 0 dB to 48 dB in 8 dB steps

with the use of an external gain stage. The receive path LPF

cutoff frequency can be selected to either 12 MHz or 26 MHz.

TxDAC+ is a registered trademark and MxFE is a trademark of Analog Devices, Inc.

The filter cutoff frequency can also be tuned or bypassed where

filter requirements differ. The 10-bit ADC uses a multistage

differential pipeline architecture to achieve excellent dynamic

performance with low power consumption.

The digital transmit and receive ports are multiplexed onto a

10-bit databus and have individual TX/RX clocks and TX/RX

enable lines. This interface connects directly to Homelug 1.0

PHY/MAC chips from Intellon and Conexant.

The AD9975 is available in a space-saving 48-lead LQFP package. The device is specified over the commercial (–40°C to

+85°C) temperature range.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

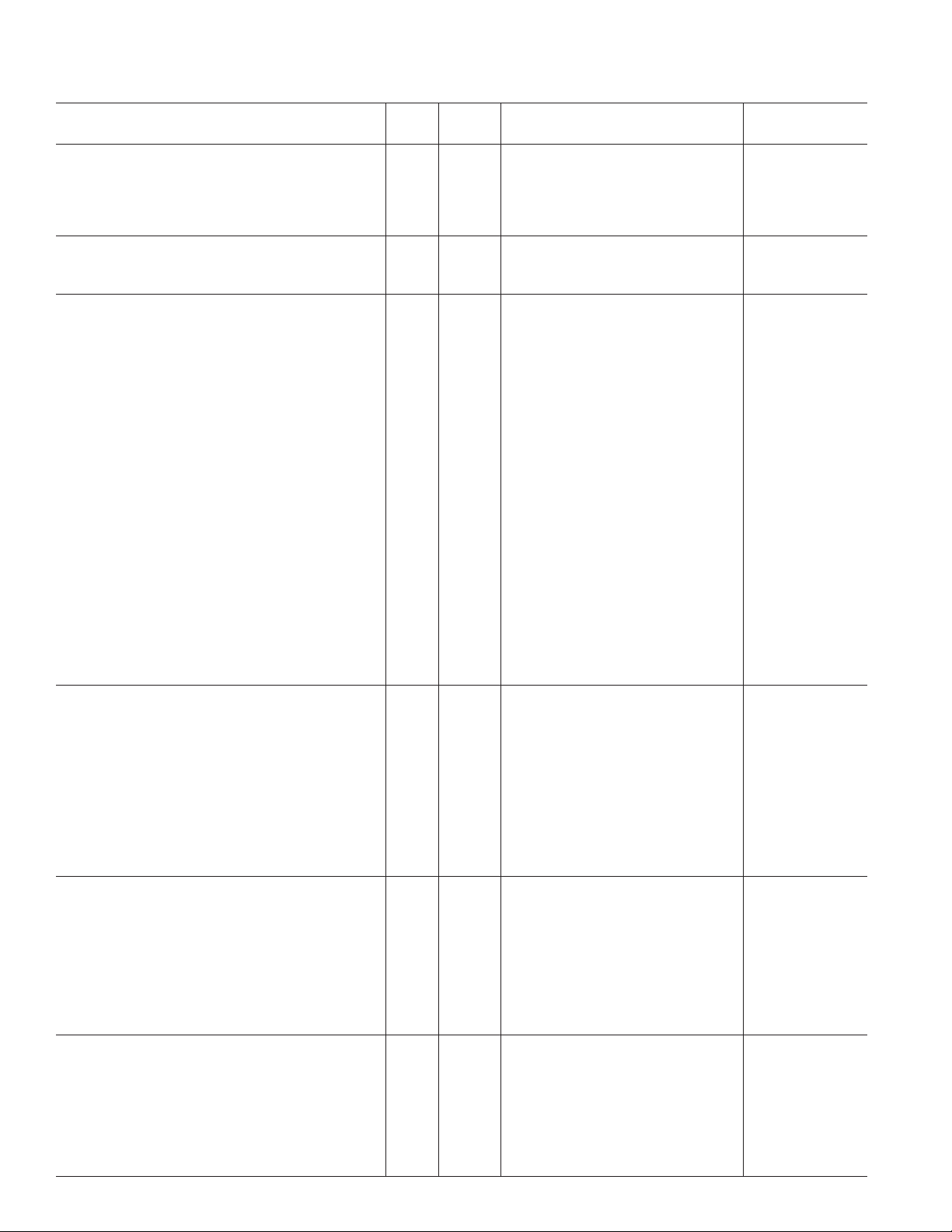

AD9975–SPECIFICATIONS

(VS = 3.3 V ⴞ10%, F

R

= 4.02 k⍀, 100 ⍀ DAC Load.)

SET

= 50 MHz, F

OSCIN

= 100 MHz, Gain = –6 dB,

DAC

Test

Parameter Temp Level Min Typ Max Unit

OSC IN CHARACTERISTICS

Frequency Range Full I 10 50 MHz

Duty Cycle 25°CII 40 50 60 %

Input Capacitance 25°C III 3 pF

Input Impedance 25°C III 100 MΩ

CLOCK OUTPUT CHARACTERISTICS

CLKA Jitter (F

Derived from PLL) 25°CII 14 ps rms

CLKA

CLKA Duty Cycle 25°C III 50 ± 5%

TX CHARACTERISTICS

2× Interpolation Filter Characteristics

TX Path Latency, 2× Interpolation Full II 30 F

DAC

Cycles

Pass-Band Flatness 0 MHz to 20.7 MHz Full II 0.8 dB

Stop-Band Rejection @ 29.3 MHz Full II 35 dB

TxDAC

Resolution Full II 10 Bits

Conversion Rate Full II 10 100 MHz

Full-Scale Output Current Full II 2 10 20 mA

Voltage Compliance Range (TX+ or TX– AVSS) Full II –0.5 +1.5 V

Gain Error 25°CII –5.5 ±2+5.0 %FS

Output Offset 25°CII 0 2 TBD µA

Differential Nonlinearity 25°C III 0.5 LSB

Integral Nonlinearity 25°CII 1 LSB

Output Capacitance 25°C III 5 pF

Phase Noise @ 1 kHz Offset, 10 MHz Signal 25°C III –100 dBc/Hz

Signal-to-Noise and Distortion (SINAD)

5 MHz Analog Out (20 MHz BW) 25°CII –60.6 dB

Wideband SFDR (to Nyquist, 50 MHz max) 25°C III

5 MHz Analog Out 25°C III –76.2 dBc

Narrowband SFDR (3 MHz Window)

5 MHz Analog Out 25°C III –77.9 dBc

IMD (f1 = 6.25 MHz, f2 = 7.8125 MHz) 25°C III –77 dBFS

RX PATH CHARACTERISTICS (LFP Bypassed)

Resolution N/A N/A 10 Bits

Conversion Rate Full II 10 50 MHz

Pipeline Delay, ADC Clock Cycles N/A N/A 5.5 Cycles

Dynamic Performance (A

@ F

= 50 MHz, RX LPF Bypassed

OSCIN

= –0.5 dBFS, f = 5 MHz)

IN

Signal-to-Noise and Distortion Ratio (SINAD) Full III –56.6 dB

Effective Number of Bits (ENOB) Full III 9.1 Bits

Signal-to-Noise Ratio (SNR) Full III –59.2 dB

Total Harmonic Distortion (THD) Full III –60.1 dB

Spurious-Free Dynamic Range (SFDR) Full III –66 dB

RX PATH GAIN/OFFSET

Minimum Programmable Gain 25°CI –6 dB

Maximum Programmable Gain

Narrow Band Rx LPF or Rx LPF Bypassed 25°CI +36 dB

Wideband Rx LPF

25°CI +30 dB

Gain Step Size 25°CI 2 dB

Gain Step Accuracy 25°CII ± 0.4 dB

Gain Range Error Full II ± 1.0 dB

Absolute Gain Error, PGA Gain = 0 dB Full II ± 0.8 dB

RX PATH INPUT CHARACTERISTICS

Input Voltage Range (Gain = –6 dB) Full III 4 Vppd

Input Capacitance 25°C III 4 pF

Differential Input Resistance 25°C III 270 Ω

Input Bandwidth (–3 dB) (Rx LPF Bypassed) 25°C III 50 MHz

Input Referred Noise (at +36 dB Gain with Filter) 25ºC III 16 µV rms

Input Referred Noise (at –6 dB Gain with Filter) 25ºC III 684 µV rms

Common-Mode Rejection 25ºC III 40 dB

REV. 0–2–

AD9975

Test

Parameter Temp Level Min Typ Max Unit

RX PATH LPF (Low Cutoff Frequency)

Cutoff Frequency Full III 12 MHz

Cutoff Frequency Variation Full III ± 7%

Attenuation @ 22 MHz Full III 20 dB

Pass-Band Ripple Full II ± 1.0 dB

Group Delay Variation Full II 30 ns

Settling Time (to 1% FS, Min to Max Gain Change) 25°CII 150 ns

Total Harmonic Distortion at Max Gain (THD) Full I –61 dBc

RX PATH LPF (High Cutoff Frequency)

Cutoff Frequency Full III 26 MHz

Cutoff Frequency Variation Full III ± 7%

Attenuation @ 35 MHz Full III 20 dB

Pass-Band Ripple Full II ± 1.2 dB

Group Delay Variation Full II 15 ns

Settling Time (to 1% FS, Min to Max Gain Change) 25°CII 80 ns

Total Harmonic Distortion at Max Gain (THD) Full I –61 dBc

RX PATH DIGITAL HPF

Latency (ADC Clock Source Cycles) 1 Cycle

Roll-Off in Stop Band 6 dB/Octave

–3 dB Frequency f

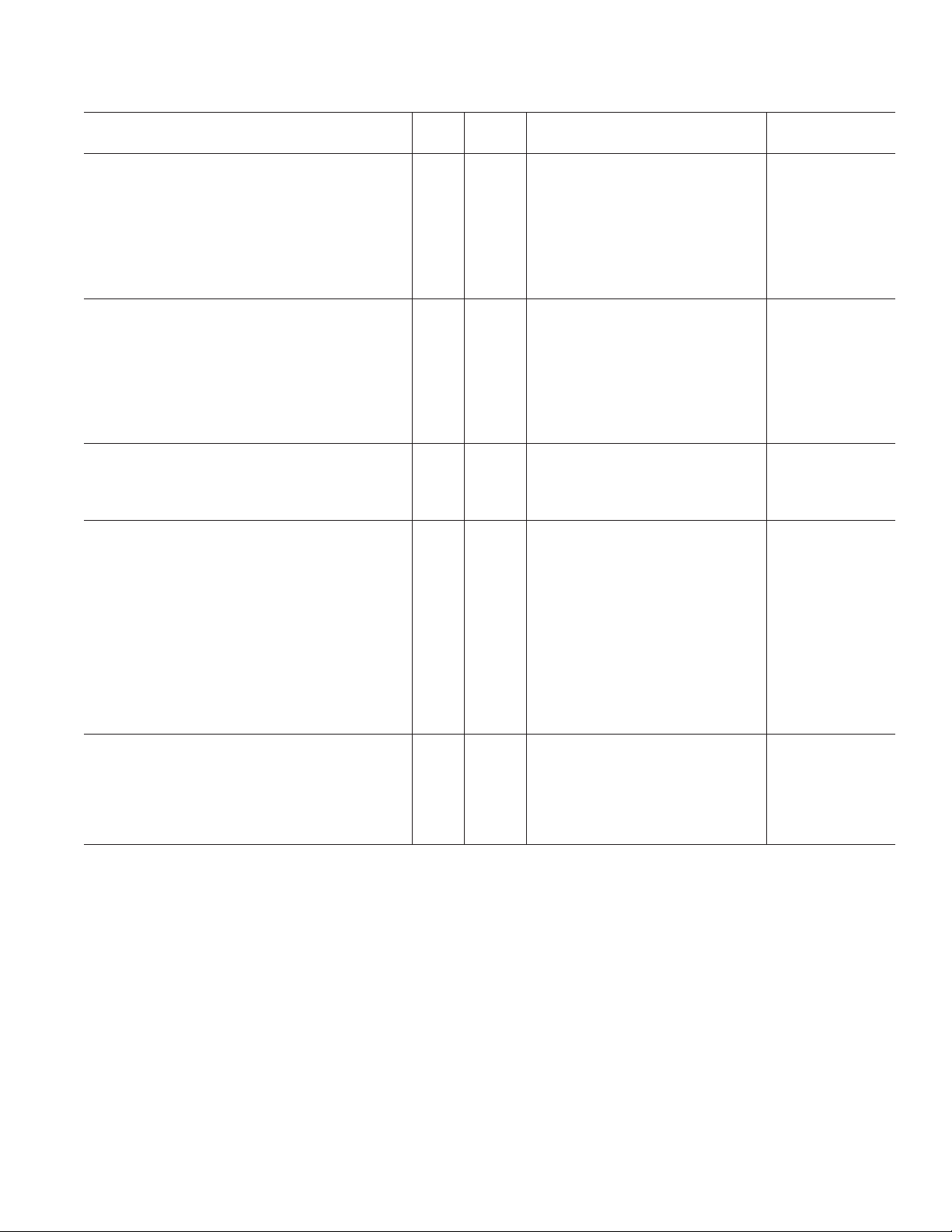

POWER-DOWN/DISABLE TIMING

Power-Down Delay (Active-to-Power-Down)

DAC 25°CII 200 ns

Interpolator 25°CII 200 ns

Power-Up Delay (Power-Down-to-Active)

DAC 25°CII 10 µs

PLL 25°CII 10 µs

ADC 25°CII 1000 µs

PGA 25°CII 1 µs

LPF 25°CII 1 µs

Interpolator 25°CII 200 ns

Minimum RESET Pulsewidth Low (tRL) Full III 5 f

ADIO PORT INTERFACE

Maximum Input Word Rate 25°CI 100 MHz

TX-Data Setup Time (t

TX-Hold Hold Time (t

RX-Data Valid Time(t

)25°CII 3.0 ns

SU

)25°CII 0 ns

HD

)25°CII 3.0 ns

VT

RX-Data Hold Time (tHT)25°CII 1.5 ns

/400 Hz

ADC

OSCIN

Cycles

REV. 0

–3–

AD9975

SPECIFICATIONS

(continued)

Test

Parameter Temp Level Min Typ Max Unit

SERIAL CONTROL BUS

Maximum SCLK Frequency (f

Clock Pulsewidth High (t

Clock Pulsewidth Low (t

PWH

PWL

) Full II 25 MHz

SCLK

) Full II 18 ns

) Full II 18 ns

Clock Rise/Fall Time Full II 10 µs

Data/Chip-Select Setup Time (t

) Full II 25 ns

DS

Data Hold Time (tDH) Full II 0 ns

Data Valid Time (tDV) Full II 20 ns

CMOS LOGIC INPUTS

Logic “1” Voltage 25°CII

V

– 0.7 V

DRVDD

Logic “0” Voltage 25°CII 0.4 V

Logic “1” Current 25°CII 12 µA

Logic “0” Current 25°CII 12 µA

Input Capacitance 25°C III 3 pF

CMOS LOGIC OUTPUTS (1 mA Load)

Logic “1” Voltage Full II

V

– 0.6 V

DRVDD

Logic “0” Voltage 25°CII 0.4 V

Digital Output Rise/Fall Time Full II 1.5 2.5 ns

POWER SUPPLY

All Blocks Powered Up

I

Digital Supply Current (I

Clock Supply Current (I

Analog Supply Current (I

(Total Supply Current) 25°CI 210 227 mA

S_TOTAL

+ I

DRVDD

)25°C III 5.5 mA

CLKVDD

)25°C III 182 mA

AVDD

)25°C III 22.5 mA

DVDD

Power Consumption of Functional Blocks

Rx LPF 25°C III 110 mA

ADC and SPGA 25°C III 55 mA

Rx Reference 25°C III 2 mA

Interpolator 25°C III 20 mA

DAC 25°C III 18 mA

PLL-A 25°C III 22

All Blocks Powered Down

I

Digital Supply Current (I

Clock Supply Current (I

Analog Supply Current (I

Specifications subject to change without notice.

(Total Supply Current) 25°CI 21 27 mA

S_TOTAL

+ I

DRVDD

)25°C III 0 mA

CLKVDD

)25°C III 11 mA

AVDD

)25°C III 10 mA

DVDD

ABSOLUTE MAXIMUM RATINGS*

Power Supply (VS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.9 V

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . 5 mA

Digital Inputs . . . . . . . . . . . . . . . . –0.3 V to DRVDD + 0.3 V

Analog Inputs . . . . . . . . . . . . . . . . . –0.3 V to AVDD + 0.3 V

Operating Temperature . . . . . . . . . . . . . . . . . . –40°C to +85°C

Maximum Junction Temperature . . . . . . . . . . . . . . . . . 150°C

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . . . 300°C

*Absolute Maximum Ratings are limiting values to be applied individually and

beyond which the serviceability of the circuit may be impaired. Functional

operability under any of these conditions is not necessarily implied. Exposure to

absolute maximum rating conditions for extended periods of time may affect

device reliability.

EXPLANATION OF TEST LEVELS

I. Devices are 100% production tested at 25°C and guaranteed

by design and characterization testing for the commercial

operating temperature range (–40°C to +85°C).

II. Parameter is guaranteed by design and/or characterization

testing.

III. Parameter is a typical value only.

THERMAL CHARACTERISTICS

Thermal Resistance

48-Lead LQFP

= 57ºC/W

θ

JA

= 28ºC/W

θ

JC

REV. 0–4–

WARNING!

ESD SENSITIVE DEVICE

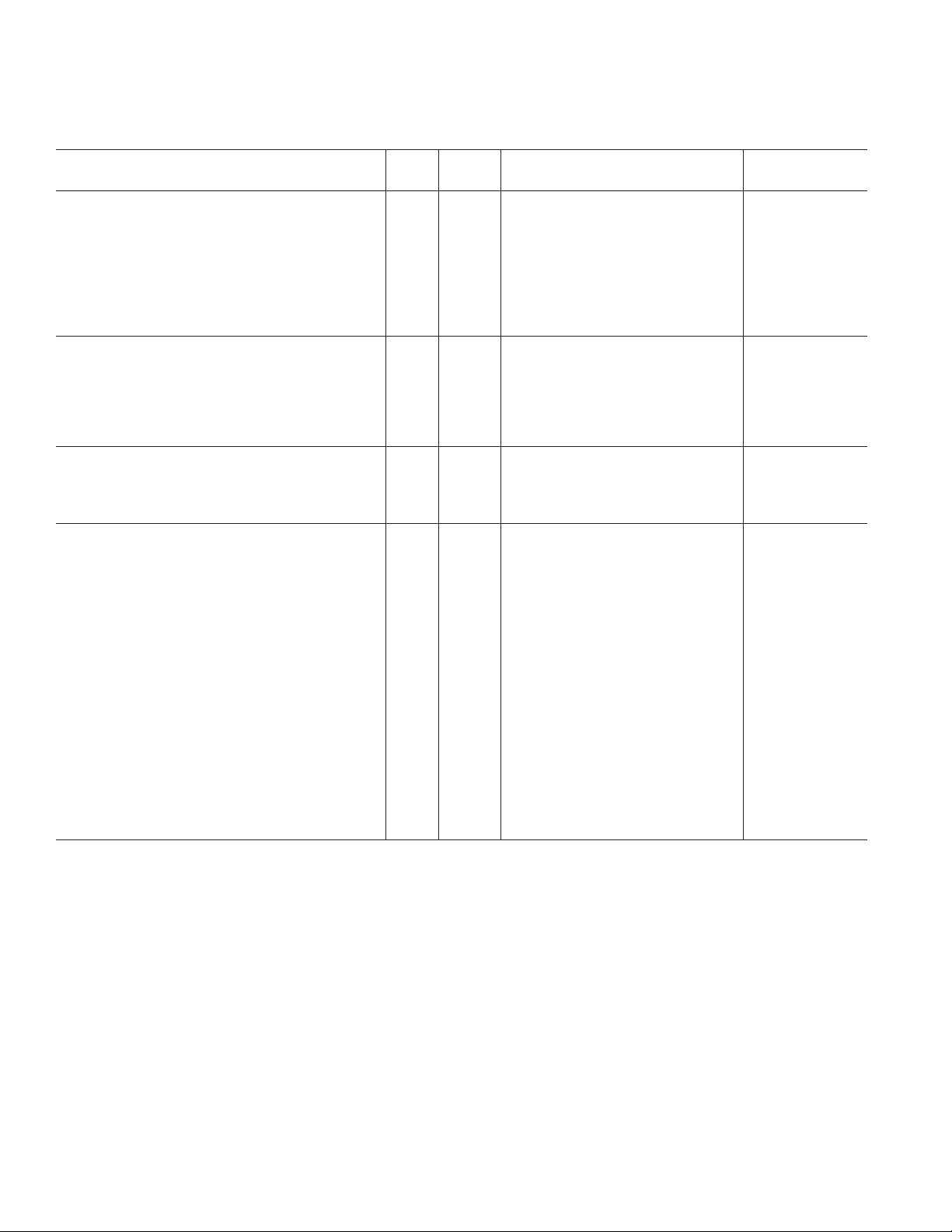

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD9975ABST –40ºC to +85ºC 48-Lead LQFP ST-48

AD9975ABSTEB –40ºC to +85ºC AD9975 EVAL Board

AD9975ABSTRL –40ºC to +85ºC AD9975ABST Reel

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD9975 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

AD9975

PIN FUNCTION DESCRIPTION

Pin No. Mnemonic Function

1OSC IN Crystal Oscillator Inverter Input

2 SENABLE Serial Bus Enable Input

3 SCLK Serial Bus Clock Input

4 SDATA Serial Bus Data I/O

5, 38, 47 AVDD Analog 3.3 V Power Supply

6, 9, 39, 42, AVSS Analog Ground

43, 46

7Tx+ Transmit DAC + Output

8 Tx– Transmit DAC – Output

10 FS ADJ DAC Full-Scale Output Current

Adjust with External Resistor

11 REFIO DAC Band Gap Decoupling Node

12 CLKVDD Power Supply for CLKOUT1

13 DVSS Digital Ground

14 DVDD Digital 3.3 V Power Supply

15–17 AGC[2:0] AGC Control Inputs

18 CLKOUT1 Auxiliary Clock Output

19–28 ADIO[9:0] Digital Data I/O Port

29 RXEN ADIO Direction Control Input

30 TXEN TX Path Enable

31 TXCLK ADIO Sample Clock Input

32 RXCLK ADIO Request Clock Input

33 CLKOUT2 Auxiliary Clock Output

34 RXBOOST/ External Gain Control Output/

SDO Serial Data Output

35 DRVDD Digital I/O 3.3 V Power Supply

36 DRVSS Digital I/O Ground

37 RESET Reset Input

40, 41 REFB, REFT ADC Reference Decoupling Node

44 Rx+ Receive Path + Input

45 Rx– Receive Path – Input

48 XTAL Crystal Oscillator Inverter Output

OSC IN

SENABLE

SCLK

SDATA

AV DD

AVSS

TX+

TX–

AVSS

FS ADJ

REFIO

CLKVDD

PIN CONFIGURATION

XTAL47AV DD46AVSS45RX–44RX+43AVSS42AVSS41REFT40REFB39AVSS38AV DD37RESET

48

1

2

3

4

5

6

7

8

9

10

11

12

13

14

DVSS

DVD D

AD9975

48-PIN LQFP

TOP VIEW

(Not to Scale)

15

AGC216AGC117AGC0

18

19

ADIO920ADIO821ADIO722ADIO623ADIO524ADIO4

CLKOUT1

36

DRVSS

35

DRVDD

34

RXBOOST/SDO

33

CLKOUT2

32

RXCLK

31

TXCLK

30

TXEN

29

RXEN

28

ADIO0

27

ADIO1

26

ADIO2

25

ADIO3

REV. 0

–5–

AD9975

DEFINITIONS OF SPECIFICATIONS

Clock Jitter

The clock jitter is a measure of the intrinsic jitter of the PLL

generated clocks. It is a measure of the jitter from one rising

edge of the clock with respect to another edge of the clock nine

cycles later.

Differential Nonlinearity Error (DNL, No Missing Codes)

An ideal converter exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. Guaranteed no

missing codes to 10-bit resolution indicate that all 1024 codes,

respectively, must be present over all operating ranges.

Integral Nonlinearity Error (INL)

Linearity error refers to the deviation of each individual code from

a line drawn from “negative full scale” through “positive full

scale.” The point used as negative full scale occurs 1/2 LSB

before the first code transition. Positive full scale is defined as a

level 1 1/2 LSB beyond the last code transition. The deviation is

measured from the middle of each particular code to the true

straight line.

Phase Noise

Single-sideband phase noise power density is specified relative

to the carrier (dBc/Hz) at a given frequency offset (1 kHz) from

the carrier. Phase noise can be measured directly on a generated

single tone with a spectrum analyzer that supports noise marker

measurements. It detects the relative power between the carrier

and the offset (1 kHz) sideband noise and takes the resolution

bandwidth (rbw) into account by subtracting 10 log(rbw). It also

adds a correction factor that compensates for the implementation

of the resolution bandwidth, log display, and detector characteristic.

Output Compliance Range

The range of allowable voltage at the output of a current-output

DAC. Operation beyond the maximum compliance limits may

cause either output stage saturation, resulting in nonlinear performance, or breakdown.

Spurious-Free Dynamic Range (SFDR)

The difference, in dB, between the rms amplitude of the DAC’s

output signal (or ADC’s input signal) and the peak spurious

signal over the specified bandwidth (Nyquist bandwidth, unless

otherwise noted).

Pipeline Delay (Latency)

The number of clock cycles between conversion initiation and

the associated output data being made available.

Offset Error

First transition should occur for an analog value 1/2 LSB above

negative full scale. Offset error is defined as the deviation of the

actual transition from that point.

Gain Error

The first code transition should occur at an analog value 1/2 LSB

above negative full scale. The last transition should occur for an

analog value 1 1/2 LSB below the nominal full scale. Gain error

is the deviation of the actual difference between first and last

code transitions and the ideal difference between first and last

code transitions.

Input Referred Noise

The rms output noise is measured using histogram techniques.

The ADC output code’s standard deviation is calculated in LSB

and converted to an equivalent voltage. This results in a

noise figure that can directly be referred to the RX input of

the AD9975.

Signal-to-Noise and Distortion Ratio (SINAD)

SINAD is the ratio of the rms value of the measured input signal

to the rms sum of all other spectral components below the Nyquist

frequency, including harmonics but excluding dc. The value for

SINAD is expressed in decibels.

Effective Number of Bits (ENOB)

For a sine wave, SINAD can be expressed in terms of the number

of bits. Using the following formula,

N SINAD dB= (–.)/.176 602

it is possible to get a measure of performance expressed as N,

the effective number of bits.

Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured input signal to

the rms sum of all other spectral components below the Nyquist

frequency, excluding harmonics and dc. The value for SNR is

expressed in decibels.

Total Harmonic Distortion (THD)

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured input signal and is

expressed as a percentage or in decibels.

Power Supply Rejection

Power supply rejection specifies the converter’s maximum

full-scale change when the supplies are varied from nominal to

minimum and maximum specified voltages.

REV. 0–6–

Loading...

Loading...