DUAL Channel 500MSPS DDS with 10-bit DACs

Preliminary Technical Data

FEATURES

Two synchronized DDS channels @500 MSPS

Independent frequency / phase / amplitude

control between all channels

Matched latencies for Freq, Phase, and Amplitude changes

Excellent channel to channel isolation

Frequency sweeping capability

Up to 16 levels of modulation (pin selectable)

Programmable DAC full scale current

Two integrated 10-bit D/A converters(DACs)

32-bit frequency tuning resolution

14-bit phase offset resolution

10-bit output amplitude scaling resolution

Serial I/O Port(SPI) with enhanced data throughput

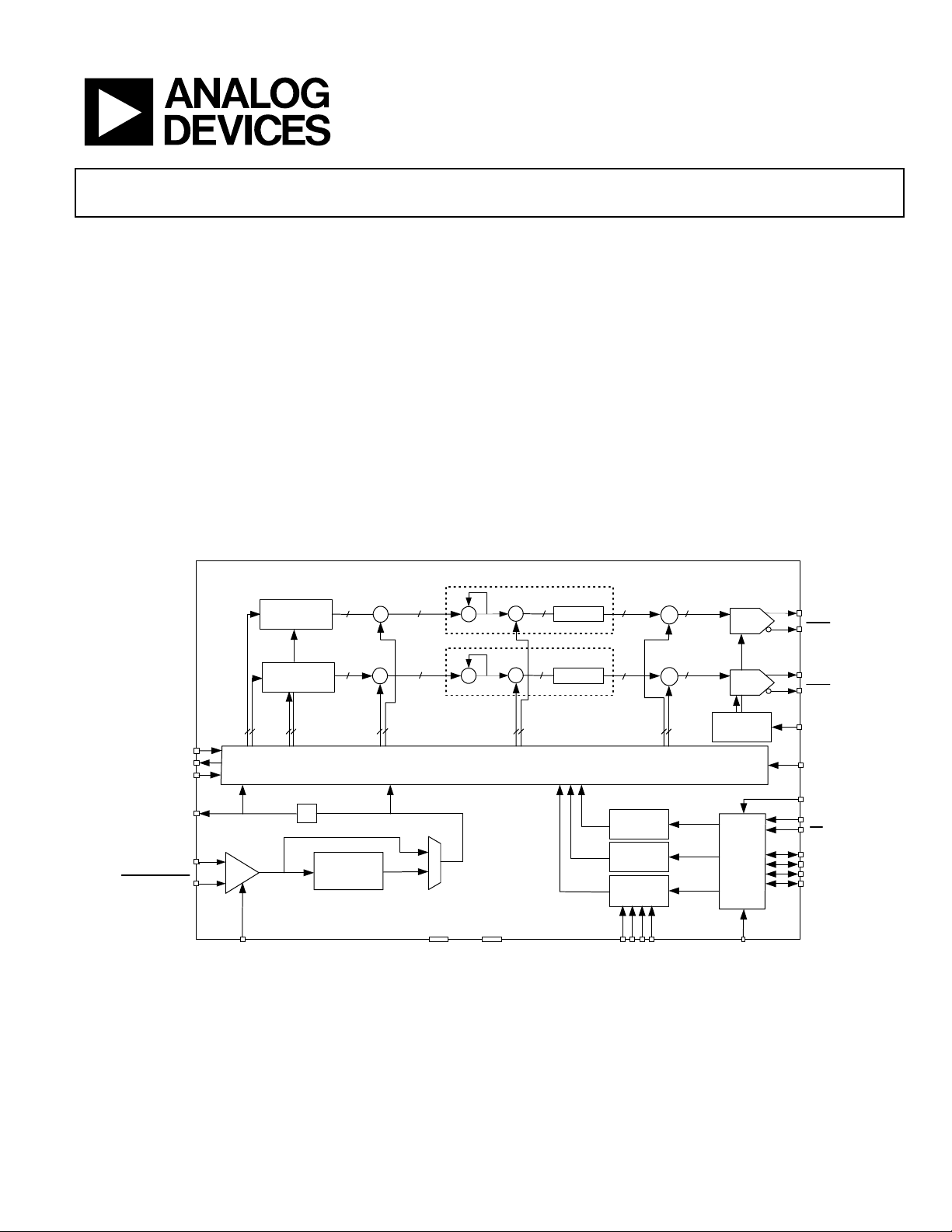

FUNCTIONAL BLOCK DIAGRAM

AD9958

Software/Hardware controlled power-down

Dual supply operation (1.8 V DDS core / 3.3 V serial I/O)

Built-in synchronization for multiple devices

Selectable REF CLK multipier(PLL) 4x to 20x (bypassable)

Selectable REF CLK crystal operation

56 pin LFCSP package

APPLICATIONS

Agile L.O. frequency synthesis

Phased array radar / sonar

Instrumentation

Synchronized clocking

RF source for AOTF

SYNC_IN

SYNC_OUT

IO_UPDATE

SYNC_CLK

OSC / REF_CLK

OSC / REF_CLK

ACCUMULATOR

ACCUMULATOR

32

DFTW

BUFFER / XTAL

OSCILLATOR

CLK_MODE_SEL

FREQUENCY

FREQUENCY

RAMP

RATE

÷4

32

32

8

REF CLOCK

MULTIPLIER

4x to 20x

Σ

32

Σ

32

32

FTW

Timing & Control Logic

SYSTEM

CLK

M

U

X

AVDD DVDD

Figure 1 AD9958 Block Diagram

Σ

Σ

PHASE

OFFSET

DDS CORE

Σ

Σ

1.8V1.8V

COS(X)

15

DDS CORE

COS(X)

15

14

10

10

AMP

CONTROL

CONTROL

REGISTERS

CHANNEL

REGISTERS

PROFILE

REGISTERS

P

P

P

P

S

S

S

S

0

3

2

1

×

10

×

10

10

DAC

DAC

SCALABLE

DAC REF

CURRENT

I/O

Port

Buffer

3.3V

DVDD_IO

IOUT

IOUT

IOUT

IOUT

DAC_RSET

PWR_DWN_CTL

MASTER_RESET

SCLK

CS

SDIO_0

SDIO_1

SDIO_2

SDIO_3

Rev. PrB

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

AD9958 Preliminary Technical Data

AD9958—SPECIFICATIONS

Table 1. Unless otherwise noted, AVDD, DVDD = 1.8 V ± 5%, DVDD_I/O = 3.3 V ± 5%, R

Frequency = 500 MSPS (REF_CLK multiplier bypassed)

Parameter

REF CLOCK INPUT CHARACTERISTICS

Frequency Range

REF_CLK Multiplier bypassed 0 500 MHz

REF_CLK Multiplier enabled at 4x(min) 25 125 MHz

REF_CLK Multiplier enabled at 20x(max) 5 25 MHz

Internal VCO range w/ REF_CLK multiplier enabled 100 500 MHz

Crystal Ref Clock source mode 20 30 MHz

Input Power Sensitivity -15 3 dBm External 50 ohm termination

Input voltage level 400 mV

Input Capacitance 3 pF

Input Impedance 1500 ohms

Duty Cycle w/ REF_CLK Multiplier bypassed 50 %

Duty Cycle w/ REF_CLK Multiplier enabled 35 65 %

CLK Mode Select logic 1 Voltage 1.25 V Not a 3.3V digital input

CLK Mode Select logic 0 Voltage 0.6 V Not a 3.3V digital input

DAC OUTPUT CHARACTERISTICS

Resolution 10 Bits

Full Scale Ouput Current 10 mA

Gain Error -10 10 %FS

Output Offset 0.6 uA

Differential Nonlinearity -0.5 0.5 LSB

Integral Nonlinearity -1 1 LSB

Output Capactiance

Voltage Compliance Range

Channel to Channel Isolation 60 dB

Channel to Channel amplitude matching error 2 %

WIDEBAND SFDR

1-20 MHz Analog Out -65 dBc

20-60 MHz Analog Out -62 dBc

60-100 MHz Analog Out -59 dBc

100-150 MHz Analog Out -56 dBc

150-200 MHz Analog Out -54 dBc

NARROWBAND SFDR

1.1 MHz Analog Out (+/- 10kHz) -90 dBc

1.1 MHz Analog Out (+/- 50kHz) -88 dBc

1,1 MHz Analog Out (+/- 250kHz) -86 dBc

1.1 MHz Analog Out (+/- 1MHz) -85 dBc

15.1 MHz Analog Out (+/- 10kHz)

15.1 MHz Analog Out (+/- 50kHz) -87 dBc

15.1 MHz Analog Out (+/- 250kHz) -85 dBc

15.1 MHz Analog Out (+/- 1MHz) -83 dBc

40.1 MHz Analog Out (+/- 10kHz)

40.1 MHz Analog Out (+/- 50kHz) -87 dBc

40.1 MHz Analog Out (+/- 250kHz) -84 dBc

40.1 MHz Analog Out (+/- 1MHz) -82 dBc

Min Typ

5

AVDD–

0.50

-90

-90

Max Units

pF

AVDD

+ 0.50

= 1.96 kΩ, External Reference Clock

SET

Test Conditions/Comments

REF_CLK inputs must be AC

coupled due to internal biasing

Must be referenced to AVDD

V

Wideband SFDR defined as DC to

dBc

dBc

Nyquist

Rev. PrB | Page 2 of 9

Preliminary Technical Data AD9958

Parameter

75.1 MHz Analog Out (+/- 10kHz) -87 dBc

75.1 MHz Analog Out (+/- 50kHz) -85 dBc

75.1 MHz Analog Out (+/- 250kHz) -83 dBc

75.1 MHz Analog Out (+/- 1MHz) -82 dBc

100.1 MHz Analog Out (+/- 10kHz) -87 dBc

100.1 MHz Analog Out (+/- 50kHz) -85 dBc

100.1 MHz Analog Out (+/- 250kHz) -83 dBc

100.1 MHz Analog Out (+/- 1MHz) -81

200.1 MHz Analog Out (+/- 10kHz) -87 dBc

200.1 MHz Analog Out (+/- 50kHz) -85 dBc

200.1 MHz Analog Out (+/- 250kHz) -83 dBc

200.1 MHz Analog Out (+/- 1MHz) -81

PHASE NOISE CHARACTERISTICS

Residual Phase Noise @15.1 MHz(Aout)

@1kHz offset TBD dBc/ Hz

@10kHz offset TBD dBc/ Hz

@100kHz offset TBD dBc/ Hz

@1MHz offset TBD dBc/ Hz

Residual Phase Noise @ 75.1 MHz(Aout)

@1kHz offset TBD dBc/ Hz

@10kHz offset TBD dBc/ Hz

@100kHz offset TBD dBc/ Hz

@1MHz offset TBD dBc/ Hz

Residual Phase Noise @ 200.1 MHz(Aout)

@1kHz offset TBD dBc/ Hz

@10kHz offset TBD dBc/ Hz

@100kHz offset TBD dBc/ Hz

@1MHz offset TBD dBc/ Hz

Residual Phase Noise @ 15.1 MHz(Aout)

w/ REF_CLK multiplier enabled 4x

@1kHz offset TBD dBc/ Hz

@10kHz offset TBD dBc/ Hz

@100kHz offset TBD dBc/ Hz

@1MHz offset TBD dBc/ Hz

Residual Phase Noise @ 75.1 MHz(Aout)

w/ REF_CLK multiplier enabled 4x

@1kHz offset TBD dBc/ Hz

@10kHz offset TBD dBc/ Hz

@100kHz offset TBD dBc/ Hz

@1MHz offset TBD dBc/ Hz

Residual Phase Noise @ 200.1 MHz(Aout)

w/ REF_CLK multiplier enabled 4x

@1kHz offset

@10kHz offset

@100kHz offset

@1MHz offset

SERIAL PORT TIMING CHARACTERISTICS

Maximum Frequency 200

Minimum Clock Pulsewidth Low (t

Minimum Clock Pulsewidth High (t

) TBD

PWL

) TBD

PWH

Min Typ

TBD

TBD

TBD

TBD

Max Units Test Conditions/Comments

dBc

dBc

dBc/ Hz

dBc/ Hz

dBc/ Hz

dBc/ Hz

MHz

ns

ns

Rev. PrB | Page 3 of 9

Loading...

Loading...