CCD Signal Processor with

™

Precision Timing

Generator

AD9937

FEATURES

12 MSPS Correlated Double Sampler (CDS)

10-Bit 12 MHz A/D Converter

No Missing Codes Guaranteed

6 dB to 40 dB Variable Gain Amplifier (VGA)

Black Level Clamp with Variable Level Control

Complete On-Chip Timing Generator

Precision Timing Core with 1.7 ns Resolution

On-Chip: 6-Channel Horizontal and 1-Channel RS Drivers

4-Phase Vertical Transfer Clocks

Electronic and Mechanical Shutter Modes

On-Chip Sync Generator with External Sync Option

APPLICATIONS

Digital Still Cameras

Industrial Imaging

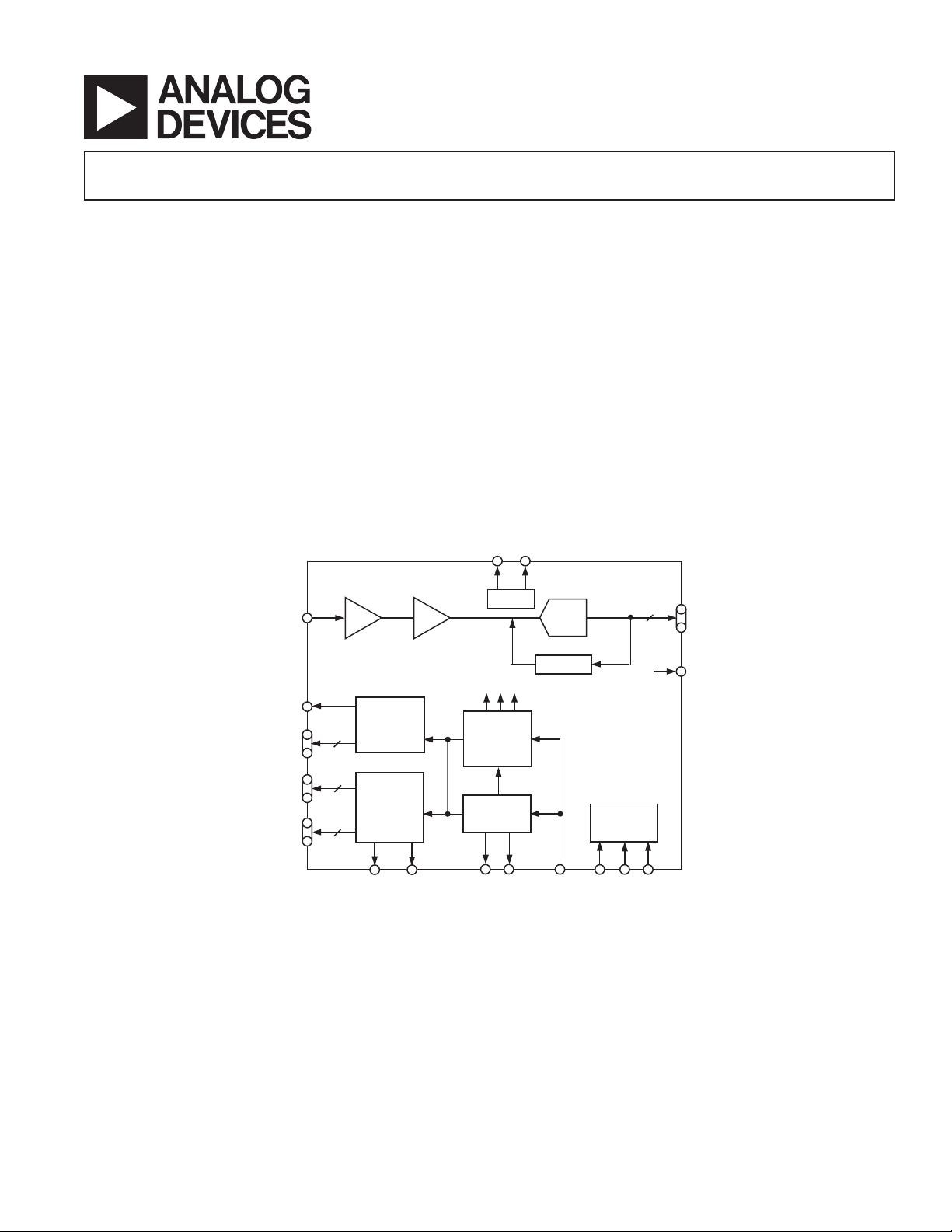

FUNCTIONAL BLOCK DIAGRAM

RS

H1 A–D

H2 A, B

V1 A/B

V3 A/B

TG1A

TG1B

TG3A

TG3B

AD9937

6

V2

V4

4

4

CDS

HORIZONTAL

DRIVERS

V- H

CONTROL

6dB TO 40dB

VGA

INTERNAL CLOCKS

PRECISION

GENERATOR

GENERATOR

GENERAL DESCRIPTION

The AD9937 is a highly integrated CCD signal processor. It

includes a complete analog front end with A/D conversion,

combined with a full-function programmable timing generator.

A Precision Timing core allows adjustment of high speed clocks

with 1.7 ns resolution at 12 MHz operation.

The AD9937 is specified at pixel rates of up to 12 MHz. The

analog front end includes black level clamping, CDS, VGA, and

a 10-bit A/D converter. The timing generator provides all the

necessary CCD clocks: RS, H-clocks, V-clocks, sensor gate pulses,

and substrate charge reset pulse. Operation is programmed using a

3-wire serial interface.

The AD9937 is packaged in a 56-lead LFCSP and specified over

an operating temperature range of –25°C to +85°C.

REFT REFB

VREF

ADC

CLAMP

TIMING

SYNC

INTERNAL

REGISTERS

10

DOUT

VCLK

LM OFD HD VD

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

VCKM

SLD SCK SDA

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

AD9937

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . 1

FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . . . . 1

SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

DIGITAL SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . 3

ANALOG SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . 4

TIMING SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . 5

ABSOLUTION MAXIMUM RATINGS . . . . . . . . . . . . . . . 5

PACKAGE THERMAL CHARACTERISTICS . . . . . . . . . 5

ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

PIN CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . . 6

TERMINOLOGY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Differential Nonlinearity . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Peak Nonlinearity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Total Output Noise . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Power Supply Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

EQUIVALENT CIRCUITS . . . . . . . . . . . . . . . . . . . . . . . . . 7

TYPICAL PERFORMANCE CHARACTERISTICS . . . . . 8

REGISTER MAPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

SERIAL INTERFACE TIMING . . . . . . . . . . . . . . . . . . . . 18

Control Register Serial Interface . . . . . . . . . . . . . . . . . . . 18

System and Mode Register Serial Interface . . . . . . . . . . . 18

Page/Burst Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Random Access Option . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Internal Power-On Reset Circuitry . . . . . . . . . . . . . . . . . . 19

VD Synchronous and Asynchronous Register Operation . 19

Asynchronous Register Operation . . . . . . . . . . . . . . . . . . 19

VD Synchronous Register Operation . . . . . . . . . . . . . . . . 19

SYSTEM OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

ANALOG FRONT END DESCRIPTION AND

OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

DC Restore . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Correlated Double Sampler . . . . . . . . . . . . . . . . . . . . . . . 21

PRECISION TIMING HIGH SPEED TIMING

GENERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Timing Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

High Speed Clock Programmability . . . . . . . . . . . . . . . . . 22

H-Driver and RS Outputs . . . . . . . . . . . . . . . . . . . . . . . . 22

MASTER AND SLAVE MODE OPERATION . . . . . . . . . 25

HORIZONTAL AND VERTICAL TIMING . . . . . . . . . . . 25

Individual HMASK Sequence . . . . . . . . . . . . . . . . . . . . . 25

Individual PBLK Sequences . . . . . . . . . . . . . . . . . . . . . . 25

Controlling CLPOB Clamp Pulse Timing . . . . . . . . . . . . 28

Vertical Sensor Transfer Gate Timing . . . . . . . . . . . . . . . 29

SHUTTER TIMING CONTROL . . . . . . . . . . . . . . . . . . . 29

Normal Shutter Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

High Precision Shutter Mode . . . . . . . . . . . . . . . . . . . . . . 29

Controlling LM Pulse Timing . . . . . . . . . . . . . . . . . . . . . 31

SPECIAL HORIZONTAL PATTERN TIMING . . . . . . . . 32

MASKING H1 AND H2 OUTPUTS . . . . . . . . . . . . . . . . . 33

Horizontal Masking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Vertical Masking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

VERTICAL TIMING GENERATION . . . . . . . . . . . . . . . 35

CCD REGIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

POWER-UP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

STANDBY SEQUENCE . . . . . . . . . . . . . . . . . . . . . . . . . . 40

POWER-DOWN SEQUENCE . . . . . . . . . . . . . . . . . . . . . . 41

CIRCUIT LAYOUT INFORMATION . . . . . . . . . . . . . . . 42

OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 44

TABLES

Table I. Control Register Map . . . . . . . . . . . . . . . . . . . . . . . . 9

Table II. VTP Sequence System Register Map . . . . . . . . . . 10

Table III. H/LM System Register Map . . . . . . . . . . . . . . . . 12

Table IV. Shutter System Register Map . . . . . . . . . . . . . . . . 13

Table V. Mode_A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table VI. Mode_B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table VII. Serial Interface Registers . . . . . . . . . . . . . . . . . . 18

Table VIII. RS, H1, SHP, SHD, and DOUTPHASE

Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table IX. Precision Timing Edge Locations for RS, H1,

SHP, SHD, and DOUTPHASE . . . . . . . . . . . . . . . . . . . . . 23

Table X. HD and VD Registers . . . . . . . . . . . . . . . . . . . . . . 25

Table XI. PBLK Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table XII. CLPOB Registers . . . . . . . . . . . . . . . . . . . . . . . . 28

Table XIII. TG Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table XIV. OFD Registers . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table XV. LM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table XVI. Special H Pattern Registers . . . . . . . . . . . . . . . . 33

Table XVII. Sequence Change Positions Registers . . . . . . . 35

Table XVIII. Start-Up Polarities . . . . . . . . . . . . . . . . . . . . . 39

REV. 0–2–

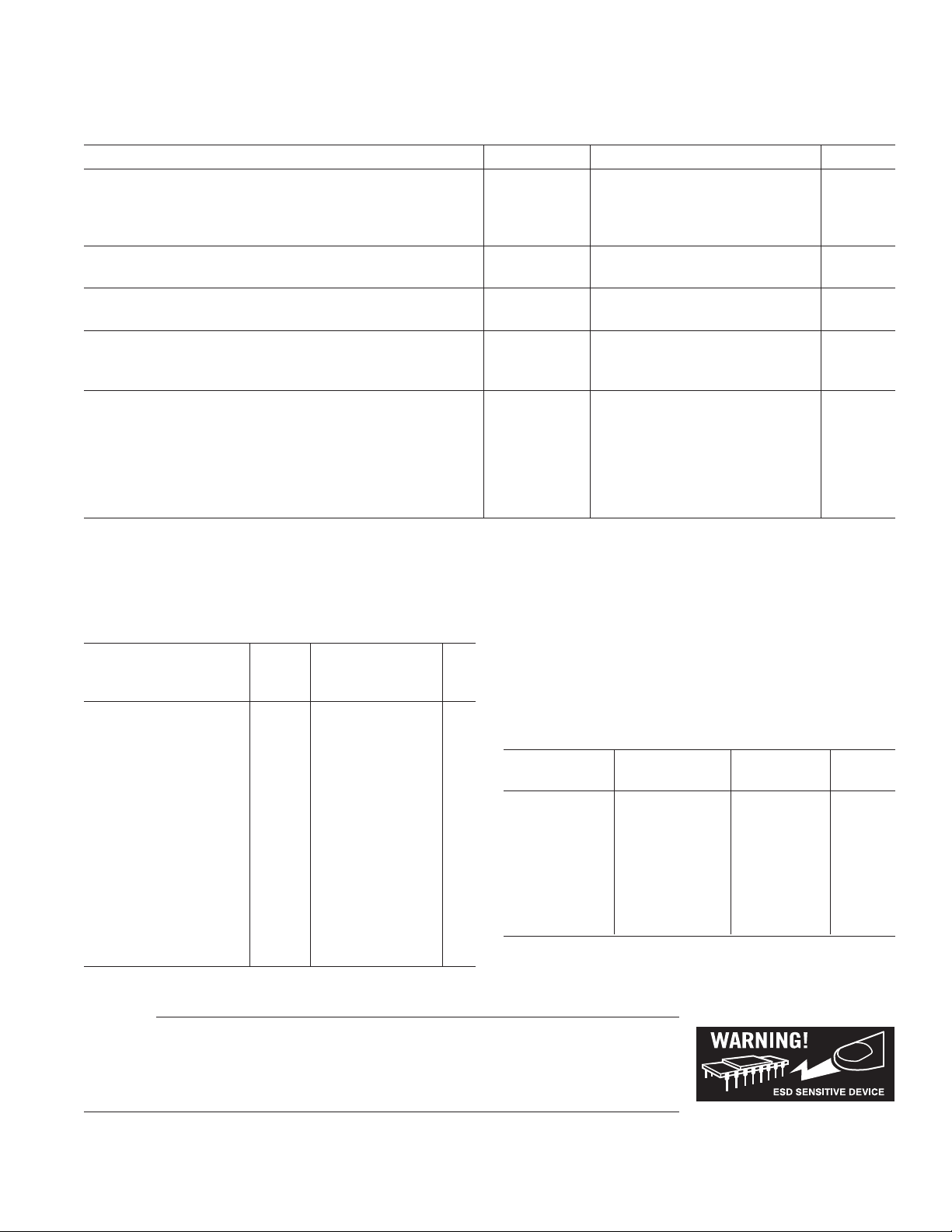

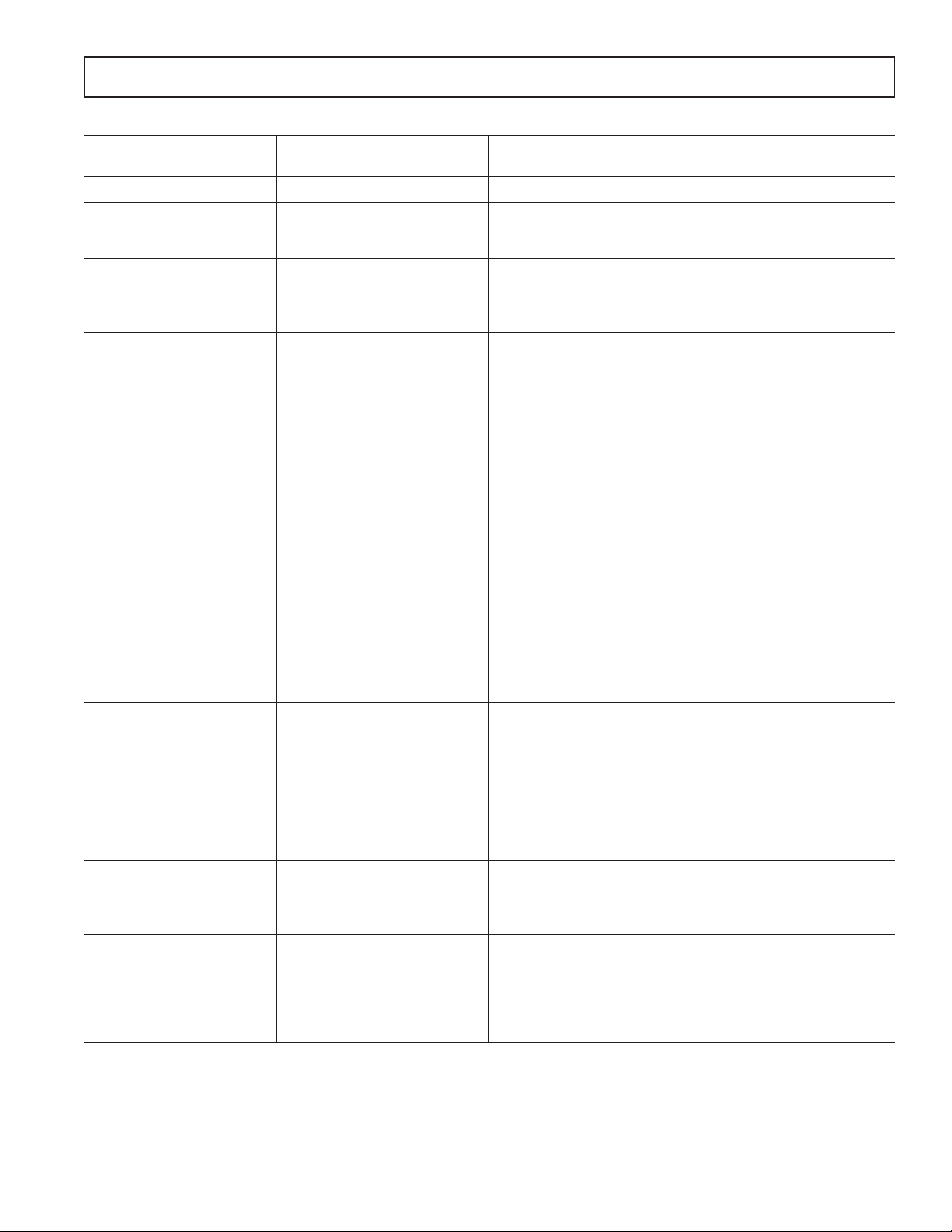

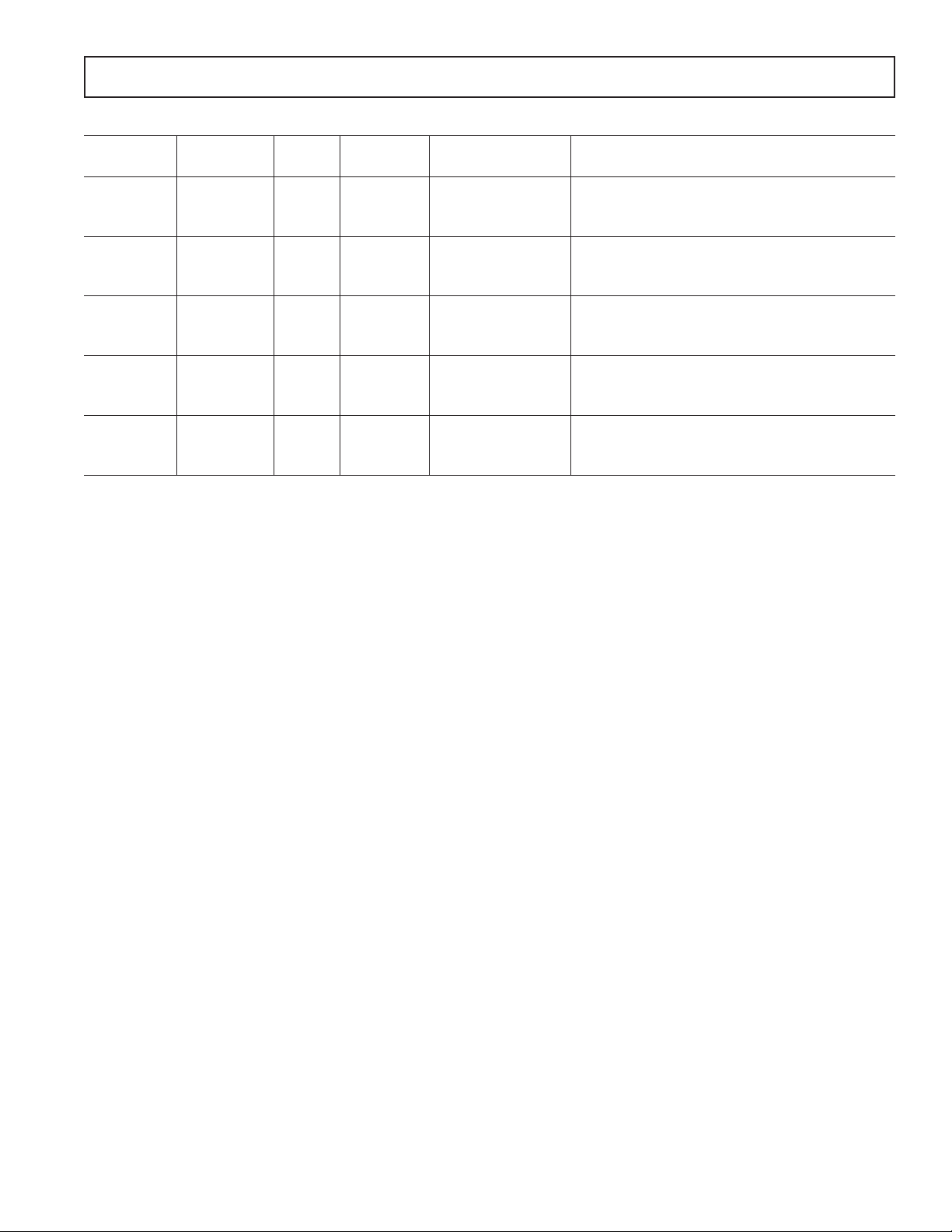

AD9937–SPECIFICATIONS

Parameter Min Typ Max Unit

TEMPERATURE RANGE

Operating –25 +85 °C

Storage –65 +150 °C

POWER SUPPLY VOLTAGE

AVDD (AFE Analog Supply) 2.7 3.0 3.6 V

TCVDD (Timing Core Analog Supply) 2.7 3.0 3.6 V

RSVDD (RS Driver) 2.7 3.0 3.6 V

HVDD1 (H1A, H2A, and H1C Drivers) 2.7 3.0 3.6 V

HVDD2 (H1B, H2B, and H1D Drivers) 2.7 3.0 3.6 V

DRVDD (Data Output Drivers) 2.7 3.0 3.6 V

DVDD (Digital) 2.7 3.0 3.6 V

POWER CONSUMPTION @ 10 MHz

Power from (AVDD + TCVDD + DRVDD + DVDD) 100 mW

Power from (HVDD1 + HVDD2)

Power from (RSVDD)

2

Standby Mode (AFE_STBY and DIG_STBY = 0) 1.5 mW

VCKM MAX CLOCK RATE 12 MHz

NOTES

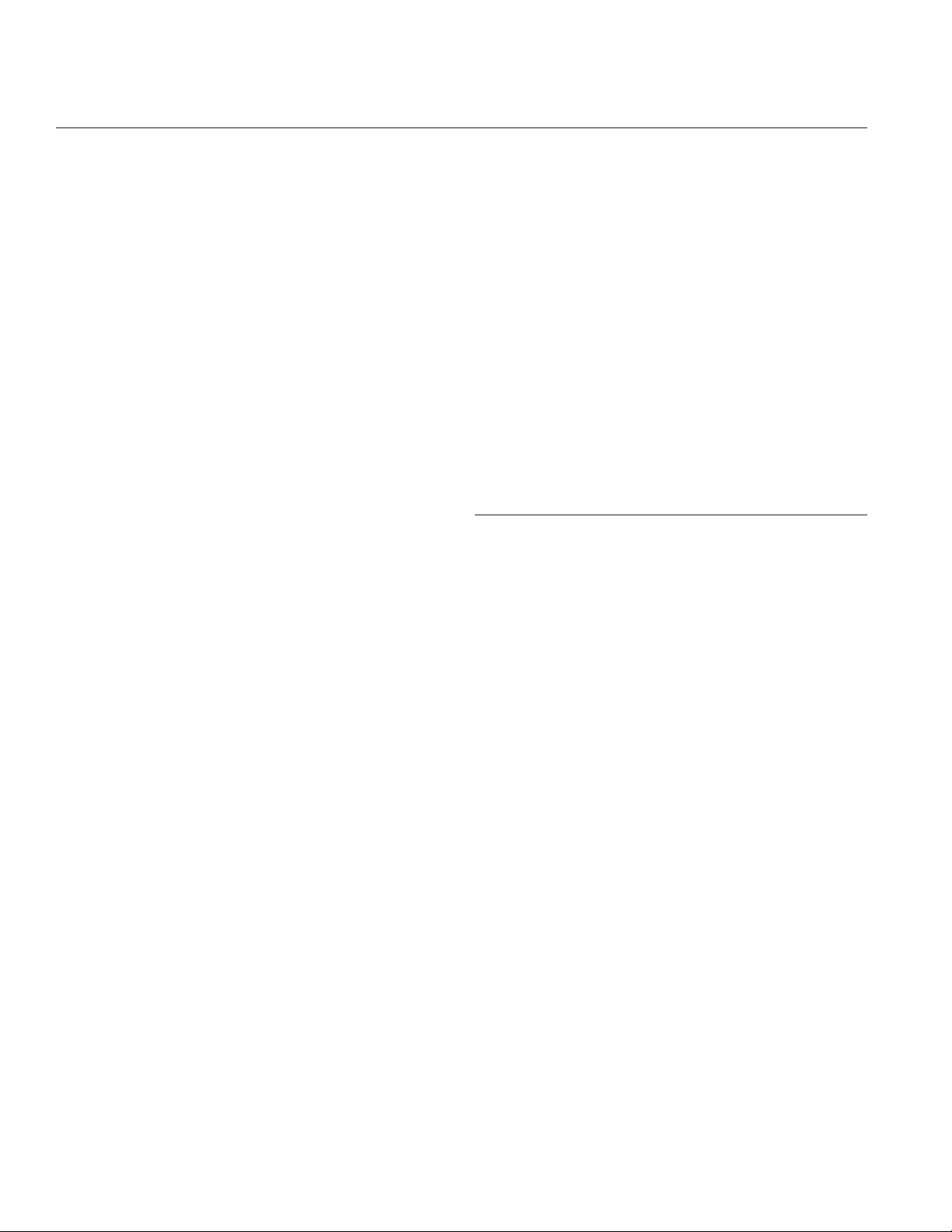

H1A H2A H1B H2B H1C H1D

30 30 30 30 30 30

1

25 mW

3mW

10pF 10pF 10pF 10pF 10pF 10pF 10pF

30pF 50pF 30pF 50pF 30pF 30pF

10pF

1

H1 (A–D) and H2 (A, B) Loads

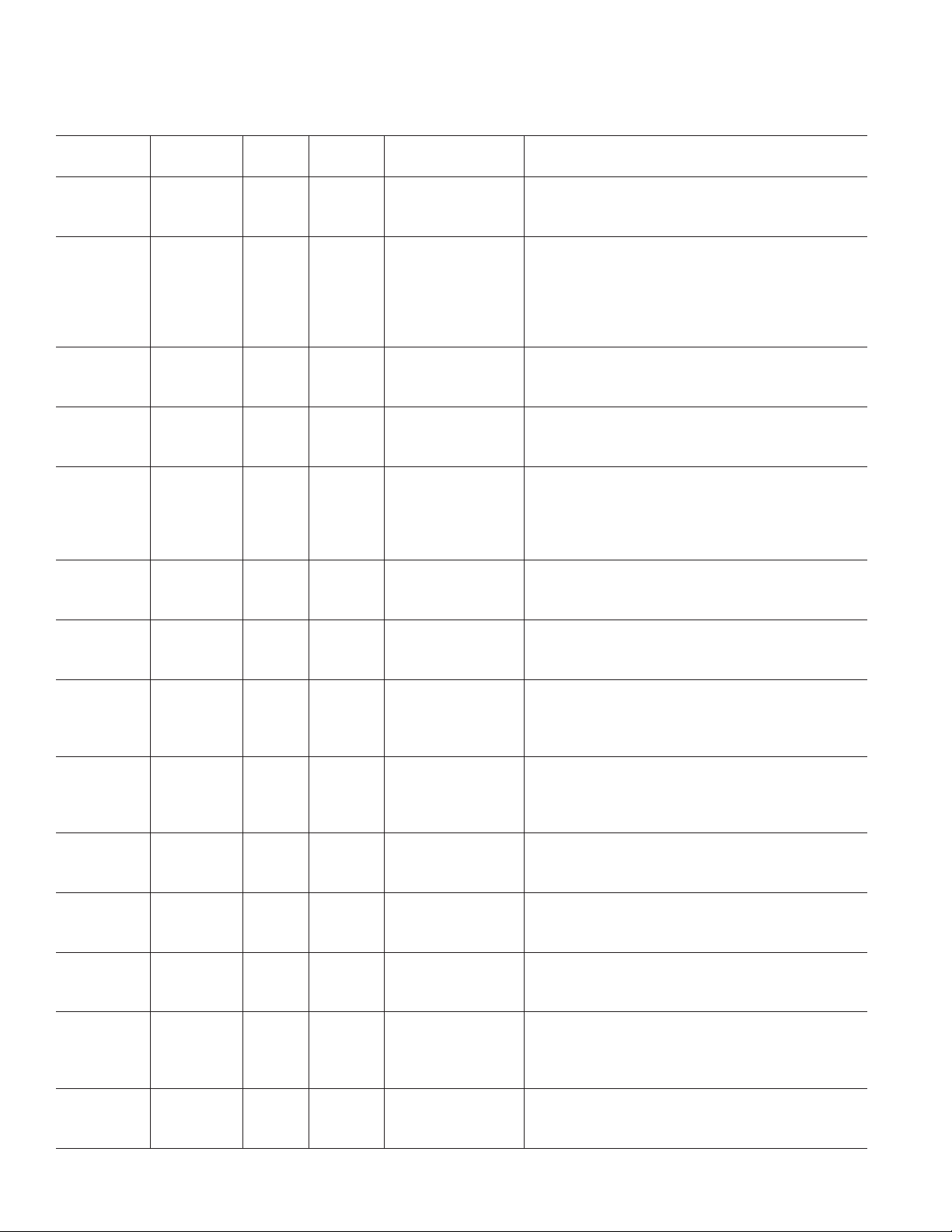

DIGITAL SPECIFICATIONS

(RSVDD = HVDD = 2.7 V to 3.6 V, –25C to +85C, unless otherwise noted.)

RS

30

10pF

2

RS Load

Parameter Symbol Min Typ Max Unit

LOGIC INPUTS (VCKM, SLD, SDA, and SCK)

High Level Input Voltage V

Low Level Input Voltage V

High Level Input Current I

Low Level Input Current I

Input Capacitance C

IH

IL

IH

IL

IN

2.1 V

0.6 V

40 µA

40 µA

10 pF

LOGIC OUTPUTS (Except H1(A–D), H2(A, B), and RS)

High Level Output Voltage @ IOH = 2 mA V

Low Level Output Voltage @ IOL = 2 mA V

OH

OL

DRVDD – 0.5 V

0.5 V

H-DRIVER OUTPUTS (H1(A–D), H2(A, B))

High Level Output Voltage @ Max Current V

Low Level Output Voltage @ Max Current V

OH

OL

DVDD – 0.5 V

0.5 V

H1(A–D) Maximum Output Current (Programmable) 12.25 mA

H2(A, B) Maximum Output Current (Programmable) 12.25 mA

Maximum Load Current 100 pF

RS-DRIVER OUTPUTS

High Level Output Voltage @ Max Current V

Low Level Output Voltage @ Max Current V

OH

OL

RSVDD – 0.5 V

0.5 V

RS Maximum Output Current (Programmable) 12.25 mA

Maximum Load Current 100 pF

Specifications subject to change without notice.

REV. 0 –3–

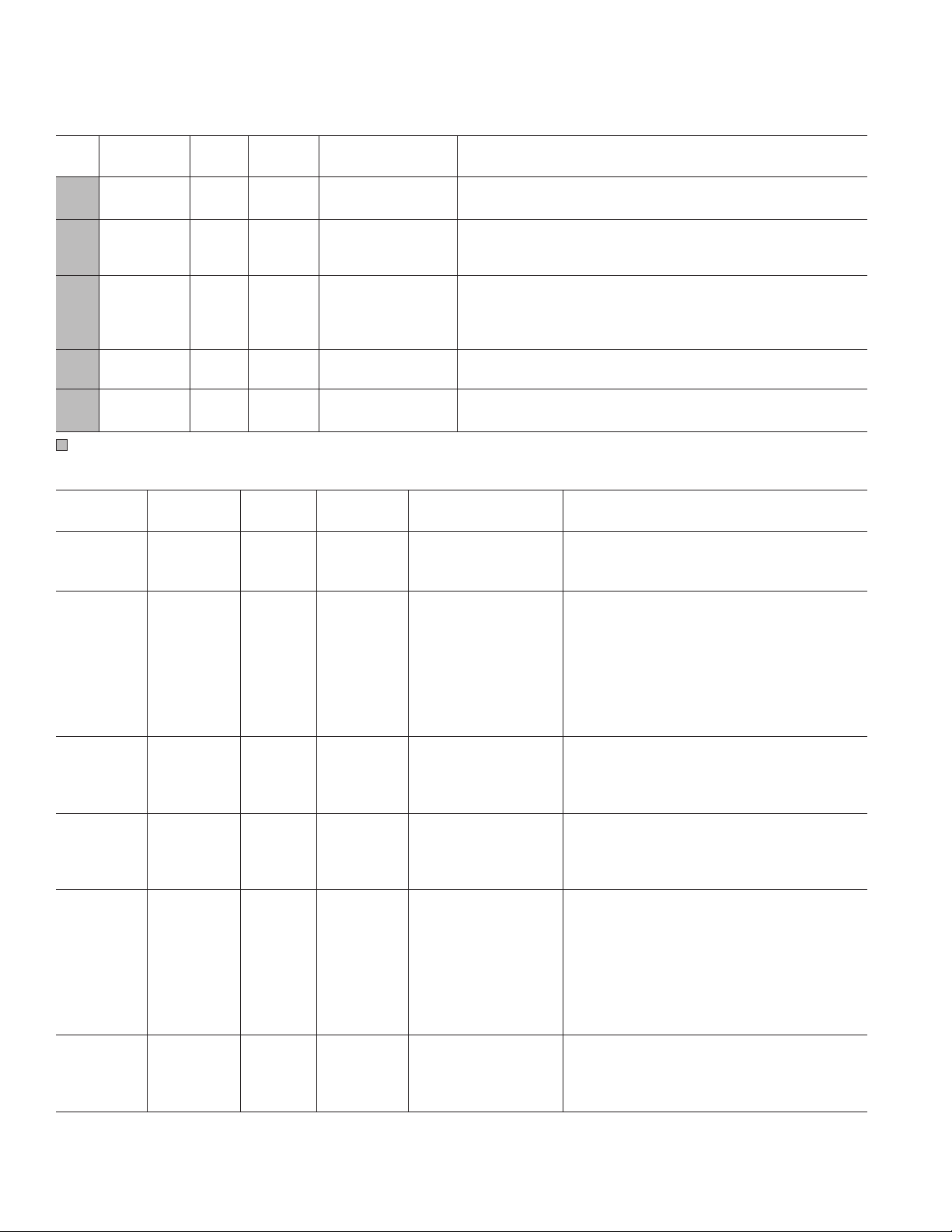

AD9937

ANALOG SPECIFICATIONS

(AVDD = 3 V, f

= 12 MHz, –25C to +85C, unless otherwise noted.)

CLI

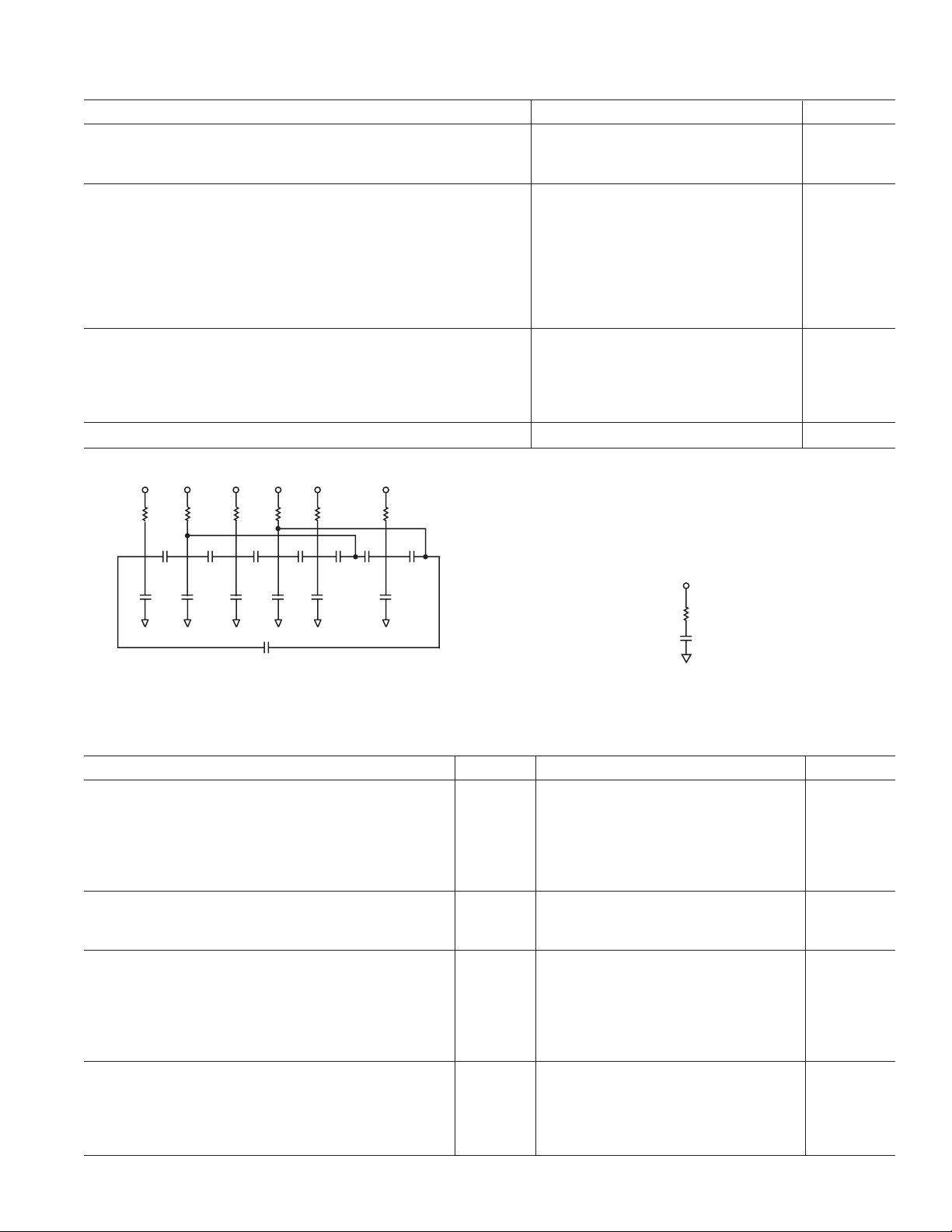

Parameter Min Typ Max Unit Notes

CDS

Allowable CCD Reset Transient 500 mV Input signal characteristics.*

Max Input Range before Saturation 1.0 V p-p

Max CCD Black Pixel Amplitude ±100 mV

VARIABLE GAIN AMPLIFIER (VGA)

Max Output Range 2.0 V p-p

Gain Control Resolution 10 Bits

Gain Monotonicity Guaranteed

Gain Range

Low Gain (VGA Code 0) 5.3 dB

Max Gain (VGA Code 1023) 40 41.1 dB

BLACK LEVEL CLAMP

Clamp Level Resolution 255 Steps

Clamp Level LSB measured at ADC output.

Min Clamp Level 0 LSB

Max Clamp Level 63.75 LSB

A/D CONVERTER

Resolution 10 Bits

Differential Nonlinearity (DNL) ± 0.4 ± 1.0 LSB

No Missing Codes Guaranteed

Full-Scale Input Voltage 2.0 V

VOLTAGE REFERENCE

Reference Top Voltage (REFT) 2.0 V

Reference Bottom Voltage (REFB) 1.0 V

SYSTEM PERFORMANCE Includes entire signal chain.

Gain Accuracy

Low Gain (VGA Code 17) 5 6 7 dB Gain = (0.035 × Code) + 5.4 dB

Max Gain (VGA Code 1023) 40.2 41.2 42.2 dB

Peak Nonlinearity, 500 mV Input Signal 0.1 % 12 dB gain applied.

Total Output Noise 0.3 LSB rms AC ground input, 6 dB gain applied.

Power Supply Rejection (PSR) 40 dB Measured with step change on supply.

*Input signal characteristics defined as follows:

500mV TYP

RESET

TRANSIENT

100mV MAX

OPTICAL

BLACK PI XEL

Specifications subject to change without notice.

1V MAX

INPUT

SIGNAL RANGE

REV. 0–4–

AD9937

TIMING SPECIFICATIONS

(CL = 20 pF, AVDD = DVDD = DRVDD = 3 V, f

= 12 MHz, unless otherwise noted.)

CLI

Parameter Symbol Min Typ Max Unit

MASTER CLOCK, VCKM

VCKM Clock Period t

CONV

83.33 ns

VCKM High/Low Pulsewidth 41.67 ns

Delay from VCKM Rising Edge to Internal Pixel Position 0 t

AFE CLAMP PULSES

CLPOB Pulsewidth

AFE SAMPLE LOCATION

1

2

1

(See Figure 13)

SHP Sample Edge to SHD Sample Edge t

VCKMDLY

S1

220Pixels

33.34 41.67 ns

9ns

DATA OUTPUTS

Output Delay from VCLK Rising Edge t

OD

9ns

Pipeline Delay from SHP/SHD Sampling (See Figure 40) 9 Cycles

SERIAL INTERFACE

Maximum SCK Frequency f

SLD to SCK Setup Time t

SCK to SLD Hold Time t

SDA Valid to SCK Rising Edge Setup t

SCK Falling Edge to SDA Valid Hold t

SCK Falling Edge to SDA Valid Read t

NOTES

1

Parameter is programmable.

2

Minimum CLPOB pulsewidth is for functional operation only. Wider typical pulses are recommended to achieve good clamp performance.

Specifications subject to change without notice.

SCLK

LS

LH

DS

DH

DV

10 MHz

10 ns

10 ns

10 ns

10 ns

10 ns

ABSOLUTE MAXIMUM RATINGS

With

Respect

PACKAGE THERMAL CHARACTERISTICS

Thermal Resistance

JA = 24.9°C/W

Parameter To Min Max Unit

AVDD AVSS –0.3 +3.9 V

TCVDD TCVSS –0.3 +3.9 V

ORDERING GUIDE

HVDD HVSS –0.3 +3.9 V

RSVDD RSVSS –0.3 +3.9 V

DVDD DVSS –0.3 +3.9 V

DRVDD DRVSS –0.3 +3.9 V

Model Range Description Option

AD9937KCP –25°C to +85°CLead Frame CP-56

Temperature Package Package

RS Output RSVSS –0.3 RSVDD + 0.3 V

H1(A–D), H2(A, B)Output HVSS –0.3 HVDD + 0.3 V

Digital Outputs DVSS –0.3 DVDD + 0.3 V

Digital Inputs DVSS –0.3 DVDD + 0.3 V

AD9937KCPRL –25°C to +85°CLead Frame CP-56

SCK, SLD, SDA DVSS –0.3 DVDD + 0.3 V

VRT, VRB AVSS –0.3 AVDD + 0.3 V

CCDIN AVSS –0.3 AVDD + 0.3 V

Junction Temperature 150 °C

Lead Temperature, 10 sec 350 °C

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD9937 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

Chip Scale

Package

(LFCSP)

Chip Scale

Package

(LFCSP)

REV. 0

–5–

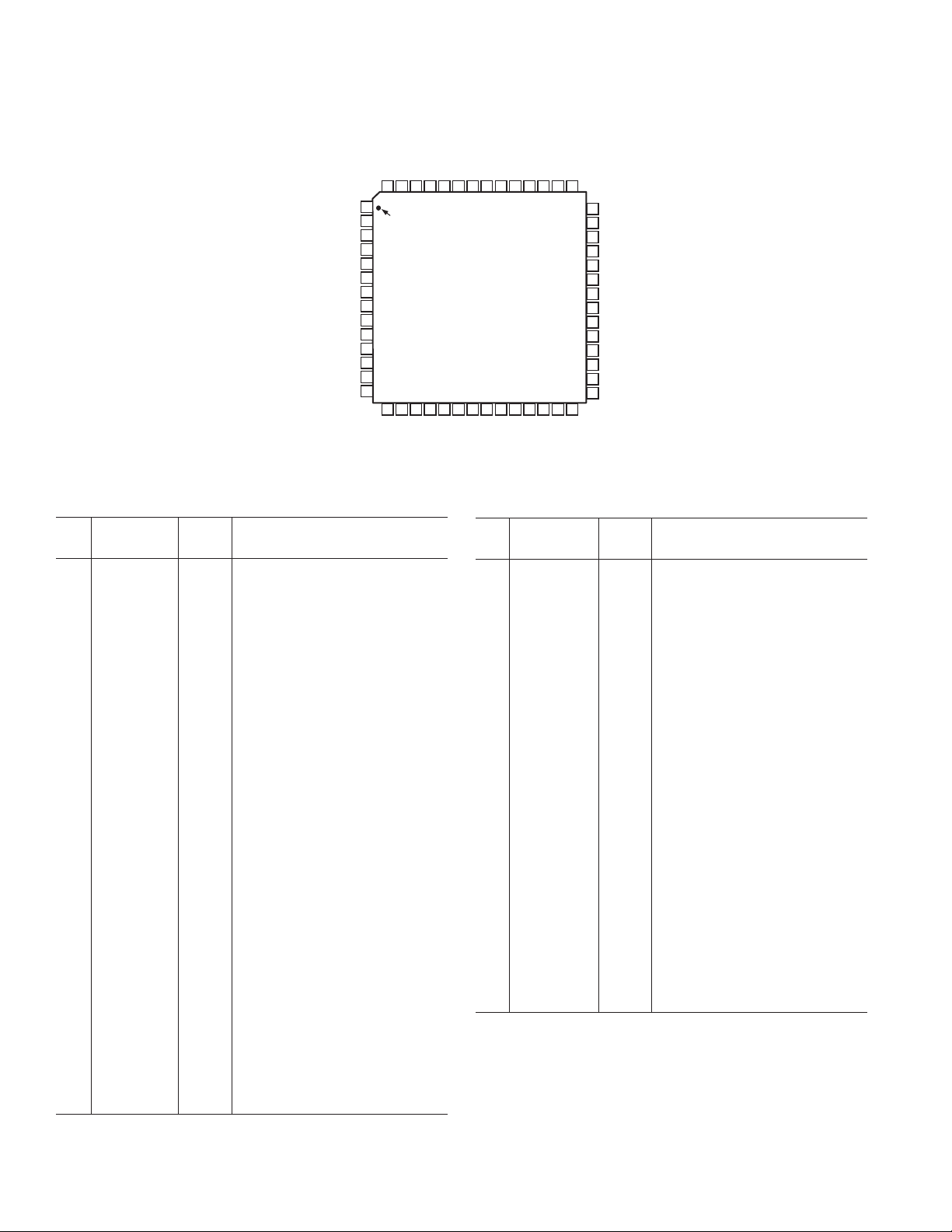

AD9937

NC

NC

D0

D1

D2

D3

DRVSS

DRVDD

D4

D5

D6

D7

D8

D9

NC = NO CONNECT

PIN CONFIGURATION

SCK

SLD

SDA

VDHDOFD

DVSS

DVD DLMV4

4950515253545556

1

PIN 1

2

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13

14

VCLK

HVDD2

H1D

HVSS2

AD9937

TOP VIEW

(Not to Scale)

H2B

H1B

HVDD1

HVSS1

TG3B

V3A/B

H2A

H1A

TG3A

RS

RSVSS

48 47 46 45 44 43

H1C

V2

2827262515 16 17 18 19 20 21 22 23 24

RSVDD

42

41

40

39

38

37

36

35

34

33

32

31

30

29

TG1B

V1A/B

TG1A

REFB

REFT

AVSS

CCDIN

AV DD

VCKM

TCVDD

TCVSS

NC

NC

NC

PIN FUNCTION DESCRIPTIONS

Pin

No. Mnemonic Type2Description

1NCNCNo Connect

2NCNCNo Connect

3D0DOData Output

4D1DOData Output

5D2DOData Output

6D3DOData Output

7 DRVSS P Data Output Driver Ground

8 DRVDD P Data Output Driver Supply

9D4DOData Output

10 D5 DO Data Output

11 D6 DO Data Output

12 D7 DO Data Output

13 D8 DO Data Output

14 D9 DO Data Output

15 VCLK DO Data Output Clock

16 HVDD2 P Horizontal Driver Supply 2

for H1D, H2B, and H1B

17 HVSS2 P Horizontal Driver Ground 2

18 H1D DO CCD Horizontal Clock 4

19 H2B DO CCD Horizontal Clock 6

20 H1B DO CCD Horizontal Clock 2

21 HVDD1 P Horizontal Driver Supply 1

for H1C, H2A, and H1A

22 HVSS1 P Horizontal Driver Ground 1

23 H1C DO CCD Horizontal Clock 3

24 H2A DO CCD Horizontal Clock 5

25 H1A DO CCD Horizontal Clock 1

26 RSVSS P RS Driver Ground

27 RS DO CCD Reset Gate Clock

28 RSVDD P RS Driver Supply

29 NC NC No Connect

30 NC NC No Connect

1

Pin

No. Mnemonic Type2Description

31 NC NC No Connect

32 TCVSS P Analog Ground for Timing Core

33 TCVDD P Analog Supply for Timing Core

34 VCKM DI

3

Reference Clock Input

35 AVDD P Analog Supply for AFE

36 CCDIN AI CCD Input Signal

37 AVSS P Analog Ground for AFE

38 REFT AO Voltage Reference Top Bypass

39 REFB AO Voltage Reference Bottom Bypass

40 TG1A DO CCD Sensor Gate Pulse 1

41 V1A/B DO CCD Vertical Transfer Clock 1

42 TG1B DO CCD Sensor Gate Pulse 2

43 V2 DO CCD Vertical Transfer Clock 2

44 TG3A DO CCD Sensor Gate Pulse 3

45 V3A/B DO CCD Vertical Transfer Clock 3

46 TG3B DO CCD Sensor Gate Pulse 4

47 V4 DO CCD Vertical Transfer Clock 4

48 LM DO Line Memory Control Pulse

49 DVDD P Digital Supply

50 DVSS P Digital Ground

51 OFD DO CCD Substrate Reset Pulse

52 HD DO Horizontal Sync Pulse

53 VD DO Vertical Sync Pulse

54 SLD DI

55 SDA DI

56 SCK DI

NOTES

1

See Figure 41 for circuit configuration.

2

AI = Analog Input, AO = Analog Output, DI = Digital Input,

DO = Digital Output, DIO = Digital Input/Output, P = Power,

NC = No Connection.

3

Schmitt trigger type input.

3

3-Wire Serial Load Pulse

3

3-Wire Serial Data

3

3-Wire Serial Clock

REV. 0–6–

AD9937

TERMINOLOGY

Differential Nonlinearity (DNL)

An ideal ADC exhibits code transitions that are exactly 1 LSB

apart. DNL is the deviation from this ideal value. Thus, every

code must have a finite width. No missing codes guaranteed to

10-bit resolution indicates that all 1024 codes must be present

over all operating conditions.

Peak Nonlinearity

Peak nonlinearity, a full signal chain specification, refers to the

peak deviation of the output of the AD9937 from a true straight

line. The point used as zero scale occurs 1/2 LSB before the first

code transition. Positive full scale is defined as a level 1 1/2 LSB

beyond the last code transition. The deviation is measured from

the middle of each particular output code to the true straight line.

The error is then expressed as a percentage of the 2 V ADC fullscale signal. The input signal is always appropriately gained up

to fill the ADC’s full-scale range.

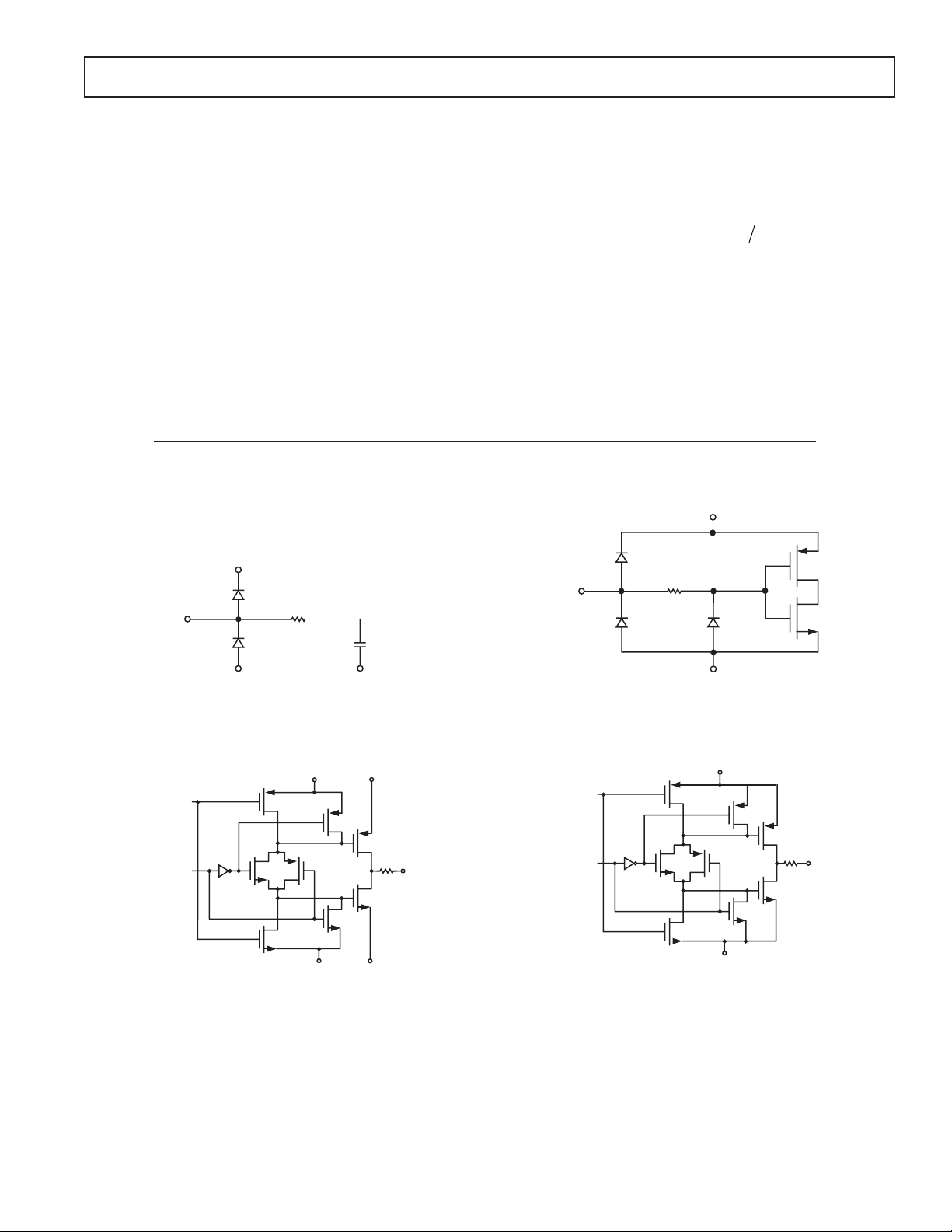

EQUIVALENT CIRCUITS

AVDD

Total Output Noise

The rms output noise is measured using histogram techniques.

The standard deviation of the ADC output codes is calculated

in LSB and represents the rms noise level of the total signal

chain at the specified gain setting. The output noise can be

converted to an equivalent voltage, using the relationship

12LSB ADC Full Scale codes

=

()

N

where N is the bit resolution of the ADC. For the AD9937, 1 LSB

is 1.95 mV.

Power Supply Rejection (PSR)

The PSR is measured with a step change applied to the supply

pins. This represents a very high frequency disturbance on the

AD9937’s power supply. The PSR specification is calculated

from the change in the data outputs for a given step change in

the supply voltage.

DVDD

330

DATA

TRISTATEOUT

R

AVSS

AVSS

Figure 1. CCDIN

DVDD

DVSS

DRVDD

DRVSS

Figure 2. Digital Data Outputs

DOUT

DVSS

Figure 3. Digital Inputs

HVDD1, HVDD2,

OR RSVDD

RS,

H1 (A–D),

H2 (A, B)

ENABLE

HVSS1, HVSS2,

OR RSVSS

OUTPUT

Figure 4. H1(A–D), H2(A, B), and RS Drivers

REV. 0

–7–

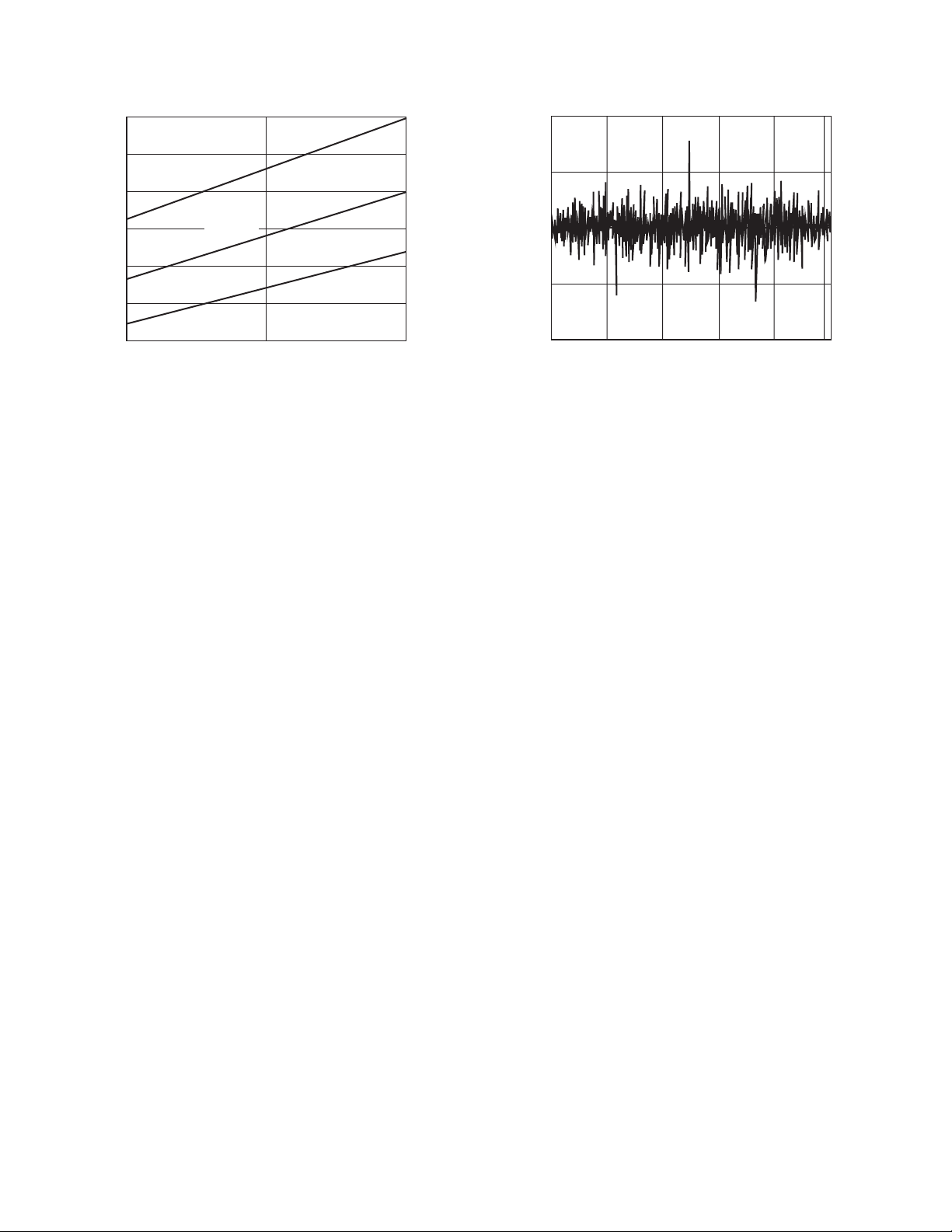

AD9937–Typical Performance Characteristics

0

160

150

140

130

120

POWER DISSIPATION – mW

110

100

81210

VDD = 3.3V

VDD = 3.0V

VDD = 2.7V

TPC 1. Power vs. Sample Rate

SAMPLE RATE – MHz

0.50

0.25

0

DNL – LSB

–0.25

–0.50

0 200

VDD = 3.0V

400 600 800 100

CODE

TPC 2. Typical DNL Performance

REV. 0–8–

AD9937

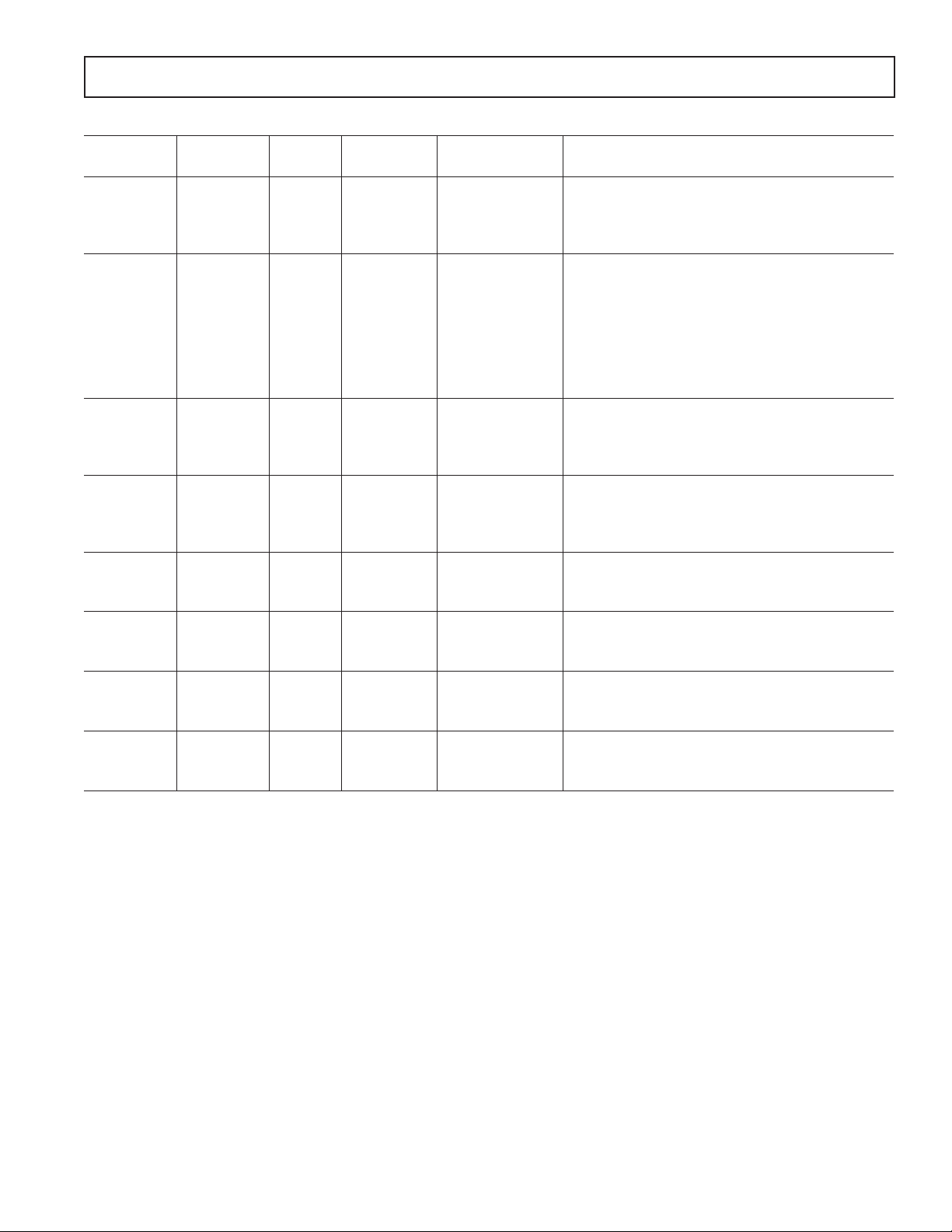

Table I. Control Register Map

Bit Bit Register

Addr Breakdown Width Default Name Function

0 (23:0) 24 0 SW_RESET Software Reset = 000000 (Reset All Registers to Default).

10 10 OUTCONT_REG Internal OUTCONT Signal Control (0 = Digital Outputs held

at fixed dc level, 1 = Normal Operation).

(23:1) 23 Unused

2(1:0) 2 0 AFE_STBY AFE Standby (0 = Full Standby, 1 = Normal Operation,

2/3 = Reference Standby).

210DIG_STBY Digital Standby (0 = Full Standby, 1 = Normal Operation).

(23:3) 21 Unused

3(7:0) 8 0x80 REFBLACK Black Clamp Level.

811BC_EN 1 = Black Clamp Enable.

910TESTMODE This register should always be set to 0.

10 1 0 TESTMODE This register should always be set to 0.

11 1 0 PBLK_LEVEL 0 = Blank to 0, 1 = Blank to Clamp Level (REFBLACK).

12 1 0 TRISTATEOUT 0 = Data Outputs are Driven, 1 = Data Outputs are Three-Stated.

13 10 RETIMEOUT_BAR 0 = Retime Data Outputs, 1 = Do Not Retime Data Outputs.

14 1 0 GRAY_ENCODE 1 = Gray Encode ADC Outputs.

(16:15) 2 0 TESTMODE This register should always be set to 0.

17 1 0 TESTMODE This register should always be set to 0.

18 1 1 TESTMODE This register should always be set to 1.

(23:19) 5 Unused

40 10 VCKM_DIVIDE VCKM Input Clock Divider (0 = VCKM, 1 = VCKM/2).

110H1BLKRETIME Retimes the H1 HBLK to Internal Clock.

210LM_INVERT LM Inversion Control (1 = Invert Programmed LM).

310TGOFD_INVERT TG and OFD Inversion Control (1 = Invert Programmed TG

and ODF).

410VDHD_INVERT VD and HD Inversion Control (1 = Invert Programmed VD

and HD; Note that Internal VD/HD Are HI Active).

510MASTER Operating Mode (0 = Slave Mode, 1 = Master Mode).

(23:6) 18 Unused

5(5:0) 6 0x00 SHDLOC SHD Sample Location.

(11:6) 6 0x24 SHPLOC SHP Sample Location.

(17:12) 6 0x00 DOUTPHASE Data Output [9:0] and VCLK Phase Adjustment.

(19:18) 2 0x00 DOUT_DELAY Data Output Clock Selection (0 = No Delay, 1 = ~4 ns, 2 = ~8 ns,

3 = ~12 ns).

20 1 0 VCLKMASK VCLK Masking Control (1 = Mask).

21 1 1 VCLK_INVERT 1 = Invert VCLK.

22 1 0 DTEST 1 = Internal Digital Signal Test Mode.

23 1 – Unused

6(5:0) 6 0x00 H1POSLOC H1 Positive Edge Location.

(11:6) 6 0x20 H1NEGLOC H1 Negative Edge Location.

(17:12) 6 0x00 RSPOSLOC RS Positive Edge Location.

(23:18) 6 0x10 RSNEGLOC RS Negative Edge Location.

7(2:0) 3 4 H1DRV H1A/B/C/D Drive Strength (0 = OFF, 1 = 1.75 mA, 2 = 3.5 mA,

3 = 5.25 mA, 4 = 7 mA, 5 = 8.75 mA, 6 = 10.5 mA, 7 = 12.25 mA).

(5:3) 3 4 H2DRV H2A/B Drive Strength (see H1DRV).

(8:6) 3 4 RSDRV RS Drive Strength (see H1DRV).

(23:9) 15 Unused

(23:1) 23 Unused

REV. 0

–9–

AD9937

Table I. Control Register Map (continued)

Bit Bit Register

Addr Breakdown Width Default Name Function

80 10 MODE Mode Control Bit. (0 = Mode A, 1 = Mode B)

(23:1) 23 Unused

90 11 SPEN Single Pulse (SP) Output Enable.

(4:1) 4 0x9 SPLOGIC Single Pulse Logic Setting (0 = OR, 1 = AND).

(23:5) 19 Unused

10 0 1 1 OFDEN OFD Output Enable Control (0 = Disable, 1 = Enable).

(11:1) 11 0x7FF OFDNUM Total Number of OFD Pulses per Field.

12 1 1 TGEN TG Output Enable Control (0 = Disable, 1 = Enable).

(23:13) 11 Unused

11 (11:0) 12 4095 OFDHPTOG1 High Precision OFD Toggle Position 1.

(23:12) 12 4095 OFDHPTOG2 High Precision OFD Toggle Position 2.

12 (9:0) 10 0x000 VGAGAIN VGA Gain Control.

(23:10) 14 Unused

Denotes VD synchronous registers (control addresses 8, 9, 10, 11, and 12).

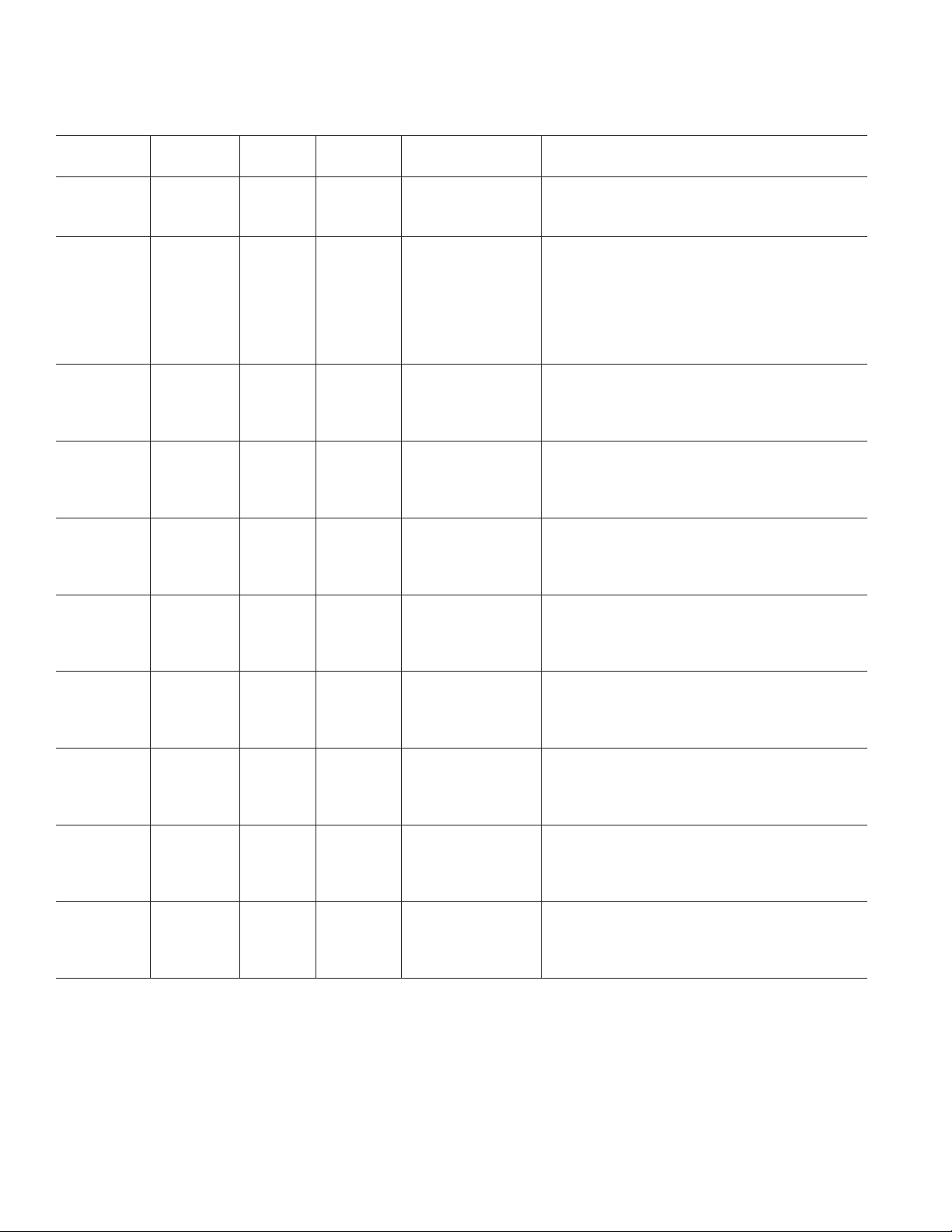

Table II. VTP Sequence System Register Map (Addr 0x14)

Bit Bit Register

Addr Breakdown Width Default Name Function

VTP_Reg(0) (11:0) 12 ENDADDRESS Sub Word End Address

(23:12) 12 STARTADDRESS Sub Word Start Address

(31:24) 8 VTP_Reg_Addr System Register Address 0x14

VTP_Reg(1) (8:0) 9 279 VTPLEN_0 VTP0: Length between Repetitions

(17:9) 9 75 V1TOG1_0 VTP0: V1 Toggle Position 1

(26:18) 9 250 V1TOG2_0 VTP0: V1 Toggle Position 2

27 1 1 V1POL_0 VTP0: V1 Start Polarity

28 1 0 V2POL_0 VTP0: V2 Start Polarity

29 1 0 V3POL_0 VTP0: V3 Start Polarity

30 1 1 V4POL_0 VTP0: V4 Start Polarity

31 1 Unused

VTP_Reg(2) (8:0) 9 40 V2TOG1_0 VTP0: V2 Toggle Position 1

(17:9) 9 145 V2TOG2_0 VTP0: V2 Toggle Position 2

(26:18) 9 110 V3TOG1_0 VTP0: V3 Toggle Position 1

(31:27) 5 Unused

VTP_Reg(3) (8:0) 9 215 V3TOG2_0 VTP0: V3 Toggle Position 2

(17:9) 9 5 V4TOG1_0 VTP0: V4 Toggle Position 1

(26:18) 9 180 V4TOG2_0 VTP0: V4 Toggle Position 2

(31:27) 5 Unused

VTP_Reg(4) (8:0) 9 99 VTPLEN_1 VTP1: Length between Repetitions

(17:9) 9 29 V1TOG1_1 VTP1: V1 Toggle Position 1

(26:18) 9 99 V1TOG2_1 VTP1: V1 Toggle Position 2

27 1 1 V1POL_1 VTP1: V1 Start Polarity

28 1 0 V2POL_1 VTP1: V2 Start Polarity

29 1 0 V3POL_1 VTP1: V3 Start Polarity

30 1 1 V4POL_1 VTP1: V4 Start Polarity

31 1 Unused

VTP_Reg(5) (8:0) 9 15 V2TOG1_1 VTP1: V2 Toggle Position 1

(17:9) 9 57 V2TOG2_1 VTP1: V2 Toggle Position 2

(26:18) 9 43 V3TOG1_1 VTP1: V3 Toggle Position 1

(31:27) 5 Unused

REV. 0–10–

AD9937

Table II. VTP Sequence System Register Map (Addr 0x14) (continued)

Bit Bit Register

Addr Breakdown Width Default Name Function

VTP_Reg(6) (8:0) 9 85 V3TOG2_1 VTP1: V3 Toggle Position 2

(17:9) 9 1 V4TOG1_1 VTP1: V4 Toggle Position 1

(26:18) 9 71 V4TOG2_1 VTP1: V4 Toggle Position 2

(31:27) 5 Unused

VTP_Reg(7) (8:0) 9 99 VTPLEN_2 VTP2: Length between Repetitions

(17:9) 9 29 V1TOG1_2 VTP2: V1 Toggle Position 1

(26:18) 9 99 V1TOG2_2 VTP2: V1 Toggle Position 2

27 1 1 V1POL_2 VTP2: V1 Start Polarity

28 1 0 V2POL_2 VTP2: V2 Start Polarity

29 1 0 V3POL_2 VTP2: V3 Start Polarity

30 1 1 V4POL_2 VTP2: V4 Start Polarity

31 1 Unused

VTP_Reg(8) (8:0) 9 15 V2TOG1_2 VTP2: V2 Toggle Position 1

(17:9) 9 57 V2TOG2_2 VTP2: V2 Toggle Position 2

(26:18) 9 43 V3TOG1_2 VTP2: V3 Toggle Position 1

(31:27) 5 Unused

VTP_Reg(9) (8:0) 9 85 V3TOG2_2 VTP2: V3 Toggle Position 2

(17:9) 9 1 V4TOG1_2 VTP2: V4 Toggle Position 1

(26:18) 9 71 V4TOG2_2 VTP2: V4 Toggle Position 2

(31:27) 5 Unused

VTP_Reg(10) (11:0) 12 40 SP1TOG1 SP1 Toggle Position 1 (V1A/V1B)

(23:12) 12 410 SP1TOG2 SP1 Toggle Position 2 (V1A/V1B)

(31:24) 8 Unused

VTP_Reg(11) (11:0) 12 490 SP2TOG1 SP2 Toggle Position 1 (V2)

(23:12) 12 780 SP2TOG2 SP2 Toggle Position 2 (V2)

(31:24) 8 Unused

VTP_Reg(12) (11:0) 12 80 SP3TOG1 SP3 Toggle Position 1 (V3A/V3B)

(23:12) 12 360 SP3TOG2 SP3 Toggle Position 2 (V3A/V3B)

(31:24) 8 Unused

VTP_Reg(13) (11:0) 12 450 SP4TOG1 SP4 Toggle Position 1 (V4)

(23:12) 12 820 SP4TOG2 SP4 Toggle Position 2 (V4)

(31:24) 8 Unused

REV. 0

–11–

AD9937

Table III. H/LM System Register Map (Addr 0x15)

Bit Bit Register

Addr Breakdown Width Default Name Function

HLM_Reg(0) (11:0) 12 ENDADDRESS Sub Word End Address

(23:12) 12 STARTADDRESS Sub Word Start Address

(31:24) 8 HLM_Reg_Addr System Register Address 0x15

HLM_Reg(1) 0 1 0 H1APOL H1A Special H-Pattern Start Polarity

110H1BPOL H1B Special H-Pattern Start Polarity

211H1CPOL H1C Special H-Pattern Start Polarity

311H1DPOL H1D Special H-Pattern Start Polarity

410H2APOL H2A Special H-Pattern Start Polarity

510H2BPOL H2B Special H-Pattern Start Polarity

(31:6) 26 Unused

HLM_Reg(2) (5:0) 6 0x00 SPH1A1 H1A Special H-Pattern during LM Repetition 1

(11:6) 6 0x04 SPH1B1 H1B Special H-Pattern during LM Repetition 1

(17:12) 6 0x01 SPH1C1 H1C Special H-Pattern during LM Repetition 1

(31:18) 14 Unused

HLM_Reg(3) (5:0) 6 0x07 SPH1D1 H1D Special H-Pattern during LM Repetition 1

(11:6) 6 0x08 SPH2A1 H2A Special H-Pattern during LM Repetition 1

(17:12) 6 0x22 SPH2B1 H2B Special H-Pattern during LM Repetition 1

(31:18) 14 Unused

HLM_Reg(4) (5:0) 6 0x34 SPH1A2 H1A Special H-Pattern during LM Repetition 2

(11:6) 6 0x34 SPH1B2 H1B Special H-Pattern during LM Repetition 2

(17:12) 6 0x04 SPH1C2 H1C Special H-Pattern during LM Repetition 2

(31:18) 14 Unused

HLM_Reg(5) (5:0) 6 0x04 SPH1D2 H1D Special H-Pattern during LM Repetition 2

(11:6) 6 0x3A SPH2A2 H2A Special H-Pattern during LM Repetition 2

(17:12) 6 0x0B SPH2B2 H2B Special H-Pattern during LM Repetition 2

(31:18) 14 Unused

HLM_Reg(6) (5:0) 6 0x3D SPH1A3 H1A Special H-Pattern during LM Repetition 3

(11:6) 6 0x3F SPH1B3 H1B Special H-Pattern during LM Repetition 3

(17:12) 6 0x3C SPH1C3 H1C Special H-Pattern during LM Repetition 3

(31:18) 14 Unused

HLM_Reg(7) (5:0) 6 0x3C SPH1D3 H1D Special H-Pattern during LM Repetition 3

(11:6) 6 0x03 SPH2A2 H2A Special H-Pattern during LM Repetition 3

(17:12) 6 0x02 SPH2B3 H2B Special H-Pattern during LM Repetition 3

(31:18) 14 Unused

HLM_Reg(8) (7:0) 8 99 LMLEN0 LM Pattern 0 (LM0): LM Counter Length

(15:8) 8 5 LMTOG1_0 LM Pattern 0 (LM0): Toggle Position 1

(23:16) 8 55 LMTOG2_0 LM Pattern 0 (LM0): Toggle Position 2

(31:24) 8 87 SPHSTART0 LM Pattern 0 (LM0): Special H Pulse Start Position

HLM_Reg(9) (7:0) 8 29 LMLEN1 LM Pattern 1 (LM1): LM Counter Length

(15:8) 8 2 LMTOG1_1 LM Pattern 1 (LM1): Toggle Position 1

(23:16) 8 26 LMTOG2_1 LM Pattern 1 (LM1): Toggle Position 2

(31:24) 8 0 SPHSTART1 LM Pattern 1 (LM1): Special H Pulse Start Position

REV. 0–12–

Table IV. Shutter System Register Map (Addr 0x16)

Bit Bit Register

Addr Breakdown Width Default Name Function

Shut_Reg(0) (11:0) 12 ENDADDRESS Sub Word End Address

(23:12) 12 STARTADDRESS Sub Word Start Address

(31:24) 8 SHUT_Reg_Addr System Register Address 0x16

Shut_Reg(1) (11:0) 12 80 TGTOG1_0 TG0 Pulse Toggle Position 1

(23:12) 12 370 TGTOG2_0 TG0 Pulse Toggle Position 2

(31:24) 8 Unused

Shut_Reg(2) (11:0) 12 490 TGTOG1_1 TG1 Pulse Toggle Position 1

(23:12) 12 780 TGTOG2_1 TG1 Pulse Toggle Position 2

(31:24) 8 Unused

Shut_Reg(3) (11:0) 12 540 OFDTOG1_0 OFD0 Pulse Toggle Position 1

(23:12) 12 720 OFDTOG2_0 OFD0 Pulse Toggle Position 2

(31:24) 8 Unused

Shut_Reg(4) (11:0) 12 830 OFDTOG1_1 OFD1 Pulse Toggle Position 1

(23:12) 12 860 OFDTOG2_1 OFD1 Pulse Toggle Position 2

(31:24) 8 Unused

AD9937

REV. 0

–13–

AD9937

Table V. Mode_A (Addr 0x17)

Bit Bit Register

Addr Breakdown Width Default Name Function

Mode_Reg(0) (11:0) 12 ENDADDRESS Sub Word End Address

(23:12) 12 STARTADDRESS Sub Word Start Address

(31:24) 8 MODE_Reg_Addr Mode Register Address (Mode A = Addr 0x17)

Mode_Reg(1) (6:0) 7 0 TGACTLINE TG Active Line

7 10TGPATSEL0 TG1A/B Pattern Selector (0 = TG0, 1 = TG1)

8 11TGPATSEL1 TG3A/B Pattern Selector (0 = TG0, 1 = TG1)

(12:9) 4 0xA TGMASK TG Masking Control (1 = Mask)

13 1 0 OFDPATSEL OFD Pattern Selection (0 = OFD0, 1 = OFD1)

(31:14) 18 Unused

Mode_Reg(2) (11:0) 12 831 HDTOG1 HD Toggle Position 1

(23:12) 12 866 HDTOG2 HD Toggle Position 2

(31:24) 8 Unused

Mode_Reg(3) (11:0) 12 4095 HDTOG3 HD Toggle Position 3

(23:12) 12 4095 HDTOG4 HD Toggle Position 4

(31:24) 8 Unused

Mode_Reg(4) (11:0) 12 2339 HDLASTLEN HD Last Line Length

(22:12) 11 262 VDLEN VD Field Length

(26:23) 4 0 VDTOG1 VD Toggle Position 1

(30:27) 4 4 VDTOG2 VD Toggle Position 2

31 1 Unused

Mode_Reg(5) (11:0) 12 1543 CLPOBTOG1 CLPOB Toggle Position 1

(23:12) 12 1557 CLPOBTOG2 CLPOB Toggle Position 2

(31:24) 8 Unused

Mode_Reg(6) (11:0) 12 4095 CLPOBTOG3 CLPOB Toggle Position 3

(23:12) 12 4095 CLPOBTOG4 CLPOB Toggle Position 4

(31:24) 8 Unused

Mode_Reg(7) (11:0) 12 0 HBLKTOG1 HBLK Toggle Position 1

(23:12) 12 869 HBLKTOG2 HBLK Toggle Position 2

24 1 0 H1TOG12POL H1 Polarity between Toggle Positions 1 and 2

(31:25) 7 Unused

Mode_Reg(8) (11:0) 12 4095 HBLKTOG3 HBLK Toggle Position 3

(23:12) 12 4095 HBLKTOG4 HBLK Toggle Position 4

24 1 0 H1TOG34POL H1 Polarity between Toggle Positions 3 and 4

(31:25) 7 Unused

Mode_Reg(9) (11:0) 12 6 PBLKTOG1 PBLK Toggle Position 1

(23:12) 12 878 PBLKTOG2 PBLK Toggle Position 2

(31:24) 8 Unused

Mode_Reg(10) (11:0) 12 4095 PBLKTOG3 PBLK Toggle Position 3

(23:12) 12 4095 PBLKTOG4 PBLK Toggle Position 4

(31:24) 8 Unused

Mode_Reg(11) (10:0) 11 255 PBLKSTART PBLK Start Position

(21:11) 11 3 PBLKSTOP PBLK Stop Position

(31:22) 10 Unused

Mode_Reg(12) (10:0) 11 0 HMASKSTART Vertical H Masking Start Position

(21:11) 11 1 HMASKSTOP Vertical H Masking Stop Position

22 1 0 H1MASKPOL Masking Polarity for H1 during Vertical Blanking Period

(31:23) 9 Unused

Mode_Reg(13) (11:0) 12 550 LMSTART0 LM Counter Start Position 1

(23:12) 12 4095 LMSTART1 LM Counter Start Position 2

(31:24) 8 Unused

REV. 0–14–

Loading...

Loading...