with 12-Bit DAC

AD9914

Rev. PrJ

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

Trad emarks and registered trademarks are the property of their respective owners.

Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved.

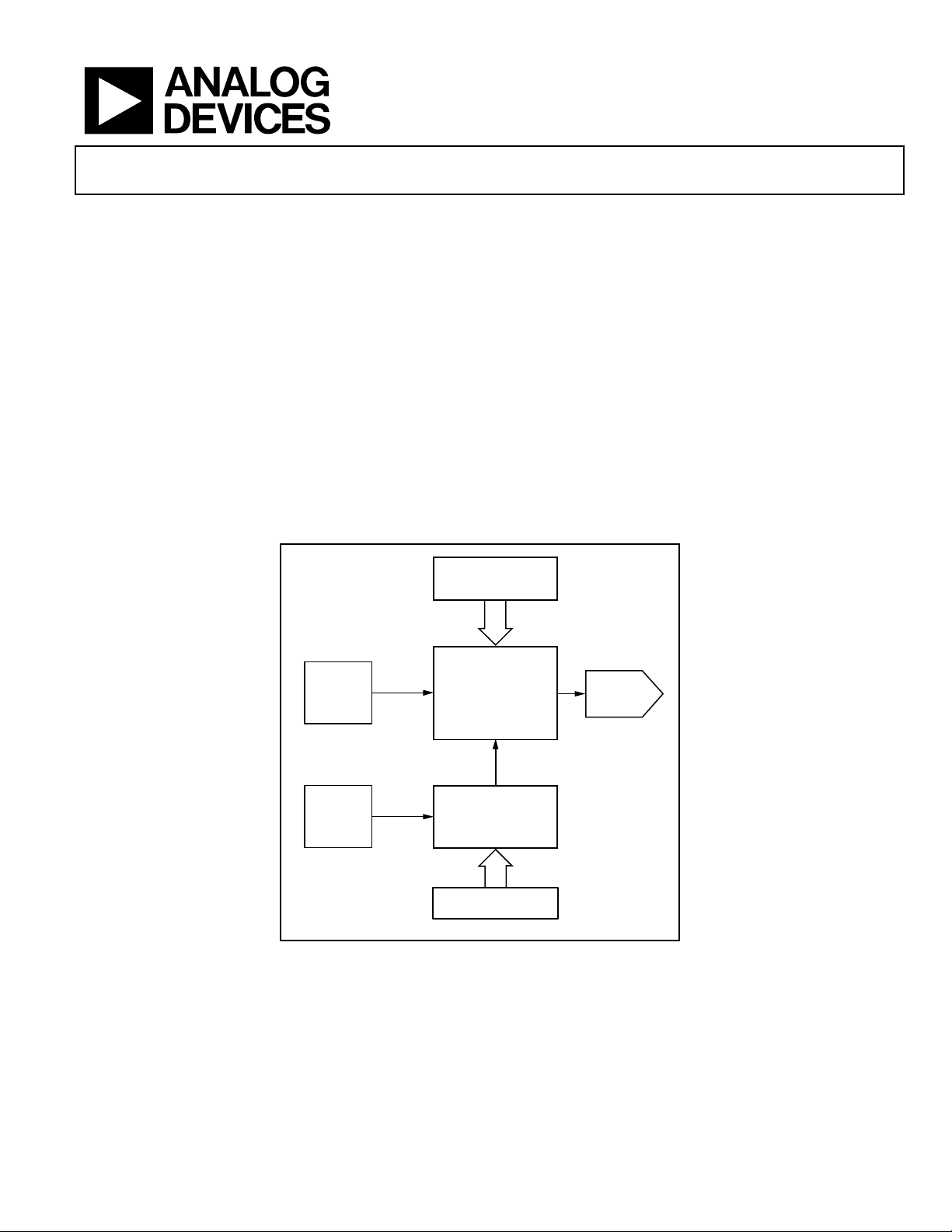

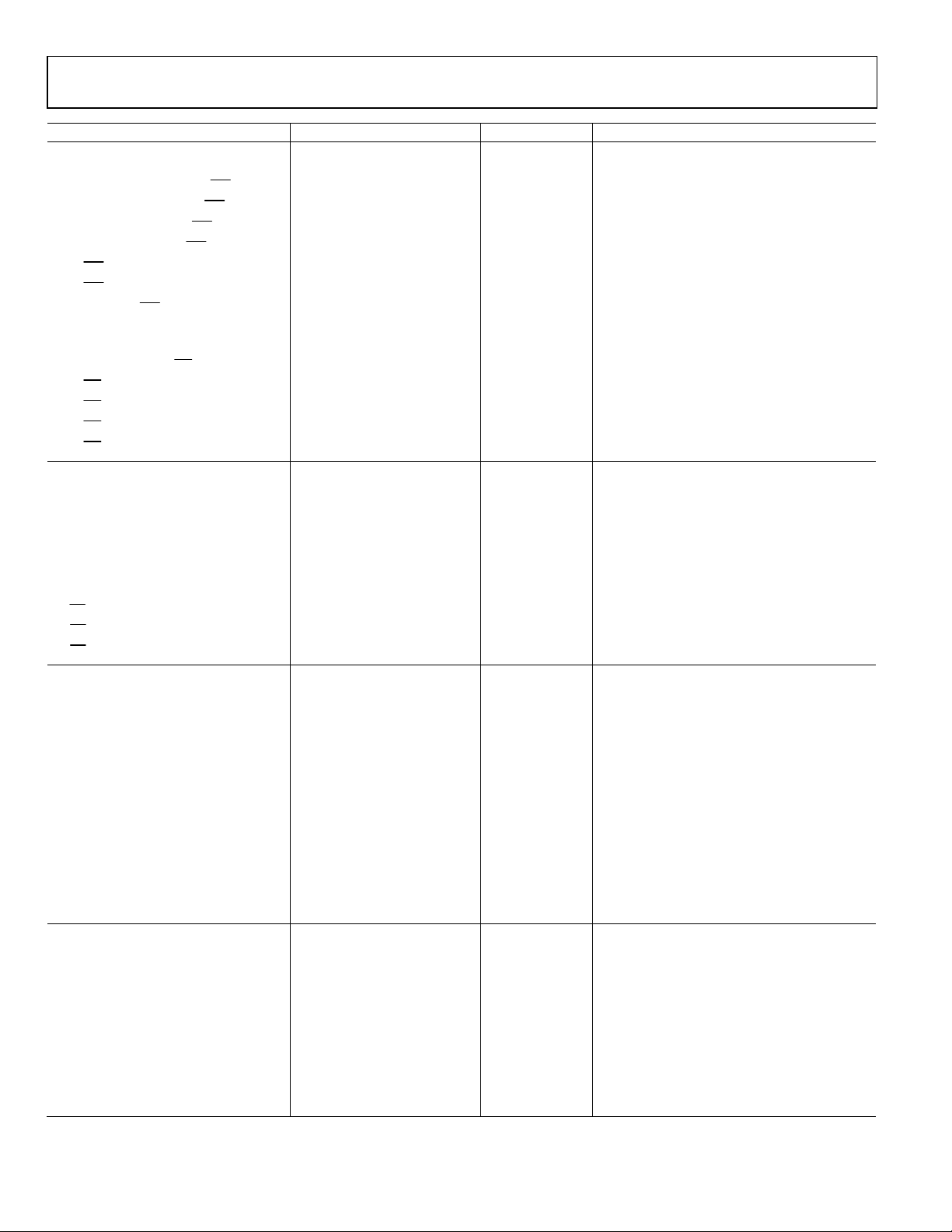

12-BIT DAC

3.5GSPS DDS CORE

TIMINGAND CONTROL

10836-001

AD9914

HIGH SPEE D P ARALLEL

MODULATION

PORT

LINEAR

SWEEP

BLOCK

SERIAL O R P ARALLEL

DATA PORT

REF CLK

MULTIPLIER

Preliminary Technical Data

FEATURES

3.5 GSPS internal clock speed

Integrated 12-bit DAC

Frequency tuning resolution to 271 pHz

16-bit phase tuning resolution

12-bit amplitude scaling

Programmable modulus

Automatic linear and nonlinear frequency sweeping

capability

32-bit parallel datapath interface

8 frequency/phase offset profiles

Phase noise −128 dBc/Hz (10 kHz offset at 1396 MHz)

Wide band SFDR <−50 dBc

Serial or parallel I/O control

1.8 V/3.3 V power supplies

FUNCTIONAL BLOCK DIAGRAM

3.5 GSPS Direct Digital Synthesizer

Software and hardware controlled power-down

88-lead LFCSP package

PLL REF CLK multiplier

Phase modulation capability

Amplitude modulation capability

Multichip synchronization

APPLICATIONS

Agile LO frequency synthesis

Programmable clock generator

FM chirp source for radar and scanning systems

Test and measurement equipment

Acousto-optic device drivers

Polar modulator

Fast frequency hopping

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

AD9914 Preliminary Technical Data

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 3

Specifications ..................................................................................... 4

DC Specifications ......................................................................... 4

AC Specifications .......................................................................... 5

Absolute Maximum Ratings ............................................................ 8

Thermal Performance .................................................................. 8

ESD Caution .................................................................................. 8

Pin Configuration and Function Descriptions ............................. 9

Typical Performance Characteristics ........................................... 12

Equivalent Circuits ......................................................................... 16

Theory of Operation ...................................................................... 17

Single Tone Mode ....................................................................... 17

Profile Modulation Mode .......................................................... 17

Digital Ramp Modulation Mode .............................................. 17

Parallel Data Port Modulation Mode ....................................... 17

Programmable Modulus Mode ................................................. 17

Functional Block Detail ................................................................. 19

DDS Core ..................................................................................... 19

12-Bit DAC Output .................................................................... 20

DAC Calibration Output ........................................................... 20

Reconstruction Filter ................................................................. 20

Clock Input (REF_CLK/

PLL Lock Indication .................................................................. 22

Output Shift Keying (OSK) ....................................................... 22

Digital Ramp Generator (DRG) ............................................... 23

Power-Down Control ................................................................ 27

Programming and Function pins ................................................. 28

Serial Programming ....................................................................... 29

Control Interface—Serial I/O ................................................... 29

General Serial I/O Operation ................................................... 29

Instruction Byte .......................................................................... 29

Serial I/O Port Pin Descriptions .............................................. 29

Serial I/O Timing Diagrams ..................................................... 30

MSB/LSB Transfers .................................................................... 30

Parallel Programming .................................................................... 31

Register Map and Bit Descriptions .............................................. 32

Outline Dimensions ....................................................................... 38

Ordering Guide .......................................................................... 38

REF_CLK

) ........................................ 21

Rev. PrJ | Page 2 of 38

Preliminary Technical Data AD9914

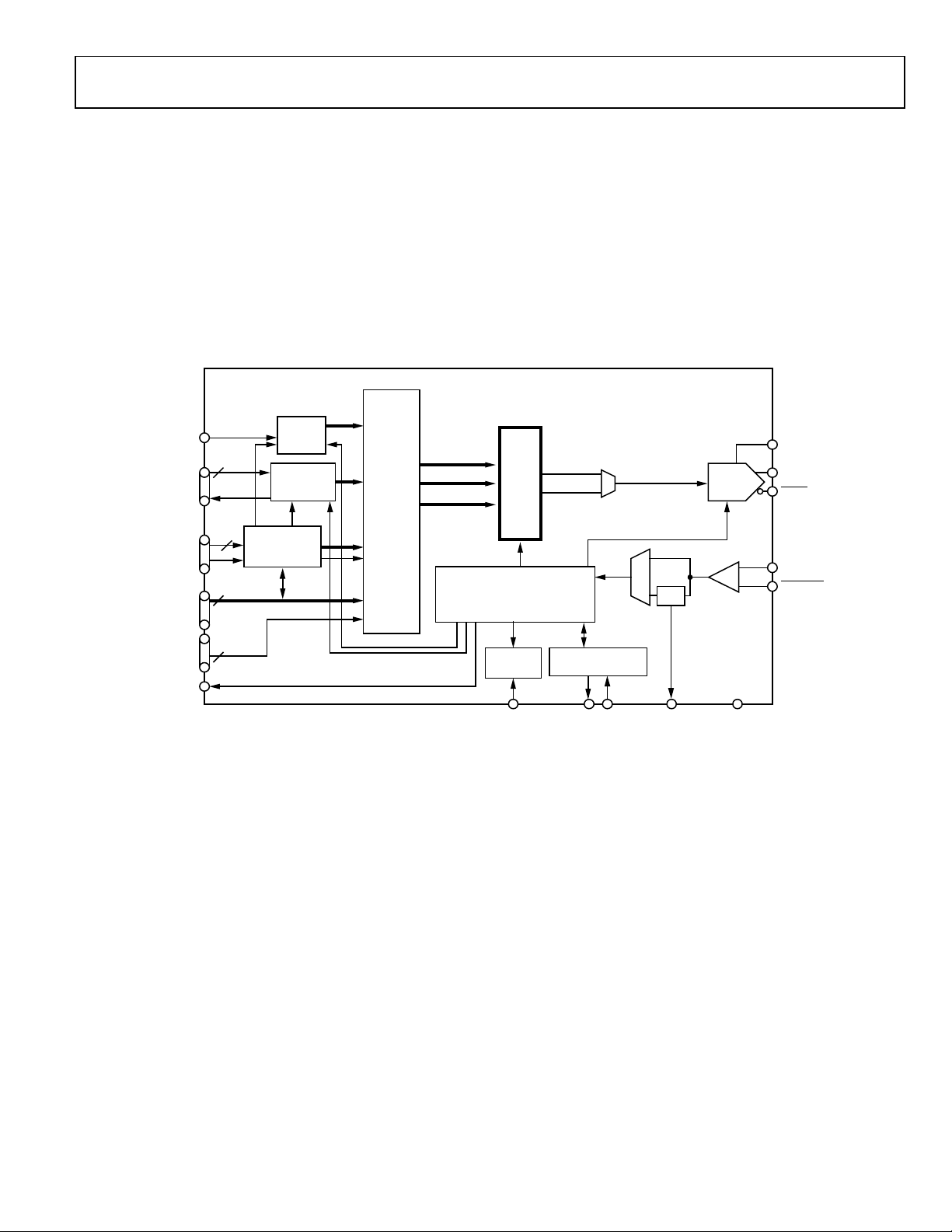

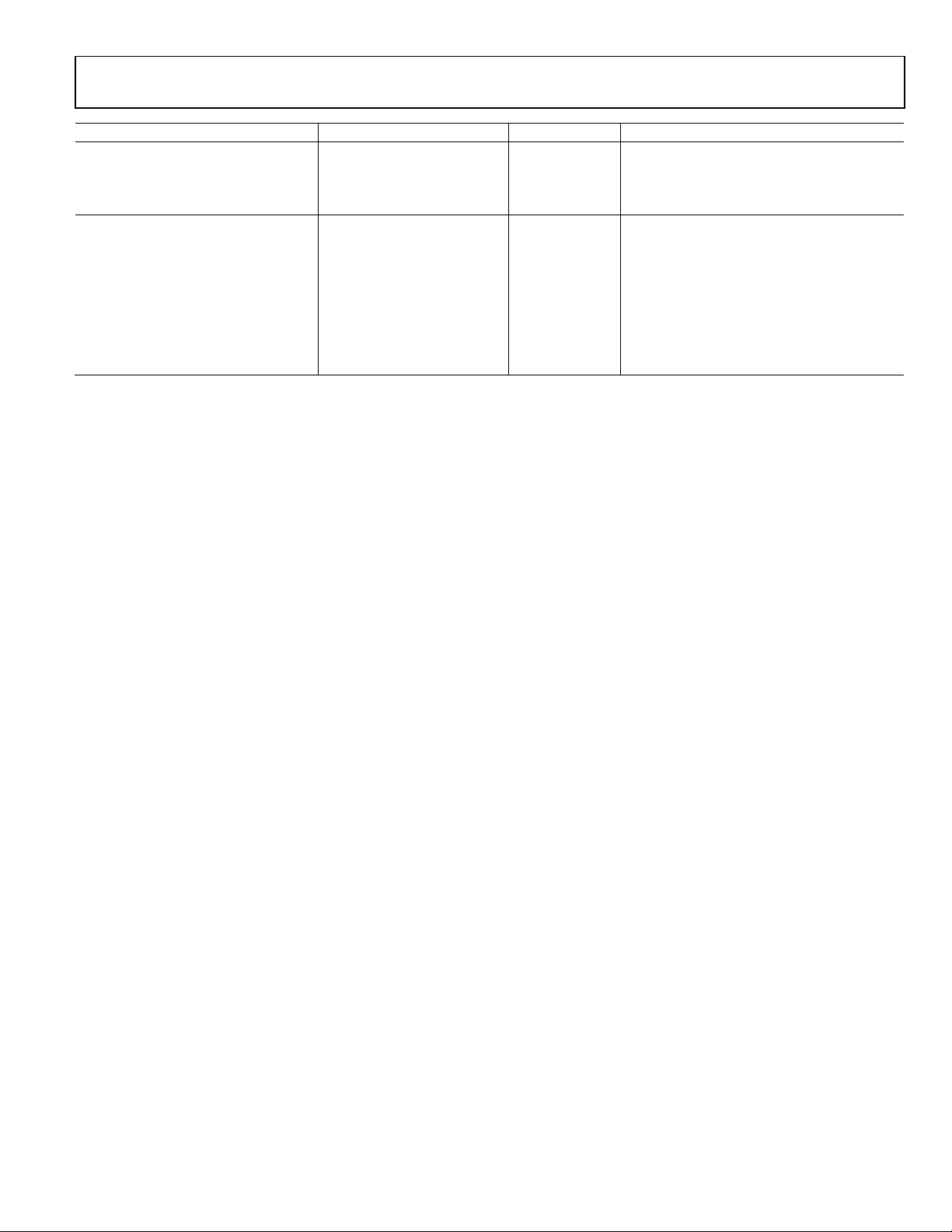

10836-002

32

F0 – F3

D0 – D31

PROFILES[2:0]

I/O_UPDATE

POWER-

DOWN

CONTROL

EXT_PWR_DWN

DAC_RSET

AOUT

AOUT

OSK

DROVER

DRCTL

DRHOLD

SYNC_CLK

A

θ

CLOCK

AMPLIT UDE ( A)

FREQUENCY (ω)

PHASE (θ)

DIGITAL

RAMP

GENERATOR

2

4

MULTICHIP

SYNCHRONIZATION

SYSCLK

PLL

REF_CLK

REF_CLK

AD9914

OUTPUT

SHIFT

KEYING

DATA

ROUTE

AND

PARTITION

CONTROL

3

INTERNAL CLOCK TIMI NG

AND CONTROL

ω

Acos (ωt + θ)

Asin (ωt + θ)

SYNC_OUT

SYNC_IN

LOOP_FILTER

MASTER_RESET

DAC

12-BIT

DDS

INTERNAL

PROGRAMMING

REGISTERS

GENERAL DESCRIPTION

The AD9914 is a direct digital synthesizer (DDS) featuring a

12-bit DAC. The AD9914 uses advanced DDS technology,

coupled with an internal high speed, high performance DAC

to form a digitally programmable, complete high frequency

synthesizer capable of generating a frequency-agile analog

output sinusoidal waveform at up to 1.4 GHz. The AD9914

enables fast frequency hopping and fine tuning resolution

(64-bit capable using programmable modulus mode). The

AD9914 also offers fast phase and amplitude hopping capability.

The frequency tuning and control words are loaded into the

AD9914 via a serial or parallel I/O port. The AD9914 also

supports a user defined linear sweep mode of operation for

generating linear swept waveforms of frequency, phase, or

amplitude. A high speed, 32-bit parallel data input port is

included enabling high data rates for polar modulation schemes

and fast reprogramming of the phase, frequency, and amplitude

tuning words.

The AD9914 is specified to operate over the extended industrial

temperature range (see Absolute Maximum Ratings section).

Figure 2. Detailed Block Diagram

Rev. PrJ | Page 3 of 38

AD9914 Preliminary Technical Data

DVDD_I/O

I

DVDD

433

mA

Pin 6, Pin 23, Pin 73

AVDD (1.8V)

Input Low Voltage (VIL)

0.8 V

INH

INL

Input Resistance

1.4 kΩ

Differential

Internally Generated DC Bias

2 V

SPECIFICATIONS

DC SPECIFICATIONS

AVDD (1.8V) and DVDD (1.8V) = 1.8 V ± 5%, AVDD (3.3V) and DVDD_I/O (3.3V) = 3.3 V ± 5%, T = 25°C, R

I

= 20 mA, external reference clock frequency = 3.5 GHz with reference clock (REF CLK) multiplier bypassed, unless otherwise noted.

OUT

Table 1.

Parameter Min Typ Max Unit Test Conditions/Comments

SUPPLY VOLTAGE

DVDD_I/O 3.135 3.30 3.465 V Pin 16, Pin 83

DVDD 1.71 1.80 1.89 V Pin 6, Pin 23, Pin 73

AVDD(3.3V) 3.135 3.30 3.465 V Pin 34, Pin 36, Pin 39, Pin 40, Pin 43, Pin 47, Pin 50, Pin 52,

Pin 53, Pin 60

AVDD (1.8V) 1.71 1.80 1.89 V Pin 32, Pin 56, Pin 57

SUPPLY CURRENT See also the total power dissipation specifications

I

20 mA Pin 16, Pin 83

I

640 mA Pin 34, Pin 36, Pin 39, Pin 40, Pin 43, Pin 47, Pin 50, Pin 52,

AVDD (3.3V)

Pin 53, Pin 60

I

178 mA Pin 32, Pin 56, Pin 57

TOTAL POWER DISSIPATION

Base DDS Power, PLL Disabled 2392 3091 mW 3.5 GHz, single-tone mode, modules disabled, linear

sweep disabled, amplitude scaler disabled

Base DDS Power, PLL Enabled 2237 2627 mW 2.5 GHz, single-tone mode, modules disabled, linear

sweep disabled, amplitude scaler disabled

Linear Sweep Additional Power 28 mW

Modulus Additional Power 20 mW

Amplitude Scaler Additional

138 mW Manual or automatic

Power

Full Power-Down Mode 400 616 mW Using either the power-down and enable register or the

EXT_PWR_DWN pin

CMOS LOGIC INPUTS

Input High Voltage (VIH) 2.0 DVDD_I/O V

= 3.3 kΩ,

SET

Input Current (I

Maximum Input Capacitance (CIN) 3 pF

CMOS LOGIC OUTPUTS

Output High Voltage (VOH) 2.7 DVDD_I/O V IOH = 1 mA

Output High Voltage (VOL) 0.4 V IOL = 1 mA

REF CLK INPUT CHARACTERISTICS REF CLK inputs should always be ac-coupled (both single-

REF CLK Multiplier Bypassed

Input Capacitance 1 pF Single-ended, each pin

Voltage

Differential Input Voltage 0.8 1.5 mV p-p

REF CLK Multiplier Enabled

Input Capacitance 1 pF Single-ended, each pin

Input Resistance 1.4 kΩ Differential

Internally Generated DC Bias

Voltage

Differential Input Voltage 0.8 1.5 mV p-p

, I

) ±60 ±200 µA At VIN = 0 V and VIN = DVDD_I/O

ended and differential)

2 V

Rev. PrJ | Page 4 of 38

Preliminary Technical Data AD9914

AC SPECIFICATIONS

AVDD (1.8V) and DVDD (1.8V) = 1.8 V ± 5%, AVDD3 (3.3V) = 3.3 V ± 5%, DVDD_I/O (3.3V) = 3.3 V ± 5%, T = 25°C, R

I

= 20 mA, external reference clock frequency = 3.5 GHz with reference clock (REF CLK) multiplier disabled, unless otherwise noted.

OUT

Table 2.

Parameter Min Typ Max Unit Test Conditions/Comments

REF CLK INPUT Input frequency range

REF CLK Multiplier Bypassed

Input Frequency Range 500 3500 MHz Maximum f

Duty Cycle 45 55 %

Minimum Differential Input Level 632 mV p-p Equivalent to 316 mV swing on each leg

System Clock (SYSCLK) PLL Enabled

VCO Frequency Range 2400 2500 MHz

VCO Gain (KV) 50 MHz/V

Maximum PFD Rate 125 MHz

CLOCK DRIVERS

SYNC_CLK Output Driver

Frequency Range 146 MHz

Duty Cycle 45 50 55 %

Rise Time/Fall Time (20% to 80%) 650 ps

SYNC_OUT Output Driver 10 pF load

Frequency Range 9.1 MHz

Duty Cycle 33 66 % CFR2 Bit 9 = 1

Rise Time (20% to 80%) 1350 ps 10 pF load

Fall Time (20% to 80%) 1670 ps 10 pF load

DAC OUTPUT CHARACTERISTICS

Output Frequency Range (1st Nyquist

0 1750 MHz

Zone)

Output Resistance 50 Ω Single-ended (each pin internally terminated to

AVDD (3.3V))

Output Capacitance 5 pF

Full-Scale Output Current 20.48 mA Range depends on DAC R

Gain Error −10 +10 % FS

Output Offset 0.6 A

Voltage Compliance Range AVDD −

0.50

AVDD +

V

0.50

Wideband SFDR See the Typical Performance Characteristics

section

101.1 MHz Output −66 dBc 0 MHz to 1750 MHz

427.5 MHz Output −65 dBc 0 MHz to 1750 MHz

696.5 MHz Output −57 dBc 0 MHz to 1750 MHz

1396.5 MHz Output −52 dBc 0 MHz to 1750 MHz

Narrow-Band SFDR See the Typical Performance Characteristics

section

100.5 MHz Output −95 dBc ±500 kHz

427.5 MHz Output −95 dBc ±500 kHz

696.5 MHz Output −95 dBc ±500 kHz

1396.5 MHz Output −92 dBc ±500 kHz

DIGITAL TIMING SPECIFICATIONS

Time Required to Enter Power-Down TBD µs Power-down mode loses DAC/PLL calibration

settings

Time Required to Leave Power-Down TBD µs Must recalibrate DAC/PLL

Minimum Master Reset time TBD TBD

Maximum DAC Calibration Time (t

Maximum PLL Calibration Time (t

) TBD TBD f

CAL

) TBD TBD

REF_CLK

CAL

= f

Synchronization Time 16 SYNC_IN cycles

Maximum Profile Toggle Rate 1 SYNC_CLK

period

Rev. PrJ | Page 5 of 38

is 0.4 × f

OUT

/384 USR 0 register, Bit 6 = 0

SYSCLK

SYSCLK

SET

SET

resistor

= 3.3 kΩ,

AD9914 Preliminary Technical Data

Parameter Min Typ Max Unit Test Conditions/Comments

PARALLEL PORT TIMING

Write Timing

Address Setup Time to WR Active

Address Hold Time to WR Inactive

Data Setup Time to WR Inactive

Data Hold Time to WR Inactive

WR Minimum Low Time

WR Minimum High Time

Minimum WR Time

Read Timing

Address to Data Valid 92 ns

Address Hold to RD Inactive

RD Active to Data Valid

RD Inactive to Data Tristate

RD Minimum Low Time

RD Minimum High Time

SERIAL PORT TIMING

SCLK Clock Rate (1/t

SCLK Pulse Width High, t

SCLK Pulse Width Low, t

) 80 MHz SCLK duty cycle = 50%

CLK

1.5 ns

HIGH

5.1 ns

LOW

SDIO to SCLK Setup Time, tDS 4.9 ns

SDIO to SCLK Hold Time, tDH 0 ns

SCLK Falling Edge to Valid Data on

SDIO/SDO, t

CS to SCLK Setup Time, t

CS to SCLK Hold Time, t

CS Minimum Pulse Width High, t

DV

S

H

PWH

DATA PORT TIMING

D[31:0] Setup Time to SYNC_CLK 2 ns

D[31:0] Hold Time to SYNC_CLK 0 ns

F[3:0] Setup Time to SYNC_CLK 2 ns

F[3:0] Hold Time to SYNC_CLK 0 ns

IO_UPDATE Pin Setup Time to

SYNC_CLK

IO_UPDATE Pin Hold Time to

SYNC_CLK

Profile Pin Setup Time to SYNC_CLK ns

Profile Pin Hold Time to SYNC_CLK 2 ns

DR_CTL/DR_HOLD Setup Time to

SYNC_CLK

DR_CTL/DR_HOLD Hold Time to

SYNC_CLK

DATA LATENCY (PIPELINE DELAY)

Single Tone Mode (Matched Latency

Disabled)

Frequency 320 SYSCLK cycles

Phase 296 SYSCLK cycles

Amplitude 104 SYSCLK cycles

Single Tone Mode (Matched Latency

Enabled)

Frequency 320 SYSCLK cycles

Phase 320

Amplitude 320 SYSCLK cycles

1 ns

0 ns

3.8 ns

0 ns

2.1 ns

3.8 ns

10.5 ns

0 ns

69 ns

50 ns

69 ns

50 ns

78 ns

4 ns

0 ns

4 ns

2 ns

0 ns

2 0 ns

0 ns

SYSCLK cycles = fS = system clock frequency

in GHz

Rev. PrJ | Page 6 of 38

Preliminary Technical Data AD9914

Parameter Min Typ Max Unit Test Conditions/Comments

Profile Pin Selection Mode

Frequency 320 SYSCLK cycles

Phase 296 SYSCLK cycles

Amplitude 104 SYSCLK cycles

Modulation Mode with 32-Bit Parallel

Port

Frequency 296 SYSCLK cycles

Phase 272 SYSCLK cycles

Amplitude 80 SYSCLK cycles

Sweep Mode

Frequency 392 SYSCLK cycles

Phase 368 SYSCLK cycles

Amplitude 176 SYSCLK cycles

Rev. PrJ | Page 7 of 38

AD9914 Preliminary Technical Data

per JEDEC JESD51-6

θ

Junction-to-board thermal

13.3

°C/W

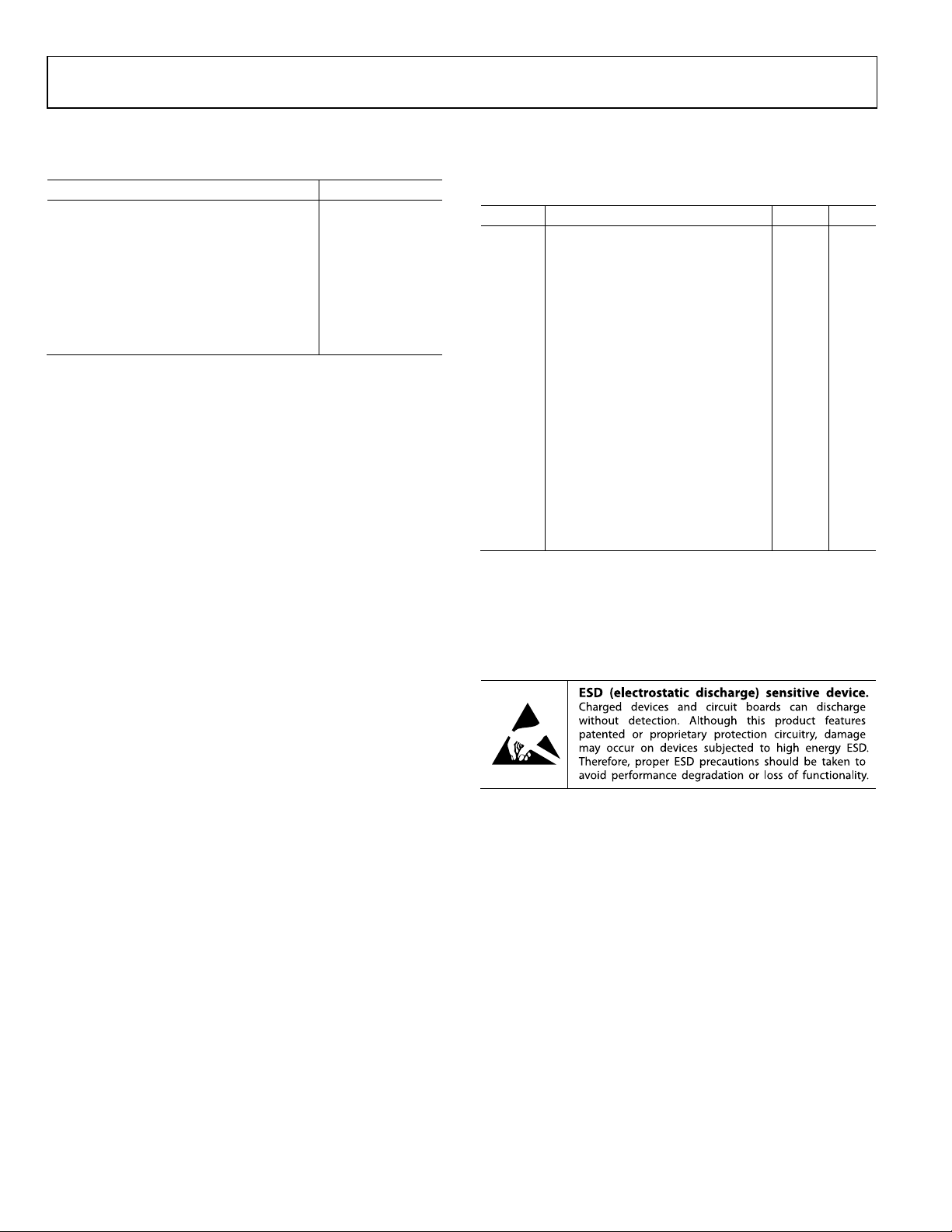

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

AVDD (1.8V), DVDD (1.8V) Supplies 2 V

AVDD (3.3V), DVDD_I/O (3.3V) Supplies 4 V

Digital Input Voltage −0.7 V to +4 V

Digital Output Current 5 mA

Storage Temperature Range −65°C to +150°C

Operating Temperature Range −40°C to +85°C

Maximum Junction Temperature 150°C

Lead Temperature (10 sec Soldering) 300°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL PERFORMANCE

Table 4.

Symbol Description Value1 Unit

θJA

θ

JMA

θ

JMA

JB

ΨJB

θJC

ΨJT

1

Results are from simulations. PCB is JEDEC multilayer. Thermal performance

for actual applications requires careful inspection of the conditions in the

application to determine if they are similar to those assumed in these

calculations.

Junction-to-ambient thermal

resistance (Still Air) per JEDEC

JESD51-2

Junction-to-ambient thermal

resistance (1.0 m/sec airflow)

per JEDEC JESD51-6

Junction-to-ambient thermal

resistance (2.0 m/sec air flow)

resistance (still air) per JEDEC

JESD51-8

Junction-to-board characterization

parameter (still air) per JEDEC

JESD51-6

Junction-to-case thermal resistance 2.21 °C/W

Junction-to-top-of-package

characterization parameter (still air)

per JEDEC JESD51-2

24.1 °C/W

21.3 °C/W

20.0 °C/W

12.8 °C/W

0.23 °C/W

ESD CAUTION

Rev. PrJ | Page 8 of 38

Preliminary Technical Data AD9914

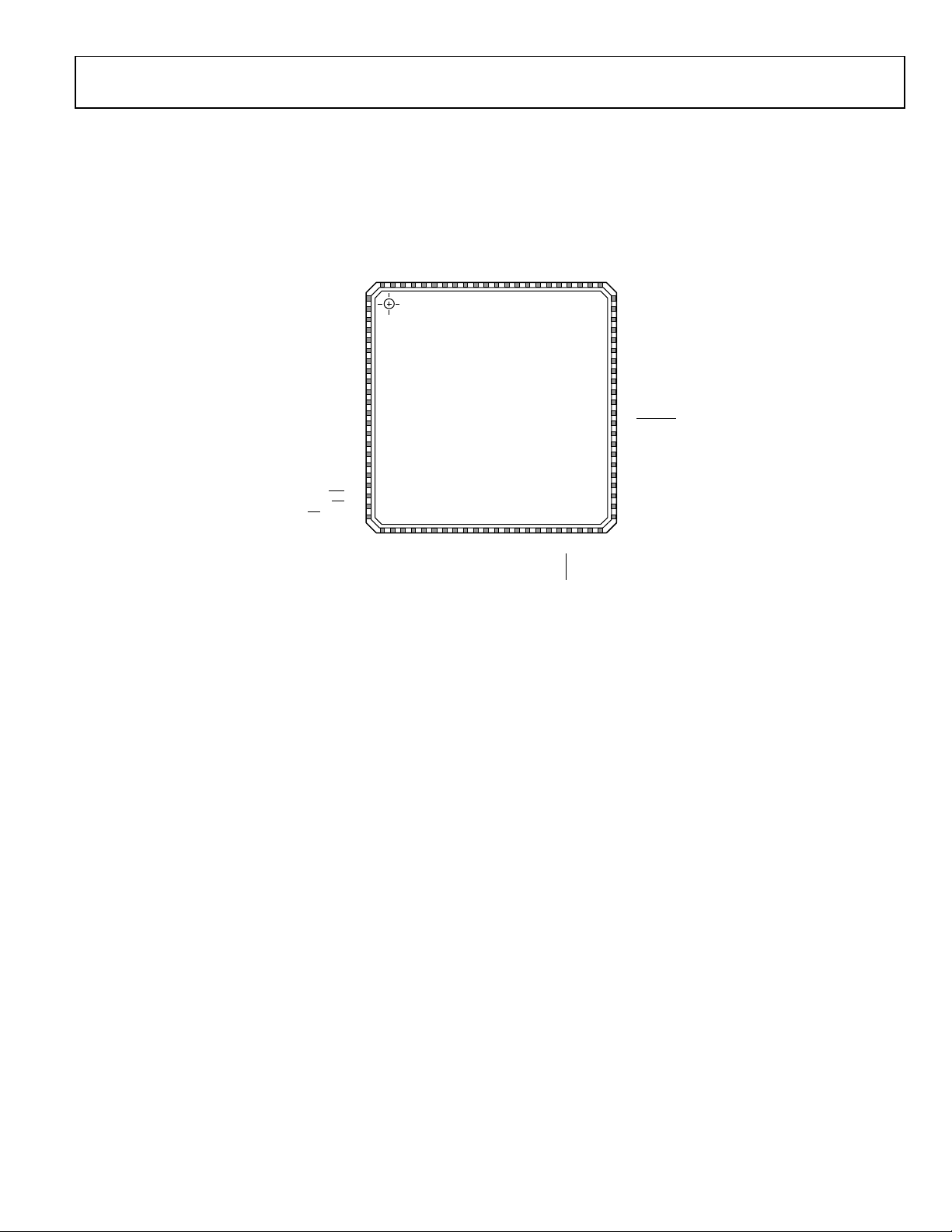

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

D17

D16

D15/A7

D14/A6

D13/A5

DVDD (1.8V)

DGND

D12/A4

D11/A3

D10/A2

D9/A1

D8/A0

D7

D6

D5

DVDD_I/O ( 3.3V)

17DGND

18D4/SYNCIO

19D3/SDO

20D2/SDIO/WR

23242526272829303132333436

37

DVDD (1.8V)

DGND

PS0

PS1

PS2

F0F1F2

F3

AVDD (1.8V)

AGND

AVDD (3.3V)

35AGND

AVDD (3.3V)

AGND

38AGND

39AVDD (3.3V)

40AVDD (3.3V)

41

AOUT

58

57

56

55

54

53

52

51

50

49

48

47

46

45

LOOP_FILTER

59 REF

60 AVDD (3.3V)

61 SYNC_OUT

62 SYNC_IN

63 DRCTL

64 DRHOLD

65 DROVER

66 OSK

AVDD (1.8V)

AVDD (1.8V)

REF CLK

REF CLK

AVDD (3.3V)

AVDD (3.3V)

AGND

AVDD (3.3V)

AGND

DAC_RSET

AVDD (3.3V)

AGND

DAC_BP

7877767574737271706968

67

D23

79 D22

80 D21

81 D20

82 SYNC_CLK

83 DVDD_I/O ( 3.3V)

84 DGND

85 MASTER_RESET

86 I/O_UPDATE

87 D19

88 D18

D24

D25

D26

DGND

DVDD (1.8V)

D27

D28

D29

D30

D31

EXT_PWR_DWN

NOTES

1. THE EPAD M US T BE SOLDERED TO GROUND.

10836-003

21D1/SCLK/RD

22D0/CS/PWD

42AOUT

43AVDD (3.3V)

44AGND

AD9914

TOP VIEW

(Not to S cale)

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

Rev. PrJ | Page 9 of 38

AD9914 Preliminary Technical Data

Table 5. Pin Function Descriptions

Pin No. Mnemonic I/O1 Description

1, 2, 13 to 15, 68

to 72, 75 to 81,

87, 88

3 D15/A7 I/O Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins

4 D14/A6 I/O Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins

5 D13/A5 I/O Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins

8 D12/A4 I/O Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins

9 D11/A3 I/O Parallel Port Pin/Address Line. The state of the F0 to F3 function pins determines if this acts as

10 D10/A2 I/O Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins

11 D9/A1 I/O Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins

12 D8/A0 I/O Parallel Port Pin/Address Line. Multipurpose pin depending on the state of the function pins

18 D4/SYNCIO I Parallel Port Pin/Serial Port Synchronization Pin. Multipurpose pin depending on the state of

19 D3/SDO I/O Parallel Port Pin/Serial Data Output. Multipurpose pin depending on the state of the function

20 D2/SDIO/WR I/O Parallel Port Pin/Serial Data Input and Output/Write Input. Multipurpose pin depending on

21 D1/SCLK/RD I Parallel Port Pin/Serial Clock/Read Input. Multipurpose pin depending on the state of the

22 D0/CS/PWD I Parallel Port Pin/Chip Select/Parallel Width. Multipurpose pin depending on the state of the

6, 23, 73 DVDD (1.8V) I Digital Core Supplies (1.8 V).

7, 17, 24, 74, 84 DGND I Digital Ground.

16, 83 DVDD_I/O (3.3V) I Digital Input/Output Supplies (3.3 V).

32, 56, 57 AVDD (1.8V) I Analog Core Supplies (1.8 V).

33, 35, 37, 38,

44, 46, 49, 51

34, 36, 39, 40,

43, 47, 50, 52,

53, 60

D5 to D7, D16 to

D31, D27 to D31

AGND I Analog Ground.

AVDD (3.3V) I Analog DAC Supplies (3.3 V).

I/O Parallel Port Pins. The 32-bit parallel port offers the option for serial or parallel programming

of the internal registers. In addition, the parallel port can be configured to provide direct FSK,

PSK, or ASK (or combinations thereof ) modulation data. The 32-bit parallel port configuration

is set by the state of the four function pins (F0 to F3).

(F0 to F3). The state of the F0 to F3 function pins determines if this acts as a line for direct

FSK, PSK, or ASK data or as an address line for programming the internal registers.

(F0 to F3). The state of the F0 to F3 function pins determines if this acts as a line for direct

FSK, PSK, or ASK data or as an address line for programming the internal registers.

(F0 to F3). The state of the F0 to F3 function pins determines if this acts as a line for direct

FSK, PSK, or ASK data or as an address line for programming the internal registers.

(F0 to F3). The state of the F0 to F3 function pins determines if this acts as a line for direct

FSK, PSK, or ASK data or as an address line for programming the internal registers.

a line for direct FSK, PSK, or ASK data or as an address line for programming the internal

registers.

(F0 to F3). The state of the F0 to F3 function pins determines if this acts as a line for direct

FSK, PSK, or ASK data or as an address line for programming the internal registers.

(F0 to F3). The state of the F0 to F3 function pins determines if this acts as a line for direct

FSK, PSK, or ASK data or as an address line for programming the internal registers.

(F0 to F3). The state of the F0 to F3 function pins determines if this acts as a line for direct

FSK, PSK, or ASK data or as an address line for programming the internal registers.

the function pins (F0 to F3). This pin is D4 for direct FSK, PSK, or ASK data. If serial mode is

invoked via F0 to F3, this pin is used to reset the serial port.

pins (F0 to F3). This pin is D3 for direct FSK, PSK, or ASK data. If serial mode is invoked via (F0F3), this pin is used for readback mode for serial operation.

the state of the function pins (F0 to F3). This pin is D2 for direct FSK, PSK, or ASK data. If serial

mode is invoked via F0 to F3, this pin is used for the SDIO for serial operation. If parallel mode

is enabled, this pin is used to write to change the values of the internal registers.

function pins (F0 to F3). This pin is D1 for direct FSK, PSK, or ASK data. If serial mode is

invoked via F0 to F3, this pin is used for SCLK for serial operation. If parallel mode is enabled,

this pin is used to read back the value of the internal registers.

function pins (F0 to F3). This pin is D0 for direct FSK, PSK, or ASK data. If serial mode is

invoked via F0 to F3, this pin is used for the chip select for serial operation. If parallel mode is

enabled, this pin is used to set either 8-bit data or 16-bit data.

Rev. PrJ | Page 10 of 38

Preliminary Technical Data AD9914

up on the SYNC_CLK pin.

28, 29, 30, 31

F0 to F3

I

Function Pins. Digital Inputs. The state of these pins determine if a serial or parallel interface

63

DRCTL

I

Ramp Control. Digital input (active high). This pin controls the sweep direction (up/down).

64

DRHOLD

I

Ramp Hold. Digital input (active high). Pauses the sweep when active.

Pin No. Mnemonic I/O1 Description

25, 26, 27 PROFILE[0:2] I Profile Select Pins. Digital inputs (active high). Use these pins to select one of eight

phase/frequency profiles for the DDS. Changing the state of one of these pins transfers the

current contents of all I/O buffers to the corresponding registers. State changes should be set

is used. In addition, the function pins determine how the 32-bit parallel data-word is

partitioned for FSK, PSK, or ASK modulation mode.

41

42 AOUT O DAC Output Source. Analog output (voltage mode). Internally connected through a 50 Ω

45 DAC_BP I DAC Bypass Pin.

48 DAC_RSET O Analog Reference. This pin programs the DAC output full-scale reference current. Connect a

54

55 REF_CLK I Reference Clock Input. Analog input.

58 LOOP_FILTER O External PLL Loop Filter Node.

59 REF O Local PLL Reference Supply. Typically at 2.05 V.

61 SYNC_OUT O Digital Synchronization Output. Used to synchronize multiple chips together.

62 SYNC_IN I Digital Synchronization Input. Used to synchronize multiple chips together.

O DAC Complementary Output Source. Analog output (voltage mode). Internally connected

AOUT

through a 50 Ω resistor to AVDD (3.3V).

resistor to AVDD (3.3V).

3.3 kΩ resistor to AGND.

REF_CLK

I Complementary Reference Clock Input. Analog input.

65 DROVER O Ramp Over. Digital output (active high). This pin switches to Logic 1 whenever the digital

ramp generator reaches its programmed upper or lower limit.

66 OSK I Output Shift Keying. Digital input (active high). When the OSK features are placed in either

manual or automatic mode, this pin controls the OSK function. In manual mode, it toggles

the multiplier between 0 (low) and the programmed amplitude scale factor (high). In

automatic mode, a low sweeps the amplitude down to zero and a high sweeps the

amplitude up to the amplitude scale factor.

67 EXT_PWR_DWN I External Power-Down. Digital input (active high). A high level on this pin initiates the

currently programmed power-down mode.

82 SYNC_CLK O Clock Output. Digital output. Many of the digital inputs on the chip, such as I/O_UPDATE,

PROFILE[2:0], and the parallel data port (D0 to D31), must be set up on the rising edge of this

signal.

85 MASTER_RESET I Master Reset. Digital input (active high). Clears all memory elements and sets registers to

default values.

86 I/O_UPDATE I Input/Output Update. Digital input (active high). A high on this pin transfers the contents of

the I/O buffers to the corresponding internal registers.

EPAD Exposed Pad. The EPAD must be soldered to ground.

1

I = input, O = output.

Rev. PrJ | Page 11 of 38

AD9914 Preliminary Technical Data

START 0Hz

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

175MHz/DIV STOP 1.75GHz

SFDR (dBc)

10836-004

START 0Hz

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

175MHz/DIV STOP 1.75GHz

SFDR (dBc)

10836-005

START 0Hz

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

175MHz/DIV STOP 1.75GHz

SFDR (dBc)

10836-006

CENTER 171.5MHz

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

50kHz/DIV SPAN 500kHz

SFDR (dBc)

10836-007

CENTER 427.5MHz

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

50kHz/DIV SPAN 500kHz

SFDR (dBc)

10836-008

CENTER 696.5MHz

–100

–90

–80

–70

–60

–50

–40

–30

–20

–10

0

50kHz/DIV SPAN 500kHz

SFDR (dBc)

10836-009

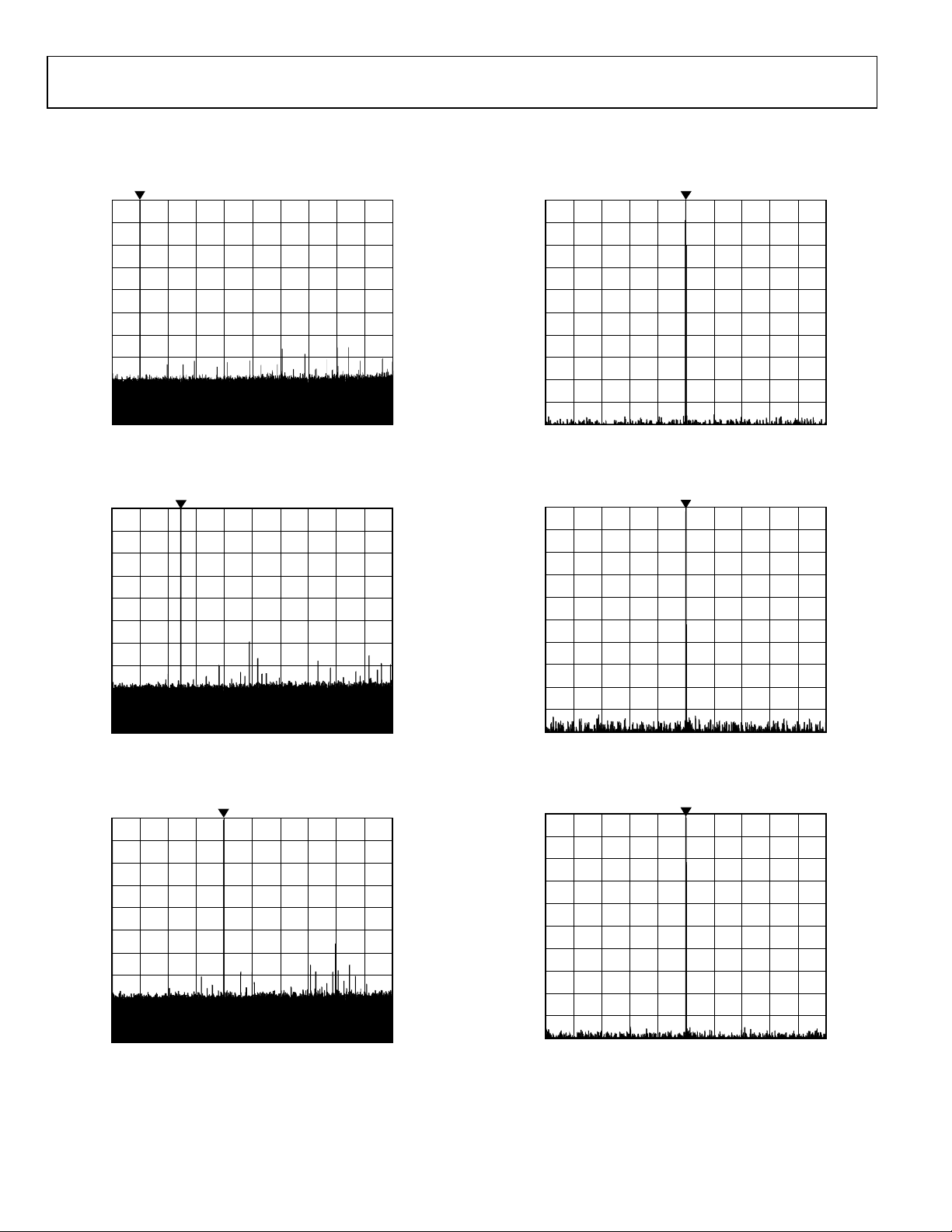

TYPICAL PERFORMANCE CHARACTERISTICS

Nominal supply voltage; DAC R

= 3.3 kΩ, 25°C, unless otherwise noted.

SET

Figure 4. Wideband SFDR at 171.5 MHz

SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 5. Wideband SFDR at 427.5 MHz

SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 7. Narrow-Band SFDR at 171.5 MHz,

SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 8. Narrow-Band SFDR at 427.5 MHz,

SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Figure 6. Wideband SFDR at 696.5 MHz,

SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Rev. PrJ | Page 12 of 38

Figure 9. Narrow-Band SFDR at 696.5 MHz,

SYSCLK = 3.5 GHz (SYSCLK PLL Bypassed)

Loading...

Loading...