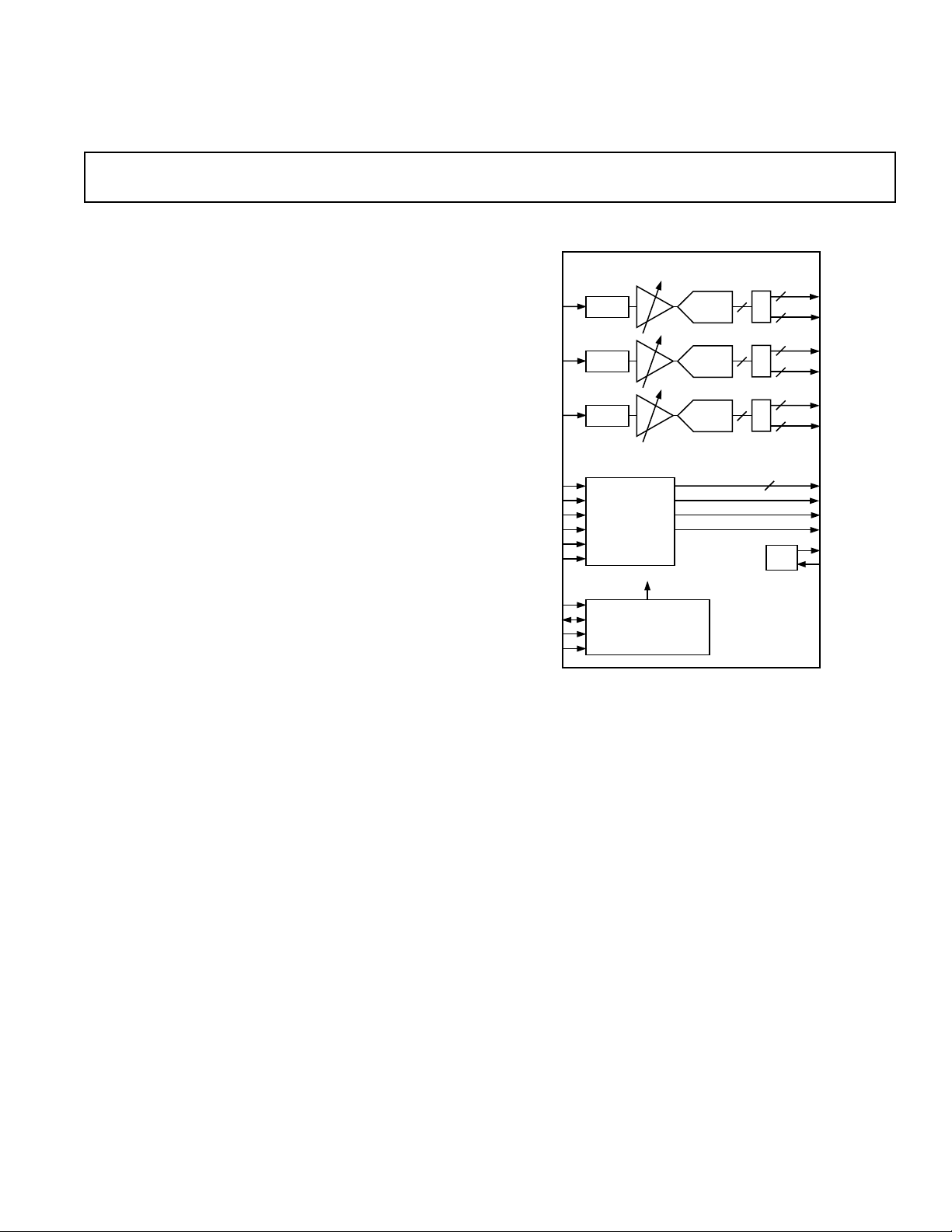

Analog Interface for

CLAMP

R

IN

A/D

8

8

8

R

OUTA

R

OUTB

CLAMP

G

IN

A/D

8

8

8

G

OUTA

G

OUTB

CLAMP

B

IN

A/D

8

8

8

B

OUTA

B

OUTB

SYNC

PROCESSING

AND CLOCK

GENERATION

HSYNC

COAST

CLAMP

CKINV

CKEXT

FILT

2

DATACK

HSOUT

VSOUT

SOGOUT

ANALOG INTERFACE

REF

REFOUT

REFIN

SERIAL REGISTER AND

POWER MANAGEMENT

SCL

SDA

A

1

A

0

AD9886

a

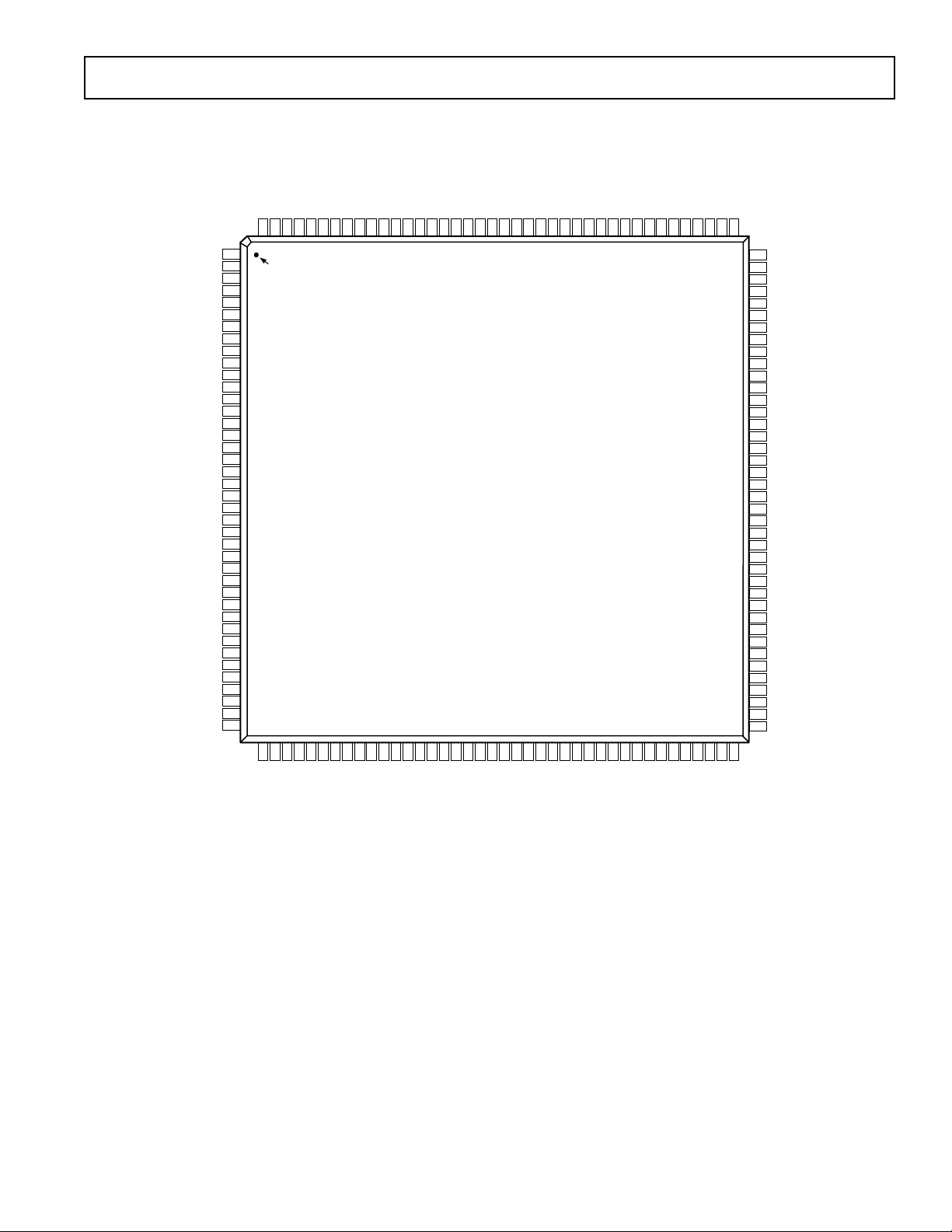

GENERAL DESCRIPTION

The AD9886 is a complete 8-bit 140 MSPS monolithic analog

interface optimized for capturing RGB graphics signals from

personal computers and workstations. Its 140 MSPS encode

rate capability and full-power analog bandwidth of 330 MHz

supports resolutions up to SXGA (1280 × 1024 at 75 Hz).

For ease of design and to minimize cost, the AD9886 is a fully

integrated interface solution for FPDs. The AD9886 includes a

140 MHz triple ADC with internal 1.25 V reference, PLL to

generate a pixel clock from an HSYNC, and programmable

gain, offset, and clamp control. The user provides only a 3.3 V

power supply, analog input, and an HSYNC signal. Three-state

CMOS outputs may be powered from 2.5 V to 3.3 V.

The AD9886’s on-chip PLL generates a pixel clock from an

HSYNC. Pixel clock output frequencies range from 12 MHz to

140 MHz. PLL clock jitter is 500 ps p-p typical at 140 MSPS.

When the COAST signal is presented, the PLL maintains its

output frequency in the absence of HSYNC. A sampling phase

adjustment is provided. Data, HSYNC and Clock output phase

relationships are maintained. The PLL can be disabled and an

external clock input provided as the pixel clock. The AD9886

also offers full sync processing for composite sync and sync-ongreen applications.

A clamp signal is generated internally or may be provided by the

user through the CLAMP input pin. This interface is fully programmable via a 2-wire serial interface.

FEATURES

Analog Interface

140 MSPS Maximum Conversion Rate

330 MHz Analog Bandwidth

0.5 V to 1.0 V Analog Input Range

500 ps p-p PLL Clock Jitter at 140 MSPS

3.3 V Power Supply

Full Sync Processing

Midscale Clamp for YUV Applications

Flat Panel Displays

AD9886

FUNCTIONAL BLOCK DIAGRAM

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

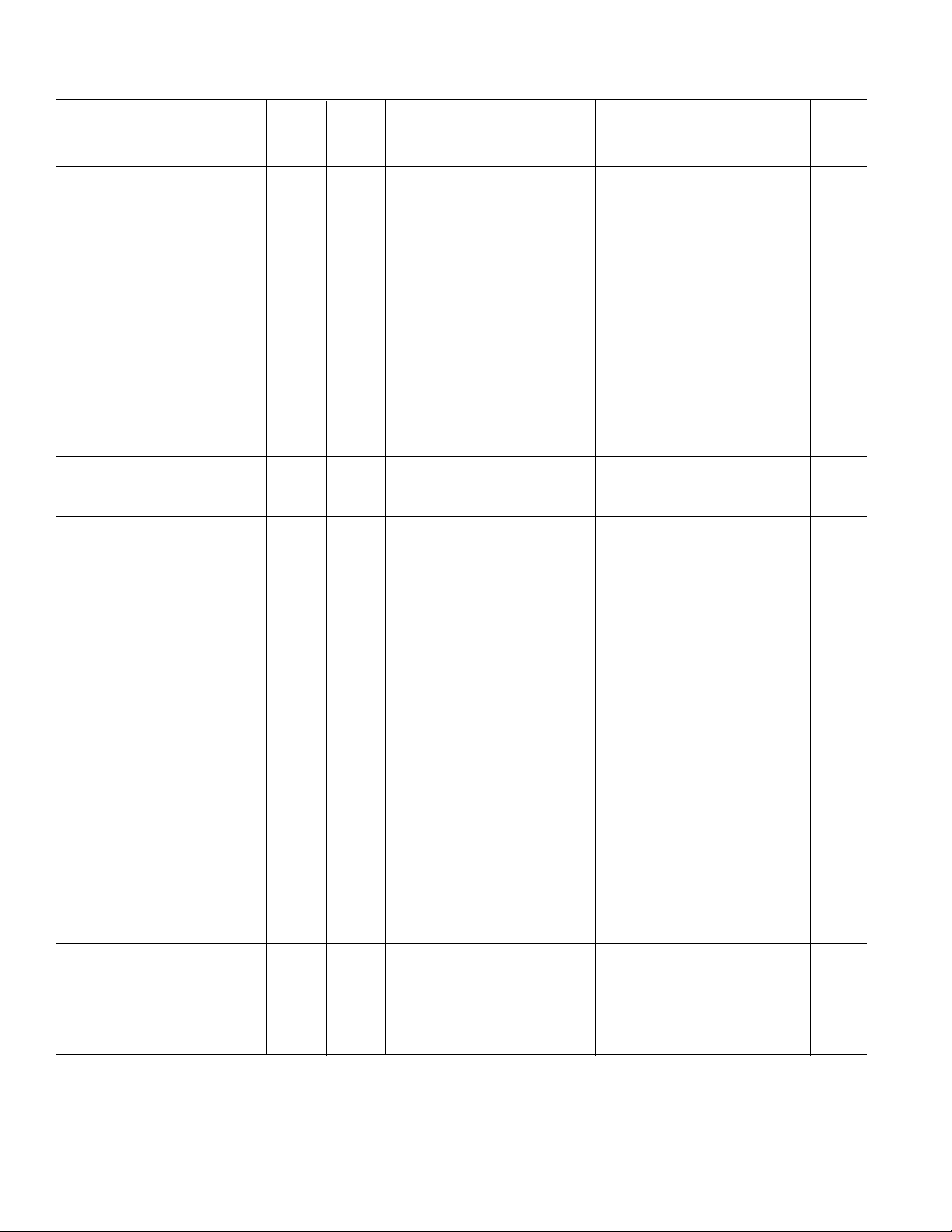

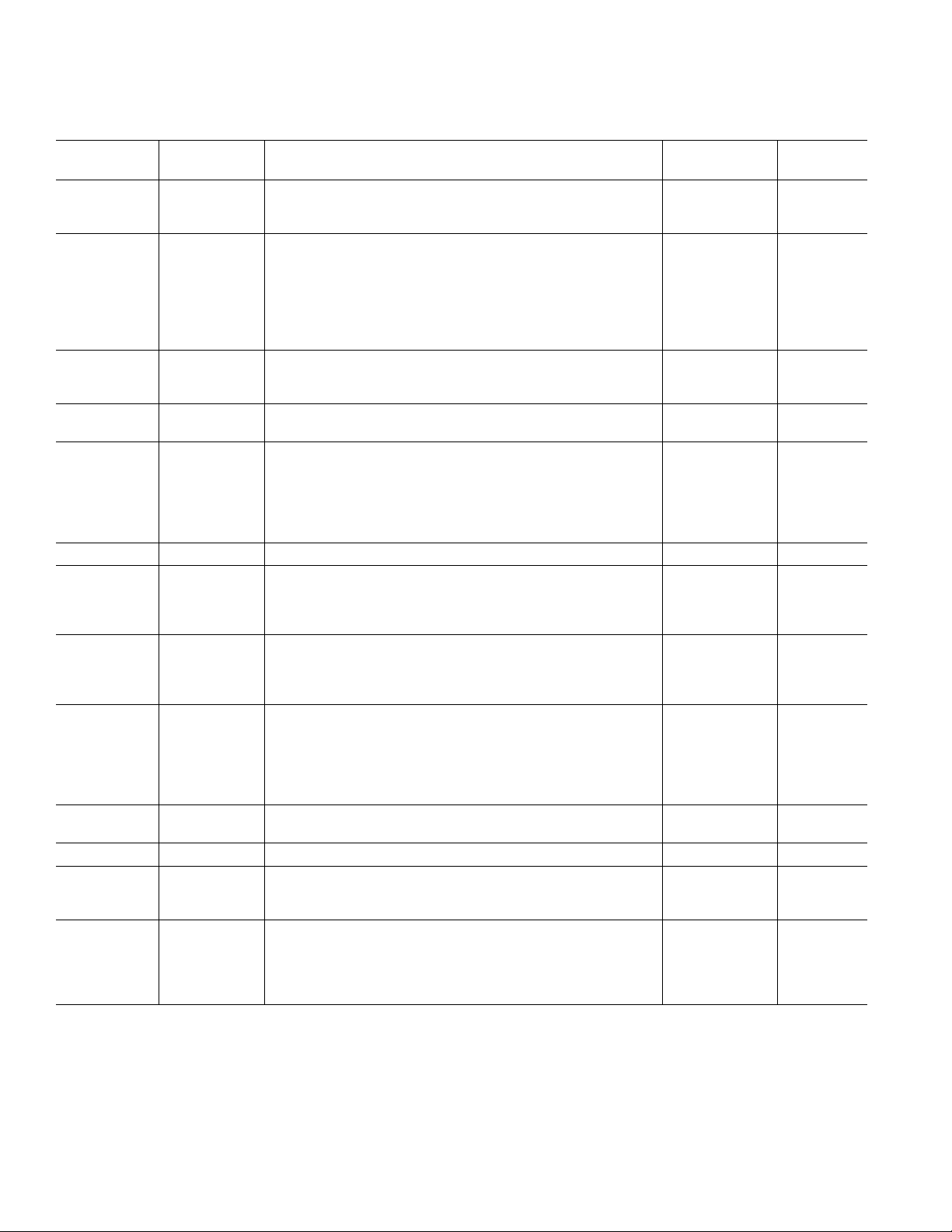

AD9886–SPECIFICATIONS

(VD = 3.3 V, VDD = 3.3 V, ADC Clock = Maximum Conversion Rate.)

Test AD9886KS-100 AD9886KS-140

Parameter Temp Level Min Typ Max Min Typ Max Unit

RESOLUTION 8 8 Bits

DC ACCURACY

Differential Nonlinearity 25°CI ± 0.5 +1.15/–1.0 ± 0.5 +1.25/–1.0 LSB

Full VI +1.15/–1.0 +1.25/–1.0 LSB

Integral Nonlinearity 25°CI ± 0.5 ± 1.4 ± 0.5 ± 1.65 LSB

Full VI ± 1.75 ± 2.5 LSB

No Missing Codes Full VI Guaranteed Guaranteed

ANALOG INPUT

Input Voltage Range

Minimum Full VI 0.5 0.5 V p–p

Maximum Full VI 1.0 1.0 V p–p

Gain Tempco 25°C V 135 150 ppm/°C

Input Bias Current 25°CIV 1 1 µA

Full IV 1 1 µA

Input Offset Voltage Full VI 7 50 7 50 mV

Input Full-Scale Matching Full VI 8.0 8.0 % FS

Offset Adjustment Range Full VI 44 50 56 44 50 56 % FS

REFERENCE OUTPUT

Output Voltage Full VI 1.20 1.25 1.30 1.20 1.25 1.30 V

Temperature Coefficient Full V ± 50 ± 50 ppm/°C

SWITCHING PERFORMANCE

1

Maximum Conversion Rate Full VI 100 140 MSPS

Minimum Conversion Rate Full IV 10 10 MSPS

Data to Clock Skew, t

t

BUFF

t

STAH

t

DHO

t

DAL

t

DAH

t

DSU

t

STASU

t

STOSU

SKEW

Full IV –0.5 +2.0 –0.5 +2.0 ns

Full VI 4.7 4.7 µs

Full VI 4.0 4.0 µs

Full VI 0 0 µs

Full VI 4.7 4.7 µs

Full VI 4.0 4.0 µs

Full VI 250 250 µs

Full VI 4.7 4.7 µs

Full VI 4.0 4.0 µs

HSYNC Input Frequency Full IV 15 110 15 110 kHz

Maximum PLL Clock Rate Full VI 100 140 MHz

Minimum PLL Clock Rate Full IV 12 12 MHz

PLL Jitter 25°C IV 400 700

Full IV 1000

Sampling Phase Tempco Full IV

15 15 ps/°C

2

2

400 700

1000

3

3

ps p-p

ps p-p

DIGITAL INPUTS

Input Voltage, High (V

Input Voltage, Low (V

Input Current, High (V

Input Current, Low (V

) Full VI 2.5 2.5 V

IH

) Full VI 0.8 0.8 V

IL

) Full IV –1.0 –1.0 µA

IH

) Full IV 1.0 1.0 µA

IL

Input Capacitance 25°CV 3 3 pF

DIGITAL OUTPUTS

Output Voltage, High (VOH) Full VI VD– 0.1 VD– 0.1 V

Output Voltage, Low (V

) Full VI 0.1 0.1 V

OL

Duty Cycle

DATACK, DATACK Full IV 45 50 55 45 50 55 %

Output Coding Binary Binary

–2–

REV. 0

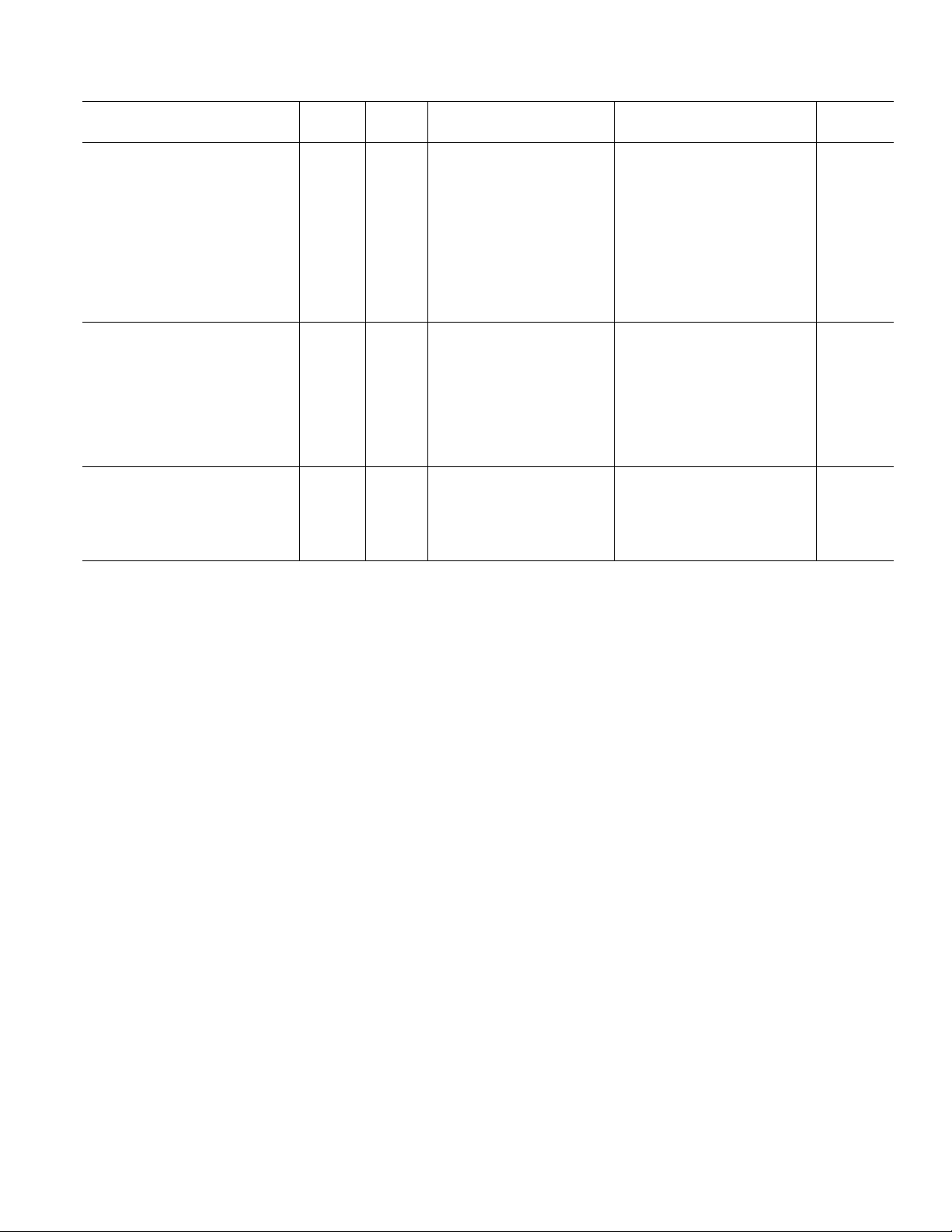

AD9886

Test AD9886KS-100 AD9886KS-140

Parameter Temp Level Min Typ Max Min Typ Max Unit

POWER SUPPLY

VD Supply Voltage Full IV 3.0 3.3 3.6 3.0 3.3 3.6 V

Supply Voltage Full IV 2.2 3.3 3.6 2.2 3.3 3.6 V

V

DD

P

Supply Voltage Full IV 3.0 3.3 3.6 3.0 3.3 3.6 V

VD

Supply Current (VD)25°C V 140 155 mA

I

D

Supply Current (VDD)

I

DD

IP

Supply Current (PVD)25°C V 15 16 mA

VD

Total Power Dissipation Full VI 564 850 715 850 mW

Power-Down Supply Current Full VI 13 25 13 25 mA

Power-Down Dissipation Full VI 43 82.5 43 82.5 mW

DYNAMIC PERFORMANCE

Analog Bandwidth, Full Power 25°C V 330 330 MHz

Transient Response 25°CV 2 2 ns

Overvoltage Recovery Time 25°C V 1.5 1.5 ns

Signal-to-Noise Ratio (SNR)

(Without Harmonics) Full V 45 45 dB

= 40.7 MHz

f

IN

Crosstalk Full V 60 60 dBc

THERMAL CHARACTERISTICS

θJC Junction-to-Case

Thermal Resistance V 20 20 °C/W

θJA Junction-to-Ambient

Thermal Resistance V 40 40 °C/W

NOTES

1

Drive Strength = 11.

2

VCO Range = 01, Charge Pump Current = 001, PLL Divider = 1693.

3

VCO Range = 10, Charge Pump Current = 110, PLL Divider = 1600.

4

DEMUX = 1, DATACK and DATACK Load = 10 pF, Data Load = 5 pF.

5

Using external pixel clock.

Specifications subject to change without notice.

4

25°C V 34 48 mA

5

25°C V 46 46 dB

REV. 0

–3–

AD9886

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

VD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6 V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6 V

V

DD

Analog Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . V

VREF IN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

to 0.0 V

D

to 0.0 V

D

Digital Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 V to 0.0 V

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . 20 mA

Operating Temperature . . . . . . . . . . . . . . . . . –25°C to +85°C

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

Maximum Junction Temperature . . . . . . . . . . . . . . . . 175°C

Maximum Case Temperature . . . . . . . . . . . . . . . . . . . 150°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions outside of those indicated in the operation

sections of this specification is not implied. Exposure to absolute maximum ratings

for extended periods may affect device reliability.

ORDERING GUIDE

Temperature Package Package

Model Range Description Option

AD9886KS-140 0°C to 70°C Plastic Quad Flatpack S-160

AD9886KS-100 0°C to 70°C Plastic Quad Flatpack S-160

AD9886/PCB 25°C Evaluation Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD9886 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

EXPLANATION OF TEST LEVELS

Test Level

I 100% production tested.

II 100% production tested at 25°C and sample tested at

specified temperatures.

III Sample tested only.

IV Parameter is guaranteed by design and characterization testing.

V Parameter is a typical value only.

VI 100% production tested at 25°C; guaranteed by design and

characterization testing.

–4–

REV. 0

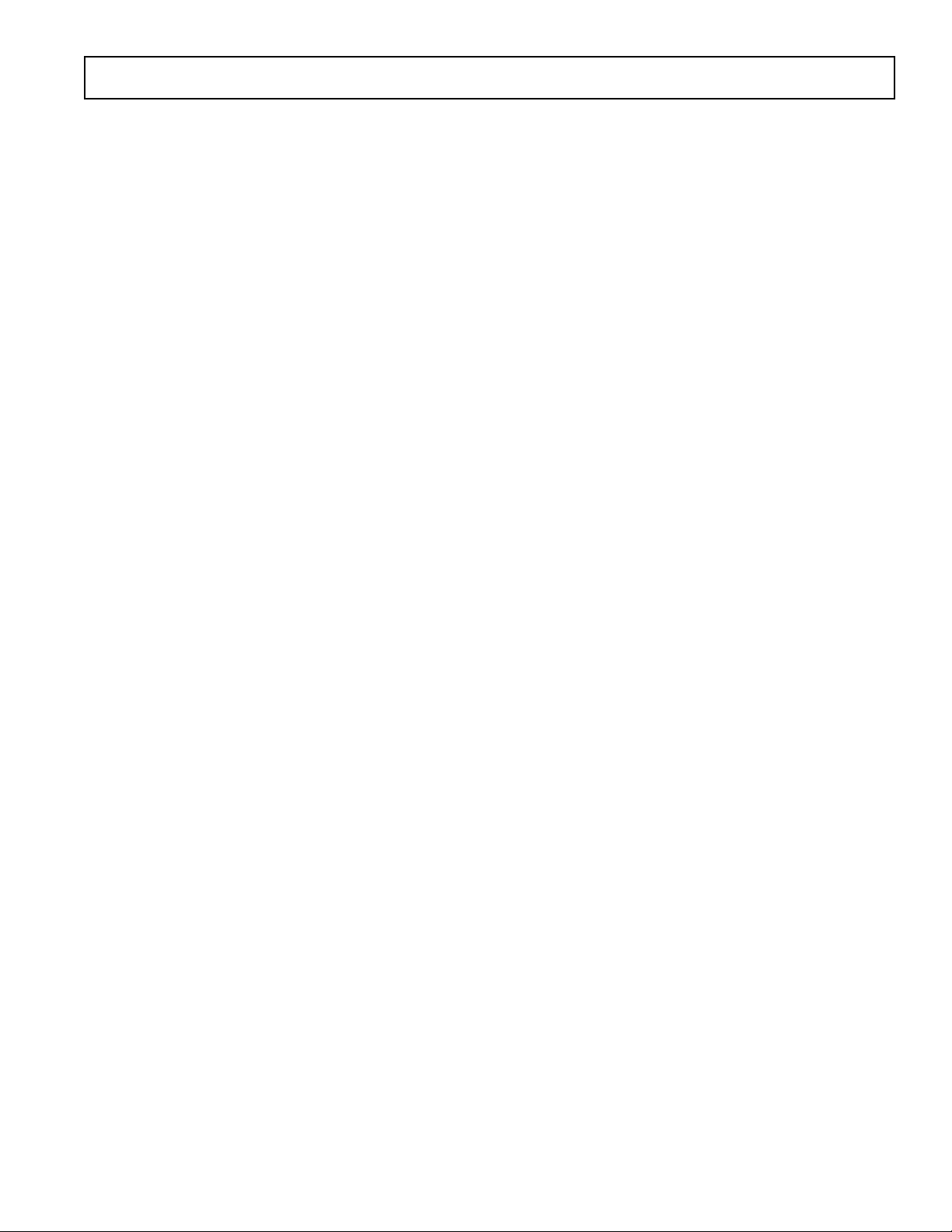

PIN CONFIGURATION

AD9886

VDD

GND

GREEN A<7>

GREEN A<6>

GREEN A<5>

GREEN A<4>

GREEN A<3>

GREEN A<2>

GREEN A<1>

GREEN A<0>

VDD

GND

GREEN B<7>

GREEN B<6>

GREEN B<5>

GREEN B<4>

GREEN B<3>

GREEN B<2>

GREEN B<1>

GREEN B<0>

VDD

GND

BLUE A<7>

BLUE A<6>

BLUE A<5>

BLUE A<4>

BLUE A<3>

BLUE A<2>

BLUE A<1>

BLUE A<0>

VDD

GND

BLUE B<7>

BLUE B<6>

BLUE B<5>

BLUE B<4>

BLUE B<3>

BLUE B<2>

BLUE B<1>

BLUE B<0>

OUT

SCANINGNDVDREF

129

128

127

126

REFINVDVDGND

125

123

122

124

GND

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

RMIDSCV

R

AIN

RCLAMPV

VD

GND

VD

VD

GND

GND

GMIDSCV

G

AIN

GCLAMPV

SOGIN

VD

GND

VD

VD

GND

GND

BMIDSCV

B

AIN

BCLAMPV

VD

GND

VD

GND

CKINV

CLAMP

SDA

SCL

A0

A1

PVD

PVD

GND

GND

COAST

CKEXT

HSYNC

VSYNC

RED B<0>

RED B<1>

RED B<2>

RED B<3>

RED B<4>

RED B<5>

RED B<6>

RED B<7>

GND

VDD

RED A<0>

RED A<1>

RED A<2>

RED A<3>

RED A<4>

RED A<5>

RED A<6>

RED A<7>

GND

VDD

SOGOUT

160

159

158

157

156

155

154

153

152

151

150

149

146

145

144

143

142

141

148

147

1

PIN 1

2

IDENTIFIER

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

140

AD9886

TOP VIEW

(Not to Scale)

HSOUT

VSOUTNCS

139

138

137

CDT

136

DATACLKB

DATACLK

GND

VDD

135

133

132

134

GND

131

GND

130

REV. 0

4142434445464748495051

NCNCNC

OUT

VDD

GND

GND

GND

SCAN

NC = NO CONNECT

NC

535455565758596061

52

VD

VD

NC

CLK

GND

SCAN

VD

NC

NC

GND

NC

–5–

62

6364656668697071726773747576787980

VD

VD

NC

GND

NC

NC

GND

NC

NC

GND

VD

NCNCNC

GND

PVD

GND

77

PVD

FILT

PVD

GND

AD9886

Table I. Complete Pinout List

P

in Pin Pin

Type Name Function Value Number

Analog Video R

Inputs G

AIN

AIN

B

AIN

External HSYNC Horizontal SYNC Input 3.3 V CMOS 82

Sync/Clock VSYNC Vertical SYNC Input 3.3 V CMOS 81

Inputs SOGIN Input for Sync-on-Green 0.0 V to 1.0 V 108

CLAMP Clamp Input (External CLAMP Signal) 3.3 V CMOS 93

COAST PLL COAST Signal Input 3.3 V CMOS 84

CKEXT External Pixel Clock Input (to Bypass the PLL) or 10 kΩ to V

CKINV ADC Sampling Clock Invert 3.3 V CMOS 94

Sync Outputs HSOUT HSYNC Output Clock (Phase-Aligned with DATACK) 3.3 V CMOS 139

VSOUT VSYNC Output Clock (Phase-Aligned with DATACK) 3.3 V CMOS 138

SOGOUT Sync on Green Slicer Output 3.3 V CMOS 140

Voltage REFOUT Internal Reference Output (Bypass with 0.1 µF to Ground) 1.25 V 126

Reference REFIN Reference Input (1.25 V ± 10%) 1.25 ± 10% 125

Clamp Voltages R

V Red Channel Midscale Clamp Voltage Output 120

MIDSC

V Red Channel Midscale Clamp Voltage Output 0.0 V to 0.75 V 118

R

CLAMP

V Green Channel Midscale Clamp Voltage Output 111

G

MIDSC

V Green Channel Midscale Clamp Voltage Output 0.0 V to 0.75 V 109

G

CLAMP

V Blue Channel Midscale Clamp Voltage Output 101

B

MIDSC

B

V Blue Channel Midscale Clamp Voltage Output 0.0 V to 0.75 V 99

CLAMP

PLL Filter FILT Connection for External Filter Components for Internal PLL 78

Power Supply V

V

PV

D

DD

D

GND Ground 0 V

Serial Port SDA Serial Port Data I/O 3.3 V CMOS 92

(2-Wire SCL Serial Port Data Clock (100 kHz max) 3.3 V CMOS 91

Serial Interface) A0 Serial Port Address Input 1 3.3 V CMOS 90

A1 Serial Port Address Input 2 3.3 V CMOS 89

Data Outputs Red B[7:0] Port B/Odd Outputs of Converter “Red,” Bit 7 Is the MSB 3.3 V CMOS 153–160

Green B[7:0] Port B/Odd Outputs of Converter “Green,” Bit 7 Is the MSB 3.3 V CMOS 13–20

Blue B[7:0] Port B/Odd Outputs of Converter “Blue,” Bit 7 Is the MSB 3.3 V CMOS 33–40

Red A[7:0] Port A/Even Outputs of Converter “Red,” Bit 7 Is the MSB 3.3 V CMOS 143–150

Green A[7:0] Port A/Even Outputs of Converter “Green,” Bit 7 Is the MSB 3.3 V CMOS 3–10

Blue A[7:0] Port A/Even Outputs of Converter “Blue,” Bit 7 Is the MSB 3.3 V CMOS 23–30

Data Clock DATACK Data Output Clock for the Analog and Digital Interface 3.3 V CMOS 134

Outputs DATACK Data Output Clock Complement for the Analog Interface Only 3.3 V CMOS 135

Sync Detect S

Scan Function SCAN

CDT

SCAN

SCAN

IN

OUT

CLK

No Connect NC These Pins Should be Left Unconnected 46–49, 53,

Analog Input for Converter R 0.0 V to 1.0 V 119

Analog Input for Converter G 0.0 V to 1.0 V 110

Analog Input for Converter B 0.0 V to 1.0 V 100

DD

3.3 V CMOS 83

Analog Power Supply 3.3 V ± 10%

Output Power Supply 3.3 V ± 10%

PLL Power Supply 3.3 V ± 10%

Sync Detect Output 3.3 V CMOS 136

Input for SCAN Function 3.3 V CMOS 129

Output for SCAN Function 3.3 V CMOS 45

Clock for SCAN Function 3.3 V CMOS 50

56, 57, 59,

60, 62, 63,

65, 66,

71–73, 137

–6–

REV. 0

AD9886

PIN FUNCTION DETAIL

Inputs

R

AIN

G

AIN

B

AIN

Analog Input for RED Channel

Analog Input for GREEN Channel

Analog Input for BLUE Channel

High-impedance inputs that accept the RED,

GREEN, and BLUE channel graphics signals,

respectively. (The three channels are identical and can be used for any colors, but colors

are assigned for convenient reference.)

They accommodate input signals ranging

from 0.5 V to 1.0 V full scale. Signals should

be ac-coupled to these pins to support clamp

operation.

HSYNC Horizontal Sync Input

This input receives a logic signal that establishes the horizontal timing reference and

provides the frequency reference for pixel

clock generation.

The logic sense of this pin is controlled by

serial register 0Fh Bit 7 (HSYNC Polarity).

Only the leading edge of HSYNC is active,

the trailing edge is ignored. When HSYNC

Polarity = 0, the falling edge of HSYNC is

used. When HSYNC Polarity = 1, the rising

edge is active.

The input includes a Schmitt trigger for noise

immunity, with a nominal input threshold

of 1.5 V.

Electrostatic Discharge (ESD) protection

diodes will conduct heavily if this pin is driven

more than 0.5 V above the maximum tolerance voltage (3.3 V), or more than 0.5 V

below ground.

VSYNC Vertical Sync Input

This is the input for vertical sync.

SOGIN Sync-on-Green Input

This input is provided to assist with processing

signals with embedded sync, typically on the

GREEN channel. The pin is connected to a

high-speed comparator with an internally generated threshold, which is set to 0.15 V above

the negative peak of the input signal.

When connected to an ac-coupled graphics

signal with embedded sync, it will produce a

noninverting digital output on SOGOUT.

(This is usually a composite sync signal,

containing both vertical and horizontal sync

information that must be separated before

passing the horizontal sync signal to HSYNC).

When not used, this input should be left

unconnected. For more details on this function and how it should be configured, refer to

the Sync on Green section.

CLAMP External Clamp Input

This logic input may be used to define the

time during which the input signal is clamped

to the reference dc level (ground for RGB or

midscale for YUV). It should be exercised

when the reference dc level is known to be

present on the analog input channels, typically during the back porch of the graphics

signal. The CLAMP pin is enabled by setting

control bit EXTCLMP to 1 (the default

power-up is 0). When disabled, this pin is

ignored and the clamp timing is determined

internally by counting a delay and duration

from the trailing edge of the HSYNC input.

The logic sense of this pin is controlled by

CLAMPOL. When not used, this pin must be

grounded and EXTCLMP programmed to 0.

COAST Clock Generator Coast Input (Optional)

This input may be used to cause the pixel

clock generator to stop synchronizing with

HSYNC and continue producing a clock at

its current frequency and phase. This is useful

when processing signals from sources that fail

to produce horizontal sync pulses when in the

vertical interval. The COAST signal is generally not required for PC-generated signals.

The logic sense of this pin is controlled by

COAST Polarity.

When not used, this pin may be grounded

and COAST Polarity programmed to 1, or tied

HIGH (to V

through a 10 kΩ resistor) and

D

COAST Polarity programmed to 0. COAST

Polarity defaults to 1 at power-up.

CKEXT External Clock Input (Optional)

This pin may be used to provide an external

clock to the AD9886, in place of the clock

internally generated from HSYNC.

It is enabled by programming EXTCLK to 1.

When an external clock is used, all other internal functions operate normally. When unused,

this pin should be tied through a 10 kΩ resistor

to GROUND, and EXTCLK programmed to

0. The clock phase adjustment still operates

when an external clock source is used.

CKINV Sampling Clock Inversion (Optional)

This pin may be used to invert the pixel

sampling clock, which has the effect of

shifting the sampling phase 180°. This is in

support of Alternate Pixel Sampling mode,

wherein higher-frequency input signals (up

to 280 Mpps) may be captured by first sampling the odd pixels, then capturing the even

pixels on the subsequent frame.

This pin should be exercised only during

blanking intervals (typically vertical blanking)

as it may produce several samples of corrupted

data during the phase shift.

CKINV should be grounded when not used.

REV. 0

–7–

AD9886

Outputs

DRA

D

RB7-0

D

GA7-0

D

GB7-0

D

BA7-0

D

BB7-0

7-0

Data Output, Red Channel, Port A

Data Output, Red Channel, Port B

Data Output, Green Channel, Port A

Data Output, Green Channel, Port B

Data Output, Blue Channel, Port A

Data Output, Blue Channel, Port B

These are the main data outputs. Bit 7 is

the MSB.

Each channel has two ports. When the part is

operated in single-channel mode (DEMUX =

0), all data are presented to Port A, and Port B

is placed in a high-impedance state.

Programming DEMUX to 1 established dualchannel mode, wherein alternate pixels are

presented to Port A and Port B of each channel. These will appear simultaneously, two

pixels presented at the time of every second

input pixel, when PAR is set to 1 (parallel

mode). When PAR = 0, pixel data appear

alternately on the two ports, one new sample

with each incoming pixel (interleaved mode).

In dual channel mode, the first pixel after

HSYNC is routed to Port A. The second

pixel goes to Port B, the third to A, etc. This

can be reversed by setting OUTPHASE to 1.

The delay from pixel sampling time to output

is fixed. When the sampling time is changed

by adjusting the PHASE register, the output

timing is shifted as well. The DATACK,

DATACK, and HSOUT outputs are also

moved, so the timing relationship among the

signals is maintained.

DATACK Data Output Clock

DATACK Data Output Clock Complement

Differential data clock output signals to be

used to strobe the output data and HSOUT

into external logic.

They are produced by the internal clock generator and are synchronous with the internal

pixel sampling clock.

When the AD9886 is operated in singlechannel mode, the output frequency is equal

to the pixel sampling frequency. When operating in dual channel mode, the clock frequency

is one-half the pixel frequency, as is the output

data frequency.

When the sampling time is changed by adjusting the PHASE register, the output timing

is shifted as well. The Data, DATACK,

DATACK, and HSOUT outputs are all

moved, so the timing relationship among the

signals is maintained.

Either or both signals may be used, depending on the timing mode and interface design

employed.

HSOUT Horizontal Sync Output

A reconstructed and phase-aligned version of

the Hsync input. Both the polarity and duration of this output can be programmed via

serial bus registers.

By maintaining alignment with DATACK,

DATACK, and Data, data timing with

respect to horizontal sync can always be

determined.

SOGOUT Sync-On-Green Slicer Output

This pin can be programmed to output

either the output from the Sync-On-Green

slicer comparator or an unprocessed but

delayed version of the HSYNC input. See

the Sync Block Diagram to view how this

pin is connected.

(Note: Besides slicing off SOG, the output

from this pin receives no additional processing on the AD9886. VSYNC separation is

performed via the sync separator.)

REFOUT Internal Reference Output

Output from the internal 1.25 V bandgap

reference. This output is intended to drive

relatively light loads. It can drive the AD9886

Reference Input directly, but should be externally buffered if it is used to drive other loads

as well.

The absolute accuracy of this output is ±4%,

and the temperature coefficient is ±50 ppm,

which is adequate for most AD9886 applications. If higher accuracy is required, an

external reference may be employed instead.

If an external reference is used, connect this

pin to ground through a 0.1 µF capacitor.

REFIN Reference Input

The reference input accepts the master reference voltage for all AD9886 internal circuitry

(1.25 V ±10%). It may be driven directly by

the REFOUT pin. Its high impedance presents a very light load to the reference source.

This pin should always be bypassed to Ground

with a 0.1 µF capacitor.

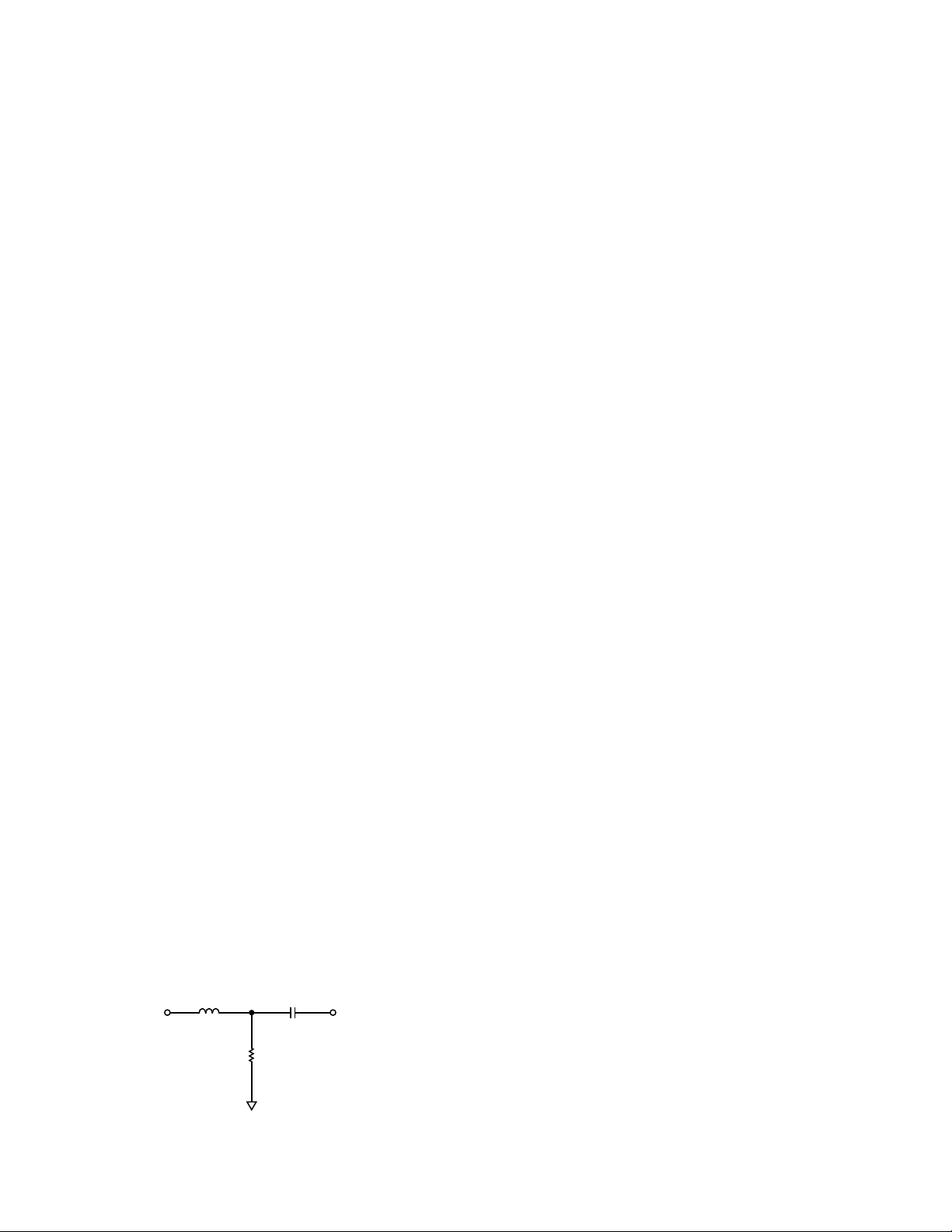

FILT External Filter Connection

For proper operation, the pixel clock generator PLL requires an external filter. Connect

the filter shown Figure 7 to this pin. For

optimal performance, minimize noise and

parasitics on this node.

–8–

REV. 0

AD9886

Power Supply

V

D

Main Power Supply

These pins supply power to the main elements of the circuit. It should be as quiet and

filtered as possible.

V

DD

Digital Output Power Supply

A large number of output pins (up to 52)

switching at high speed (up to 140 MHz)

generates a lot of power supply transients

(noise). These supply pins are identified

separately from the V

can be taken to minimize output noise transferred into the sensitive analog circuitry.

If the AD9886 is interfacing with lowervoltage logic, V

lower supply voltage (as low as 2.5 V) for

compatibility.

PV

D

Clock Generator Power Supply

The most sensitive portion of the AD9886 is

the clock generation circuitry. These pins

provide power to the clock PLL and help the

user design for optimal performance. The

designer should provide “quiet,” noise-free

power to these pins.

GND Ground

The ground return for all circuitry on chip.

It is recommended that the AD9886 be

assembled on a single solid ground plane,

with careful attention to ground current paths.

pins so special care

D

may be connected to a

DD

Serial Port (Two-Wire)

SDA Serial Port Data I/O

SCL Serial Port Data Clock

A0 Serial Port Address Input 1

A1 Serial Port Address Input 2

For a full description of the 2-wire serial register and how it works, refer to the Control

Register section.

SCAN Function

SCAN

IN

Data Input for SCAN Function

Data can be loaded serially into the 48-bit

SCAN register through this pin, clocking it in

with the SCAN

pin. It then comes out of

CLK

the 48 data outputs in parallel. This function

is useful for loading known data into a graphics controller chip for testing purposes.

SCAN

OUT

Data Output for SCAN Function

The data in the 48-bit SCAN register can be

read through this pin. Data is read on a FIFO

basis and is clocked via the SCAN

SCAN

CLK

Data Clock for SCAN Function

This pin clocks the data through the SCAN

register. It controls both data input and

data output.

CLK

pin.

REV. 0

–9–

AD9886

DESIGN GUIDE

General Description

The AD9886 is a fully integrated solution for capturing analog

RGB signals and digitizing them for display on flat panel monitors

or projectors. The circuit is ideal for providing a computer

interface for HDTV monitors or as the front end to highperformance video scan converters.

Implemented in a high-performance CMOS process, the interface can capture signals with pixel rates of up to 140 MHz and

with an Alternate Pixel Sampling mode, up to 280 MHz.

The AD9886 includes all necessary input buffering, signal dc

restoration (clamping), offset and gain (brightness and contrast)

adjustment, pixel clock generation, sampling phase control,

and output data formatting. All controls are programmable via

a 2-wire serial interface. Full integration of these sensitive analog

functions makes system design straightforward and less sensitive to the physical and electrical environment.

With a typical power dissipation of less than 750 mW and an

operating temperature range of 0°C to 70°C, the device requires

no special environmental considerations.

Input Signal Handling

The AD9886 has three high-impedance analog input pins for

the Red, Green, and Blue channels. They will accommodate

signals ranging from 0.5 V to 1.0 V p-p.

Signals are typically brought onto the interface board via a

DVI-I connector, a 15-pin D connector, or via BNC connectors.

The AD9886 should be located as close as practical to the

input connector. Signals should be routed via matched-impedance traces (normally 75 Ω) to the IC input pins.

At that point the signal should be resistively terminated (75 Ω

to the signal ground return) and capacitively coupled to the

AD9886 inputs through 47 nF capacitors. These capacitors

form part of the dc restoration circuit.

In an ideal world of perfectly matched impedances, the best

performance can be obtained with the widest possible signal

bandwidth. The ultrawide bandwidth inputs of the AD9886

(330 MHz) can track the input signal continuously as it moves

from one pixel level to the next, and digitize the pixel during a

long, flat pixel time. In many systems, however, there are mismatches, reflections, and noise, which can result in excessive

ringing and distortion of the input waveform. This makes it

more difficult to establish a sampling phase that provides good

image quality. It has been shown that a small inductor in series

with the input is effective in rolling off the input bandwidth

slightly, and providing a high quality signal over a wider range

of conditions. Using a Fair-Rite #2508051217Z0 High-Speed

Signal Chip Bead inductor in the circuit of Figure 1 gives good

results in most applications.

RGB

INPUT

47nF

75⍀

R

AIN

G

AIN

B

AIN

Figure 1. Analog Input Interface Circuit

HSYNC, VSYNC Inputs

The AD9886 takes a horizontal sync signal, which is used to

generate the pixel clock and clamp timing. It is possible to operate the AD9886 without applying HSYNC (using an external

clock, external clamp, and single port output mode) but a number

of features of the chip will be unavailable, so it is recommended

that HSYNC be provided. This can be either a sync signal

directly from the graphics source, or a preprocessed TTL or

CMOS level signal.

The HSYNC input includes a Schmitt trigger buffer for immunity

to noise and signals with long rise times. In typical PC-based

graphic systems, the sync signals are simply TTL-level drivers

feeding unshielded wires in the monitor cable. As such, no termination is required or desired.

Serial Control Port

The serial control port is designed for 3.3 V logic. If there are

5 V drivers on the bus, these pins should be protected with

150 Ω series resistors placed between the pull-up resistors and

the input pins.

Output Signal Handling

The digital outputs are designed and specified to operate from a

3.3 V power supply (V

). They can also work with a VDD as

DD

low as 2.5 V for compatibility with other 2.5 V logic.

Clamping

RGB Clamping

To properly digitize the incoming signal, the dc offset of the

input must be adjusted to fit the range of the on-board A/D

converters.

Most graphics systems produce RGB signals with black at

ground and white at approximately 0.75 V. However, if sync

signals are embedded in the graphics, the sync tip is often at

ground and black is at 300 mV. Then white is at approximately

1.0 V. Some common RGB line amplifier boxes use emitterfollower buffers to split signals and increase drive capability.

This introduces a 700 mV dc offset to the signal, which must be

removed for proper capture by the AD9886.

The key to clamping is to identify a portion (time) of the signal

when the graphic system is known to be producing black. An

offset is then introduced which results in the A/D converters

producing a black output (code 00h) when the known black

input is present. The offset then remains in place when other

signal levels are processed, and the entire signal is shifted to

eliminate offset errors.

In most graphics systems, black is transmitted between active

video lines. Going back to CRT displays, when the electron

beam has completed writing a horizontal line on the screen (at

the right side), the beam is quickly deflected to the left side of

the screen (called horizontal retrace) and a black signal is provided to prevent the beam from disturbing the image.

In systems with embedded sync, a blacker-than-black signal

(HSYNC) is produced briefly to signal the CRT that it is time

to begin a retrace. For obvious reasons, it is important to avoid

clamping on the tip of HSYNC. Fortunately, there is virtually

always a period following HSYNC called the back porch where

a good black reference is provided. This is the time when clamping should be done.

–10–

REV. 0

Loading...

Loading...