Analog Devices AD9101SE, AD9101AR, AD9101AE Datasheet

125 MSPS Monolithic

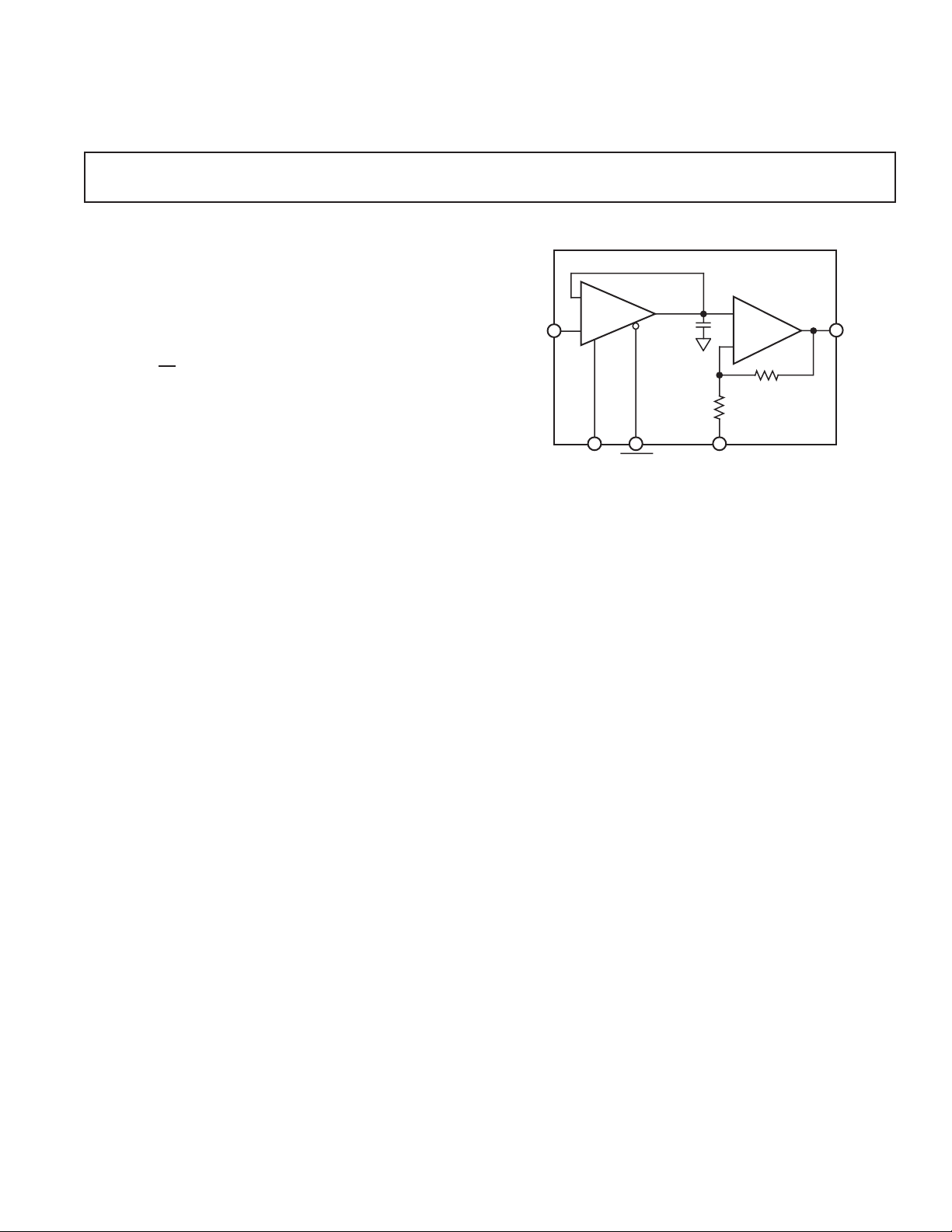

CLOCK CLOCK

V

IN

C

HOLD

4X

AMP

+

RTN

R

3R

–

+

SAMPLER

–

AD9101

V

OUT

a

Sampling Amplifier

AD9101

FEATURES

350 MHz Sampling Bandwidth

125 MHz Sampling Rate

Excellent Hold Mode Distortion

–75 dB @ 50 MSPS (25 MHz V

–57 dB @ 125 MSPS (50 MHz V

7 ns Acquisition Time to 0.1%

<1 ps Aperture Jitter

66 dB Feedthrough Rejection @ 50 MHz

3.3 nV/√ APPLICATIONS

Direct IF Sampling

Digital Sampling Oscilloscopes

HDTV Cameras

Peak Detectors

Radar/EW/ECM

Spectrum Analysis

Test Equipment/CCD Testers

DDS DAC Deglitcher

Hz Spectral Noise Density

)

IN

)

IN

The benefits of using a track-and-hold ahead of a flash converter

have been well known for many years. However, before the

AD9101, there was no track-and-hold amplifier with sufficient

GENERAL DESCRIPTION

The AD9101 is an extremely accurate, general purpose, high

speed sampling amplifier. Its fast and accurate acquisition speed

allows for a wide range of frequency vs. resolution performance.

The AD9101 is capable of 8 to 12 bits of accuracy at clock rates

of 125 MSPS or 50 MSPS, respectively. This level of performance makes it an ideal driver for almost all 8- to 12-bit A/D

encoders on the market today.

In effect, the AD9101 is a track-and-hold with a post amplifier.

This configuration allows the front end sampler to operate at

relatively low signal amplitudes. This results in dramatic improvement in both track and hold mode distortion while keeping

power low.

The gain-of-four output amplifier has been optimized for fast

and accurate large signal step settling characteristics even when

heavily loaded. This amplifier’s fast Settling Time Linearity

(STL) characteristic causes the amplifier to be transparent to

the low signal level distortion of the sampler. When sampled,

output distortion levels reflect only the distortion performance

of the sampler.

Dramatic SNR and distortion improvements can be realized

when using the AD9101 with high speed flash converters. Flash

bandwidth and linearity to markedly increase the dynamic performance of such flashes as the AD9002, AD9012, AD9020,

and AD9060.

A new application made possible by the AD9101 is direct IFto-digital conversion. Using the Nyquist principle, the IF

frequency can be rejected and the baseband signal can be

recovered. As an example, a 40 MHz IF is modulated by a

10 MHz bandwidth signal. By sampling at 25 MSPS, the signal

of interest is detected.

The AD9101 is offered in commercial and military temperature

ranges. Commercial versions include the AD9101AR in plastic

SOIC and AD9101AE in ceramic LCC. Military devices are

available in ceramic LCC. Contact the factory for availability of

versions in DIP and/or military versions.

PRODUCT HIGHLIGHTS

1. Guaranteed Hold-Mode Distortion

2. 125 MHz Sampling Rate to 8 Bits; 50 MHz to 12 Bits

3. 350 MHz Sampling Bandwidth

4. Super-Nyquist Sampling Capability

5. Output Offset Adjustable

converters generally have excellent linearity at dc and low frequencies. However, as signal slew rate increases, their performance degrades due to the internal comparators’ aperture delay

variations and finite gain bandwidth product.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 World Wide Web Site: http://www.analog.com

Fax: 617/326-8703 © Analog Devices, Inc., 1997

FUNCTIONAL BLOCK DIAGRAM

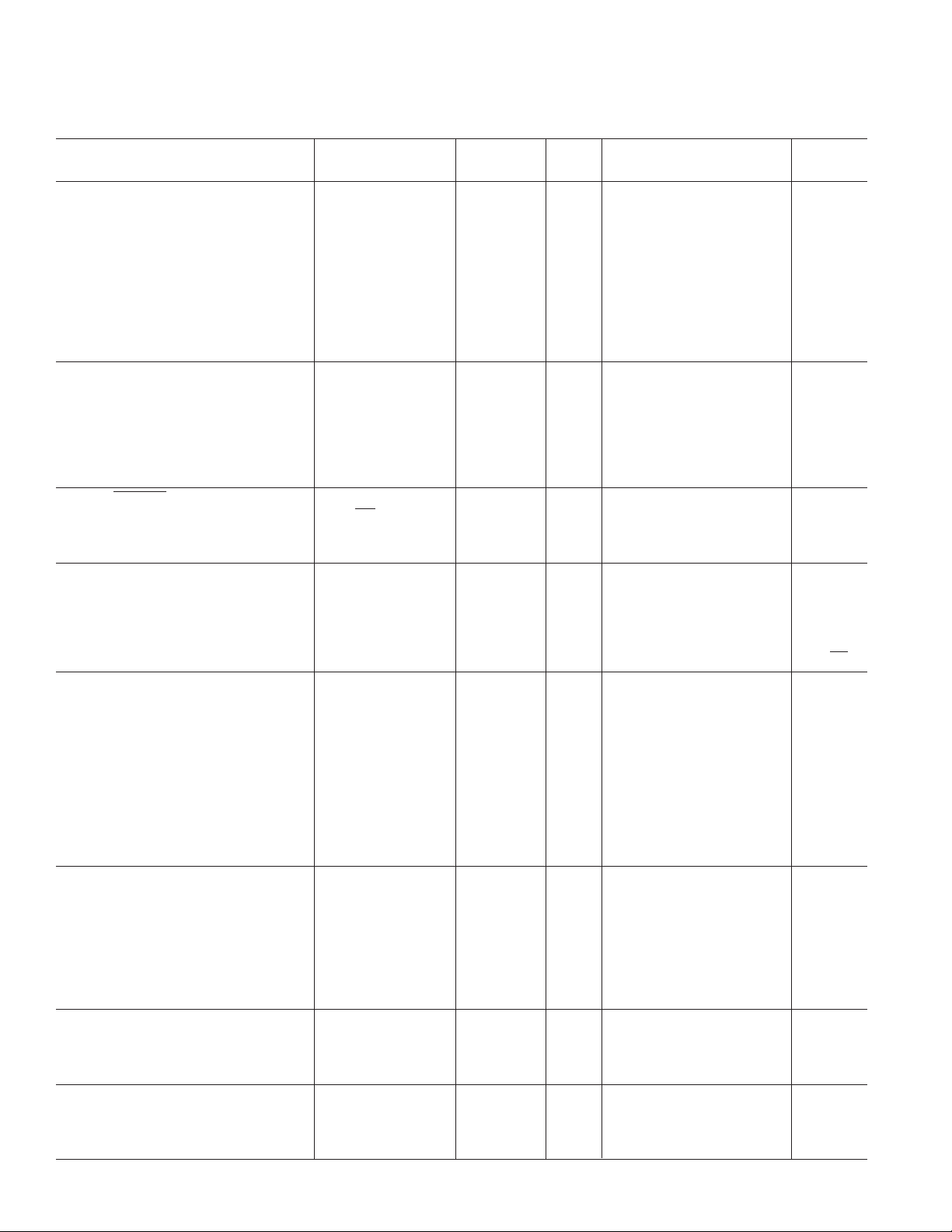

AD9101–SPECIFICA TIONS

ELECTRICAL CHARACTERISTICS

(+VS = +5 V, –VS = –5.2 V, R

= 100 V, RlN = 50 V unless otherwise noted)

LOAD

Test AD9101

Parameter Conditions Temp Level Min Typ Max Units

DC ACCURACY

Gain ∆V

Offset V

= 0.5 V 25°C I 3.93 4 4.07 V/V

IN

∆V

= 0.5 V Full VI 3.9 4.1 V/V

IN

= 0 V 25°CI ±3±10 mV

IN

V

= 0 V Full VI ±15 mV

IN

Output Resistance 25°C V 0.4 Ω

Output Drive Capability Full VI ±60 ± 70 mA

PSRR ∆V

Pedestal Sensitivity to Positive Supply ∆V

= 0.5 V p-p 25°CVI3743 dB

S

= 0.5 V p-p Full V 4 mV/V

S

Pedestal Sensitivity to Negative Supply ∆VS = 0.5 V p-p Full V 8 mV/V

ANALOG INPUT/OUTPUT

Output Voltage Range Full VI ±2.4 ±2.7 V

Input Bias Current 25°CI ±5±15 µA

Full VI ±20 µA

Input Capacitance 25°CV 2 pF

Input Resistance 25°C–T

T

MIN

CLOCK/

CLOCK INPUTS

Input Bias Current CL/

Input Low Voltage (V

Input High Voltage (VIH)

1

)

IL

1

VIN = 0.5 V p-p Full VI –1.8 –1.5 V

VIN = 0.5 V p-p Full VI –1.0 –0.8 V

CL = –1.0 V Full VI 3 3.6 mA

VI 30 125 kΩ

MAX

VI 25 kΩ

TRACK MODE DYNAMICS

Bandwidth (–3 dB) V

Slew Rate 4 Volt Output Step Full IV 1300 1800 V/µs

Overdrive Recovery Time

2

(to 0.1%) VIN = ±1 V to 0 V 25°CV 55 ns

= 1 V p-p Full IV 160 250 MHz

OUT

Integrated Output Noise (5 MHz–200 MHz) 25°C V 210 µV

Input RMS Spectral Noise @ 10 MHz 25°C V 3.3 µV/√Hz

HOLD MODE DYNAMICS

Worst Harmonic (23 MHz, 50 MSPS) V

Worst Harmonic (48 MHz, 100 MSPS) V

Worst Harmonic (48 MHz, 100 MSPS) V

Worst Harmonic (48 MHz, 100 MSPS) V

Worst Harmonic (48 MHz, 125 MSPS) V

Sampling Bandwidth (–3 dB)

Hold Noise

4

(RMS) Full V 150 × t

3

= 2 V p-p 25°C V –75 dBFS

OUT

= 2 V p-p 25°C IV –62 –57 dBFS

OUT

= 2 V p-p Full (Ind.) IV –53 dBFS

OUT

= 2 V p-p Full (Mil.) IV –51 dBFS

OUT

= 2 V p-p 25°C V –57 dBFS

OUT

VIN = 0.5 V p-p 25°C V 350 MHz

H

mV/s

Droop Rate 25°CI ±5±18 mV/µs

Full VI ±40 mV/µs

Feedthrough Rejection (50 MHz) V

= 2 V p-p Full V –66 dB

OUT

TRACK-TO-HOLD SWITCHING

Aperture Delay 25°C V –250 ps

Aperture Jitter 25°C V <1 ps rms

Pedestal Offset V

Transient Amplitude V

Settling Time to 4 mV V

Glitch Product

5

= 0 V 25°CI ±5±20 mV

IN

V

= 0 V Full VI ±35 mV

IN

= 0 V Full V 8 mV

IN

= 0 V Full V 4 ns

IN

VIN = 0 V 25°C V 20 pV-s

HOLD-TO-TRACK SWITCHING

Acquisition Time to 0.1% 2 V Output Step 25°CV 7 ns

Acquisition Time to 0.01% 2 V Output Step 25°CIV 1114ns

2 V Output Step Full IV 16 ns

POWER SUPPLY

+V

Current Full VI 55 70 mA

S

–V

Current Full VI 59 73 mA

S

Power Dissipation Full VI 570 715 mW

–2–

REV. 0

AD9101

T

NOTES

1

If the analog input exceeds ±300 mV, the clock levels should be shifted as shown in the Theory of Operation section entitled “Driving the Encode Clock.”

2

Time to recover within rated error band from 160% overdrive.

3

Sampling bandwidth is defined as the –3 dB frequency response of the input sampler to the hold capacitor when operating in the sampling mode. It is greater than

tracking bandwidth because it does not include the bandwidth of the output amplifier.

4

Hold mode noise is proportional to the length of time a signal is held. For example, if the hold time (t

(150 mV/s × 20 ns). This value must be combined with the track mode noise to obtain total noise.

5

Total energy of worst case track-to-hold or hold-to-track glitch.

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS

Supply Voltage (+VS) . . . . . . . . . . . . . . . . . . . . –0.5 V to +6 V

Supply Voltage (–V

) . . . . . . . . . . . . . . . . . . . . –6 V to +0.5 V

S

Analog Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±5 V

CLOCK/

Continuous Output Current

CLOCK Input . . . . . . . . . . . . . . . . . –5 V to +0.5 V

4

. . . . . . . . . . . . . . . . . . . . 70 mA

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range

AE, AR . . . . . . . . . . . . . . . . . . . . . . . . . . . . –40°C to +85°C

SE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –55°C to +125°C

Junction Temperature (Ceramic)

Junction Temperature (Plastic)

Soldering Temperature (1 minute)

NOTES

1

Absolute maximum ratings are limiting values to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability is not necessarily implied. Exposure to absolute maximum rating

conditions for an extended period of time may affect device reliability.

2

Typical thermal impedances (no air flow, soldered to PC board) are as follows:

Ceramic LCC: θJA = 48°C/W; θJC = 9.9°C/W; Plastic SOIC: θJA = 54°C/W;

θ

= 7.3°C/W.

JC

3

For surface mount devices, mounted by vapor phase soldering. Prior to vapor phase

soldering, plastic units should receive a minimum eight hour bakeout at 110°C to

drive off any moisture absorbed in plastic during shipping or storage. Through-hole

devices can be soldered at +300°C for 10 seconds.

4

Output is short circuit protected to ground. Continuous short circuit may affect

device reliability.

1

2

. . . . . . . . . . . . . . . +175°C

2

. . . . . . . . . . . . . . . . +150°C

3

. . . . . . . . . . . . . . +220°C

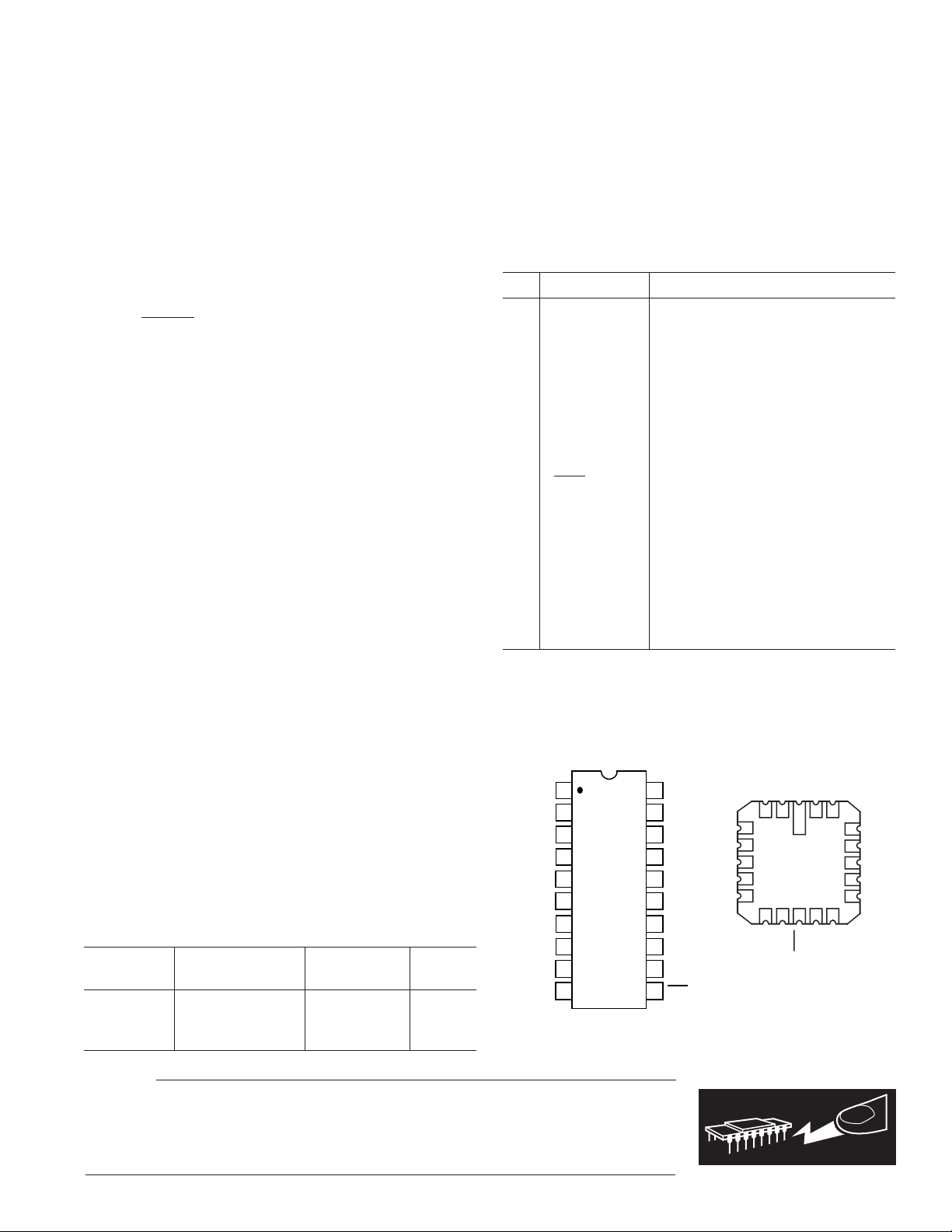

Pin Description

Pin Description Connection

1 RTN Gain Set Resistor Return*

2 RTN Gain Set Resistor Return*

3C

4+V

5+V

6 GND Hold Capacitor Ground

7 GND Hold Capacitor Ground

8+V

9+V

10 CLK True ECL T/H Clock

11

12 –V

13 –V

14 N/C No Connection

15 V

16 GND Ground (Signal Return)

17 –V

18 –V

19 C

20 V

*See “Matching the AD9101 to A/D Encoders.” Both pins should be either

grounded or connected to voltage source for offset.

EXPLANATION OF TEST LEVELS

Test Level

I – 100% production tested.

II – 100% production tested at +25°C, and sample tested at

specified temperatures.

III – Periodically sample tested.

IV – Parameter is guaranteed by design and characterization

testing.

V – Parameter is a typical value only.

VI – All devices are 100% production tested at +25°C. 100%

production tested at temperature extremes for extended

temperature devices; sample tested at temperature

extremes for commercial/industrial devices.

ORDERING INFORMATION

Temperature Package Package

Model Range Description Option

RTN

RTN

C

+V

+V

GND

GND

+V

+V

CLK

B+

AD9101AR –40°C to +85°C Plastic SOIC R-20

AD9101AE –40 °C to +85°C LCC E-20A

AD9101SE –55 °C to +125°C LCC E-20A

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9101 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

) is 20 ns, the accumulated noise is typically 3 µV

H

B+

S

S

S

S

Bootstrap Capacitor (Positive Bias)

+5 V Power Supply (Analog)

+5 V Power Supply (Analog)

+5 V Power Supply (Digital)

+5 V Power Supply (Digital)

CLK Complement ECL T/H Clock

S

S

IN

S

S

B–

OUT

–5.2 V Power Supply (Digital)

–5.2 V Power Supply (Digital)

Analog Signal Input

–5.2 V Power Supply (Analog)

–5.2 V Power Supply (Analog)

Bootstrap Capacitor (Negative Bias)

Analog Signal Output

PIN CONFIGURATIONS

20-Pin SOIC

1

2

3

4

S

AD9101

5

S

TOP VIEW

(Not to Scale)

6

7

8

S

9

S

10

V

20

C

19

–V

18

–V

17

GND

16

15

V

14

NC

–V

13

–V

12

11

CLK

20-Contact Ceramic LCC

OU

B–

V

S

S

IN

C

19

18

17

16

BOTTOM VIEW

15

14

13

S

–V

20

S

–V

OUT

B–

IN

–V

S

–V

S

GND

V

NC

S

S

1112

1

RTN

23

CLK

RTN

CLK

WARNING!

ESD SENSITIVE DEVICE

B+

C

4

5

6

7

8

910

S

+V

+V

+V

GND

GND

+V

S

S

S

REV. 0

–3–

AD9101

Acquisition Time is the amount of time it takes the AD9101

to reacquire the analog input when switching from hold to track

mode. The interval starts at the 50% clock transition point and

ends when the input signal is reacquired to within a specified

error band at the hold capacitor.

Aperture Delay establishes when the input signal is actually

sampled. It is the time difference between the analog propagation delay of the front-end buffer and the control switch delay

time (the time from the hold command transition to when the

switch is opened). For the AD9101, this is a negative value,

meaning that the analog delay is longer than the switch delay.

Aperture Jitter is the random variation in the aperture delay.

This is measured in ps-rms and is manifested as phase noise on

the held signal.

Droop Rate is the change in output voltage as a function of

time (dV/dt). It is measured at the AD9101 output with the device in hold mode and the input held at a specified dc value; the

measurement starts immediately after the T/H switches from

track to hold.

Feedthrough Rejection is the ratio of the output signal to the

input signal when in hold mode. This is a measure of how well

the switch isolates the input signal from feeding through to the

output.

+2V

Hold-to-Track Switch Delay is the time delay from the track

command to the point when the output starts to change to acquire a new signal level.

Pedestal Offset is the offset voltage measured immediately after the AD9101 is switched from track to hold with the input

held at zero volts. It manifests itself as a dc offset during the

hold time.

Sampling Bandwidth is the –3 dB frequency response from

the input to the hold capacitor under sampling conditions. It is

greater than the tracking bandwidth because it does not include

the bandwidth of the output amplifier which is optimized for

settling time rather than bandwidth.

Track-to-Hold Settling Time is the time necessary for the

track to hold switching transient to settle to within 4 mV of its

final value.

Track-to-Hold Switching Transient is the maximum peak

switch induced transient voltage which appears at the AD9101

output when it is switched from track to hold.

APERTURE

DELAY

(–0.25 ns)

ANALOG

INPUT (x 4)

SAMPLER OUTPUT SIGNAL (x 4)

AND AMPLIFIER OUTPUT SIGNAL

CLOCK

INPUTS

0V

-2V

+2V

0V

-2V

"1"

"0"

ACQUISITION

TIME (SEE

TEXT)

HOLD TO TRACK

SWITCH DELAY

TIME (1.5 ns)

CLOCK

"HOLD"

Timing Diagram (500 ps/div)

VOLTAGE

LEVEL HELD

OBSERVED AT

HOLD CAPACITOR

OBSERVED AT

AMPLIFIER OUTPUT

CLOCK

"TRACK"

TRACK TO

HOLD

SETTLING

(4 ns)

"HOLD"

CLOCK

–4–

REV. 0

Loading...

Loading...