Dual 6-Bit, 60 MSPS

a

FEATURES

Two Matched ADCs on Single Chip

CMOS-Compatible I/O

Low-Power (400 mW) Dissipation

Single +5 V Supply

On-Chip Voltage Reference

Self-Biased for AC-Coupled Inputs

28-Lead SOIC and SSOP Packages

APPLICATIONS

Direct Broadcast Satellite (DBS) Receivers

QAM Demodulators

Wireless LANs

VSAT Receivers

PRODUCT DESCRIPTION

The AD9066 is a dual 6-bit ADC that has been optimized for

low-cost in-phase and quadrature (I and Q) demodulators.

Primary applications include digital direct broadcast satellite

applications where broadband quadrature phase shift keying

(QPSK) modulation is used. In these receivers the recovered signal

is separated into I and Q vector components and digitized.

To reduce total system cost and power dissipation, the AD9066

provides an internal voltage reference and operates from a

single +5 volt power supply. Digital outputs are CMOS compatible and rated to 60 MSPS conversion rates. The digital

input (ENCODE) utilizes a CMOS input stage with a TTL

compatible (1.4 V) threshold.

The AD9066 is housed in a 28-lead SOIC and a 28-lead SSOP

package and is available in two temperature grades. The

AD9066JR is rated for operation over the 0°C to 70°C commercial temperature range. The AD9066AR/ARS is rated for the

–40°C to +85°C industrial temperature range.

The internal voltage reference insures that the analog input is

biased to midscale with low offset when driven from an accoupled source. In dc-coupled applications, the midscale voltage

reference can be used to control external biasing amplifiers to

minimize offsets due to variations in temperature or supply voltage.

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

Monolithic A/D Converter

AD9066

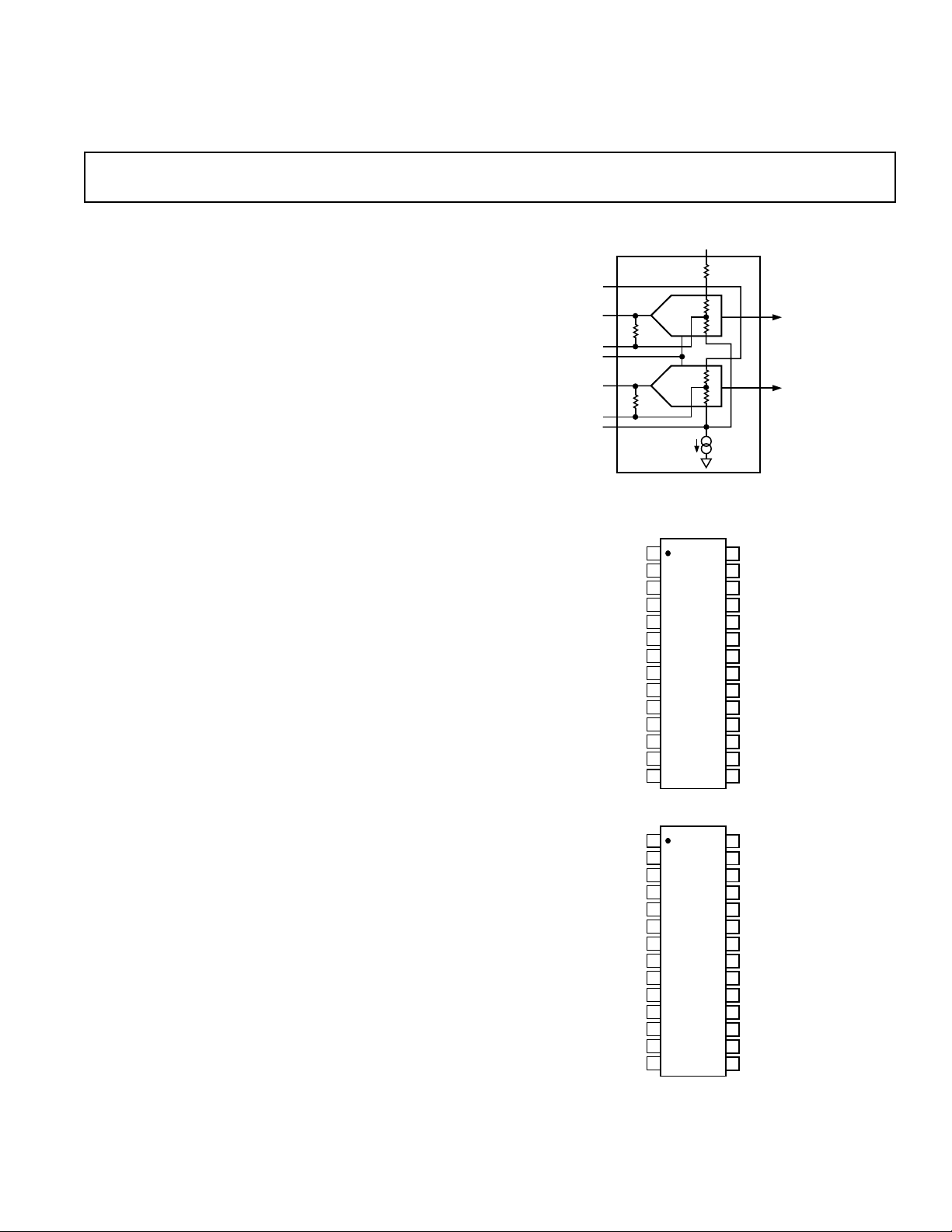

FUNCTIONAL BLOCK DIAGRAM

+V

S

AD9066

VT

INA

REF A

ENCODE

INB

REF B

VB

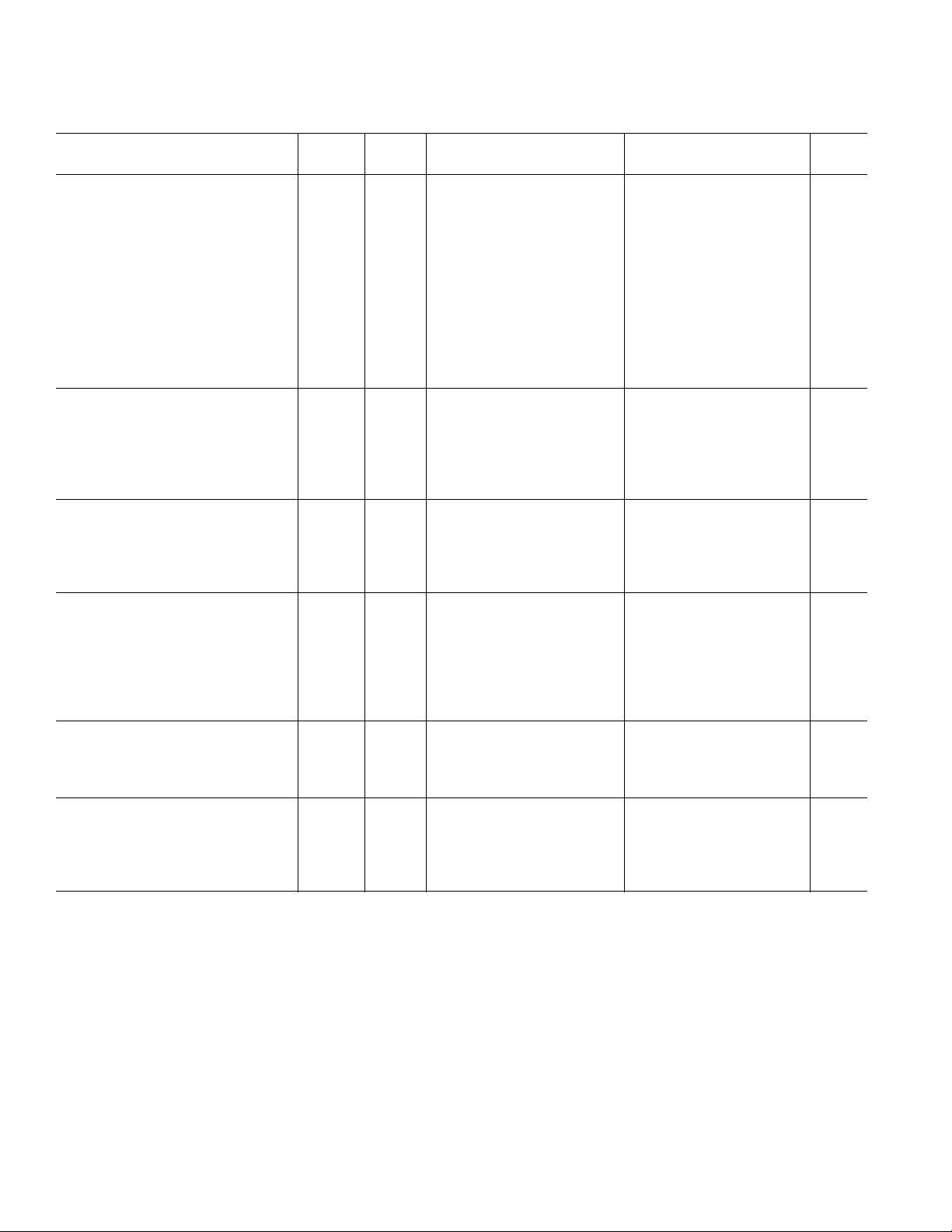

PIN CONFIGURATIONS

ENCODE D5A (MSB)

REF A D4B

REF B D2B

REF A

REF B

(LSB) D0B

(MSB) D5B

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

6-BIT

DAC

6-BIT

DAC

1

2

+V

S

3

GND D3A

4

GND D2A

5

+V

S

AD9066

6

INA D0A (LSB)

GND GND

+V

INB D3B

+V

INB

D1B

D2B

D3B

D4B

+V

(JR/AR)

7

TOP VIEW

(Not to Scale)

8

S

9

VT D5B (MSB)

10

11

12

13

VB D1B

14

NC D0B (LSB)

NC = NO CONNECT

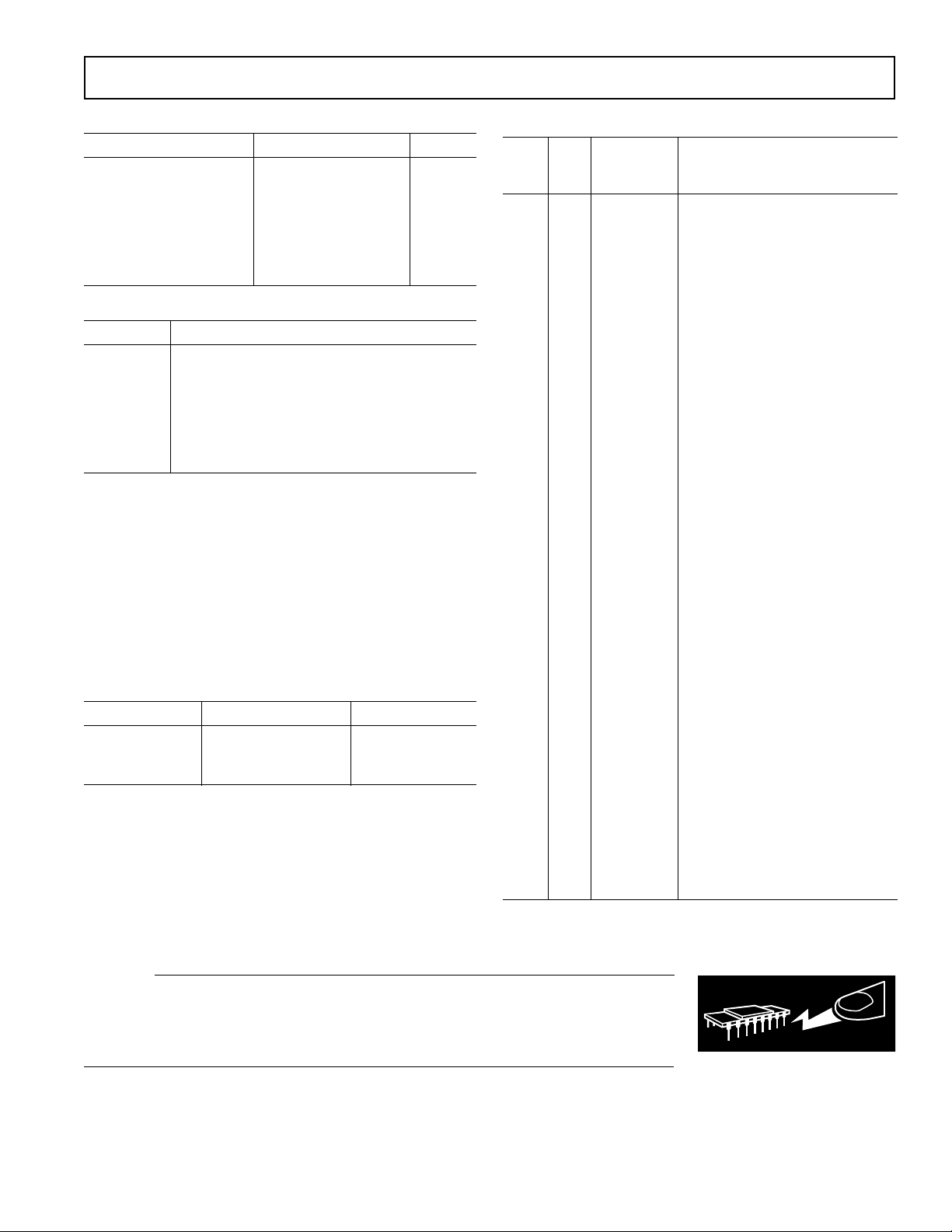

1

S

2

VT

3

4

5

AD9066

6

VB

NC

(ARS)

7

TOP VIEW

(Not to Scale)

8

9

10

11

12

13

14

S

NC = NO CONNECT

28

D4A

27

26

25

D1A

24

23

22

+V

21

20

19

18

17

16

15

28

GND

27

INA

26

+V

25

GND

24

GND

+V

23

22

ENCODE

21

D5A (MSB)

20

D4A

19

D3A

18

D2A

17

D1A

16

D0A (LSB)

15

GND

S

S

S

D0A-D5A

D0B-D5B

AD9066–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

(+VS = +5 V, AIN = 15.5 MHz, Encode Rate = 60 MSPS, TC = TA)

Test AD9066JR AD9066AR/ARS

Parameter Level Temp Min Typ Max Min Typ Max Unit

ANALOG INPUT

Full-Scale Input Range VI Full 475 500 525 450 500 530 mV

Gain Matching (FS Range) IV Full 16 16 mV

DC Input (Midscale)

Input Offset

1

1

V +25°C+V

– 1.1 +VS – 1.1 V

S

VI Full –1.0 +1.0 –1.0 +1.0 LSBs

Input Capacitance IV Full 10 15 10 15 pF

Input Resistance (DC) VI Full 25 45 55 22 45 57 kΩ

Input Bandwidth (3 dB) V +25°C 100 100 MHz

Gain Flatness (to 15 MHz) V +25°C 0.25 0.25 dB

Integral Linearity VI Full –1.0 +1.0 –1.0 +1.0 LSBs

Differential Linearity VI Full –0.5 +0.5 –0.5 +0.5 LSBs

Monotonicity VI Full Guaranteed Guaranteed

SWITCHING PERFORMANCE

Max Conversion Rate VI Full 60 60 MSPS

Output Delay (t

Output Delay (t

V

PD

2

)

2

)

IV Full 4 4 ns

IV Full 11 12 ns

Aperture Uncertainty (Jitter) V +25°C 10 10 ps rms

Aperture Time (tA) V +25°C 1.0 1.0 ns

DYNAMIC PERFORMANCE

3

Effective Number of Bits VI +25°C 5.3 5.7 5.2 5.7 Bits

SINAD VI +25°C3436 3336 dB

Harmonic Distortion (THD) VI +25°C4050 4050 dB

Crosstalk Rejection IV +25°C4050 4050 dBc

ENCODE INPUT

Logic High Voltage VI Full 2.0 2.0 V

Logic Low Voltage VI Full 0.8 0.8 V

Input High Current VI Full 500 500 µA

Input Low Current VI Full 500 500 µA

Pulsewidth High IV Full 7.0 7.0 ns

Pulsewidth Low IV Full 7.0 7.0 ns

DIGITAL OUTPUTS

Output Coding Full Offset Binary Offset Binary

Logic High Voltage (I

= 1 mA) VI Full 3.8 3.8 V

OH

Logic Low Voltage (IOL = 1 mA) VI Full 0.4 0.4 V

POWER SUPPLY

+VS Supply Voltage VI Full 4.75 5.25 4.75 5.25 V

Power Supply Rejection Ratio

Supply Current VI Full 80 120 80 120 mA

+V

S

Power Dissipation

NOTES

1

For ac coupled applications, the ADC is internally biased to insure that the midpoint transition of the ADC is within the limits specified with no signal applied. For

dc coupled applications, the dc value of the midpoint transition voltage will track the supply voltage within the limits shown for dc input (midscale) plus the dc offset.

Power Supply Rejection Ratio (PSRR) refers to the variation of the input signal range (gain) to supply voltage.

2

tV and tPD are measured from the 1.4 V level of the Clock and the 50% level between VOHand VOL. The ac load on all the digital outputs during test is 10 pF (max),

the dc load will not exceed ± 40 µA.

3

Effective number of bits (ENOB) and THD are measured using a FFT with a pure sine wave analog input @ 15.5 MHz, 1 dB below full scale. ENOB is calculated by

ENOB = (SNR – 1.76 dB)/6.02; THD is measured from full scale to the sum of the second through seventh harmonic of the input.

4

Typical thermal impedance for the “R” style (SOIC) 28-lead package is: θJC = 4°C/W, θCA = 41°C/W, θJA = 45°C/W, and the “RS” style (SSOP) 28-lead package is:

θJC = 26.97°C/W, θCA = 51.61°C/W, θJA = 78.58°C/W.

Specifications subject to change without notice.

4

1

IV Full 110 130 110 130 mV/V

VI Full 400 600 400 600 mW

–2–

REV. A

AD9066

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS

Pin Min Max Unit

ENCODE –0.5 +V

+V

S

7.0 V

INA, INB –0.5 +V

VT 2.5 +V

REF A, REF B –0.5 +V

VB 0.0 +V

S

S

S

S

S

V

V

V

V

V

D0–D5 Current OUT 20 mA

EXPLANATION OF TEST LEVELS

Test Level Description

I 100% Production Tested

II 100% Production Tested at +25°C, and

Sample Tested at Specified Temperatures

III Sample Tested Only

IV Parameter Is Guaranteed by Design

V Parameter Is Typical Value Only

VI 100% Tested at +25°C

DIE LAYOUT AND MECHANICAL INFORMATION

Die Dimensions . . . . . . . . . . . . . . . . . 132 × 68 × 21 (±1) mils

Pad Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 × 4 mils

Metalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Aluminum

Backing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . None

Substrate Potential . . . . . . . . . . . . . . . . . . . . . . . . . . . Ground

Transistor Count . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5,810

Passivation . . . . . . . . . . . . . . . . . . . . . . . . . . . . Silicon Nitride

Die Attach . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Silver Filled

Bond Wire . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Gold

ORDERING GUIDE

Model Temperature Range Package Option*

AD9066AR –40°C to +85°C R-28

AD9066JR 0°C to +70°C R-28

AD9066ARS –40°C to +85°C RS-28

*R = “SO” Small Outline Package; RS = SSOP.

PIN DESCRIPTIONS

AR:JR ARS

Pin Pin

No. No. Name Function

1 22 ENCODE TTL Compatible CMOS Clock,

Samples on Rising Edge.

223+V

S

+5 V Supply for Digital Input.

3 24 GND Ground.

4 25 GND Ground.

526+V

S

+5 V Supply (Analog).

6 27 INA Channel A Analog Input.

7 28 GND Ground.

81+V

S

+5 V Supply (Analog).

9 2 VT Top of Voltage Reference, Bypass

to GND.

10 3 REF A Mid Reference to ADC A, Bypass

to GND.

11 4 INB Channel B Analog Input.

12 5 REF B Mid Reference to ADC B, Bypass

to GND.

13 6 VB Bottom of Reference Ladder, By-

pass to GND.

14 7 NC No Connect.

15 8 D0B (LSB) Digital Outputs Channel B,

CMOS Compatible.

16 9 D1B

17 10 D2B

18 11 D3B

19 12 D4B

20 13 D5B (MSB)

21 14 +V

S

+5 V Supply for Digital Outputs.

22 15 GND Ground.

23 16 D0A (LSB) Digital Outputs Channel A,

CMOS Compatible.

24 17 D1A

25 18 D2A

26 19 D3A

27 20 D4A

28 21 D5A (MSB)

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD9066 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

REV. A

–3–

Loading...

Loading...