Analog Devices AD9058 Datasheet

Dual 8-Bit 50 MSPS

8

Q

8

I

RF

LO

G

G

AD9058

90°

a

FEATURES

Two Matched ADCs on Single Chip

50 MSPS Conversion Speed

On-Board Voltage Reference

Low Power (<1W)

Low Input Capacitance (10 pF)

65 V Power Supplies

Flexible Input Range

APPLICATIONS

Quadrature Demodulation for Communications

Digital Oscilloscopes

Electronic Warfare

Radar

GENERAL DESCRIPTION

The AD9058 combines two independent high performance

8-bit analog-to-digital converters (ADCs) on a single monolithic IC. Combined with an optional onboard voltage reference, the AD9058 provides a cost effective alternative for

systems requiring two or more ADCs.

Dynamic performance (SNR, ENOB) is optimized to provide

up to 50 MSPS conversion rates. The unique architecture

results in low input capacitance while maintaining high performance and low power (<0.5 watt/channel). Digital inputs

and outputs are TTL compatible.

Performance has been optimized for an analog input of 2 V

p-p (± 1 V; 0 V to +2 V). Using the onboard +2 V voltage

reference, the AD9058 can be set up for unipolar positive

operation (0 V to +2 V). This internal voltage reference can

drive both ADCs.

Commercial (0°C to +70°C) and military (–55°C to +125°C)

temperature range parts are available. Parts are supplied in

hermetic 48-lead DIP and 44-lead “J” lead packages.

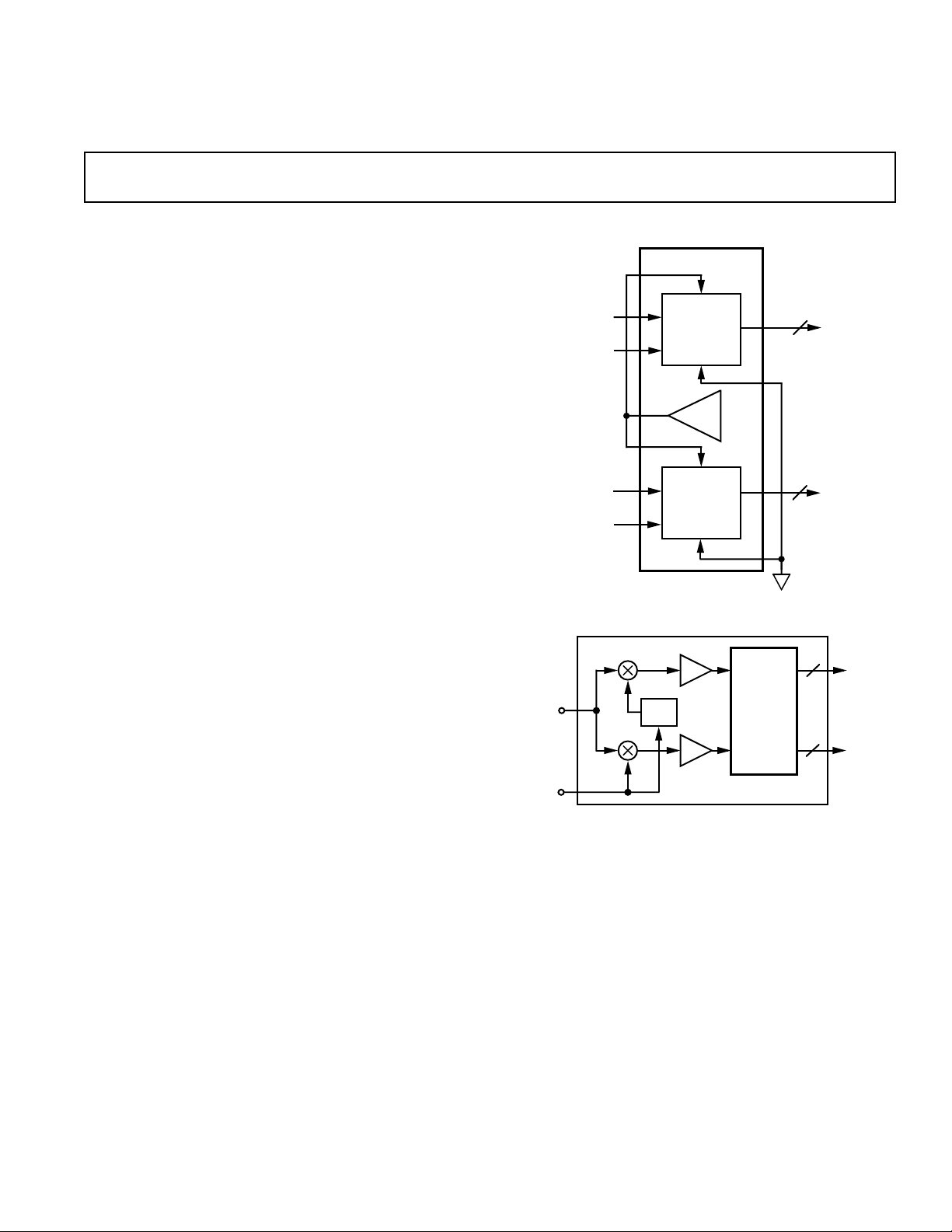

A/D Converter

AD9058

FUNCTIONAL BLOCK DIAGRAM

AD9058

+V

REF

8-BIT

ENCODE

A

IN

ENCODE

A

IN

QUADRATURE RECEIVER

ANALOG-

TO-

DIGITAL

CONVERTER

–V

REF

+2 V

REF

8-BIT

ANALOG-

TO-

DIGITAL

CONVERTER

–V

REF

+V

REF

8

A

8

B

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

AD9058–SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS

1

Analog Input . . . . . . . . . . . . . . . . . . . . . . . . .–1.5 V to +2.5 V

+V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +6 V

S

–V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +0.8 V to –6 V

S

Digital Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . –0.5 V to +V

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . 20 mA

Voltage Reference Current . . . . . . . . . . . . . . . . . . . . . . .53 mA

+V

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +2.5 V

REF

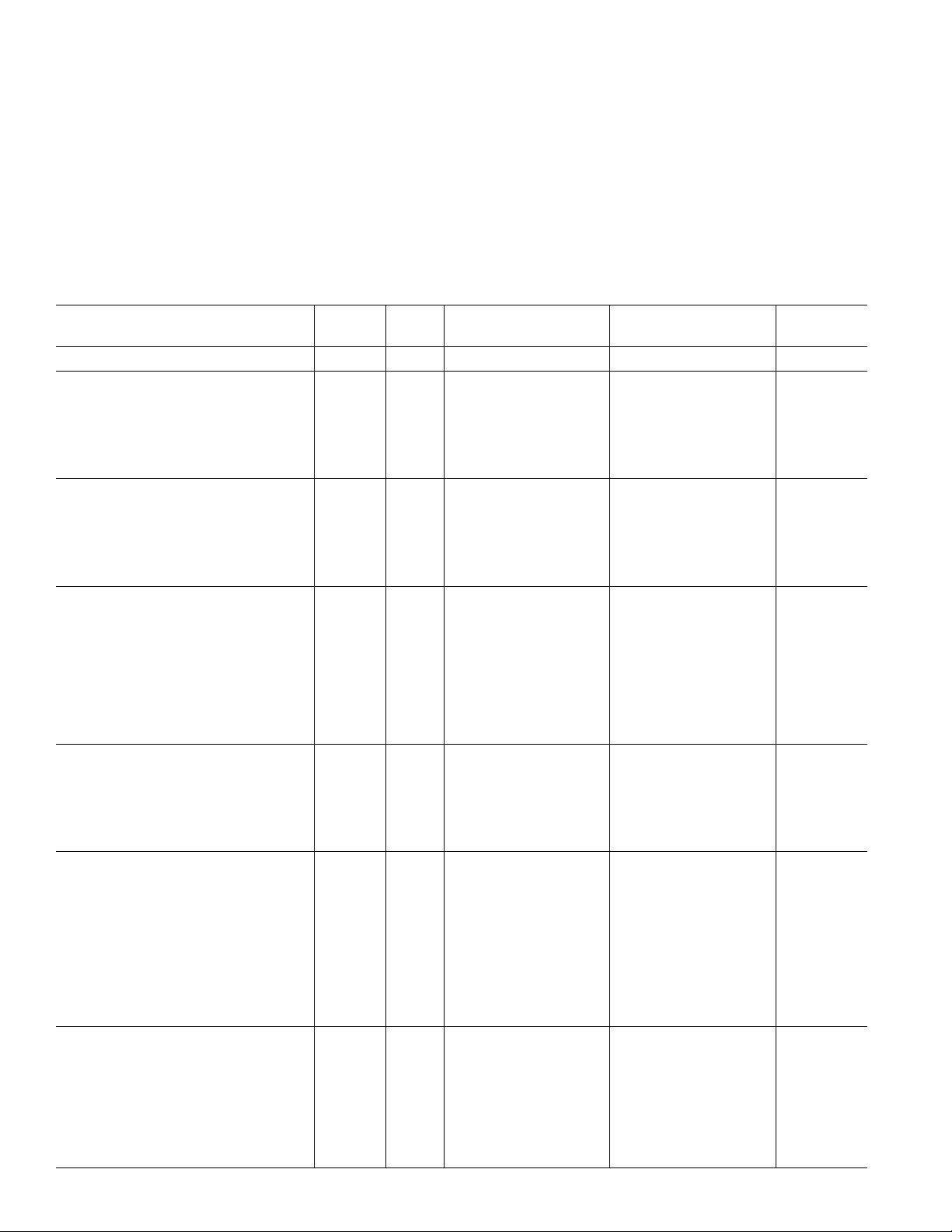

[ⴞVS = ⴞ5 V; V

ELECTRICAL CHARACTERISTICS

GROUND, unless otherwise noted.]2 All specifications apply to either of the two ADCs

–V

Operating Temperature Range

2

Maximum Junction Temperature

S

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . .+300°C

= +2 V (internal); ENCODE = 40 MSPS; AIN = 0 V to +2 V; –V

REF

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –1.5

REF

AD9058JD/JJ/KD/KJ . . . . . . . . . . . . . . . . . . . 0°C to +70°C

3

AD9058JD/JJ/KD/KJ . . . . . . . . . . . . . . . . . . . . . . . .+175°C

REF

Test AD9058JD/JJ AD9058KD/KJ

Parameter (Conditions) Temp Level Min Typ Max Min Typ Max Unit

RESOLUTION 8 8 Bits

DC ACCURACY

Differential Nonlinearity +25°C I 0.25 0.65 0.25 0.5 LSB

Full VI 0.8 0.7 LSB

Integral Nonlinearity +25°C I 0.5 1.3 0.5 1.0 LSB

Full VI 1.4 1.25 LSB

No Missing Codes Full VI GUARANTEED GUARANTEED

ANALOG INPUT

Input Bias Current +25°C I 75 170 75 170 µA

Full VI 340 340 µA

Input Resistance +25°C I 12 28 12 28 kΩ

Input Capacitance +25°CIV 1015 1015 pF

Analog Bandwidth +25°C V 175 175 MHz

REFERENCE INPUT

Reference Ladder Resistance +25°C I 120 170 220 120 170 220 Ω

Full VI 80 270 80 270 Ω

Ladder Tempco Full V 0.45 0.45 Ω/°C

Reference Ladder Offset +25°CI 8 16 8 16 mV

(Top) Full VI 24 24 mV

Reference Ladder Offset +25°CI 8 23 8 23 mV

(Bottom) Full VI 33 33 mV

Offset Drift Coefficient Full V 50 50 µV/°C

INTERNAL VOLTAGE REFERENCE

Reference Voltage +25°C I 1.95 2.0 2.20 1.95 2.0 2.20 V

Full VI 1.90 2.25 1.90 2.25 V

Temperature Coefficient Full V 150 150 µV/°C

Power Supply Rejection

Ratio (PSRR) +25°C I 10 25 10 25 mV/V

SWITCHING PERFORMANCE

Maximum Conversion Rate

Aperture Delay (t

) +25°C IV 0.1 0.8 1.5 0.1 0.8 1.5 ns

A

4

+25°C I 50 50 60 MSPS

Aperture Delay Matching +25°C IV 0.2 0 5 0.2 0.5 ns

Aperture Uncertainty (Jitter) +25°C V 10 10 ps, rms

Output Delay (Valid) (t

Output Delay (t

) Tempco Full V 16 16 ps/°C

V

Propagation Delay (t

Propagation Delay (t

4

)

V

4

)

PD

) Tempco Full V –16 –16 ps/°C

PD

+25°CI 8 5 8 ns

+25°C I 12 12 19 ns

Output Time Skew +25°CV 1 1 ns

ENCODE INPUT

Logic “1” Voltage Full VI 2 2 V

Logic “0” Voltage Full VI 0.8 0.8 V

Logic “1” Current Full VI 600 600 µA

Logic “0” Current Full VI 1000 1000 µA

Input Capacitance +25°CV 5 5 pF

Pulsewidth (High) +25°CI 8 8 ns

Pulsewidth (Low) +25°CI 8 8 ns

=

–2–

REV. B

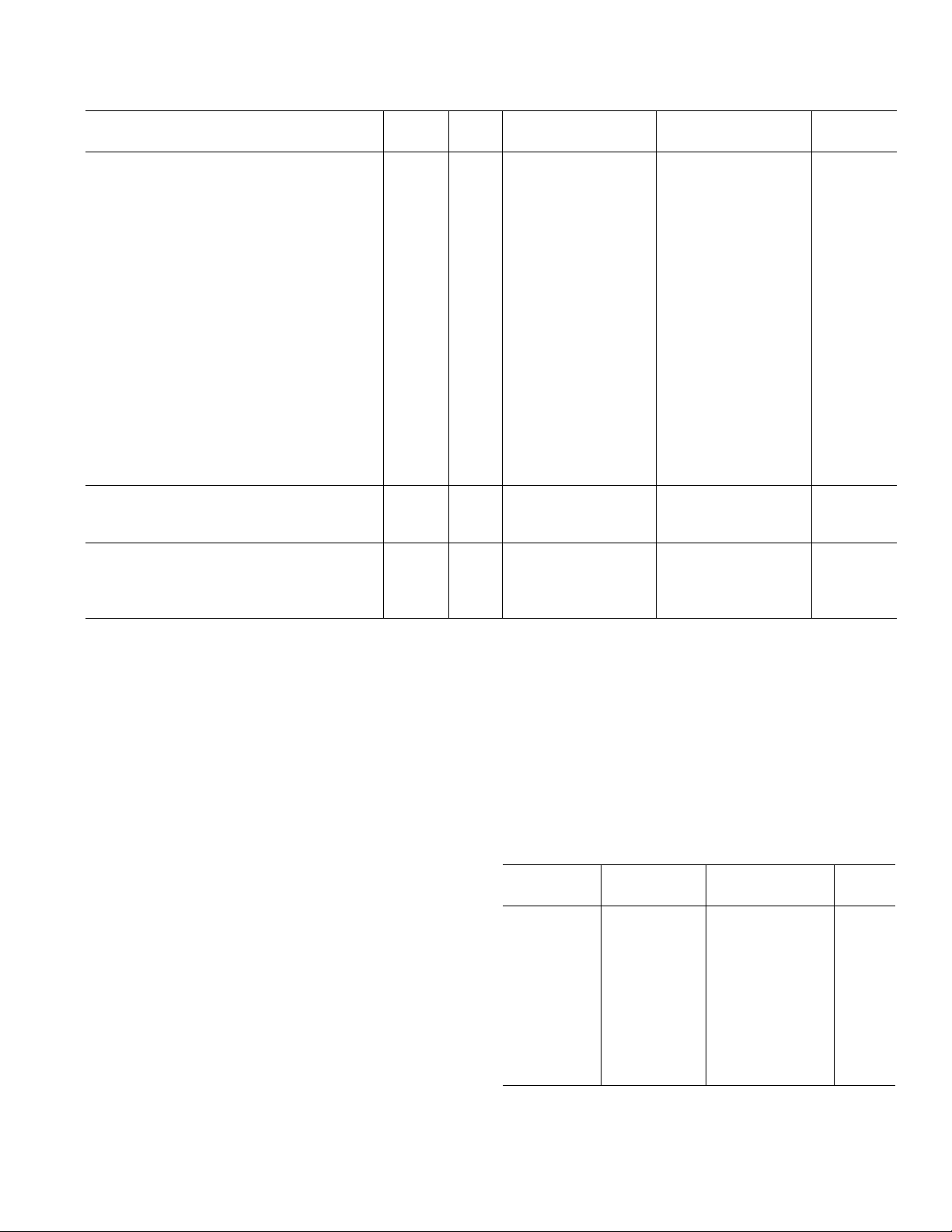

AD9058

Test AD9058JD/JJ AD9058KD/KJ

Parameter (Conditions) Temp Level Min Typ Max Min Typ Max Unit

DYNAMIC PERFORMANCE

Transient Response +25°CV 2 2 ns

Overvoltage Recovery Time +25°CV 2 2 ns

Effective Number of Bits (ENOB)

Analog Input @ 2.3 MHz +25°C I 7.7 7.2 7.7 Bits

@ 10.3 MHz +25°C I 7.4 7.1 7.4 Bits

Signal-to-Noise Ratio

5

Analog Input @ 2.3 MHz +25°C I 48 45 48 dB

@ 10.3 MHz +25°C I 46 44 46 dB

5

Signal-to-Noise Ratio

(Without Harmonics)

Analog Input @ 2.3 MHz +25°C I 48 46 48 dB

@ 10.3 MHz +25°C I 47 45 47 dB

2nd Harmonic Distortion

Analog Input @ 2.3 MHz +25°C I 58 48 58 dBc

@ 10.3 MHz +25°C I 58 48 58 dBc

3rd Harmonic Distortion

Analog Input @ 2.3 MHz +25°C I 58 50 58 dBc

@ 10.3 MHz +25°C I 58 50 58 dBc

Crosstalk Rejection

6

DIGITAL OUTPUTS

Logic “1” Voltage (I

= 2 mA) Full VI 2.4 2.4 V

OH

Logic “0” Voltage (IOL = 2 mA) Full VI 0.4 0.4 V

POWER SUPPLY

7

+VS Supply Current Full VI 127 154 127 154 mA

–V

Supply Current Full VI 27 38 27 38 mA

S

Power Dissipation Full VI 770 960 770 960 mW

NOTES

1

Absolute maximum ratings are limiting values to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability is

not necessarily implied. Exposure to absolute maximum rating conditions for an extended period of time may affect device reliability.

2

For applications in which +VS may be applied before –VS, or +VS current is not limited to 500 mA, a reverse biased clamping diode should be inserted between

ground and –VS to prevent destructive latch up. See section entitled “Using the AD9058.”

3

Typical thermal impedances: 44-lead hermetic J-Leaded ceramic package: θJA = 86.4°C/W; θJC = 24.9°C/W; 48-lead hermetic DIP θJA = 40°C/W;

θ

= 12°C/W.

JC

4

To achieve guaranteed conversion rate, connect each data output to ground through a 2 k Ω pull-down resistor.

5

SNR performance limits for the 48-lead DIP “D” package are 1 dB less than shown. ENOB limits are degraded by 0.3 dB. SNR and ENOB measured with

analog input signal 1 dB below full scale at specified frequency.

6

Crosstalk rejection measured with full-scale signals of different frequencies (2.3 MHz and 3.5 MHz) applied to each channel. With both signals synchronously

encoded at 40 MSPS, isolation of the undesired frequency is measured with an FFT.

7

Applies to both A/Ss and includes internal ladder dissipation.

Specifications subject to change without notice.

5

+25°C IV 60 48 60 dBc

EXPLANATION OF TEST LEVELS

Test Level

I – 100% production tested.

II – 100% production tested at +25°C, and sample tested at

specified temperatures.

III – Sample tested only.

IV – Parameter is guaranteed by design and characterization

testing.

V – Parameter is a typical value only.

VI – All devices are 100% production tested at +25°C. 100%

production tested at temperature extremes for extended

temperature devices; sample tested at temperature

extremes for commercial/industrial devices.

REV. B

ORDERING GUIDE

Temperature Package

Model Range Description Option

AD9058JJ 0°C to +70°C 44-Lead J-Leaded J-44

Ceramic

2

AD9058KJ 0°C to +70°C 44-Lead J-Leaded J-44

Ceramic, AC Tested

AD9058TJ/883

3

–55°C to +125°C 44-Lead J-Leaded J-44

Ceramic, AC Tested

AD9058JD 0°C to +70°C 48-Lead Ceramic DIP D-48

AD9058KD 0°C to +70°C 48-Lead Ceramic D-48

AD9058TD/883

3

–55°C to +125°C 48-Lead Ceramic D-48

DIP, AC Tested

DIP, AC Tested

NOTES

1

D = Hermetic Ceramic DIP Package; J = Leaded Ceramic Package.

2

Hermetically sealed ceramic package; footprint equivalent to PLCC.

3

For specifications, refer to Analog Devices Military Products Databook.

–3–

1

Loading...

Loading...