Analog Devices AD8401 Datasheet

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

8-Bit, 4-Channel Data

Acquisition System

AD8401

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703

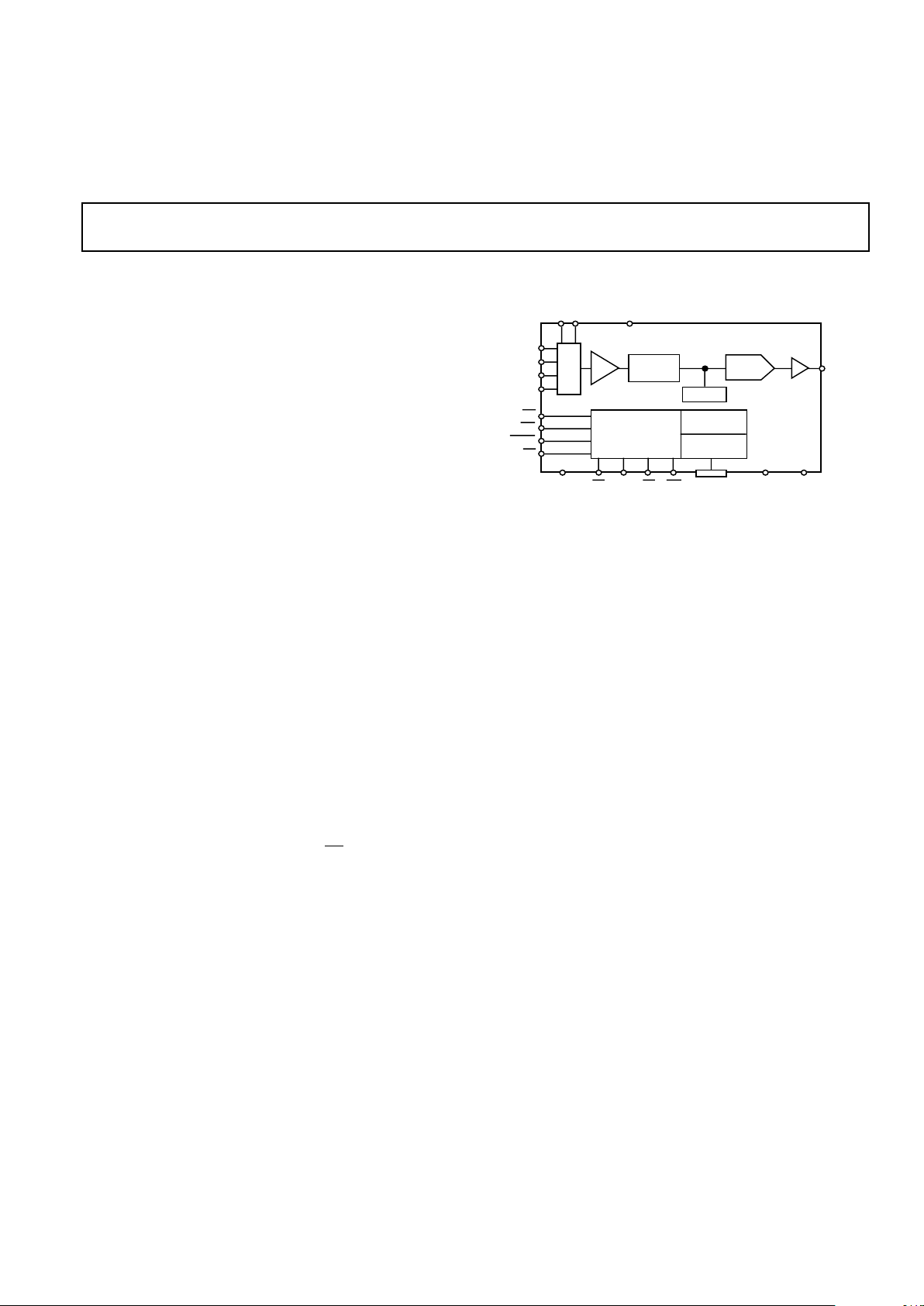

FUNCTIONAL BLOCK DIAGRAM

V

OUT

DGND

AG

DACAGADC

DATA I/O

(8 BITS)

M

U

X

T/H

8-BIT ADC

1.25 REF

8-BIT

DAC

RS

INT

BUSY

ST

DAC REG

ADC REG

CONTROL LOGIC

A0 A1

VDD (+5.0V)

RD WRCLK CS

AD8401

V

A

IN

V

B

IN

V

C

IN

V

D

IN

FEATURES

2 ms ADC with T/H

4-Channel MUX

AD899 Compatible

+5 Volt Operation

On-Chip Reference

4 ms Voltage Output DAC

Fast Bus Access Time—75 ns

APPLICATIONS

Servo Controls

Digitally Controlled Calibration

Process Control Equipment

GENERAL DESCRIPTION

The AD8401 is a complete data acquisition and control system

containing ADC, DAC, 4-channel MUX, and internal voltage

reference. Built using CBCMOS, this monolithic circuit offers

the user a complete system with very high package density and

reliability.

The converter is a successive approximation ADC with T/H,

and is capable of operating with conversion times as short as

2 µs. Analog input bandwidth is 200 kHz, and DAC output volt-

age settling time is less than 4 µs, making the AD8401 capable

of controlling servo loops with speed and precision.

The 8-bit data interface provides both read and write operation

for parallel bus interfaces to microcontrollers and DSP processors. An external 5 MHz clock sets the 2 µs conversion rate.

Slower clocks reduce the conversion time and the internal power

dissipation. The standard control lines: Reset, Busy, Interrupt,

Read and Write complete the handshaking signals for microprocessor communication. A start trigger

ST input allows pre-

cise sampling intervals in synchronous sampling applications.

The input multiplexer addressing is designed for direct interface

to the AD899 hard-disk drive, read-channel device with no extra

hardware or special software. Analog input range levels are likewise compatible with the AD899.

The AD8401 is designed to operate from a single +5 volt supply, which will give an ADC input range of 0 V to 3.0 V, and

DAC output range of 0 V to 2.5 V.

The AD8401 is offered in the SOIC-28 surface mount package,

and is guaranteed to operate over the extended industrial temperature range of –40°C to +85°C.

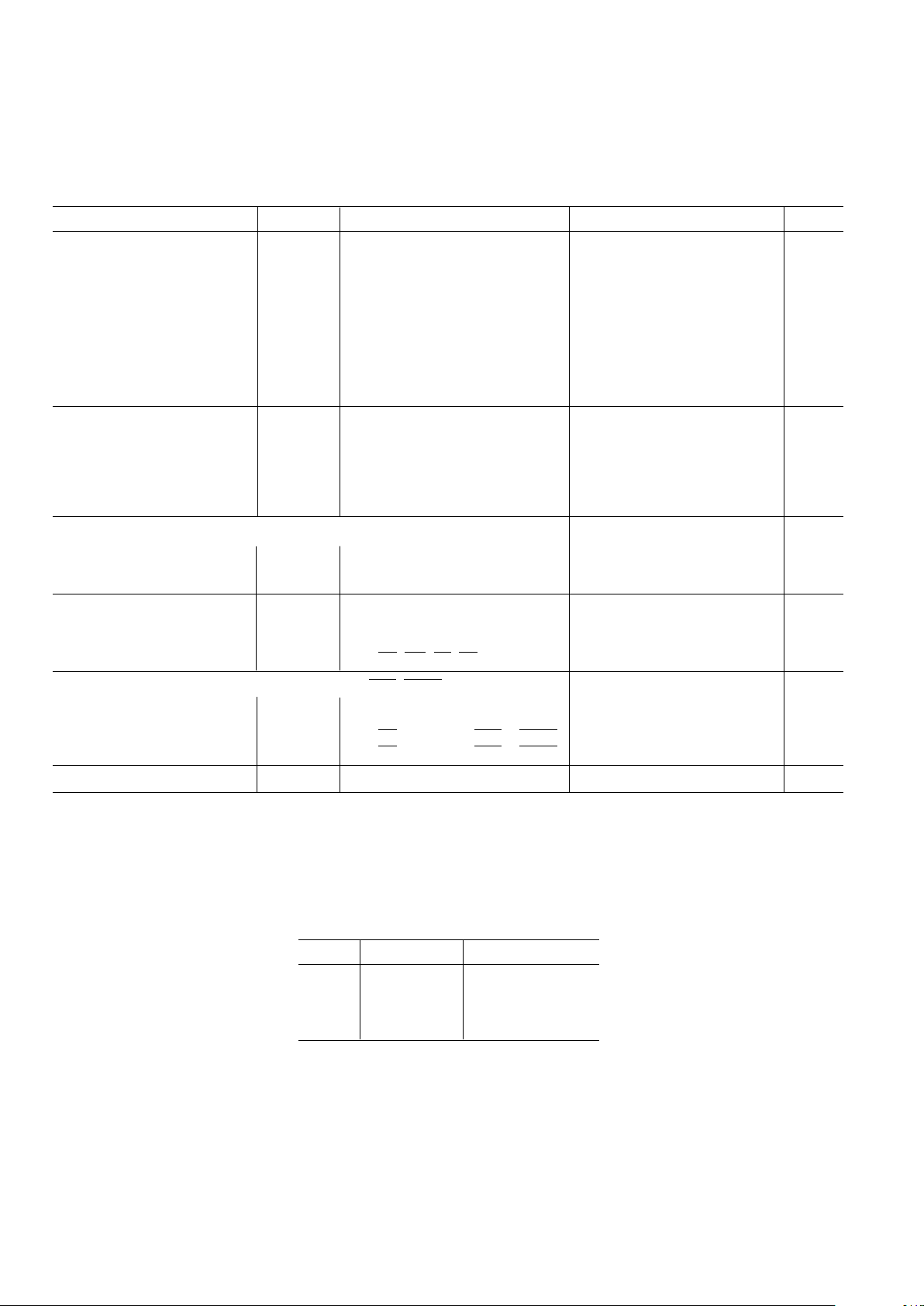

Parameter Symbol Conditions Min Typ Max Units

STATIC PERFORMANCE

Resolution N 8 Bits

Total Unadjusted Error TUE ±3 LSB

Relative Accuracy INL –1 +1 LSB

Differential Nonlinearity DNL –1 +1 LSB

Offset Error V

OSE

TA = +25°C –4 +4 LSB

T

A

= Full Temp Range –6 +6 LSB

Full-Scale Error A

E

TA = +25°C –4 +4 LSB

T

A

= Full Temp Range –6 +6 LSB

∆Full-Scale/∆V

DD

TA = +25°C 1 LSB

DYNAMIC PERFORMANCE

Signal-to-Noise Ratio SNR 44 dB

Total Harmonic Distortion THD 48 dB

Intermodulation Distortion IMD 60 dB

Frequency Response 0 to 200 kHz 0.1 dB

Track/Hold Acquisition Time t

AQ

200 ns

ANALOG INPUTS (Applies to Inputs A, B. C, D)

Unipolar Input Range V

IN

03V

Input Current I

IN

–500 +500 µA

Input Capacitance C

IN

10 pF

LOGIC INPUTS

Clock Input Current Low I

CKL

VIN = 0 V 1.6 mA

Clock Input Current High I

CKH

VIN = V

DD

40 µA

Input Leakage Current I

L

CS, RD, RS, ST 10 µA

LOGIC OUTPUTS (Applies to Outputs DB0–DB7,

INT, BUSY)

Logic Output Low Voltage V

OL

IOL = 1.6 mA 0.4 V

Logic Output High Voltage V

OH

IOH = 200 µA 4.0 V

Output Leakage Current I

OZ

CS = 1 (Except INT & BUSY)10µA

Output Capacitance C

OZ

CS = 1 (Except INT & BUSY)10pF

CONVERSION TIME t

C

External Clock 2 µs

Specifications subject to change without notice.

REV. 0

–2–

AD8401–SPECIFICA TIONS

ADC ELECTRICAL CHARACTERISTICS

A1 A0 Input Selected

00V

IN

A

01V

IN

B

10V

IN

C

11V

IN

D

Table I. Multiplexer Address Input Decode

(@ VDD = +5.0 V 6 5%, AG

DAC

= AG

ADC

= 0.0 V; f

CLK

= 5 MHz; –408C ≤ TA ≤ +858C,

unless otherwise noted)

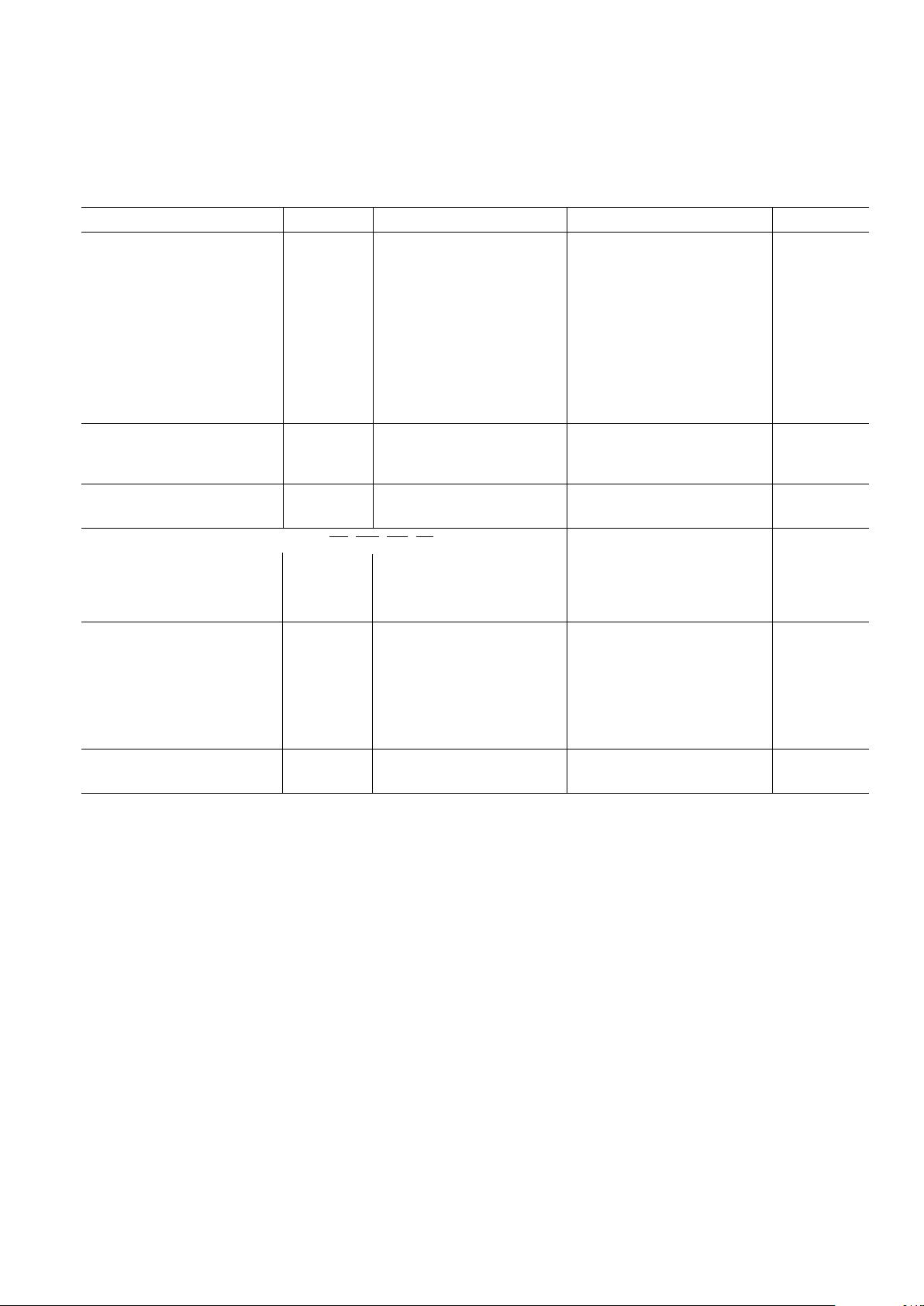

DAC ELECTRICAL CHARACTERISTICS

Parameter Symbol Conditions Min Typ Max Units

STATIC PERFORMANCE

Resolution N 8 Bits

Total Unadjusted Error TUE ±2 LSB

Relative Accuracy INL –1 +1 LSB

Differential Nonlinearity DNL –1 +1 LSB

Offset Error V

OSE

TA = +25°C –2 +2 LSB

T

A

= Full Temp Range –2.5 +2.5 LSB

Full-Scale Error A

E

TA = +25°C –3 +3 LSB

T

A

= Full Temp Range –4 +4 LSB

∆Full-Scale/∆V

DD

TA = +25°C –0.5 +0.5 LSB

Load Regulation at Full-Scale –0.2 +0.2 LSB

DYNAMIC PERFORMANCE

Signal-to-Noise Ratio SNR 44 dB

Total Harmonic Distortion THD 48 dB

ANALOG OUTPUT

Output Voltage Range OVR 0 +2.5 V

LOGIC INPUTS (Applies to DB0–DB7, CS, WR, RD, RS)

Logic Input Low Voltage V

IL

0.8 V

Logic Input High Voltage V

IH

2.4 V

Input Leakage Current I

L

–10 10 µA

Input Capacitance C

IL

10 pF

AC CHARACTERISTICS

Voltage Output Settling Time t

S

To ±1/2 LSB of Final Value 2 4 µs

Positive Full-Scale Change t

POS

10% to 90% 1 2 µs

Negative Full-Scale Change t

NEG

90% to 10% 2 4 µs

DAC Glitch Impulse 15 nV s

Digital Feedthrough 1 nV s

VIN to V

OUT

Isolation f = 50 kHz 60 dB

POWER REQUIREMENTS

Positive Supply Current I

DD

No Load 13 mA

Specifications subject to change without notice.

(@ VDD = +5.0 V 6 5%, AG

DAC

= AG

ADC

= 0.0 V; RL = 2 kV, CL = 100 pF

to AG

DAC

; –408C ≤ TA ≤ +858C, unless otherwise noted)

AD8401

–3–

REV. 0

AD8401

–4–

REV. 0

WARNING!

ESD SENSITIVE DEVICE

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD8401 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

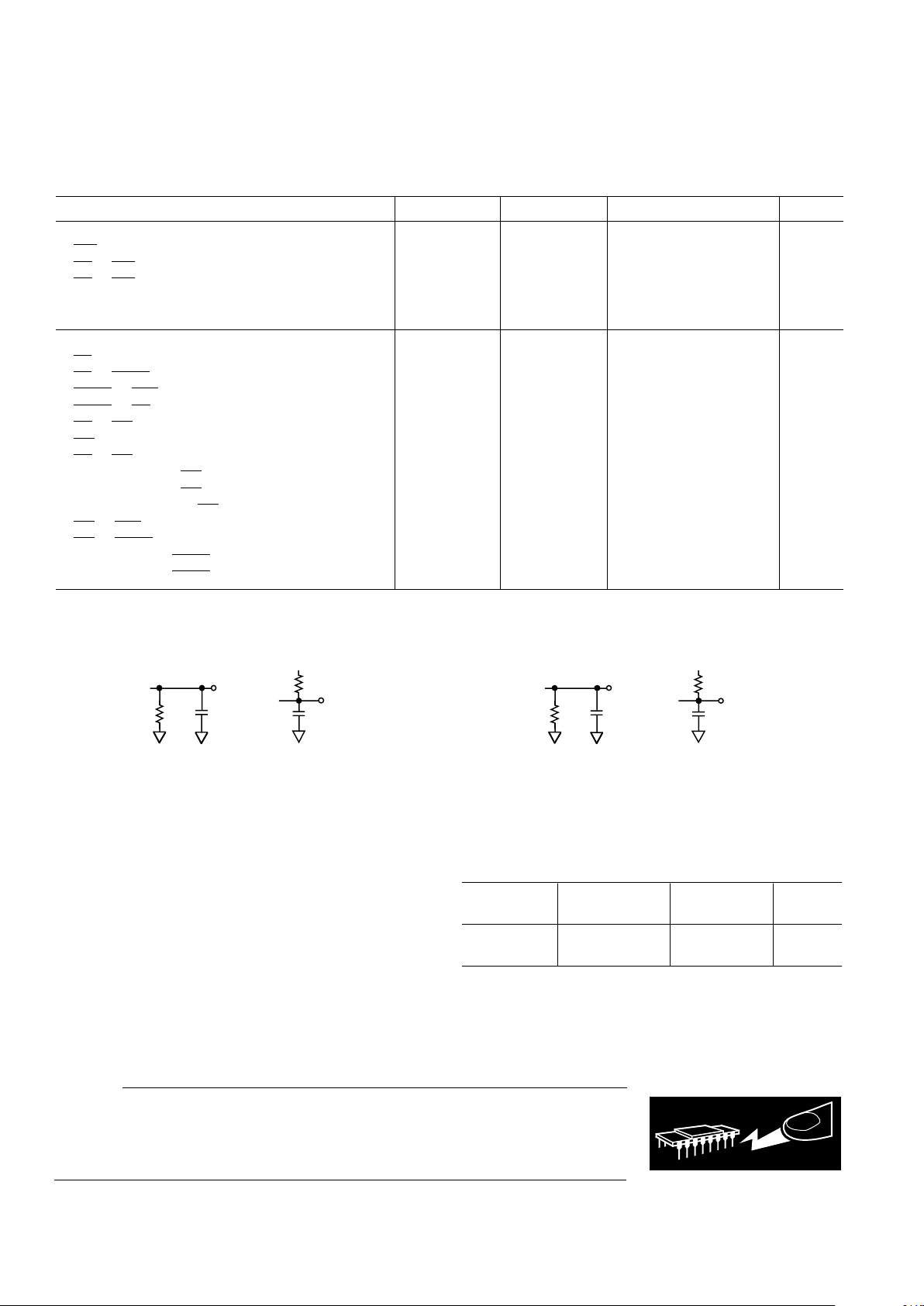

TIMING ELECTRICAL SPECIFICATIONS

(@ VDD = +5.0 V 6 5%, AG

DAC

= AG

ADC

= 0.0 V; f

CLK

= 5 MHz; –408C ≤ TA ≤ +858C,

unless otherwise noted)

Parameters

1, 2, 3

Symbol Condition Min Typ Max Units

DAC TIMING (See Figure 8 Timing Diagram)

WR Pulse Width t

1

50 ns

CS to WR Setup Time t

2

0ns

CS to WR Hold Time t

3

0ns

Data Setup Time t

4

60 ns

Data Hold Time t

5

0ns

ADC TIMING (See Figures 6 and 7 Timing Diagrams)

ST Pulse Width t

6

40 ns

ST to BUSY Delay t

7

110 ns

BUSY to INT Delay t

8

30 ns

BUSY to CS Delay t

9

0ns

CS to RD Setup Time t

10

0ns

RD Pulse Width

4

t

11

75 ns

CS to RD Hold Time t

12

0ns

Data Access after

RD t

13

CL = 20 pF 10 75 ns

Data Access after

RD t

13

CL = 100 pF 10 135 ns

Bus Relinquish after

RD t

14

10 70 ns

RD to INT Delay t

15

85 ns

RD to BUSY Delay t

16

110 ns

Data Valid after

BUSY t

17

CL = 20 pF 90 ns

Data Valid after BUSY t

17

CL = 100 pF 135 ns

NOTES

1

All input control signals are specified with tR = tF = 5 ns (10% to 90% of +5 V) and timed from a voltage level of 1.6 V.

2

t13 and t17 are measured with the load circuits of Figure 1 and defined as the time required for an output to cross either 0.8 V or 2.4 V.

3

t14 is defined as the time required for the data line to change 0.5 V when loaded with the circuit of Figure 2.

4

t15 is determined by t13.

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage (VDD) . . . . . . . . . . . . . . . . . . . . . . . . . . . +8 V

Input Voltages . . . . . . . . . . . . . . . . . . . –0.3 V to V

DD

+ 0.3 V

Output Short-Circuit Duration . . . . . . . . . . . . . . . . Indefinite

Package Power Dissipation . . . . . . . . . . . . . . (T

J

max–TA)/θ

JA

Thermal Resistance θ

JA

28-Lead SOIC (R) . . . . . . . . . . . . . . . . . . . . . . . . . 53°C/W

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Operating Temperature Range . . . . . . . . . . . . –40°C to +85°C

Junction Temperature Range (T

J

max) . . . . –65°C to +150°C

Lead Temperature Range (Soldering, 60 sec) . . . . . . +300°C

*Stresses above those listed under “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

ORDERING GUIDE

Temperature Package Package

Model* Range Description Option

AD8401AR –40°C to +85°C 28-Lead SOIC SOL-28

AD8401Chips +25°C Die

*The AD8401 contains 1257 transistors.

Figure 1. Load Circuits for Data Access Time Test

a. V

OH

to High Z

a. High Z to V

OH

b. High Z to V

OL

DGND

CL

3kΩ

DBN

DBN

CL

3kΩ

+5V

DGND

DGND

10pF

3kΩ

DBN

DBN

10pF

3kΩ

+5V

DGND

b. VOL to High Z

Figure 2. Load Circuits for Bus Relinquish Time Test

Loading...

Loading...