R

Active Receive Mixer

Preliminary Datasheet

FEATURES

Broadband RF port: LF to 500 MHz

Conversion gain: 3 dB

Noise figure: 12 dB

Input IP3: 24 dBm

Input P

LO drive: 0 dBm

External control of mixer bias for low power operation

Single-ended, 50 Ω LO input ports

High Input Impedance RF port

Single-supply operation: 5 V @ 97 mA

Power-down mode

Exposed paddle LFCSP: 3 mm × 3 mm

APPLICATIONS

Cellular base station receivers and transmitters

ISM receivers and transmitters

Radio links

RF Instrumentation

: 8.5 dBm

1dB

COMM

RFCM

RFIN

VPMX

DC to 500 MHz

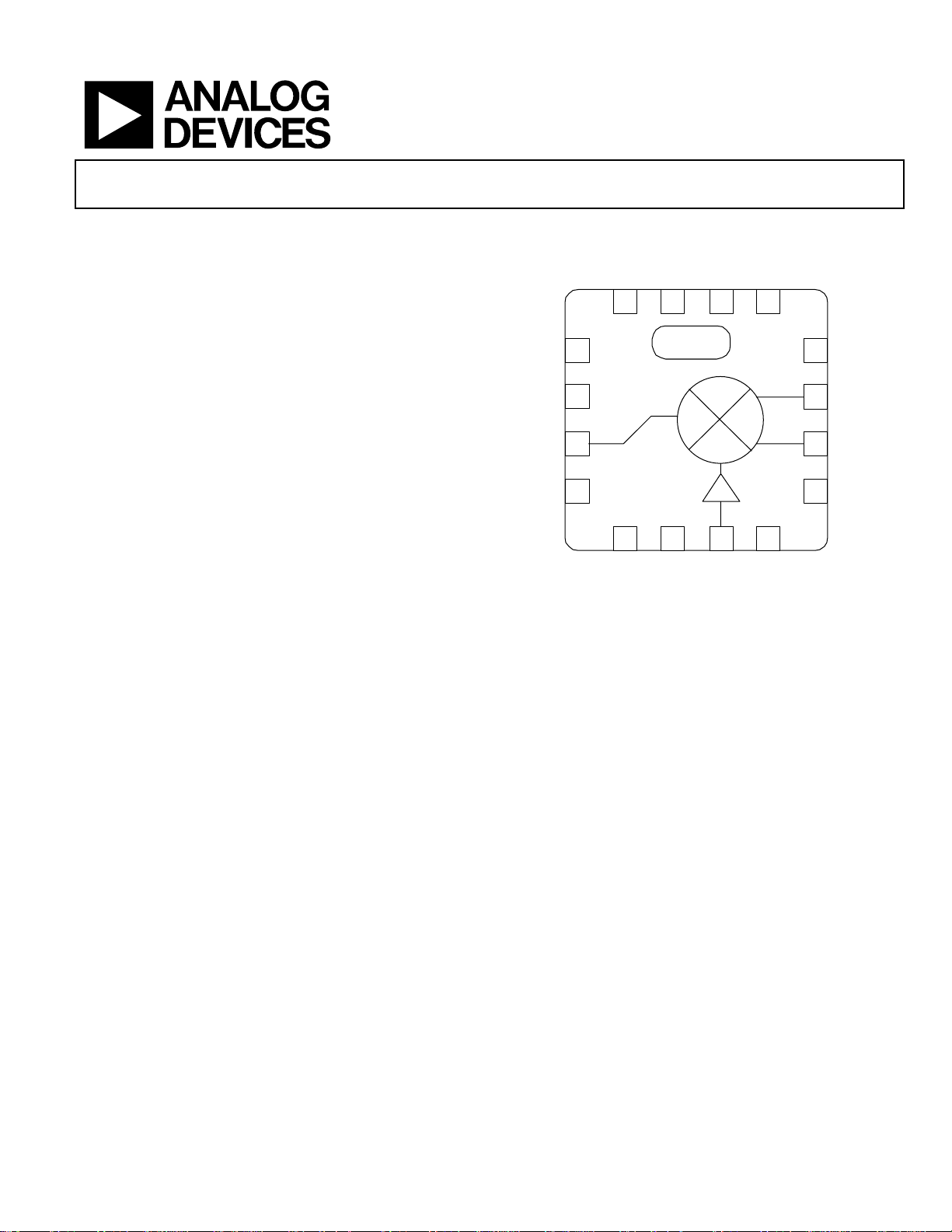

FUNCTIONAL BLOCK DIAGRAM

BPWDNVPDC

COMMEX

9101112

13

14

15

16

1234

VPLO LOCM LOIN COMM

BIAS

Figure 1.

AD8342

COMM

8

7

IFOP

IFOM

6

COMM

5

GENERAL DESCRIPTION

The AD8342 is a high performance, broadband active mixer. It

is well suited for demanding receive applications that require

wide bandwidth on all ports and very low intermodulation distortion and noise figure.

The AD8342 provides a typical conversion gain of 3dB at

500 MHz. The integrated LO driver supports a 50 Ω input impedance with a low LO drive level, helping to minimize external

component count.

The high input impedance RF port can be terminated and

driven single ended or a matching network can be used for best

noise or power match. The RF input accepts input signals as

large as 1.7 V p-p or 8 dBm (re: 50 Ω) at P

1dB

.

The open-collector differential outputs provide excellent balance and can be used with a differential filter or IF amplifier,

such as the AD8369 or AD8351. These outputs may also be

converted to a single-ended signal through the use of a matching network or a transformer (balun). When centered on the

VPOS supply voltage, each of the differential outputs may swing

2.5 V p-p.

The AD8342 is fabricated on an Analog Devices proprietary,

high performance SiGe IC process. The AD8342 is available in a

16-lead LFCSP package. It operates over a −40°C to +85°C temperature range. An evaluation board is also available.

Rev. PrB

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents

or other rights of third parties that may result from its use. Specifications subject to change

without notice. No license is granted by implication or otherwise under any patent or patent

rights of Analog Devices. Trademarks and registered trademarks are the property of their

respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

AD8342 Preliminary Datasheet

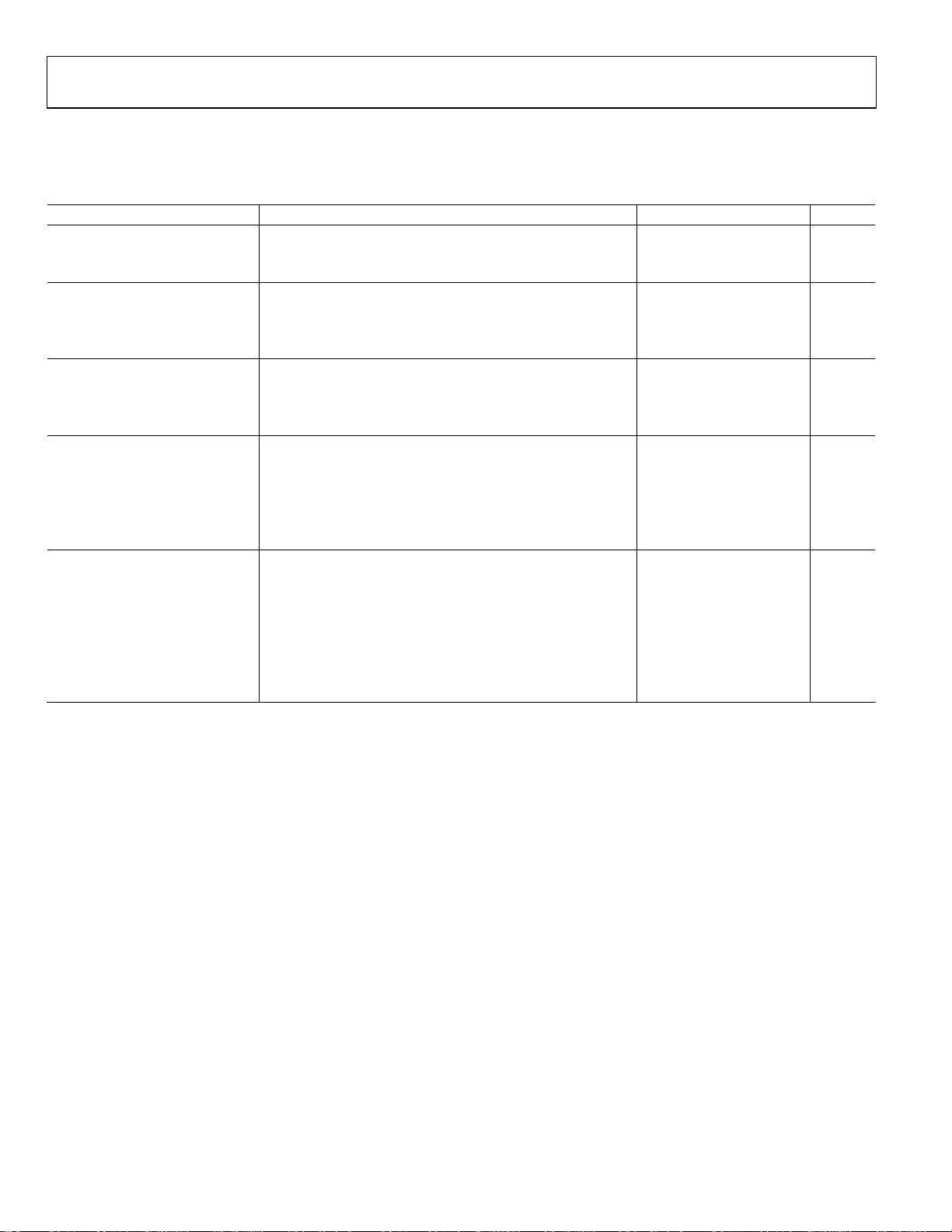

SPECIFICATIONS

VS = 5 V, TA = 25°C, fRF = 500 MHz, fLO = 600 MHz, LO power = 0 dBm, ZO = 50 Ω, R

Table 1.

Parameter Conditions Min Typ Max Unit

RF INPUT INTERFACE (Pin 15, RFIN and Pin 14, RFCM)

Return Loss Hi-Z input terminated off-chip 10 dB

DC Bias Level Internally generated; port must be ac-coupled 2.5 V

OUTPUT INTERFACE

Output Impedance Differential impedance, f = 200 MHz 9||1 kΩ||pF

DC Bias Voltage Externally generated 4.75 VS 5.25 V

Power Range Via a 4:1 balun +13 dBm

LO INTERFACE

LO Power −10 0 +4 dBm

Return Loss 10 dB

DC Bias Voltage Internally generated; port must be ac-coupled VS − 1.6 V

POWER-DOWN INTERFACE

PWDN Threshold VS − 1.4 V

PWDN Response Time Device enabled, IF output to 90% of its final level 0.4 µs

Device disabled, supply current < 5 mA 0.01 µs

PWDN Input Bias Current Device enabled −80 µA

Device disabled +100 µA

POWER SUPPLY

Positive Supply Voltage 4.75 5 5.25 V

Quiescent Current

VPDC Supply current for bias cells 5 mA

VPMX, IFOP, IFOM Supply current for mixer, R

VPLO Supply current for LO limiting amplifier 35 mA

Total Quiescent Current VS = 5 V TBD 97 TBD mA

Power-Down Current Device disabled 500 µA

= 1.82 kΩ 57 mA

BIAS

= 1.82 kΩ, unless otherwise noted.

BIAS

Rev. PrB | Page 2 of 8

Preliminary Datasheet AD8342

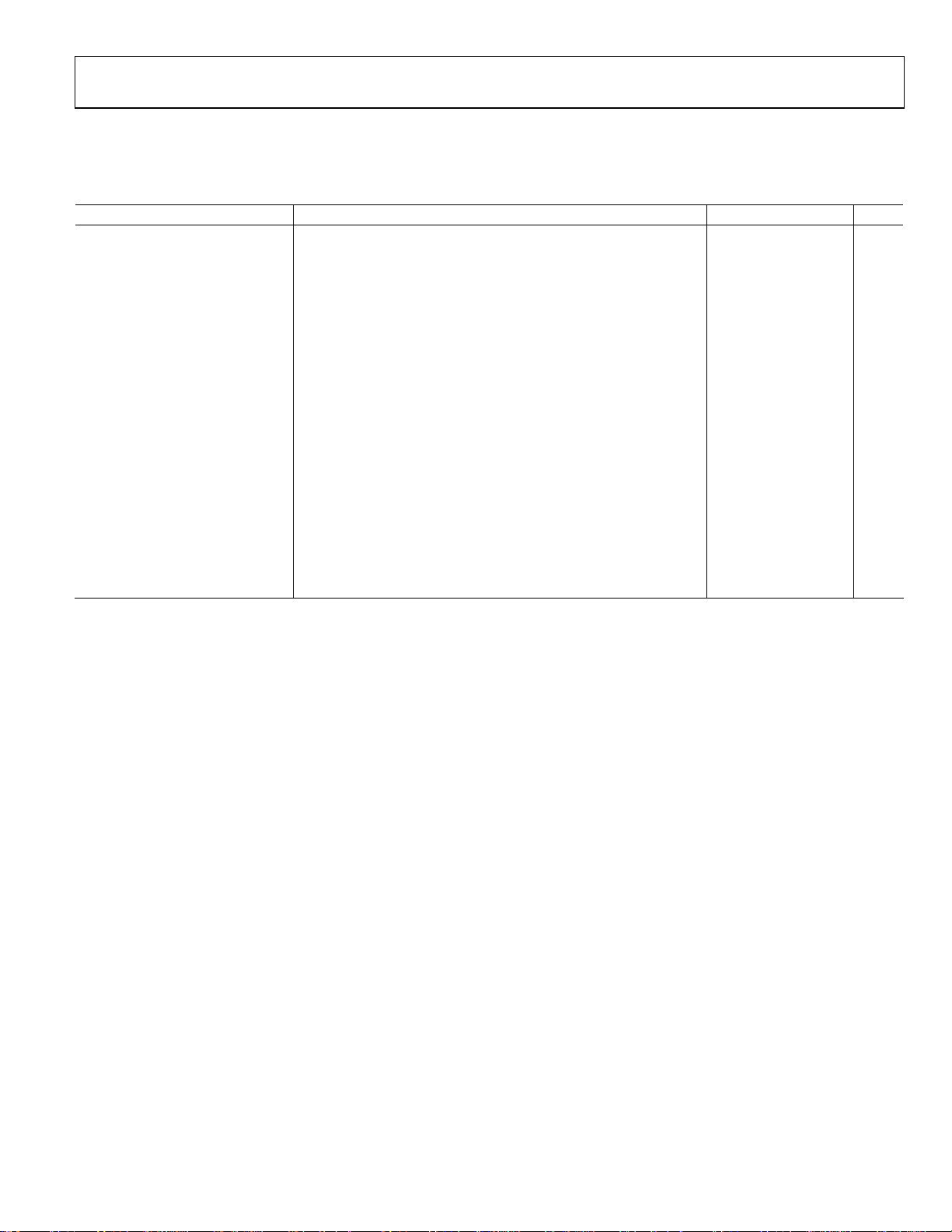

AC PERFORMANCE

VS = 5 V, TA = 25°C, LO power = 0 dBm, ZO = 50 Ω, R

Table 2.

Parameter Conditions Min Typ Max Unit

RF Frequency Range LF 500 MHz

LO Frequency Range High Side LO LF 850 MHz

IF Frequency Range Note: the upper “IF” is when used as an upconverter DC 350 MHz

Conversion Gain fRF = 460 MHz, fLO = 550 MHz, fIF = 90 MHz 3.2 dB

f

= 238 MHz, fLO = 286 MHz, fIF = 48 MHz 3.4 dB

RF

SSB Noise Figure fRF = 460 MHz, fLO = 550 MHz, fIF = 90 MHz 12.5 dB

f

Input Third-Order Intercept

Input Second-Order Intercept f

f

= 238 MHz, fLO = 286 MHz, fIF = 48 MHz 12.2 dB

RF

= 460 MHz, f

f

RF1

f

= 90 MHz, each RF tone -10 dBm

IF

= 238 MHz, f

f

RF1

= 45MHz, each RF tone -10 dBm

f

IF

= 460 MHz, f

RF1

= 238 MHz, f

RF1

Input 1 dB Compression Point fRF = 460 MHz, fLO = 550 MHz, fIF = 90 MHz 8.5 dBm

f

= 238 MHz, fLO = 286 MHz, fIF = 48 MHz 8.5 dBm

RF

LO to IF Output Leakage LO Power = 0 dBm, fRF = 500 MHz, fLO = 600 MHz TBD dBm

LO to RF Input Leakage LO Power = 0 dBm, fRF = 500 MHz, fLO = 600 MHz TBD dBm

2xLO to IF Output Leakage LO Power = 0 dBm, fRF = 500 MHz, fLO = 600 MHz TBD dBm

RF to IF Output Leakage RF Power = -10 dBm, fRF = 500 MHz, fLO = 600 MHz TBD dBm

IF/2 Spurious RF Power = -10 dBm, fRF = 500 MHz, fLO = 600 MHz TBD dBm

= 1.82 kΩ, unless otherwise noted.

BIAS

= 461 MHz, fLO = 550 MHz,

RF2

= 239 MHz, fLO = 286MHz,

RF2

= 480 MHz, fLO = 550 MHz, fIF = 90 MHz 48 dBm

RF2

= 248 MHz, fLO = 286 MHz, fIF = 48 MHz 48 dBm

RF2

22.5 dBm

23.5 dBm

Rev. PrB | Page 3 of 8

Loading...

Loading...