Analog Devices AD8328 Datasheet

5 V Upstream

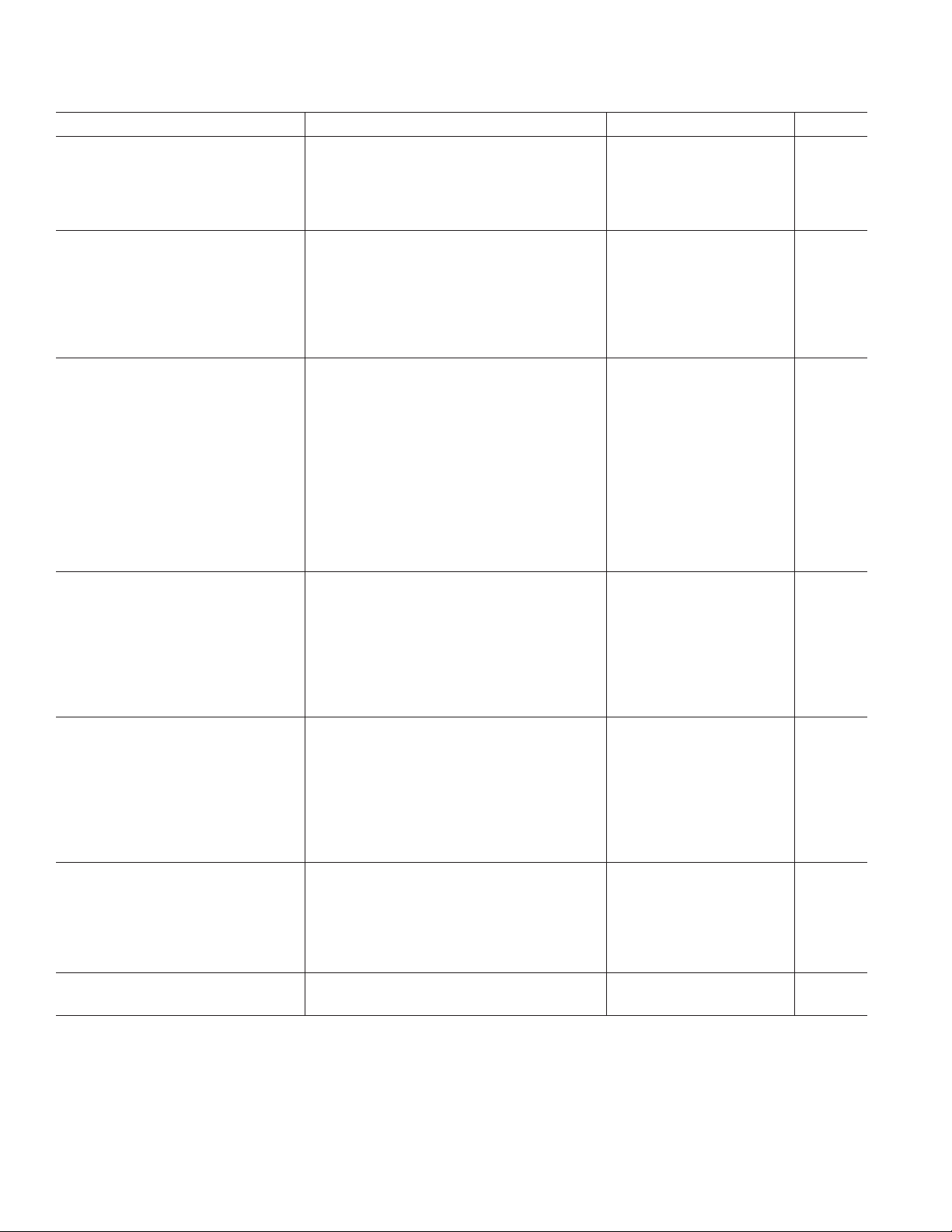

5 15 25 35 45 55 65

DISTORTION – dBc

FREQUENCY – MHz

V

OUT

= 60dBmV

@MAX GAIN,

THIRD HARMONIC

V

OUT

= 60 dBmV

@MAX GAIN,

SECOND HARMONIC

–70

–68

–66

–64

–62

–60

–58

–56

–54

–52

–50

a

FEATURES

Supports DOCSIS and EuroDOCSIS Standards for

Reverse Path Transmission Systems

Gain Programmable in 1 dB Steps over a 59 dB Range

Low Distortion at 60 dBmV Output:

–57.5 dBc SFDR at 21 MHz

–54 dBc SFDR at 65 MHz

Output Noise Level @ Minimum Gain 1.2 nV/√Hz

Maintains 300 Output Impedance TX-Enable and

Transmit-Disable Condition

Upper Bandwidth: 107 MHz (Full Gain Range)

5 V Supply Operation

Supports SPI Interfaces

APPLICATIONS

DOCSIS and EuroDOCSIS Cable Modems

CATV Set-Top Boxes

CATV Telephony Modems

Coaxial and Twisted Pair Line Driver

V

IN+

V

IN–

ZIN (SINGLE) = 800

Z

(DIFF) = 1.6k

IN

Cable Line Driver

AD8328

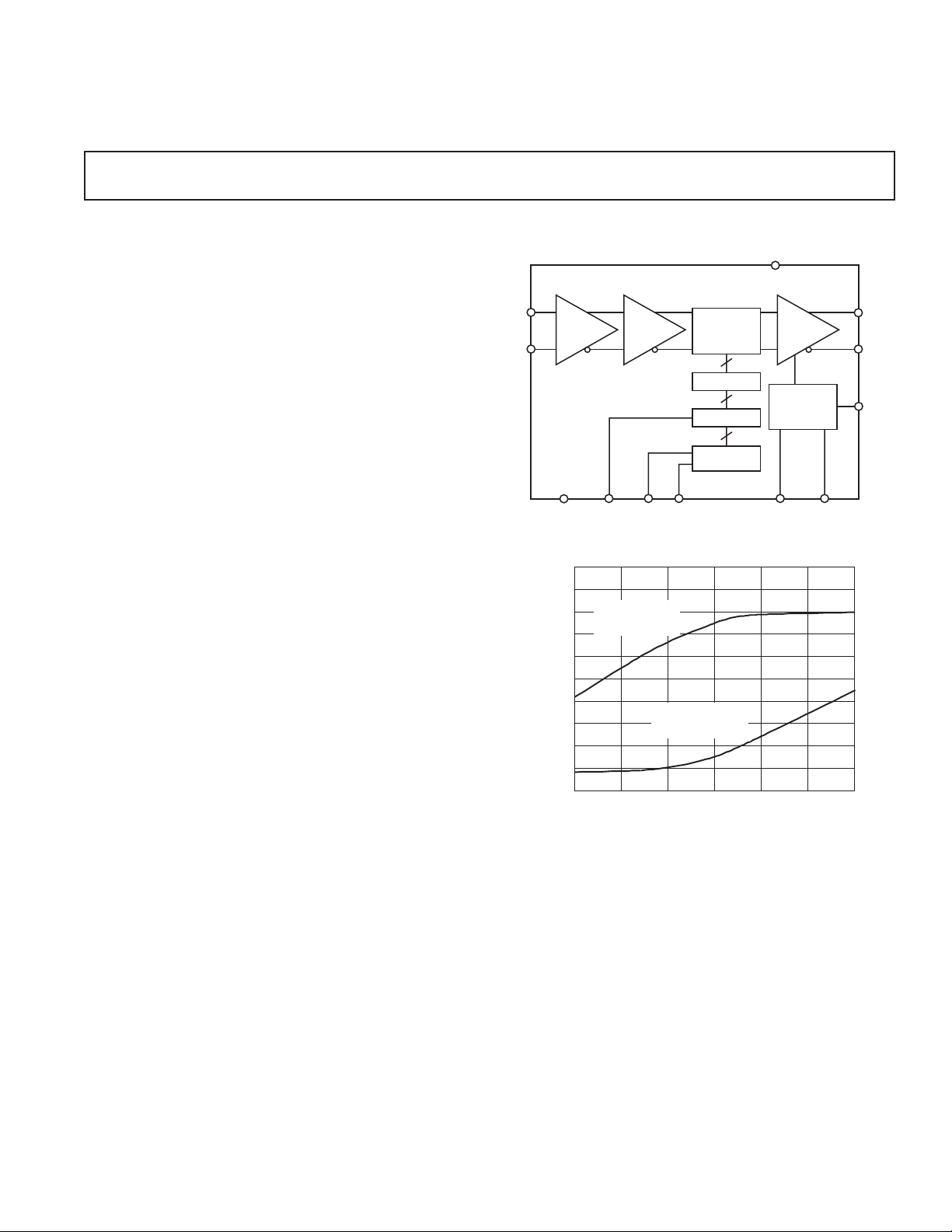

FUNCTIONAL BLOCK DIAGRAM

BYP

AD8328

DIFF OR

SINGLE

INPUT

AMP

GND

VERNIER

SDATA CLK TXEN

DATEN

ATTENUATION

CORE

8

DECODE

8

DATA LATCH

8

SHIFT

REGISTER

POWER-DOWN

POWER

AMP

Z

LOGIC

OUT

300

SLEEP

DIFF =

*

V

OUT+

V

OUT–

RAMP

GENERAL DESCRIPTION

The AD8328 is a low cost amplifier designed for coaxial line

driving. The features and specifications make the AD8328

ideally suited for MCNS-DOCSIS and Euro-DOCSIS applications. The gain of the AD8328 is digitally controlled. An 8-bit

serial word determines the desired output gain over a 59 dB range,

resulting in gain changes of 1 dB/LSB.

The AD8328 accepts a differential or single-ended input signal. The

output is specified for driving a 75 Ω load through a 2:1 transformer.

Distortion performance of –53 dBc is achieved with an output

level up to 60 dBmV at 65 MHz bandwidth over a wide temperature range.

This device has a sleep mode function that reduces the quiescent

current to 2.6 mA and a full power-down function that reduces

power-down current to 20 µA.

The AD8328 is packaged in a low cost 20-lead LFCSP package

and a 20-lead QSOP package. The AD8328 operates from a single

5V supply and has an operational temperature range of –40°C

to +85°C.

*Patent Pending

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

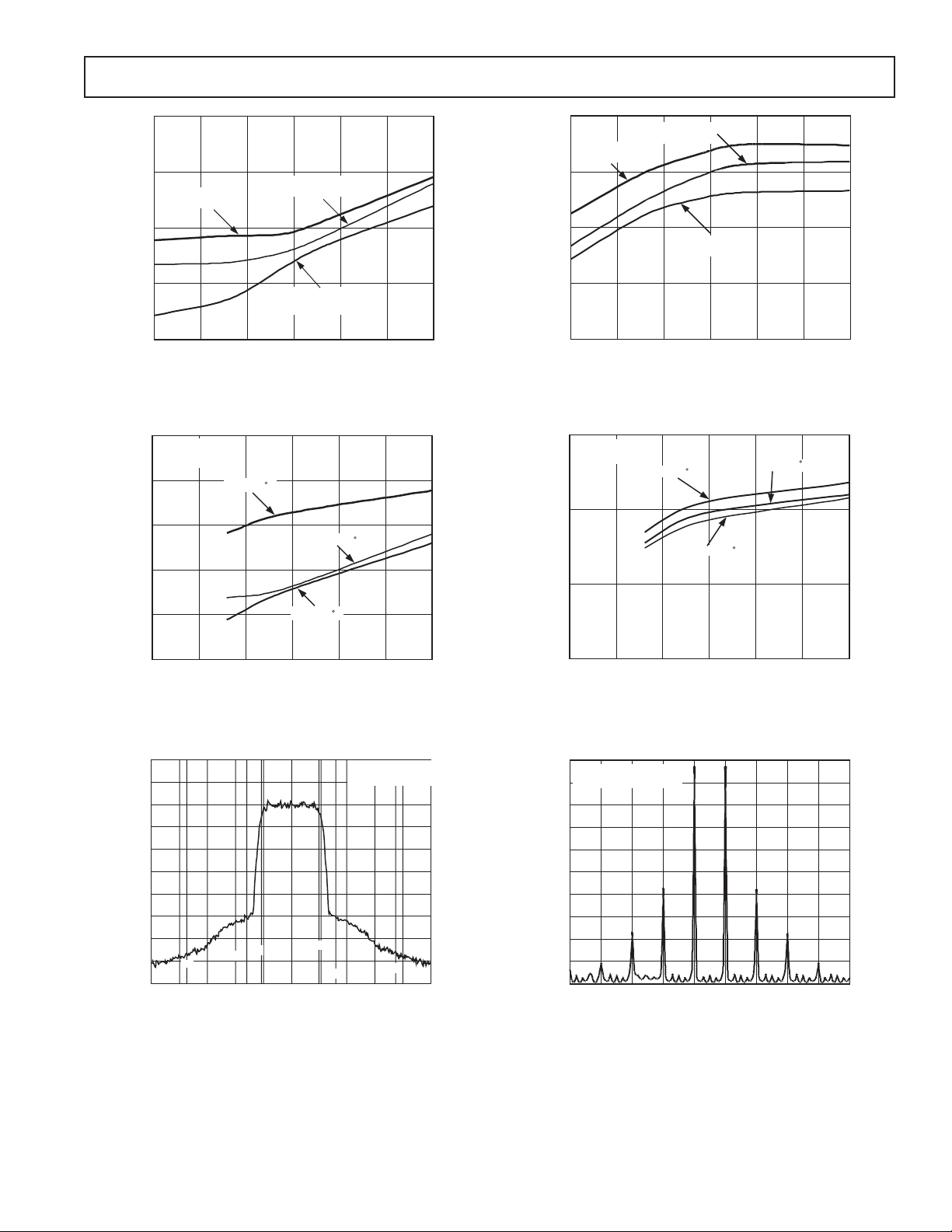

Figure 1. Worst Harmonic Distortion vs. Frequency

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

(TA = 25C, VS = 5 V, RL = RIN = 75 , VIN (Differential) = 29 dBmV.

AD8328

–SPECIFICATIONS

Parameter Conditions Min Typ Max Unit

INPUT CHARACTERISTICS

Specified AC Voltage Output = 60 dBmV, Max Gain 29 dBmV

Input Resistance Single-Ended Input 800 Ω

Differential Input 1600 Ω

Input Capacitance 2pF

GAIN CONTROL INTERFACE

Voltage Gain Range 58 59.0 60 dB

Max Gain Gain Code = 60 Dec 30.5 31.5 32.5 dB

Min Gain Gain Code = 1 Dec –28.5 –27.5 –26.5 dB

Output Step Size 0.6 1.0 1.4 dB/LSB

Output Step Size Temperature T

= –40°C to +85°C ± 0.0005 dB/°C

A

Coefficient

OUTPUT CHARACTERISTICS

Bandwidth (–3 dB) All Gain Codes (1–60 Decimal Codes) 107 MHz

Bandwidth Roll-Off f = 65 MHz 1.2 dB

1 dB Compression Point

Output Noise

2

2

Max Gain, f = 10 MHz, Output Referred 17.9 18.4 dBm

Min Gain, f = 10 MHz, Input Referred 2.2 3.3 dBm

Max Gain f = 10 MHz 135 151 nV/√Hz

Min Gain f = 10 MHz 1.2 1.3 nV/√Hz

Transmit Disable f = 10 MHz 1.1 1.2 nV/√Hz

Noise Figure

2

Max Gain f = 10 MHz 16.7 17.7 dB

Differential Output Impedance TX Enable and TX Disable 75 ± 30%

OVERALL PERFORMANCE

Second-Order Harmonic Distortion

4, 5

f = 33 MHz, V

f = 65 MHz, V

Third-Order Harmonic Distortion

2, 6

ACPR

Isolation (Transmit Disable)

4, 5

f = 21 MHz, V

f = 65 MHz, V

2

Max Gain, f = 65 MHz –85 –81 dB

POWER CONTROL

TX Enable Settling Time Max Gain, VIN = 0 2.5 µs

TX Disable Settling Time Max Gain, V

Output Switching Transients

2

Equivalent Output = 31 dBmV 2.5 6 mV p-p

Equivalent Output = 61 dBmV 16 54 mV p-p

Output Settling

Due to Gain Change Min to Max Gain 60 ns

Due to Input Step Change Max Gain, VIN = 29 dBmV 30 ns

POWER SUPPLY

Operating Range 4.75 5 5.25 V

Quiescent Current Max Gain 98 120 140 mA

Min Gain 18 26 34 mA

Transmit Disable (TXEN = 0) 1 2.6 3.5 mA

SLEEP Mode (Power-Down) 1 20 100 µA

OPERATING TEMPERATURE –40 +85 °C

RANGE

NOTES

1

TOKO 458PT-1087 used for above specifications. Typical insertion loss of 0.3 dB @ 10 MHz.

2

Guaranteed by design and characterization to ± 4 sigma for TA = 25°C.

3

Measured through a 2:1 transformer.

4

Specification is worst case over all gain codes.

5

Guaranteed by design and characterization to ± 3 sigma for TA = 25°C.

6

VIN = 29 dBmV, QPSK modulation, 160 KSPS symbol rate.

The AD8328 is characterized using a 2:1 transformer1 at the device output.)

3

= 60 dBmV @ Max Gain –67 –56 dBc

OUT

= 60 dBmV @ Max Gain –61 –55 dBc

OUT

= 60 dBmV @ Max Gain –57.5 –56 dBc

OUT

= 60 dBmV @ Max Gain –54 –52.5 dBc

OUT

= 0 3.8 µs

IN

–58 –56 dBc

Ω

REV. 0–2–

AD8328

LOGIC INPUTS (TTL/CMOS Compatible Logic)

(DATEN, CLK, SDATA, TXEN, SLEEP, V

= 5 V. Full Temperature Range.)

CC

Parameter Min Typ Max Unit

Logic 1 Voltage 2.1 5.0 V

Logic 0 Voltage 0 0.8 V

Logic 1 Current (V

Logic 0 Current (V

Logic 1 Current (V

Logic 0 Current (V

Logic 1 Current (V

Logic 0 Current (V

Specifications subject to change without notice.

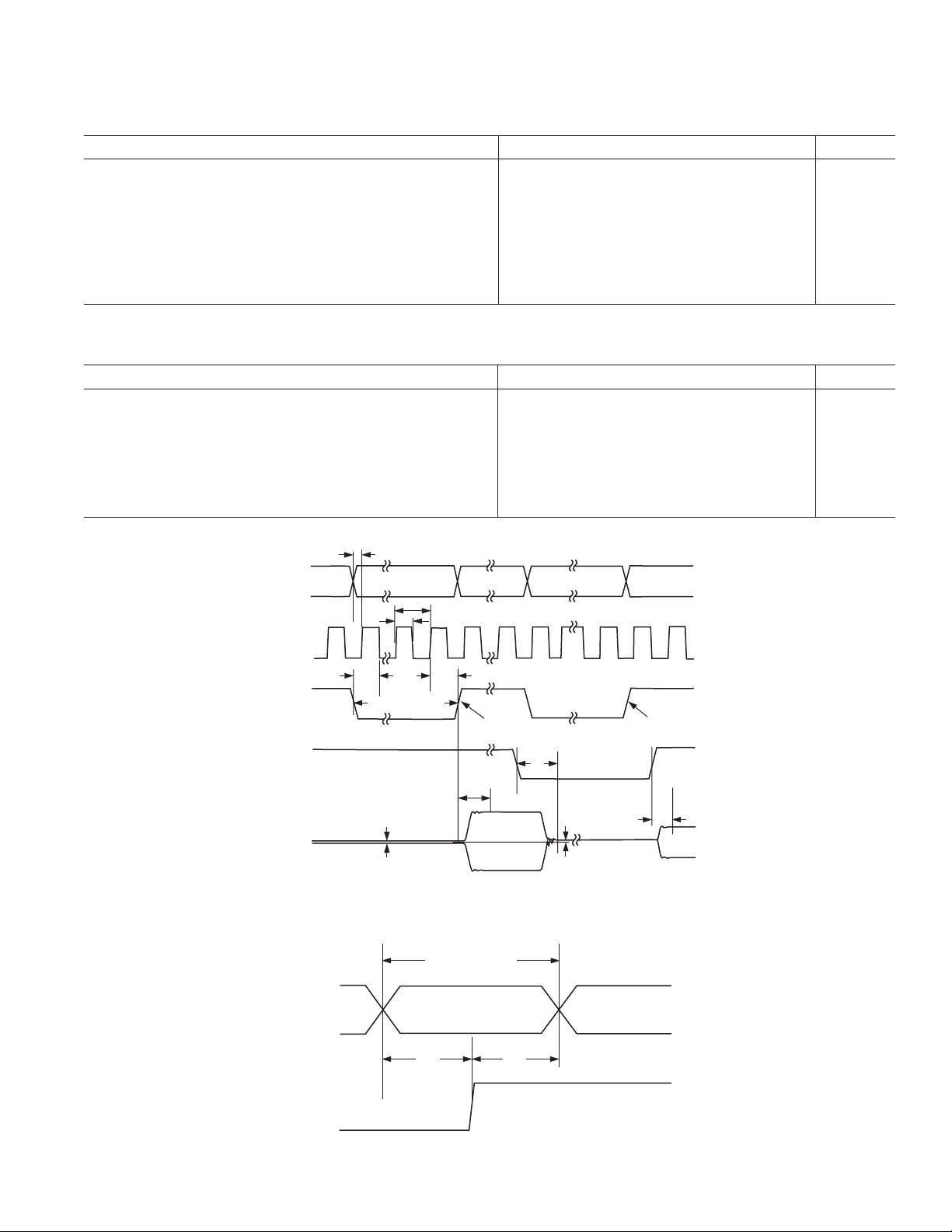

TIMING REQUIREMENTS

= 5 V) CLK, SDATA, DATEN 020nA

INH

= 0 V) CLK, SDATA, DATEN –600 –100 nA

INL

= 5 V) TXEN 50 190 µA

INH

= 0 V) TXEN –250 –30 µA

INL

= 5 V) SLEEP 50 190 µA

INH

= 0 V) SLEEP –250 –30 µA

INL

(Full Temperature Range, VCC = 5 V, tR = tF = 4 ns, f

= 8 MHz, unless otherwise noted.)

CLK

Parameter Min Typ Max Unit

Clock Pulsewidth (t

Clock Period (t

Setup Time SDATA vs. Clock (t

Setup Time DATEN vs. Clock (t

Hold Time SDATA vs. Clock (t

Hold Time DATEN vs. Clock (t

)16.0 ns

WH

)32.0 ns

C

) 5.0 ns

DS

)15.0 ns

ES

) 5.0 ns

DH

) 3.0 ns

EH

Input Rise and Fall Times, SDATA, DATEN, Clock (tR, tF)10ns

Specifications subject to change without notice.

t

DS

SDATA

CLK

VALID DATA-WORD G1

MSB. . . .LSB

t

C

t

WH

VALID DATA-WORD G2

DATEN

TXEN

ANALOG

OUTPUT

t

ES

8 CLOCK CYCLES

SIGNAL AMPLITUDE (p-p)

t

EH

GAIN TRANSFER (G1)

t

GS

t

OFF

Figure 2. Serial Interface Timing

VALID DATA BIT

SDATA

MSB MSB-1 MSB-2

t

DH

CLK

t

DS

GAIN TRANSFER (G2)

t

ON

REV. 0

Figure 3. SDATA Timing

–3–

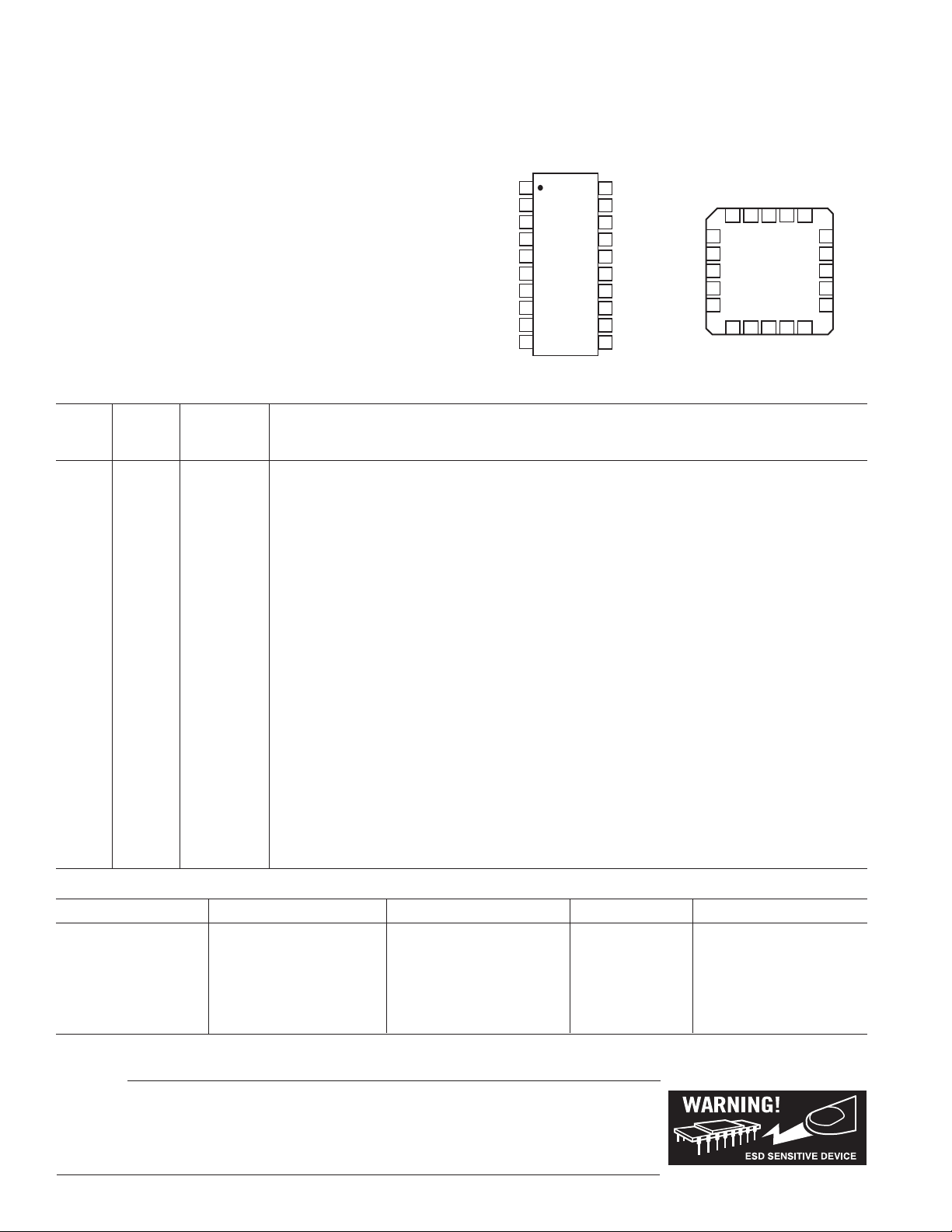

AD8328

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 V

Input Voltage

20-Lead

PIN CONFIGURATIONS

QSOP

20-Lead

LFCSP

VIN+, VIN– . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.5 V p-p

DATEN, SDATA, CLK,

SLEEP, TXEN . . . . . . . . . . . . . . . . . . . . –0.8 V to +5.5 V

Internal Power Dissipation

QSOP, LFCSP . . . . . . . . . . . . . . . . . . . . . . . . . . . 700 mW

Operating Temperature Range . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature, Soldering 60 seconds . . . . . . . . . . 300°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

GND

V

GND

GND

V

V

GND

DATEN

SDATA

CLK

CC

IN+

IN–

2

3

4

AD8328

5

TOP VIEW

(Not to Scale)

6

7

8

9

10

NC = NO CONNECT

20

19

18

17

16

15

14

13

12

11

GND

V

CC

TXEN

RAMP

V

OUT

V

OUT

BYP

NC

SLEEP

GND

CC

V

1

GND

2

GND

+

–

V

IN+

V

IN–

GND

3

(Not to Scale)

4

5

6 78910

DATEN

GND

GND

AD8328

TOP VIEW

CLK

SDATA

CC

V

GND

TXEN

161720 19 18

SLEEP

15

RAMP

V

14

OUT

+

V

13

OUT

–

12

BYP

11

NC

1

PIN FUNCTION DESCRIPTIONS

Pin No. Pin No.

20-Lead 20-Lead

LFCSP QSOP Mnemonic Description

1 ,2, 5, 1, 3, 4, 7, GND Common External Ground Reference

9, 18, 19 11, 20

17, 20 2, 19 V

35 V

46 V

CC

IN+

IN–

Common Positive External Supply Voltage. A 0.1 µF capacitor must decouple each pin.

Noninverting Input. DC-biased to approximately VCC/2. Should be ac-coupled with a 0.1 µF capacitor.

Inverting Input. DC-biased to approximately VCC/2. Should be ac-coupled with a 0.1 µF capacitor.

68 DATEN Data Enable Low Input. This port controls the 8-bit parallel data latch and shift register. A Logic 0- to-1

transition transfers the latched data to the attenuator core (updates the gain) and simultaneously

inhibits serial data transfer into the register. A 1-to-0 transition inhibits the data latch (holds the previous

gain state) and simultaneously enables the register for serial data load.

79 SDATA Serial Data Input. This digital input allows for an 8-bit serial (gain) word to be loaded into the internal

register with the MSB (most significant bit) first.

810CLK Clock Input. The clock port controls the serial attenuator data transfer rate to the 8-bit master-slave

register. A Logic 0-to-1 transition latches the data bit and a 1-to-0 transfers the data bit to the slave.

This requires the input serial data-word to be valid at or before this clock transition.

10 12 SLEEP Low Power Sleep Mode. In the Sleep mode, the AD8328’s supply current is reduced to 20 µA. A Logic 0

powers down the part (High Z

State), and a Logic 1 powers up the part.

OUT

12 14 BYP Internal Bypass. This pin must be externally ac-coupled (0.1 µF capacitor).

13 15 V

14 16 V

OUT–

OUT+

Negative Output Signal

Positive Output Signal

15 17 RAMP External RAMP Capacitor (optional)

16 18 TXEN Logic 0 disables forward transmission. Logic 1 enables forward transmission.

ORDERING GUIDE

Model Temperature Range Package Description θ

AD8328ARQ –40°C to +85°C 20-Lead QSOP 83.2°C/W

AD8328ARQ-REEL –40°C to +85°C 20-Lead QSOP 83.2°C/W

AD8328ARQ-EVAL Evaluation Board

AD8328ACP –40°C to +85°C 20-Lead LFCSP 30.4°C/W

AD8328ACP-REEL –40°C to +85°C 20-Lead LFCSP 30.4°C/W

JA

1

1

2

2

AD8328ACP-EVAL Evaluation Board

1

Thermal Resistance measured on SEMI standard 4-layer board.

2

Thermal Resistance measured on SEMI standard 4-layer board, paddle soldered to board.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD8328 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

Package Option

RQ-20

RQ-20

CP-20

CP-20

REV. 0–4–

Typical Performance Characteristics–AD8328

FREQUENCY – MHz

–40

41.6

V

OUT

– dBmV

–30

–20

–10

0

10

20

30

40

50

60

41.7 41.8 41.9 42 42.1 42.2 42.3

V

OUT

= 57dBmV/TONE

@ MAX GAIN

42.4 42.5

55

60

V

= 61dbmV

OUT

@MAX GAIN

65

DISTORTION – dBc

70

75

5

15

25

V

= 60dbmV

OUT

@MAX GAIN

V

= 59dbmV

OUT

@MAX GAIN

35 45 55 65

FREQUENCY – MHz

TPC 1. Second-Order Harmonic Distortion

vs. Frequency for Various Output Powers

–50

V

= 60dBmV

OUT

@ MAX GAIN

–55

–60

–65

DISTORTION – dBc

–70

TA = –40 C

TA = +25 C

TA = +85 C

50

V

= 61dBmV

OUT

@MAX GAIN

55

60

DISTORTION – dBc

65

70

5

15

V

= 60dBmV

OUT

@MAX GAIN

V

= 59dBmV

OUT

@MAX GAIN

35 45 55 65

25

FREQUENCY – MHz

TPC 4. Third-Order Harmonic Distortion vs.

Frequency for Various Output Powers

–50

V

= 60dBmV

OUT

@ MAX GAIN

–55

–60

DISTORTION – dBc

TA = +85 C

TA = –40 C

TA = +25 C

–75

515 6525 35 45 55

TPC 2. Second-Order Harmonic Distortion

vs. Frequency vs. Temperature

10

0

–10

–20

–30

–40

– dBm

OUT

–50

P

–60

–70

–80

REV. 0

–90

FREQUENCY – MHz

CH PWR

ACP

C0

c11

c11

C0

cu1

TPC 3. Adjacent Channel Power

SPAN 750kHz75kHz/DIV

60dBmV

–58.2dB

cu1

–5–

–65

56515

25 35 45

FREQUENCY – MHz

55

TPC 5. Third-Order Harmonic Distortion vs.

Frequency vs. Temperature

TPC 6. Two-Tone Intermodulation Distortion

Loading...

Loading...