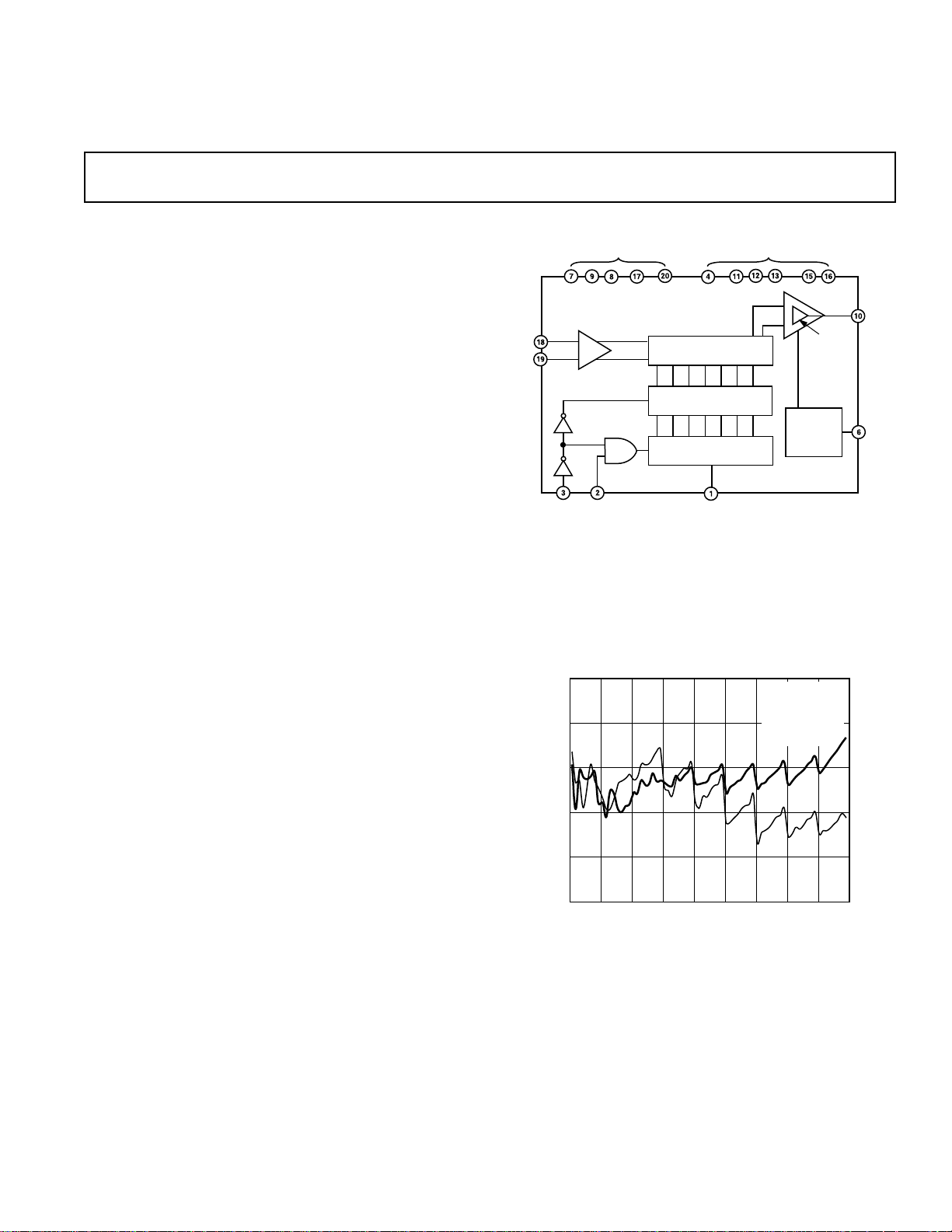

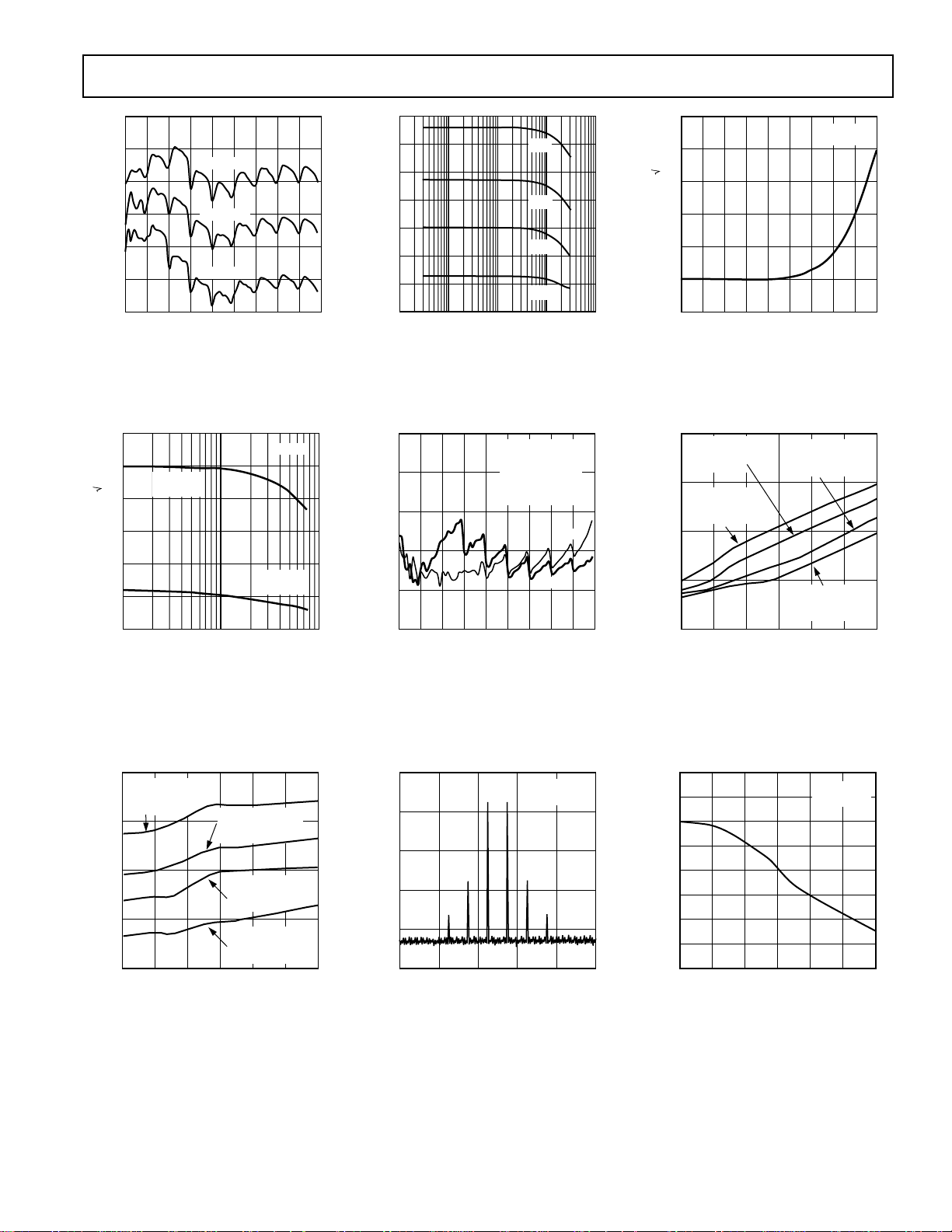

Gain Programmable

GAIN CONTROL – Decimal

DISTORTION – dBc

–90

0 8 16 24 32 40 48 56 64 72

–80

–70

–60

–50

–40

fO = 42MHz

V

IN

= 137mV p-p

(P

IN

= –15dBm)

(P

OUT

= 11dBm @

MAX GAIN)

HD3

HD2

a

FEATURES

Linear in dB Gain Response Over >53 dB Range

Drives Low Distortion >11 dBm Signal into 75 ⍀ Load:

–53 dBc SFDR at 42 MHz

Very Low Output Noise Level

Maintains Constant 75 ⍀ Output Impedance

Power-Up and Power-Down Condition

No Line Transformer Required

Upper Bandwidth: 235 MHz (Min Gain)

9 V Single Supply Operation

Power-Down Functionality

Supports SPI Interface

Low Cost

APPLICATIONS

Gain Programmable Line Driver

HFC High Speed Data Modems

Interactive CATV Set-Top Boxes

CATV Plant Test Equipment

General Purpose IF Variable Gain Block

VIN+

VIN–

CATV Line Driver

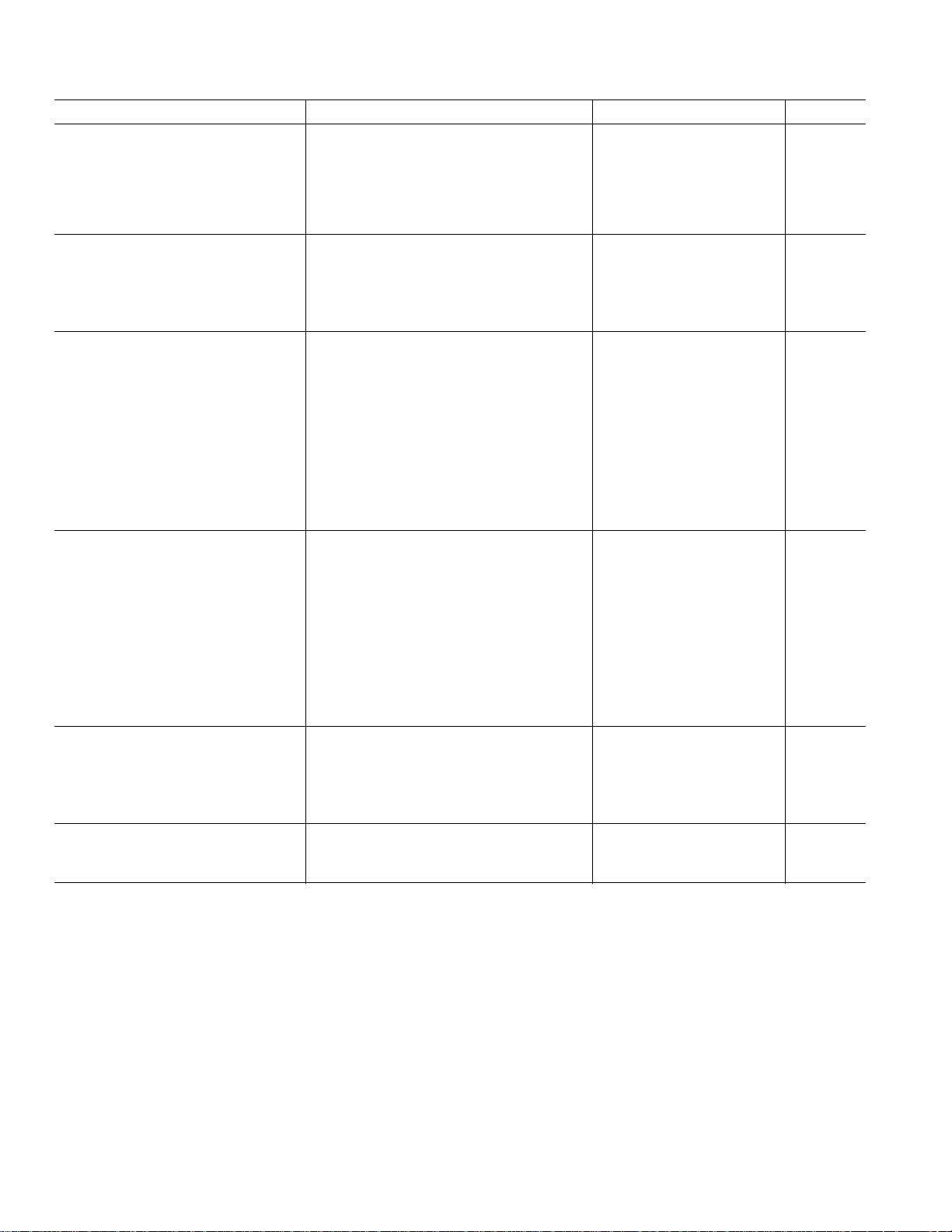

FUNCTIONAL BLOCK DIAGRAM

AD8321

INV

DATEN CLK

ATTENUATOR CORE

DATA LATCH

DATA SHIFT REGISTER

DATA SHIFT REGISTER

SDATA

AD8321

GNDVCC

PWR

AMP

REVERSE

AMP

POWER-

DOWN/

SWITCH

INTER

VOUT

PD

DESCRIPTION

The AD8321 is a low cost digitally controlled variable gain

amplifier optimized for coaxial line driving applications such as

cable modems that are designed to the DOCSIS* (upstream)

standard. An 8-bit serial word determines the desired output

gain over a 53.4 dB range, resulting in gain changes of 0.75 dB/

LSB.

The AD8321 comprises a digitally controlled variable attenuator

of 0 dB to –53.4 dB, which is preceded by a low noise, fixed

gain buffer and followed by a low distortion high power amplifier. The AD8321 accepts a differential or single-ended input

signal. The output is specified for driving a 75 Ω load, such as

coaxial cable, although the AD8321 is capable of driving other

loads. Performance of –53 dBc is achieved with an output level

up to 11 dBm at 42 MHz bandwidth using a 9 V supply.

A key performance and cost advantage of the AD8321 results

from the ability to maintain a constant 75 Ω output impedance

during power-up and power-down conditions. This eliminates

the need for external 75 Ω termination, resulting in twice the

effective output voltage when compared to a standard operational amplifier, thus eliminating the need for a transformer.

*Data-Over-Cable Service Interface Specifications

The AD8321 is packaged in a low cost 20-lead SOIC, operates

from a single +9 V supply, and has an operational temperature

range of –40°C to +85°C.

Figure 1. Harmonic Distortion vs. Gain Control

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

(@ VCC = +9 V, TA = +25ⴗC, VIN = 0.137 V p-p, single-ended input, RL = 75 ⍀, RIN =

AD8321–SPECIFICATIONS

75 ⍀ unless otherwise noted)

Parameter Conditions Min Typ Max Units

INPUT CHARACTERISTICS

Specified AC Voltage Output = 11 dBm, Max Gain 0.137 V p-p

Noise Figure Max Gain, f = 10 MHz 15 dB

Input Resistance Single-Ended Input 820 Ω

Differential Input 900 Ω

Input Capacitance 2.0 pF

GAIN CONTROL INTERFACE

Gain Range 52.4 53.4 54.4 dB

Maximum Gain 25.25 26 26.75 dB

Minimum Gain –28.15 –27.4 –26.4 dB

Gain Scaling Factor 0.7526 dB/LSB

OUTPUT CHARACTERISTICS

Bandwidth (–3 dB) All Gain Codes 120 MHz

Bandwidth Roll-Off f = 65 MHz 0.8 dB

Bandwidth Peaking f = 65 MHz 0 dB

Output Offset Voltage All Gain Codes, Full Temperature Range ±30 mV

Output Noise Spectral Density Max Gain, f = 10 MHz 60 nV/√Hz

Min Gain, f = 10 MHz 20 nV/√Hz

Output Noise Temperature Sensitivity 0 ≤ T

≤ +70°C, Min Gain 0.02 nV/√Hz/°C

A

Power-Down Spectral Density 1 nV/√Hz

1 dB Compression Point Max Gain, f = 10 MHz +19.5 dBm

Output Impedance Power-Up and Power-Down 60 75 90 Ω

OVERALL PERFORMANCE

Worst Harmonic Distortion f = 42 MHz, P

f = 65 MHz, P

Distortion Temperature Sensitivity –40°C ≤ T

A

= 11 dBm, VCC = +9 V –53 dBc

OUT

= 11 dBm, VCC = +9 V –51 dBc

OUT

≤ +85°C 0.03 dBc/°C

Gain Accuracy f = 10 MHz, All Gain Codes ±0.2 dB

Gain Temperature Sensitivity 0 ≤ T

≤ +70°C 0.004 dB/°C

A

Output Settling to 1 mV

Gain Change @ T

Input Change Max Gain, V

= 1 Min to Max Gain, VIN = 0 V 60 ns

DATEN

= 0.15 V Step 30 ns

IN

Signal Feedthrough Power Down, 65 MHz, Min Gain –80 dBc

VIN = 0.137 V p-p

POWER CONTROL

Power-Down Settling Time to 1 mV Max Gain, V

Power-Up Settling Time to 1 mV Max Gain, V

Power-Up/Down Pedestal Offset Max Gain, V

= 0 40 ns

IN

= 0 300 ns

IN

= 0 ±30 mV

IN

Power-Up/Down Glitch Max Gain, VIN = 0 40 mV p-p

POWER SUPPLY

Quiescent Current Power-Up, V

= +9 V 82 90 97 mA

CC

Power-Down, VCC = +9 V 45 52 60 mA

Specifications subject to change without notice.

–2–

REV. 0

AD8321

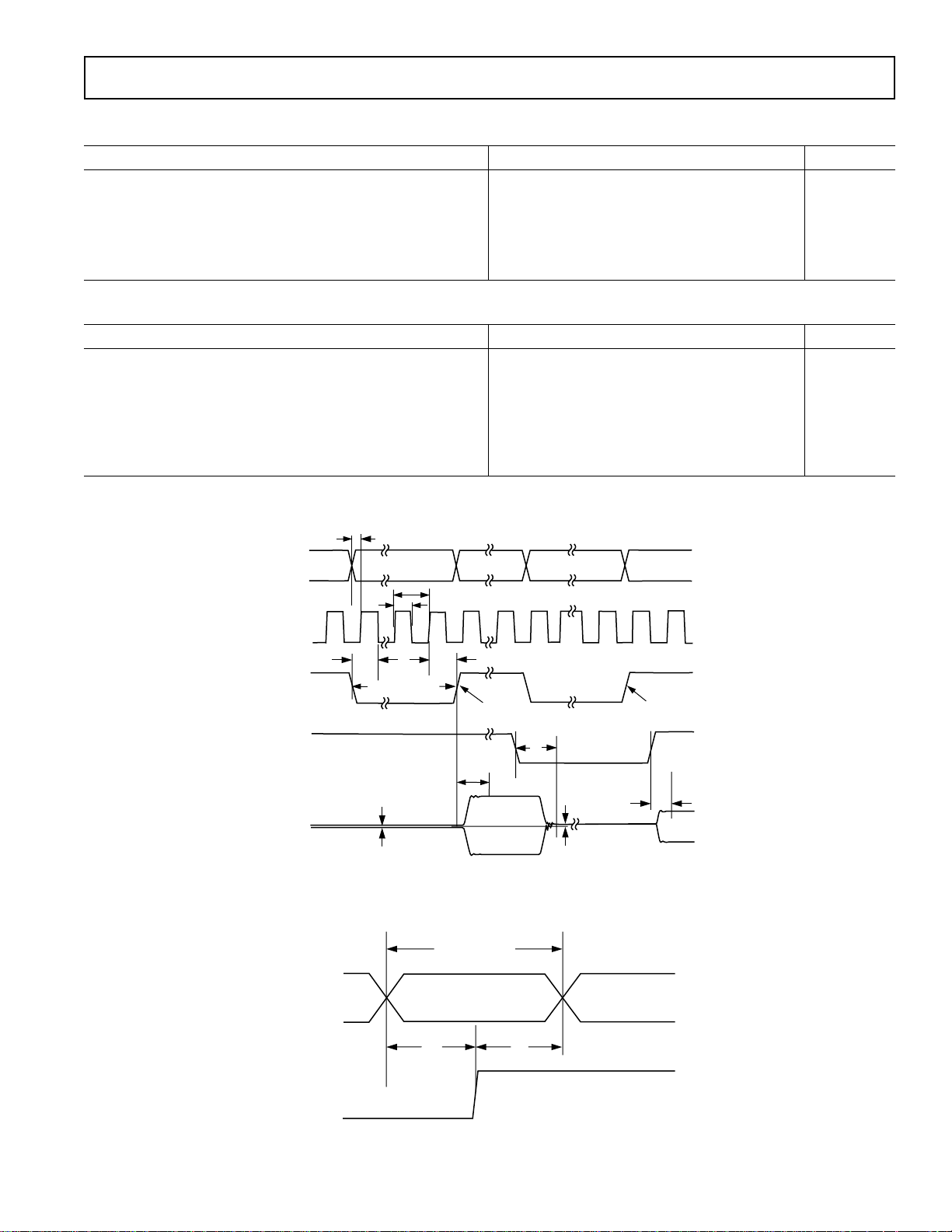

LOGIC INPUTS (TTL/CMOS Logic)

(DATEN, CLK, SDATA, VCC = +9 V; Full Temperature Range)

Parameter Min Typ Max Units

Logic “1” Voltage 2.1 5.0 V

Logic “0” Voltage 0 0.8 V

Logic “1” Current (V

Logic “0” Current (V

Logic “1” Current (V

Logic “0” Current (V

TIMING REQUIREMENTS

= 5 V) CLK, SDATA, DATEN 020nA

INH

= 0 V) CLK, SDATA, DATEN –600 –100 nA

INL

= 5 V) PD 50 190 µA

INH

= 0 V) PD –250 –30 µA

INL

(Full Temperature Range, VCC = +9 V, TR = TF = 4 ns, f

= 8 MHz unless otherwise noted.)

CLK

Parameter Min Typ Max Units

Clock Pulsewidth (T

Clock Period (T

Setup Time SDATA vs. Clock (T

Setup Time DATEN vs. Clock (T

Hold Time SDATA vs. Clock (T

Hold Time DATEN vs. Clock (T

) 16.0 ns

WH

) 32.0 ns

C

) 5.0 ns

DS

) 15.0 ns

ES

) 5.0 ns

DH

) 3.0 ns

EH

Input Rise and Fall Times, SDATA, DATEN, Clock (TR, TF)10ns

T

DS

SDATA

CLK

VALID DATA WORD G1

MSB. . . .LSB

T

C

T

WH

VALID DATA WORD G2

DATEN

PD

ANALOG

OUTPUT

T

ES

8 CLOCK CYCLES

SIGNAL AMPLITUDE (p-p)

Figure 2. Serial Interface Timing

SDATA

MSB

CLK

T

EH

GAIN TRANSFER (G1)

T

GS

VALID DATA BIT

MSB-1 MSB-2

T

DS

T

T

DH

OFF

PEDESTAL

GAIN TRANSFER (G2)

T

ON

Figure 3. SDATA Timing

–3–REV. 0

AD8321

ABSOLUTE MAXIMUM RATINGS*

Supply Voltage +V

S

Pins 7, 8, 9, 17, 20 . . . . . . . . . . . . . . . . . . . . . . . . . . . +11 V

Input Voltages

Pins 18, 19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±0.5 V

Pins 1, 2, 3, 6 . . . . . . . . . . . . . . . . . . . . . . –0.8 V to +5.5 V

Internal Power Dissipation

Small Outline (R) . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.90 W

Operating Temperature Range . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Lead Temperature, Soldering 60 seconds . . . . . . . . . . +300°C

*Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

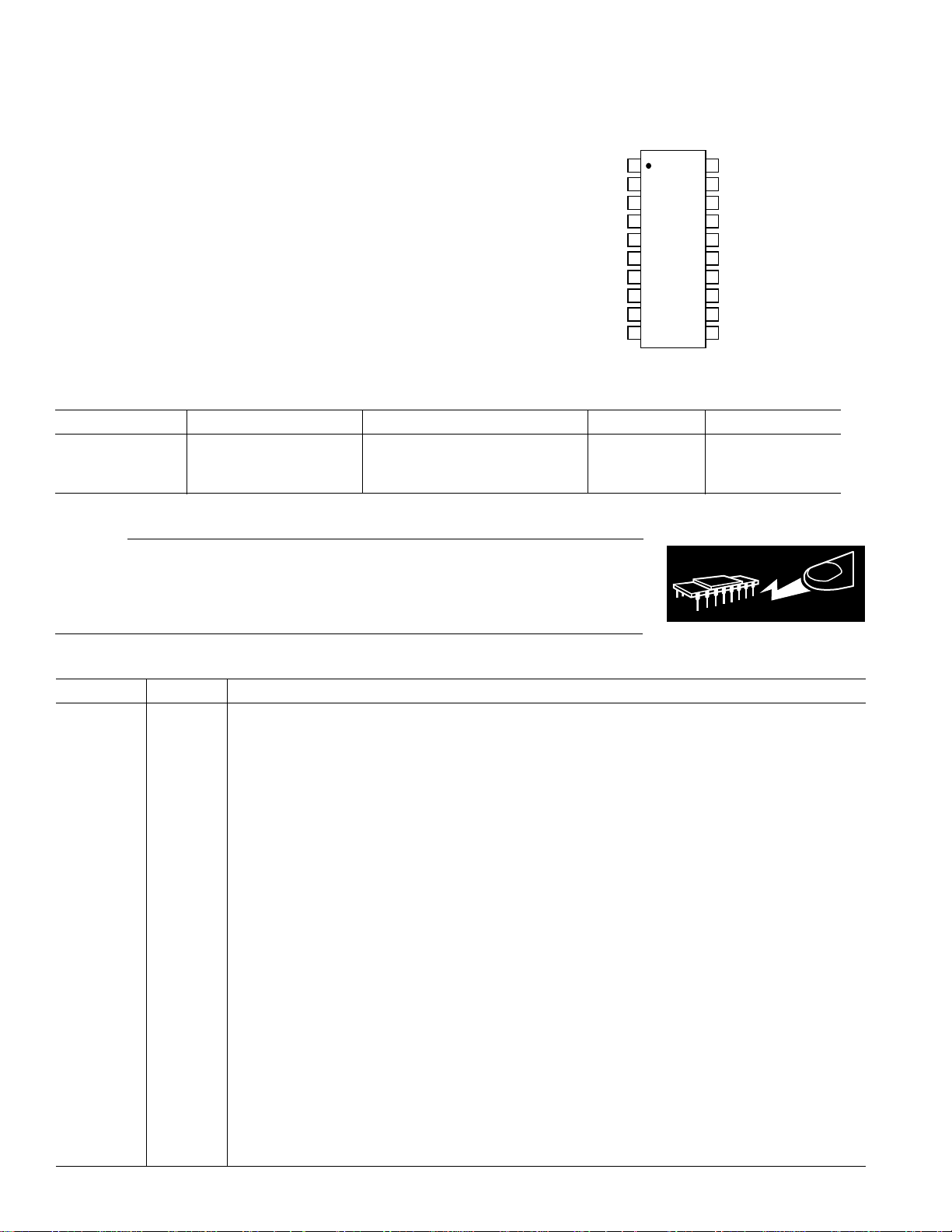

PIN CONFIGURATION

SDATA

CLK

DATEN

GND

BYP1

PD

VCC

VCC

VCC

VOUT

1

2

3

4

5

AD8321

TOP VIEW

6

(Not to Scale)

7

8

9

10

20

VCC

19

VIN–

18

VIN+

17

VCC

16

GND

15

GND

14

BYP2

13

GND

12

GND

11

GND

ORDERING GUIDE

Model Temperature Range Package Description

JA

Package Option

AD8321AR –40°C to +85°C 20-Lead SOIC 58°C/W* R-20

AD8321AR-REEL –40°C to +85°C 20-Lead SOIC 58°C/W* R-20

AD8321-EVAL Evaluation Board

*Thermal Resistance measured on SEMI standard 4-layer board.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

WARNING!

Although the AD8321 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

ESD SENSITIVE DEVICE

PIN FUNCTION DESCRIPTIONS

Pin Function Description

1 SDATA Serial Data Input. This digital input allows for an 8-bit serial (gain) word to be loaded into the internal

register with the MSB (most significant bit) first.

2 CLK Clock Input. The clock port controls the serial attenuator data transfer rate to the 8-bit master-slave

register. A Logic 0-to-1 transition latches the data bit and a 1-to-0 transfers the data bit to the slave.

This requires the input serial data word to be valid at or before this clock transition.

3 DATEN Data Enable Low Input. This port controls the 8-bit parallel data latch and shift register. A Logic 0-to-

1 transition transfers the latched data to the attenuator core (updates the gain) and simultaneously

inhibits serial data transfer into the register. A 1-to-0 transition inhibits the data latch (holds the previous gain state) and simultaneously enables the register for serial data load.

4, 11, 12,

13, 15, 16 GND Common External Ground Reference.

5 BYP1 V

/2 Reference Pin. A dc output reference level that is equal to 1/2 of the supply voltage (VCC). This

CC

port should be externally ac-decoupled (0.1 µF capacitor). For external use of this reference voltage,

buffering is required.

6 PD Power-Down Low Logic Input. A Logic 0 powers down (shuts off) the power amplifier disabling the

output signal and enabling the reverse amplifier. A Logic 1 enables the output power amplifier and

disables the reverse amplifier.

7, 8, 9, 17, 20 VCC Common Positive External Supply Voltage.

10 VOUT Output Signal Port. DC-biased to approximately V

CC

/2.

14 BYP2 Internal Bypass. This pin must be externally ac-decoupled (0.1 µF cap).

18 VIN+ Noninverting Input. DC-biased to approximately V

/2. For single-ended inverting operation, use

CC

0.1 µF decoupling capacitor between VIN+ and ground.

19 VIN– Inverting Input. DC-biased to approximately V

/2. Should be ac-coupled with a 0.1 µF capacitor.

CC

–4–

REV. 0

Typical Performance Characteristics–AD8321

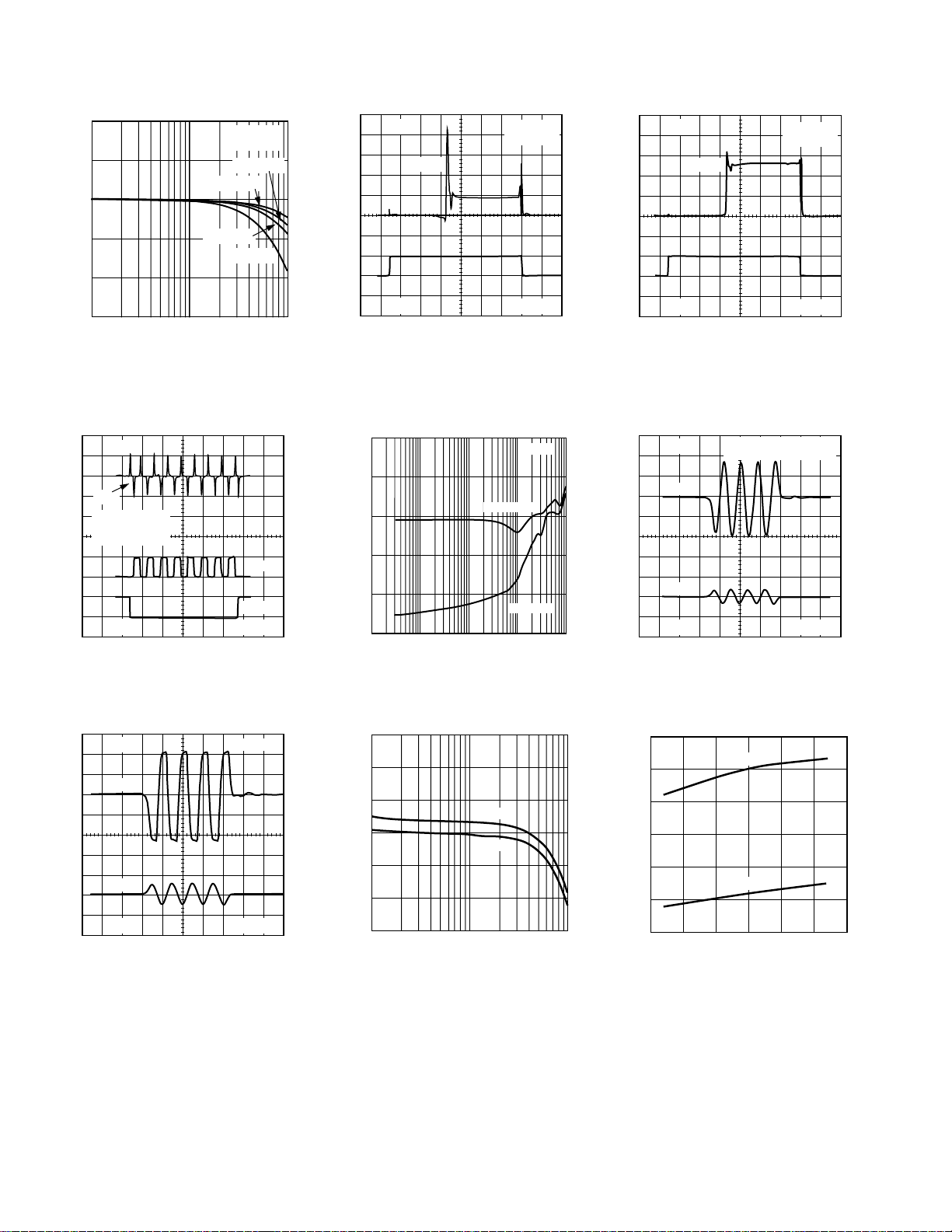

FREQUENCY – MHz

3RD ORDER INTERCEPT – dBm

5

22

23

24

25

27

PO = 11dBm

MAX GAIN

26

15 25

35 45

55

28

29

30

65

0.6

0.3

0

–0.3

–0.6

GAIN ERROR – dB

–0.9

–1.2

08

f = 10MHz

f = 42MHz

f = 65MHz

16 24 32 40 48 56 64 72

GAIN CONTROL – Decimal

Figure 4. Gain Error vs. Gain Control

70

PD = 1

60

50

40

30

OUTPUT NOISE – nV/ Hz

20

10

MAX GAIN

(71D)

MIN GAIN

(00D)

1 10 100

FREQUENCY – MHz

Figure 7. Output Referred Noise vs.

Frequency

30

–10

GAIN – dB

–20

–30

–40

20

10

0

0.1

1 10 100

FREQUENCY – MHz

71D

46D

23D

00D

Figure 5. AC Response

–30

–40

–50

–60

DISTORTION – dBc

–70

–80

0816

GAIN CONTROL – Decimal

fO = 65MHz

= 0.137V p-p

V

IN

(P

= –15dBm)

IN

(P

= 11dBm @

OUT

MAX GAIN)

HD2

24 40 48 56 64 72

32

Figure 8. Harmonic Distortion vs.

Gain Control

HD3

1000

70

60

50

40

30

OUTPUT NOISE – nV/ Hz

20

10

08

16 24 32 40 48 56 64 72

GAIN CONTROL – Decimal

f = 10MHz

PD =1

Figure 6. Output Referred Noise vs.

Gain Control

–47

PIN = –14dBm

= 12dBm @

(P

OUT

MAX GAIN)

–50

PIN = –13dBm

= 13dBm @

(P

OUT

MAX GAIN)

–53

DISTORTION – dBc

–56

–59

5 15 25 45 55 65

FUNDAMENTAL FREQUENCY – MHz

PIN = –15dBm

(P

OUT

MAX GAIN)

PIN = –17dBm

(P

OUT

MAX GAIN)

35

= 11dBm @

= 9dBm @

Figure 9. Second Order Harmonic

Distortion vs. Frequency for Various

Input Levels

–47

PIN = –13dBm

(P

MAX GAIN)

–50

–53

DISTORTION – dBc

–56

–59

5 15 25 45 55 65

Figure 10. Third Order Harmonic

Distortion vs. Frequency for Various

Input Levels

REV. 0

= 13dBm @

OUT

FUNDAMENTAL FREQUENCY – MHz

PIN = –14dBm

= 12dBm @

(P

OUT

MAX GAIN)

PIN = –15dBm

= 11dBm @

(P

OUT

MAX GAIN)

PIN = –17dBm

= 9dBm @

(P

OUT

MAX GAIN)

35

20

0

–20

– dBm

OUT

–40

P

–60

–80

41.0

41.4 41.8 42.2 42.6 43.0

FREQUENCY – MHz

PO = 11dBm

MAX GAIN

Figure 11. Two-Tone Intermodulation Distortion

–5–

Figure 12. Third Order Intercept vs.

Frequency

AD8321

34

30

26

GAIN – dB

22

18

14

1 10 100

FREQUENCY – MHz

MAX GAIN

= 11dBm

P

O

CL = 10pF

CL = 0pF

CL = 20pF

CL = 50pF

Figure 13. AC Response for Various

Capacitor Loads

7.5mV

V

OUT

VIN = 0V p-p

MAX GAIN

tr(CLK) = 3ns

CLK

DATEN

5V

150ns

Figure 16. Clock Feedthrough

5mV

5V

V

OUT

MIN GAIN

V

= 0V p-p

IN

PD

75ns

Figure 14. Power Up/Power Down

Glitch

0

–20

–40

–60

FEEDTHROUGH – dB

–80

–100

0.1

1 10 100

FREQUENCY – MHz

PD = 0

MAX GAIN

MIN GAIN

1000

Figure 17. Input Signal Feedthrough

vs. Frequency

15mV

5V

V

OUT

MAX GAIN

= 0V p-p

V

IN

PD

75ns

Figure 15. Power Up/Power Down

Glitch

0.75V

V

OUT

V

IN

200mV

MAX GAIN

V

= 0V p-p – 0.137V p-p

IN

30ns

Figure 18. Output Settling Time Due

to Input Change

1.5V

V

V

OUT

IN

0.5V

MAX GAIN

30ns

Figure 19. Overload Recovery

90

85

80

75

70

IMPEDANCE – V

65

60

1 10 100

PD = 0

PD = 1

FREQUENCY – MHz

Figure 20. Output Impedance vs.

Frequency

100

90

80

– mA

70

CC

+I

60

50

40

–50

–25 0 25

PD =1

PD = 0

50 75 100

TEMPERATURE – 8C

Figure 21. Supply Current vs.

Temperature

–6–

REV. 0

Loading...

Loading...