Triple Differential Driver

FEATURES

Triple high speed fully differential driver

225 MHz −3 dB large signal bandwidth

Easily drives 1.4 V p-p video signal into source-terminated

100 Ω UTP cable

1600 V/µs slew rate

Fixed internal gain of 2

Internal common-mode feedback network

Output balance error −60 dB @ 50 MHz

Differential input and output

Differential-to-differential or single-ended-to-differential

operation

Adjustable output common-mode voltage

Output pull-down feature for line isolation

Low distortion: 64 dB SFDR @ 10 MHz on 5 V supply,

= 200 Ω

R

L, dm

Low offset: 4 mV typical output referred on 5 V supply

Low power: 26 mA @ 5 V for three drivers

Wide supply voltage range: +5 V to ±5 V

Available in space-saving packaging: 4 mm × 4 mm LFCSP

APPLICATIONS

KVM (keyboard-video-mouse) networking

UTP (unshielded twisted pair) driving

Differential signal multiplexing

GENERAL DESCRIPTION

The AD8133 is a major advancement beyond using discrete

op amps for driving differential RGB signals over twisted pair

cable. The AD8133 is a triple, low cost differential or singleended input to differential output driver, and each amplifier has

a fixed gain of 2 to compensate for the attenuation of line termination resistors. The AD8133 is specifically designed for RGB

signals but can be used for any type of analog signals or high speed

data transmission. The AD8133 is capable of driving either Category 5 unshielded twisted pair (UTP) cable or differential printed

circuit board transmission lines with minimal signal degradation.

With Output Pull-Down

AD8133

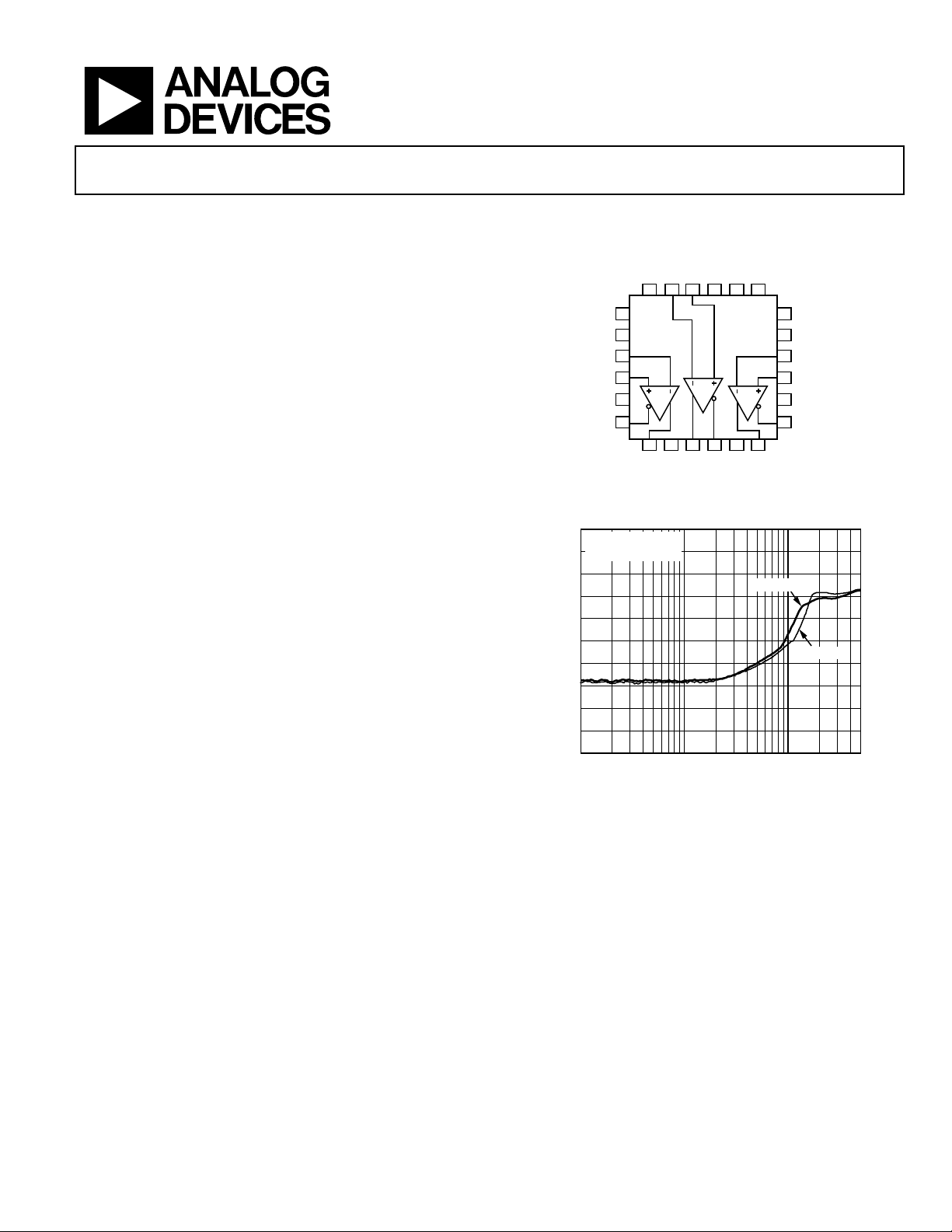

FUNCTIONAL BLOCK DIAGRAM

A

B

OCM

VS+–IN B

+IN B

B

A

S+

V

+OUT A

+OUT B

OPD

V

–IN A

+IN A

V

–OUT A

1

2

S–

3

4

5

S–

6

24 23 22 21 20

7 8 9 10 11

Figure 1.

0

∆V

= 2V p-p

OUT, dm

∆V

OUT, cm

/∆V

OUT, dm

FREQUENCY (MHz)

–10

–20

–30

–40

–50

–60

–70

–80

OUTPUT BALANCE ERROR (dB)

–90

–100

1 10 100 500

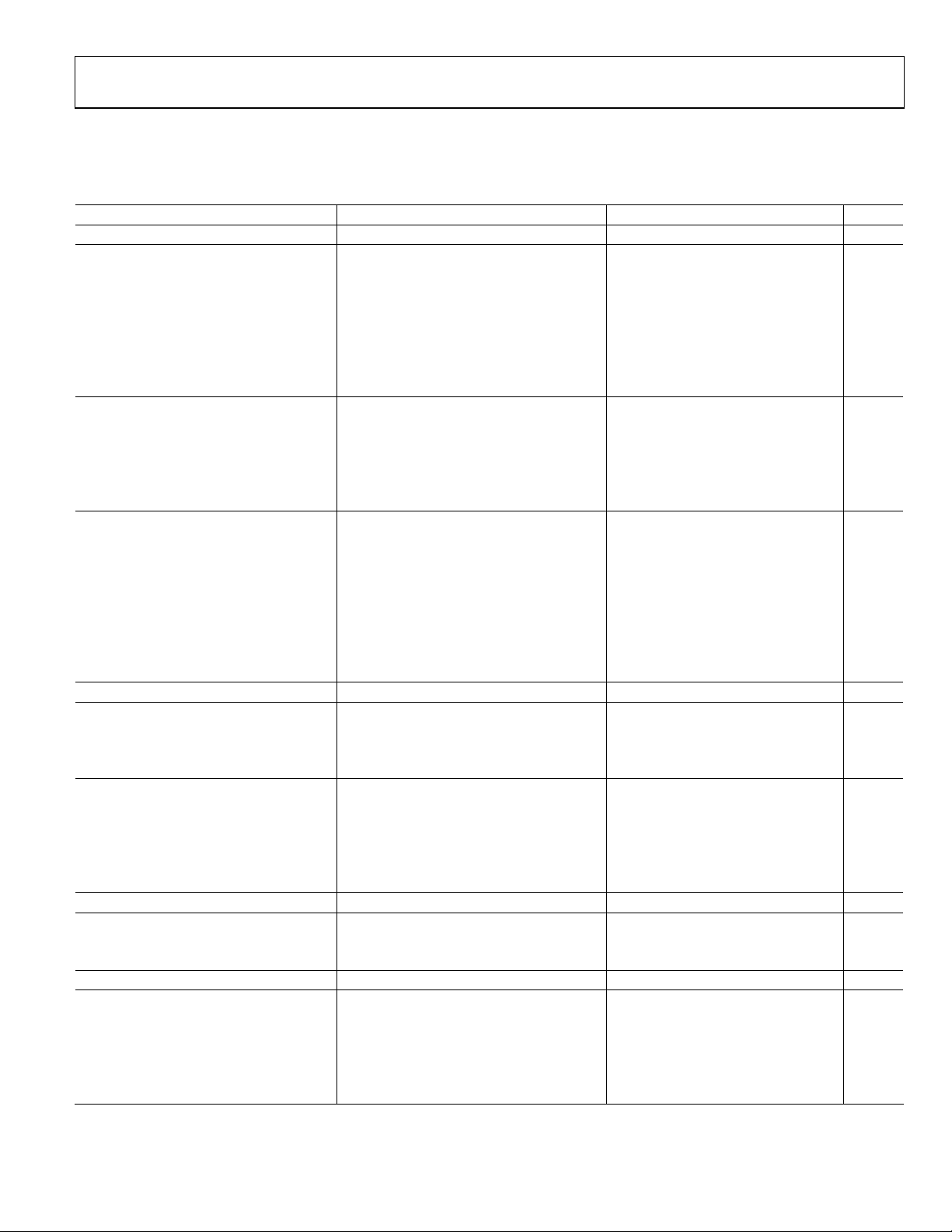

Figure 2. Output Bal ance vs. Fre quency

Manufactured on Analog Devices’ next generation XFCB bipolar process, the AD8133 has a large signal bandwidth of

225 MHz and a slew rate of 1600 V/µs. The AD8133 has an

internal common-mode feedback feature that provides output

amplitude and phase matching that is balanced to −60 dB at

50 MHz, suppressing harmonics and minimizing radiated electromagnetic interference (EMI).

VS–V

AD8133

C

S+

V

–OUT B

OCM

V

19

12

+OUT C

VS = ±5V

18

17

16

15

14

13

V

OCM

V

S+

–IN C

+IN C

V

S–

–OUT C

VS = +5V

C

04769-0-001

04769-0-034

The outputs of the AD8133 can be set to a low voltage state to

be used with series diodes for line isolation, allowing easy differential multiplexing over the same twisted pair cable. The

AD8133 driver can be used in conjunction with the AD8129

and AD8130 differential receivers.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

The output common-mode level is easily adjustable by applying

a voltage to the V

input pin. The V

OCM

input can also be used

OCM

to transmit signals on the output common-mode voltages.

The AD8133 is available in a 24-lead LFCSP package and can

operate over the temperature range of −40°C to +85°C.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

AD8133

TABLE OF CONTENTS

Specifications..................................................................................... 3

Driving a Capacitive Load......................................................... 13

Absolute Maximum Ratings............................................................ 5

Thermal Resistance ...................................................................... 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Descriptions............................. 6

Typical Performance Characteristics............................................. 7

Theory of Operation ...................................................................... 12

Definition of Terms.................................................................... 12

Analyzing an Application Circuit............................................. 12

Closed-Loop Gain...................................................................... 12

Calculating an Application Circuit’s Input Impedance ......... 13

Input Common-Mode Voltage Range in Single-Supply

Applications

.................................................................................. 13

REVISION HISTORY

7/04—Revision 0: Initial Version

Output Pull-Down (OPD) ........................................................ 13

Output Common-Mode Control............................................. 13

Applications..................................................................................... 14

Driving RGB Video Signals Over Category-5 UTP Cable.... 14

Output Pull-Down ..................................................................... 15

KVM Networks........................................................................... 15

Layout and Power Supply Decoupling Considerations .... 15

Amplifier-to-Amplifier Isolation ............................................. 15

Exposed Paddle (EP).................................................................. 15

Outline Dimensions....................................................................... 16

Ordering Guide .......................................................................... 16

Rev. 0 | Page 2 of 16

AD8133

SPECIFICATIONS

VS = ±5V, V

Table 1.

Parameter Conditions Min Typ Max Unit

DIFFERENTIAL INPUT PERFORMANCE

DYNAMIC PERFORMANCE

−3 dB Small Signal Bandwidth VO = 0.2 V p-p 450 MHz

−3 dB Large Signal Bandwidth VO = 2 V p-p 225 MHz

Bandwidth for 0.1 dB Flatness VO = 0.2 V p-p 60 MHz

V

Slew Rate VO = 2 V p-p, 25% to 75% 1600 V/µs

Settling Time to 0.1% VO = 2 V Step 15 ns

Isolation between Amplifiers f = 10 MHz, between Amplifiers A and B 81 dB

DIFFERENTIAL INPUT CHARACTERISTICS

Input Common-Mode Voltage Range −5 to +5 V

Input Resistance Differential 1.5 kΩ

Single-Ended Input 1.13 kΩ

Input Capacitance Differential 1 pF

DC CMRR ∆V

DIFFERENTIAL OUTPUT CHARACTERISTICS

Differential Signal Gain ∆V

Output Voltage Swing Each Single-Ended Output VS− + 1.9 VS+ – 1.6 V

Output Offset Voltage −24 +4 +24 mV

Output Offset Drift T

Output Balance Error ∆V

DC −70 −58 dB

Output Voltage Noise (RTO) f = 1 MHz 25 nV/√Hz

Output Short-Circuit Current 90 mA

V

to V

OCM

V

DYNAMIC PERFORMANCE

OCM

−3 dB Bandwidth ∆V

Slew Rate V

DC Gain ∆V

V

INPUT CHARACTERISTICS

OCM

Input Voltage Range ±3.1 V

Input Resistance 70 kΩ

Input Offset Voltage −15 −6 +15 mV

Input Offset Voltage Drift T

DC CMRR ∆V

POWER SUPPLY

Operating Range +4.5 ±6 V

Quiescent Current 28 29 mA

PSRR ∆V

OUTPUT PULL-DOWN PERFORMANCE

OPD Input Low Voltage VS− to VS+ − 4.15 V

OPD Input High Voltage VS+ − 3.15 to VS+ V

OPD Input Bias Current 67 90 µA

OPD Assert Time 100 ns

OPD De-Assert Time 100 ns

Output Voltage When OPD Asserted Each Output, OPD Input @ VS+ VS− + 0.86 VS− + 0.90 V

= 0 V @ 25°C, RL, dm = 200 Ω, unless otherwise noted. T

OCM

= 2 V p-p 55 MHz

O

/∆V

OUT, dm

OUT, dm

to T

MIN

/∆V

OUT, cm

PERFORMANCE

O, cm

= 100 mV p-p

OCM

= −1 V to +1 V, 25% to 75% 1000 V/µs

OCM

= ±1 V 0.980 0.995 1.005 V/V

OCM

to T

MIN

OUT, dm

OUT, dm

, ∆V

IN, cm

IN, cm

/∆V

; ∆V

IN, dm

IN, dm

MAX

, ∆V

IN, dm

OUT, dm

MAX

/∆V

, ∆V

OCM

OCM

/∆VS; ∆VS = ±1 V −84 −76 dB

to T

MIN

= −40°C to +85°C.

MAX

= ±1 V −50 dB

= ±1 V 1.925 1.960 2.000 V/V

±30 µV/°C

= 2 V p-p, f = 50 MHz −60 dB

330 MHz

±50 µV/°C

= ±1 V −42 dB

Rev. 0 | Page 3 of 16

AD8133

= 5 V, V

V

S

= 2.5 V @ 25°C, R

OCM

= 200 Ω, unless otherwise noted. T

L, dm

MIN

to T

= −40°C to +85°C.

MAX

Table 2.

Parameter Conditions Min Typ Max Unit

DIFFERENTIAL INPUT PERFORMANCE

DYNAMIC PERFORMANCE

−3 dB Small Signal Bandwidth VO = 0.2 V p-p 400 MHz

−3 dB Large Signal Bandwidth VO = 2 V p-p 200 MHz

Bandwidth for 0.1 dB Flatness VO = 0.2 V p-p 50 MHz

Slew Rate VO = 2 V p-p, 25% to 75% 1400 V/µs

Settling Time to 0.1% VO = 2 V Step 14 ns

Isolation Between Amplifiers f = 10 MHz, between Amplifiers A and B 75 dB

DIFFERENTIAL INPUT CHARACTERISTICS

Input Common-Mode Voltage Range 0 to 5 V

Input Resistance Differential 1.5 kΩ

Single-Ended Input 1.13 kΩ

Input Capacitance Differential 1 pF

DC CMRR ∆V

OUT, dm

/∆V

IN, cm

, ∆V

= ±1 V −50 dB

IN, cm

DIFFERENTIAL OUTPUT CHARACTERISTICS

Differential Signal Gain ∆V

OUT, dm

/∆V

IN, dm

; ∆V

= ±1 V 1.925 1.960 2.000

IN, dm

Output Voltage Swing Each Single-Ended Output VS− + 1.25 VS+ − 1.15 V

Output Offset Voltage −24 +4 +24 mV

Output Offset Drift T

Output Balance Error ∆V

MIN

to T

OUT, cm

MAX

/∆V

IN, dm

, ∆V

±30 µV/°C

= 2 V p-p, f = 50 MHz −60 dB

OUT, dm

DC −70 −58 dB

Output Voltage Noise (RTO) f = 1 MHz 25 nV/√Hz

Output Short-Circuit Current 90 mA

V

PERFORMANCE

OCM

V

DYNAMIC PERFORMANCE

OCM

−3 dB Bandwidth ∆V

Slew Rate V

DC Gain ∆V

V

INPUT CHARACTERISTICS

OCM

= 100 mV p-p

OCM

= −1 V to +1 V, 25% to 75% 700 V/µs

OCM

= ±1 V, T

OCM

MIN

to T

MAX

290 MHz

0.980 0.995 1.005 V/V

Input Voltage Range 1.25 to 3.85 V

Input Resistance 70 kΩ

Input Offset Voltage −15 +2 +15 mV

Input Offset Voltage Drift T

DC CMRR ∆V

MIN

to T

O, dm

MAX

/∆V

OCM

±50 µV/°C

; ∆V

= ±1 V −42 dB

OCM

POWER SUPPLY

Operating Range +4.5 ±6 V

Quiescent Current 26 27 mA

PSRR ∆V

/∆VS; ∆VS = ±1 V −84 −76 dB

OUT, dm

OUTPUT PULL-DOWN PERFORMANCE

OPD Input Low Voltage VS− to VS+ − 3.85 V

OPD Input High Voltage VS+ − 2.85 to VS+ V

OPD Input Bias Current 63 80 µA

OPD Assert Time 100 ns

OPD De-Assert Time 100 ns

Output Voltage When OPD Asserted Each Output, OPD Input @ VS+ VS− + 0.79 VS− + 0.82 V

Rev. 0 | Page 4 of 16

AD8133

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating

Supply Voltage 12 V

All V

OCM

±V

S

Power Dissipation See Figure 3

Input Common-Mode Voltage ±V

S

Storage Temperature −65°C to +125°C

Operating Temperature Range −40°C to +85°C

Lead Temperature Range

300°C

(Soldering 10 sec)

Junction Temperature 150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any

other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions, i.e., θJA is specified

for the device soldered in a circuit board in still air.

Table 4. Thermal Resistance with the Underside Pad

Connected to the Plane

Package Type/PCB Type θ

JA

24-Lead LFCSP/4-Layer 70 °C/W

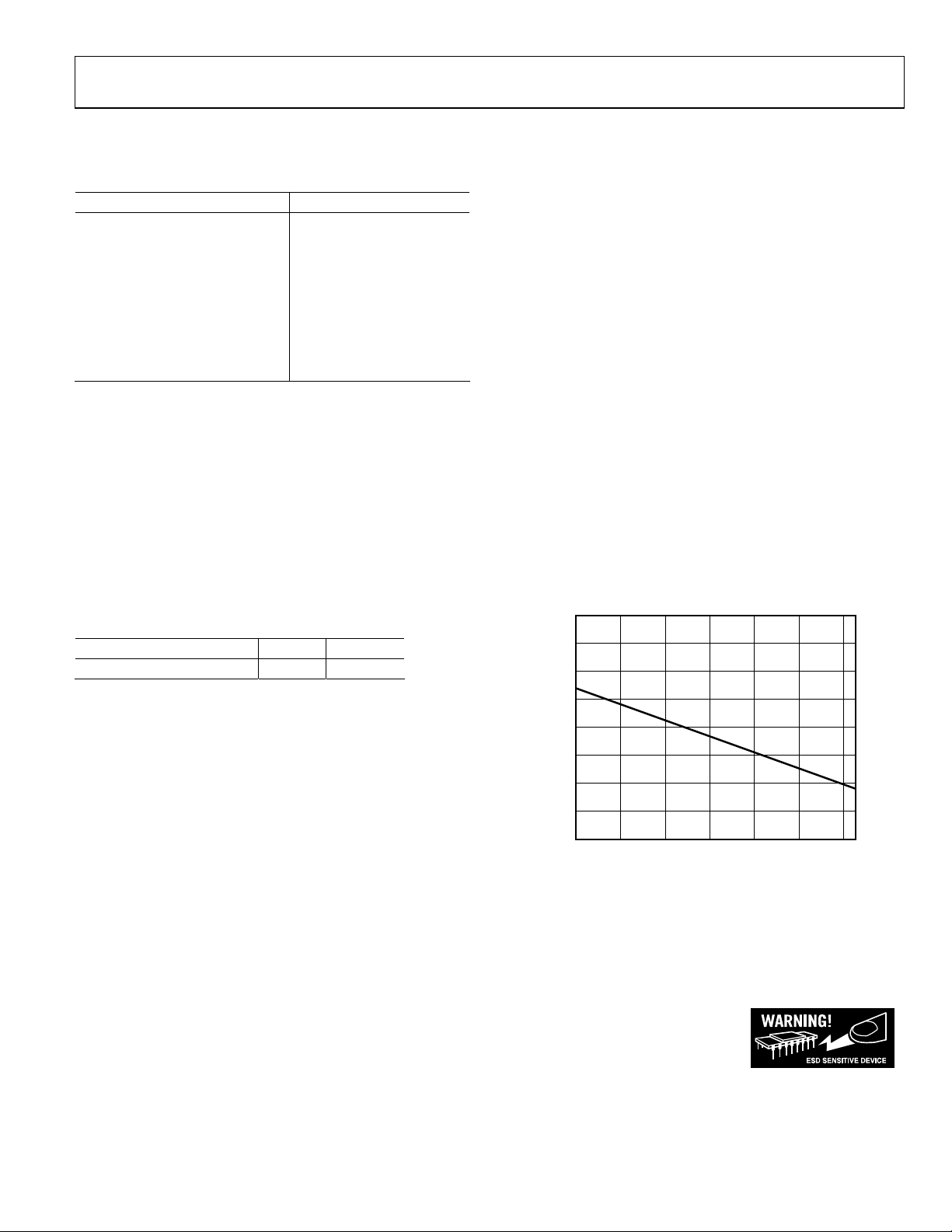

Maximum Power Dissipation

The maximum safe power dissipation in the AD8133 package is

limited by the associated rise in junction temperature (T

the die. At approximately 150°C, which is the glass transition

temperature, the plastic changes its properties. Even temporarily

exceeding this temperature limit may change the stresses that

the package exerts on the die, permanently shifting the parametric performance of the AD8133. Exceeding a junction temperature of 175°C for an extended period of time can result in

changes in the silicon devices potentially causing failure.

Unit

) on

J

The power dissipated in the package (P

quiescent power dissipation and the power dissipated in the

package due to the load drive for all outputs. The quiescent

power is the voltage between the supply pins (V

quiescent current (I

). The load current consists of differential

S

and common-mode currents flowing to the loads, as well as

currents flowing through the internal differential and commonmode feedback loops. The internal resistor tap used in the

common-mode feedback loop places a 4 kΩ differential load on

the output. RMS output voltages should be considered when

dealing with ac signals.

Airflow reduces θ

. Als o, more metal dire ctly in contact with

JA

the package leads from metal traces, through holes, ground,

and power planes reduces the θ

JA

underside of the package must be soldered to a pad on the PCB

surface that is thermally connected to a copper plane in order to

achieve the specified θ

.

JA

Figure 3 shows the maximum safe power dissipation in the

package versus ambient temperature for the 24-lead LFCSP

(70°C/W) package on a JEDEC standard 4-layer board with the

underside paddle soldered to a pad that is thermally connected

to a PCB plane. θ

4.0

3.5

3.0

2.5

2.0

1.5

1.0

MAXIMUM POWER DISSIPATION (W)

0.5

0

–40 –20 0 20 40 60 80

Figure 3. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

values are approximations.

JA

AMBIENT TEMPERATURE (°C)

) is the sum of the

D

) times the

S

. The exposed paddle on the

LFCSP

04769-0-024

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic

discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of

functionality.

Rev. 0 | Page 5 of 16

Loading...

Loading...