ANALOG DEVICES AD8124 Service Manual

Triple Differential Receiver with

V

200 Meter Adjustable Cable Equalization

FEATURES

Compensates cables to 200 meters for wideband video

All resolutions through UXGA

Fast rise and fall times

8 ns with 2 V step @ 200 meters of UTP cable

37 dB peak gain at 100 MHz

Two frequency response gain adjustment pins

High frequency peaking adjustment (V

Broadband flat gain adjustment (V

Pole location adjustment pin (V

POLE

)

Compensates for variations between cables

Can be optimized for either UTP or coaxial cable

DC output offset adjust (V

OFFSET

)

Low output offset voltage: 24 mV

Compensates both RGB and YPbPr

Two on-chip comparators with hysteresis

Can be used for common-mode sync extraction

Available in 40-lead, 6 mm × 6 mm LFCSP

APPLICATIONS

Keyboard-video-mouse (KVM)

Digital signage

RGB video over UTP cables

Professional video projection and distribution

HD video

Security video

GENERAL DESCRIPTION

The AD8124 is a triple, high speed, differential receiver and

equalizer that compensates for the transmission losses of UTP

and coaxial cables up to 200 meters in length. Various gain stages

are summed together to best approximate the inverse frequency

response of the cable. Logic circuitry inside the AD8124 controls

the gain functions of the individual stages so that the lowest

noise can be achieved at short-to-medium cable lengths. This

technique optimizes its performance for low noise, short-tomedium range applications, while at the same time provides

the high gain bandwidth required for longer cable equalization

(up to 200 meters). Each channel features a high impedance

differential input that is ideal for interfacing directly with the cable.

GAIN

)

PEAK

)

AD8124

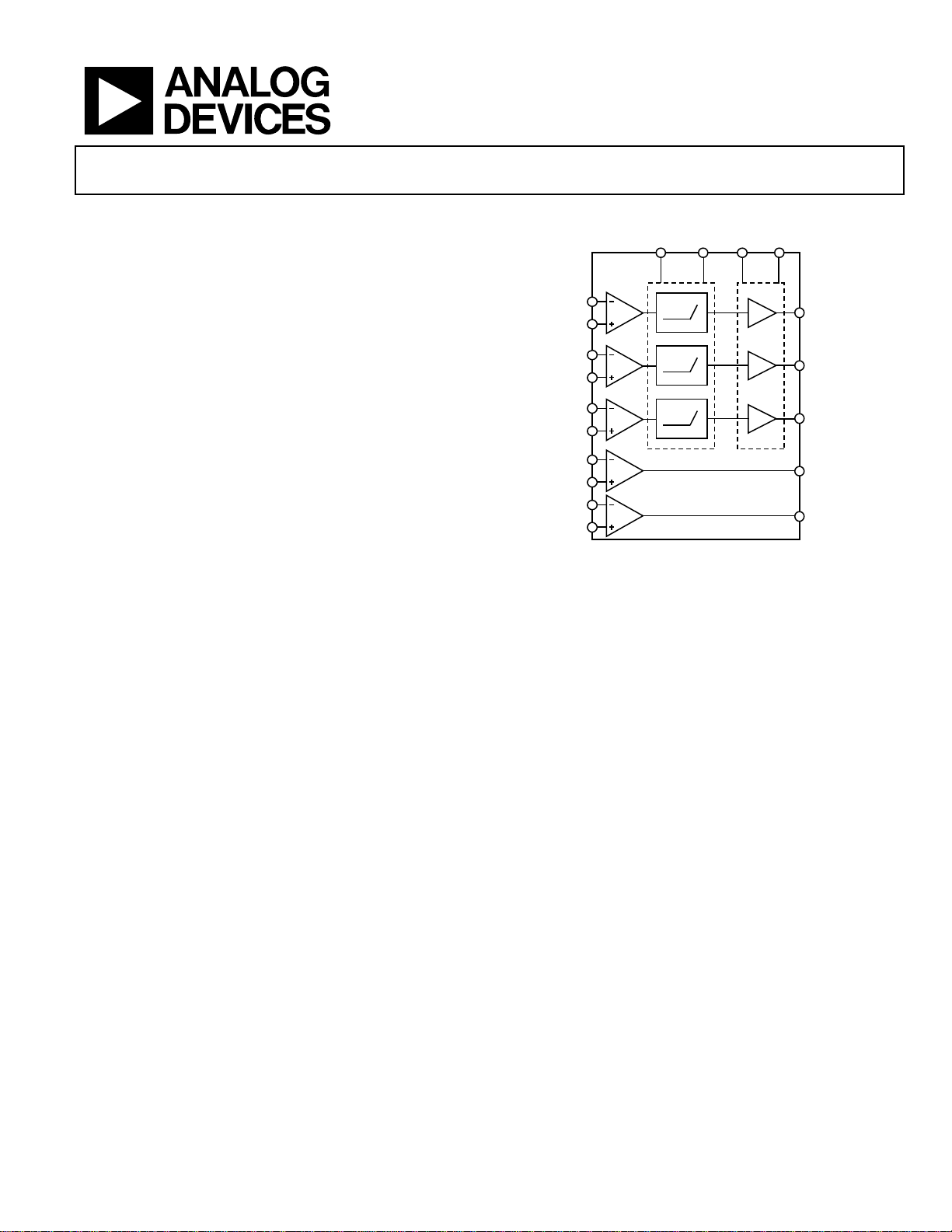

FUNCTIONAL BLOCK DIAGRAM

PEAKVPOLEVOFFSETVGAIN

AD8124

–IN

R

+IN

R

–IN

G

+IN

G

–

IN

B

+IN

B

–IN

CMP1

+IN

CMP1

–IN

CMP2

+IN

CMP2

Figure 1.

The AD8124 has three control pins for optimal cable

compensation, as well as an output offset adjust pin. Two

voltage-controlled pins are used to compensate for different

cable lengths; the V

peaking and the V

pin controls the amount of high frequency

PEAK

pin adjusts the broadband flat gain, which

GAIN

compensates for the low frequency flat cable loss.

For added flexibility, an optional pole adjustment pin, V

allows movement of the pole locations, allowing for the

compensation of different gauges and types of cable as well

as variations between different cables and/or equalizers. The

V

pin allows the dc voltage at the output to be adjusted,

OFFSET

adding flexibility for dc-coupled systems.

The AD8124 is available in a 6 mm × 6 mm, 40-lead LFCSP

and is rated to operate over the extended temperature range of

−40°C to +85°C.

OUT

OUT

OUT

OUT

OUT

R

G

B

CMP1

CMP2

POLE

09601-001

,

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2011 Analog Devices, Inc. All rights reserved.

AD8124

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Revision History ............................................................................... 2

Specifications..................................................................................... 3

Absolute Maximum Ratings............................................................ 5

Thermal Resistance ...................................................................... 5

Maximum Power Dissipation..................................................... 5

ESD Caution.................................................................................. 5

Pin Configuration and Function Description .............................. 6

Typical Performance Characteristics ............................................. 7

Theory of Operation ...................................................................... 10

Input Common-Mode Voltage Range Considerations .........10

Applications Information.............................................................. 11

Basic Operation .......................................................................... 11

Comparators ............................................................................... 11

Sync Pulse Extraction Using Comparators............................. 12

Using the V

PEAK

, V

POLE

, V

GAIN

, and V

Inputs................... 12

OFFSET

Using the AD8124 with Coaxial Cable.................................... 13

Driving 75 Ω Video Cable with the AD8124.......................... 13

Driving a Capacitive Load......................................................... 13

Power Supply Filtering............................................................... 13

Layout and Power Supply Decoupling Considerations......... 14

Power-Down ............................................................................... 14

Outline Dimensions....................................................................... 15

Ordering Guide .......................................................................... 15

REVISION HISTORY

1/11—Revision 0: Initial Version

Rev. 0 | Page 2 of 16

AD8124

SPECIFICATIONS

TA = 25°C, VS = ±5 V, RL = 150 Ω, Belden Cable (BL-7987R), V

Figure 16, unless otherwise noted.

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

DYNAMIC PERFORMANCE

10% to 90% Rise/Fall Time V

Settling Time to 2% V

–3 dB Large Signal Bandwidth V

V

= 2 V step, 200 meters Cat-5 8 ns

OUT

= 2 V step, 200 meters Cat-5 47 ns

OUT

= 2 V p-p, <10 meters Cat-5 110 MHz

OUT

= 2 V p-p, 200 meters Cat-5 52 MHz

OUT

Integrated Output Voltage Noise 200 meter setting, integrated to 160 MHz 4 mV rms

INPUT DC PERFORMANCE

Input Voltage Range −IN and +IN ±3.0 V

Maximum Differential Voltage Swing 4 V p-p

Voltage Gain ΔVO/ΔVI, V

Common-Mode Rejection Ratio (CMRR) At dc, V

At dc, V

At 1 MHz, V

GAIN

= V

PEAK

= 1.15 V, V

PEAK

PEAK

Input Resistance Common mode 4.4 MΩ

Differential 3.7 MΩ

Input Capacitance Common mode 1.0 pF

Differential 0.5 pF

Input Bias Current 2.4 μA

V

Pin Current 30 μA

OFFSET

V

Pin Current 0.5 μA

GAIN

V

Pin Current 0.4 μA

PEAK

V

Pin Current 0.4 μA

POLE

ADJUSTMENT PINS

V

Input Voltage Range Relative to GND 0 to 1.5 V

PEAK

V

Input Voltage Range Relative to GND 0 to 1.5 V

POLE

V

Input Voltage Range Relative to GND 0 to 1.5 V

GAIN

V

to OUT Gain OUT/V

OFFSET

Maximum Flat Gain V

GAIN

, range limited by output swing 1 V/V

OFFSET

= 1.5 V 1.9 dB

OUTPUT CHARACTERISTICS

Output Voltage Swing 150 Ω load −3.75 to +3.69 V

1 kΩ load −3.66 to +3.69 V

Output Offset Voltage Referred to output, V

Referred to output, V

= 1.5 V

V

POLE

Output Offset Voltage Drift Referred to output 33 μV/°C

POWER SUPPLY

Operating Voltage Range ±4.5 ±5.5 V

Positive Quiescent Supply Current 132 mA

Negative Quiescent Supply Current 126 mA

Supply Current Drift, ICC/IEE 80 μA/°C

Positive Power Supply Rejection Ratio DC, referred to output −51 dB

Negative Power Supply Rejection Ratio DC, referred to output −63 dB

Power Down, VIH (Minimum) Minimum Logic 1 voltage 1.1 V

Power Down, VIL (Maximum) Maximum Logic 0 voltage 0.8 V

Positive Supply Current, Powered Down V

Negative Supply Current, Powered Down V

PEAK

PEAK

= V

= V

GAIN

GAIN

= V

= V

OFFSET

= 0 V, V

PEAK

, V

GAIN

, and V

are set to recommended settings shown in

POLE

set for 0 meters of cable 1 V/V

= V

GAIN

= 1.15 V, V

POLE

POLE

= 0 V −86 dB

POLE

= 1.4 V, V

GAIN

GAIN

= V

PEAK

= 1.15 V, V

PEAK

= 1.4 V, V

GAIN

= 1.5 V −65 dB

POLE

= 1.5 V −50 dB

POLE

= V

= 0 V 24 mV

POLE

= 1.4 V,

GAIN

37 mV

= 0 V 1.1 μA

= 0 V 0.7 μA

Rev. 0 | Page 3 of 16

AD8124

Parameter Test Conditions/Comments Min Typ Max Unit

COMPARATORS

Output Voltage Levels VOH/V

Hysteresis V

Propagation Delay t

Rise/Fall Times t

OL

HYST

PD, LH/tPD, HL

RISE/tFALL

Output Resistance 0.03 Ω

OPERATING TEMPERATURE RANGE −40 +85 °C

3.33/0.043 V

70 mV

17.5/10.0 ns

9.3/9.3 ns

Rev. 0 | Page 4 of 16

AD8124

ABSOLUTE MAXIMUM RATINGS

Table 2.

Parameter Rating

Supply Voltage 11 V

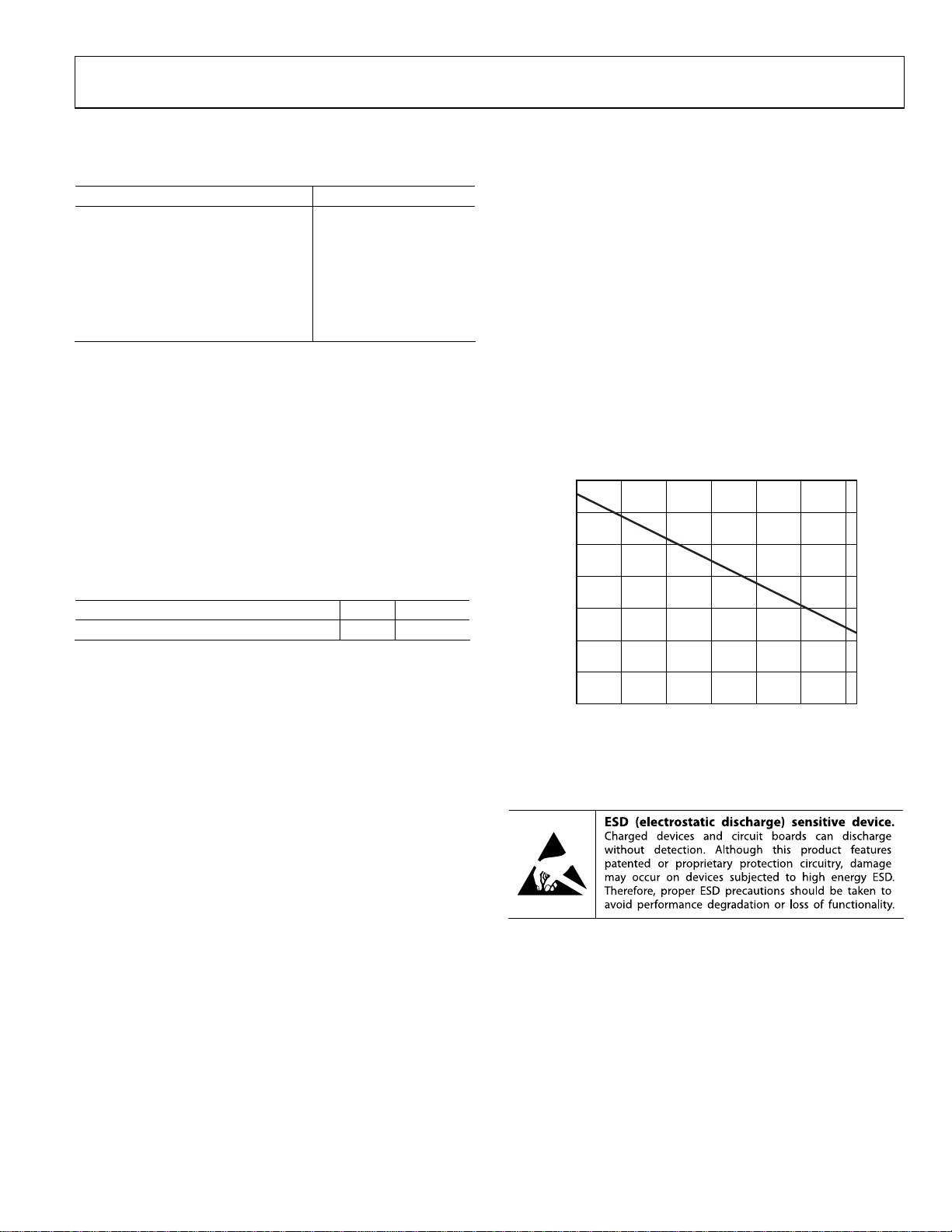

Power Dissipation See Figure 2

Input Voltage (Any Input) VS− − 0.3 V to VS+ + 0.3 V

Storage Temperature Range −65°C to +125°C

Operating Temperature Range −40°C to +85°C

Lead Temperature (Soldering, 10 sec) 300°C

Junction Temperature 150°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

THERMAL RESISTANCE

θJA is specified for the worst-case conditions; that is, θJA is

specified for the device soldered in a circuit board in still air.

voltage difference between the associated power supply and the

output voltage. The total power dissipation due to load currents

is then obtained by taking the sum of the individual power

dissipations. RMS output voltages must be used when dealing

with ac signals.

Airflow reduces θ

. In addition, more metal directly in contact

JA

with the package leads from metal traces, through holes, ground,

and power planes reduces the θ

. The exposed paddle on the

JA

underside of the package must be soldered to a pad on the PCB

surface that is thermally connected to a solid plane (usually the

ground plane) to achieve the specified θ

.

JA

Figure 2 shows the maximum safe power dissipation in the

package vs. the ambient temperature for the 40-lead LFCSP

(29°C/W) on a JEDEC standard 4-layer board with the underside

paddle soldered to a pad that is thermally connected to a PCB

plane. θ

values are approximations.

JA

7

6

5

Table 3. Thermal Resistance with the Underside Pad

Connected to the Plane

Package Type/PCB Type θJA Unit

40-Lead LFCSP/4-Layer 29 °C/W

MAXIMUM POWER DISSIPATION

The maximum safe power dissipation in the AD8124 package

is limited by the associated rise in junction temperature (T

the die. At approximately 150°C, which is the glass transition

temperature, the plastic changes its properties. Even temporarily

exceeding this temperature limit can change the stresses that the

package exerts on the die, permanently shifting the parametric

performance of the AD8124. Exceeding a junction temperature

of 175°C for an extended time can result in changes in the

silicon devices, potentially causing failure.

The power dissipated in the package (P

) is the sum of the

D

quiescent power dissipation and the power dissipated in the

package due to the load drive for all outputs. The quiescent

power is the voltage between the supply pins (V

quiescent current (I

). The power dissipation due to each load

S

) times the

S

current is calculated by multiplying the load current by the

) on

J

4

3

2

MAXIMUM POWER DISSIPATION (W)

1

0

–40 –20 0 20 40 60 80

AMBIENT TEMPERATURE (°C)

Figure 2. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

ESD CAUTION

09601-003

Rev. 0 | Page 5 of 16

Loading...

Loading...