Analog Devices AD7945, AD7943, AD7948 Datasheet

V

DD

R

FB

DGND

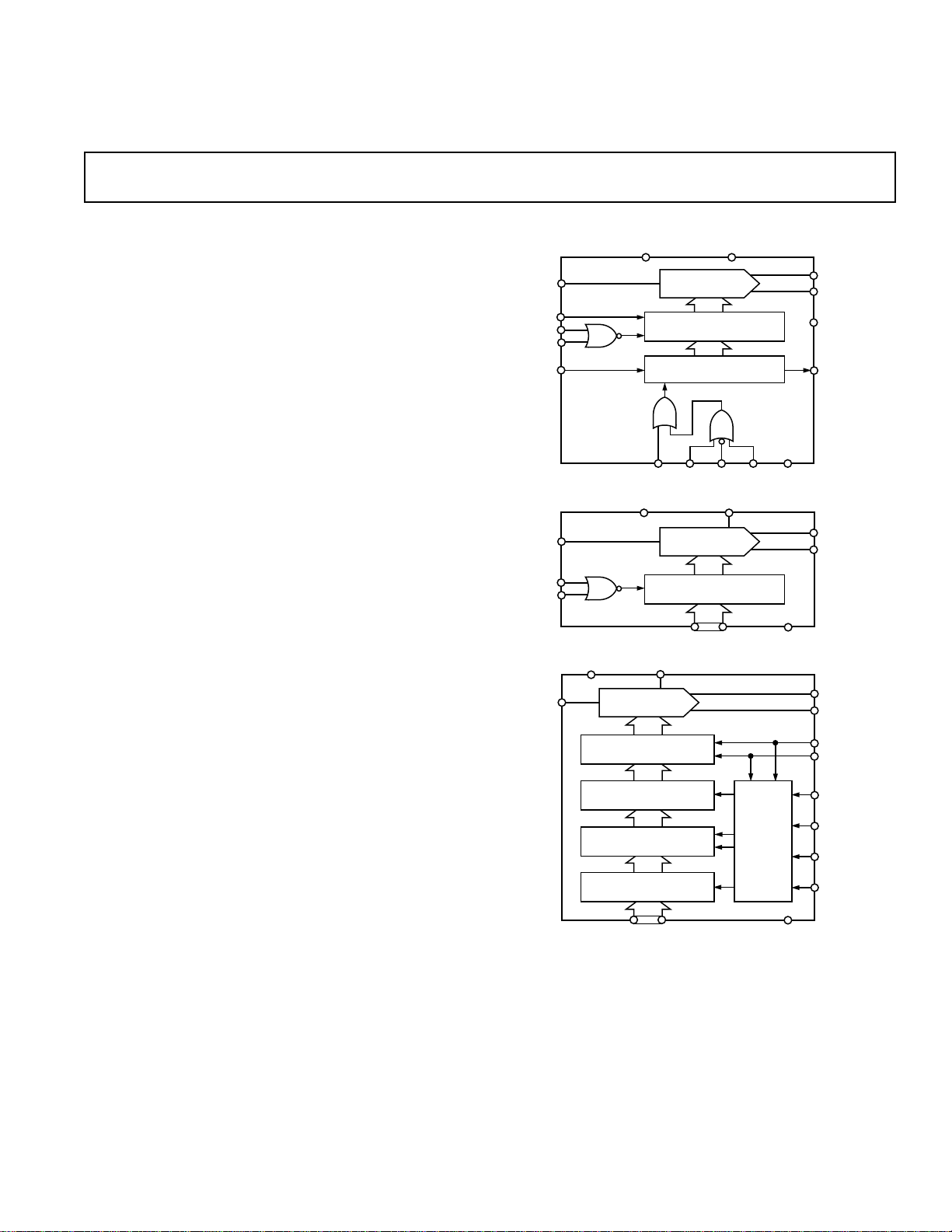

AD7948

DB7–DB0

DF/DOR

CTRL

LDAC

WR

CSLSB

CSMSB

I

OUT1

AGND

V

REF

12-BIT DAC

12

12

DATA OVERRIDE LOGIC

12

DAC REGISTER

12

INPUT REGISTERS

CONTROL

LOGIC

DATA STEERING LOGIC

8

CS

WR

V

DD

R

FB

I

OUT1

AGND

V

REF

DGNDDB11–DB0

AD7945

12-BIT DAC

12

INPUT LATCH

12

AD7943

V

DD

R

FB

I

OUT1

AGND

I

OUT2

SRO

STB1 DGNDSTB2

STB3

STB4

CLR

LD1

LD2

SRI

V

REF

12-BIT DAC

DAC REGISTER

INPUT SHIFT REGISTER

+3.3 V/+5 V Multiplying

a

FEATURES

12-Bit Multiplying DACs

Guaranteed Specifications with +3.3 V/+5 V Supply

0.5 LSBs INL and DNL

Low Power: 5 mW typ

Fast Interface

40 ns Strobe Pulsewidth (AD7943)

40 ns Write Pulsewidth (AD7945, AD7948)

Low Glitch: 60 nV-s with Amplifier Connected

Fast Settling: 600 ns to 0.01% with AD843

APPLICATIONS

Battery-Powered Instrumentation

Laptop Computers

Upgrades for All 754x Series DACs (5 V Designs)

GENERAL DESCRIPTION

The AD7943, AD7945 and AD7948 are fast 12-bit multiplying

DACs that operate from a single +5 V supply (Normal Mode)

and a single +3.3 V to +5 V supply (Biased Mode). The

AD7943 has a serial interface, the AD7945 has a 12-bit parallel

interface, and the AD7948 has an 8-bit byte interface. They will

replace the industry-standard AD7543, AD7545 and AD7548

in many applications, and they offer superior speed and power

consumption performance.

The AD7943 is available in 16-lead DIP, 16-lead SOP (Small

Outline Package) and 20-lead SSOP (Shrink Small Outline

Package).

The AD7945 is available in 20-lead DIP, 20-lead SOP and 20lead SSOP.

The AD7948 is available in 20-lead DIP, 20-lead SOP and 20lead SSOP.

12-Bit DACs

AD7943/AD7945/AD7948

FUNCTIONAL BLOCK DIAGRAMS

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1998

AD7943/AD7945/AD7948–SPECIFICATIONS

1

NORMAL MODE

(AD7943: V

AD7945, AD7948: VDD = +4.5 V to +5.5 V; V

Parameter B Grades2T Grade

= +4.5 V to +5.5 V; V

DD

= AGND = 0 V; V

IOUT1

IOUT1

= V

REF

2, 3

= AGND = 0 V; V

IOUT2

= +10 V; TA = T

MIN

= +10 V; TA = T

REF

to T

, unless otherwise noted.)

MAX

MIN

to T

MAX

Units Test Conditions/Comments

, unless otherwise noted.

ACCURACY

Resolution 12 12 Bits 1 LSB = V

/212= 2.44 mV when V

REF

Relative Accuracy ±0.5 ±0.5 LSB max

Differential Nonlinearity ± 0.5 ±0.5 LSB max All Grades Guaranteed Monotonic over

Temperature

Gain Error

T

to T

MIN

Gain Temperature Coefficient

MAX

4

±2 ±2 LSB max

2 2 ppm FSR/°C typ

5 5 ppm FSR/°C max

Output Leakage Current

I

OUT1

@ +25°C 10 10 nA max See Terminology Section

T

MIN

to T

MAX

100 100 nA max Typically 20 nA over Temperature

REFERENCE INPUT

Input Resistance 6 6 kΩ min Typical Input Resistance = 9 kΩ

12 12 kΩ max

DIGITAL INPUTS

V

, Input High Voltage 2.4 2.4 V min

INH

V

, Input Low Voltage 0.8 0.8 V max

INL

I

, Input Current ±1 ±1 µA max

INH

CIN, Input Capacitance

4

10 10 pF max

DIGITAL OUTPUT (AD7943 SRO) For 1 CMOS Load

Output Low Voltage (V

Output High Voltage (VOH)V

) 0.2 0.2 V max

OL

– 0.2 V

DD

– 0.2 V min

DD

POWER REQUIREMENTS

V

Range 4.5/5.5 4.5/5.5 V min/V max

DD

Power Supply Sensitivity

∆Gain/∆V

I

(AD7943) 5 5 µA max V

DD

DD

4

–75 –75 dB typ

= VDD – 0.1 V min, V

INH

= 0.1 V max.

INL

SRO Open Circuit. No STB Signal. Typically

1 µA. Typically 100 µA with a 1 MHz STB

Frequency. At Input Levels of 0.8 V and 2.4 V,

I

Is Typically 2.5 mA.

I

(AD7945, AD7948) 5 5 µA max V

DD

DD

= VDD – 0.1 V min, V

INH

= 0.1 V max.

INL

Typically 1 µA. At Input Levels of 0.8 V and

2.4 V, IDD Is Typically 2.5 mA.

NOTES

1

The AD7943, AD7945 and AD7948 are specified in the normal current mode configuration and in the biased current mode for single-supply applications.

Figures 14 and 15 are examples of normal mode operation.

2

Temperature ranges as follows: B Grades: –40°C to +85°C; T Grade: –55°C to +125°C.

3

The T Grade applies to the AD7945 only.

4

Guaranteed by design.

Specifications subject to change without notice.

REF

=10V

–2–

REV. B

AD7943/AD7945/AD7948

SPECIFICATIONS

1

BIASED MODE

wise noted. AD7945, AD7948: VDD = +3 V to +5.5 V; V

(AD7943: VDD = +3 V to +5.5 V; V

IOUT1

Parameter A Grades2Units Test Conditions/Comments

ACCURACY

Resolution 12 Bits 1 LSB = (V

Relative Accuracy ±1 LSB max

Differential Nonlinearity ±0.9 LSB max All Grades Guaranteed Monotonic

Gain Error @ +25°C ±3 LSB max

to T

T

MIN

Gain Temperature Coefficient

MAX

3

±4 LSB max

2 ppm FSR/°C typ

5 ppm FSR/°C max

Output Leakage Current See Terminology Section

I

OUT1

@ +25°C 10 nA max

to T

T

MIN

MAX

100 nA max Typically 20 nA over Temperature

Input Resistance This Varies with DAC Input Code

@ I

Pin (AD7943) 6 kΩ min

OUT2

@ AGND Pin (AD7945, AD7948) 6 kΩ min

DIGITAL INPUTS

V

, Input High Voltage @ VDD = +5 V 2.4 V min

INH

, Input High Voltage @ VDD = +3.3 V 2.1 V min

V

INH

, Input Low Voltage @ VDD = +5 V 0.8 V max

V

INL

, Input Low Voltage @ VDD = +3.3 V 0.6 V max

V

INL

, Input Current ±1 µA max

I

INH

CIN, Input Capacitance

3

10 pF max

DIGITAL OUTPUT (SRO) For 1 CMOS Load

Output Low Voltage (V

Output High Voltage (VOH)V

) 0.2 V max

OL

DD

POWER REQUIREMENTS

Range 3.0/5.5 V min/V max

V

DD

Power Supply Sensitivity

∆Gain/∆V

(AD7943) 5 µA max V

I

DD

(AD7945, AD7948) 5 µA max V

I

DD

NOTES

1

These specifications apply with the devices biased up at 1.23 V for single supply applications. The model numbering reflects this by means of a “–B” suffix

(for example: AD7943AN-B). Figure 16 is an example of Biased Mode Operation.

2

Temperature ranges as follows: A Versions: –40° C to +85° C.

3

Guaranteed by design.

Specifications subject to change without notice.

DD

3

–75 dB typ

=V

IOUT1

= AGND = 1.23 V; V

IOUT2

= AGND = 1.23 V; V

– 0.2 V min

= +0 V to 2.45 V; TA = T

REF

= +0 V to 2.45 V; TA = T

REF

V

IOUT1

over Temperature

= VDD – 0.1 V min, V

INH

SRO Open Circuit; No STB Signal; Typically

1 µA. Typically 100 µA with 1 MHz STB

Frequency.

= VDD – 0.1 V min, V

INH

Typically 1 µA.

to T

MIN

MAX

– V

IOUT1

REF)

= 1.23 V and V

to T

MIN

, unless other-

MAX

, unless otherwise noted.)

12

/2

= 300 µV When

= 0 V

REF

= 0.1 V max.

INL

= 0.1 V max.

INL

REV. B

–3–

AD7943/AD7945/AD7948

AC PERFORMANCE CHARACTERISTICS

NORMAL MODE

0 V. V

= 6 V rms, 1 kHz sine wave; TA = T

REF

(AD7943: VDD = +4.5 V to +5.5 V; V

to T

MIN

cluded for Design Guidance and are not subject to test.

Parameter B Grades T Grade Units Test Conditions/Comments

DYNAMIC PERFORMANCE

Output Voltage Settling Time 600 700 ns typ To 0.01% of Full-Scale Range. V

Digital to Analog Glitch Impulse 60 60 nV-s typ Measured with V

Multiplying Feedthrough Error –75 –75 dB max DAC Latch Loaded with All 0s

Output Capacitance 60 60 pF max All 1s Loaded to DAC

30 30 pF max All 0s Loaded to DAC

Digital Feedthrough (AD7943) 5 5 nV-s typ Feedthrough to the DAC Output with LD1,

Digital Feedthrough (AD7945, AD7948) 5 5 nV-s typ Feedthrough to the DAC Output with CS

Total Harmonic Distortion –83 –83 dB typ

Output Noise Spectral Density

@ 1 kHz 35 35 nV/√Hz typ All 1s Loaded to DAC. V

Specifications subject to change without notice.

= V

IOUT1

; DAC output op amp is AD843; unless otherwise noted.) These characteristics are in-

MAX

= AGND = 0 V. AD7945, AD7948: VDD = +4.5 V to +5.5 V; V

IOUT2

IOUT1

=AGND =

REF

+10 V; DAC Latch Alternately Loaded with

All 0s and All 1s

= 0 V. DAC Latch

REF

Alternately Loaded with All 0s and All 1s

LD2 High and Alternate Loading of All 0s

and All 1s into the Input Shift Register

High and Alternate Loading of All 0s and

All 1s to the DAC Bus

= 0 V. Output

REF

Op Amp Is OP07

=

AC PERFORMANCE CHARACTERISTICS

BIASED MODE

1.23 V. V

= 1 kHz, 2.45 V p-p, sine wave biased at 1.23 V; DAC output op amp is AD820; TA = T

REF

(AD7943: V

characteristics are included for Design Guidance and are not subject to test.

Parameter A Grades Units Test Conditions/Comments

DYNAMIC PERFORMANCE

Output Voltage Settling Time 5 µs typ To 0.01% of Full-Scale Range. V

Digital to Analog Glitch Impulse 60 nV-s typ V

Multiplying Feedthrough Error –75 dB max DAC Latch Loaded with All 0s

Output Capacitance 60 pF max All 1s Loaded to DAC

Digital Feedthrough 5 nV-s typ Feedthrough to the DAC Output with LD1, LD2

Digital Feedthrough (AD7945, AD7948) 5 nV-s typ Feedthrough to the DAC Output with CS High

Total Harmonic Distortion –83 dB typ

Output Noise Spectral Density

@ 1 kHz 25 nV/√Hz typ All 1s Loaded to DAC. V

Specifications subject to change without notice.

= +3 V to +5.5 V; V

DD

= V

IOUT1

= AGND = 1.23 V. AD7945, AD7948: VDD = +3 V to +5.5 V; V

IOUT2

to T

MIN

; unless otherwise noted.) These

MAX

DAC Latch Alternately Loaded with All 0s and All 1s

= 1.23 V. DAC Register Alternately Loaded

REF

with All 0s and All 1s

30 pF max All 0s Loaded to DAC

High and Alternate Loading of All 0s and All 1s

into the Input Shift Register

and Alternate Loading of All 0s and All 1s to the

DAC Bus

= 1.23 V

REF

REF

= AGND =

IOUT1

= 0 V

REV. B–4–

AD7943/AD7945/AD7948

1

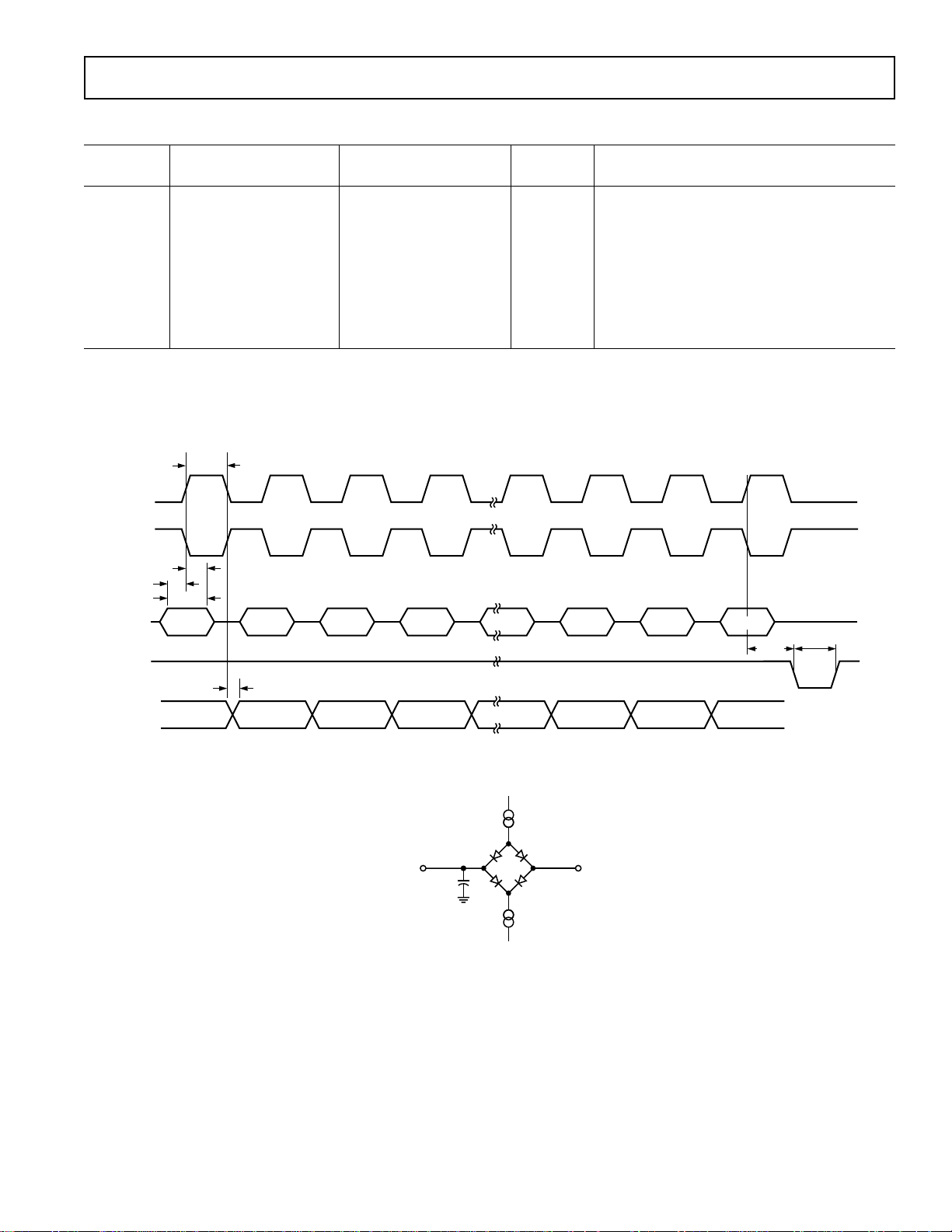

AD7943 TIMING SPECIFICATIONS

(TA = T

Limit @ Limit @

Parameter VDD = +3 V to +3.6 V VDD = +4.5 V to +5.5 V Units Description

2

t

STB

t

DS

t

DH

t

SRI

t

LD

t

CLR

t

ASB

3

t

SV

NOTES

1

All input signals are specified with tr = tf = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V. tr and tf should not exceed 1 µs on any digital input.

2

STB mark/space ratio range is 60/40 to 40/60.

3

t

is measured with the load circuit of Figure 2 and defined as the time required for the output to cross 0.8 V or 2.4 V.

SV

Specifications subject to change without notice.

STB1,

STB2,

STB4

60 40 ns min STB Pulsewidth

15 10 ns min Data Setup Time

35 25 ns min Data Hold Time

55 35 ns min SRI Data Pulsewidth

55 35 ns min Load Pulsewidth

55 35 ns min CLR Pulsewidth

0 0 ns min Min Time Between Strobing Input Shift

60 35 ns max STB Clocking Edge to SRO Data Valid Delay

t

STB

MIN

to T

, unless otherwise noted)

MAX

Register and Loading DAC Register

STB3

SRI

LD1,

LD2,

CLR

SRO

t

DH

t

DS

t

SRI

DB11(N)

(MSB)

DB10(N)

t

SV

DB10(N–1)

Figure 1. AD7943 Timing Diagram

I

OL

+2.1V

I

OH

TO OUTPUT

PIN

50pF

1.6mA

C

L

200mA

Figure 2. Load Circuit for Digital Output Timing Specifications

DB0(N)

t

DB0(N–1)

ASB

t

, t

LD

CLR

REV. B –5–

Loading...

Loading...